(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau

(43) International Publication Date

13 October 2011 (13.10.2011)

(10) International Publication Number

**WO 2011/125566 A1**

(51) International Patent Classification:

**H03K 3/356** (2006.01)    **H03K 23/00** (2006.01)

**H03K 19/0175** (2006.01)    **H03K 23/54** (2006.01)

(21) International Application Number:

**PCT/JP2011/057496**

(22) International Filing Date:

**18 March 2011 (18.03.2011)**

(25) Filing Language:

**English**

(26) Publication Language:

**English**

(30) Priority Data:

**2010-090296**    **9 April 2010 (09.04.2010)**    **JP**

(71) Applicant (for all designated States except US): **SEMICONDUCTOR ENERGY LABORATORY CO., LTD.**

[JP/JP]; 398, Hase, Atsugi-shi, Kanagawa, 2430036 (JP).

(72) Inventors; and

(75) Inventors/Applicants (for US only): **TAKAHASHI, Kei**

[JP/JP]; c/o SEMICONDUCTOR ENERGY LABORATORY CO., LTD., 398, Hase, Atsugi-shi, Kanagawa, 2430036 (JP). **ITO, Yoshiaki**.

(81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PE, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

Published:

— with international search report (Art. 21(3))

(54) Title: DIVIDER CIRCUIT

**FIG. 1**

(57) Abstract: A divider circuit includes a shift register which generates  $2X$  ( $X$  is a natural number greater than or equal to 2) pulse signals in accordance with a first clock signal or a second clock signal and outputs them, and a divided signal output circuit which generates a signal to be a third clock signal with a cycle  $X$  times longer than a cycle of the first clock signal in accordance with the  $2X$  pulse signals and outputs it. The divided signal output circuit includes  $X$  first transistors which control whether voltage of the signal to be the third clock signal is set to first voltage; and  $X$  second transistors which control whether voltage of the signal to be the third clock signal is set to second voltage.

**WO 2011/125566 A1**

## DESCRIPTION

## DIVIDER CIRCUIT

## 5 TECHNICAL FIELD

[0001]

One embodiment of the present invention relates to a divider circuit.

## BACKGROUND ART

10 [0002]

In recent years, a divider circuit has been used for driving a digital circuit with the use of a plurality of clock signals each with a different cycle from each other.

[0003]

As an example of a conventional divider circuit, a divider circuit including a 15 flip-flop can be given (e.g., Patent Document 1).

[Reference]

[Patent Document]

[0004]

[Patent Document 1] Japanese Published Patent Application No. H05-048432

20

## DISCLOSURE OF INVENTION

[0005]

For example, although the conventional divider circuit including a flip-flop, which is disclosed in Patent Document 1, can have a simple circuit configuration, a 25 malfunction might occur in the case where a clock signal with a short cycle is divided. For example, since the conventional divider circuit including a flip-flop generates an output signal by selectively outputting power supply voltage, operation speed is slow, and in the case where a clock signal with a short cycle is generated by the divider circuit, a malfunction might occur and a clock signal is not generated in some cases.

30 [0006]

One embodiment of the present invention is to prevent a malfunction in dividing operation of a divider circuit.

[0007]

According to one embodiment of the present invention, generated is a plurality of pulse signals which are voltage signals each having a value set in accordance with voltage of an input clock signal, and generated is a clock signal with a cycle  $N$  times ( $N$  is a natural number greater than or equal to 2) longer than a cycle of the input clock signal, with the use of the plurality of generated pulse signals.

[0008]

One embodiment of the present invention is a divider circuit including a shift register which is supplied with a first clock signal and a second clock signal, generates 10  $2X$  ( $X$  is a natural number greater than or equal to 2) pulse signals sequentially outputting pulses, in accordance with the first clock signal and the second clock signal, and outputs the generated  $2X$  pulse signals; and a divided signal output circuit which generates a signal to be a third clock signal with a cycle  $X$  times longer than a cycle of the first clock signal, in accordance with the  $2X$  pulse signals, and outputs the generated 15 signal to be the third clock signal. The divided signal output circuit includes  $X$  first transistors each having a source, a drain, and a gate, in which different pulse signal among the first to  $X$ -th pulse signals of the  $2X$  pulse signals is input to the respective gates of the  $X$  first transistors. In other words, the first to  $X$ -th pulse signals among the  $2X$  pulse signals are separately input to the respective gates of the  $X$  first transistors. 20 The  $X$  first transistors control whether voltage of a signal to be the third clock signal is set to first voltage; and  $X$  second transistors each having a source, a drain, and a gate, in which different pulse signal among the  $(X + 1)$ -th to  $2X$ -th pulse signals of the  $2X$  pulse signals is input to the respective gates of the  $X$  second transistors. In other words, the  $(X + 1)$ -th to  $2X$ -th pulse signals of the  $2X$  pulse signals are separately input to the 25 respective gates of the  $X$  second transistors. The  $X$  second transistors control whether voltage of the signal to be the third clock signal is set to second voltage.

[0009]

One embodiment of the present invention is a divider circuit including a first unit divider circuit which is supplied with a first clock signal and a second clock signal 30 and generates a third clock signal with a cycle  $X$  times ( $X$  is a natural number greater than or equal to 2) longer than a cycle of the first clock signal; and a second unit divider

circuit which is supplied with the third clock signal and generates a fourth clock signal with a cycle  $K$  times ( $K$  is a natural number greater than or equal to 2) longer than the cycle of the third clock signal in accordance with the third clock signal. The first unit divider circuit includes a shift register which generates  $2X$  ( $X$  is a natural number greater than or equal to 2) pulse signals sequentially outputting pulses, in accordance with the first clock signal and the second clock signal, and outputs the generated  $2X$  pulse signals; and a divided signal output circuit which generates a voltage signal in accordance with the  $(2 \times X)$  pulse signals, and outputs the generated voltage signal as the third clock signal. The divided signal output circuit includes  $X$  first transistors each having a source, a drain, and a gate, in which different pulse signal among the first to  $X$ -th pulse signals of the  $2X$  pulse signals is input to the respective gates of the  $X$  first transistors. In other words, the first to  $X$ -th pulse signals among the  $2X$  pulse signals are separately input to the respective gates of the  $X$  first transistors. The  $X$  first transistors control whether voltage of the voltage signal is set to first voltage, and  $X$  second transistors each having a source, a drain, and a gate, in which different pulse signal among the  $(X + 1)$ -th to  $2X$ -th pulse signals of the  $2X$  pulse signals is input to the respective gates of the  $X$  second transistors. In other words, the  $(X + 1)$ -th to  $2X$ -th pulse signals of the  $2X$  pulse signals are separately input to the respective gates of the  $X$  second transistors. The  $X$  second transistors control whether voltage of the voltage signal is set to second voltage.

[0010]

According to one embodiment of the present invention, a malfunction can be prevented even in operation of dividing a clock signal with a short cycle.

25 BRIEF DESCRIPTION OF DRAWINGS

[0011]

In the accompanying drawings:

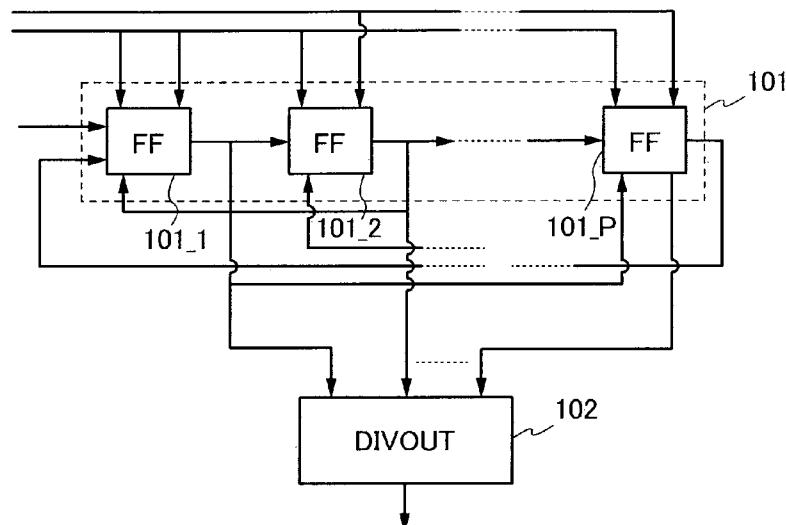

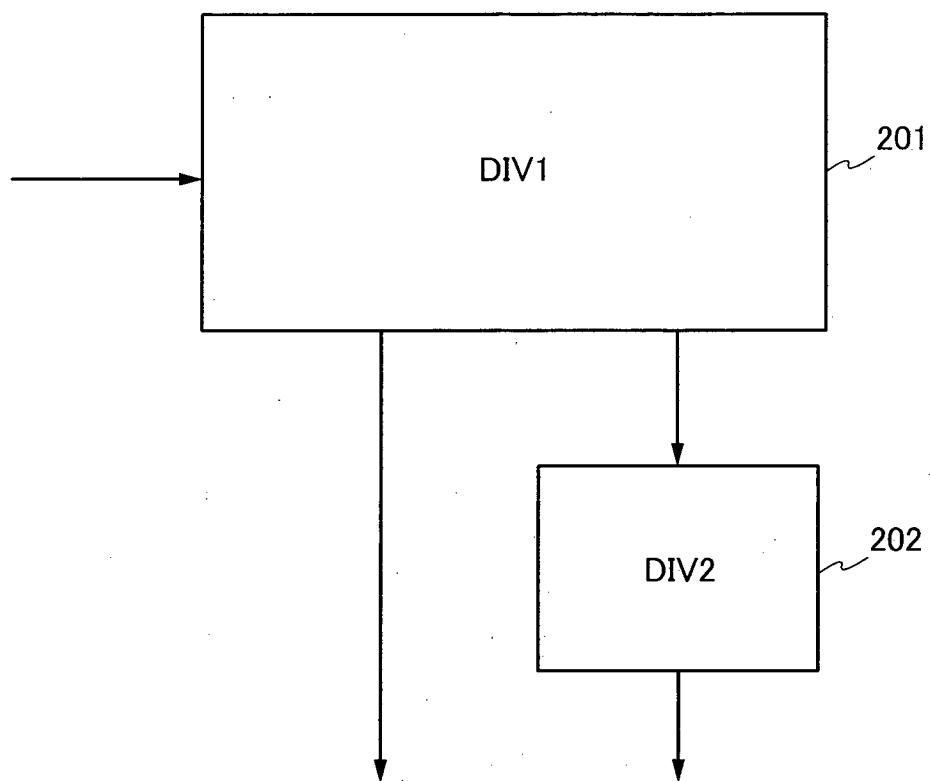

FIG. 1 is a block diagram illustrating an example of a structure of a divider circuit in Embodiment 1;

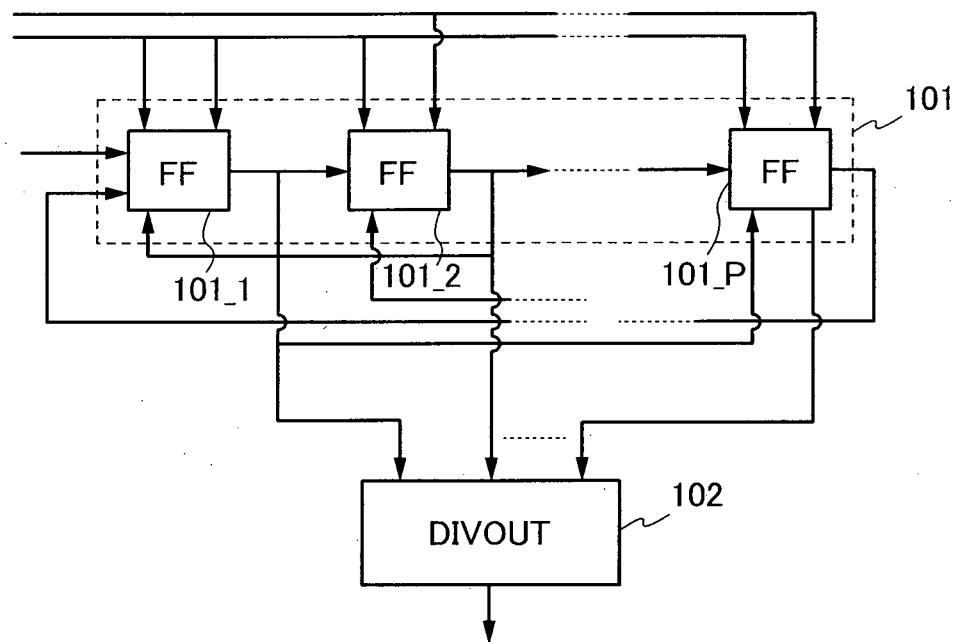

30 FIGS. 2A to 2C each illustrate an example of a structure of a shift register in a divider circuit in Embodiment 2;

FIGS. 3A and 3B each illustrate an example of a structure of a divided signal output circuit in a divider circuit in Embodiment 2;

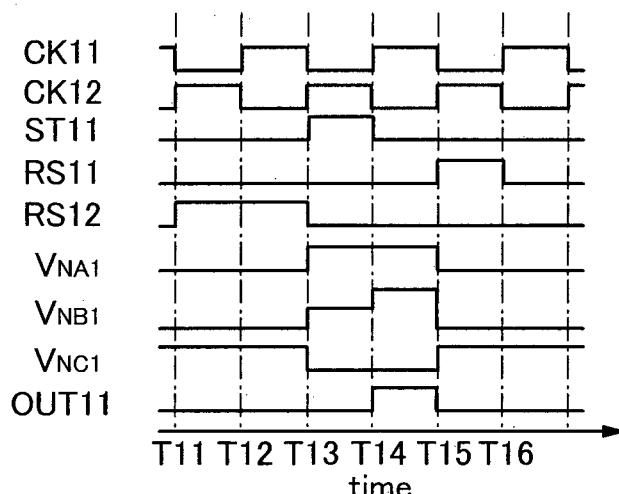

FIGS. 4A to 4C are timing charts each showing an example of operation of a shift register in a divider circuit in Embodiment 2;

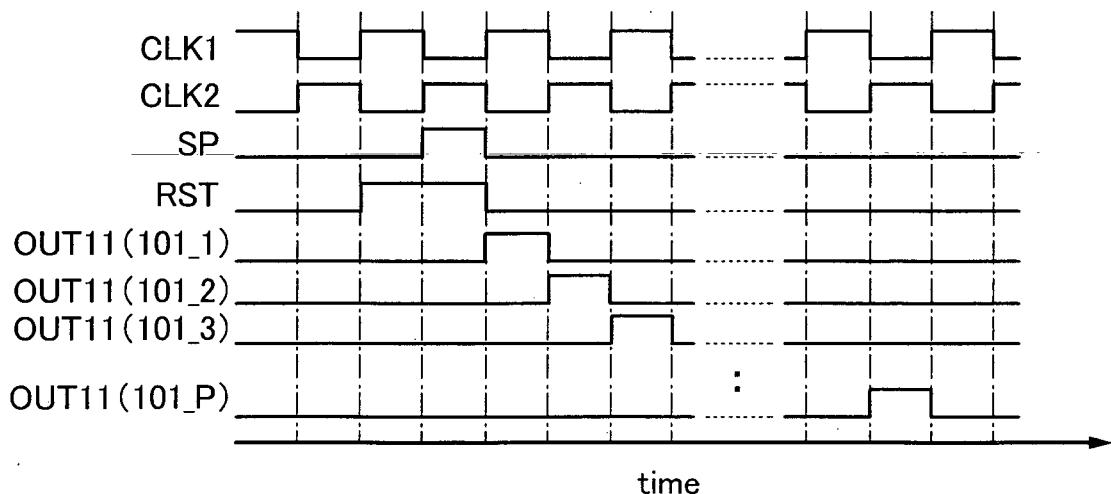

5 FIG. 5 is a timing chart showing an example of operation of a divided signal output circuit in a divider circuit in Embodiment 2;

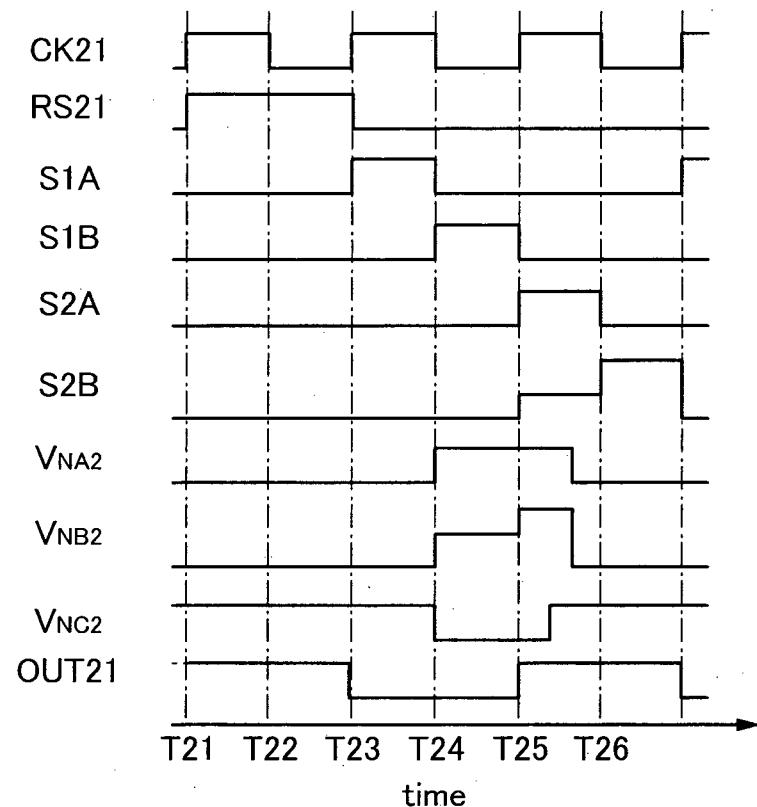

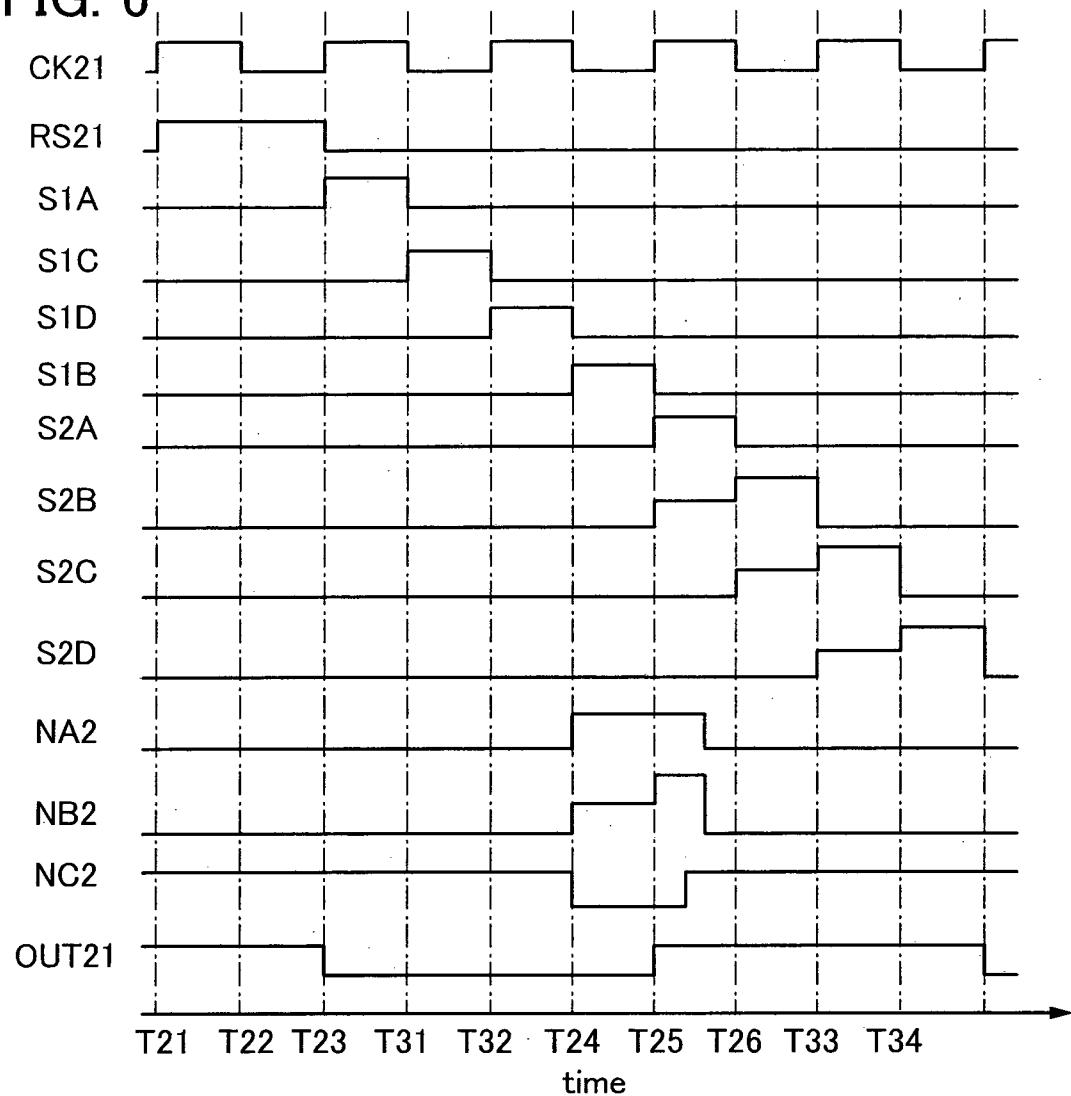

FIG. 6 is a timing chart showing an example of operation of a divided signal output circuit in a divider circuit in Embodiment 2;

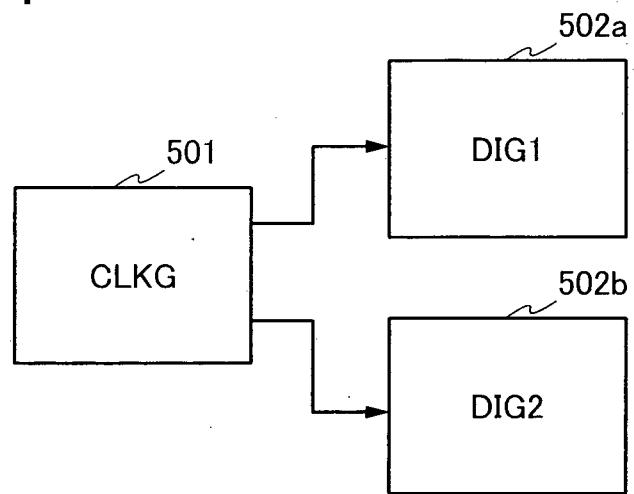

10 FIG. 7 is a block diagram illustrating an example of a structure of a divider circuit in Embodiment 3;

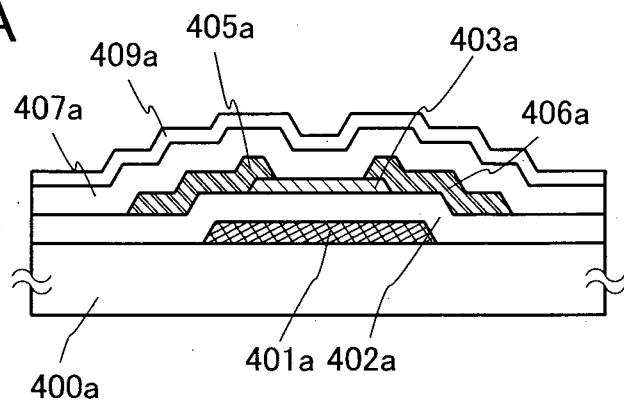

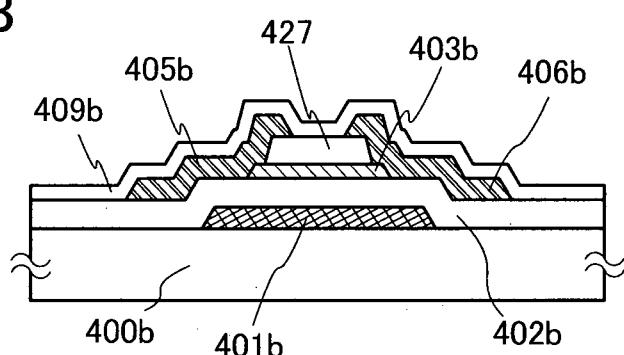

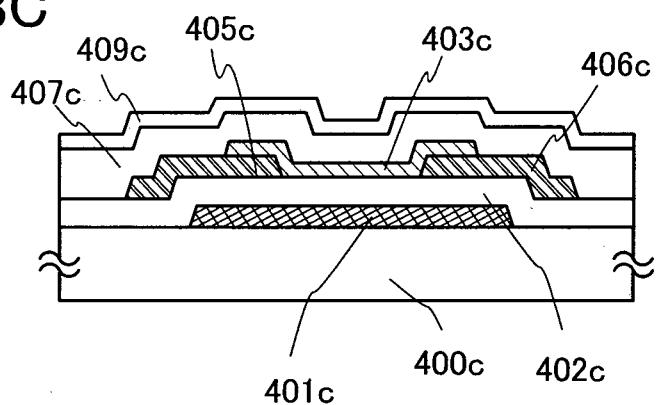

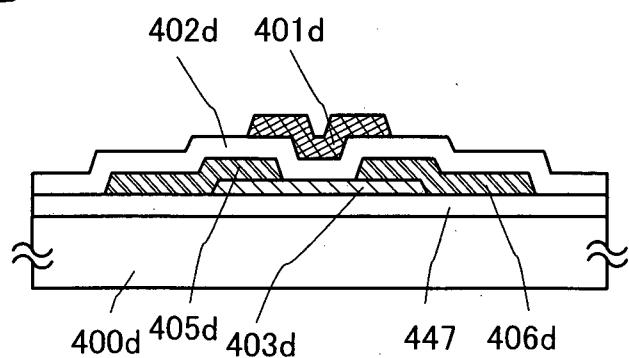

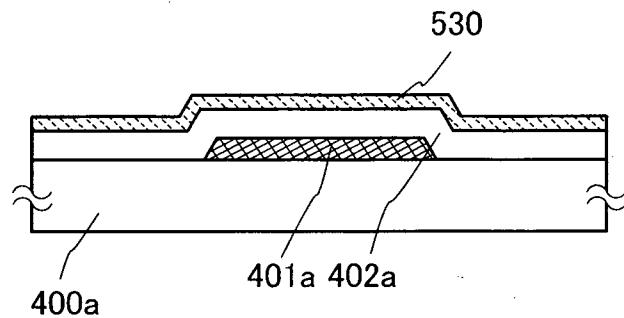

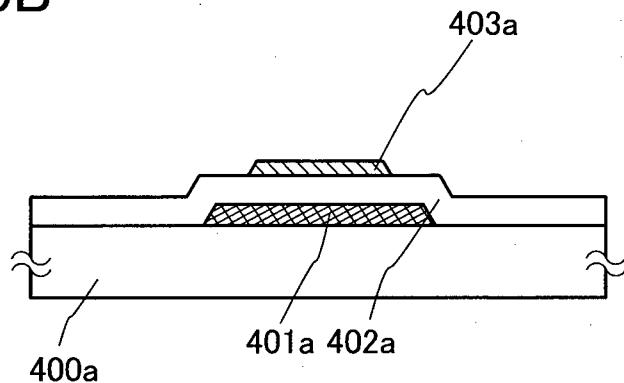

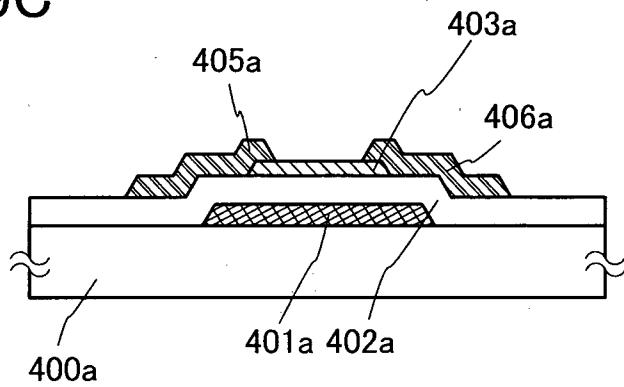

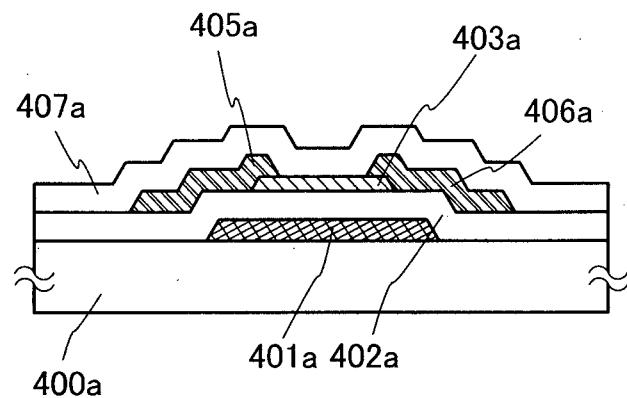

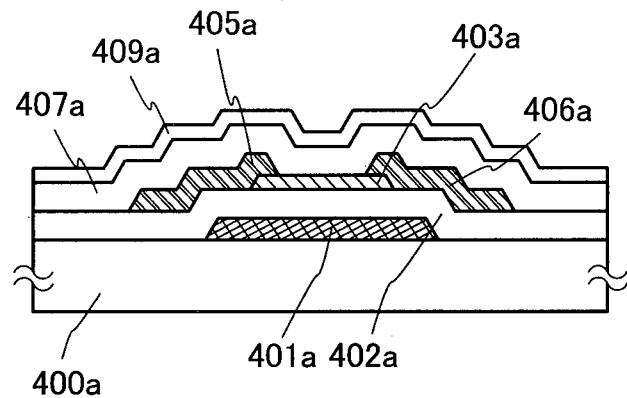

FIGS. 8A to 8D are cross-sectional schematic views each illustrating an example of a structure of a transistor in Embodiment 4;

FIGS. 9A to 9C are cross-sectional schematic views illustrating a method for manufacturing the transistor illustrated in FIG. 8A;

15 FIGS. 10A and 10B are cross-sectional schematic views illustrating a method for manufacturing the transistor illustrated in FIG. 8A; and

FIG. 11 is a block diagram illustrating an example of a structure of a semiconductor device in Embodiment 5.

## 20 BEST MODE FOR CARRYING OUT THE INVENTION

[0012]

Hereinafter, examples of embodiments of the present invention will be described with reference to the drawings. Note that the present invention is not limited to the following description and it will be easily understood by those skilled in the art that modes and details can be modified in various ways without departing from the spirit and the scope of the present invention. Therefore, the present invention should not be interpreted as being limited to the description of the embodiments to be given below.

[0013]

30 Note that contents of the embodiments can be combined with or replaced with each other as appropriate.

[0014]

## (Embodiment 1)

In this embodiment, a divider circuit including a shift register will be described.

[0015]

5 A structure of the divider circuit of this embodiment will be described with reference to FIG. 1. FIG. 1 is a block diagram illustrating an example of the structure of the divider circuit of this embodiment.

[0016]

10 The divider circuit illustrated in FIG. 1 includes a shift register 101 and a divided signal output circuit (also referred to as DIVOUT) 102.

[0017]

15 A clock signal is input to the shift register 101. For example, a clock signal CLK1 (also referred to as a signal CLK1) and a clock signal CLK2 (also referred to as a signal CLK2) are input to the shift register 101 as the clock signal. Further, the shift register 101 outputs  $2X$  ( $X$  is a natural number greater than or equal to 2) pulse signals.

[0018]

20 As a signal in the divider circuit of this embodiment, for example, a signal with voltage can be used. As the signal with voltage (also referred to as a voltage signal), an analog signal or a digital signal, which has at least first voltage and second voltage, can be used. For example, a binary digital signal such as a clock signal becomes at a low level and a high level, thereby having the first voltage (low-level voltage) and the second voltage (high-level voltage). Further, each of the high-level voltage and the low-level voltage preferably has a fixed value. However, since noise or the like has an influence on an electronic circuit, each of the high-level voltage and the low-level voltage does not necessarily have a fixed value and may have a value within a fixed range where a value can be seen as substantially equivalent. Further, as the signal in the divider circuit of this embodiment, a signal having first to third voltages may be used. As the third voltage, for example, voltage higher than or equal to the second voltage can be used.

25

30 [0019]

Note that voltage generally refers to a difference between potentials at two points (also referred to as a potential difference). However, values of both a voltage

and a potential are represented using volt (V) in a circuit diagram or the like in some cases, so that it is difficult to discriminate between them. Thus, in this specification, a potential difference between a potential at one point and a reference potential is sometimes used as a voltage at the point unless otherwise specified.

5 [0020]

The signal CLK1 and the signal CLK2 are clock signals whose waveforms are different from each other by a 1/2 cycle.

[0021]

10 The shift register 101 includes sequential circuits (also referred to as FFs) (sequential circuits 101\_1 to 101\_P) of  $P$  ( $P = 2 \times X$ ) stages, which includes  $P$  sequential circuits.

[0022]

15 The signal CLK1 or the signal CLK2 is input to the sequential circuits. Further, the sequential circuits output a signal having voltage set in accordance with the input clock signal as an output signal. The sequential circuit includes a transistor for controlling voltage of the output signal, for example.

[0023]

Note in the divider circuit, the transistor includes at least a source, a drain, and a gate unless otherwise specified.

20 [0024]

A source refers to a source region, part of or the whole of a source electrode, or part of or the whole of a source wiring. A conductive layer having a function of both a source electrode and a source wiring is referred to as a source in some cases without distinction between a source electrode and a source wiring.

25 [0025]

A drain refers to a drain region, part of or the whole of a drain electrode, or part of or the whole of a drain wiring. A conductive layer having a function of both a drain electrode and a drain wiring is referred to as a drain in some cases without distinction between a drain electrode and a drain wiring.

30 [0026]

A gate refers to part of or the whole of a gate electrode, or part of or the whole of a gate wiring. A conductive layer having a function of both a gate electrode and a

gate wiring is referred to as a gate in some cases without distinction between a gate electrode and a gate wiring.

[0027]

A source and a drain of a transistor interchange with each other depending on a 5 structure, an operation condition, or the like of a transistor in some cases.

[0028]

As a transistor in the divider circuit, a transistor having a semiconductor layer including a semiconductor (e.g., silicon) belonging to Group 14 of the periodic table or an oxide semiconductor layer can be used, for example. The semiconductor layer 10 including a semiconductor belonging to Group 14 or the oxide semiconductor layer has a function of a channel formation layer of a transistor. The oxide semiconductor layer is highly purified to be an intrinsic (also referred to as I-type) or substantially intrinsic semiconductor layer. Note that the high purification means at least one of the following concepts: removal of hydrogen from an oxide semiconductor layer as much 15 as possible; and reduction of defects, which are caused by oxygen deficiency in an oxide semiconductor layer, by supply of oxygen to the oxide semiconductor layer. Further, all transistors included in the divider circuit can have the same conductivity type. When all the transistors have the same conductivity type, a manufacturing process can be simplified as compared to the case where transistors with different 20 conductivity types are used.

[0029]

The sequential circuit sets the voltage of the output signal in accordance with the voltage of the clock signal in such a manner that a transistor for controlling the voltage of the output signal of the sequential circuit is turned on. For example, in the 25 sequential circuit in the odd-numbered stage, the transistor for controlling the voltage of the output signal sets the voltage of the output signal in accordance with the signal CLK1. In the sequential circuit in the even-numbered stage, the transistor for controlling the voltage of the output signal sets the voltage of the output signal in accordance with the signal CLK2. In the transistor for controlling the voltage of the output signal, capacitance is between the gate and either the source or the drain. Therefore, in the sequential circuit, the voltage of the gate of the transistor can be set 30 higher than or equal to power supply voltage. Accordingly, it takes shorter time to set

the voltage of the output signal to a desired value, and at least part of the voltage of the output signal can be higher than or equal to the power supply voltage. As the capacitance between the gate and either the source or the drain, parasitic capacitance, a capacitor which is additionally provided, or the like can be used.

5 [0030]

The  $2X$  pulse signals are input to the divided signal output circuit 102. The divided signal output circuit 102 has a function of generating a signal to be a signal CLK3 with a cycle  $X$  times longer than the cycle of the signal CLK1 in accordance with the input  $2X$  pulse signals, and outputting the generated signal to be the signal CLK3 as an output signal. Note that generation of a signal with a cycle  $X$  times longer than the cycle of the signal CLK1 is also referred to as frequency division.

10 [0031]

The divided signal output circuit 102 includes at least  $X$  transistors Tr1 and  $X$  transistors Tr2.

15 [0032]

Different pulse signal among the first to  $X$ -th pulse signals is input to the respective gates of the  $X$  transistors Tr1. In other words, the first to  $X$ -th pulse signals among the  $2X$  pulse signals are separately input to the respective gates of the  $X$  transistors Tr1. The transistors Tr1 have a function of controlling whether the voltage 20 of the signal to be the signal CLK3 in a predetermined period is set to the first voltage.

[0033]

Different pulse signal among the  $(X + 1)$ -th to  $2X$ -th pulse signals is input to the respective gates of the  $X$  transistors Tr2. In other words, the  $(X + 1)$ -th to  $2X$ -th pulse signals of the  $2X$  pulse signals are separately input to the respective gates of the  $X$  transistors Tr2. The transistors Tr2 have a function of controlling whether the voltage 25 of the signal to be the signal CLK3 in a predetermined period is set to the second voltage.

[0034]

An example of the divider circuit of this embodiment includes a shift register 30 and a divided signal output circuit. The shift register has a function of outputting  $2X$  pulse signals in accordance with a first clock signal and a second clock signal. The

divided signal output circuit sets voltage of a signal to be a third clock signal in such a manner that  $X$  first transistors and  $X$  second transistors are sequentially turned on in accordance with the  $2X$  pulse signals, and thus outputs the third clock signal with a cycle  $X$  times longer than a cycle of the first clock signal. In the shift register in the 5 divider circuit of this embodiment, it takes shorter time to set the voltage of the pulse signal to a desired value. This is because the voltage of the pulse signal to be an output signal is set in accordance with the voltage of the clock signal, for example. Accordingly, with the use of the shift register, operation speed of the divider circuit can be improved, and a malfunction in dividing operation can be prevented.

10 [0035]

(Embodiment 2)

In this embodiment, an example of a structure of the divider circuit in the above Embodiment 1 will be described.

[0036]

15 First, an example of a structure of each sequential circuit in the shift register of the divider circuit of the above embodiment will be described with reference to FIGS. 2A to 2C. FIGS. 2A to 2C each illustrate an example of a structure of the sequential circuit in the shift register of the divider circuit of this embodiment.

[0037]

20 A set signal ST11 (also referred to as a signal ST11), a reset signal RS11 (also referred to as a signal RS11), a reset signal RS12 (also referred to as a signal RS12), a clock signal CK11 (also referred to as a signal CK11), a clock signal CK12 (also referred to as a signal CK12), and power supply voltage Vp are input to each sequential circuit. Further, each sequential circuit outputs an output signal OUT11 (also referred 25 to as a signal OUT11).

[0038]

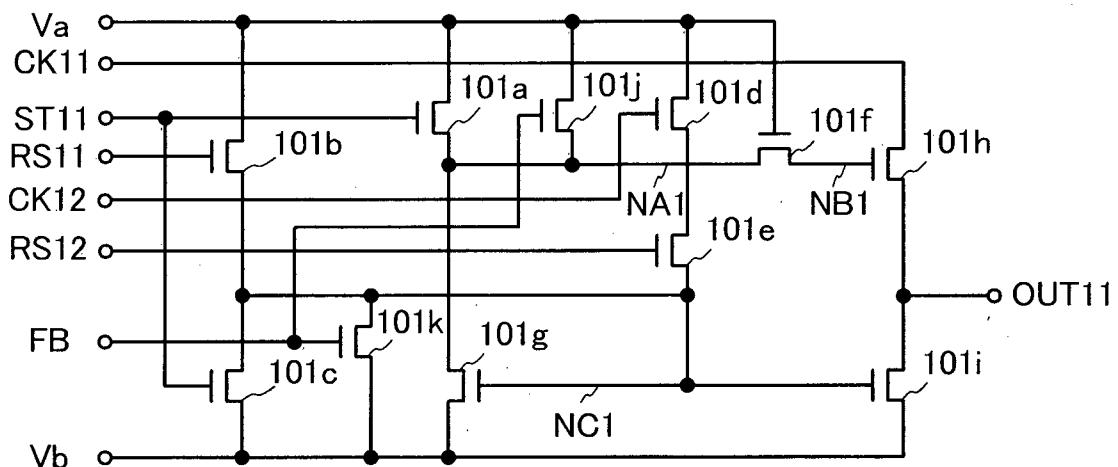

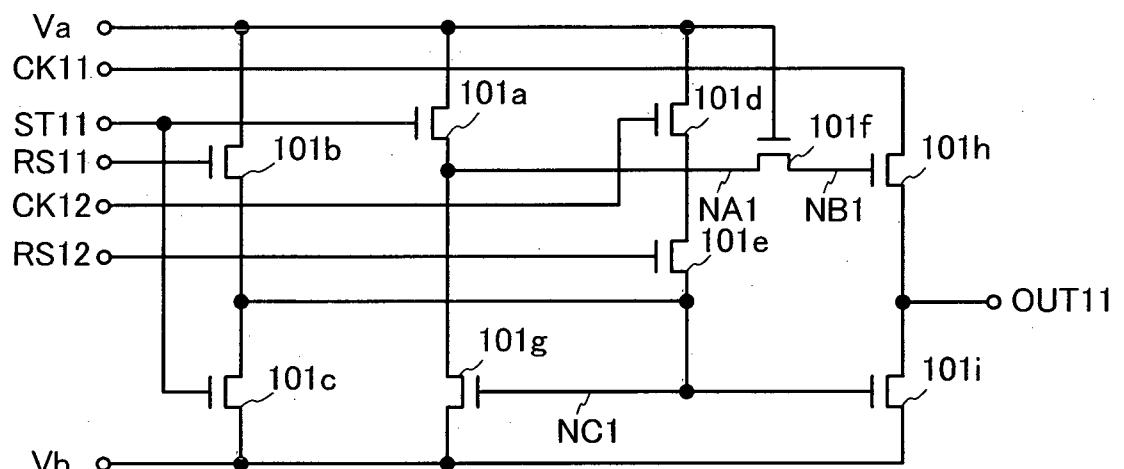

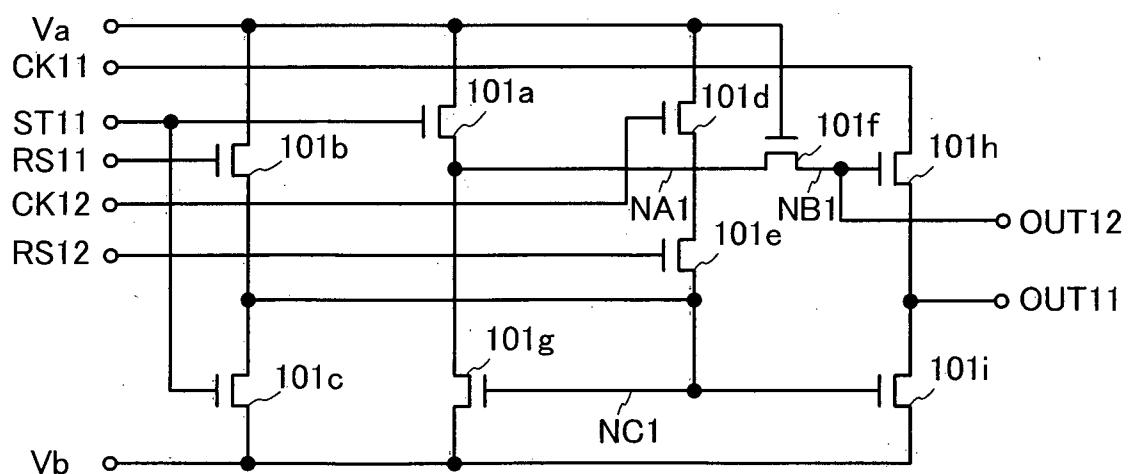

FIG. 2A illustrates an example of a structure of a sequential circuit in the first stage. The sequential circuit illustrated in FIG. 2A includes transistors 101a to 101k.

[0039]

30 Voltage Va is input to one of a source and a drain of the transistor 101a, and the signal ST11 is input to a gate of the transistor 101a.

[0040]

The voltage Va is input to one of a source and a drain of the transistor 101b, and the signal RS11 is input to a gate of the transistor 101b.

[0041]

One of a source and a drain of the transistor 101c is electrically connected to 5 the other of the source and the drain of the transistor 101b, voltage Vb is input to the other of the source and the drain of the transistor 101c, and the signal ST11 is input to a gate of the transistor 101c.

[0042]

Note that one of the voltage Va and the voltage Vb is to be high power supply 10 voltage Vdd and the other of the voltage Va and the voltage Vb is to be low power supply voltage Vss. The high power supply voltage Vdd is relatively higher than the low power supply voltage Vss, and the low power supply voltage Vss is relatively lower than the high power supply voltage Vdd. Values of the voltage Va and the voltage Vb interchange depending on polarity of a transistor or the like in some cases. A potential 15 difference between the voltage Va and the voltage Vb is power supply voltage Vp.

[0043]

The voltage Va is input to one of a source and a drain of the transistor 101d, and the signal CK12 is input to a gate of the transistor 101d.

[0044]

One of a source and a drain of the transistor 101e is electrically connected to 20 the other of the source and the drain of the transistor 101d, the other of the source and the drain of the transistor 101e is electrically connected to the other of the source and the drain of the transistor 101b, and the signal RS12 is input to a gate of the transistor 101e.

[0045]

One of a source and a drain of the transistor 101f is electrically connected to 30 the other of the source and the drain of the transistor 101a, and the voltage Va is input to a gate of the transistor 101f. Note that a portion where the one of the source and the drain of the transistor 101f is connected to the other of the source and the drain of the transistor 101a is also referred to as a node NA1.

[0046]

One of a source and a drain of the transistor 101g is electrically connected to

the other of the source and the drain of the transistor 101a, the voltage Vb is input to the other of the source and the drain of the transistor 101g, and a gate of the transistor 101g is electrically connected to the other of the source and the drain of the transistor 101e.

[0047]

5 The signal CK11 is input to one of a source and a drain of the transistor 101h, and a gate of the transistor 101h is electrically connected to the other of the source and the drain of the transistor 101f. Note that a portion where the gate of the transistor 101h is connected to the other of the source and the drain of the transistor 101f is also referred to as a node NB1.

10 [0048]

One of a source and a drain of the transistor 101i is electrically connected to the other of the source and the drain of the transistor 101h, the voltage Vb is input to the other of the source and the drain of the transistor 101i, and a gate of the transistor 101i is electrically connected to the other of the source and the drain of the transistor 101e.

15 Note that a portion where the gate of the transistor 101i, the other of the source and the drain of the transistor 101b, the one of the source and the drain of the transistor 101c, the other of the source and the drain of the transistor 101e, the gate of the transistor 101g, and one of a source and a drain of the transistor 101k are connected to one another is also referred to as a node NC1.

20 [0049]

The voltage Va is input to one of a source and a drain of the transistor 101j, the other of the source and the drain of the transistor 101j is electrically connected to the other of the source and the drain of the transistor 101a, and a signal FB is input to a gate of the transistor 101j. The signal FB is a feedback signal, which is a signal OUT11 (also referred to as a signal OUT11(101\_P)) of the sequential circuit 101\_P in the P-th stage.

[0050]

30 The one of the source and the drain of the transistor 101k is electrically connected to the other of the source and the drain of the transistor 101b, the voltage Vb is input to the other of the source and the drain of the transistor 101k, and the signal FB is input to a gate of the transistor 101k.

[0051]

FIG. 2B illustrates an example of a structure of the sequential circuits in the second to  $((P/2) + 1)$ -th stages.

[0052]

The sequential circuit illustrated in FIG. 2B has a structure, in which the 5 transistor 101j and the transistor 101k are omitted from the structure of the sequential circuit illustrated in FIG. 2A. Therefore, the description of the example of the structure of the sequential circuit illustrated in FIG. 2A is employed as appropriate.

[0053]

FIG. 2C illustrates an example of a structure of the sequential circuits in the 10  $((P/2) + 2)$ -th to  $P$ -th stages.

[0054]

The sequential circuit illustrated in FIG. 2C has a structure in which voltage of the node NB1 is output as a signal OUT12, in addition to the structure of the sequential circuit illustrated in FIG. 2B. Therefore, the description of the sequential circuit 15 illustrated in FIG. 2A is employed as appropriate for a portion having the structure same as the structure of the sequential circuit illustrated in FIG. 2B.

[0055]

A start signal SP (also referred to as a signal SP) is input to the sequential circuit in the first stage as the signal ST11. The signal SP is a pulse signal.

20 [0056]

The signal OUT11 of the sequential circuit in the  $Q$ -th ( $Q$  is a natural number greater than or equal to 1 and less than or equal to  $(P - 1)$ ) stage is input to the sequential circuit in the  $(Q + 1)$ -th stage as the signal ST11.

[0057]

25 The signal OUT11 of the sequential circuit in the  $(U + 1)$ -th ( $U$  is a natural number greater than or equal to 1 and less than or equal to  $(P - 1)$ ) stage is input to the sequential circuit in the  $U$ -th stage as the signal RS11.

[0058]

30 The signal OUT11 of the sequential circuit in the first stage is input to the sequential circuit in the  $P$ -th stage as the signal RS11.

[0059]

To the sequential circuit in the even-numbered stage, the signal CLK2 is input as the signal CK11 and the signal CLK1 is input as the signal CK12.

[0060]

To the sequential circuit in the odd-numbered stage, the signal CLK1 is input as 5 the signal CK11 and the signal CK12.

[0061]

A signal RST is input to each of the sequential circuits as the signal RS12. The signal RST is a pulse signal. Note that the signal SP can be generated with the use of the signal RST.

10 [0062]

Next, an example of a structure of a divided signal output circuit in the divider circuit of this embodiment will be described with reference to FIGS. 3A and 3B. FIGS. 3A and 3B each illustrate an example of the structure of the divided signal output circuit in the divider circuit of this embodiment.

15 [0063]

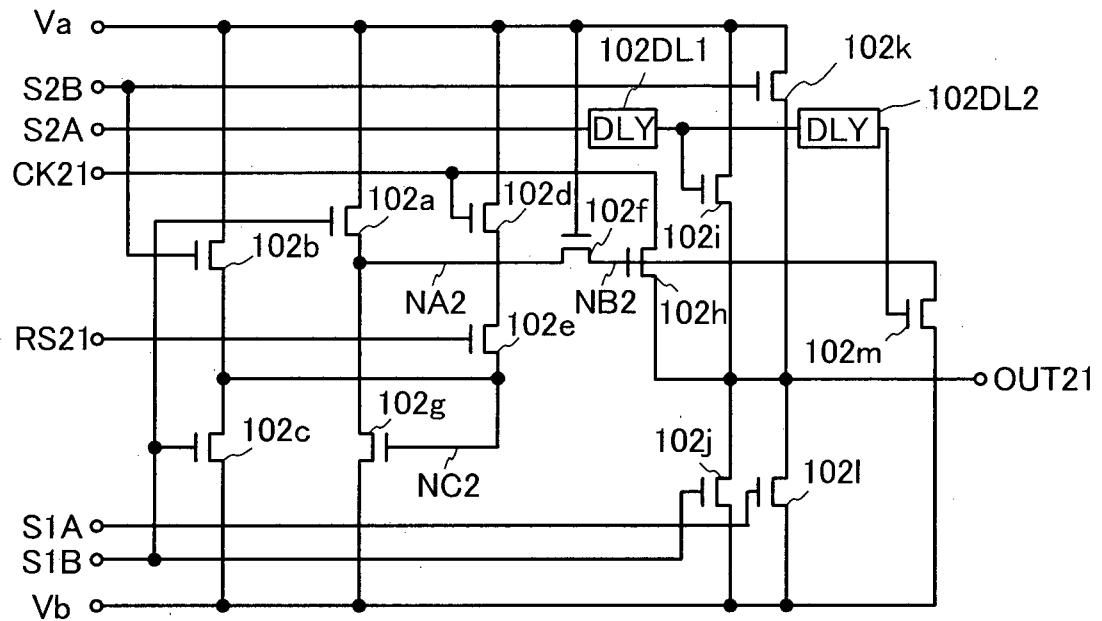

The divided signal output circuit illustrated in FIG. 3A is a divided signal output circuit in which a shift register includes sequential circuits of four stages. The divided signal output circuit illustrated in FIG. 3A includes transistors 102a to 102m, a delay circuit 102DL1, and a delay circuit 102DL2.

20 [0064]

A signal S1A, a signal S1B, a signal S2A, a signal S2B, a clock signal CK21 (also referred to as a signal CK21), a reset signal RS21 (also referred to as a signal RS21), and power supply voltage Vp are input to the divided signal output circuit illustrated in FIG. 3A. Further, the divided signal output circuit illustrated in FIG. 3A 25 outputs an output signal OUT21 (also referred to as a signal OUT21). The signal OUT21 is a clock signal in which frequency of the clock signal CLK1 is divided by  $N$ . That is, a cycle of the signal OUT21 is  $N$  times longer than a cycle of the clock signal CLK1.

[0065]

30 Voltage Va is input to one of a source and a drain of the transistor 102a, and the signal S1B is input to a gate of the transistor 102a.

[0066]

The voltage  $V_a$  is input to one of a source and a drain of the transistor 102b, and the signal  $S2B$  is input to a gate of the transistor 102b.

[0067]

One of a source and a drain of the transistor 102c is electrically connected to the other of the source and the drain of the transistor 102b, voltage  $V_b$  is input to the other of the source and the drain of the transistor 102c, and the signal  $S1B$  is input to a gate of the transistor 102c.

[0068]

The voltage  $V_a$  is input to one of a source and a drain of the transistor 102d, and the signal  $CK21$  is input to a gate of the transistor 102d.

[0069]

One of a source and a drain of the transistor 102e is electrically connected to the other of the source and the drain of the transistor 102d, and the other of the source and the drain of the transistor 102e is electrically connected to the other of the source and the drain of the transistor 102b, and the signal  $RS21$  is input to a gate of the transistor 102e.

[0070]

One of a source and a drain of the transistor 102f is electrically connected to the other of the source and the drain of the transistor 102a, and the voltage  $V_a$  is input to a gate of the transistor 102f. Note that a portion where the one of the source and the drain of the transistor 102f is connected to the other of the source and the drain of the transistor 102a is also referred to as a node NA2.

[0071]

One of a source and a drain of the transistor 102g is electrically connected to the other of the source and the drain of the transistor 102a, the voltage  $V_b$  is input to the other of the source and the drain of the transistor 102g, and a gate of the transistor 102g is electrically connected to the other of the source and the drain of the transistor 102b. Note that a portion where the gate of the transistor 102g, the other of the source and the drain of the transistor 102b, the one of the source and the drain of the transistor 102c, and the other of the source and the drain of the transistor 102e are connected to one another is also referred to as a node NC2.

[0072]

The signal CK21 is input to one of a source and a drain of the transistor 102h, and a gate of the transistor 102h is electrically connected to the other of the source and the drain of the transistor 102f. Note that a portion where the gate of the transistor 102h is connected to the other of the source and the drain of the transistor 102f is also 5 referred to as a node NB2.

[0073]

The voltage Va is input to one of a source and a drain of the transistor 102i, the other of the source and the drain of the transistor 102i is electrically connected to the other of the source and the drain of the transistor 102h, and the signal S2A is input to a 10 gate of the transistor 102i through the delay circuit 102DL1.

[0074]

One of a source and a drain of the transistor 102j is electrically connected to the other of the source and the drain of the transistor 102h, the voltage Vb is input to the other of the source and the drain of the transistor 102j, and the signal S1B is input to a 15 gate of the transistor 102j.

[0075]

The voltage Va is input to one of a source and a drain of the transistor 102k, the other of the source and the drain of the transistor 102k is electrically connected to the other of the source and the drain of the transistor 102h, and the signal S2B is input to a 20 gate of the transistor 102k.

[0076]

One of a source and a drain of the transistor 102l is electrically connected to the other of the source and the drain of the transistor 102h, the voltage Vb is input to the other of the source and the drain of the transistor 102l, and the signal S1A is input to a 25 gate of the transistor 102l.

[0077]

One of a source and a drain of the transistor 102m is electrically connected to the other of the source and the drain of the transistor 102f, the voltage Vb is input to the other of the source and the drain of the transistor 102m, and the signal S2A is input to a 30 gate of the transistor 102m through the delay circuit 102DL1 and the delay circuit 102DL2.

[0078]

To the sequential circuit illustrated in FIG. 3A, the signal CLK1 is input as the signal CK21, the signal RST is input as the signal RS21, the signal OUT11 of the sequential circuit in the first stage in the shift register 101 (also referred to as a signal OUT11(101\_1)) is input as the signal S1A, the signal OUT11 of the sequential circuit in the second stage in the shift register 101 (also referred to as a signal OUT11(101\_2)) is input as the signal S1B, the signal OUT11 of the sequential circuit in the third stage in the shift register 101 (also referred to as a signal OUT11(101\_3)) is input as the signal S2A, and the signal OUT12 of the sequential circuit 101\_4 in the fourth stage in the shift register 101 (also referred to as a signal OUT12(101\_4)) is input as the signal S2B.

10 [0079]

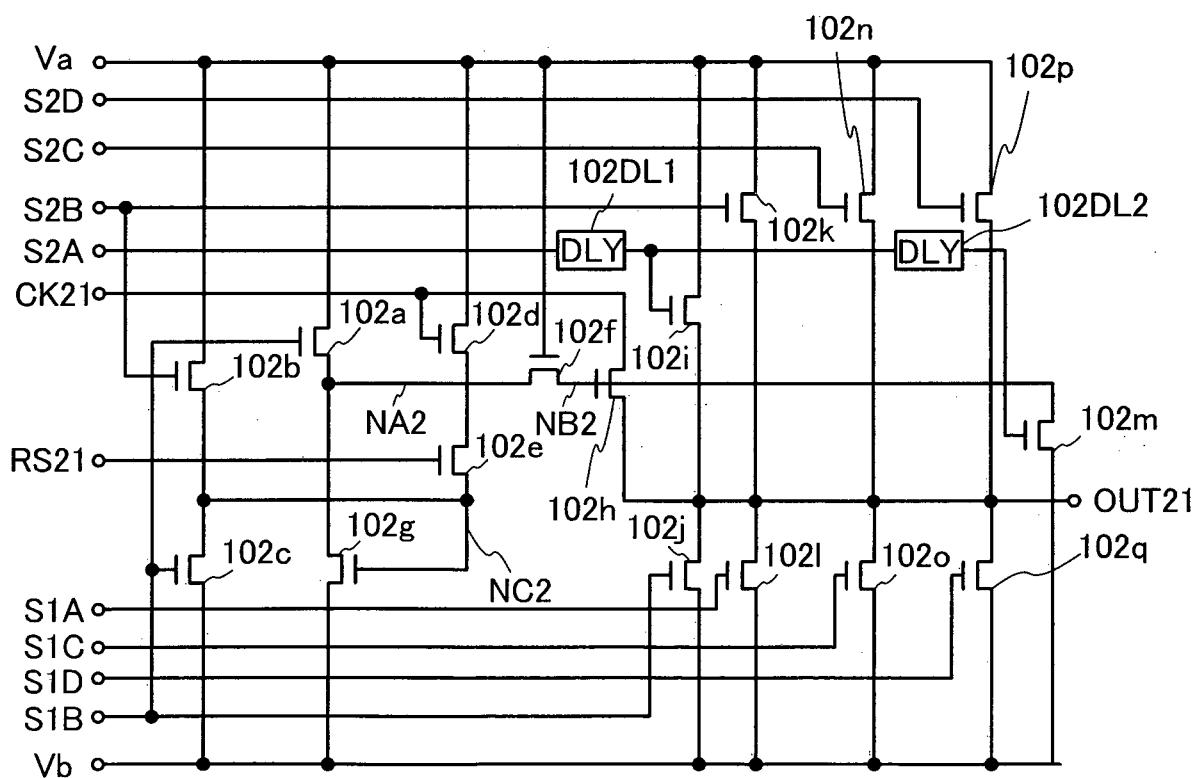

The divided signal output circuit illustrated in FIG. 3B is a divided signal output circuit in which the shift register 101 includes sequential circuits of eight stages. The divided signal output circuit illustrated in FIG. 3B includes transistors 102n to 102q in addition to the structure of the divided signal output circuit illustrated in FIG. 3A, and 15 a signal S1C, a signal S1D, a signal S2C, and a signal S2D are further input.

[0080]

The voltage Va is input to one of a source and a drain of the transistor 102n, the other of the source and the drain of the transistor 102n is electrically connected to the other of the source and the drain of the transistor 102h, and the signal S2C is input to a 20 gate of the transistor 102n.

[0081]

One of a source and a drain of the transistor 102o is electrically connected to the other of the source and the drain of the transistor 102h, the voltage Vb is input to the other of the source and the drain of the transistor 102o, and the signal S1C is input to a 25 gate of the transistor 102o.

[0082]

The voltage Va is input to one of a source and a drain of the transistor 102p, the other of the source and the drain of the transistor 102p is electrically connected to the other of the source and the drain of the transistor 102h, and the signal S2D is input to a 30 gate of the transistor 102p.

[0083]

One of a source and a drain of the transistor 102q is electrically connected to the other of the source and the drain of the transistor 102h, the voltage Vb is input to the other of the source and the drain of the transistor 102q, and the signal S1D is input to a gate of the transistor 102q.

5 [0084]

Further, to the divided signal output circuit illustrated in FIG. 3B, the signal CLK1 is input as the signal CK21, the signal RST is input as the signal RS21, the signal OUT11 of the sequential circuit in the first stage in the shift register 101 is input as the signal S1A, the signal OUT11 of the sequential circuit in the second stage in the shift 10 register 101 is input as the signal S1B, the signal OUT11 of the sequential circuit in the third stage in the shift register 101 is input as the signal S1C, the signal OUT12 of the sequential circuit in the fourth stage in the shift register 101 is input as the signal S1D, the signal OUT11 of the sequential circuit in the fifth stage in the shift register 101 (also referred to as a signal OUT11(101\_5)) is input as the signal S2A, the signal OUT12 of 15 the sequential circuit in the sixth stage in the shift register 101 (also referred to as a signal OUT12(101\_6)) is input as the signal S2B, the signal OUT12 of the sequential circuit in the seventh stage in the shift register 101 (also referred to as a signal OUT12(101\_7)) is input as the signal S2C, and the signal OUT12 of the sequential circuit in the eighth stage in the shift register 101 (also referred to as a signal 20 OUT12(101\_8)) is input as the signal S2D.

[0085]

Note that the delay circuit 102DL1 and the delay circuit 102DL2 are each formed using  $2N$  ( $N$  is a natural number) invertors which are electrically connected in parallel, for example.

25 [0086]

Next, an example of operation of the divider circuit of this embodiment will be described.

[0087]

First, an example of operation of the shift register 101 in the divider circuit will 30 be described with reference to FIGS. 4A to 4C. FIGS. 4A to 4C are timing charts each showing an example of operation of the shift register in the divider circuit of this

embodiment. Note that here, as an example, all the transistors 101a to 101i have N-type conductivity, the high power supply voltage Vdd is input as the voltage Va, and the low power supply voltage Vss is input as the voltage Vb.

[0088]

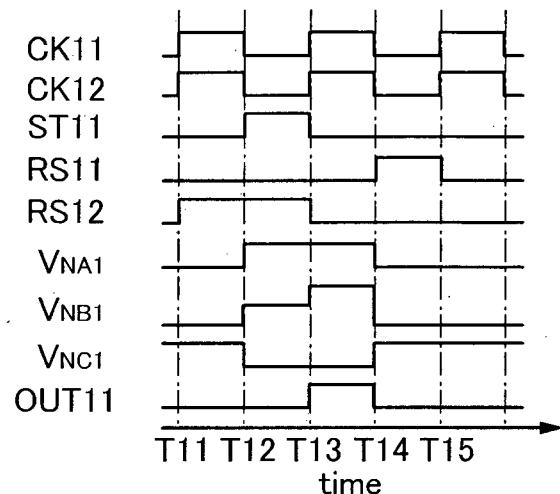

5 FIG. 4A is a timing chart showing an example of operation of the sequential circuit in the odd-numbered stage. In FIG. 4A, at a time T11, the signal CK11 and the signal CK12 are each set to a high level, the signal ST11 is at a low level, the signal RS11 is at a low level, and the signal RS12 is set to a high level.

[0089]

10 At this time, the sequential circuit is set to a reset state. Further, the transistor 101b and the transistor 101c are turned off and the transistor 101d and the transistor 101e are turned on; therefore, voltage of the node NC1 (also referred to as  $V_{NC1}$ ) becomes equivalent to the value of the voltage Va and the transistor 101g and the transistor 101i are turned on. In addition, the transistor 101a is turned off and the transistor 101g is in an on state; therefore, voltage of the node NA1 (also referred to as  $V_{NA1}$ ) becomes equivalent to the value of the voltage Vb. Moreover, since the transistor 101f is in an on state, voltage of the node NB1 (also referred to as  $V_{NB1}$ ) becomes equivalent to the value of the voltage Vb, and the transistor 101h is turned off. The transistor 101h is turned off and the transistor 101i is turned on, so that the signal

15

20 OUT11 is set to a low level.

[0090]

Next, at a time T12, the signal CK11 and the signal CK12 are each set to a low level, the signal ST11 is set to a high level, the signal RS11 remains at a low level, and the signal RS12 remains at a high level.

25 [0091]

At this time, the sequential circuit is set to a set state. The transistor 101b remains off, the transistor 101c is turned on, the transistor 101d is turned off, and the transistor 101e remains on; therefore, the voltage of the node NC1 remains equivalent to the value of the voltage Vb and the transistor 101g and the transistor 101i are turned off.

30 Further, the transistor 101a is turned on and the transistor 101g is turned off; therefore, the voltage of the node NA1 becomes equivalent to the value of the voltage Va. Moreover, since the transistor 101f is in an on state, the voltage of the node NB1

becomes equivalent to the value of the voltage  $V_a$ , the transistor 101h is turned on, the voltage of the node NA1 and the voltage of the node NB1 become equivalent to the value of the voltage  $V_a$ ; accordingly, the transistor 101f is turned off. The transistor 101h is turned on and the transistor 101i is turned off, so that the signal OUT11 remains 5 at a low level.

[0092]

Next, at a time T13, the signal CK11 and the signal CK12 are each set to a high level, the signal ST11 is set to a low level, the signal RS11 remains at a low level, and the signal RS12 is set to a low level.

10 [0093]

At this time, the transistor 101b remains off, the transistor 101c is turned off, the transistor 101d is turned on, and the transistor 101e is turned off; therefore, the voltage of the node NC1 remains equivalent to the value of the voltage  $V_b$ , and the transistor 101g and the transistor 101i remain off. Further, the transistor 101a is turned 15 off and the transistor 101g remains off; therefore, the voltage of the node NA1 remains equivalent to the value of the voltage  $V_a$ . The transistor 101f remains off and the node NB1 enters a floating state. The transistor 101h remains on and the transistor 101i remains off, so that the voltage of the other of the source and the drain of the transistor 101h is increased. Then, the voltage of the node NB1 is increased because of 20 capacitive coupling due to parasitic capacitance generated between the gate of the transistor 101h and the other of the source and the drain of the transistor 101h. This is so-called bootstrap operation. The voltage of the node NB1 is increased to a value which is larger than the sum of the voltage  $V_a$  and the threshold voltage of the transistor 101h (also referred to as  $V_{th101h}$ ), that is,  $V_a + V_{th101h} + V_x$ . At this time, the transistor 25 101h remains on. Further, the signal OUT11 is set to a high level.

[0094]

Next, at a time T14, the signal CK11 and the signal CK12 are each set to a low level, the signal ST11 remains at a low level, the signal RS11 is set to a high level, and the signal RS12 remains at a low level.

30 [0095]

At this time, the transistor 101b is turned on, the transistor 101c and the transistor 101e remain off, and the transistor 101d is turned off; therefore, the voltage of

the node NC1 becomes equivalent to the value of the voltage Va, and the transistor 101g and the transistor 101i are turned on. Further, the transistor 101a remains off and the transistor 101g is turned on; therefore, the voltage of the node NA1 becomes equivalent to the value of the voltage Vb and the transistor 101f is turned on. Since transistor 101f is turned on, the voltage of the node NB1 becomes equivalent to the value of the voltage Vb and the transistor 101h is turned off. Since the transistor 101h is turned off and the transistor 101i is turned on, the signal OUT11 is set to a low level.

[0096]

Thus, the sequential circuit in the odd-numbered stage outputs a pulse of the signal OUT11.

[0097]

FIG. 4B is a timing chart showing an example of operation of the sequential circuit in the even-numbered stage. In FIG. 4B, at the time T11, the signal CK11 is set to a low level, the signal CK12 is set to a high level, the signal ST11 is set to a low level, the signal RS11 is set to a low level, and the signal RS12 is set to a high level.

[0098]

At this time, the sequential circuit is set to a reset state. The transistor 101b and the transistor 101c are turned off, and the transistor 101d and the transistor 101e are turned on; therefore, the voltage of the node NC1 becomes equivalent to the value of the voltage Va, and the transistor 101g and the transistor 101i are turned on. Further, the transistor 101a is turned off and the transistor 101g is turned on; therefore, the voltage of the node NA1 becomes equivalent to the value of the voltage Vb. Since the transistor 101f is in an on state, the voltage of the node NB1 becomes equivalent to the value of the voltage Vb and the transistor 101h is turned off. The transistor 101h is turned off and the transistor 101i is turned on, so that the signal OUT11 is set to a low level.

[0099]

Next, at the time T12, the signal CK11 is set to a high level, the signal CK12 is set to a low level, the signal ST11 remains at a low level, the signal RS11 remains at a low level, and the signal RS12 remains at a high level.

[0100]

At this time, the transistor 101b and the transistor 101c remain off, the

transistor 101e remains on, and the transistor 101d is turned off; therefore, the voltage of the node NC1 remains equivalent to the value of the voltage Va, and the transistor 101g and the transistor 101i remain on. Further, the transistor 101a remains off and the transistor 101g remains on; therefore, the voltage of the node NA1 remains equivalent to the value of the voltage Vb. Since the transistor 101f remains on, the voltage of the node NB1 remains equivalent to the value of the voltage Vb and the transistor 101h remains off. The transistor 101h remains off and the transistor 101i remains on, so that the signal OUT11 remains at a low level.

[0101]

10 Next, at the time T13, the signal CK11 is set to a low level, the signal CK12 is set to a high level, the signal ST11 is set to a high level, the signal RS11 remains at a low level, and the signal RS12 is set to a low level.

[0102]

15 At this time, the sequential circuit is set to a set state. The transistor 101b remains off, the transistor 101c is turned on, the transistor 101d is turned on, and the transistor 101e is turned off; therefore, the voltage of the node NC1 becomes equivalent to the value of the voltage Vb and the transistor 101g and the transistor 101i are turned off. Further, the transistor 101a is turned on and the transistor 101g is turned off; therefore, the voltage of the node NA1 becomes equivalent to the value of the voltage 20 Va. Since the transistor 101f remains on, the voltage of the node NB1 becomes equivalent to the value of the voltage Va and the transistor 101h is turned on. When the voltage of the node NA1 and the voltage of the node NB1 become equivalent to the value of the voltage Va, the transistor 101f is turned off. The transistor 101h is turned on and the transistor 101i is turned off, so that the signal OUT11 remains at a low level.

25 [0103]

Next, at the time T14, the signal CK11 is set to a high level, the signal CK12 is set to a low level, the signal ST11 is set to a low level, the signal RS11 remains at a low level, and the signal RS12 remains at a low level.

[0104]

30 At this time, the transistor 101b and the transistor 101e remain off, and the transistor 101c and the transistor 101d are turned off; therefore, the voltage of the node NC1 remains equivalent to the value of the voltage Vb and the transistor 101g and the

transistor 101i remain off. Further, the transistor 101a is turned off and the transistor 101g remains off; therefore, the voltage of the node NA1 remains equivalent to the value of the voltage Va. The transistor 101f remains off, the node NB1 enters a floating state, the transistor 101h remains on, and the transistor 101i remains off; 5 therefore, the voltage of the other of the source and the drain of the transistor 101h is increased. Then, the voltage of the node NB1 is increased because of capacitive coupling due to parasitic capacitance generated between the gate of the transistor 101h and the other of the source and the drain of the transistor 101h. The voltage of the node NB1 is increased to a value which is larger than the sum of the voltage Va and the 10 threshold voltage of the transistor 101h (also referred to as  $V_{th101h}$ ), that is,  $Va + V_{th101h} + Vx$ . At this time, the transistor 101h remains on, and the transistor 101i remains off, so that the signal OUT11 is set to a high level.

[0105]

Next, at a time T15, the signal CK11 is set to a low level, the signal CK12 is set 15 to a high level, the signal ST11 remains at a low level, the signal RS11 is set to a high level, and the signal RS12 remains at a low level.

[0106]

At this time, the transistor 101c and the transistor 101e remain off and the transistor 101b is turned on; therefore, the voltage of the node NC1 becomes equivalent 20 to the value of the voltage Va, and the transistor 101g and the transistor 101i are turned on. Further, the transistor 101a remains off and the transistor 101g is turned on; therefore, the voltage of the node NA1 becomes equivalent to the value of the voltage Vb. Since the transistor 101f is turned on, the voltage of the node NB1 becomes equivalent to the value of the voltage Vb and the transistor 101h is turned off. The 25 transistor 101h is turned off and the transistor 101i is turned on, so that the signal OUT11 is set to a low level.

[0107]

Thus, the sequential circuit outputs a pulse of the signal OUT11.

[0108]

30 Further, an example of operation of the sequential circuit illustrated in FIG. 2A will be described with the use of the description of the example of operation of the

sequential circuit described with reference to FIG. 4A.

[0109]

In the sequential circuit illustrated in FIG. 2A, in addition to the operation of the sequential circuit illustrated in FIG. 2B, the transistor 101j and the transistor 101k are turned on when a pulse of the signal FB is input. When the transistor 101j is turned on, the voltage of the node NA1 becomes equivalent to the value of the voltage Va and the transistor 101f is turned off. When the transistor 101k is turned on, the voltage of the node NB1 becomes equivalent to the value of the voltage Vb and the transistor 101g and the transistor 101i are turned off.

10 [0110]

Further, operation of the sequential circuit illustrated in FIG. 2C is the same as the operation of the sequential circuit illustrated in FIG. 2B described above; therefore, the description of the example of the operation of the sequential circuit illustrated in FIG. 2B is employed as appropriate.

15 [0111]

FIG. 4C is a timing chart showing an example of operation of the shift register illustrated in FIG. 1.

[0112]

In FIG. 4C, first, a pulse of the signal RST is input, so that each sequential circuit is set to a reset state. Then, a pulse of the signal SP is input, so that the sequential circuit 101\_1 in the first stage is set to a set state. In the next period, the sequential circuit 101\_1 in the first stage outputs the pulse of the signal OUT11. Further, the pulse of the signal OUT11 of the sequential circuit 101\_1 in the first stage is input to the sequential circuit 101\_2 in the second stage as the set signal ST11, so that the sequential circuit 101\_2 in the second stage is set to a set state. The sequential circuit 101\_2 in the second stage outputs the pulse of the signal OUT11 in the next period. The above operation is sequentially performed in up to and including the sequential circuit 101\_P in the P-th stage. Thus, the pulses of the signals OUT11 of the sequential circuit 101\_1 in the first stage to the sequential circuit 101\_P in the P-th stage are sequentially output. The above is an example of operation of the shift register in the divider circuit of this embodiment.

[0113]

Further, as an example of operation of a divided signal output circuit in a divider circuit of this embodiment, an example of operation of the divided signal output circuit having the structure illustrated in FIG. 3A will be described with reference to FIG.

5 FIG. 5 is a timing chart showing an example of operation of the divided signal output circuit having the structure illustrated in FIG. 3A.

[0114]

In FIG. 5, at a time T21, the signal CK21 is set to a high level, the signal RS21 is set to a high level, the signal S1A is at a low level, the signal S1B is at a low level, the 10 signal S2A is at a low level, and voltage of the signal S2B is equivalent to the value of the voltage Vb.

[0115]

At this time, the divided signal output circuit is set to a reset state. The transistor 102b and the transistor 102c are turned off and the transistor 102d and the 15 transistor 102e are turned on; therefore, voltage of the node NC2 (also referred to as  $V_{NC2}$ ) becomes equivalent to the value of the voltage Va and the transistor 102g is turned on. Further, the transistor 102g is turned on and the transistor 102a is turned off; therefore, voltage of the node NA2 (also referred to as  $V_{NA2}$ ) becomes equivalent to the value of the voltage Vb. Since the transistor 102f is in an on state, voltage of the 20 node NB2 (also referred to as  $V_{NB2}$ ) becomes equivalent to the value of the voltage Vb and the transistor 102h is turned off. Further, the transistor 102h, the transistor 102i, the transistor 102j, the transistor 102k, the transistor 102l, and the transistor 102m are turned off, so that the signal OUT21 maintains the state in the previous period.

[0116]

25 Next, at a time T22, the signal CK21 is set to a low level, the signal RS21 remains at a high level, the signal S1A remains at a low level, the signal S1B remains at a low level, the signal S2A remains at a low level, and the voltage of the signal S2B remains equivalent to the value of the voltage Vb.

[0117]

30 At this time, the transistor 102b and the transistor 102c remain off, the transistor 102d is turned off, and the transistor 102e remains on; therefore, the voltage of the node NC2 remains equivalent to the value of the voltage Va and the transistor

102g remains on. Further, the transistor 102a remains off and the transistor 102g remains on; therefore, the voltage of the node NA2 remains equivalent to the value of the voltage Vb. Since the transistor 102f remains on, the voltage of the node NB2 remains equivalent to the value of the voltage Vb and the transistor 102h remains off.

5 Further, the transistor 102h, the transistor 102i, the transistor 102j, the transistor 102k, the transistor 102l, and the transistor 102m remain off, so that the signal OUT21 maintains the state in the previous period.

[0118]

Next, at a time T23, the signal CK21 is set to a high level, the signal RS21 is set to a low level, the signal S1A is set to a high level, the signal S1B remains at a low level, the signal S2A remains at a low level, and the voltage of the signal S2B remains equivalent to the value of the voltage Vb.

[0119]

At this time, the transistor 102b and the transistor 102c remain off, the transistor 102d is turned on, and the transistor 102e is turned off; therefore, the voltage of the node NC2 remains equivalent to the value of the voltage Va and the transistor 102g remains on. Further, the transistor 102a remains off and the transistor 102g remains on; therefore, the voltage of the node NA2 remains equivalent to the value of the voltage Vb. Since the transistor 102f remains on, the voltage of the node NB2 remains equivalent to the value of the voltage Vb and the transistor 102h remains off. Further, the transistor 102l is turned on and the transistor 102h, the transistor 102i, the transistor 102j, the transistor 102k, and the transistor 102m remain off, so that the signal OUT21 is set to a low level.

[0120]

25 Next, at a time T24, the signal CK21 is set to a low level, the signal RS21 remains at a low level, the signal S1A is set to a low level, the signal S1B is set to a high level, the signal S2A remains at a low level, and the voltage of the signal S2B remains equivalent to the value of the voltage Vb.

[0121]

30 At this time, the transistor 102b and the transistor 102e remain off, the transistor 102c is turned on, and the transistor 102d is turned off; therefore, the voltage of the node NC2 becomes equivalent to the value of the voltage Vb and the transistor

102g is turned off. Further, the transistor 102a is turned on and the transistor 102g is turned off; therefore, the voltage of the node NA2 becomes equivalent to the value of the voltage Va. Since the transistor 102f is in an on state, the voltage of the node NB2 becomes equivalent to the value of the voltage Va, the transistor 102h is turned on, and 5 the voltage of the node NA2 and the voltage of the node NB2 become equivalent to the value of the voltage Va; accordingly, the transistor 102f is turned off. Further, the transistor 102l is turned off, the transistor 102h and the transistor 102j are turned on, and the transistor 102i, the transistor 102k, and the transistor 102m remain off, so that the signal OUT21 remains at a low level.

10 [0122]

Next, at a time T25, the signal CK21 is set to a high level, the signal RS21 remains at a low level, the signal S1A remains at a low level, the signal S1B is set to a low level, the signal S2A is set to a high level, and the voltage of the signal S2B becomes equivalent to the value of the voltage Va.

15 [0123]

At this time, the transistor 102a is turned off and the transistor 102f remains off; therefore, the node NB2 enters a floating state. Since the transistor 102h remains on, the voltage of the other of the source and the drain of the transistor 102h is increased. Then, the voltage of the node NB2 is increased because of capacitive coupling due to 20 parasitic capacitance generated between the gate of the transistor 102h and the other of the source and the drain of the transistor 102h. This is so-called bootstrap operation. The voltage of the node NB2 is increased to a value which is larger than the sum of the voltage Va and the threshold voltage of the transistor 102h (also referred to as  $V_{th102h}$ ), that is,  $Va + V_{th102h} + Vx$ . At this time, the transistor 102h remains on. Further, the 25 transistor 102i and the transistor 102k are turned on, the transistor 102j is turned off, the transistor 102h remains on, and the transistor 102l remains off; therefore, the signal OUT21 is set to a high level. Further, the transistor 102b and the transistor 102d are turned on, the transistor 102c is turned off, and the transistor 102e remains off; therefore, the 30 voltage of the node NC2 becomes equivalent to the value of the voltage Va and the transistor 102g is turned on. Since the transistor 102g is in an on state and the transistor 102a is in an off state, the voltage of the node NB2 becomes equivalent to the value of the voltage Vb. Further, the transistor 102f is turned on and the transistor

102m is turned on, so that the voltage of the node NB2 becomes equivalent to the value of the voltage Vb and the transistor 102h is turned off.

[0124]

5 Next, at a time T26, the signal CK21 is set to a low level, the signal RS21 remains at a low level, the signal S1A remains at a low level, the signal S1B remains at a low level, the signal S2A is set to a low level, and the voltage of the signal S2B becomes  $V_a + V_{th_{102h}} + V_x$ .

[0125]

10 At this time, the transistor 102b remains on, the transistor 102c and the transistor 102e remain off, and the transistor 102d is turned off; therefore, the voltage of the node NC2 remains equivalent to the value of the voltage  $V_a$  and the transistor 102g remains on. Further, the transistor 102a remains off and the transistor 102g remains on; therefore, the voltage of the node NA2 remains equivalent to the value of the voltage  $V_b$ . Since the transistor 102f remains on, the voltage of the node NB2 remains 15 equivalent to the value of the voltage  $V_b$  and the transistor 102h remains off. Further, the transistor 102i and the transistor 102m are turned off, the transistor 102h, the transistor 102j, and the transistor 102l remain off, and the transistor 102k remains on, so that the signal OUT21 remains at a high level.

[0126]

20 Thus, the divided signal output circuit outputs the signal CLK3 as the signal OUT21. The signal CLK3 is a clock signal, whose cycle is twice longer than the cycle of the signal CLK1.

[0127]

25 Further, an example of operation of the divided signal output circuit illustrated in FIG. 3B will be described with the use of the above-described description of the example of operation of the divided signal output circuit illustrated in FIG. 3A.

[0128]

30 An example of operation of the divided signal output circuit illustrated in FIG. 3B will be described with reference to FIG. 6. FIG. 6 is a timing chart showing an example of operation of the divided signal output circuit illustrated in FIG. 3B.

[0129]

As shown in FIG. 6, in the divided signal output circuit illustrated in FIG. 3B,

in addition to the operation of the divided signal output circuit illustrated in FIG. 3A, at a time T31 between the time T23 and the time T24, the signal CK21 is set to a low level, the signal RS21 remains at a low level, the signal S1A is set to a low level, the signal S1C is set to a high level, the signal S1D remains at a low level, the signal S1B remains 5 at a low level, the signal S2A remains at a low level, the voltage of the signal S2B remains equivalent to the value of the voltage Vb, the voltage of the signal S2C remains equivalent to the value of the voltage Vb, and the signal S2D remains at a low level.

[0130]

At this time, the transistor 102b, the transistor 102c, and the transistor 102e 10 remain off and the transistor 102d is turned off; therefore, the voltage of the node NC2 remains equivalent to the value of the voltage Va and the transistor 102g remains on. Further, the transistor 102a remains off and the transistor 102g remains on; therefore, the voltage of the node NA2 remains equivalent to the value of the voltage Vb. Since 15 the transistor 102f remains on, the voltage of the node NB2 remains equivalent to the value of the voltage Vb and the transistor 102h remains off. The transistor 102l is turned off, the transistor 102o is turned on, and the transistor 102h, the transistor 102i, the transistor 102j, the transistor 102k, the transistor 102m, the transistor 102n, the transistor 102p, and the transistor 102q remain off, so that the signal OUT21 remains at a low level.

20 [0131]

Next, at a time T32, the signal CK21 is set to a high level, the signal RS21 remains at a low level, the signal S1A remains at a low level, the signal S1C is set to a low level, the signal S1D is set to a high level, the signal S1B remains at a low level, the signal S2A remains at a low level, the voltage of the signal S2B remains equivalent to 25 the value of the voltage Vb, the voltage of the signal S2C remains equivalent to the value of the voltage Vb, and the voltage of the signal S2D remains equivalent to the value of the voltage Vb.

[0132]

At this time, the transistor 102b, the transistor 102c, and the transistor 102e 30 remain off, and the transistor 102d is turned on; therefore, the voltage of the node NC2 remains equivalent to the value of the voltage Va and the transistor 102g remains on. Further, the transistor 102a remains off and the transistor 102g remains on; therefore,

the voltage of the node NA2 remains equivalent to the value of the voltage Vb. Since the transistor 102f remains on, the voltage of the node NB2 remains equivalent to the value of the voltage Vb and the transistor 102h remains off. Further, the transistor 102o is turned off, the transistor 102q is turned on, and the transistor 102h, the transistor 5 102i, the transistor 102j, the transistor 102k, the transistor 102l, the transistor 102m, the transistor 102n, and the transistor 102p remain off, so that the signal OUT21 remains at a low level.

[0133]

Further, at the time T25, the signal CK21 is set to a high level, the signal RS21 10 remains at a low level, the signal S1A remains at a low level, the signal S1C remains at a low level, the signal S1D remains at a low level, the signal S1B is set to a low level, the signal S2A is set to a high level, the voltage of the signal S2B becomes equivalent to the value of the voltage Va, the voltage of the signal S2C remains equivalent to the value of the voltage Vb, and the voltage of the signal S2D remains equivalent to the 15 value of the voltage Vb.

[0134]

At this time, the transistor 102a is turned off and the transistor 102f remains off; therefore, the node NB2 enters a floating state. Since the transistor 102h remains 20 on, the voltage of the other of the source and the drain of the transistor 102h is increased. Then, the voltage of the node NB2 is increased because of capacitive coupling due to parasitic capacitance generated between the gate of the transistor 102h and the other of the source and the drain of the transistor 102h. This is so-called bootstrap operation. The voltage of the node NB2 is increased to a value which is larger than the sum of the voltage Va and the threshold voltage of the transistor 102h (also referred to as  $V_{th102h}$ ), 25 that is,  $Va + V_{th102h} + Vx$ . At this time, the transistor 102h remains on. Further, the transistor 102i and the transistor 102k are turned on, the transistor 102j is turned off, the transistor 102h remains on, and the transistor 102l, the transistor 102n, the transistor 102o, and the transistor 102q remain off; therefore, the signal OUT21 is set to a high level. The transistor 102b and the transistor 102d are turned on, the transistor 102c is 30 turned off, and the transistor 102e remains off; therefore, the voltage of the node NC2 becomes equivalent to the value of the voltage Va and the transistor 102g is turned on. Since the transistor 102g is turned on and the transistor 102a is turned off, the voltage of

the node NB2 becomes equivalent to the value of the voltage Vb. Further, the transistor 102f is turned on and the transistor 102m is turned on, so that the voltage of the node NB2 becomes equivalent to the value of the voltage Vb and the transistor 102h is turned off.

5 [0135]

Next, at the time T26, the signal CK21 is set to a low level, the signal RS21 remains at a low level, the signal S1A remains at a low level, the signal S1C remains at a low level, the signal S1D remains at a low level, the signal S1B remains at a low level, the signal S2A is set to a low level, the voltage of the signal S2B becomes  $V_a + V_{th102h}$  10 +  $V_x$ , the voltage of the signal S2C becomes equivalent to the value of the voltage  $V_a$ , and the voltage of the signal S2D remains equivalent to the value of the voltage Vb.

[0136]

At this time, the transistor 102b remains on, the transistor 102c and the transistor 102e remain off, and the transistor 102d is turned off; therefore, the voltage of 15 the node NC2 remains equivalent to the value of the voltage  $V_a$  and the transistor 102g remains on. Further, the transistor 102a remains off and the transistor 102g remains on; therefore, the voltage of the node NA2 remains equivalent to the value of the voltage Vb. Since the transistor 102f remains on, the voltage of the node NB2 remains equivalent to the value of the voltage Vb and the transistor 102h remains off. Further, 20 the transistor 102i and the transistor 102m are turned off, the transistor 102n is turned on, the transistor 102k remains on, and the transistor 102h, the transistor 102j, the transistor 102l, the transistor 102o, and the transistor 102q remain off, so that the signal OUT21 remains at a high level.

[0137]

25 Further, at a time T33 after the time T26, the signal CK21 is set to a high level, the signal RS21 remains at a low level, the signal S1A remains at a low level, the signal S1C remains at a low level, the signal S1D remains at a low level, the signal S1B remains at a low level, the signal S2A remains at a low level, the voltage of the signal S2B becomes equivalent to the value of the voltage Vb, the voltage of the signal S2C 30 becomes  $V_a + V_{th101h} + V_x$ , and the voltage of the signal S2D becomes equivalent to the value of the voltage  $V_a$ .

[0138]

At this time, the transistor 102c remains off, the transistor 102b is turned off, the transistor 102d is turned on, and the transistor 102e remains off; therefore, the voltage of the node NC2 remains equivalent to the value of the voltage Va, and the 5 transistor 102g remains on. Further, the transistor 102a remains off and the transistor 102g remains on; therefore, the voltage of the node NA2 remains equivalent to the value of the voltage Vb. Since the transistor 102f remains on, the voltage of the node NB2 remains equivalent to the value of the voltage Vb and the transistor 102h remains off. Further, the transistor 102n remains on, the transistor 102k is turned off, the transistor 10 102p is turned on, and the transistor 102h, the transistor 102i, the transistor 102j, the transistor 102l, the transistor 102m, the transistor 102o, and the transistor 102q remain off, so that the signal OUT21 remains at a high level.

[0139]

Further, at a time T34, the signal CK21 is set to a low level, the signal RS21 15 remains at a low level, the signal S1A remains at a low level, the signal S1C remains at a low level, the signal S1D remains at a low level, the signal S1B remains at a low level, the signal S2A remains at a low level, the voltage of the signal S2B remains equivalent to the value of the voltage Vb, the voltage of the signal S2C becomes equivalent to the value of the voltage Vb, and the voltage of the signal S2D becomes  $Va + Vth_{102h} + Vx$ .

20 [0140]

At this time, the transistor 102b, the transistor 102c, and the transistor 102e remain off and the transistor 102d is turned off; therefore, the voltage of the node NC2 remains equivalent to the value of the voltage Va and the transistor 102g remains on. The transistor 102a remains off and the transistor 102g remains on; therefore, the 25 voltage of the node NA2 remains equivalent to the value of the voltage Vb. Since the transistor 102f remains on, the voltage of the node NB2 remains equivalent to the value of the voltage Vb and the transistor 102h remains off. Further, the transistor 102n is turned off, the transistor 102p remains on, and the transistor 102h, the transistor 102i, the transistor 102j, the transistor 102k, the transistor 102l, the transistor 102m, the 30 transistor 102o, and the transistor 102q remain off, so that the signal OUT21 remains at a high level.

[0141]

Thus, the divided signal output circuit outputs the signal CLK3 as the signal OUT21. The signal CLK3 is a clock signal whose cycle is four times longer than the cycle of the signal CLK1.

[0142]

5 As described above, an example of the divider circuit of this embodiment includes a shift register and a divided signal output circuit. The shift register has a function of outputting  $2X$  pulse signals in accordance with a first clock signal and a second clock signal. The divided signal output circuit sets voltage of a signal to be a third clock signal in such a manner that  $X$  first transistors and  $X$  second transistors are sequentially turned on in accordance with the  $2X$  pulse signals, and the divided signal output circuit outputs the third clock signal with a cycle  $X$  times longer than a cycle of the first clock signal. In the shift register in the divider circuit of this embodiment, it takes shorter time to set the voltage of the pulse signal to a desired value. This is because the voltage of the pulse signal to be an output signal is set in accordance with 10 the voltage of the clock signal. Accordingly, with the use of the shift register, operation speed of the divider circuit can be improved, and a malfunction in dividing 15 operation can be prevented.

[0143]

In an example of the divider circuit of this embodiment, a voltage signal having 20 a value higher than power supply voltage is employed for setting voltage of a signal to be a third clock signal to a second voltage. With such a structure, the voltage of the third clock signal at a high level can be set higher than or equal to the power supply voltage.

[0144]

25 (Embodiment 3)

In this embodiment, a divider circuit in which a divider circuit including a shift register and a divider circuit having another structure are used in combination will be described.

[0145]

30 An example of a structure of the divider circuit of this embodiment will be described with reference to FIG. 7. FIG. 7 is a block diagram illustrating an example of a structure of the divider circuit of this embodiment.

[0146]

The divider circuit illustrated in FIG. 7 includes a unit divider circuit 201 (also referred to as DIV1) and a unit divider circuit 202 (also referred to as DIV2).

[0147]

5 A start signal SP31 (also referred to as a signal SP31) and a clock signal CK31 (also referred to as a signal CK31) are input to the unit divider circuit 201. The unit divider circuit 201 outputs a clock signal CK32 (also referred to as a signal CK32) with a cycle  $X$  times longer than a cycle of the signal CK31. Any of the divider circuits described in the above embodiments can be applied to the unit divider circuit 201. In

10 this case, the signal SP31 corresponds to the signal SP and the signal CK32 corresponds to the signal OUT21.

[0148]

The signal SP31 and the signal CK32 are input to the unit divider circuit 202. The unit divider circuit 202 outputs a clock signal CK33 (also referred to as a signal CK33) with a cycle  $K$  times ( $K$  is a natural number greater than or equal to 2) longer than a cycle of the signal CK32. A flip-flop can be used for the unit divider circuit 202, for example. Further, the unit divider circuit 202 may include a plurality of flip-flops. When a flip-flop is formed using transistors of the same conductivity type, the divider circuit 202 can be formed in the same process as the unit divider circuit 201. With

20 such a structure, clock signals which have cycles different from each other and  $K$  times longer than the cycle of the signal CK32 can be generated.

[0149]

As described with reference to FIG. 7, an example of the divider circuit of this embodiment is provided with a first unit divider circuit and a second unit divider circuit.

25 The first unit divider circuit is the divider circuit described in any of the above embodiments, and a cycle of a clock signal which is an output signal of the second unit divider circuit is longer than a cycle of a clock signal which is an output signal of the first unit divider circuit. The second unit divider circuit can have a circuit configuration simpler than that of the first unit divider circuit. Further, the speed of

30 dividing operation is generally faster as a cycle of the clock signal at the time after frequency division is shorter. Therefore, when the first unit divider circuit and the second unit divider circuit are used in combination, clock signals with cycles different

from each other can be generated while increase in an area of a circuit is suppressed, and a malfunction is suppressed.

[0150]

(Embodiment 4)

5 In this embodiment, a transistor including an oxide semiconductor layer, which can be used in any of the divider circuits of the above embodiments, will be described.

[0151]

10 The transistor including an oxide semiconductor layer, which can be used in any of the divider circuits of the above embodiments, is a transistor including a semiconductor layer which is highly purified to be intrinsic (also referred to as I-type) or substantially intrinsic.

[0152]

15 Examples of an oxide semiconductor used in the oxide semiconductor layer are a four-component metal oxide, a three-component metal oxide, and a two-component metal oxide. As the four-component metal oxide, an In-Sn-Ga-Zn-O-based metal oxide or the like can be used, for example. As the three-component metal oxide, an In-Ga-Zn-O-based metal oxide, an In-Sn-Zn-O-based metal oxide, an In-Al-Zn-O-based metal oxide, a Sn-Ga-Zn-O-based metal oxide, an Al-Ga-Zn-O-based metal oxide, a Sn-Al-Zn-O-based metal oxide, or the like can be used, for example. As the 20 two-component metal oxide, an In-Zn-O-based metal oxide, a Sn-Zn-O-based metal oxide, an Al-Zn-O-based metal oxide, a Zn-Mg-O-based metal oxide, a Sn-Mg-O-based metal oxide, an In-Mg-O-based metal oxide, an In-Sn-O-based metal oxide, or the like can be used, for example. In addition, an In-O-based metal oxide, a Sn-O-based metal oxide, a Zn-O-based metal oxide, or the like can also be used as the oxide 25 semiconductor. Moreover, the metal oxide that can be used as the oxide semiconductor may contain  $\text{SiO}_2$ .

[0153]

As the oxide semiconductor, a material represented by  $\text{InMO}_3(\text{ZnO})_m$  ( $m$  is 30 larger than 0) can be used. Here,  $M$  represents one or more metal elements selected from Ga, Al, Mn, and Co. For example, Ga, Ga and Al, Ga and Mn, Ga and Co, and the like can be given as  $M$ .

[0154]

The band gap of the oxide semiconductor layer is greater than or equal to 2 eV, preferably greater than or equal to 2.5 eV, more preferably greater than or equal to 3 eV, which reduces the number of carriers generated by thermal excitation to a negligible level. In addition, the amount of impurity such as hydrogen which might serve as a 5 donor is reduced to a certain amount or less so that the carrier concentration is lower than  $1 \times 10^{14}/\text{cm}^3$ , preferably lower than or equal to  $1 \times 10^{12}/\text{cm}^3$ . That is, the carrier concentration of the oxide semiconductor layer is reduced to zero or substantially zero.

[0155]