(12)发明专利

(10)授权公告号 CN 106209695 B

(45)授权公告日 2020.01.07

(21)申请号 201610857392.2

(74)专利代理机构 上海专利商标事务有限公司 31100

(22)申请日 2013.05.16

代理人 张欣

(65)同一申请的已公布的文献号

(51)Int.CI.

申请公布号 CN 106209695 A

H04L 12/933(2013.01)

(43)申请公布日 2016.12.07

(56)对比文件

(30)优先权数据

CN 101620585 A, 2010.01.06,

13/477,322 2012.05.22 US

CN 102449614 A, 2012.05.09,

(62)分案原申请数据

US 2009/0141654 A1, 2009.06.04,

201380024563.8 2013.05.16

审查员 徐千慧

(73)专利权人 英特尔公司

地址 美国加利福尼亚州

(72)发明人 S·兰甘纳坦 M·沃什

D·J·哈利曼

权利要求书3页 说明书19页 附图9页

(54)发明名称

给加载/存储通信协议提供低功率物理单元

(57)摘要

在一个实施例中,可以使用会聚的协议堆栈来统一从第一通信协议到第二通信协议的通信,以跨物理互连来提供数据传输。此堆栈可以被包含在一种设备中,该设备包括用于包括事务和链路层的第一通信协议的协议堆栈,以及耦合到所述协议堆栈以在所述设备和通过物理链路耦合到所述设备的装置之间提供通信的物理(PHY)单元。此PHY单元可以包括符合第二通信协议的物理单元电路。描述并要求保护其他实施例。

1. 一种用于数据传输的装置,包括:

用于外围组件互连Express<sup>TM</sup>PCIe<sup>TM</sup>通信协议的协议堆栈模块,所述协议堆栈模块包括事务层和链路层;以及

耦合到所述协议堆栈模块的物理单元,用于在所述装置和通过物理链路耦合到所述装置的设备之间提供通信,所述物理单元包括链路训练和管理逻辑,以及与移动行业处理器接口MIPI规范相符的物理单元电路M-PHY,其中所述链路训练和管理逻辑用于将所述物理链路配置和初始化为在训练所述链路前所确定的链路宽度。

2. 如权利要求1所述的装置,其特征在于,所述物理单元电路包括多个物理单元电路,每一物理单元电路都通过所述物理链路的单一信道来进行通信。

3. 如权利要求1所述的装置,其特征在于,所述链路训练和管理逻辑用于支持多通道通信。

4. 如权利要求1所述的装置,其特征在于,所述链路训练和管理逻辑用于支持非对称的链路宽度配置。

5. 如权利要求1所述的装置,其特征在于,所述链路训练和管理逻辑用于支持动态带宽可缩放性。

6. 如权利要求1所述的装置,其特征在于,所述物理链路具有从所述装置到所述设备的,与从所述设备到所述装置相比非对称的宽度。

7. 如权利要求1所述的装置,其特征在于,所述物理链路能够配置为从所述装置到所述设备以同从所述设备到所述装置相比非对称的频率操作。

8. 如权利要求1所述的装置,其特征在于,所述物理链路会由于所述装置的复位而被配置成初始链路宽度和频率。

9. 如权利要求1所述的装置,其特征在于,所述装置包括片上系统SoC。

10. 如权利要求9所述的装置,其特征在于,所述SoC包括多个核,所述协议堆栈模块耦合到所述多个核。

11. 如权利要求1所述的装置,还包括耦合在所述装置和所述设备之间的边带互连。

12. 如权利要求11所述的装置,其特征在于,所述装置还包括第二物理单元,用于实现同所述装置经由所述边带互连的通信。

13. 如权利要求11所述的装置,其特征在于,所述装置用于经由所述物理链路以第一数据速率发送第一信息,并经由所述边带互连以第二数据速率发送第二信息,所述第二数据速率低于所述第一数据速率。

14. 如权利要求1所述的装置,其特征在于,所述装置还包括串行物理单元以用于连接到至少一个外围设备。

15. 如权利要求14所述的装置,其特征在于,所述装置包括多频段无线电设备。

16. 一种用于数据传输的装置,包括:

根复合体,所述根复合体包括:

和外围组件互连Express<sup>TM</sup>PCIe<sup>TM</sup>通信协议相符的事务层;

耦合到所述事务层的链路层,所述链路层和所述PCIe<sup>TM</sup>通信协议相符;以及

物理单元,其耦合到所述链路层以实现经由物理链路的通信,所述物理单元包括:

链路训练和管理逻辑,以及与移动行业处理器接口MIPI规范相符的物理单元电路M-

PHY, 其中所述链路训练和管理逻辑用于将所述物理链路配置和初始化为在训练所述物理链路前所确定的链路宽度, 并且用于支持多通道通信、非对称的链路宽度配置、以及动态带宽可缩放性; 以及

至少一个端口, 用于耦合到所述物理链路, 所述至少一个端口能够配置为在N和1之间的多个链路宽度, 其中N至少为16, 所述至少一个端口包括:

发送电路, 包括编码器以根据8b/10b编码来编码数据; 以及

接收机电路, 包括解码器以根据所述8b/10b编码来解码数据。

17. 如权利要求16所述的装置, 其中所述物理链路具有从所述根复合体到设备的、与从所述设备到所述根复合体相比非对称的宽度。

18. 如权利要求16所述的装置, 其中所述物理链路能够配置为从所述根复合体到设备以同从所述设备到所述根复合体相比非对称的频率操作。

19. 如权利要求16所述的装置, 其特征在于, 所述物理链路会由于所述根复合体的复位而被配置成初始链路宽度和频率。

20. 如权利要求16所述的装置, 其特征在于, 所述根复合体包括片上系统SoC。

21. 如权利要求20所述的装置, 其特征在于, 所述SoC包括多个核, 协议堆栈模块包括所述事务层和所述链路层, 所述协议堆栈模块耦合到所述多个核。

22. 一种用于数据传输的系统, 包括:

片上系统SoC, 其包括:

多个核;

用于外围组件互连Express<sup>TM</sup>PCIe<sup>TM</sup>通信协议的协议堆栈模块, 所述协议堆栈模块包括事务层和链路层; 以及

物理单元, 其耦合到所述协议堆栈模块以在所述SoC和通过物理链路耦合到所述SoC的第一收发器之间提供通信, 所述物理单元包括链路训练和管理逻辑, 以及与移动行业处理器接口MIPI规范相符的物理单元电路M-PHY, 其中所述链路训练和管理逻辑用于将所述物理链路配置和初始化为在训练所述链路前所确定的链路宽度;

耦合在所述SoC和所述第一收发器之间的所述物理链路, 其中所述物理链路能够配置为以从所述SoC到所述第一收发器和从所述第一收发器到所述SoC非对称的宽度来操作;

经由所述物理链路耦合到所述SoC的所述第一收发器, 所述第一收发器包括:

用于所述PCIe<sup>TM</sup>通信协议的第二协议堆栈模块, 所述第二协议堆栈模块包括第二事务层和第二链路层; 以及

第二物理单元, 其耦合到所述协议堆栈模块以在所述SoC和通过物理链路耦合到所述SoC的第一收发器之间提供通信, 所述第二物理单元包括第二链路训练和管理逻辑, 和第二M-PHY;

耦合到所述SoC的图像捕捉装置, 用于捕捉图像信息; 以及

耦合到所述SoC的触摸屏显示器。

23. 如权利要求22所述的系统, 其特征在于, 所述物理单元电路包括多个物理单元电路, 每一物理单元电路都通过所述物理链路的单一信道来进行通信。

24. 如权利要求22所述的系统, 其特征在于, 所述链路训练和管理逻辑用于支持动态带宽可缩放性。

25. 如权利要求22所述的系统,其特征在于,所述SoC还包括至少一个有序核和至少一个无序核。

26. 如权利要求22所述的系统,还包括经由第二物理链路耦合到所述SoC的第二收发器。

27. 如权利要求22所述的系统,其特征在于,所述系统包括平板计算机。

28. 一种用于数据传输的方法,包括:

在用于物理链路的训练过程之前为所述物理链路确定链路宽度,所述物理链路耦合根复合体和设备,其中所述根复合体包括用于外围组件互连Express<sup>TM</sup>PCIe<sup>TM</sup>通信协议的协议堆栈模块,所述协议堆栈模块包括事务层和链路层,并且所述根复合体包括物理单元,所述物理单元耦合到所述协议堆栈模块以在所述根复合体和通过物理链路耦合到所述根复合体的设备之间提供通信,所述物理单元包括链路训练和管理逻辑,和与移动行业处理器接口MIPI规范相符的物理单元电路M-PHY;

将所述物理链路配置和初始化为所确定的链路宽度;以及

训练所述物理连接,包括执行所述物理链路的每个通道的比特锁,执行所述物理链路的每个通道的符号锁,和执行所述物理链路的多个通道的通道-通道去扭斜以处理多个通道之间的信号偏斜中的差异以重新对准字节。

29. 一种存储有指令的机器可读的介质,所述指令,响应于在计算设备上执行,导致计算设备执行如权利要求28所述的方法,或实现如权利要求1—21中任一项所述的装置的功能,或实现如权利要求22—27中任一项所述的系统的功能。

## 给加载/存储通信协议提供低功率物理单元

[0001] 本申请是国际申请号为PCT/US2013/041305,国际申请日为2013年5月16日,进入中国国家阶段的申请号为201380024563.8,名称为“给加载/存储通信协议提供低功率物理单元”的发明专利申请的分案申请。

### 技术领域

[0002] 各实施例涉及互连技术。

[0003] 背景

[0004] 为在系统内的不同设备之间提供通信,使用某种类型的互连机制。取决于系统实现,可以有各种这样的互连。通常,为使两个设备相互进行通信,它们共享共同的通信协议。

[0005] 用于在计算机系统中的各设备之间进行通信的一种典型的通信协议是外围组件互连Express (PCI Express™(PCIe™)) 通信协议,符合基于PCI Express™规范基本规范版本3.0(2010年11月18日发布)(下文简称为PCIe™规范)的链路。此通信协议是加载/存储输入/输出IO)互连系统的一个示例。设备之间的通信通常以非常高的速度根据此协议串行地执行。开发了关于此协议的各种参数,旨在实现最大性能,不考虑功率效率,因为PCIe™通信协议是在台式计算机的上下文中开发的。结果,其特征中有许多不会缩减到可能合并到移动系统中的较低功率的解决方案。

[0006] 除关于常规加载/存储通信协议的这些功率顾虑之外,现有的链路管理方案通常非常复杂,并涉及大量的状态,导致在各状态之间执行过渡需要一个冗长的过程。这部分地由于现有的链路管理机制,这些机制被开发成理解多个不同形状因子要求,诸如连接器,不同系统合并等等。一个这样的示例是根据PCIe™通信协议的链路管理。

[0007] 附图简述

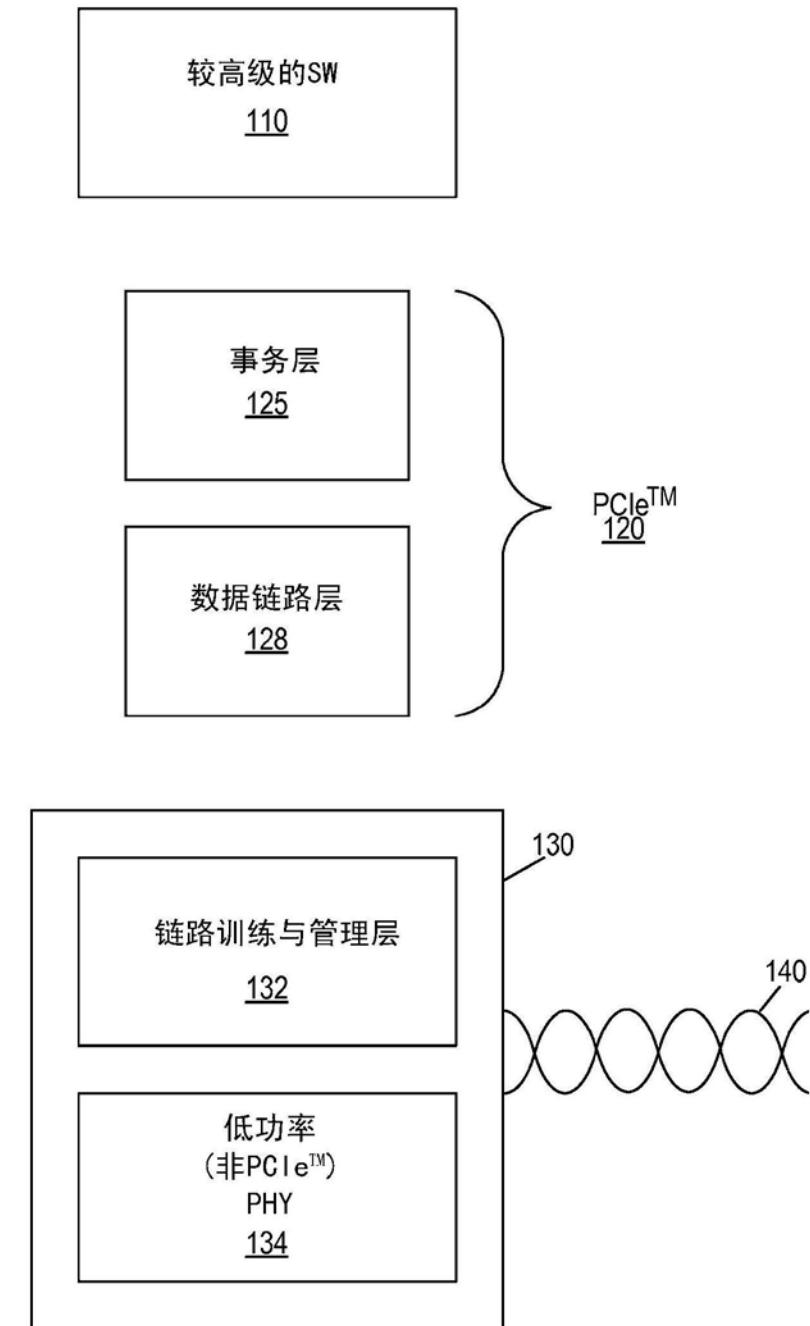

[0008] 图1是根据本发明的一个实施例的通信协议的协议堆栈的高级框图。

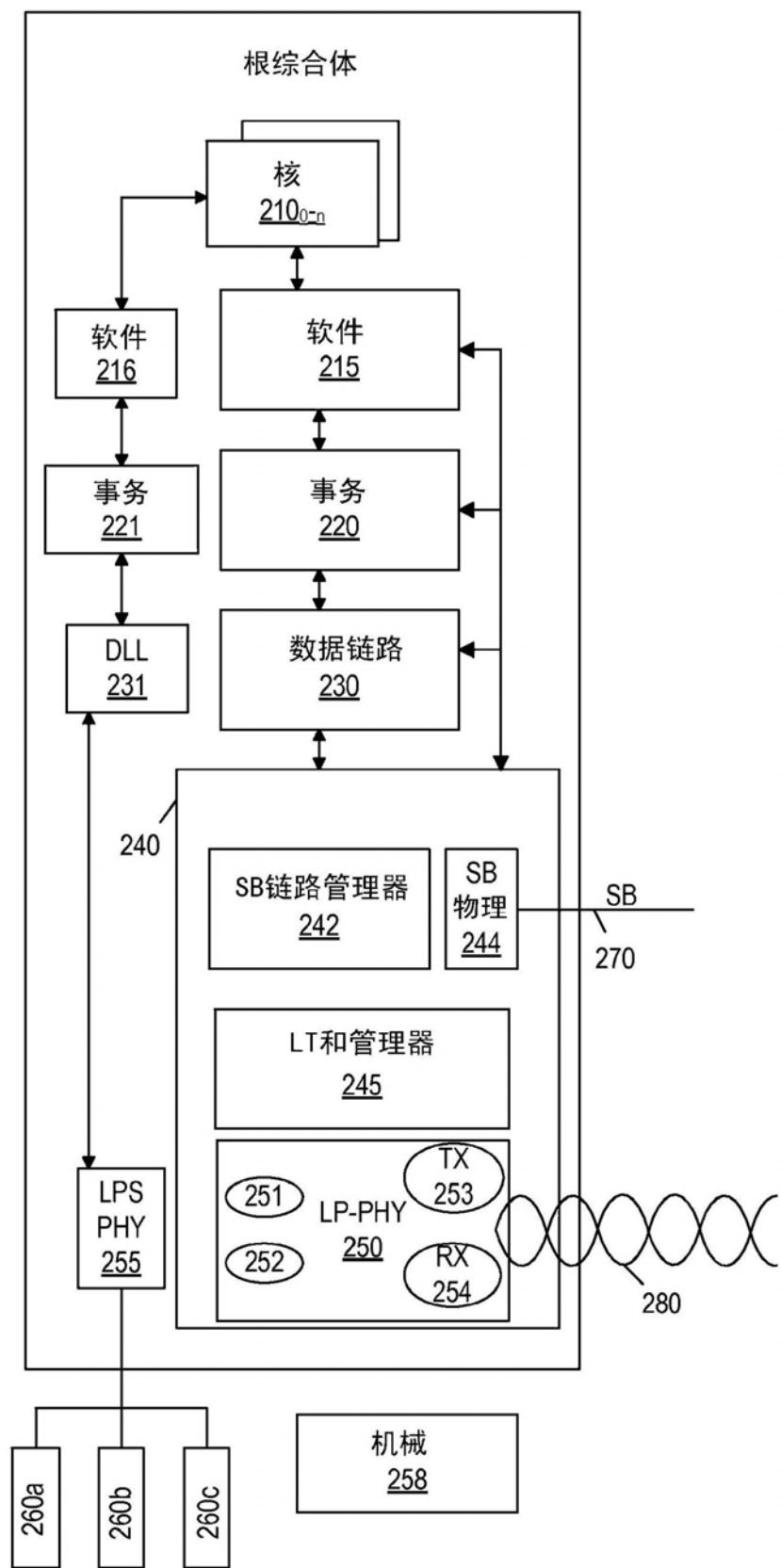

[0009] 图2是根据本发明的一个实施例的片上系统(SoC)的框图。

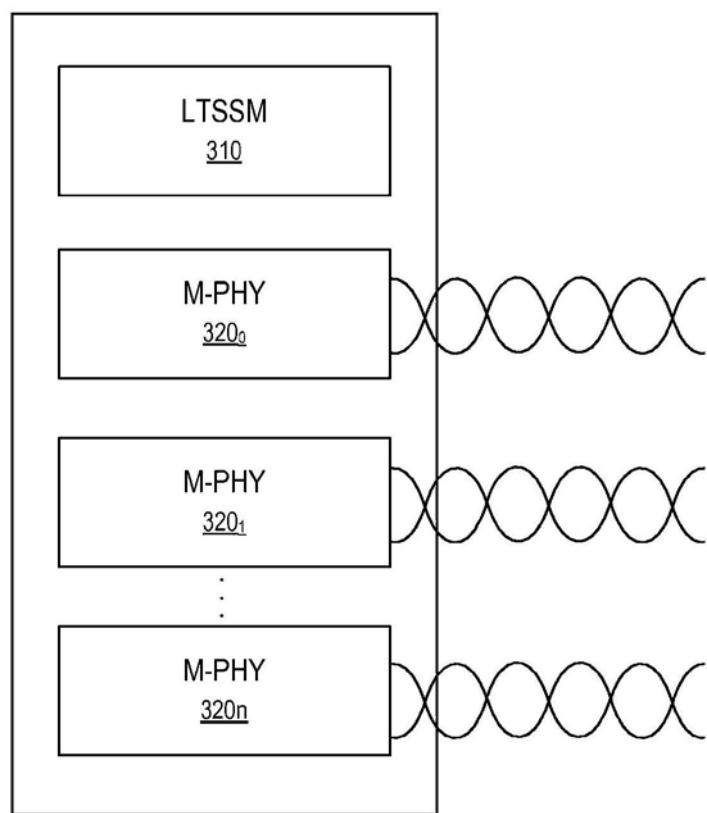

[0010] 图3是根据本发明的另一实施例的物理单元的框图。

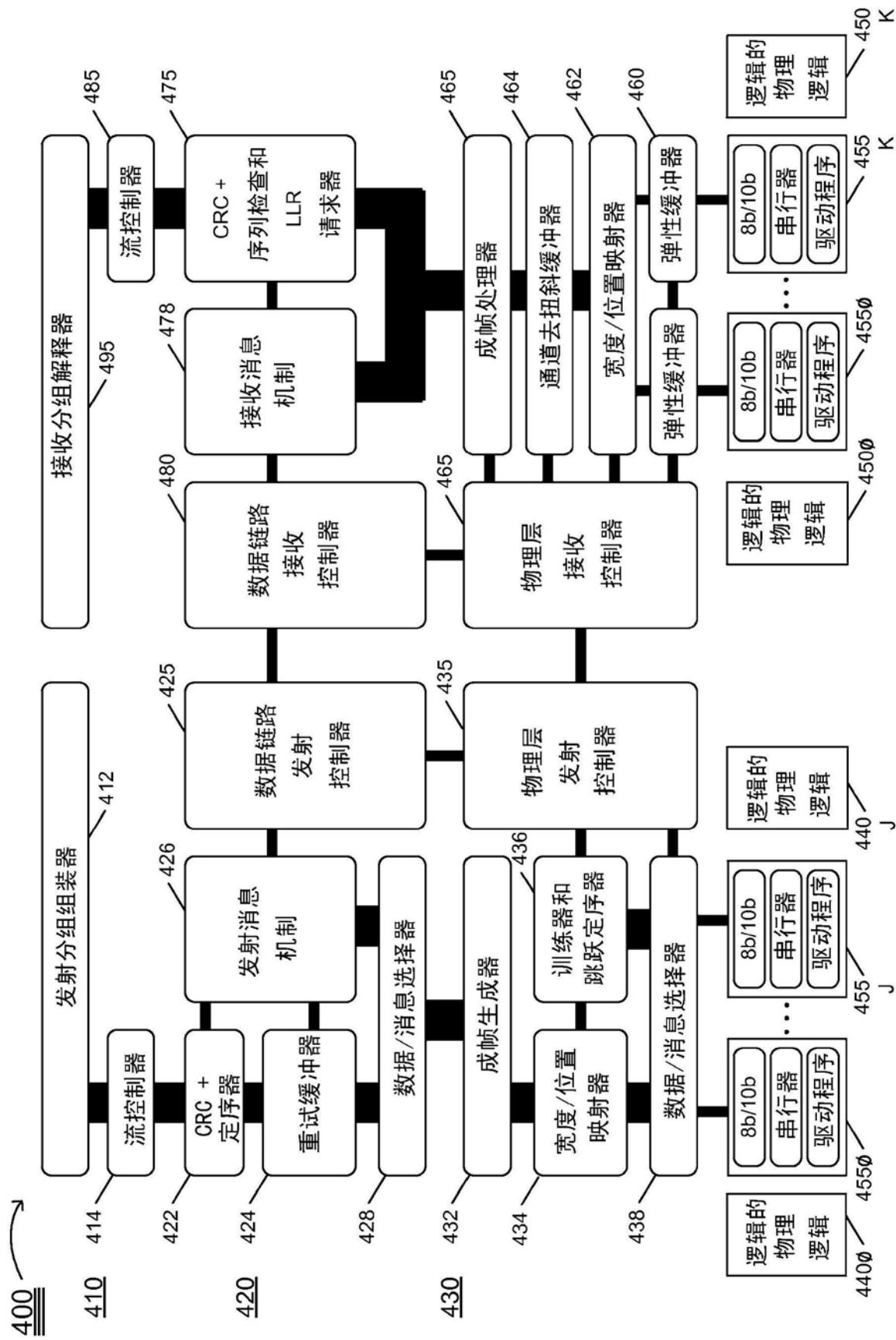

[0011] 图4是根据本发明的一个实施例的协议堆栈的进一步的细节的框图。

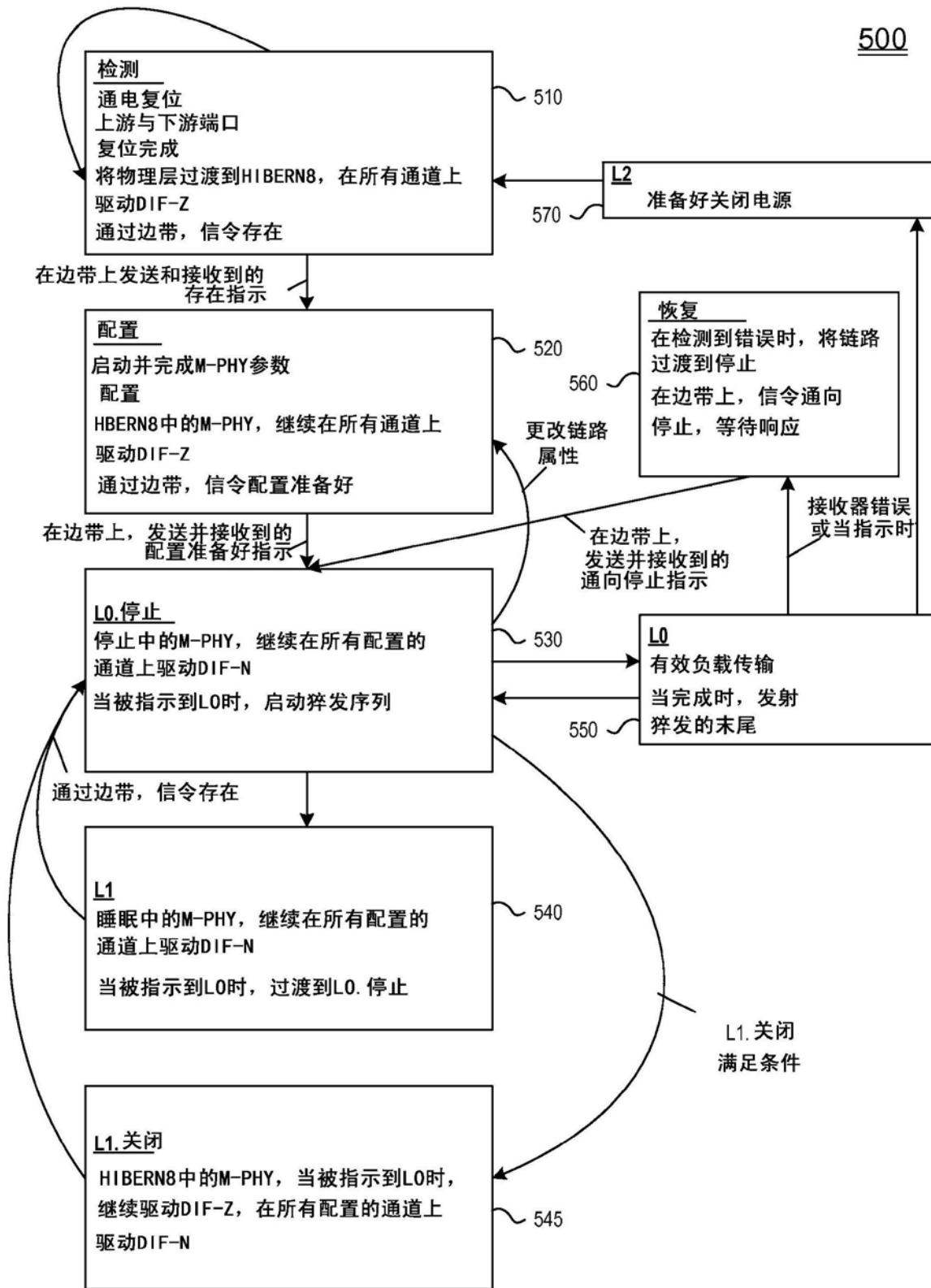

[0012] 图5是根据本发明的一个实施例的链路训练状态机的状态图,该状态机可以是链路管理器的一部分。

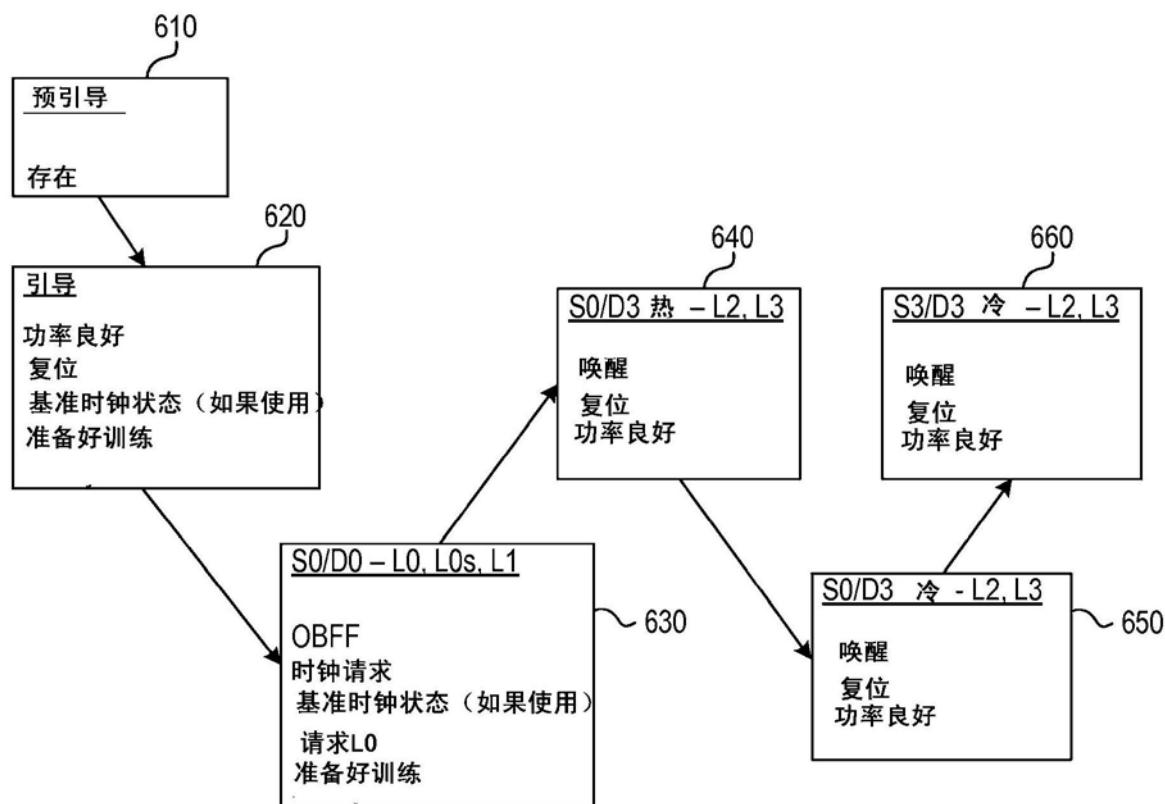

[0013] 图6是根据本发明的一个实施例的边带机制的各种状态的流程图。

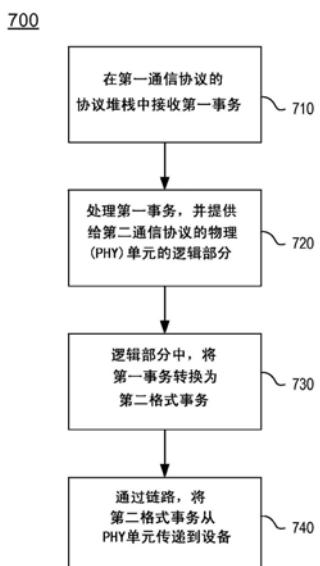

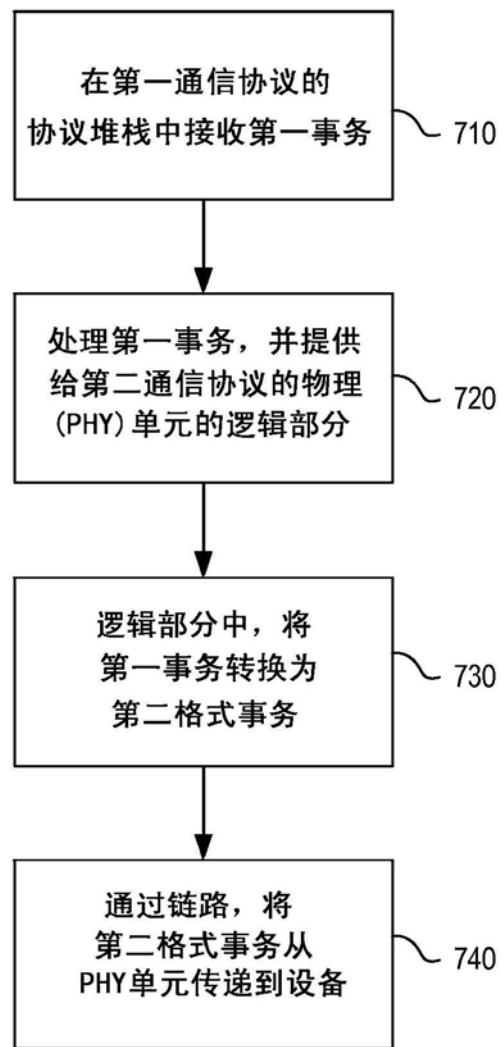

[0014] 图7是根据本发明的一个实施例的方法的流程图。

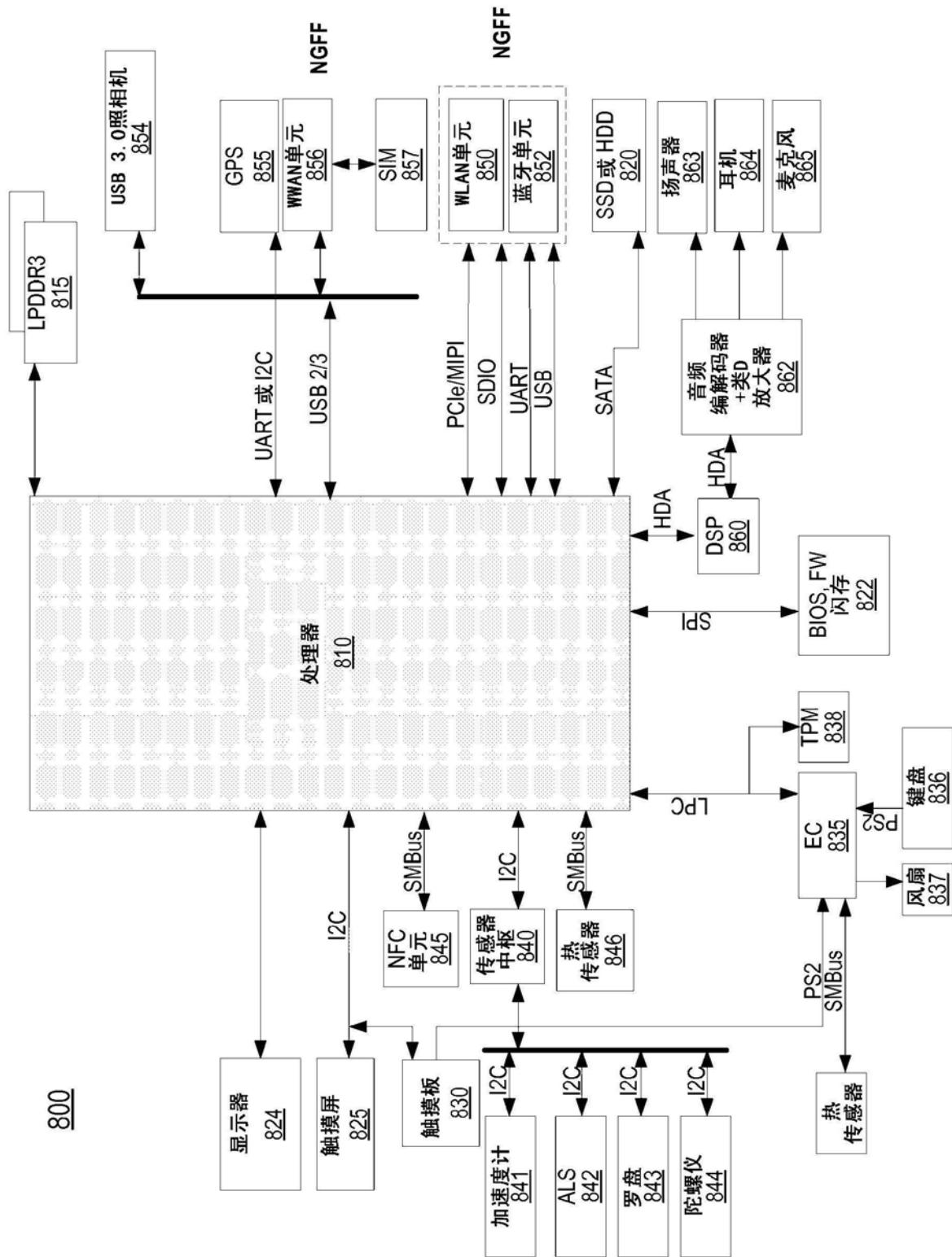

[0015] 图8是存在于根据本发明的一个实施例的计算机系统中的组件的框图。

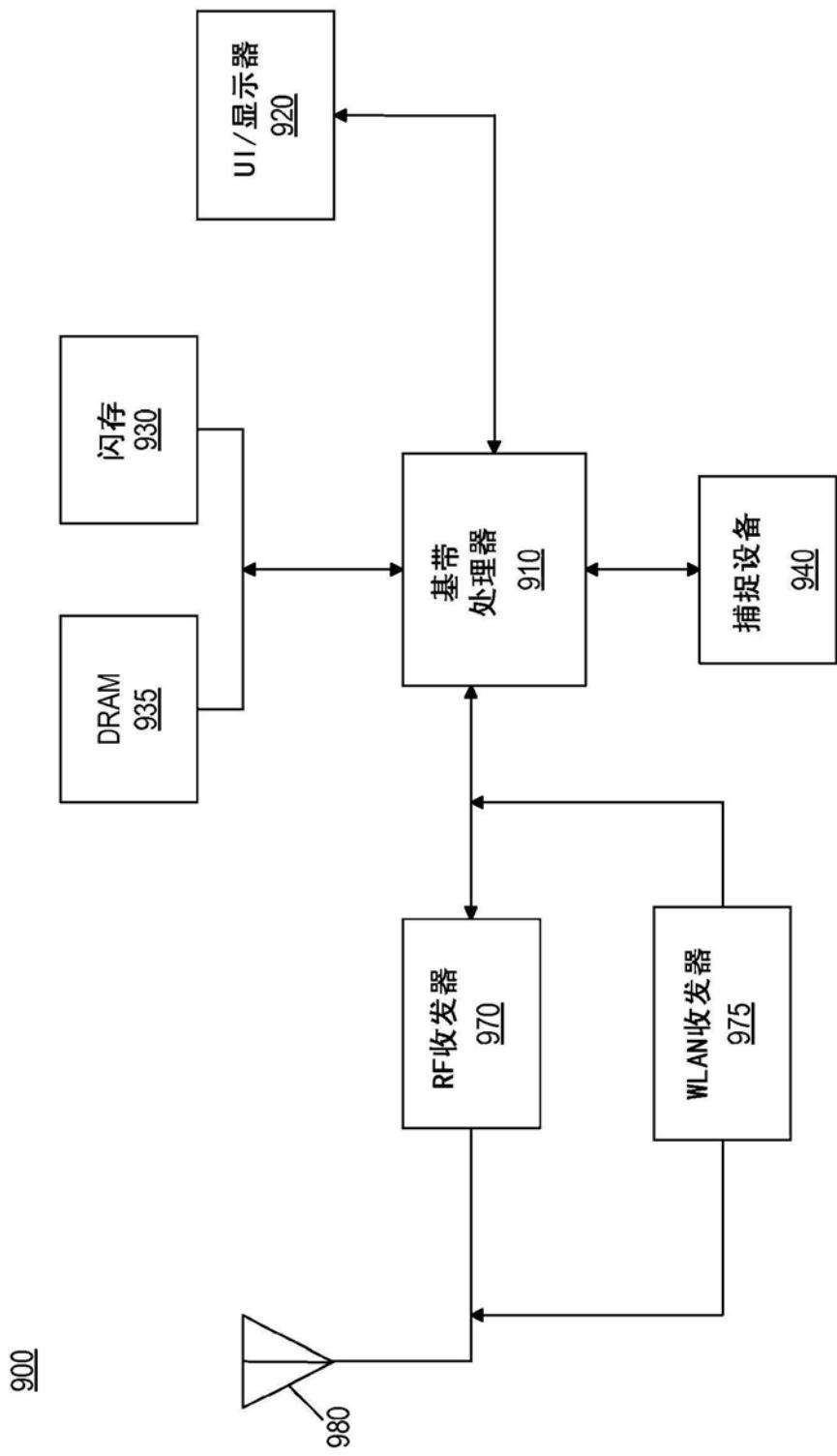

[0016] 图9是可以与各实施例一起使用的示例系统的框图。

### 具体实施方式

[0017] 各实施例可以提供输入/输出(IO)互连技术,该技术具有低功率、加载/存储架构,并特别适用于移动设备中,包括诸如智能电话之类的蜂窝电话,平板电脑、电子阅读器、超极本™等等。

[0018] 在各实施例中,给定通信协议的协议堆栈可以与不同通信协议的物理单元,或至少不同于给定通信协议的物理单元的物理(PHY)单元一起使用。物理单元包括逻辑层和物理或电气层两者,这些层通过互连提供信息信号的实际、物理通信,该互联诸如链接两个独立半导体管芯(可以是单一集成电路(IC)封装,或,例如,通过电路板路由、迹线等等耦合的单独的封装内的两个半导体管芯)的链路。另外,物理单元可以执行数据分组的成帧/去成帧(deframe),执行链路训练和初始化,并处理数据分组,以便传递到物理互连从物理互连接收。

[0019] 虽然可以有不同的实现,但是,在一个实施例中,协议堆栈可以是基于常规个人计算机(PC)的通信协议的协议堆栈,该通信协议诸如外围组件互连Express((PCI) Express<sup>TM</sup>(PCIe<sup>TM</sup>))通信协议,其符合PCI Express<sup>TM</sup>规范基本规范版本3.0(2010年11月18日发布的)(下文简称为PCIe<sup>TM</sup>规范),应用协议扩展的进一步的版本,或另一这样的协议,而物理单元不符合PCIe<sup>TM</sup>通信协议。此物理单元可以专门设计用于实现低功率操作,以允许基本上不变的PCIe<sup>TM</sup>上协议堆栈与此低功率物理电路的合并。如此,可以利用PCIe<sup>TM</sup>通信协议的宽的旧式基础,以便合并到以低功率操作的便携及其他非基于PC的形状因子中。虽然本发明的范围在这方面不受限制,但是,在一个实施例中,此物理单元可以是从移动平台修改而来的物理单元,诸如符合移动行业处理器接口(MIPI)联盟(这是一个设置移动计算设备的标准的小组)的M-PHY规范版本1.00.00-2011年2月8日(MIPI董事会于2011年4月28日批准)(下文简称为MIPI规范)的所谓的M-PHY。然而,可以使用其他低功率物理单元,诸如符合其他低功率规范的,诸如用于在多芯片封装内将各个管芯耦合在一起的,或自定义低功率解决方案。如此处所使用的,术语“低功率”意味着在低于常规PC系统的功率消耗级别,可以适用于各种移动和便携式设备。作为示例,“低功率”可以是比常规PCIe<sup>TM</sup>物理单元消耗较少功率的物理单元。

[0020] 如此,通过将传统的PCIe<sup>TM</sup>协议堆栈与不同类型的物理单元集成,可以利用为PCIe<sup>TM</sup>开发的大量的旧式组件的再次使用,以便合并到移动或其他便携或低功率平台中。

[0021] 各实施例还可以利用现有的加载/存储I/O技术,特别是PCIe<sup>TM</sup>,被设计为实现最大性能的认识,其中,功率效率不是主要顾虑因素,如此,不会缩减到低功率应用。通过组合常规加载/存储协议堆栈的某些部分与低功率设计的物理单元,各实施例可以保留PCIe<sup>TM</sup>的性能优势,而同时在设备和平台级别实现最佳等级功率。

[0022] 如此,各实施例可以是与具有大量的旧式基础的普遍存在的PCIe<sup>TM</sup>架构兼容的软件。另外,各实施例还可以实现移动设计的PHY,例如,M-PHY,的直接PHY再次使用。如此,可以在有效率的功率/比特传输的情况下,利用电磁接口/射频接口(EMI/RFI)友好的方法,实现低活动和空闲功率,因为PHY可以以不会干扰相关联的无线电的时钟速率操作(因为PHY的时钟频率的谐波不会干扰典型的无线电解决方案操作的常见的无线电频率(例如,1.8,1.9,2.4千兆赫(GHz)或其他这样的无线电频率)。

[0023] 各实施例还可以进一步提供架构增强,这些增强实现优化的链路训练和管理机制(LTSSM);优化的流控制和重试缓冲和管理机制;用于改变链路操作模式的架构的协议;快速硬件-支持的设备状态保存和恢复;以及,用于带有可选的带内支持的链路管理的合并的边带机制。

[0024] 在各实施例中,PCIe<sup>TM</sup>事务和数据链路层可被实现为具有有限的修改的协议堆栈

的一部分,以考虑不同的链路速度和非对称的链路。另外,还可以提供修改的链路训练和管理,以包括对于多通道通信、非对称的链路配置、边带合并,以及动态带宽可缩放性的支持。各实施例还可以进一步提供对于现有的基于PCIe™的和非基于PCIe™的逻辑和电路(诸如M-PHY逻辑和电路)之间的桥接的支持。

[0025] 此分层方法使现有的软件堆栈(例如,操作系统(OS)、虚拟机管理器和驱动程序)能在不同的物理层上无缝地运行。对数据链路和事务层的影响被最小化,并可以包括更新与更新确认频率、重播计时器等等相关的计时器。

[0026] 如此,各实施例会限制在PCIe™系统中提供的某些灵活性,因为这种灵活性在某些情况下会在PCIe™系统及其他系统中产生某些复杂性。确实这样,因为这两种协议提供大量灵活性,以实现即插即用能力。相反,各实施例可以定制一种最小化设计中的灵活性的量的解决方案,因为当合并到给定系统时,例如,作为互连到另一集成电路(IC)的片上系统(SoC),发生已知和固定的配置。由于在实现上存在的精确配置是已知的,由于SoC和连接的设备两者都粘接在平台内,例如,焊接到系统的电路板,因此,不需要对于这些设备的即插即用能力,如此,可能不需要PCIe™或其他基于PC的通信协议中固有的使不同的设备能无缝合并到带有即插即用能力的系统中的较大的灵活性。

[0027] 作为一个示例,SoC可以充当在第一IC中实现的,并耦合到第二IC的根综合体,第二IC可以是无线电解决方案,可包括多个无线通信设备的一个或多个设备。这样的设备的范围可以从低功率短程通信系统,诸如符合Bluetooth™规范的、本地无线通信,诸如符合给定电气与电子工程师学会(IEEE)802.11标准的所谓的WiFi™系统,到之间较高功率无线系统,诸如给定蜂窝通信协议,诸如3G或4G通信协议。

[0028] 现在参考图1,所示是根据本发明的一个实施例的通信协议的协议堆栈的高级别框图。如图1所示,堆栈100可以是诸如IC之类的半导体组件内的软件、固件和硬件的组合,以在半导体器件和耦合到它的另一器件之间处理数据通信。在图1的实施例中,示出了高级视图,以较高级软件110开始,该软件110可以是各种类型的在给定平台上执行的软件。此较高级软件可包括操作系统(OS)软件、固件、应用程序软件等等。要通过互连140传递的数据可以穿过在图1内一般性地示出的协议堆栈的各层,互连140可以是将半导体器件与另一组件耦合的给定物理互连。可以看出,此协议堆栈的某些部分可以是常规PCIe™堆栈120的一部分,并可以包括事务层125和数据链路层128。一般而言,事务层125操作以生成事务层分组(TLP),TLP可以是按时间分隔的基于请求或响应的分组,当目标设备收集用于响应的数据时,允许链路携带其他通信量。事务层进一步处理基于信用的流控制。如此,事务层125在设备的处理电路和诸如数据链路层和物理层之类的互连架构之间提供接口。关于这一点,事务层的主要职责是分组(即,事务层分组(TLP))的组装和拆卸,以及处理基于信用的流控制。

[0029] 数据链路层128又可以排列由事务层所生成的TLP,并确保TLP在两个端点之间的可靠递送(包括处理错误检查)和确认处理。如此,链路层128充当事务层和物理层之间的中间阶段,并提供用于通过链路在两个组件之间交换TLP的可靠机制。链路层的一端接受由事务层组装的TLP,应用标识符,计算并应用错误检测代码,例如,循环恢复代码(CRC),并将修改过的TLP提交到物理层,用于跨物理链路传输到外部设备。

[0030] 在在数据链路层128中处理之后,可以将分组传递到PHY单元130。一般而言,PHY单

元130可以包括低功率PHY 134,该低功率PHY 134可以包括逻辑层和物理(包括电气)子层。在一个实施例中,通过PHY单元130来表示的物理层在物理上将分组发射到外部设备。物理层包括准备用于传输的传出信息的发射部分,以及在将接收到的信息传给链路层之前标识并准备接收到的信息的接收器部分。给发射器提供了序列化并发射到外部设备的符号。给接收器提供了来自外部设备的串行化的符号,接收器将接收到的信号转换为比特流。将比特流解串行化,并提供给逻辑子块。

[0031] 在一个实施例中,低功率PHY 134(可以是给定低功率PHY,专门开发的或从诸如M-PHY之类的另一PHY修改而来的),可以用于对分组化的数据的处理,以便沿着互连140传递。在图1中进一步可以看出,在PHY单元130内还可以存在链路训练和管理层132(此处也被称为“链路管理器”)。在各实施例中,链路管理器132可包括可以从诸如PCIe<sup>TM</sup>协议之类的另一通信协议实现的某些逻辑,以及处理常规(例如,上面的PCIe<sup>TM</sup>协议堆栈)以及不同的协议的物理PHY 134之间的连接的专门逻辑。

[0032] 在图1的实施例中,互连140可被实现为差分线对,可以是两对单向线路。在某些实现中,可以使用多组差分对来增大带宽。需要注意的是,根据PCIe<sup>TM</sup>通信协议,要求每一方向上的差分对的数量是相同的。然而,根据各实施例,可以在每一方向提供不同数量的对,这可以提供更有效率并且更低功率的操作。此整体会聚的堆栈和链路140可以被称为移动Express PCIe<sup>TM</sup>互连或链路。尽管在图1的实施例中以此高级别示出的,但是,可以理解,本发明的范围在这方面不受限制。即,可以理解,图1所示出的视图简单地关于从事务层到物理层的协议堆栈,以及较高级别的软件,没有示出包括此堆栈的SoC或其他半导体器件的各种其他电路。

[0033] 现在参考图2,所示是根据本发明的一个实施例的SoC的框图。如图2所示,SoC 200可以用于实现到各种类型的平台的任何类型的SoC,从诸如智能电话、个人数字助理(PDA)、平板电脑、上网本、超极本<sup>TM</sup>等等相对较小的低功率便携式设备,到可以以较高级别的系统实现的比较高级的SoC。

[0034] 如图2所示,SoC 200可以包括一个或多个核210<sub>0</sub>-210<sub>n</sub>。如此,在各实施例中,多核SoC是可能的,其中,核可以全部是给定架构的同构核,例如,有序或无序处理器。或者,也可以有异构核,例如,某些相对较小的低功率核,例如,有序架构的,且存在额外的核,可以是较大的并且更加复杂化的架构,例如,无序架构。协议堆栈允许数据在系统的这些核及其他组件中的一个或多个之间的传递。可以看出,此堆栈可包括软件215,该软件215可以是较高级软件,诸如OS、固件以及在核中的一个或多个上执行的应用级软件。另外,协议堆栈还包括事务层220和数据链路层230。在各实施例中,这些事务和数据链路层可以符合诸如PCIe<sup>TM</sup>协议之类的给定通信协议。当然,在其他实施例中,可以存在诸如符合通用串行总线(USB)协议堆栈之类的不同的协议堆栈的层。此外,在某些实现中,如此处所描述的低功率PHY电路可以与现有的替换的协议堆栈多路复用。

[0035] 仍参考图2,此协议堆栈又可以耦合到物理单元240,该物理单元240可以包括可以通过多个互连提供通信的多个物理单元。在一个实施例中,第一物理单元250可以是低功率PHY单元,在一个实施例中,该低功率PHY单元可以对应于符合MIPI规范的M-PHY,以通过主互连280提供通信。另外,还可以存在边带(SB)PHY单元244。在所示出的实施例中,此边带PHY单元可以通过边带互连270提供通信,该边带互连270可以是合并的边带,以提供某些边

带信息,例如,以比耦合到第一PHY 250的主要互连280较慢的数据速率。在某些实施例中,协议堆栈的各层可以具有耦合到此SB PHY 244的单独的边带,以允许沿着此边带互连的通信。

[0036] 另外,PHY单元240还可以包括可以被用来控制SB PHY 244的SB链路管理器242。另外,链路训练和状态管理器245可以存在,并可以被用来使协议堆栈(符合第一通信协议)适应第一PHY 250(符合第二通信协议),以及提供对第一PHY 250和互连280的总体控制。

[0037] 进一步可以看出,在第一PHY 250中可以存在各种组件。更准确地说,可以存在发射器和接收器电路(即,TX 253和RX 254)。一般而言,此电路可以被用来执行串行化操作,解串行化操作以及通过主要互连280的数据传输和接收。保存状态管理器251可以存在,并可以被用来当它处于低功率状态时保存关于第一PHY 250的配置及其他状态信息。此外,编码器252还可以存在,以执行线编码,例如,根据8b/10b协议。

[0038] 在图2中进一步可以看出,可以存在机械接口258。此机械接口258可以是给定互连,以从根综合体200提供通信,更具体地是通过主要互连280往返于第一PHY 250的通信。在各实施例中,此机械连接可以通过诸如球栅阵列(BGA)或其他表面安装,或镀通孔连接之类的半导体器件的针脚。

[0039] 除这些主要通信机制之外,额外的通信接口可以通过低功率串行(LPS)PHY单元255,该PHY单元255通过包括软件层216、事务层221以及链路层231的单独堆栈耦合在核210和一个或多个芯片外设备260a-c之间,芯片外设备260a-c可以是各种低数据速率外围设备,诸如传感器、加速度计、温度传感器、全球定位系统(GPS)电路、罗盘电路、触摸屏电路、键盘电路、鼠标电路等等。

[0040] 请注意,在各实施例中,边带互连270和主要互连280两者都可以耦合在SoC 200和另一半导体组件(例如,另一IC,诸如多频带无线解决方案)之间。

[0041] 再次,尽管图2的图示是相对较高的级别,但是,各种变体也是可以的。例如,可以提供多个低功率PHY,以允许较高速率的数据通信,例如,通过多个信道,其中,每一信道都与独立PHY相关联。现在参考图3,所示是根据本发明的另一个实施例的物理单元的框图。如图3所示,物理单元300包括链路训练和状态管理器310。此状态管理器可以如上文所描述的,并可以是逻辑集合,以允许第一通信协议的协议堆栈与第二(例如,不同的)通信协议的物理单元的连接。

[0042] 在图3中进一步可以看出,链路训练和状态管理器310可以与多个M-PHY 320<sub>0</sub>-320<sub>n</sub>进行通信。通过提供一个以上的这样的PHY,可以发生较高速率的数据通信。请注意,尽管图3中所示出的每一M-PHY都可以包括某些逻辑,以允许发生其各个独立通信,对这些不同的M-PHY的通信的总体控制可以通过链路训练和状态管理器310。此外,还可以理解,尽管在图3中示出了多个M-PHY,但是,在其他实施例中,可以存在另一种类型的多个PHY单元,并可以提供另外的多个异构的PHY单元。请注意,每一M-PHY单元都可以用作唯一逻辑链路的一部分,或分组使用,其中,一个组与单一逻辑链路相关联。每一设备通常都可以消耗单一逻辑链路,但是,在某些实施例中,单一物理设备可以消耗多个逻辑链路,例如,以为多功能组件的不同的功能提供专用的链路资源。

[0043] 现在参考图4,所示是根据本发明的一个实施例的协议堆栈的进一步的细节的框图。如图4所示,堆栈400包括各层,包括事务层410、数据链路层420以及物理层430。如上文

所描述的,这些不同的层可以使用PCIe<sup>TM</sup>协议堆栈的常规事务和数据链路部分,或这样的堆栈的修改版本来配置,以适应此第一通信协议的这些层和另一通信协议的物理层之间的交互,在图4的实施例中,该另一通信协议可以是符合MIPI规范的M-PHY。

[0044] 如图4所示,关于从协议堆栈400发射信息的发射方向,在事务层的发射分组组装器412中接收向协议堆栈的传入的信息,例如,来自诸如核之类的SoC或其他处理逻辑的其他电路,事务层通常组合控制和数据路径以形成TLP。在被组装为发射分组(在各实施例中,可以是具有,例如,1到4096字节(或较小的最大允许的大小,例如,128或256)的数据分组)之后,组装的数据分组被提供到流控制器414,该流控制器414基于排队用于传输的接下来的TLP所需的数量,判断是否有足够的流控制信用可用,并控制分组向数据链路层420的注入。更准确地说,可以看出,这些被注入的分组被提供了错误检测器和定序器422,该定序器422,在一个实施例中,可以生成TLP序列号和LCRC。进一步可以看出,数据链路层420还包括发射消息机制426,该机制426又生成用于链路管理功能的DLLP,并耦合到数据链路发射控制器425,该控制器425是用于流控制和数据链路完整性(ACK/NAK)机制的控制器功能;请注意,这可以细分,以便这些功能使用不同的逻辑块来实现。

[0045] 进一步可以看出,处理过的数据分组被提供到重试缓冲器424,该重试缓冲器424保留每一TLP的副本,直到由链路的另一端的组件确认,请注意,在实践中,这可以利用堆栈上较高的缓冲(在组装器412中或上方)来实现,它们可以存储在对应的条目中,直到通过数据/消息选择器428选择用于传输到物理层430。一般而言,上文所描述的事务和数据链路层可以根据常规PCIe<sup>TM</sup>协议堆栈电路进行操作,带有如下文进一步描述的某些修改。

[0046] 相反,关于物理层430,也可以发生此层的某些逻辑组件的更多修改,例如,如从PCIe<sup>TM</sup>协议堆栈修改的,用于提供到另一通信协议的物理单元的实际物理部分的连接。可以看出,可以将传入的分组应用于成帧生成器432,该成帧生成器432添加物理层成帧符号,并生成用于分组的成帧,并将它们提供到宽度/位置映射器434,该宽度/位置映射器434在数据路径中移位字节,以生成用于外部传输的所需的对准,调整数据路径宽度(如果需要的话),宽度/位置映射器434又耦合到训练器和跳跃定序器(skip sequencer)436,该训练器和跳跃定序器436可以被用来执行链路训练和跳跃定序。可以看出,成帧生成器432、训练器/定序器436和数据/顺序选择器438全部都可以耦合到物理层发射控制器435,该物理层发射控制器435是LTSSM和相关的逻辑的收发器部分。框436是生成物理层传输(诸如训练集(TS)和跳跃排序集)的逻辑。如此,可以选择成帧的分组,并将它们提供给物理电路,执行编码,串行化,并将对应于经过处理的分组的串行化的信号驱动到物理互连中。在一个实施例中,可以在成帧生成器432中执行不同的通信协议之间的符号差异的映射。

[0047] 可以看出,可以为此物理互连提供多个单个信道或通道。在所示出的实施例中,每一物理信道或通道都可包括其自己的独立的PHY单元发射电路445<sub>0</sub>-445<sub>j</sub>,在一个实施例中,每一个电路445<sub>0</sub>-445<sub>j</sub>都可以是符合MIPI规范的M-PHY单元的一部分。如此处所描述的,与其中发射器和接收器的数量匹配的PCIe<sup>TM</sup>不同,可以存在不同数量的发射器和接收器。如此,可以看出,每一发射电路445都可包括操作以根据8b/10b编码来对符号进行编码的编码器、将经过编码的符号串行化的串行器,以及将信号驱动到物理互连中的驱动器。进一步可以看出,每一通道或信道都可以与逻辑单元440<sub>0</sub>-440<sub>j</sub>相关联,逻辑单元440<sub>0</sub>-440<sub>j</sub>可以是符合M-PHY的MIPI规范的逻辑电路,以如此,通过对应的通道,管理物理通信。

[0048] 注意,这些多个通道可以被配置成以不同速率操作,各实施例可以包括不同数量的这样的通道。此外,还可以在发射与接收方向具有不同数量的通道和通道速度。如此,虽然给定逻辑单元440控制PHY 445的对应的通道的操作,但是,可以理解,物理层发射控制器435可以操作以控制通过物理互连的总体信息传输。注意,在某些情况下,由与每一通道相关联的不同的逻辑执行某种非常基本的功能;对于通道可以被分配给超过单一链路的情况,可以提供多个LTSSM实例;对于已经训练的链路,在控制收发器和接收器端的每一组件中有单一LTSSM。此总体控制可包括功率控制、链路速度控制、链路宽度控制,初始化等等。

[0049] 仍参考图4,通过物理互连接收到的传入信息可以类似地经由物理层430、数据链路层420以及事务层410的接收机制,穿过这些层。在图4所示出的实施例中,每一PHY单元都还可以包括接收电路,即,接收电路455<sub>0</sub>–455<sub>k</sub>,在所示出的实施例中,这些接收电路可以对于物理链路的每一个通道存在。请注意,在此实施例中,接收器电路455和发射器电路445的数量不同。可以看出,此物理电路可包括接收传入的信息的输入缓冲器,使信息解串行化的解串行化器,以及可以操作以解码以8b/10b编码传递的符号的解码器。进一步可以看出,每一通道或信道都可以与逻辑单元450<sub>0</sub>–450<sub>k</sub>相关联,逻辑单元450<sub>0</sub>–450<sub>k</sub>可以是符合给定规范(诸如对于M-PHY的MIPI规范)的逻辑电路,由此经由对应的通道管理物理通信。

[0050] 又可以将经过解码的符号提供到物理层430的逻辑部分,可以看出,该物理层430可以包括弹性缓冲器460,其中弹性缓冲器适应此组件以及链路上的其他组件之间的时钟的差异;请注意,其位置可以在各种实现中移动,例如,在8b/10b解码器下面,或与通道去扭斜缓冲器组合并存储传入的经过解码的符号。又可以将信息提供到宽度/位置映射器462,从那里到通道去扭斜缓冲器464,该通道去扭斜缓冲器跨多个通道并对于多通道情况执行去扭斜,缓冲器464可以在各通道之间处理信号偏斜中的差异,以重新对准字节。又可以将经去扭斜的信息提供到成帧处理器466,该成帧处理器466可以消除传入的信息中存在的成帧。可以看出,物理层接收控制器465可以耦合到弹性缓冲器460、映射器462、去扭斜缓冲器464以及成帧处理器466并控制它们。

[0051] 仍参考图4,可以将恢复的分组提供到接收消息机制478以及错误检测器,序列检查器和链路级重试(LLR)请求器475。此电路可以对传入的分组执行错误校正检查,例如,通过执行CRC校验和操作,执行定序检查,以及请求不正确地接收到的分组的链路级别重试。接收消息机制478和错误检测器/请求器475两者都可以在数据链路接收控制器480的控制之下。

[0052] 仍参考图4,可以将如此在单元475中处理的分组提供到事务层410,更具体而言,提供到流控制器485,该流控制器485对这些分组执行流控制,以将它们提供到分组解释器495。分组解释器495执行对分组的解释,并将它们转发到选择的目的地,例如,给定核或接收器的其他逻辑电路。虽然在图4的实施例中以此高级示出的,但是,可以理解,本发明的范围在这方面不受限制。

[0053] 请注意,PHY 440可以使用由PCIe<sup>TM</sup>支持的相同8b/10b编码来进行传输。8b/10b编码方案提供不同于用于表示字符的数据符号的特殊符号。这些特殊符号可以用于如在PCIe<sup>TM</sup>规范的物理层章节所描述各种链路管理机制。在MIPI M-PHY规范中描述了由M-PHY的额外的特殊符号使用。各实施例可以在PCIe<sup>TM</sup>和MIPI M-PHY符号之间提供映射。

[0054] 现在参考表1,所示是根据本发明的一个实施例的PCIe<sup>TM</sup>符号到M-PHY符号的示例

性映射。如此,此表示出了根据本发明的一个实施例的会聚的协议堆栈的特殊符号的映射。

[0055] 表1

[0056]

| 控制符号 | PCIe 编码 | 会聚的堆栈的映射 | MIPI M-PHY 映射 | 备注 |

|------|---------|----------|---------------|----|

|------|---------|----------|---------------|----|

[0057]

|       |     |     |      |                                                               |

|-------|-----|-----|------|---------------------------------------------------------------|

| K28.5 | COM | COM | 标记 0 |                                                               |

| K28.3 | IDL | IDL | 标记 1 |                                                               |

| K28.6 | 预留  | SDP | 标记   | 注意: 这里映射 SDP, 因为原始 PCIe 编码 映 射 到 M-PHY 预留的编码。                 |

| K23.7 | PAD | SKP | 标记 3 | 注意: 将 SKP 映 射 到 中 性 差 异 K23.7 符 号, 因 为 它 不 推 进 扰 频 器 / 解 扰 器。 |

| K27.7 | STP | STP | 标记 4 |                                                               |

| K29.7 | END | END | 标记 5 |                                                               |

| K30.7 | EDB | EDB | 标记 6 |                                                               |

[0058]

|       |     |     |     |                                                                                                                                                                                                                                                |

|-------|-----|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| K28.1 | FTS | PAD | 填充值 | <p>注意：这<br/>里映射 PAD，<br/>因为 SKP 采<br/>取了其编码。<br/>不需要 FTS，<br/>因为可以使<br/>用 M-PHY<br/>SYNC 机制。<br/>M-PHY<br/>SYNC 机制是<br/>较好的选项，<br/>因为定义的<br/>SYNC 符号具<br/>有较高边缘<br/>密度。</p> <p>RMMI 规<br/>范 要 求<br/>M-PHY 在<br/>TX_DORDY<br/>低时插入填<br/>充值。</p> |

|-------|-----|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

[0059]

|       |     |    |    |                                                  |

|-------|-----|----|----|--------------------------------------------------|

| K28.0 | SKP | 预留 | 预留 |                                                  |

| K28.2 | SDP | 预留 | 预留 |                                                  |

| K28.7 | EIE | 预留 | 预留 | 注意：不要求 EIE，因为 M-PHY 噪声抑制电路正在检测 DIF-Z 到 DIF-N 过渡。 |

| 其他    | 预留  | 预留 | 预留 |                                                  |

[0060] 8b/10b解码规则与对于PCIe<sup>TM</sup>规范定义的相同。对于8b/10b规则的唯一例外是当检测到猝发的末尾时,这是违犯8b/10b规则的特定的序列。根据各实施例,物理层430可以向数据链路层420提供在猝发的末尾过程中遇到的任何错误的通知。

[0061] 在一个实施例中,符号向通道的成帧和应用可以如在PCIe<sup>TM</sup>规范中那样定义,而数据扰频可以与如在PCIe<sup>TM</sup>规范中定义相同。然而,注意,在根据MIPI规范的通信的PREPARE阶段发射的数据符号不被扰频。

[0062] 对于链路初始化和训练,链路管理器可以提供链路的配置和初始化,如上文所讨论的,链路可包括通道的一个或多个信道,对正常的数据传输的支持,当从链路错误恢复时对状态转换的支持,以及从低功率状态端口重新启动。

[0063] 为实现这样的操作,下列物理和链路相关的特征可以是先验地已知的,例如,在初始化之前:PHY参数(例如,包括初始链路速度和支持的速度;以及初始链路宽度和支持的链路宽度)。

[0064] 在一个实施例中,训练可以包括各种操作。这样的操作可以包括以配置的链路速度和宽度,初始化链路,每个通道的比特锁、每个通道的符号锁、通道极性以及对于多通道链路的通道-通道去扭斜。如此,训练可以发现通道极性并相应地执行调整。然而,注意,根据本发明的一个实施例的链路训练可以不包括链路数据速率和宽度协商、链路速度和宽度退化。相反,如上文所描述的,在链路的初始化时,两个实体先验地知道初始链路宽度和速度,如此,可以避免与协商相关联的时间和计算成本。

[0065] PCIe<sup>TM</sup>排序的组可以与下列修改一起使用:TS1和TS2排序的组被用来促进IP再次使用,但是,忽略训练排序的组的许多字段。此外,还不使用快速训练序列。可以保留电气闲置有序集(EIOS),以促进IP再次使用,如跳跃OS那样,但是,跳跃OS的频率可以不同于根据PCIe<sup>TM</sup>规范。还应注意,数据流排序的组和符号可以与根据PCIe<sup>TM</sup>规范相同。

[0066] 传递下列事件,以促进链路训练和管理:(1)可以被用来表明在链路的远端存在有效PHY的存在;以及(2)配置准备好,其被触发以指出PHY参数配置完成,PHY已准备好以配置的简档操作。在一个实施例中,可以通过根据本发明的一个实施例的合并的边带信号,传递

这样的信息。

[0067] 为了控制电气闲置情况,PHY具有猝发的末尾序列,该序列用于指出发射器正在进入电气闲置状态。在一个实施例中,边带信道可以被用来发信号从电气闲置退出。注意,此指示可以作为PHY噪声抑制电路破坏机制的补充。符号的OPENS序列可以作为EIOS发射,以指出进入电气闲置状态。

[0068] 在某些实施例中,未定义快速训练序列(FTS)。相反,PHY可以使用特定的物理层序列,以便从停止/睡眠状态退出到猝发状态,猝发状态可以被用来寻址比特锁,符号锁和通道到通道去扭斜。为稳健,可以定义少量的FTS,作为符号的序列。数据流有序集的启动可以根据PCIe<sup>TM</sup>规范,如链路错误恢复那样。

[0069] 至于链路数据速率,在各实施例中,链路初始化的初始数据速率可以是预定的数据速率。通过经过恢复状态,可以发生从此初始链路速度的数据速率变化。各实施例可以支持非对称的链路数据速率,其中,数据速率被允许在相反的方向不同。

[0070] 在一个实施例中,支持的链路宽度可以根据PCIe<sup>TM</sup>规范的那些。进一步地,如上文所描述的,各实施例可以不支持用于协商链路宽度的协议,因为链路宽度是预定的,结果,可以简化链路训练。当然,各实施例可以提供对于相反的方向的非对称的链路宽度的支持。同时,要为链路的每一方向配置的初始链路宽度和初始数据速率可以是在训练启动之前先验地已知的。

[0071] 相对于PHY单元的物理端口,xN端口的形成xN链路以及x1链路的能力(其中,N可以是32,16,12,8,4,2,以及1)不是必需的,xN端口的形成N和1之间的任何链路宽度的能力是可选的。此行为的一个示例包括x16端口,该x16端口只能配置为只有一个链路,但是,链路的宽度可以被配置成x12、x8、x4、x2,以及x16和x1的必需的宽度。如此,使用根据本发明的一个实施例的协议堆栈来寻求实现设备的设计人员可以允许两个不同的组件满足上面要求的方式连接这些组件之间的端口。如果组件之间的端口以不符合如组件的端口描述/数据表所定义的预期使用的方式连接,则行为是未定义的。

[0072] 另外,将端口拆分为两个或更多链路的能力不会被阻止。如果这样的支持适用于给定设计,则端口可以被配置成在训练过程中支持特定的宽度。此行为的一个示例将是能够配置两个x8链路、四个x4链路,或16个x1链路的x16端口。

[0073] 当使用8b/10b编码时,无歧义的通道-通道去扭斜机制,如在PCIe规范中那样,是在训练序列过程中接收到的排序集的COM符号,或SKP排序集,因为在配置的链路的所有通道上同时发射排序集。在HS-BURST(HS-猝发)的同步序列过程中发射的MK0符号可以用于通道-通道去扭斜。

[0074] 如上文参考图4简要地描述的,链路训练和状态管理器可以被配置成执行各种操作,包括使PCIe<sup>TM</sup>协议堆栈的上层适应不同协议较低层PHY单元。此外,此链路管理器可以配置和管理单一或多个通道,并可以包括对于对称的链路带宽、状态机与PCIe<sup>TM</sup>事务和数据链路层、链路训练,可选对称的链路停止状态的兼容性,以及对用于稳健通信的边带信号的控制。相应地,各实施例用于实现具有有限的修改的PCIe<sup>TM</sup>事务和数据链路层,以考虑不同链路速度和非对称的链路。此外,通过使用根据本发明的一个实施例的链路管理器,可以实现对于多通道、非对称的链路配置、边带合并和动态带宽可缩放性的支持,同时进一步实现不同的通信协议的在各层之间的桥接。

[0075] 现在参考图5,所示是根据本发明的一个实施例的链路训练状态机的状态图500,该状态机可以是链路管理器的一部分。如图5所示,链路训练可以在检测状态510开始。此状态发生在通电复位上,并适用于上游和下游端口。在复位完成之后,所有配置的通道都可以过渡到给定状态,即,HIBERN8状态,此时,链路的每一端都可以例如通过PRESENCE信号使用边带信道发信号。注意,在此检测状态下,可以在所有通道上驱动高阻抗信号,即,DIF-Z信号。

[0076] 如此,当将PRESENCE事件发信号并接收到PRESENCE事件时,控制从检测状态510进入配置状态520,在所有配置的通道上驱动此高阻抗。在配置状态520,可以配置PHY参数,并且在链路的每一端的所有配置的通道上完成时,可以指出配置准备好信号(CFG-RDY),例如,使用边带互连,同时在所有通道上都维持高阻抗。

[0077] 如此,在通过边带互连发送并接收此配置准备好指示时,控制进入停止状态530。即,在此L0.STALL状态,PHY过渡到STALL状态,并继续,以在所有配置的通道上驱动高阻抗。可以看出,取决于数据是否可用于传输或接收,控制可以转到活动状态L1(状态530)、低功率状态(L1状态540)、较深的低功率状态(L1.OFF(L1.关闭)状态545),或回到配置状态520。

[0078] 如此,在STALL状态下,可以在全部配置的通道上传递负的驱动信号DIF-N。然后,当由启动器指示时,BURST序列可以开始。相应地,在MARKER 0(MK0)符号的传输之后,控制进入活动状态530。

[0079] 在一个实施例中,接收器可以检测所有配置的通道上的从STALL状态退出,并根据,例如,MIPI规范,执行比特锁和符号锁。在带有多通道链路的各实施例中,此MK0符号可以被用来建立通道-通道去扭斜。

[0080] 相反,当被指示到低功率状态(即,L1状态540)时,所有配置的通道可以过渡到SLEEP(睡眠)状态。当被指示到较深的功率状态(即,L1.OFF(L1.关闭)状态545)时,所有配置的通道可以过渡到HIBERN8状态。最后,当被指示回到配置状态时,类似地,所有配置的通道都过渡到HIBERN8状态。

[0081] 仍参考图5,对于活动数据传输,如此,控制转到活动状态550。具体而言,这是链路和事务层开始使用数据链路层分组(DLLP)和TLP来交换信息的状态。如此,有可以发生效负载传输,在这样的传输结束时,可以传递猝发的TAIL末尾符号。

[0082] 可以看出,控制可以从该活动状态传递回STALL(停止)状态530,到恢复状态560,例如,响应于接收器错误或当以别的方式指示时,或到较深的低功率(例如,L2)状态570。

[0083] 为返回到停止状态,发射器可以发送EIOS序列,接下来是全部配置的通道上的猝发的末尾指示。

[0084] 如果发生错误或以别的方式指示的,则控制也可以转到恢复状态560。这里,到恢复的过渡导致两个方向上的全部配置的通道进入STALL(停止)状态。为实现此,可以在边带互连上发送GO TO STALL(通向停止)信号,此信号的发射器可以等待响应。当发送和接收此停止信号时,如由边带互连上的接收到的GO TO STALL指示所指示的,控制回到STALL状态530。注意,此恢复状态因此使用边带确定协议,以协调同时进入STALL状态。

[0085] 对于低功率状态L1和L1.OFF,操作根据状态540和545。具体而言,控制从STALL状态进入L1较低的功率状态540,以便PHY可以被置于SLEEP(睡眠)状态。在此状态下,可以在全部配置的通道上驱动负的驱动信号,即,DIF-N信号。当被指示退出状态时,控制回到

STALL状态530,例如,通过边带互连上的PRESENCE信号的信令。

[0086] 还可以看出,当满足全部L1.OFF条件时,可以进入较深的低状态L1.OFF。在一个实施例中,这些条件可以包括完全地功率选通或关闭到PHY单元的电能。在此较深的低功率状态下,可以将PHY置于HIBERN8状态,以及在全部配置的通道上驱动的高阻抗信号。为退出此状态,通过全部配置的通道上的DIF-N的驱动,控制回到STALL状态。

[0087] 在图5中进一步可以看出,可以存在附加状态,即,当电源准备关闭时可以从活动状态进入的更深的低功率状态(L2)570。在一个实施例中,此状态可以与PCIe规范的状态相同。

[0088] 现在参考表2,所示是根据本发明的一个实施例的符合PCIe<sup>TM</sup>规范的LTSSM状态和对应的M-PHY状态之间的映射。

[0089] 表2

[0090]

| LTSSM 状态 | M-PHY 状态                        | 细节                                            |

|----------|---------------------------------|-----------------------------------------------|

| 检测, 轮询   | SAVE (保存)                       | 通过 SAVE 子状态的状态转换                              |

| 配置       | BURST (猝发)                      | BURST (PREP, SYNC) 子状态                        |

| 恢复       | BURST/SLEEP/STALL<br>(猝发/睡眠/停止) | 可以处于 BURST 状态, 但是, 将通过 SLEEP/STALL, 过渡到 BURST |

| L0       | BURST (猝发) (有效负载)               | BURST 模式和交换事务                                 |

| LOs      | STALL (停止)                      | STALL 状态                                      |

| L1       | SLEEP (睡眠)                      | SLEEP 状态                                      |

| L1.OFF   | HIBERN8                         | HIBERN8                                       |

| L2       | UNPOWERED(不通电)                  | UNPOWERED 状态                                  |

| 禁用       | DISABLED (禁用)                   | DISABLED 状态                                   |

| 回送       | 无动作                             | 链路速度可能会在进入时从“配置”改变到回                          |

[0091]

|     |                     |                  |

|-----|---------------------|------------------|

|     |                     | 送                |

| 热复位 | INLINE RESET (联机复位) | IN-LINE RESET 状态 |

[0092] 如上文参考图2所描述的,各实施例提供了合并的边带机制,该机制可以用于链路管理、以及可选带内支持。如此,通过使用边带电路和互连,可以独立于主要互连的物理层的较高速度(并且较高的功率消耗)电路,进行链路管理和控制。进一步地,如此,当与主要互连相关联的PHY单元的某些部分断电时,可以使用此边带信道,实现降低的功率消耗。此外,在主要互连的训练之前,也可以使用此合并的边带机制,当在主要互连上存在故障时,也可以使用该机制。

[0093] 更进一步,通过此合并的边带机制,可以存在单一互连,例如,在每一方向的一对有差异的线路,降低了针脚数,并添加新能力。各实施例还可以实现更快的并且更加稳健的时钟/功率选通,并可以消除诸如使用此链路的PCIe边带机制之类的常规协议中的歧义。

[0094] 虽然本发明的范围在这方面不受限制,但是,在不同的实施例中,边带互连(例如,图2的边带互连270)可被实现为单一线路双向边带信号,双线路双方向单向的信号组,低速度带内信令机制,诸如在低功率脉宽调制(PWM)模式下使用M-PHY可用的,或作为带内高速度信令机制,诸如物理层排序的组或DLLP。

[0095] 作为示例,而不作出限制,可以支持各种物理层方法。第一种方法可以是当使用边带互连时提供最低针脚数的单一线路双向边带信号。在某些实施例中,此信号可以在现有的边带上多路复用,例如,PERST#、WAKE#或CLKREQ信号。第二种方法可以是双线路双方向单向的信号组,与单线方法相比,可以更简单,在某种程度上更有效率,但是,以额外的针脚为代价。这样的实现可以在现有的边带上多路复用,例如,用于主机设备的PERST#,以及用于设备主机的CLKREQ#(在此示例中,保持现有的信号方向性,简化双模态实现)。第三种方法可以是低速带内信令机制,诸如M-PHY LS PWM模式,相对于边带机制,它降低了针脚数,且仍可以支持类似低功率级别。由于此操作模式与高速操作互相排斥,因此,它可以与诸如物理层排序的组或DLLP之类的高速带内机制组合。尽管此方法不是低功率,但是,它最大化与现有的高速I/O的共同性。当与低速度带内信令相结合时,此方法可以提供好的低功率解决方案。

[0096] 为在给定系统中实现这些配置中的一个或多个,可以提供语义层,该语义层可以被用来确定要通过物理层交换的信息的含义,以及策略层,该策略层可以被用来理解设备/平台级别动作/反应。在一个实施例中,在SB PHY单元中可以存在这些层。

[0097] 通过提供分层的方法,各实施例允许不同的物理层实现,这些实现可以包括双边带能力(在某些实现中,由于简单性和/或低功率操作,可以是首选的)和带内,对于其他实现,带内可以是首选的,例如,避免对额外的针脚数的需求。

[0098] 在一个实施例中,若干个边带信号可以,例如,通过语义层,被配置为单一分组,用于通过合并的边带机制(或带内机制)进行通信。在一个实施例中,下面的表3示出了在一个实施例中可以存在的各种信号。在所示出的表中,通过箭头示出了信号的逻辑方向,其中,

向上箭头被定义为到主机(例如,根综合体)的方向,向下箭头被定义为到设备的方向(例如,诸如无线电解决方案之类的外围设备)。

- [0099] 表3

- [0100] 设备存在↑

- [0101] 功率良好↓

- [0102] 断电↓

- [0103] 基准时钟良好↓

- [0104] 基本复位↓

- [0105] 配置准备好↑↓

- [0106] 准备好训练↑↓

- [0107] 开始训练↑↓

- [0108] L1pg请求↑↓

- [0109] L1pg拒绝↑↓

- [0110] L1pg准许↑↓

- [0111] OBFF CPU活动↓

- [0112] OBFF DMA↓

- [0113] OBFF空闲↓

- [0114] 唤醒↑

- [0115] 确认握手接收↑↓

[0116] 现在参考图6,所示是根据本发明的一个实施例的边带机制的各种状态的流程图。如图6所示,这些各种状态可以对于根综合体(例如,主机控制的操作)。状态图600可以通过主机提供对各种状态的控制。可以看出,操作在预引导状态610开始,其中,可以传递存在信号。注意,此存在信号可以如上文对于链路管理操作所描述的。然后,控制进入引导状态620,其中,可以传递各种信号,即,功率良好的信号、复位信号、基准时钟状态信号和准备好训练信号。注意,可以通过单一分组,来传递这些信号中的全部,其中,这些信号中的每一个都可以对应于分组的指示符或字段(例如,分组的一个比特指示符)。

[0117] 仍参考图6,接下来,控制进入活动状态630,此时,系统可以处于活动状态(例如,S0),对应的设备(例如,下游设备可以是活动设备状态(例如,D0),且链路可以处于活动状态、停止或低功率状态(例如,L0,L0s,或L1))。可以看出,在此状态下,可以传递各种信号,包括OBFF信号、时钟请求信号、基准时钟状态、请求L0信号和准备好训练信号。

[0118] 接下来,控制可以转到低功率状态640,例如,在执行上面的信令之后。可以看出,在此低功率状态640,系统可以处于活动状态,而设备可以处于相对低等待时间低功率状态(例如,D3热)。另外,链路可以处于给定低功率状态(例如,L2或L3)。如在这些状态看出,通过合并的边带分组传递的信号可以包括唤醒信号、复位信号以及功率良好的信号。

[0119] 随着系统进入较深的低功率状态,可以进入第二低功率状态650,例如,当系统处于S0状态且设备处于D3冷状态时,链路类似地处于L2或L3状态。可以看出,可以传递相同唤醒、复位和功率良好信号。在图6中还可以看出,在较深的功率状态660(例如,系统低功率状态,S3)和设备低功率状态(例如,D3冷),以及相同链路低功率状态L2和L3,可以发生相同信号。虽然是利用传递的特定边带信息组所示出的,但是,可以理解,本发明的范围在这方面

不受限制。

[0120] 如此,各实施例给分层结构提供可以平衡简单性和低等待时间-灵活性的可扩展性。如此,现有的边带信号和额外的边带信号可以替换为较小数量的信号,并允许边带机制的未来扩展,无需添加更多针脚。

[0121] 现在参考图7,所示是根据本发明的一个实施例的方法的流程图。如图7所示,方法700可以被用来通过会聚的协议堆栈来传递数据,该会聚的协议堆栈包括一个通信协议的上层,以及不同的通信协议的较低的,例如,物理层。在所示出的示例中,假设如上文所描述的会聚的协议堆栈,即,带有PCIe<sup>TM</sup>协议的上事务和数据链路层以及不同规范,例如,MIPI规范的物理层。当然,还可以存在用于将这两种通信协议会聚到单一协议堆栈中的额外的逻辑,诸如上文参考图4所讨论的逻辑和电路。

[0122] 如图7所示,方法700可以通过在第一通信协议的协议堆栈中接收第一事务开始(框710)。例如,诸如核、其他执行引擎等根综合体的各种逻辑寻求向另一设备发送信息。相应地,此信息可以传递给事务层。可以看出,控制进入框720,在那里,可以处理事务,并将事务提供给第二通信协议的PHY的逻辑部分。此处理可以包括上文参考图4的流程所讨论的各种操作,其中,可以发生接收数据、执行流控制、链路操作、分组化操作等等的不同的操作。另外,还可以发生向PHY提供数据链路层分组的各种操作。接下来,控制进入框730,在那里,在PHY的逻辑部分中,可以将此第一事务转换为第二格式事务。例如,可以执行符号的任何转换(如果需要的话)。另外,还可以发生各种转换操作,如此,使事务变为用于在链路上传输的格式。相应地,控制可以转到框740,在那里,可以通过链路,将此第二格式化的事务从PHY传递到设备。作为示例,在线编码、串行化等等之后,第二格式事务可以是串行化的数据。虽然在图7的实施例中以此高级别示出的,但是,可以理解,本发明的范围在这方面不受限制。

[0123] 现在参考图8,所示是存在于根据本发明的一个实施例的计算机系统中的组件的框图。如图8所示,系统800可包括许多不同的组件。这些组件可被实现为IC,其一些部分,单独的电子器件,或适用于诸如计算机系统的主板或插入式卡之类的电路板的其他模块,或作为以别的方式包括在计算机系统的机架内的组件。还应注意,图8的框图旨在示出计算机系统的许多组件的高级视图。然而,可以理解,在某些实现中,可以存在额外的组件,此外,在其他实现中,还可以有所示出的组件的不同的布局。

[0124] 如图8所示,处理器810可以是低功率多核处理器插槽,诸如超低电压处理器,可以充当主处理单元,以及用于与系统的各种组件进行通信的中央中枢。这样的处理器可被实现为SoC。在一个实施例中,处理器810可以是基于Intel<sup>®</sup>架构Core<sup>TM</sup>的处理器,诸如i3、i5、i7或加利福尼亚州圣克拉拉的英特尔公司所提供的另一这样的处理器。然而,可以理解,在其他实施例中,可以存在其他低功率处理器,诸如加利福尼亚州桑尼威尔的超微半导体有限公司(AMD)所提供的,来自ARM控股有限公司的基于ARM的设计,或来自加利福尼亚州桑尼威尔的MIPS技术公司的基于MIPS的设计,以及它们的被许可方或采用者,诸如Apple A5处理器。

[0125] 处理器810可以与系统存储器815进行通信,该系统存储器815,在一个实施例中,可以通过多个存储器设备来实现,以提供一定量的系统存储器。作为示例,存储器可以符合电子设备工程联合协会(JEDEC)低功率基于双倍数据速率(LPDDR)的设计,诸如符合JEDEC

JESD 209-2E的当前LPDDR2标准(2009年4月发布),或将提供对LPDDR2的扩展以增大带宽的下一代LPDDR标准,被称为LPDDR3。作为示例,可以存在2/4/8千兆字节(GB)的系统存储器,并通过一个或多个存储器互连耦合到处理器810。在各实现中,单个存储器设备可以是不同的封装类型,诸如单管芯封装(SDP)、双管芯封装(DDP)或四管芯封装(QDP)。在某些实施例中,这些设备可以直接焊接到主板中,以提供较低轮廓的解决方案,而在其他实施例中,设备可以被配置为一个或多个存储器模块,这些存储器模块又可以通过给定连接器耦合到主板。

[0126] 为提供诸如数据、应用、一个或多个操作系统等信息的持久性存储,大容量存储器820还可以耦合到处理器810。在各实施例中,为实现较薄的和较轻的系统设计以及改善系统响应性,此大容量存储器可以通过SSD来实现。然而,在其他实施例中,大容量存储器可以主要使用带有较小量的SSD存储器的硬盘驱动器(HDD)来实现,以充当SSD缓存,以在断电情况下实现上下文状态及其他这样的信息的非易失性存储,以便在系统活动的重新启动时可以进行快速的通电。也如图8所示出的,闪存设备822可以例如通过串行外围接口(SPI)耦合到处理器810。此闪存设备可以提供系统软件——包括基本输入/输出软件(BIOS)以及系统的其他固件——的非易失性存储。

[0127] 在系统800内可以存在各种输入/输出(I/O)设备。具体而言,在图8的实施例中示出了显示器824,该显示器824可以是在机架的盖子部分内配置的高清晰度LCD或LED面板。此显示器面板还可以提供触摸屏825,例如在显示器面板上方从外部适应,以便通过用户与此触摸屏的交互,用户输入可以被提供到系统,以实现所需操作,例如,关于信息显示的,访问信息等等。在一个实施例中,显示器824可以通过显示器互连耦合到处理器810,该显示器互连可被实现为高性能图形互连。触摸屏825可以通过另一互连(在一个实施例中,可以是I<sup>2</sup>C互连)耦合到处理器810。如在图8中进一步示出的,除触摸屏825之外,通过触摸的用户输入也可以通过触摸板830进行,触摸板830可以在机架内配置,还可以与触摸屏825耦合到相同I<sup>2</sup>C互连。

[0128] 为感知计算及其他目的,在系统内可以存在各种传感器,它们可以以不同的方式耦合到处理器810。某些惯性和环境传感器可以通过传感器中枢840,例如,经由I<sup>2</sup>C互连,耦合到处理器810。在图8所示出的实施例中,这些传感器可以包括加速度计841、环境光传感器(ALS)842、罗盘843和陀螺仪844。在一个实施例中,其他环境传感器可以包括一个或多个热传感器846,这些热传感器846可以通过系统管理总线(SMBus)总线耦合到处理器810。还应理解,根据本发明的一个实施例,传感器中的一个或多个可以通过LPS链路耦合到处理器810。

[0129] 也参见图8,各种外围设备可以通过低管脚数(LPC)互连耦合到处理器810。在所示出的实施例中,各种组件可以通过嵌入式控制器835耦合。这样的组件可包括键盘836(例如,通过PS2接口耦合)、风扇837,以及热传感器839。在某些实施例中,触摸板830还可以通过PS2接口耦合到EC 835。另外,安全性处理器,诸如可信平台模块(TPM)838,诸如符合可信计算组(TCG)TPM规范版本1.2(2003年10月2日),还可以通过此LPC互连,耦合到处理器810。

[0130] 系统800可以以各种方式,包括以无线方式,与外部设备进行通信。在图8所示出的实施例中,存在各种无线模块,每一个无线模块都可以对应于为特定无线通信协议配置的无线电。用于在近距离(诸如近场)内进行无线通信的一种方式可以通过近场通信(NFC)单

元845,在一个实施例中,该单元845可以通过SMBus与处理器810进行通信。请注意,通过此NFC单元845,彼此紧邻的设备可以进行通信。例如,用户可以通过使两个设备靠近,并允许传输诸如标识信息、支付信息之类的信息,诸如图像数据之类的数据等等,允许系统800与另一(例如,)便携式设备(诸如用户的智能电话)进行通信。无线电功率传输还可以使用NFC系统来执行。

[0131] 在图8中进一步可以看出,额外的无线单元可包括其他近距离无线引擎,包括WLAN单元850和蓝牙单元852。通过使用WLAN单元850,可以实现符合给定电气与电子工程师学会(IEEE)802.11标准的Wi-Fi<sup>TM</sup>通信,而通过蓝牙单元852,可以进行通过蓝牙协议的近距离通信。这些单元可以通过,例如,USB链路或通用异步收发器(UART)链路,与处理器810进行通信。或者,这些单元可以通过互连,通过低功率互连,诸如如此处所描述的会聚的PCIe/MIPI互连,或另一这样的协议,诸如串行数据输入/输出(SDIO)标准,耦合到处理器810。当然,可以在一个或多个插入式卡上配置的这些外围设备之间的实际物理连接,可以通过适用于主板的NGFF连接器。

[0132] 另外,例如,符合蜂窝式或其他无线广域协议的无线广域通信可以通过WWAN单元856进行,该WWAN单元856又可以耦合到用户标识模块(SIM)857。另外,为允许接收并使用位置信息,还可以存在GPS模块855。请注意,在图8所示出的实施例中,WWAN单元856和诸如照相机模块854之类的集成的捕捉设备可以通过给定USB协议,诸如USB 2.0或3.0链路,或UART或I<sup>2</sup>C协议,进行通信。再次,这些单元的实际物理连接可以通过NGFF插入式卡与在主板上配置的NGFF连接器的自适应。

[0133] 为提供音频输入和输出,可以通过数字信号处理器(DSP)860来实现音频处理器,DSP 860可以通过高清晰度音频(HDA)链路来耦合到处理器810。类似地,DSP 860可以与集成的编码器/解码器(CODEC)和放大器862进行通信,放大器862又可以耦合到可以在机架内实现的输出扬声器863。类似地,放大器和CODEC 862可以耦合,以从麦克风865接收音频输入,在一个实施例中,麦克风865可以通过双阵列麦克风来实现,以提供高质量音频输入,以允许对系统内的各种操作的语音激活的控制。还应注意,可以从放大器/CODEC 862向耳机插孔864提供音频输出。

[0134] 如此,各实施例可以用于许多不同的环境中。现在参考图9,所示出的是可以与各实施例一起使用的示例系统900的框图。可以看出,系统900可以是智能电话或其他无线通信装置。如图9的框图所示,系统900可以包括基带处理器910,该基带处理器910可以是多核处理器,该多核处理器可以处理基带处理任务以及进行应用处理。如此,基带处理器910可以执行涉及通信的各种信号处理,以及执行设备的计算操作。基带处理器910又可以耦合到用户界面/显示器920,在某些实施例中,用户界面/显示器920通过触摸屏显示器来实现。另外,基带处理器910还可以耦合到存储器系统,在图9的实施例中,存储器系统包括非易失性存储器,即,闪存930和系统存储器,即,动态随机存取存储器(DRAM)935。进一步可以看出,基带处理器910还可以耦合到诸如图像捕捉设备之类的捕捉设备940,该捕捉设备940可以记录视频和/或静止图像。

[0135] 为允许发射和接收通信,在基带处理器910和天线980之间可以耦合各种电路。具体而言,可以存在射频(RF)收发器970和无线局域网(WLAN)收发器975。一般而言,RF收发器970可以被用来根据给定无线通信协议,诸如3G或4G无线通信协议,诸如根据码分多址

(CDMA)、全球移动通信系统通信 (GSM)、长期演进 (LTE) 或其他协议,接收和发射无线数据和呼叫。还可以提供其他无线通信,诸如无线电信号,例如,AM/FM,或全球定位卫星 (GPS) 信号的接收或传输。另外,通过WLAN收发器975,也可以实现本地无线信号,诸如符合Bluetooth™ 标准或诸如IEEE802.11a/b/g/n之类的IEEE 802.11标准。请注意,基带处理器910和收发器970和975中的一个或两者之间的链路可以通过低功率会聚的互连,该低功率会聚的互连组合并映射PCIe™互连和诸如MIPI互连之类的低功率互连的功能。虽然在图9的实施例中以此高级别示出的,但是,可以理解,本发明的范围在这方面不受限制。

[0136] 各实施例可以用于许多不同类型的系统中。例如,在一个实施例中,通信设备可以被配置为执行此处所描述的各种方法和技术。当然,本发明的范围不仅限于通信设备,相反,其他实施例可以涉及其他类型的用于处理指令的设备,包括指令的一个或多个机器可读的介质,所述指令,响应于在计算设备上执行,导致设备执行此处所描述的方法和技术中的一个或多个。

[0137] 各实施例可以以代码来实现,并可以存储在其上存储了指令的非瞬时的存储介质上,指令可以被用来对系统进行编程以执行指令。存储介质可以包括,但不仅限于,任何类型的磁盘,包括软盘、光盘、固态驱动器 (SSD)、光盘只读存储器 (CD-ROM)、光盘可重写 (CD-RW),以及磁光盘、诸如只读存储器 (ROM) 之类的半导体器件、诸如动态随机存取存储器 (DRAM)、和静态随机存取存储器 (SRAM) 之类的随机访问存储器 (RAM)、可擦除编程只读存储器 (EPROM)、闪存、电可擦除编程只读存储器 (EEPROM)、磁卡或光卡,或适于存储电子指令的任何其他类型的介质。

[0138] 尽管是参考数量有限的实施例来描述本发明的,但是,那些精通本技术的人将从中理解很多修改和变体。所附权利要求书涵盖所有这样的修改和变体都将在本发明的真正的精神和范围内。

100

图1

200

图2

300

图3

图4

图5

600

图6

700

图7

图8

图9