(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7604299号**

**(P7604299)**

(45)発行日 令和6年12月23日(2024.12.23)

(24)登録日 令和6年12月13日(2024.12.13)

(51)国際特許分類

|        |                |        |      |

|--------|----------------|--------|------|

| H 02 J | 3/24 (2006.01) | H 02 J | 3/24 |

| H 02 J | 3/38 (2006.01) | H 02 J | 3/38 |

F I

|       |

|-------|

| 1 1 0 |

|-------|

請求項の数 6 (全13頁)

(21)出願番号 特願2021-50893(P2021-50893)

(22)出願日 令和3年3月25日(2021.3.25)

(65)公開番号 特開2022-148986(P2022-148986)

A)

(43)公開日 令和4年10月6日(2022.10.6)

審査請求日 令和5年12月25日(2023.12.25)

|          |                                                    |

|----------|----------------------------------------------------|

| (73)特許権者 | 000003687<br>東京電力ホールディングス株式会社<br>東京都千代田区内幸町一丁目1番3号 |

| (73)特許権者 | 000006105<br>株式会社明電舎<br>東京都品川区大崎2丁目1番1号            |

| (74)代理人  | 100086232<br>弁理士 小林 博通                             |

| (74)代理人  | 100092613<br>弁理士 富岡 潔                              |

| (74)代理人  | 100104938<br>弁理士 鵜澤 英久                             |

| (74)代理人  | 100210240<br>弁理士 太田 友幸                             |

| (72)発明者  | 鈴木 健一                                              |

最終頁に続く

(54)【発明の名称】 系統連系電力変換装置および系統連系電力変換装置の制御方法

**(57)【特許請求の範囲】****【請求項1】**

同期発電機を模擬した仮想同期発電機制御が行われ、直流電源の直流電力を交流電力に変換するDC/A/C変換器を有し、前記DC/A/C変換器の出力がLCフィルタを介して電力系統と連系される系統連系電力変換装置であって、

出力電流検出値と系統電圧検出値の実効値と交流電圧指令値とに基づいて、内部誘起電圧を算出する内部誘起電圧算出部と、

前記系統電圧検出値に基づいて、系統周波数とPLL角周波数を出力するPLLと、

前記系統周波数が周波数上側閾値よりも大きい場合、または、前記系統周波数が周波数下側閾値よりも小さい場合、または、前記系統電圧検出値が電圧上側閾値よりも大きい場合、または、前記系統電圧検出値が電圧下側閾値よりも小さい場合、系統擾乱が発生していると判定して系統擾乱判定信号を出力する系統擾乱判定部と、

前記内部誘起電圧と前記出力電流検出値と前記DC/A/C変換器の出力指令値である機械入力指令値とに基づいて、前記仮想同期発電機制御を行うための同期発電機を模擬したVSG角周波数を算出し、前記DC/A/C変換器停止状態かつ前記系統擾乱判定信号が出力されていない場合は前記PLL角周波数に基づいた位相を出力し、前記DC/A/C変換器運転状態もしくは前記系統擾乱判定信号が出力されている場合は前記VSG角周波数に基づいた位相を出力する仮想同期発電機モデルと、

前記内部誘起電圧と前記系統電圧検出値と前記出力電流検出値とに基づいて、同期発電機の内部インピーダンスによる電圧降下を模擬し、系統電圧指令値を算出する仮想同期イ

ンピーダンス補償部と、

前記系統電圧検出値を前記系統電圧指令値に制御する電圧制御を行い、P W M制御指令値を出力するP C S出力電圧制御部と、

前記P W M制御指令値と前記位相に基づいて、前記D C / A C変換器のゲート信号を生成し、前記D C / A C変換器を使用しない場合は前記D C / A C変換器の前記ゲート信号をブロックし、前記系統擾乱判定信号が出力されると前記ゲート信号を前記D C / A C変換器に出力開始するP W M制御部と、

を備えたことを特徴とする系統連系電力変換装置。

#### 【請求項2】

前記仮想同期発電機モデルは、

10

前記機械入力指令値を機械入力トルクに換算する機械入力トルク算出部と、

前記内部誘起電圧と前記出力電流検出値から電気出力トルクを算出する電気出力トルク算出部と、

前記機械入力トルクから前記電気出力トルクを減算する第1減算器と、

スイッチの出力の前回値に基づいて制動巻線に発生するトルクを模擬した制動トルクを出力するダンピングブロックと、

前記第1減算器の出力から前記制動トルクを減算する第2減算器と、

前記第2減算器の出力を慣性定数で除算する慣性ブロックと、

前記慣性ブロックの出力に前記スイッチの出力の前回値を加算して前記V S G角周波数を出力する第1加算器と、

20

前記D C / A C変換器停止状態かつ前記系統擾乱判定信号が出力されていない場合は前記P L L角周波数を出力し、前記D C / A C変換器運転状態もしくは前記系統擾乱判定信号が出力されている場合は前記V S G角周波数を出力する前記スイッチと、

前記スイッチの出力に基本周波数を加算して角周波数として出力する第2加算器と、

前記第2加算器の出力を積分して前記位相を出力する第1積分器と、

を備えたことを特徴とする請求項1記載の系統連系電力変換装置。

#### 【請求項3】

前記系統擾乱判定部は、前記系統周波数の上昇時の変化率が上昇時の閾値よりも大きい場合、または、前記系統周波数の低下時の変化率が低下時の閾値よりも大きい場合、系統擾乱が発生していると判定して前記系統擾乱判定信号を出力することを特徴とする請求項1または2記載の系統連系電力変換装置。

30

#### 【請求項4】

前記仮想同期発電機モデルは、

前記系統周波数または前記系統電圧検出値の変動時に、前記出力電流検出値に応じて前記慣性定数を可変とすることを特徴とする請求項2記載の系統連系電力変換装置。

#### 【請求項5】

前記仮想同期発電機モデルは、

前記出力電流検出値に基づいて慣性定数変化量を出力するテーブルと、

前記慣性定数変化量を積分する第2積分器と、

前記第2積分器の出力を制限値で制限して慣性定数調整量として出力するリミッタと、

40

通常慣性定数に前記慣性定数調整量を加算して前記慣性定数を算出する加算器と、を備えたことを特徴とする請求項4記載の系統連系電力変換装置。

#### 【請求項6】

同期発電機を模擬した仮想同期発電機制御が行われ、直流電源の直流電力を交流電力に変換するD C / A C変換器を有し、前記D C / A C変換器の出力がL Cフィルタを介して電力系統と連系される系統連系電力変換装置の制御方法であって、

内部誘起電圧算出部が、出力電流検出値と系統電圧検出値の実効値と交流電圧指令値に基づいて、内部誘起電圧を算出し、

P L Lが、前記系統電圧検出値に基づいて、系統周波数とP L L角周波数を出力し、

系統擾乱判定部が、前記系統周波数が周波数上側閾値よりも大きい場合、または、前記

50

系統周波数が周波数下側閾値よりも小さい場合、または、前記系統電圧検出値が電圧上側閾値よりも大きい場合、または、前記系統電圧検出値が電圧下側閾値よりも小さい場合、系統擾乱が発生していると判定して系統擾乱判定信号を出力し、

仮想同期発電機モデルが、前記内部誘起電圧と前記出力電流検出値と前記DC/A/C変換器の出力指令値である機械入力指令値に基づいて、前記仮想同期発電機制御を行うための同期発電機を模擬したVSG角周波数を算出し、前記DC/A/C変換器停止状態かつ前記系統擾乱判定信号が出力されていない場合は前記PLL角周波数に基づいた位相を出力し、前記DC/A/C変換器運転状態もしくは前記系統擾乱判定信号が出力されている場合は前記VSG角周波数に基づいた位相を出力し、

仮想同期インピーダンス補償部が、前記内部誘起電圧と前記系統電圧検出値と前記出力電流検出値に基づいて、同期発電機の内部インピーダンスによる電圧降下を模擬し、系統電圧指令値を算出し、

PCS出力電圧制御部が、前記系統電圧検出値を前記系統電圧指令値に制御する電圧制御を行い、PWM制御指令値を出力し、

PWM制御部が、前記PWM制御指令値と前記位相に基づいて、前記DC/A/C変換器のゲート信号を生成し、前記DC/A/C変換器を使用しない場合は前記DC/A/C変換器の前記ゲート信号をブロックし、前記系統擾乱判定信号が出力されると前記ゲート信号を前記DC/A/C変換器に出力開始することを特徴とする系統連系電力変換装置の制御方法。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、インバータの出力特性に疑似慣性を持たせた系統連系電力変換装置において、インバータによる電力消費を低減させつつ系統安定化に寄与するための運転方法に関する。

##### 【背景技術】

##### 【0002】

特許文献1に代表される同期発電機相当の特性を持たせた系統連系電力変換装置は、系統事故や需給アンバランスなどによって生じる系統電圧・系統周波数の変動を抑制するよう作用する。

##### 【0003】

一般的に、蓄電池を有する系統連系電力変換装置は、ピークシフトやDR(Dissaster Recovery)などの運用方法によって蓄電池を充電または放電するが、蓄電池を使用しない期間はインバータをゲートブロックする。

##### 【先行技術文献】

##### 【特許文献】

##### 【0004】

##### 【文献】特許第6084863号

##### 【発明の概要】

##### 【発明が解決しようとする課題】

##### 【0005】

しかし、疑似慣性を有した系統連系電力変換装置で系統安定化に寄与させるためには、常時インバータを駆動させておく必要がある。蓄電池を使用しない期間すなわちインバータ出力電力がゼロの状態においても、インバータを構成する半導体スイッチを駆動することにより電力損失が発生してしまう。

##### 【0006】

以上示したようなことから、インバータ損失抑制のためにインバータを停止している状態からでも、系統安定化に寄与する系統連系電力変換装置を提供することが課題となる。

##### 【課題を解決するための手段】

##### 【0007】

本発明は、前記従来の問題に鑑み、案出されたもので、その一態様は、同期発電機を模

10

20

30

40

50

擬した仮想同期発電機制御が行われ、直流電源の直流電力を交流電力に変換する D C / A C 変換器を有し、前記 D C / A C 変換器の出力が L C フィルタを介して電力系統と連系される系統連系電力変換装置であって、出力電流検出値と系統電圧検出値の実効値と交流電圧指令値に基づいて、内部誘起電圧を算出する内部誘起電圧算出部と、前記系統電圧検出値に基づいて、系統周波数と P L L 角周波数を出力する P L L と、前記系統周波数が周波数上側閾値よりも大きい場合、または、前記系統周波数が周波数下側閾値よりも小さい場合、または、前記系統電圧検出値が電圧上側閾値よりも大きい場合、または、前記系統電圧検出値が電圧下側閾値よりも小さい場合、系統擾乱が発生していると判定して系統擾乱判定信号を出力する系統擾乱判定部と、前記内部誘起電圧と前記出力電流検出値と前記 D C / A C 変換器の出力指令値である機械入力指令値に基づいて、前記仮想同期発電機制御を行うための同期発電機を模擬した V S G 角周波数を算出し、前記 D C / A C 変換器停止状態かつ前記系統擾乱判定信号が出力されていない場合は前記 P L L 角周波数に基づいた位相を出力し、前記 D C / A C 変換器運転状態もしくは前記系統擾乱判定信号が出力されている場合は前記 V S G 角周波数に基づいた位相を出力する仮想同期発電機モデルと、前記内部誘起電圧と前記系統電圧検出値と前記出力電流検出値に基づいて、同期発電機の内部インピーダンスによる電圧降下を模擬し、系統電圧指令値を算出する仮想同期インピーダンス補償部と、前記系統電圧検出値を前記系統電圧指令値に制御する電圧制御を行い、P W M 制御指令値を出力する P C S 出力電圧制御部と、前記 P W M 制御指令値と前記位相に基づいて、前記 D C / A C 変換器のゲート信号を生成し、前記 D C / A C 変換器を使用しない場合は前記 D C / A C 変換器の前記ゲート信号をブロックし、前記系統擾乱判定信号が出力されると前記ゲート信号を前記 D C / A C 変換器に出力開始する P W M 制御部と、を備えたことを特徴とする。10

#### 【 0 0 0 8 】

また、その一態様として、前記仮想同期発電機モデルは、前記機械入力指令値を機械入力トルクに換算する機械入力トルク算出部と、前記内部誘起電圧と前記出力電流検出値から電気出力トルクを算出する電気出力トルク算出部と、前記機械入力トルクから前記電気出力トルクを減算する第 1 減算器と、スイッチの出力の前回値に基づいて制動巻線に発生するトルクを模擬した制動トルクを出力するダンピングブロックと、前記第 1 減算器の出力から前記制動トルクを減算する第 2 減算器と、前記第 2 減算器の出力を慣性定数で除算する慣性ブロックと、前記慣性ブロックの出力に前記スイッチの出力の前回値を加算して前記 V S G 角周波数を出力する第 1 加算器と、前記 D C / A C 変換器停止状態かつ前記系統擾乱判定信号が出力されていない場合は前記 P L L 角周波数を出力し、前記 D C / A C 変換器運転状態もしくは前記系統擾乱判定信号が出力されている場合は前記 V S G 角周波数を出力する前記スイッチと、前記スイッチの出力に基本周波数を加算して角周波数として出力する第 2 加算器と、前記第 2 加算器の出力を積分して前記位相を出力する第 1 積分器と、を備えたことを特徴とする。20

#### 【 0 0 0 9 】

また、その一態様として、前記系統擾乱判定部は、前記系統周波数の上昇時の変化率が上昇時の閾値よりも大きい場合、または、前記系統周波数の低下時の変化率が低下時の閾値よりも大きい場合、系統擾乱が発生していると判定して前記系統擾乱判定信号を出力することを特徴とする。30

#### 【 0 0 1 0 】

また、その一態様として、前記仮想同期発電機モデルは、前記系統周波数または前記系統電圧検出値の変動時に、前記出力電流検出値に応じて前記慣性定数を可変とすることを特徴とする。

#### 【 0 0 1 1 】

また、その一態様として、前記仮想同期発電機モデルは、前記出力電流検出値に基づいて慣性定数変化量を出力するテーブルと、前記慣性定数変化量を積分する第 2 積分器と、前記第 2 積分器の出力を制限値で制限して慣性定数調整量として出力するリミッタと、通常慣性定数に前記慣性定数調整量を加算して前記慣性定数を算出する加算器と、を備えた

10

20

30

40

50

ことを特徴とする。

**【発明の効果】**

**【0012】**

本発明によれば、インバータ損失抑制のためにインバータを停止している状態からでも、系統安定化に寄与する系統連系電力変換装置を提供することが可能となる。

**【図面の簡単な説明】**

**【0013】**

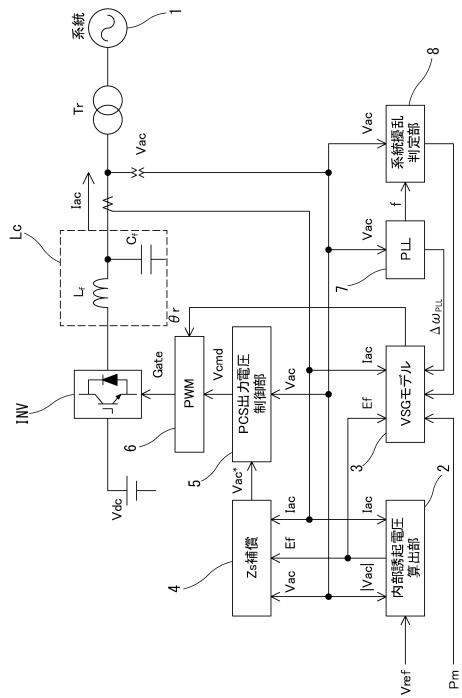

【図1】実施形態1～3の系統連系電力変換装置の全体概略図。

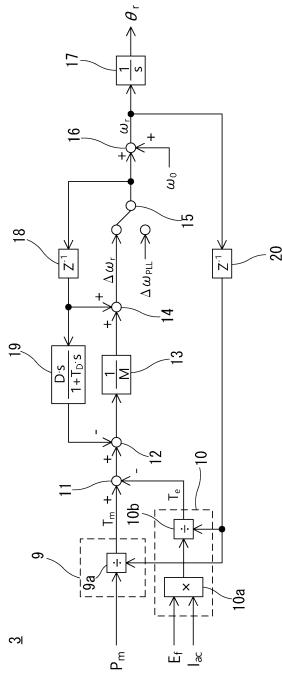

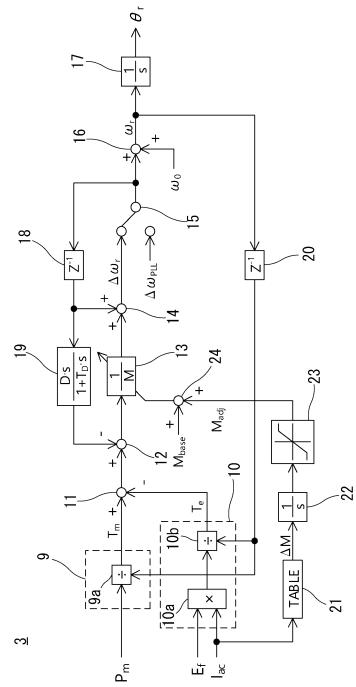

【図2】実施形態1の仮想同期発電機モデルを示すブロック図。

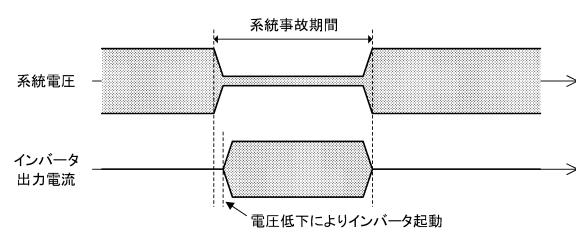

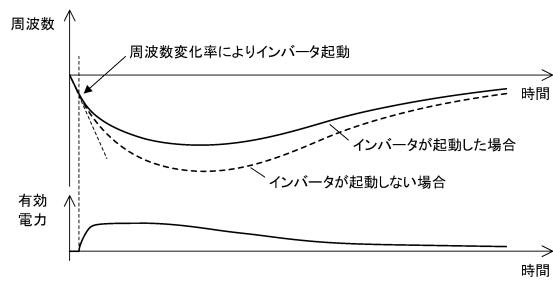

【図3】実施形態1における発電機脱落時の周波数変動およびインバータ出力有効電力の一例を示す図。 10

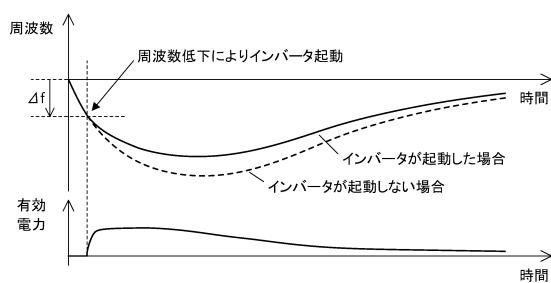

【図4】電圧低下時のインバータ動作の一例を示す図。

【図5】実施形態2における発電機脱落時の周波数変動およびインバータ出力有効電力の一例を示す図。

【図6】実施形態3の仮想同期発電機モデルを示すブロック図。

**【発明を実施するための形態】**

**【0014】**

以下、本願発明における系統連系電力変換装置の実施形態1～3を図1～図6に基づいて詳述する。

**【0015】**

[実施形態1]

図1は本実施形態1における系統連系電力変換装置の全体概略図である。図1に示すように、系統連系電力変換装置の主回路構成は、蓄電池等の直流電源Vdcの直流電力をIGBT等から成るDC/AC変換器（以下、インバータと称する）INVで交流電力に変換し、LCフィルタLCとトランスTrを介して電力系統1と連系する。LCフィルタLCは、フィルタリアクトルLfとフィルタコンデンサCfとを備える。また、LCフィルタLCとトランスTrとの間の出力電流検出値Iacと系統電圧検出値Vacが検出され、後述する制御部に出力される。

**【0016】**

系統連系電力変換装置は、LCフィルタLC後の系統電圧検出値Vacが、内部誘起電圧Efから出力電流Iacが流れることによって生じる仮想同期インピーダンスZsによる電圧降下を減算した系統電圧指令値Vac\*と一致するように制御を行う。 30

**【0017】**

本実施形態1における系統連系電力変換装置の制御部は、図1に示すように、内部誘起電圧算出部2と、仮想同期発電機モデル3と、仮想同期インピーダンス補償部4と、PCS（Power Conversion System）出力電圧制御部5と、PWM制御部6と、PLL（Phase Locked Loop）7と、系統擾乱判定部8と、を備える。

**【0018】**

内部誘起電圧算出部2は、交流電圧指令値Vrefと交流電圧検出値の実効値|Vac|と出力電流検出値Iacとを入力し、内部誘起電圧Efを算出する。 40

**【0019】**

PLL7は、インバータINVの停止時に系統電圧への同期制御を行うため、系統電圧検出値Vacに基づいて、PLL角周波数PLLを仮想同期発電機モデル3に出力する。また、PLL7は系統電圧検出値Vacに基づいて系統周波数fを系統擾乱判定部8に出力する。

**【0020】**

系統擾乱判定部8は、系統電圧検出値Vacと系統周波数fに基づいて系統擾乱が発生しているか否かを判定し、系統擾乱が発生していると判定した場合は系統擾乱判定信号を仮想同期発電機モデル3に出力する。 50

**【 0 0 2 1 】**

仮想同期発電機モデル3は、内部誘起電圧 $E_f$ と出力電流検出値 $I_{a c}$ とインバータINVの出力指令値である機械入力指令値 $P_m$ に基づいて、仮想同期発電機制御を行うための同期発電機を模擬したVSG角周波数 $r$ を算出する。インバータINV停止状態かつ系統擾乱判定信号が出力されていない場合はPLL角周波数 $P_{LL}$ に基づいた位相 $r$ を出力し、インバータINV運転状態もしくは系統擾乱判定信号が出力されている場合はVSG角周波数 $r$ に基づいた位相 $r$ を出力する。

**【 0 0 2 2 】**

仮想同期インピーダンス補償部4は、系統電圧検出値 $V_{a c}$ と出力電流検出値 $I_{a c}$ と内部誘起電圧 $E_f$ とを入力して同期発電機の内部インピーダンスによる電圧降下を模擬し、系統電圧指令値 $V_{a c}^*$ を出力する。

10

**【 0 0 2 3 】**

PCS出力電圧制御部5は、系統電圧検出値 $V_{a c}$ と系統電圧指令値 $V_{a c}^*$ を入力して系統電圧検出値 $V_{a c}$ が系統電圧指令値 $V_{a c}^*$ となるように制御し、PWM制御指令値 $V_{cmd}$ を出力する。

**【 0 0 2 4 】**

PWM制御部6は、PWM制御指令値 $V_{cmd}$ と位相 $r$ とを入力し、ゲート信号 $G_{ate}$ を生成する。直流電源Vdcを使用しない、かつ、系統擾乱判定信号が出力されていない場合はゲート信号 $G_{ate}$ をブロックする。系統擾乱判定信号が出力されている場合はゲート信号 $G_{ate}$ をインバータINVのIGBT等のスイッチング素子に出力する。

20

**【 0 0 2 5 】**

内部誘起電圧算出部2、仮想同期インピーダンス補償部4、PCS出力電圧制御部5、PLL7は、本願発明と直接関係ないため、ここでの詳細な説明は省略する。

**【 0 0 2 6 】**

図2に本実施形態1の仮想同期発電機モデル3を示す。機械入力トルク算出部9は、除算器9aにおいて、機械入力指令値 $P_m$ を角周波数 $r$ の前回値で除算し、機械入力トルク $T_m$ を算出する。

**【 0 0 2 7 】**

電気出力トルク算出部10は、乗算器10aにおいて、内部誘起電圧 $E_f$ と出力電流検出値 $I_{a c}$ を乗算する。除算器10bにおいて、乗算器10aの出力を角周波数 $r$ の前回値で除算し、電気出力トルク $T_e$ を出力する。

30

**【 0 0 2 8 】**

第1減算器11は、機械入力トルク $T_m$ から電気出力トルク $T_e$ を減算する。第2減算器12は、第1減算器11の出力からダンピングプロック19の出力である制動巻線に発生する制動トルクを減算する。

**【 0 0 2 9 】**

慣性プロック13は、第2減算器12の出力を慣性定数Mで除算して発電機の慣性を模擬する。第1加算器14は、慣性プロック13の出力にスイッチ15の出力の前回値を加算し、仮想同期発電機モデルから算出したVSG角周波数 $r$ を出力する。

**【 0 0 3 0 】**

スイッチ15は、インバータINV停止状態かつ系統擾乱判定信号が出力されていない場合はPLL角周波数 $P_{LL}$ を出力し、インバータINV運転状態もしくは系統擾乱判定信号が出力されている場合はVSG角周波数 $r$ を出力する。

40

**【 0 0 3 1 】**

第2加算器16はスイッチ15の出力に基本周波数0(50Hzまたは60Hz)を加算して、角周波数 $r$ として出力する。第1積分器17は、角周波数 $r$ を積分して位相 $r$ を出力する。

**【 0 0 3 2 】**

バッファ18は、スイッチ15の出力を一時記憶し、スイッチ15の出力の前回値として第1加算器14、ダンピングプロック19に出力する。ダンピングプロック19は、バ

50

ツファ18の出力にダンピング補償項  $D_s / 1 + TD_s$  を乗算して、制動巻線に発生する制動トルクを模擬して第2減算器12に出力する。ダンピング補償項  $D_s / 1 + TD_s$  については本願発明と直接関係ないため、ここでの詳細な説明は省略する。

#### 【0033】

バッファ20は、角周波数  $r$  を一時記憶し、角周波数  $r$  の前回値を除算器9a、10bに出力する。

#### 【0034】

系統擾乱判定部8は、系統周波数  $f$  が閾値を超過したか否かで判定する周波数判定と、系統電圧検出値  $V_{ac}$  が閾値を超過したか否かで判定する電圧判定と、を行い、どちらか一方でも閾値を超過した場合に、「系統擾乱あり」と判定して系統擾乱判定信号を出力する。

10

#### 【0035】

ここで、系統周波数  $f$  には周波数上側閾値と周波数下側閾値が設定され、系統電圧検出値  $V_{ac}$  には電圧上側閾値と電圧下側閾値が設定される。系統周波数  $f$  が正常範囲内（周波数上側閾値以下で周波数下側閾値以上）、かつ、系統電圧検出値  $V_{ac}$  が正常範囲内（電圧上側閾値以下で電圧下側閾値以上）であれば「系統擾乱が発生していない」と判定する。

#### 【0036】

系統周波数  $f$  が周波数上側閾値よりも大きい場合、または、系統周波数  $f$  が周波数下側閾値よりも小さい場合、または、系統電圧検出値  $V_{ac}$  が電圧上側閾値よりも大きい場合、または、系統電圧検出値  $V_{ac}$  が電圧下側閾値よりも小さい場合、「系統擾乱が発生している」と判定して系統擾乱判定信号を出力する。すなわち、系統周波数  $f$  または系統電圧検出値  $V_{ac}$  のうち少なくとも何れか一方が正常範囲を逸脱した場合は系統擾乱判定信号を出力する。

20

#### 【0037】

直流電源  $V_{dc}$  を使用しない期間は、PWM制御部6において、インバータINVをゲートブロックさせる。インバータINVの停止中、かつ、系統擾乱が発生していない場合は仮想同期発電機モデル3におけるスイッチ15の出力をPLL角周波数 PLLにすることで、PLL7によって系統電圧に同期制御を行い、角周波数  $r$  を系統周波数に同期させておく。

30

#### 【0038】

電力需給バランスが崩れたことによる周波数変動や系統事故等による系統電圧変動を監視し、これら系統擾乱を検出した場合にはPWM制御部6において、インバータINVをすぐに起動する。また、仮想同期発電機モデル3におけるスイッチ15の出力をVSG角周波数  $r$  にし、インバータINVの出力特性（疑似慣性）に応じた動作を行うことにより、系統の周波数変動を抑制できる。

#### 【0039】

図3に発電機が脱落したことによる周波数変動およびインバータ出力有効電力の一例を示す。発電機が脱落すると系統の周波数は低下する。この際の周波数低下の傾きは系統の慣性に依存する。その後はガバナフリーやLFC (load frequency control) などによって発電機の出力が調整され、系統周波数は定格周波数（正常時の周波数）まで戻ってくる。

40

#### 【0040】

図3の実線がインバータを起動した場合、点線がインバータINVを起動しない場合である。本実施形態1では、インバータINVが停止状態において系統周波数の低下を検出するとすぐにインバータINVの出力を開始するため、インバータINVを起動しない時と比べて周波数の低下量を抑制することが可能となる。

#### 【0041】

図4に系統側での短絡事故等により系統電圧が低下した際のインバータINV動作の一例を示す。インバータINVの停止状態において系統電圧低下を検出するとすぐにインバ

50

ータ I N V は起動するが、系統側が短絡状態のためインバータ I N V の出力可能な電流値での事故電流を出力する。

【 0 0 4 2 】

すなわち、仮想同期インピーダンス補償部 4において、通常時は予め設定された仮想同期インピーダンス  $Z_s$  と出力電流検出値  $I_{a c}$  に基づいて降下電圧を算出し、過電流発生時はインバータ I N V が出力可能な電流制限値  $I_{l i m}$  に制限するために必要な補正仮想同期インピーダンス  $Z_s'$  ( $r'$  および  $x'$ ) と出力電流検出値  $I_{a c}$  とに基づいて、降下電圧を算出する。

【 0 0 4 3 】

過電流を抑制するために必要な補正仮想同期インピーダンス  $Z_s'$  ( $r'$  および  $x'$ ) の算出方法は以下の(1)式となる。 10

【 0 0 4 4 】

【 数 1 】

$$\begin{bmatrix} r' \\ x' \end{bmatrix} = \frac{1}{I_{lim}} \begin{bmatrix} \cos \theta & \sin \theta \\ -\sin \theta & \cos \theta \end{bmatrix} \begin{bmatrix} E_d - V_d \\ E_q - V_q \end{bmatrix} \quad \cdots (1)$$

20

【 0 0 4 5 】

ここで、 $E_d$ ,  $E_q$  は内部誘起電圧  $E_f$  の d 軸成分、q 軸成分、 $V_d$ ,  $V_q$  は系統電圧検出値  $V_{a c}$  の d 軸成分、q 軸成分を示す。

【 0 0 4 6 】

なお、補正仮想同期インピーダンス  $Z_s'$  ( $r'$  および  $x'$ ) を模擬するためには、(1)式によって求めた補正仮想同期インピーダンス  $Z_s'$  が正である必要がある。過電流を抑制するためには、瞬時の出力電流位相情報を必要であるが、系統事故や負荷変動等によって出力電流が乱れた場合などに、瞬時電流から抽出した位相情報を基に補正仮想同期インピーダンス  $Z_s'$  を算出すると、負の値となってしまう場合がある。そこで、抽出した出力電流位相を以下の(2)式の範囲内に制限する。 30

【 0 0 4 7 】

【 数 2 】

$$\tan^{-1} \left( \frac{-(E_d - V_d)}{E_q - V_q} \right) \leq \theta \leq \tan^{-1} \left( \frac{E_q - V_q}{E_d - V_d} \right) \quad \cdots (2)$$

40

【 0 0 4 8 】

なお、内部誘起電圧  $E_f$  を基準として内部位相を定義することで、 $E_q = 0$  となり、簡略化することもできる。また、電流制限値  $I_{l i m}$  は固定値としても良く、出力電流検出

50

値  $I_{ac}$  を電流リミッタにかけた値でも良い。

**【0049】**

図4の説明に戻る。事故点が解除されると系統電圧は復帰し、インバータ出力電流は低下する。

**【0050】**

分散電源が普及すると系統内のインバータ電源比率が増加し運転する発電機が減少することで、系統事故時の事故電流が減少して従来の保護リレーが正常に動作しない懸念がある。本実施形態1では停止していたインバータINVも（半導体スイッチ等が動作可能な範囲で）事故電流を供給するため、従来の保護リレーが適応できる範囲が広がる。

**【0051】**

以上示したように、本実施形態1の系統連系電力変換装置によれば、系統擾乱が発生した時に、インバータINVを停止（ゲートブロック）させた状態から、インバータINVを素早く起動し、疑似慣性に応じた出力をを行うことで、インバータINVによる電力消費を低減させつつ系統の安定化に寄与する。

**【0052】**

[実施形態2]

本実施形態2では、実施形態1の系統擾乱判定部8に、周波数の変化率が閾値を超過したか否かで判定する周波数変化率判定を追加する。

**【0053】**

ここで、周波数変化率には、上昇時の閾値と低下時の閾値を設定する。なお、本明細書では、周波数低下時の周波数変化率と低下時の閾値はそれぞれ絶対値として記載する。そして、系統周波数  $f$  が正常範囲内（周波数上側閾値以下で周波数下側閾値以上）、かつ、系統電圧検出値  $V_{ac}$  が正常範囲内（電圧上側閾値以下で電圧下側閾値以上）、かつ、周波数変化率が正常範囲内（上昇時の閾値以下で低下時の閾値以下）あれば「系統擾乱が発生していない」と判定する。

**【0054】**

系統周波数  $f$  が周波数上側閾値よりも大きい場合、または、系統周波数  $f$  が周波数下側閾値よりも小さい場合、または、系統電圧検出値  $V_{ac}$  が電圧上側閾値よりも大きい場合、または、系統電圧検出値  $V_{ac}$  が電圧下側閾値よりも小さい場合、に加えて、上昇時の周波数変化率が上昇時の閾値よりも大きい場合、または、低下時の周波数変化率が低下時の閾値よりも大きい場合、「系統擾乱が発生している」と判定して系統擾乱判定信号を出力する。

**【0055】**

図5に実施形態2における発電機脱落時の周波数変動およびインバータ出力有効電力の一例を示す。周波数変化率による判定を追加することで、図5に示すように、大容量発電機の脱落などによる周波数変動時に系統周波数  $f$  が周波数閾値を超過するより早くインバータを起動することが可能となる。

**【0056】**

本実施形態2によれば、実施形態1と比べ、周波数変動時のインバータ起動が早くなり、より系統安定化に寄与することができる。

**【0057】**

[実施形態3]

本実施形態3は、仮想同期発電機モデル3に、出力電流検出値  $I_{ac}$  から慣性定数  $M$  の変化量を算出するテーブルと、慣性定数  $M$  の変化量に対する積分器とリミッタを追加し、発電機の慣性を模擬する慣性定数  $M$  を可変とする。

**【0058】**

慣性定数  $M$  を大きくすることで周波数変動が緩やかになるため、周波数変動時にインバータINVが出力する有効電力が大きくなり、系統全体の周波数変動がより抑制される。

**【0059】**

しかし、慣性定数  $M$  を大きくしすぎるとインバータINVが過負荷となり、慣性定数  $M$

10

20

30

40

50

に見合った出力を出せなくなる。

#### 【0060】

そこで、インバータINVの出力電流に応じて慣性定数Mを変化させることで、インバータINVの動作可能な範囲内でより大きな慣性定数Mで動作させる。慣性定数Mは、通常時（系統擾乱等が発生していない状態）の通常慣性定数Mbaseに系統擾乱時の慣性定数調整量Madjを加算して求める。なお、通常慣性定数MbaseはPCSのパラメータとして予め定められた設定値である。

#### 【0061】

図6に本実施形態3の仮想同期発電機モデル3のブロック図を示す。実施形態1と同様の箇所は同じ符号を付し、その説明は省略する。テーブル21は、出力電流検出値Iacの大きさに応じて慣性定数変化量Mを決定する。慣性定数変化量Mは、例えば、装置の定格電流（100%連続運転可能な電流）の80%以下は+M、装置の定格電流の120%以上は-M、それ以外は0のよう決定する。このように慣性定数変化量Mを決定することで、出力に余裕がある場合は慣性定数Mを大きくし、出力に余裕がない場合は慣性定数Mを小さくするように動作する。

10

#### 【0062】

第2積分器22は、慣性定数変化量Mを積分する。リミッタ23は、第2積分器22の出力を制限値に制限する。リミッタ23の出力が慣性定数調整量Madjとなる。

#### 【0063】

リミッタ23は、系統周波数f、系統電圧検出値Vacの変動量が小さい場合に慣性定数Mを大きくし過ぎてしまうことを防止すること、および系統周波数f、系統電圧検出値Vacの変動時のみ慣性定数Mを可変とするために設ける。

20

#### 【0064】

系統周波数f、系統電圧検出値Vacの変動が収束すると（系統周波数f、系統電圧検出値Vacの変動率が小さくなると）、制限値を徐々に0にすることで、通常時の慣性定数Mbaseのみで動作するようになる。

#### 【0065】

加算器24は、通常慣性定数Mbaseに系統擾乱時の慣性定数調整量Madjを加算して慣性定数Mを求め、慣性ブロック13に出力する。

30

#### 【0066】

以上示したように、本実施形態3によれば、実施形態1, 2の作用効果に加え、系統周波数f、系統電圧の変動時にインバータが動作可能な範囲で慣性定数Mを大きくすることで、系統周波数f、系統電圧の変動が抑制できる。

#### 【0067】

以上、本発明において、記載された具体例に対してのみ詳細に説明したが、本発明の技術思想の範囲で多彩な変形および修正が可能であることは、当業者にとって明白なことであり、このような変形および修正が特許請求の範囲に属することは当然のことである。

#### 【符号の説明】

#### 【0068】

1 ... 電力系統

40

2 ... 内部誘起電圧算出部

3 ... 仮想同期発電機モデル

4 ... 仮想同期インピーダンス補償部

5 ... PCS出力電圧制御部

6 ... PWM制御部

7 ... PLL

8 ... 系統擾乱判定部

Vdc ... 直流電源

INV... DC / AC変換器（インバータ）

Lc ... LCフィルタ

50

T r ... トランス

【図面】

【図 1】

【図 2】

【図 3】

【図 4】

10

20

30

40

50

【図 5】

【図 6】

---

フロントページの続き

東京都千代田区内幸町1丁目1番3号 東京電力パワーグリッド株式会社内

(72)発明者 大原 尚

東京都千代田区内幸町1丁目1番3号 東京電力パワーグリッド株式会社内

(72)発明者 栗原 重雄

東京都千代田区内幸町1丁目1番3号 東京電力パワーグリッド株式会社内

(72)発明者 宗像 大介

東京都千代田区内幸町1丁目1番3号 東京電力パワーグリッド株式会社内

(72)発明者 野田 秀樹

東京都千代田区内幸町1丁目1番3号 東京電力パワーグリッド株式会社内

(72)発明者 井上 稔也

東京都品川区大崎2丁目1番1号 株式会社明電舎内

審査官 新田 亮

(56)参考文献 国際公開第2021/029313 (WO, A1)

国際公開第2019/116419 (WO, A1)

(58)調査した分野 (Int.Cl., DB名)

H02J 3/24

H02J 3/38