(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2011-186451

(P2011-186451A)

(43) 公開日 平成23年9月22日(2011.9.22)

| (51) Int.Cl.                 | F 1            | テーマコード (参考) |

|------------------------------|----------------|-------------|

| <b>G02F 1/1368 (2006.01)</b> | GO2F 1/1368    | 2H092       |

| <b>G09G 3/36 (2006.01)</b>   | GO9G 3/36      | 2H193       |

| <b>G09G 3/20 (2006.01)</b>   | GO9G 3/20 623A | 5C006       |

| <b>G02F 1/133 (2006.01)</b>  | GO9G 3/20 612K | 5C080       |

|                              | GO9G 3/20 624B |             |

審査請求 未請求 請求項の数 7 O L (全 29 頁) 最終頁に続く

(21) 出願番号 特願2011-25593 (P2011-25593)

(22) 出願日 平成23年2月9日 (2011.2.9)

(31) 優先権主張番号 特願2010-29446 (P2010-29446)

(32) 優先日 平成22年2月12日 (2010.2.12)

(33) 優先権主張国 日本国 (JP)

(71) 出願人 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 山崎 舜平

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 小山 潤

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

F ターム (参考) 2H092 JA25 JA26 JA28 JA46 JA47

JB22 JB31 JB67 KA08

2H193 ZA04 ZB03 ZB05 ZE09 ZE40

ZF51

最終頁に続く

(54) 【発明の名称】表示装置

## (57) 【要約】

【課題】表示装置の消費電力を低減し、且つ表示品質の低下を抑制すること。

【解決手段】表示装置の各画素に設けられるトランジスタとして、酸化物半導体層を具備するトランジスタを適用する。なお、当該酸化物半導体層を高純度化することで、当該トランジスタのオフ電流を少なくすることが可能である。そのため、当該トランジスタのオフ電流によるデータ信号の値の変動を抑制することができる。すなわち、当該トランジスタが設けられた画素へのデータ信号の書き込み頻度を低減した場合（休止期間が長期化した場合）における表示の劣化（変化）を抑制することができる。加えて、休止期間において信号線に供給される交流の駆動信号の周波数を低減した場合における表示のちらつきを抑制することができる。

【選択図】図2

**【特許請求の範囲】****【請求項 1】**

1画面を走査する走査期間においてデータ信号が供給され、前記走査期間に続き且つ前記走査期間よりも長い休止期間において前記データ信号よりも周波数が低い交流の駆動信号が供給される信号線と、

前記走査期間に含まれる1水平走査期間において選択信号が供給され、前記1水平走査期間以外の期間において非選択信号が供給される走査線と、

ゲートが前記走査線に電気的に接続され、ソース及びドレインの一方が前記信号線に電気的に接続された、酸化物半導体層を具備するトランジスタが設けられた画素と、を有することを特徴とする表示装置。

10

**【請求項 2】**

請求項1において、

前記信号線の電位を制御する信号線駆動回路と、

前記信号線駆動回路に対して、前記データ信号又は前記駆動信号を選択的に出力するコントローラと、を有し、

前記コントローラが、

前記データ信号を生成するデータ信号生成回路と、

前記駆動信号を生成する駆動信号生成回路と、

前記コントローラの出力信号として、前記走査期間において前記データ信号を選択し、前記休止期間において前記駆動信号を選択するスイッチと、を有することを特徴とする表示装置。

20

**【請求項 3】**

請求項2において、

前記コントローラが、

前記データ信号と周波数が等しい第1のクロック信号を生成する基準クロック生成回路と、

前記第1のクロック信号を分周することで、前記駆動信号と周波数が等しい第2のクロック信号を生成する分周回路と、

前記信号線駆動回路内で用いられるクロック信号として、前記走査期間において前記第1のクロック信号を選択し、前記休止期間において前記第2のクロック信号を選択するクロック信号選択用スイッチと、を有することを特徴とする表示装置。

30

**【請求項 4】**

請求項1乃至請求項3のいずれか一項において、

前記駆動信号の電圧の変動が、前記データ信号の電圧変動範囲内にあることを特徴とする表示装置。

**【請求項 5】**

請求項1乃至請求項4のいずれか一項において、

前記画素に、

一方の端子が前記トランジスタのソース及びドレインの他方に電気的に接続され、他方の端子が共通電位線に電気的に接続された容量素子と、

一方の端子が前記トランジスタのソース及びドレインの他方並びに前記容量素子の一方の端子に電気的に接続され、他方の端子が前記共通電位線に電気的に接続された液晶素子と、が設けられ、

40

前記共通電位線の電位が、前記走査期間において前記データ信号と逆の極性を有する共通電位線用駆動信号となり、前記休止期間において固定電位を有する信号となることを特徴とする表示装置。

**【請求項 6】**

請求項1乃至請求項4のいずれか一項において、

前記画素に、

一方の端子が前記トランジスタのソース及びドレインの他方に電気的に接続され、他方

50

の端子が共通電位を供給する配線に電気的に接続された容量素子と、

一方の端子が前記トランジスタのソース及びドレインの他方並びに前記容量素子の一方の端子に電気的に接続され、他方の端子が前記共通電位を供給する配線に電気的に接続された液晶素子と、が設けられ、

前記共通電位が、前記走査期間において前記データ信号と逆の極性を有する第1の共通電位線用駆動信号となり、前記休止期間において前記駆動信号と同じ極性を有する第2の共通電位線用駆動信号となることを特徴とする表示装置。

【請求項7】

請求項6において、

前記駆動信号と前記第2の共通電位線用駆動信号が、同一の信号であることを特徴とする表示装置。 10

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、表示装置に関する。特に、アクティブマトリクス型の表示装置に関する。

【背景技術】

【0002】

マトリクス状に配列された複数の画素を有するアクティブマトリクス型の表示装置が普及している。一般的には、当該画素は、トランジスタと、該トランジスタのゲートに電気的に接続される走査線と、該トランジスタのソース及びドレインの一方に電気的に接続される信号線とを有する。そして、走査線の電位を制御することによってトランジスタをオン状態とすると共に、信号線の電位を当該画素に対するデータ信号となるように制御する。これにより、所望の画素に、所望のデータ信号を供給することができる。当該表示装置は、このような操作を各画素に対して順次行うことで表示を行っている。現在では、表示装置の表示が1秒間に60回(60Hz)書き換えられることが一般的である。すなわち、各画素に対して約0.0167秒に1回の頻度で、データ信号の入力(書き換え)を行うことが一般的である。 20

【0003】

近年では、地球環境への関心が高まり、低消費電力型の表示装置の開発が注目されている。例えば、特許文献1では、表示装置の表示の書き換え頻度を低減することで消費電力を低減する技術が開示されている。特許文献1で開示される表示装置の具体的な構成について以下に述べる。 30

【0004】

特許文献1で開示される表示装置では、1画面を走査する走査期間と、該走査期間に続き且つ該走査期間よりも長い休止期間とが設けられている。そして、当該休止期間において、走査線の電位を非選択信号に固定すると共に、信号線の電位を、(1)固定電位とする、(2)固定電位とした後に浮遊状態とする、又は(3)データ信号の周波数以下の交流の駆動信号とするなどの技術が開示されている。これにより、休止期間における信号線の電位の変動に伴う電力の消費を低減している。加えて、休止期間において信号線の電位をデータ信号の周波数以下の交流の駆動信号とする場合((3)の場合)、信号線と画素電極の容量結合に起因した当該画素電極の電位の変動を、走査期間と休止期間においてほぼ一定とすることが可能である。 40

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2002-182619号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

休止期間において信号線にデータ信号の周波数以下の交流の駆動信号を供給する場合( 50

(3)の場合)、当該休止期間の長期化及び当該駆動信号の周波数の低減が消費電力の低減に対して効果的である。しかしながら、当該休止期間の長期化及び当該駆動信号の周波数の低減のそれぞれに応じて、各画素に設けられたトランジスタのオフ電流の値に比例して、表示品質が低下する蓋然性が高くなる。

#### 【0007】

まず、当該休止期間が長期化するということは、画素がデータ信号を保持したまま、当該画素に設けられたトランジスタがオフ状態を維持する期間が長期化するということである。そのため、当該トランジスタのオフ電流によってデータ信号の値が変動し、各画素の表示が劣化(変化)する蓋然性が高くなる。

#### 【0008】

加えて、当該駆動信号は、上述したように交流の信号である。そのため、信号線の電位が、当該駆動信号の特定の半周期に該当する期間において、特定の画素が有するデータ信号よりも高電位になり、且つ、前述した半周期に続く半周期に該当する期間において、当該画素が有するデータ信号よりも低電位になるといった状態になりえる。この場合、当該画素に設けられたトランジスタに生じるオフ電流によって、前者の半周期に該当する期間において画素電極の電位がV1上昇し、後者の半周期に該当する期間において画素電極の電位がV2下降すると表現できる。ここで、V1及びV2の値は、当該半周期の長さに比例する。すなわち、当該駆動信号の周波数が低減するということは、画素が保持する信号の変動が大きくなるということである。そのため、当該トランジスタのオフ電流によってデータ信号の値が変動し、各画素の表示にちらつきを生じる蓋然性が高くなる。

10

#### 【0009】

そこで、本発明の一態様は、表示装置の消費電力を低減し、且つ表示品質の低下を抑制することを課題の一とする。

#### 【課題を解決するための手段】

#### 【0010】

上述した課題は、各画素に設けられるトランジスタとして、酸化物半導体層を具備するトランジスタを適用することによって解決することができる。なお、当該酸化物半導体層は、電子供与体(ドナー)となる不純物(水素又は水など)を徹底的に除去することにより高純度化された酸化物半導体層である。高純度化された酸化物半導体層中には水素や酸素欠損等に由来するキャリアが極めて少なく(ゼロに近い)、キャリア密度は $1 \times 10^{12} / cm^3$ 未満、好ましくは $1 \times 10^{11} / cm^3$ 未満である。即ち、酸化物半導体層の水素や酸素欠損等に由来するキャリア密度を限りなくゼロに近くする。酸化物半導体層中に水素や酸素欠損等に由来するキャリアが極めて少ないため、トランジスタのオフ電流を少なくすることができる。

30

#### 【0011】

すなわち、本発明の一態様は、1画面を走査する走査期間においてデータ信号が供給され、前記走査期間に続き且つ前記走査期間よりも長い休止期間において前記データ信号よりも周波数が低い交流の駆動信号が供給される信号線と、前記走査期間に含まれる1水平走査期間において選択信号が供給され、前記1水平走査期間以外の期間において非選択信号が供給される走査線と、ゲートが前記走査線に電気的に接続され、ソース及びドレインの一方が前記信号線に電気的に接続された、酸化物半導体層を具備するトランジスタが設けられた画素と、を有することを特徴とする表示装置である。

40

#### 【発明の効果】

#### 【0012】

本発明の一態様の表示装置は、各画素に設けられるトランジスタとして、酸化物半導体層を具備するトランジスタを適用する。なお、当該酸化物半導体層を高純度化することで、当該トランジスタのオフ電流を少なくすることが可能である。そのため、当該トランジスタのオフ電流によるデータ信号の値の変動を抑制することができる。すなわち、当該トランジスタが設けられた画素へのデータ信号の書き込み頻度を低減した場合(休止期間が長期化した場合)における表示の劣化(変化)を抑制することができる。加えて、休止期

50

間において信号線に供給される交流の駆動信号の周波数を低減した場合における表示のちらつきを抑制することができる。

**【図面の簡単な説明】**

**【0013】**

【図1】(A)表示装置の構成を示す図、(B)画素の回路図、(C)画素に設けられるトランジスタの一例を示す断面図。

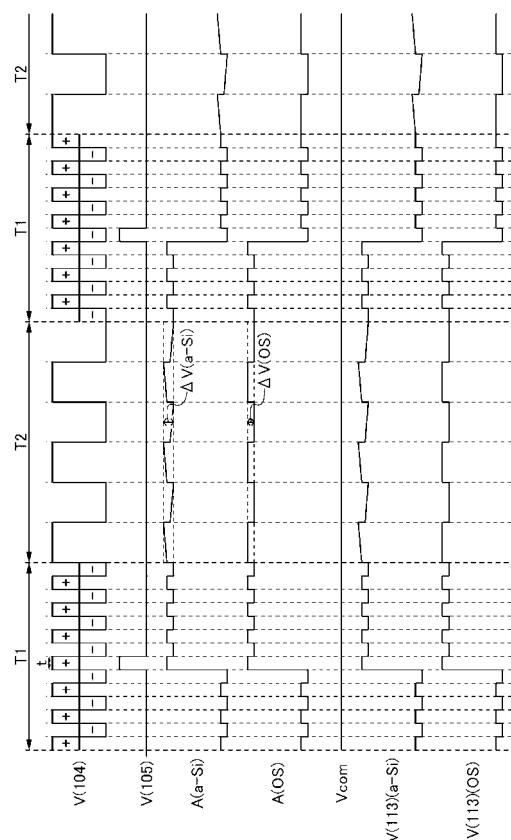

【図2】表示装置の動作を説明する図。

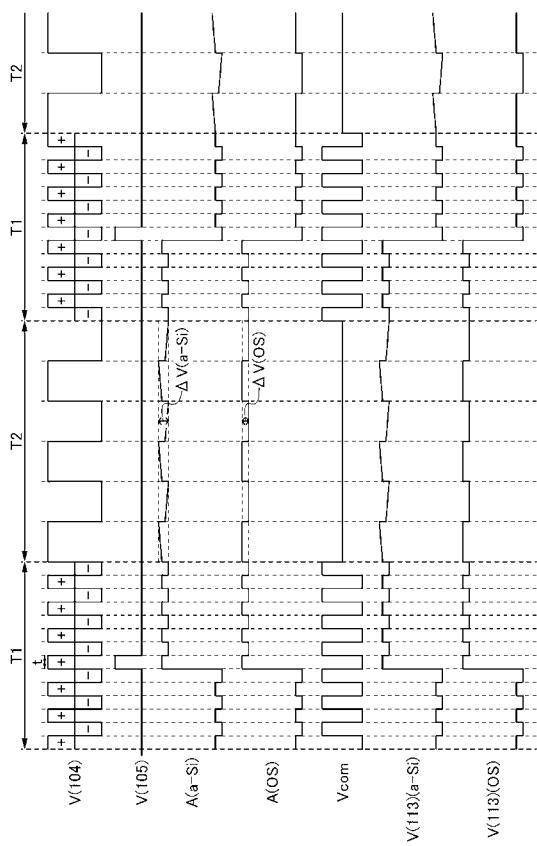

【図3】表示装置の動作を説明する図。

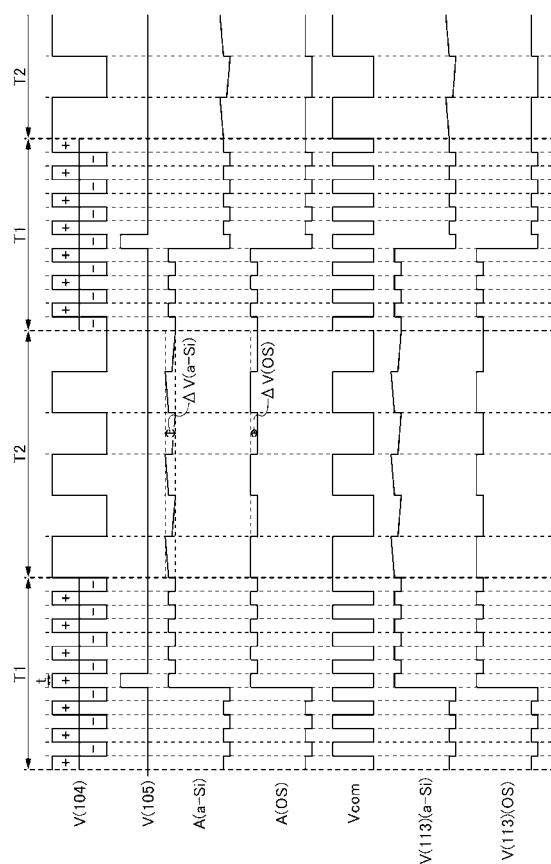

【図4】表示装置の動作を説明する図。

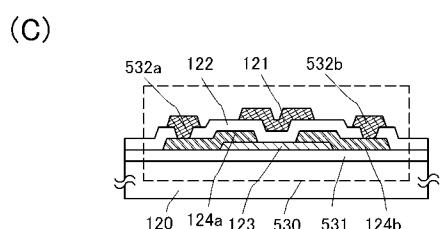

【図5】(A)～(C)表示装置の画素に設けられるトランジスタの一例を示す断面図。

10

【図6】係る表示装置の構成を示す図。

【図7】(A)～(D)トランジスタを説明する図。

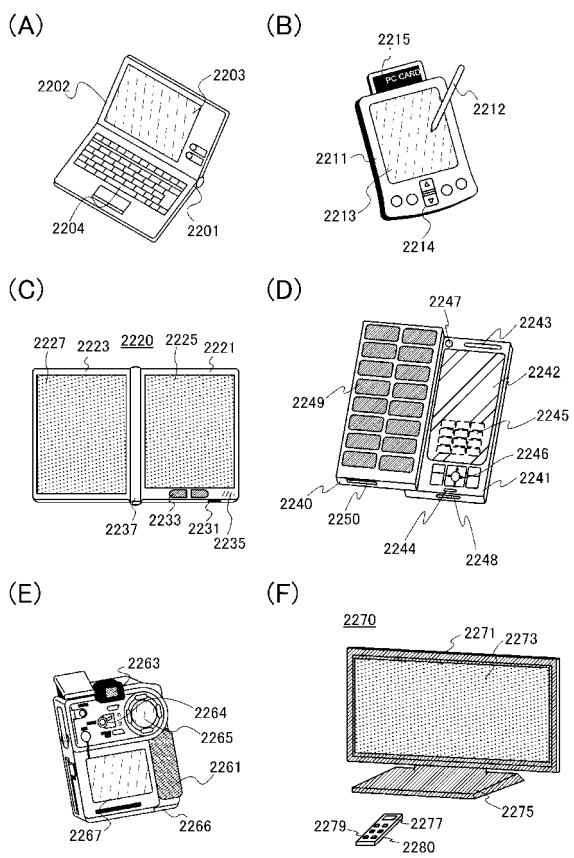

【図8】電子機器を説明する図。

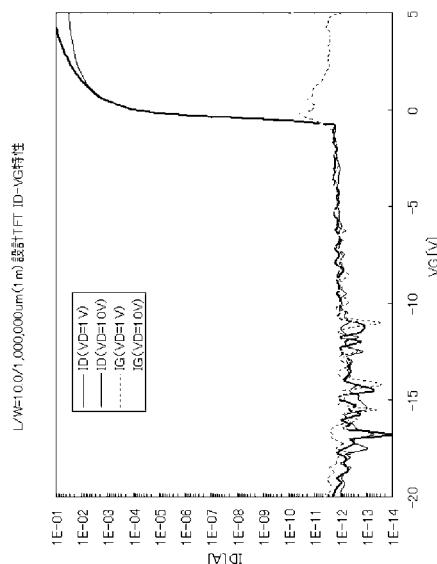

【図9】トランジスタの特性を示す図。

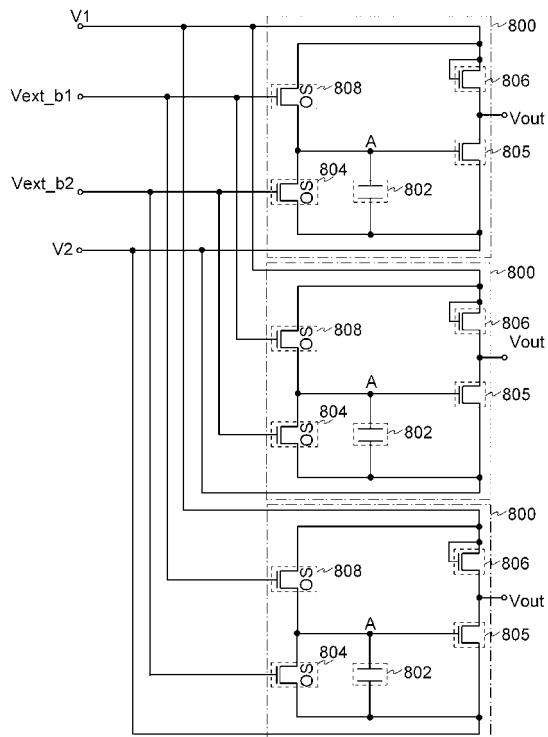

【図10】トランジスタの特性評価用回路図。

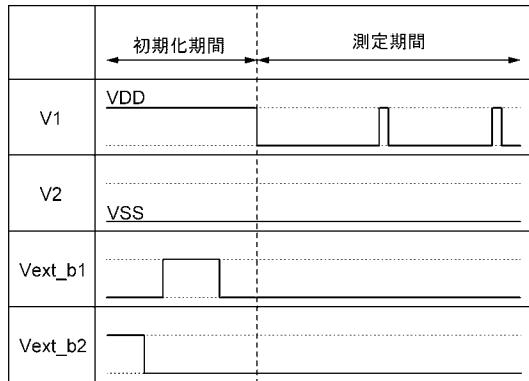

【図11】トランジスタの特性評価用タイミングチャート。

【図12】トランジスタの特性を示す図。

【図13】トランジスタの特性を示す図。

【図14】トランジスタの特性を示す図。

【発明を実施するための形態】

20

**【0014】**

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、本発明の趣旨およびその範囲から逸脱することなくその形態および詳細を様々に変更し得ることは、当業者であれば容易に理解される。したがって、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。

**【0015】**

(アクティブマトリクス型の表示装置の一例について)

はじめに、アクティブマトリクス型の表示装置の一例について説明する。具体的には、1画面を走査する走査期間と、該走査期間に続き且つ該走査期間よりも長い休止期間とが設けられたアクティブマトリクス型の液晶表示装置の一例について図1～図6を参照して説明する。なお、当該走査期間は、マトリクス状に配列された複数の画素の全てに対して、データ信号の入力が1回行われる期間であり、当該休止期間は、マトリクス状に配列された複数の画素の全てに対して、データ信号の入力が行われない期間である。

30

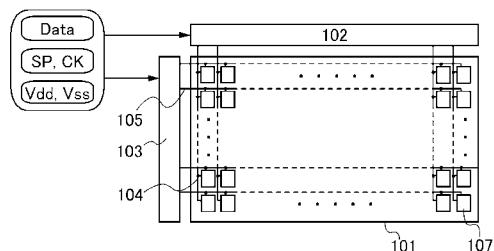

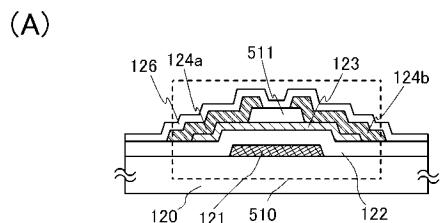

**【0016】**

図1(A)は、アクティブマトリクス型の表示装置の構成例を示す図である。図1(A)に示す表示装置は、画素部101と、信号線駆動回路102と、走査線駆動回路103と、各々が平行又は略平行に配列され、且つ信号線駆動回路102によって電位が制御される複数の信号線104と、各々が平行又は略平行に配列され、且つ走査線駆動回路103によって電位が制御される複数の走査線105とを有する。さらに、画素部101は、複数の画素107を有する。なお、複数の画素107は、マトリクス状に配列している。また、複数の信号線104の各々は、マトリクス状に配列された複数の画素のうち、いずれかの列に配列された複数の画素に電気的に接続され、複数の走査線105の各々は、マトリクス状に配列された複数の画素のうち、いずれかの行に配列された複数の画素に電気的に接続される。なお、信号線駆動回路102及び走査線駆動回路103には、外部から信号(データ信号(Data)、クロック信号(Clock)、スタート信号(Start)など)及び駆動用電源(高電源電位(Vdd)、低電源電位(Vss)など)が入力される。

40

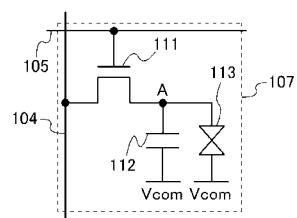

**【0017】**

図1(B)は、図1(A)に示す表示装置が有する画素107の回路図の一例を示す図である。図1(B)に示す画素107は、ゲートが走査線105に電気的に接続され、ソース及びドレインの一方が信号線104に電気的に接続されたトランジスタ111と、一

50

方の端子がトランジスタ 111 のソース及びドレインの他方に電気的に接続され、他方の端子が共通電位 (V<sub>com</sub>) を供給する配線 (共通電位線ともいう) に電気的に接続された容量素子 112 と、一方の端子がトランジスタ 111 のソース及びドレインの他方及び容量素子 112 の一方の端子に電気的に接続され、他方の端子が共通電位線に電気的に接続された液晶素子 113 と、を有する。なお、トランジスタ 111 は、n チャネル型のトランジスタである。また、トランジスタ 111 のソース及びドレインの他方、容量素子 112 の一方の端子、及び液晶素子 113 の一方の端子が電気的に接続するノードをノード A と呼ぶこととする。

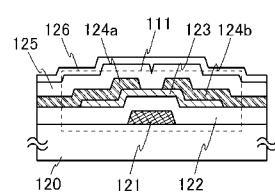

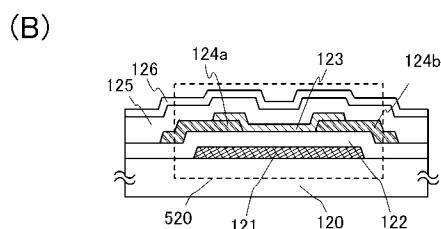

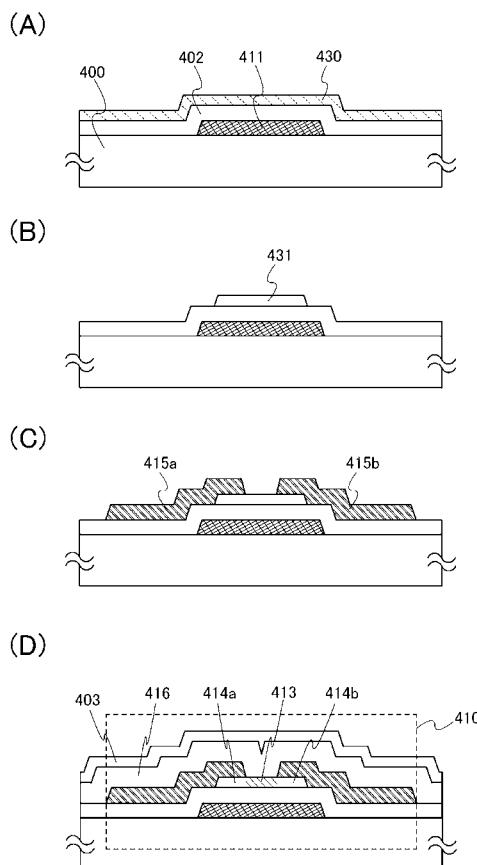

## 【0018】

図 1 (C) は、図 1 (B) に示す画素 107 に設けられたトランジスタ 111 の具体的な構造の一例を示す図である。図 1 (C) に示すトランジスタ 111 は、絶縁表面を有する基板 120 上に設けられたゲート層 121 と、ゲート層 121 上に設けられたゲート絶縁層 122 と、ゲート絶縁層 122 上に設けられた酸化物半導体層 123 と、酸化物半導体層 123 上に設けられたソース層 124a 及びドレイン層 124b とを有する。また、図 1 (C) に示すトランジスタ 111においては、トランジスタ 111 を覆い、酸化物半導体層 123 に接する絶縁層 125 と、絶縁層 125 上に設けられた保護絶縁層 126 とが形成されている。

## 【0019】

図 1 (C) に示すトランジスタ 111 は、上記の通り、半導体層として酸化物半導体層 123 を具備する。酸化物半導体層 123 に用いる酸化物半導体としては、四元系金属酸化物である In - Sn - Ga - Zn - O 系、三元系金属酸化物である In - Ga - Zn - O 系、In - Sn - Zn - O 系、In - Al - Zn - O 系、Sn - Ga - Zn - O 系、Al - Ga - Zn - O 系、Sn - Al - Zn - O 系、二元系金属酸化物である In - Zn - O 系、In - Ga - O 系、Sn - Zn - O 系、Al - Zn - O 系、Zn - Mg - O 系、Sn - Mg - O 系、In - Mg - O 系、または単元系金属酸化物である In - O 系、Sn - O 系、Zn - O 系などを用いることができる。また、上記酸化物半導体に SiO<sub>2</sub> を含んでもよい。ここで、例えば、In - Ga - Zn - O 系酸化物半導体とは、少なくとも In と Ga と Zn を含む酸化物であり、その組成比に特に制限はない。また、In と Ga と Zn 以外の元素を含んでもよい。

## 【0020】

また、酸化物半導体層 123 は、化学式 InM<sub>0.3</sub>(ZnO)<sub>m</sub> (m > 0) で表記される薄膜を用いることができる。ここで、M は、Ga、Al、Mn および Co から選ばれた一または複数の金属元素を示す。例えば M として、Ga、Ga 及び Al、Ga 及び Mn、または Ga 及び Co などを選択することができる。

## 【0021】

上述した酸化物半導体は、変動要因となる水素、水分、水酸基又は水素化合物ともいう)などの不純物を意図的に排除することで高純度化し、電気的に I 型(真性)化された酸化物半導体である。これにより、当該酸化物半導体を半導体層として用いたトランジスタの電気的特性変動を抑止することができる。

## 【0022】

よって酸化物半導体中の水素は少なければ少ないほどよい。また、高純度化された酸化物半導体層中には水素や酸素欠損等に由来するキャリアが極めて少なく(ゼロに近い)、キャリア密度は  $1 \times 10^{12} / \text{cm}^3$  未満、好ましくは  $1 \times 10^{11} / \text{cm}^3$  未満である。即ち、酸化物半導体層の水素や酸素欠損等に由来するキャリア密度を限りなくゼロに近くする。酸化物半導体層中に水素や酸素欠損等に由来するキャリアが極めて少ないため、トランジスタのオフ電流を少なくすることができる。オフ電流は少なければ少ないほど好ましい。上記酸化物半導体を半導体層として用いたトランジスタは、チャネル幅 (w) 1 μmあたりの電流値が 100 zA (ゼットアンペア) 以下、好ましくは 10 zA 以下、更に好ましくは 1 zA 以下である。さらに、pn 接合がなく、ホットキャリア劣化がないため、トランジスタの電気的特性がこれら要因の影響を受けない。

10

20

30

40

50

## 【0023】

このように酸化物半導体層に含まれる水素を徹底的に除去することにより高純度化された酸化物半導体をチャネル形成領域に用いたトランジスタは、オフ電流を極めて小さくすることができる。つまり、トランジスタの非導通状態において、酸化物半導体層は絶縁体とみなせて回路設計を行うことができる。一方で、酸化物半導体層は、トランジスタの導通状態においては、非晶質シリコンで形成される半導体層よりも高い電流供給能力を見込むことができる。

## 【0024】

絶縁表面を有する基板120として使用することができる基板に大きな制限はない。例えば、バリウムホウケイ酸ガラスやアルミニノホウケイ酸ガラスなどのガラス基板を用いることができる。

10

## 【0025】

トランジスタ111において、下地膜となる絶縁膜を基板120とゲート層121の間に設けてもよい。下地膜は、基板からの不純物元素の拡散を防止する機能があり、窒化シリコン膜、酸化シリコン膜、窒化酸化シリコン膜、又は酸化窒化シリコン膜から選ばれた一又は複数の膜による積層構造により形成することができる。

## 【0026】

ゲート層121の材料は、モリブデン、チタン、クロム、タンタル、タングステン、アルミニウム、銅、ネオジム、スカンジウム等の金属材料またはこれらを主成分とする合金材料を用いて、単層でまたは積層して形成することができる。

20

## 【0027】

ゲート絶縁層122は、プラズマCVD法又はスパッタリング法等を用いて、酸化シリコン層、窒化シリコン層、酸化窒化シリコン層、窒化酸化シリコン層、酸化アルミニウム層、窒化アルミニウム層、酸化窒化アルミニウム層、窒化酸化アルミニウム層、又は酸化ハフニウム層を単層で又は積層して形成することができる。例えば、第1のゲート絶縁層としてプラズマCVD法により膜厚50nm以上200nm以下の窒化シリコン層( $\text{SiN}_y$  ( $y > 0$ ))を形成し、第1のゲート絶縁層上に第2のゲート絶縁層として膜厚5nm以上300nm以下の酸化シリコン層( $\text{SiO}_x$  ( $x > 0$ ))を積層することができる。

## 【0028】

30

ソース層124a、ドレイン層124bに用いる導電膜としては、例えば、Al、Cr、Cu、Ta、Ti、Mo、Wから選ばれた元素、または上述した元素を成分とする合金か、上述した元素を組み合わせた合金膜等を用いることができる。また、Al、Cuなどの金属層の下側又は上側の一方または双方にTi、Mo、Wなどの高融点金属層を積層させた構成としても良い。また、Al膜に生ずるヒロックやウィスカーの発生を防止する元素(Si、Nd、Scなど)が添加されているAl材料を用いることで耐熱性を向上させることが可能となる。

## 【0029】

40

また、ソース層124a、ドレイン層124b(これらと同じ層で形成される配線層を含む)となる導電膜としては導電性の金属酸化物で形成しても良い。導電性の金属酸化物としては酸化インジウム( $\text{In}_2\text{O}_3$ )、酸化スズ( $\text{SnO}_2$ )、酸化亜鉛( $\text{ZnO}$ )、酸化インジウム酸化スズ合金( $\text{In}_2\text{O}_3\text{--SnO}_2$ 、ITOと略記する)、酸化インジウム酸化亜鉛合金( $\text{In}_2\text{O}_3\text{--ZnO}$ )またはこれらの金属酸化物材料に酸化シリコンを含ませたものを用いることができる。

## 【0030】

絶縁層125は、代表的には酸化シリコン膜、酸化窒化シリコン膜、酸化アルミニウム膜、または酸化窒化アルミニウム膜などの無機絶縁膜を用いることができる。

## 【0031】

保護絶縁層126は、窒化シリコン膜、窒化アルミニウム膜、窒化酸化シリコン膜、窒化酸化アルミニウム膜などの無機絶縁膜を用いることができる。

50

## 【0032】

また、保護絶縁層126上にトランジスタ起因の表面凹凸を低減するために平坦化絶縁膜を形成してもよい。平坦化絶縁膜としては、ポリイミド、アクリル、ベンゾシクロブテン、等の有機材料を用いることができる。また上記有機材料の他に、低誘電率材料(10w-k材料)等を用いることができる。なお、これらの材料で形成される絶縁膜を複数積層させることで、平坦化絶縁膜を形成してもよい。

## 【0033】

(トランジスタのオフ電流について)

次いで、高純度化された酸化物半導体層を具備するトランジスタのオフ電流を求めた結果について説明する。

10

## 【0034】

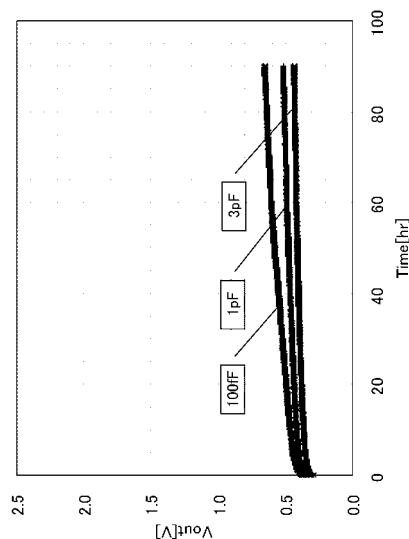

まず、高純度化された酸化物半導体層を具備するトランジスタのオフ電流が十分に小さいことを考慮して、チャネル幅Wが1mと十分に大きいトランジスタを用意してオフ電流の測定を行った。チャネル幅Wが1mのトランジスタのオフ電流を測定した結果を図9に示す。図9において、横軸はゲート電圧VG、縦軸はドレイン電流IDである。ドレイン電圧VDが+1Vまたは+10Vの場合、ゲート電圧VGが-5Vから-20Vの範囲では、トランジスタのオフ電流は、検出限界である $1 \times 10^{-12} \text{ A}$ 以下であることがわかった。また、トランジスタのオフ電流(ここでは、単位チャネル幅(1μm)あたりの値)は $1 \text{ aA}/\mu\text{m}$ ( $1 \times 10^{-18} \text{ A}/\mu\text{m}$ )以下となることがわかった。

## 【0035】

次に、高純度化された酸化物半導体層を具備するトランジスタのオフ電流をさらに正確に求めた結果について説明する。上述したように、高純度化された酸化物半導体層を具備するトランジスタのオフ電流は、測定器の検出限界である $1 \times 10^{-12} \text{ A}$ 以下であることがわかった。そこで、特性評価用素子を作製し、より正確なオフ電流の値(上記測定における測定器の検出限界以下の値)を求めた結果について説明する。

20

## 【0036】

はじめに、電流測定方法に用いた特性評価用素子について、図10を参照して説明する。

## 【0037】

図10に示す特性評価用素子は、測定系800が3つ並列に接続されている。測定系800は、容量素子802、トランジスタ804、トランジスタ805、トランジスタ806、トランジスタ808を有する。トランジスタ804、トランジスタ808には、高純度化された酸化物半導体層を具備するトランジスタを適用した。

30

## 【0038】

測定系800において、トランジスタ804のソース端子およびドレイン端子の一方と、容量素子802の端子の一方と、トランジスタ805のソース端子およびドレイン端子の一方は、電源(V2を与える電源)に接続されている。また、トランジスタ804のソース端子およびドレイン端子の他方と、トランジスタ808のソース端子およびドレイン端子の一方と、容量素子802の端子の他方と、トランジスタ805のゲート端子とは、接続されている。また、トランジスタ808のソース端子およびドレイン端子の他方と、トランジスタ806のソース端子およびドレイン端子の一方と、トランジスタ806のゲート端子は、電源(V1を与える電源)に接続されている。また、トランジスタ805のソース端子およびドレイン端子の他方と、トランジスタ806のソース端子およびドレイン端子の他方とは、出力端子に接続されている。

40

## 【0039】

なお、トランジスタ804のゲート端子には、トランジスタ804のオン状態と、オフ状態を制御する電位Vext\_b2が供給され、トランジスタ808のゲート端子には、トランジスタ808のオン状態と、オフ状態を制御する電位Vext\_b1が供給される。また、出力端子からは電位Voutが出力される。

## 【0040】

50

次に、上記の特性評価用素子を用いた電流測定方法について説明する。

#### 【0041】

まず、オフ電流を測定するために電位差を付与する初期化期間の概略について説明する。初期化期間においては、トランジスタ808のゲート端子に、トランジスタ808をオン状態とする電位 $V_{ext\_b1}$ を入力して、トランジスタ804のソース端子およびドレイン端子の他方と接続されるノード(つまり、トランジスタ808のソース端子およびドレイン端子の一方、容量素子802の端子の他方、およびトランジスタ805のゲート端子に接続されるノード)であるノードAに電位 $V1$ を与える。ここで、電位 $V1$ は、例えば高電位とする。また、トランジスタ804はオフ状態としておく。

#### 【0042】

その後、トランジスタ808のゲート端子に、トランジスタ808をオフ状態とする電位 $V_{ext\_b1}$ を入力して、トランジスタ808をオフ状態とする。トランジスタ808をオフ状態とした後に、電位 $V1$ を低電位とする。ここでも、トランジスタ804はオフ状態としておく。また、電位 $V2$ は電位 $V1$ と同じ電位とする。以上により、初期化期間が終了する。初期化期間が終了した状態では、ノードAとトランジスタ804のソース端子およびドレイン端子の一方との間に電位差が生じ、また、ノードAとトランジスタ808のソース端子およびドレイン端子の他方との間に電位差が生じることになるため、トランジスタ804およびトランジスタ808には僅かに電荷が流れる。つまり、オフ電流が発生する。

#### 【0043】

次に、オフ電流の測定期間の概略について説明する。測定期間においては、トランジスタ804のソース端子およびドレイン端子の一方の端子の電位(つまり $V2$ )、並びに、トランジスタ808のソース端子およびドレイン端子の他方の端子の電位(つまり $V1$ )は低電位に固定しておく。一方で、測定期間中は、上記ノードAの電位は固定しない(フローティング状態とする)。これにより、トランジスタ804、トランジスタ808に電荷が流れ、時間の経過と共にノードAに保持される電荷量が変動する。そして、ノードAに保持される電荷量の変動に伴って、ノードAの電位が変動する。つまり、出力端子の出力電位 $Vout$ も変動する。

#### 【0044】

上記電位差を付与する初期化期間、および、その後の測定期間における各電位の関係の詳細(タイミングチャート)を図11に示す。

#### 【0045】

初期化期間において、まず、電位 $V_{ext\_b2}$ を、トランジスタ804がオン状態となるような電位(高電位)とする。これによって、ノードAの電位は $V2$ すなわち低電位( $VSS$ )となる。なお、ノードAに低電位( $VSS$ )を与えるのは必須ではない。その後、電位 $V_{ext\_b2}$ を、トランジスタ804がオフ状態となるような電位(低電位)として、トランジスタ804をオフ状態とする。そして、次に、電位 $V_{ext\_b1}$ を、トランジスタ808がオン状態となるような電位(高電位)とする。これによって、ノードAの電位は $V1$ 、すなわち高電位( $VDD$ )となる。その後、 $V_{ext\_b1}$ を、トランジスタ808がオフ状態となるような電位とする。これによって、ノードAがフローティング状態となり、初期化期間が終了する。

#### 【0046】

その後の測定期間においては、電位 $V1$ および電位 $V2$ を、ノードAに電荷が流れ込み、またはノードAから電荷が流れ出すような電位とする。ここでは、電位 $V1$ および電位 $V2$ を低電位( $VSS$ )とする。ただし、出力電位 $Vout$ を測定するタイミングにおいては、出力回路を動作させる必要が生じるため、一時的に $V1$ を高電位( $VDD$ )とすることがある。なお、 $V1$ を高電位( $VDD$ )とする期間は、測定に影響を与えない程度の短期間とする。

#### 【0047】

上述のようにして電位差を与え、測定期間が開始されると、時間の経過と共にノードA

10

20

30

40

50

に保持される電荷量が変動し、これに従ってノードAの電位が変動する。これは、トランジスタ805のゲート端子の電位が変動することを意味するから、時間の経過と共に、出力端子の出力電位V<sub>out</sub>の電位も変化することとなる。

## 【0048】

得られた出力電位V<sub>out</sub>から、オフ電流を算出する方法について、以下に説明する。

## 【0049】

オフ電流の算出に先だって、ノードAの電位V<sub>A</sub>と、出力電位V<sub>out</sub>との関係を求めておく。これにより、出力電位V<sub>out</sub>からノードAの電位V<sub>A</sub>を求めることができる。上述の関係から、ノードAの電位V<sub>A</sub>は、出力電位V<sub>out</sub>の関数として次式のように表すことができる。

10

## 【0050】

## 【数1】

$$V_A = F(V_{out})$$

## 【0051】

また、ノードAの電荷Q<sub>A</sub>は、ノードAの電位V<sub>A</sub>、ノードAに接続される容量C<sub>A</sub>、定数(const)を用いて、次式のように表される。ここで、ノードAに接続される容量C<sub>A</sub>は、容量素子802の容量と他の容量の和である。

## 【0052】

## 【数2】

20

$$Q_A = C_A V_A + \text{const}$$

## 【0053】

ノードAの電流I<sub>A</sub>は、ノードAに流れ込む電荷(またはノードAから流れ出る電荷)の時間微分であるから、ノードAの電流I<sub>A</sub>は次式のように表される。

## 【0054】

## 【数3】

$$I_A \equiv \frac{\Delta Q_A}{\Delta t} = \frac{C_A \cdot \Delta F(V_{out})}{\Delta t}$$

30

## 【0055】

このように、ノードAに接続される容量C<sub>A</sub>と、出力端子の出力電位V<sub>out</sub>から、ノードAの電流I<sub>A</sub>を求めることができる。

## 【0056】

以上に示す方法により、オフ状態においてトランジスタのソースとドレイン間を流れるオフ電流を測定することができる。

## 【0057】

ここでは、チャネル長L = 10 μm、チャネル幅W = 50 μmの、高純度化した酸化物半導体層を具備するトランジスタ804、高純度化された酸化物半導体を具備するトランジスタ808を作製した。また、並列された各測定系800において、容量素子802の各容量値を、100 fF、1 pF、3 pFとした。

40

## 【0058】

なお、上述した測定では、V<sub>DD</sub> = 5 V、V<sub>SS</sub> = 0 Vとした。また、測定期間ににおいては、電位V<sub>1</sub>を原則としてV<sub>SS</sub>とし、10 ~ 300 secごとに、100 msecの期間だけV<sub>DD</sub>としてV<sub>out</sub>を測定した。また、素子に流れる電流Iの算出に用いられるtは、約3000 secとした。

## 【0059】

図12に、上記電流測定に係る経過時間Timeと、出力電位V<sub>out</sub>との関係を示す。図12より、時間の経過にしたがって、電位が変化している様子が確認できる。

## 【0060】

50

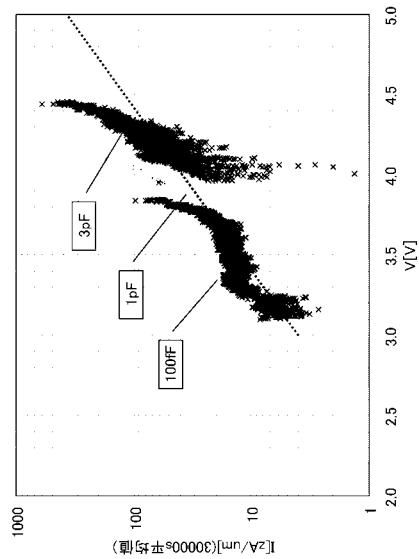

図13には、上記電流測定によって算出された室温(25)におけるオフ電流を示す。なお、図13は、トランジスタ804又はトランジスタ808のソース-ドレイン電圧Vと、オフ電流Iとの関係を表すものである。図13から、ソース-ドレイン電圧が4Vの条件において、オフ電流は約 $40\text{zA}/\mu\text{m}$ であることが分かった。また、ソース-ドレイン電圧が3.1Vの条件において、オフ電流は $10\text{zA}/\mu\text{m}$ 以下であることが分かった。なお、 $1\text{zA}$ は $10^{-21}\text{A}$ を表す。

#### 【0061】

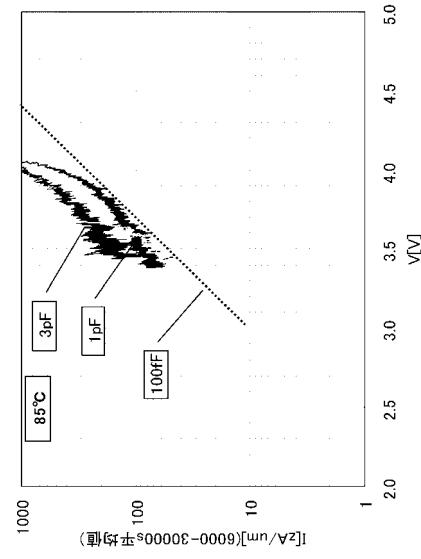

さらに、上記電流測定によって算出された85の温度環境下におけるオフ電流について図14に示す。図14は、85の温度環境下におけるソース-ドレイン電圧Vと、オフ電流Iとの関係を表すものである。図14から、ソース-ドレイン電圧が3.1Vの条件において、オフ電流は $100\text{zA}/\mu\text{m}$ 以下であることが分かった。10

#### 【0062】

以上により、高純度化された酸化物半導体層を具備するトランジスタでは、オフ電流が十分に小さくなることが確認された。

#### 【0063】

(アクティブマトリクス型の表示装置の動作の一例について)

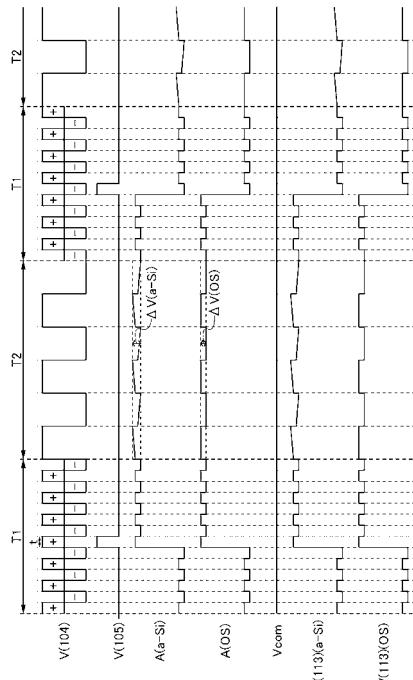

次いで、上述した表示装置の動作の一例について、図2を参照して説明する。なお、図2においては、図1(B)に示す信号線104の電位(V(104))、走査線105の電位(V(105))、トランジスタ111が酸化物半導体層を具備するトランジスタである場合におけるノードAの電位(A(OS))、共通電位(Vcom)、及びトランジスタ111が酸化物半導体層を具備するトランジスタである場合における液晶素子113に印加される電圧(V(113)(OS))を模式的に示している。加えて、図2においては、トランジスタ111がアモルファスシリコン層を具備するトランジスタである場合におけるノードAの電位(A(a-Si))、及びトランジスタ111がアモルファスシリコン層を具備するトランジスタである場合における液晶素子113に印加される電圧(V(113)(a-Si))を、比較のために、模式的に示している。20

#### 【0064】

信号線104には、走査期間(T1)においてデータ信号が供給され、休止期間(T2)において交流の駆動信号が供給される。なお、当該データ信号は、1水平走査期間(t:1ゲート選択期間ともいう)毎に極性が反転する信号である。すなわち、本明細書で開示される表示装置は、ゲートライン反転駆動を行う表示装置である。なお、当該データ信号は、アナログ信号である。また、当該駆動信号は、少なくとも1水平走査期間よりも長い期間毎に極性が反転する交流の信号である。なお、当該駆動信号は、2値の信号である。また、当該駆動信号の電圧の変動を、データ信号の電圧変動範囲内とすることができる。

#### 【0065】

走査線105には、走査期間(T1)に含まれる特定の1水平走査期間にハイレベルの電位(選択信号)が供給され、それ以外の期間ではロウレベルの電位(非選択信号)が供給される。すなわち、画素107が有するトランジスタ111は、当該1水平走査期間においてオン状態となり、それ以外の期間ではオフ状態となる。30

#### 【0066】

ノードAには、1水平走査期間においてトランジスタ111を介して信号線104からデータ信号が供給され、それ以外の期間では信号が供給されない。すなわち、当該1水平走査期間以外の期間では、ノードAは、浮遊状態となる。そのため、当該1水平走査期間以外の期間において、ノードAの電位は、信号線104とノードAの容量結合によって変動する。なお、容量結合に起因したノードAの電位の変動は、トランジスタ111が、アモルファスシリコン層を具備するトランジスタであるか、酸化物半導体層を具備するトランジスタであるかによって大きく変化することはない。

#### 【0067】

しかしながら、トランジスタ111が、アモルファスシリコンを具備するトランジスタ

10

20

30

40

50

である場合と、酸化物半導体を具備するトランジスタである場合とでは、休止期間におけるノードAの電位の変動量が異なる。具体的には、休止期間(T2)におけるノードAの電位の変動量が、酸化物半導体層を具備するトランジスタの方がアモルファスシリコン層を具備するトランジスタよりも小さくなる( $V(a-Si) > V(OS)$ となる)。これは、酸化物半導体層を具備するトランジスタの方がアモルファスシリコン層を具備するトランジスタよりもオフ電流が小さいことに起因する。

#### 【0068】

なお、ここでは、共通電位(Vcom)として固定電位を適用している。当該固定電位としては、接地電位又は0Vなどを適用することができる。

#### 【0069】

液晶素子113には、ノードAの電位と共通電位(Vcom)の電位差分の電圧が印加される。そのため、液晶素子113に印加される電圧の変化は、ノードAの電位の変化と同様である。

#### 【0070】

画素107における表示は、液晶素子113に印加される電圧によって決まる。上述した表示装置において、当該電圧は、信号線104との容量結合及びトランジスタ111に生じるオフ電流などによって変動する。従って、画素107における実際の表示は、1水平走査期間において画素107に入力されるデータ信号に基づいて形成される表示とは厳密には異なる。具体的な例を以下に述べる。仮に、走査期間において、画素107に対して1秒間に60回(約16.7msに1回)データ信号が入力されるとする。この場合、1水平走査期間は、16.7msより桁違いに短い。ここでは、当該1水平走査期間は、便宜上16.7μsとする(例えば、表示装置においてマトリクス状に配列された複数の画素の行数が1000行であるとすると、当該1水平走査期間は16.7μs程度となる)。この時、信号線104には、画素107と同列に設けられた画素に対するデータ信号の供給が当該1水平走査期間以外の期間にも行われるため、信号線104の電位は当該1水平走査期間以外の期間においても変動する。そのため、ノードAの電位も信号線104との容量結合によって変動し、画素107における16.7ms間の実質的な表示は、当該1水平走査期間(16.7μs)に信号線104から供給されるデータ信号に基づく表示とは厳密には異なる。

#### 【0071】

さらに、本明細書で開示される表示装置は、休止期間を有する。仮に、休止期間において信号線104の電位が固定電位となる又は浮遊状態となる場合、液晶素子113に印加される電圧の変動に対して、上述した容量結合による寄与がなくなる。この場合、走査期間における画素107の表示と、休止期間における画素107の表示とが異なることになる。これに対し、本明細書で開示される表示装置は、休止期間において、信号線104に対して交流の駆動信号を供給している。そのため、休止期間においても、走査期間と同程度の容量結合による寄与を、液晶素子113に印加される電圧の変動に対して与えることができる。これにより、休止期間における画素107の表示を、走査期間における表示と同様とすることができます。

#### 【0072】

また、本明細書で開示される表示装置は、画素107に設けられたトランジスタ111として酸化物半導体層を具備するトランジスタを適用している。これにより、液晶素子113に印加される電圧に対する、トランジスタ111のオフ電流の寄与を低減することができる。これにより、画素107における信号の保持期間を長期化することができる。すなわち、休止期間を長期化することができる。加えて、休止期間において、液晶素子113に印加される電圧の振幅を低減することが可能になる。これにより、画素107における表示のちらつきを低減することができる。特に、この効果は、信号線104に供給される交流の駆動信号の周波数が低減された場合に大きい。

#### 【0073】

以上のように、本明細書で開示される表示装置は、酸化物半導体を具備するトランジス

10

20

30

40

50

タをトランジスタ 111 として適用することで、休止期間の長期化された場合、又は休止期間において信号線 104 に供給される交流の駆動信号の周波数が低減された場合であっても表示品質を保持できる表示装置である。すなわち、本明細書で開示される表示装置は、消費電力の低減及び表示品質の低下の抑制が可能な表示装置である。

#### 【0074】

(アクティブマトリクス型の表示装置の変形例について)

上述した表示装置は、本発明の一態様であり、当該表示装置と異なる点を有する表示装置も本発明には含まれる。

#### 【0075】

例えば、上述した表示装置においては、共通電位線に固定電位が供給される構成について示したが、走査期間において、共通電位線に交流の駆動信号（第1の共通電位線用駆動信号）が供給される構成（いわゆる、コモン反転駆動）とすることも可能である（図3参照）。これにより、データ信号の電圧振幅を半減することが可能になる。この場合、共通電位線の電位は、走査期間においてデータ信号と逆の極性を有する2値の信号となり、休止期間において固定電位を有する信号となる。

#### 【0076】

さらに、休止期間においても、共通電位線に交流の駆動信号（第2の共通電位線用駆動信号）を供給することも可能である（図4参照）。この場合、共通電位線の電位は、走査期間においてデータ信号と逆の極性を有する2値の信号（第1の共通電位線用駆動信号）となり、休止期間において信号線 104 に供給される交流の駆動信号と同じ極性を有する2値の信号（第2の共通電位線用駆動信号）となる。なお、休止期間において、共通電位線に供給される交流の駆動信号（第2の共通電位線用駆動信号）の電圧の変動を、走査期間において、共通電位線に供給される交流の駆動信号（第1の共通電位線用駆動信号）の電圧変動範囲内とすることができます。また、休止期間において、共通電位線に供給される交流の駆動信号（第2の共通電位線用駆動信号）を、休止期間において信号線 104 に供給される交流の駆動信号と同一の信号とすることも可能である。

#### 【0077】

また、上述した表示装置においては、休止期間において信号線 104 に供給される交流の駆動信号が2値の信号である構成について示したが、当該駆動信号が多値の信号によって構成されていてもよい。

#### 【0078】

また、上述した表示装置においては、容量素子 112 の他方の端子及び液晶素子 113 の他方の端子のそれぞれが、同一の共通電位（Vcom）が供給される配線に電気的に接続される構成について示したが、容量素子 112 の他方の端子及び液晶素子 113 の他方の端子のそれぞれが電気的に接続される配線に供給される共通電位が異なっていてもよい。すなわち、容量素子 112 の他方の端子が第1の共通電位を供給する配線に電気的に接続され、液晶素子 113 の他方の端子が、第1の共通電位とは異なる、第2の共通電位を供給する配線に電気的に接続される構成としてもよい。

#### 【0079】

また、上述した表示装置においては、トランジスタ 111 として、チャネルエッヂ型と呼ばれるボトムゲート構造の一つを適用する構成について示した（図1（C）参照）が、トランジスタ 111 は、当該構成に限定されない。例えば、図5（A）～（C）に示すトランジスタを適用することが可能である。

#### 【0080】

図5（A）に示すトランジスタ 510 は、チャネル保護型（チャネルトップ型ともいう）と呼ばれるボトムゲート構造の一つである。

#### 【0081】

トランジスタ 510 は、絶縁表面を有する基板 120 上に、ゲート層 121、ゲート絶縁層 122、酸化物半導体層 123、酸化物半導体層 123 のチャネル形成領域を覆うチャネル保護層として機能する絶縁層 511、ソース層 124a、及びドレイン層 124b

10

20

30

40

50

を含む。また、ソース層 124a、ドレイン層 124b、及び絶縁層 511 を覆い、保護絶縁層 126 が形成されている。

#### 【0082】

図 5 (B) 示すトランジスタ 520 はボトムゲート型のトランジスタであり、絶縁表面を有する基板である基板 120 上に、ゲート層 121、ゲート絶縁層 122、ソース層 124a、ドレイン層 124b、及び酸化物半導体層 123 を含む。また、ソース層 124a 及びドレイン層 124b を覆い、酸化物半導体層 123 に接する絶縁層 125 が設けられている。絶縁層 125 上にはさらに保護絶縁層 126 が形成されている。

#### 【0083】

トランジスタ 520においては、ゲート絶縁層 122 は基板 120 及びゲート層 121 上に接して設けられ、ゲート絶縁層 122 上にソース層 124a、ドレイン層 124b が接して設けられている。そして、ゲート絶縁層 122、及びソース層 124a、ドレイン層 124b 上に酸化物半導体層 123 が設けられている。

#### 【0084】

図 5 (C) に示すトランジスタ 530 は、トップゲート構造のトランジスタの一つである。トランジスタ 530 は、絶縁表面を有する基板 120 上に、絶縁層 531、酸化物半導体層 123、ソース層 124a、及びドレイン層 124b、ゲート絶縁層 122、ゲート層 121 を含み、ソース層 124a、ドレイン層 124b にそれぞれ配線層 532a、配線層 532b が接して設けられ電気的に接続している。

#### 【0085】

なお、絶縁層 511、531 は、代表的には酸化シリコン膜、酸化窒化シリコン膜、酸化アルミニウム膜、または酸化窒化アルミニウム膜などの無機絶縁膜を用いることができる。また、配線層 532a、配線層 532b に用いる導電膜としては、例えば、Al、Cr、Cu、Ta、Ti、Mo、W から選ばれた元素、または上述した元素を成分とする合金か、上述した元素を組み合わせた合金膜等を用いることができる。また、Al、Cu などの金属層の下側又は上側の一方または双方に Ti、Mo、W などの高融点金属層を積層させた構成としても良い。また、Al 膜に生ずるヒロックやウイスカーの発生を防止する元素 (Si、Nd、Sc など) が添加されている Al 材料を用いることで耐熱性を向上させることが可能となる。

#### 【0086】

(アクティブマトリクス型の表示装置に対する信号供給の具体例について)

以下では、上述した表示装置において、走査期間においてデータ信号を信号線に供給し、且つ休止期間において交流の駆動信号を供給するための構成の具体例について図 6 を参照して説明する。

#### 【0087】

図 6 に示す表示装置は、コントローラ 600 を有する。コントローラ 600 は、データ信号を生成するデータ信号生成回路 601 と、交流の駆動信号を生成する駆動信号生成回路 602 と、走査期間において信号線駆動回路 102 内で用いられるクロック信号を生成する基準クロック信号生成回路 603 と、基準クロック信号生成回路 603 から入力されるクロック信号を分周した信号を出力する分周回路 604 とを有する。なお、分周回路 604 の出力信号は、休止期間において信号線駆動回路 102 内で用いられるクロック信号となる。また、当該データ信号と当該クロック信号は、周波数が等しくなるように制御される。同様に、当該駆動信号と当該分周した信号は、周波数が等しくなるように制御される。

#### 【0088】

さらに、図 6 に示す表示装置は、データ信号生成回路 601 と駆動信号生成回路 602 のいずれの出力信号を信号線駆動回路 102 に出力するかを選択するスイッチ 605 と、基準クロック信号生成回路 603 と分周回路 604 のいずれの出力信号を信号線駆動回路 102 に出力するかを選択するスイッチ 606 とを有する。具体的には、スイッチ 605 は、走査期間においてデータ信号生成回路 601 の出力信号 (データ信号) を選択し、休

10

20

30

40

50

止期間において駆動信号生成回路 602 の出力信号（駆動信号）を選択する。また、スイッチ 606 は、走査期間において基準クロック信号生成回路 603 の出力信号を選択し、休止期間において分周回路 604 の出力信号を選択する。

#### 【0089】

このような構成及び動作を行うコントローラ 600 を設けることによって、上述した表示装置の動作が可能である。

#### 【0090】

（トランジスタの製造方法の具体例について）

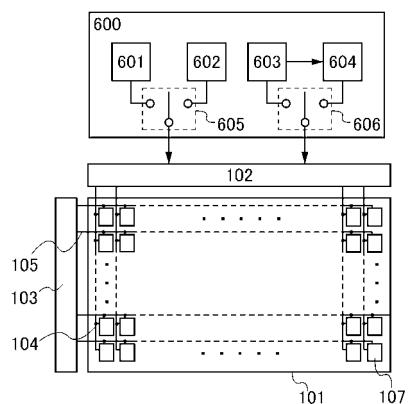

以下では、トランジスタ 111 に適用可能なトランジスタの具体例について図 7 を参照して説明する。

10

#### 【0091】

図 7 (A) ~ (D) は、トランジスタ 111 の具体的な構成及び作製工程の具体例を示す図である。なお、図 7 (D) に示すトランジスタ 410 は、チャネルエッチ型と呼ばれるボトムゲート構造の一つである。また、図 7 (D) には、シングルゲート構造のトランジスタを示すが、必要に応じて、チャネル形成領域を複数有するマルチゲート構造のトランジスタとすることができる。

#### 【0092】

以下、図 7 (A) ~ (D) を参照して、基板 400 上にトランジスタ 410 を作製する工程について説明する。

20

#### 【0093】

まず、絶縁表面を有する基板 400 上に導電膜を形成した後、第 1 のフォトリソグラフィ工程によりゲート層 411 を形成する。なお、当該工程において用いられるレジストマスクは、インクジェット法によって形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減することができる。

#### 【0094】

絶縁表面を有する基板 400 に使用することができる基板に大きな制限はないが、少なくとも、後の加熱処理に耐えうる程度の耐熱性を有していることが必要となる。例えば、バリウムホウケイ酸ガラスやアルミニノホウケイ酸ガラスなどのガラス基板を用いることができる。また、ガラス基板としては、後の加熱処理の温度が高い場合には、歪み点が 730 以上のものを用いると良い。

30

#### 【0095】

下地層となる絶縁層を基板 400 とゲート層 411 の間に設けてもよい。下地層は、基板 400 からの不純物元素の拡散を防止する機能があり、窒化シリコン膜、酸化シリコン膜、窒化酸化シリコン膜、又は酸化窒化シリコン膜から選ばれた一又は複数の膜による積層構造により形成することができる。

#### 【0096】

また、ゲート層 411 の材料は、モリブデン、チタン、クロム、タンタル、タングステン、アルミニウム、銅、ネオジム、スカンジウム等の金属材料又はこれらを主成分とする合金材料を用いて、単層で又は積層して形成することができる。

40

#### 【0097】

例えば、ゲート層 411 の 2 層の積層構造としては、アルミニウム層上にモリブデン層を積層した 2 層構造、銅層上にモリブデン層を積層した 2 層構造、銅層上に窒化チタン層若しくは窒化タンタルを積層した 2 層構造、窒化チタン層とモリブデン層を積層した 2 層構造とすることが好ましい。3 層の積層構造としては、タングステン層または窒化タングステン層と、アルミニウムとシリコンの合金層またはアルミニウムとチタンの合金層と、窒化チタン層またはチタン層とを積層した 3 層構造とすることが好ましい。

#### 【0098】

次いで、ゲート層 411 上にゲート絶縁層 402 を形成する。

#### 【0099】

ゲート絶縁層 402 は、プラズマ CVD 法又はスパッタリング法等を用いて、酸化シリ

50

コン層、窒化シリコン層、酸化窒化シリコン層、窒化酸化シリコン層、若しくは酸化アルミニウム層を単層で又は積層して形成することができる。例えば、成膜ガスとして、シラン( $\text{SiH}_4$ )、酸素及び窒素を用いてプラズマCVD法により酸化窒化シリコン層を形成すればよい。また、ゲート絶縁層402として酸化ハフニウム( $\text{HfO}_x$ )、酸化タンタル( $\text{TaO}_x$ )等のHigh-k材料を用いることもできる。ゲート絶縁層402の膜厚は、100nm以上500nm以下とし、積層の場合は、例えば、膜厚50nm以上200nm以下の第1のゲート絶縁層と、第1のゲート絶縁層上に膜厚5nm以上300nm以下の第2のゲート絶縁層とを積層して形成する。

#### 【0100】

ここでは、ゲート絶縁層402としてプラズマCVD法により膜厚100nm以下の酸化窒化シリコン層を形成する。

#### 【0101】

また、ゲート絶縁層402として、高密度プラズマ装置を用い、酸化窒化シリコン層の形成を行ってもよい。ここで高密度プラズマ装置とは、 $1 \times 10^{11} / \text{cm}^3$ 以上のプラズマ密度を達成できる装置を指している。例えば、3kW~6kWのマイクロ波電力を印加してプラズマを発生させて、絶縁層の成膜を行う。

#### 【0102】

チャンバーに材料ガスとしてシラン( $\text{SiH}_4$ )、亜酸化窒素( $\text{N}_2\text{O}$ )、及び希ガスを導入し、10Pa~30Paの圧力下で高密度プラズマを発生させてガラス等の絶縁表面を有する基板上に絶縁層を形成する。その後、シラン( $\text{SiH}_4$ )の供給を停止し、大気に曝すことなく亜酸化窒素( $\text{N}_2\text{O}$ )と希ガスを導入して絶縁層表面にプラズマ処理を行ってもよい。少なくとも亜酸化窒素( $\text{N}_2\text{O}$ )と希ガスを導入して絶縁層表面に行われるプラズマ処理は、絶縁層の成膜より後に行う。上記プロセス順序を経た絶縁層は、膜厚が薄く、例えば100nm未満であっても信頼性を確保することができる絶縁層である。

#### 【0103】

ゲート絶縁層402の形成の際、チャンバーに導入するシラン( $\text{SiH}_4$ )と亜酸化窒素( $\text{N}_2\text{O}$ )の流量比は、1:10から1:200の範囲とする。また、チャンバーに導入する希ガスとしては、ヘリウム、アルゴン、クリプトン、キセノンなどを用いることができるが、中でも安価であるアルゴンを用いることが好ましい。

#### 【0104】

また、高密度プラズマ装置により得られた絶縁層は、一定した厚さの膜形成ができるため段差被覆性に優れている。また、高密度プラズマ装置により得られる絶縁層は、薄い膜の厚みを精密に制御することができる。

#### 【0105】

上記プロセス順序を経た絶縁層は、従来の平行平板型のPCVD装置で得られる絶縁層とは大きく異なっており、同じエッチャントを用いてエッチング速度を比較した場合において、平行平板型のPCVD装置で得られる絶縁膜の10%以上または20%以上遅く、高密度プラズマ装置で得られる絶縁層は緻密な膜と言える。

#### 【0106】

なお、後の工程でi型化又は実質的にi型化される酸化物半導体(高純度化された酸化物半導体)は界面準位、界面電荷に対して極めて敏感であるため、ゲート絶縁層との界面は重要である。そのため高純度化された酸化物半導体に接するゲート絶縁層は、高品質化が要求される。従ってμ波(2.45GHz)を用いた高密度プラズマCVD装置は、緻密で絶縁耐圧の高い高品質な絶縁膜を形成できるので好ましい。高純度化された酸化物半導体と高品質ゲート絶縁層が密接することにより、界面準位を低減して界面特性を良好なものとすることができますからである。ゲート絶縁層としての膜質が良好であることは勿論のこと、酸化物半導体との界面準位密度を低減し、良好な界面を形成できることが重要である。

#### 【0107】

次いで、ゲート絶縁層402上に、膜厚2nm以上200nm以下の酸化物半導体膜4

10

20

30

40

50

30を形成する。なお、酸化物半導体膜430をスパッタ法により成膜する前に、アルゴンガスを導入してプラズマを発生させる逆スパッタを行い、ゲート絶縁層402の表面に付着している粉状物質(パーティクル、ゴミともいう)を除去することが好ましい。逆スパッタとは、ターゲット側に電圧を印加せずに、アルゴン雰囲気下で基板側にRF電源を用いて電圧を印加して基板近傍にプラズマを形成して表面を改質する方法である。なお、アルゴン雰囲気に代えて窒素、ヘリウム、酸素などを用いてもよい。

#### 【0108】

酸化物半導体膜430は、In-Ga-Zn-O系、In-Sn-O系、In-Sn-Zn-O系、In-Al-Zn-O系、Sn-Ga-Zn-O系、Al-Ga-Zn-O系、Sn-Al-Zn-O系、In-Zn-O系、In-Ga-O系、Sn-Zn-O系、Al-Zn-O系、In-O系、Sn-O系、Zn-O系の酸化物半導体膜を用いる。

ここでは、酸化物半導体膜430として、In-Ga-Zn-O系金属酸化物ターゲットを用いてスパッタ法により成膜する。この段階での断面図が図7(A)に相当する。また、酸化物半導体膜430は、希ガス(代表的にはアルゴン)雰囲気下、酸素雰囲気下、又は希ガス(代表的にはアルゴン)及び酸素の混合雰囲気下においてスパッタ法により形成することができる。また、スパッタ法を用いる場合、 $\text{SiO}_2$ を2重量%以上10重量%以下含むターゲットを用いて成膜を行い、酸化物半導体膜430に結晶化を阻害する $\text{SiO}_x$ ( $X > 0$ )を含ませ、後の工程で行う脱水化または脱水素化のための加熱処理の際に結晶化してしまうのを抑制することが好ましい。

#### 【0109】

ここでは、In、Ga、及びZnを含む金属酸化物ターゲット( $\text{In}_2\text{O}_3 : \text{Ga}_2\text{O}_3 : \text{ZnO} = 1 : 1 : 1$ [mol]、 $\text{In} : \text{Ga} : \text{Zn} = 1 : 1 : 0.5$ [atom])を用いて、基板とターゲットとの間との距離を100mm、圧力0.2Pa、直流(DC)電源0.5kW、アルゴン及び酸素(アルゴン:酸素=30sccm:20sccm、酸素流量比率40%)雰囲気下で成膜する。なお、パルス直流(DC)電源を用いると、成膜時に発生する粉状物質が軽減でき、膜厚分布も均一となるために好ましい。In-Ga-Zn-O系膜の膜厚は、5nm以上200nm以下とする。ここでは、酸化物半導体膜として、In-Ga-Zn-O系金属酸化物ターゲットを用いてスパッタ法により膜厚20nmのIn-Ga-Zn-O系膜を成膜する。また、In、Ga、及びZnを含む金属酸化物ターゲットとして、 $\text{In} : \text{Ga} : \text{Zn} = 1 : 1 : 1$ [atom]、又は $\text{In} : \text{Ga} : \text{Zn} = 1 : 1 : 2$ [atom]の組成比を有する金属酸化物ターゲットを用いることもできる。

#### 【0110】

スパッタ法にはスパッタ用電源に高周波電源を用いるRFスパッタ法とDCスパッタ法があり、さらにパルス的にバイアスを与えるパルスDCスパッタ法もある。RFスパッタ法は主に絶縁膜を成膜する場合に用いられ、DCスパッタ法は主に金属膜を成膜する場合に用いられる。

#### 【0111】

また、材料の異なるターゲットを複数設置できる多元スパッタ装置もある。多元スパッタ装置は、同一チャンバーで異なる材料膜を積層成膜することも、同一チャンバーで複数種類の材料を同時に放電させて成膜することもできる。

#### 【0112】

また、チャンバー内部に磁石機構を備えたマグнетロンスパッタ法を用いるスパッタ装置や、グロー放電を使わずマイクロ波を用いて発生させたプラズマを用いるECRスパッタ法を用いるスパッタ装置がある。

#### 【0113】

また、スパッタ法を用いる成膜方法として、成膜中にターゲット物質とスパッタガス成分とを化学反応させてそれらの化合物薄膜を形成するリアクティブスパッタ法や、成膜中に基板にも電圧をかけるバイアススパッタ法もある。

#### 【0114】

10

20

30

40

50

次いで、酸化物半導体膜430を第2のフォトリソグラフィ工程により島状の酸化物半導体層に加工する。また、当該工程において用いられるレジストマスクは、インクジェット法によって形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

#### 【0115】

次いで、酸化物半導体層の脱水化または脱水素化を行う。脱水化または脱水素化を行う第1の加熱処理の温度は、400以上750以下、好ましくは400以上基板の歪み点未満とする。ここでは、加熱処理装置の一つである電気炉に基板を導入し、酸化物半導体層に対して窒素雰囲気下450において1時間の加熱処理を行った後、大気に触れることなく、酸化物半導体層への水や水素の再混入を防ぎ、酸化物半導体層431を得る(図7(B)参照)。

10

#### 【0116】

なお、加熱処理装置は電気炉に限らず、抵抗発熱体などの発熱体からの熱伝導または熱輻射によって、被処理物を加熱する装置を備えていてもよい。例えば、GRTA(Gas Rapid Thermal Anneal)装置、LRTA(Lamp Rapid Thermal Anneal)装置等のRTA(Rapid Thermal Anneal)装置を用いることができる。LRTA装置は、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧水銀ランプなどのランプから発する光(電磁波)の輻射により、被処理物を加熱する装置である。GRTA装置は、高温のガスを用いて加熱処理を行う装置である。気体には、アルゴンなどの希ガス、または窒素のような、加熱処理によって被処理物と反応しない不活性気体が用いられる。

20

#### 【0117】

例えば、第1の加熱処理として、650～700の高温に加熱した不活性ガス中に基板を移動させて入れ、数分間加熱した後、基板を移動させて高温に加熱した不活性ガス中から出すGRTAを行ってもよい。GRTAを用いると短時間での高温加熱処理が可能となる。

30

#### 【0118】

なお、第1の加熱処理においては、窒素、またはヘリウム、ネオン、アルゴン等の希ガスに、水、水素などが含まれないことが好ましい。または、加熱処理装置に導入する窒素、またはヘリウム、ネオン、アルゴン等の希ガスの純度を、6N(99.9999%)以上、好ましくは7N(99.99999%)以上、(即ち不純物濃度を1ppm以下、好ましくは0.1ppm以下)とすることが好ましい。

#### 【0119】

また、酸化物半導体層の第1の加熱処理は、島状の酸化物半導体層に加工する前の酸化物半導体膜430に対して行うこともできる。その場合には、第1の加熱処理後に、加熱装置から基板を取り出し、第2のフォトリソグラフィ工程を行う。

#### 【0120】

酸化物半導体層に対する脱水化または脱水素化の加熱処理は、酸化物半導体層の形成後、酸化物半導体層上にソース層及びドレイン層を積層させた後、ソース層及びドレイン層上に保護絶縁膜を形成した後、のいずれで行っても良い。

40

#### 【0121】

また、ゲート絶縁層402に開口部を形成する場合、その工程は酸化物半導体膜430に脱水化または脱水素化処理を行う前でも行った後に行ってもよい。

#### 【0122】

なお、ここでの酸化物半導体膜430のエッティングは、ウェットエッティングに限定されずドライエッティングを用いてもよい。

#### 【0123】

ドライエッティングに用いるエッティングガスとしては、塩素を含むガス(塩素系ガス、例えば塩素(Cl<sub>2</sub>)、三塩化硼素(BCl<sub>3</sub>)、四塩化シリコン(SiCl<sub>4</sub>)、四塩化

50

炭素 (CCL<sub>4</sub>) など) が好ましい。

【0124】

また、フッ素を含むガス (フッ素系ガス、例えば四弗化炭素 (CF<sub>4</sub>)、六弗化硫黄 (SF<sub>6</sub>)、三弗化窒素 (NF<sub>3</sub>)、トリフルオロメタン (CHF<sub>3</sub>) など)、臭化水素 (HBr)、酸素 (O<sub>2</sub>)、これらのガスにヘリウム (He) やアルゴン (Ar) などの希ガスを添加したガス、などを用いることができる。

【0125】

ドライエッティング法としては、平行平板型 RIE (Reactive Ion Etching) 法や、ICP (Inductive Coupled Plasma : 誘導結合型プラズマ) エッティング法を用いることができる。所望の加工形状にエッティングできるように、エッティング条件 (コイル型の電極に印加される電力量、基板側の電極に印加される電力量、基板側の電極温度等) を適宜調節する。

10

【0126】

ウェットエッティングに用いるエッティング液としては、磷酸と酢酸と硝酸を混ぜた溶液などを用いることができる。また、ITO 07N (関東化学社製) を用いてもよい。

【0127】

また、ウェットエッティング後のエッティング液はエッティングされた材料とともに洗浄によって除去される。その除去された材料を含むエッティング液の廃液を精製し、含まれる材料を再利用してもよい。当該エッティング後の廃液から酸化物半導体層に含まれるインジウム等の材料を回収して再利用することにより、資源を有効活用し低コスト化することができる。

20

【0128】

所望の加工形状にエッティングできるように、材料に合わせてエッティング条件 (エッティング液、エッティング時間、温度等) を適宜調節する。

【0129】

次いで、ゲート絶縁層 402、及び酸化物半導体層 431 上に、金属導電膜を形成する。金属導電膜はスパッタ法や真空蒸着法で形成すればよい。金属導電膜の材料としては、アルミニウム (Al)、クロム (Cr)、銅 (Cu)、タンタル (Ta)、チタン (Ti)、モリブデン (Mo)、タンクステン (W) から選ばれた元素、上述した元素を成分とする合金、又は上述した元素を組み合わせた合金等が挙げられる。また、マンガン (Mn)、マグネシウム (Mg)、ジルコニア (Zr)、ベリリウム (Be)、イットリウム (Y) のいずれか一または複数から選択された材料を用いてもよい。また、金属導電膜は、単層構造でも、2層以上の積層構造としてもよい。例えば、シリコンを含むアルミニウム膜の単層構造、銅又は銅を主成分とする膜の単層構造、アルミニウム膜上にチタン膜を積層する2層構造、窒化タンタル膜又は窒化銅膜上に銅膜を積層する2層構造、チタン膜上にアルミニウム膜を積層し、さらにアルミニウム膜上にチタン膜を積層する3層構造などが挙げられる。また、アルミニウム (Al) に、チタン (Ti)、タンタル (Ta)、タンクステン (W)、モリブデン (Mo)、クロム (Cr)、ネオジム (Nd)、スカンジウム (Sc) から選ばれた元素を単数、又は複数組み合わせた膜、合金膜、もしくは窒化膜を用いてもよい。

30

【0130】

金属導電膜形成後に加熱処理を行う場合には、この加熱処理に耐えうる耐熱性を金属導電膜に持たせることが好ましい。

40

【0131】

第3のフォトリソグラフィ工程により金属導電膜上にレジストマスクを形成し、選択的にエッティングを行ってソース層 415a、ドレイン層 415b を形成した後、レジストマスクを除去する (図 7 (C) 参照)。

【0132】

なお、金属導電膜のエッティングの際に、酸化物半導体層 431 は除去されないようにそれぞれの材料及びエッティング条件を適宜調節する。

50

## 【0133】

ここでは、金属導電膜としてチタン膜を用いて、酸化物半導体層431にはIn-Ga-Zn-O系酸化物を用いて、エッチャントとしてアンモニア過水（アンモニア、水、過酸化水素水の混合液）を用いる。

## 【0134】

なお、第3のフォトリソグラフィ工程では、酸化物半導体層431は一部のみがエッチングされ、溝部（凹部）を有する酸化物半導体層となることもある。また、当該工程において用いるレジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

## 【0135】

また、フォトリソグラフィ工程で用いるフォトマスク数及び工程数を削減するため、透過した光が複数の強度となる露光マスクである多階調マスクによって形成されたレジストマスクを用いてエッチング工程を行ってもよい。多階調マスクを用いて形成したレジストマスクは複数の膜厚を有する形状となり、アッシングを行うことでさらに形状を変形することができるため、異なるパターンに加工する複数のエッチング工程に用いることができる。よって、一枚の多階調マスクによって、少なくとも二種類以上の異なるパターンに対応するレジストマスクを形成することができる。よって露光マスク数を削減することができ、対応するフォトリソグラフィ工程も削減できるため、工程の簡略化が可能となる。

10

## 【0136】

次いで、亜酸化窒素（N<sub>2</sub>O）、窒素（N<sub>2</sub>）、またはアルゴン（Ar）などのガスを用いたプラズマ処理を行う。このプラズマ処理によって露出している酸化物半導体層の表面に付着した吸着水などを除去する。また、酸素とアルゴンの混合ガスを用いてプラズマ処理を行ってもよい。

20

## 【0137】

プラズマ処理を行った後、大気に触れることなく、酸化物半導体層の一部に接する保護絶縁膜となる酸化物絶縁層416を形成する。

## 【0138】

酸化物絶縁層416は、少なくとも1nm以上の膜厚とし、スパッタ法など、酸化物絶縁層416に水、水素等の不純物を混入させない方法を適宜用いて形成することができる。酸化物絶縁層416に水素が含まれると、その水素が酸化物半導体層へ侵入して酸化物半導体層431のバックチャネルが低抵抗化（N型化）してしまい、寄生チャネルが形成される恐れがある。よって、酸化物絶縁層416はできるだけ水素を含まない膜になるように、成膜方法に水素を用いないことが重要である。

30

## 【0139】

ここでは、酸化物絶縁層416として膜厚200nmの酸化シリコン膜をスパッタ法を用いて成膜する。成膜時の基板温度は、室温以上300以下とすればよく、ここでは100とする。酸化シリコン膜のスパッタ法による成膜は、希ガス（代表的にはアルゴン）雰囲気下、酸素雰囲気下、または希ガス（代表的にはアルゴン）及び酸素雰囲気下において行うことができる。また、ターゲットとして酸化シリコンターゲットまたはシリコンターゲットを用いることができる。例えば、シリコンターゲットを用いて、酸素、及び窒素雰囲気下でスパッタ法により酸化シリコン膜を形成することができる。

40

## 【0140】

次いで、不活性ガス雰囲気下、または酸素ガス雰囲気下で第2の加熱処理（好ましくは200以上400以下、例えば250以上350以下）を行う。例えば、窒素雰囲気下で250、1時間の第2の加熱処理を行う。第2の加熱処理を行うと、酸化物半導体層の一部（チャネル形成領域）が酸化物絶縁層416と接した状態で加熱される。これにより、酸化物半導体層の一部（チャネル形成領域）に酸素が供給される。

## 【0141】

以上の工程を経ることによって、酸化物半導体層に対して脱水化または脱水素化のための加熱処理を行った後、酸化物半導体層の一部（チャネル形成領域）を選択的に酸素過剰

50

な状態とする。その結果、ゲート層 411 と重なるチャネル形成領域 413 は I 型となり、ソース層 415a に重なるソース領域 414a と、ドレイン層 415b に重なるドレイン領域 414b とが自己整合的に形成される。以上の工程でトランジスタ 410 が形成される。

#### 【0142】

85、 $2 \times 10^6$  V/cm、12 時間のゲートバイアス・熱ストレス試験（BT 試験）においては、不純物（水素等）が酸化物半導体に存在していると、不純物と酸化物半導体の主成分との結合手が、強電界（B：バイアス）と高温（T：温度）により切断され、生成された未結合手がしきい値電圧（Vth）のドリフトを誘発することとなる。これに対して、酸化物半導体の不純物、特に水素や水等を極力除去し、上述の高密度プラズマ CVD 装置を用いて緻密で絶縁耐圧の高い高品質な絶縁膜を形成し、酸化物半導体との界面特性を良好にすることにより、BT 試験に対しても安定なトランジスタを得ることができる。

10

#### 【0143】

さらに大気中、100 以上 200 以下、1 時間以上 30 時間以下の加熱処理を行ってもよい。ここでは 150 で 10 時間加熱処理を行う。この加熱処理は一定の加熱温度を保持して加熱してもよいし、室温から、100 以上 200 以下の加熱温度への昇温と、加熱温度から室温までの降温を複数回くりかえして行ってもよい。また、この加熱処理を、酸化物絶縁膜の形成前に、減圧下で行ってもよい。減圧下で加熱処理を行うと、加熱時間を短縮することができる。この加熱処理によって、酸化物半導体層から酸化物絶縁層中に水素をとりこむことができる。

20

#### 【0144】

なお、ドレイン層 415b と重畠した酸化物半導体層においてドレイン領域 414b を形成することにより、トランジスタの信頼性の向上を図ることができる。具体的には、ドレイン領域 414b を形成することで、ドレイン層 415b からドレイン領域 414b、チャネル形成領域 413 にかけて、導電性を段階的に変化させうるような構造とすることができる。

20

#### 【0145】

また、酸化物半導体層におけるソース領域又はドレイン領域は、酸化物半導体層の膜厚が 15 nm 以下と薄い場合は膜厚方向全体にわたって形成されるが、酸化物半導体層の膜厚が 30 nm 以上 50 nm 以下とより厚い場合は、酸化物半導体層の一部、ソース層又はドレイン層と接する領域及びその近傍が低抵抗化しソース領域又はドレイン領域が形成され、酸化物半導体層においてゲート絶縁層に近い領域は I 型とすることもできる。

30

#### 【0146】

酸化物絶縁層 416 上にさらに保護絶縁層を形成してもよい。例えば、RF スパッタ法を用いて窒化シリコン膜を形成する。RF スパッタ法は、量産性がよいため、保護絶縁層の成膜方法として好ましい。保護絶縁層は、水分や、水素イオンや、OH<sup>-</sup>などの不純物を含まず、これらが外部から侵入することをブロックする無機絶縁膜を用い、窒化シリコン膜、窒化アルミニウム膜、窒化酸化シリコン膜、酸化窒化アルミニウムなどを用いる。ここでは、保護絶縁層として保護絶縁層 403 を、窒化シリコン膜を用いて形成する（図 7 (D) 参照）。

40

#### 【0147】

（アクティブラトリクス型の表示装置を搭載した各種電子機器について）

以下では、本明細書で開示される表示装置を搭載した電子機器の例について図 8 を参照して説明する。

#### 【0148】

図 8 (A) は、ノート型のパーソナルコンピュータを示す図であり、本体 2201、筐体 2202、表示部 2203、キーボード 2204 などによって構成されている。

#### 【0149】

図 8 (B) は、携帯情報端末 (PDA) を示す図であり、本体 2211 には表示部 22

50

13と、外部インターフェイス2215と、操作ボタン2214等が設けられている。また、操作用の付属品としてスタイラス2212がある。

#### 【0150】

図8(C)は、電子ペーパーの一例として、電子書籍2220を示す図である。電子書籍2220は、筐体2221および筐体2223の2つの筐体で構成されている。筐体2221および筐体2223は、軸部2237により一体とされており、該軸部2237を軸として開閉動作を行うことができる。このような構成により、電子書籍2220は、紙の書籍のように用いることが可能である。

#### 【0151】

筐体2221には表示部2225が組み込まれ、筐体2223には表示部2227が組み込まれている。表示部2225および表示部2227は、続き画面を表示する構成としてもよいし、異なる画面を表示する構成としてもよい。異なる画面を表示する構成として、例えば右側の表示部(図8(C)では表示部2225)に文章を表示し、左側の表示部(図8(C)では表示部2227)に画像を表示することができる。

10

#### 【0152】

また、図8(C)では、筐体2221に操作部などを備えた例を示している。例えば、筐体2221は、電源2231、操作キー2233、スピーカー2235などを備えている。操作キー2233により、頁を送ることができる。なお、筐体の表示部と同一面にキーボードやポインティングデバイスなどを備える構成としてもよい。また、筐体の裏面や側面に、外部接続用端子(イヤホン端子、USB端子、またはACアダプタおよびUSBケーブルなどの各種ケーブルと接続可能な端子など)、記録媒体挿入部などを備える構成としてもよい。さらに、電子書籍2220は、電子辞書としての機能を持たせた構成としてもよい。

20

#### 【0153】

また、電子書籍2220は、無線で情報を送受信できる構成としてもよい。無線により、電子書籍サーバから、所望の書籍データなどを購入し、ダウンロードする構成とともに可能である。

#### 【0154】

なお、電子ペーパーは、情報を表示するものであればあらゆる分野に適用することが可能である。例えば、電子書籍以外にも、ポスター、電車などの乗り物の車内広告、クレジットカード等の各種カードにおける表示などに適用することができる。

30

#### 【0155】

図8(D)は、携帯電話機を示す図である。当該携帯電話機は、筐体2240および筐体2241の二つの筐体で構成されている。筐体2241は、表示パネル2242、スピーカー2243、マイクロフォン2244、ポインティングデバイス2246、カメラ用レンズ2247、外部接続端子2248などを備えている。また、筐体2240は、当該携帯電話機の充電を行う太陽電池セル2249、外部メモリスロット2250などを備えている。また、アンテナは筐体2241内部に内蔵されている。

#### 【0156】

表示パネル2242はタッチパネル機能を備えており、図8(D)には映像表示されている複数の操作キー2245を点線で示している。なお、当該携帯電話は、太陽電池セル2249から出力される電圧を各回路に必要な電圧に昇圧するための昇圧回路を実装している。また、上記構成に加えて、非接触ICチップ、小型記録装置などを内蔵した構成とすることもできる。

40

#### 【0157】

表示パネル2242は、使用形態に応じて表示の方向が適宜変化する。また、表示パネル2242と同一面上にカメラ用レンズ2247を備えているため、テレビ電話が可能である。スピーカー2243およびマイクロフォン2244は音声通話に限らず、テレビ電話、録音、再生などが可能である。さらに、筐体2240と筐体2241はスライドし、図8(D)のように展開している状態から重なり合った状態とすることができる、携帯に適

50

した小型化が可能である。

【0158】

外部接続端子2248はACアダプタやUSBケーブルなどの各種ケーブルと接続可能であり、充電やデータ通信が可能になっている。また、外部メモリスロット2250に記録媒体を挿入し、より大量のデータの保存および移動に対応できる。また、上記機能に加えて、赤外線通信機能、テレビ受信機能などを備えたものであってもよい。

【0159】

図8(E)は、デジタルカメラを示す図である。当該デジタルカメラは、本体2261、表示部(A)2267、接眼部2263、操作スイッチ2264、表示部(B)2265、バッテリー2266などによって構成されている。

10

【0160】

図8(F)は、テレビジョン装置を示す図である。テレビジョン装置2270では、筐体2271に表示部2273が組み込まれている。表示部2273により、映像を表示することが可能である。なお、ここでは、スタンド2275により筐体2271を支持した構成を示している。

20

【0161】

テレビジョン装置2270の操作は、筐体2271が備える操作スイッチや、別体のリモコン操作機2280により行うことができる。リモコン操作機2280が備える操作キー2279により、チャンネルや音量の操作を行うことができ、表示部2273に表示される映像を操作することができる。また、リモコン操作機2280に、当該リモコン操作機2280から出力する情報を表示する表示部2277を設ける構成としてもよい。

20

【0162】

なお、テレビジョン装置2270は、受信機やモ뎀などを備えた構成とするのが好適である。受信機により、一般的のテレビ放送の受信を行うことができる。また、モ뎀を介して有線または無線による通信ネットワークに接続することにより、一方向(送信者から受信者)または双方向(送信者と受信者間、あるいは受信者間同士など)の情報通信を行うことが可能である。

【符号の説明】

【0163】

|      |         |    |

|------|---------|----|

| 101  | 画素部     | 30 |

| 102  | 信号線駆動回路 |    |

| 103  | 走査線駆動回路 |    |

| 104  | 信号線     |    |

| 105  | 走査線     |    |

| 107  | 画素      |    |

| 111  | トランジスタ  |    |

| 112  | 容量素子    |    |

| 113  | 液晶素子    |    |

| 120  | 基板      |    |

| 121  | ゲート層    | 40 |

| 122  | ゲート絶縁層  |    |

| 123  | 酸化物半導体層 |    |

| 124a | ソース層    |    |

| 124b | ドレイン層   |    |

| 125  | 絶縁層     |    |

| 126  | 保護絶縁層   |    |

| 400  | 基板      |    |

| 402  | ゲート絶縁層  |    |

| 403  | 保護絶縁層   |    |

| 410  | トランジスタ  | 50 |

|         |              |    |

|---------|--------------|----|

| 4 1 1   | ゲート層         |    |

| 4 1 3   | チャネル形成領域     |    |

| 4 1 4 a | ソース領域        |    |

| 4 1 4 b | ドレイン領域       |    |

| 4 1 5 a | ソース層         |    |

| 4 1 5 b | ドレイン層        |    |

| 4 1 6   | 酸化物絶縁層       |    |

| 4 3 0   | 酸化物半導体膜      |    |

| 4 3 1   | 酸化物半導体層      |    |

| 5 1 0   | トランジスタ       | 10 |

| 5 1 1   | 絶縁層          |    |

| 5 2 0   | トランジスタ       |    |

| 5 3 0   | トランジスタ       |    |

| 5 3 1   | 絶縁層          |    |

| 5 3 2 a | 配線層          |    |

| 5 3 2 b | 配線層          |    |

| 6 0 0   | コントローラ       |    |

| 6 0 1   | データ信号生成回路    |    |

| 6 0 2   | 駆動信号生成回路     |    |

| 6 0 3   | 基準クロック信号生成回路 | 20 |

| 6 0 4   | 分周回路         |    |

| 6 0 5   | スイッチ         |    |

| 6 0 6   | スイッチ         |    |

| 8 0 0   | 測定系          |    |

| 8 0 2   | 容量素子         |    |

| 8 0 4   | トランジスタ       |    |

| 8 0 5   | トランジスタ       |    |

| 8 0 6   | トランジスタ       |    |

| 8 0 8   | トランジスタ       |    |

| 2 2 0 1 | 本体           | 30 |

| 2 2 0 2 | 筐体           |    |

| 2 2 0 3 | 表示部          |    |

| 2 2 0 4 | キーボード        |    |

| 2 2 1 1 | 本体           |    |

| 2 2 1 2 | スタイルス        |    |

| 2 2 1 3 | 表示部          |    |

| 2 2 1 4 | 操作ボタン        |    |

| 2 2 1 5 | 外部インターフェイス   |    |

| 2 2 2 0 | 電子書籍         |    |

| 2 2 2 1 | 筐体           | 40 |

| 2 2 2 3 | 筐体           |    |

| 2 2 2 5 | 表示部          |    |

| 2 2 2 7 | 表示部          |    |

| 2 2 3 1 | 電源           |    |

| 2 2 3 3 | 操作キー         |    |

| 2 2 3 5 | スピーカー        |    |

| 2 2 3 7 | 軸部           |    |

| 2 2 4 0 | 筐体           |    |

| 2 2 4 1 | 筐体           |    |

| 2 2 4 2 | 表示パネル        | 50 |

|         |             |    |

|---------|-------------|----|

| 2 2 4 3 | スピーカー       |    |

| 2 2 4 4 | マイクロフォン     |    |

| 2 2 4 5 | 操作キー        |    |

| 2 2 4 6 | ポインティングデバイス |    |

| 2 2 4 7 | カメラ用レンズ     |    |

| 2 2 4 8 | 外部接続端子      |    |

| 2 2 4 9 | 太陽電池セル      |    |

| 2 2 5 0 | 外部メモリスロット   |    |

| 2 2 6 1 | 本体          | 10 |

| 2 2 6 3 | 接眼部         |    |

| 2 2 6 4 | 操作スイッチ      |    |

| 2 2 6 5 | 表示部 (B)     |    |

| 2 2 6 6 | バッテリー       |    |

| 2 2 6 7 | 表示部 (A)     |    |

| 2 2 7 0 | テレビジョン装置    |    |

| 2 2 7 1 | 筐体          |    |

| 2 2 7 3 | 表示部         |    |

| 2 2 7 5 | スタンド        |    |

| 2 2 7 7 | 表示部         |    |

| 2 2 7 9 | 操作キー        | 20 |

| 2 2 8 0 | リモコン操作機     |    |

【図1】

(A)

(B)

(C)

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図 1 1】

【図 1 2】

【図 1 3】

【図 1 4】

---

フロントページの続き

(51) Int.Cl.

F I

テーマコード(参考)

|         |       |         |

|---------|-------|---------|

| G 0 9 G | 3/20  | 6 2 4 D |

| G 0 9 G | 3/20  | 6 1 1 E |

| G 0 9 G | 3/20  | 6 8 0 H |

| G 0 2 F | 1/133 | 5 5 0   |

F ターム(参考) 5C006 AA14 AA16 AC24 AC25 AC26 AC28 AF72 BB15 BC03 BC05

BC11 FA04 FA16 FA18 FA23 FA36

5C080 AA10 BB05 DD06 FF11 JJ02 JJ04 JJ05 JJ06 KK02 KK07

KK43 KK47 KK50