(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5633885号

(P5633885)

(45) 発行日 平成26年12月3日(2014.12.3)

(24) 登録日 平成26年10月24日(2014.10.24)

(51) Int.Cl.

F 1

|             |           |            |   |

|-------------|-----------|------------|---|

| HO1L 23/538 | (2006.01) | HO1L 23/52 | A |

| HO1L 25/065 | (2006.01) | HO1L 25/08 | Y |

| HO1L 25/07  | (2006.01) |            |   |

| HO1L 25/18  | (2006.01) |            |   |

請求項の数 33 (全 25 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2010-538299 (P2010-538299)  |

| (86) (22) 出願日 | 平成20年12月18日 (2008.12.18)      |

| (65) 公表番号     | 特表2011-507283 (P2011-507283A) |

| (43) 公表日      | 平成23年3月3日 (2011.3.3)          |

| (86) 國際出願番号   | PCT/CA2008/002235             |

| (87) 國際公開番号   | W02009/079772                 |

| (87) 國際公開日    | 平成21年7月2日 (2009.7.2)          |

| 審査請求日         | 平成23年12月12日 (2011.12.12)      |

| (31) 優先権主張番号  | 61/015,345                    |

| (32) 優先日      | 平成19年12月20日 (2007.12.20)      |

| (33) 優先権主張国   | 米国(US)                        |

| (31) 優先権主張番号  | 61/032,203                    |

| (32) 優先日      | 平成20年2月28日 (2008.2.28)        |

| (33) 優先権主張国   | 米国(US)                        |

|           |                                                                                                                                                              |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 508034325<br>コンバーサント・インテレクチュアル・プロパティ・マネジメント・インコーポレイテッド<br>CONVERSANT INTELLECTUAL PROPERTY MANAGEMENT INC.<br>カナダ・オンタリオ・K2K・OG7・オタワ・マーチ・ロード・390・スイート<br>・100 |

| (74) 代理人  | 100153811<br>弁理士 青山 高弘                                                                                                                                       |

| (74) 代理人  | 100199277<br>弁理士 西守 有人                                                                                                                                       |

最終頁に続く

(54) 【発明の名称】直列接続された集積回路を積層する方法およびその方法で作られたマルチチップデバイス

## (57) 【特許請求の範囲】

## 【請求項1】

直列接続された集積回路を形成するように複数のチップを積層する方法であつて、前記複数のチップは、実質的に同一のパッドの配列および配置となつてあり、前記方法は、

第1および第2のチップのそれぞれを貫通するチップバイアホールを作成するステップと、

前記チップバイアホールの中に絶縁層を配置するステップと、スルーバイア接続を形成するように前記チップバイアホールの中に導体を配置するステップと、

集積回路チップの積層ペアを形成するように前記第1のチップの上面に前記第2のチップを配置するステップと

を有し、

前記第1および第2のチップは、

前記第1のチップのトランジスタ配置面が前記第2のチップから見て遠方に向いているとともに、前記第2のチップのトランジスタ配置面が前記第1のチップから見て遠方に向いており、

前記第1のチップの信号パッドと前記第2のチップの信号パッドとの間の少なくとも1つの直列接続が前記スルーバイア接続によって形成されるように、構成される、方法。

## 【請求項2】

前記第1および第2のチップは、前記第1のチップの信号パッドと前記第2のチップの信号パッドとの間の少なくとも1つの並列接続が前記スルーバイア接続によって形成されるように、さらに構成される、請求項1に記載の方法。

【請求項3】

前記チップバイアホールを作成するステップは、第2のチップのコモン接続信号パッドと第1のチップの複製コモン接続信号パッドとの間の並列接続を促進するための第1のスルーチップバイアホールを作成するステップ、を含む、請求項2に記載の方法。

【請求項4】

前記チップバイアホールを作成するステップは、前記第1のチップの出力信号パッドと前記第2のチップの対応する入力信号パッドとの間の接続を促進するためのスルーチップバイアホールおよびスルーパッドバイアホールを作成するステップを含む、請求項1に記載の方法。

10

【請求項5】

前記第1のチップのトランジスタ配置面に絶縁層を堆積させるステップと、

前記第1のチップの信号パッドへの接続を可能とするために、前記絶縁層の中にコンタクトホールを形成するステップと、

前記コンタクトホールの中に導体を堆積させるステップと、

前記コンタクトホールの外側の部分から余分な導体材料を除去するために、導体層をエッチングするステップと、

マルチチップパッケージのためのマルチチップ回路を形成するように、集積回路チップの前記積層ペアの前記第1のチップに、集積回路チップの第2の積層ペアを取り付けるステップであって、集積回路チップの前記第2の積層ペアは、集積回路チップの第1の積層ペアと実質的に同一である、ステップと

20

をさらに含む、請求項1に記載の方法。

【請求項6】

前記複数の実質的に同一のチップへのアクセスを制御するためのメモリコントローラを備えるステップと、

前記マルチチップ回路の入力信号パッドを、前記コントローラの出力側に接続するステップと、

前記マルチチップ回路の出力信号パッドを前記コントローラの入力側に接続するステップと、をさらに含む、請求項5に記載の方法。

30

【請求項7】

マルチチップデバイスを作成する方法であって、

ラスト積層ペアを含む複数の集積回路チップの少なくとも2つの積層ペアを形成するステップと、

前記ラスト積層ペア以外の各積層ペアについて、マルチチップ回路を形成するステップと、

前記マルチチップ回路の入力信号パッドをコントローラの出力側に接続するため、および前記マルチチップ回路の出力信号パッドを前記コントローラの入力側に接続するためには、

40

ワイヤボンディングを付加するステップと

を有し、

前記少なくとも2つの積層ペアを形成するステップは、

第1および第2のチップのそれぞれを貫通するチップバイアホールを作成するステップと、

前記チップバイアホールの中に絶縁層を配置するステップと、

スルーバイア接続を形成するように前記チップバイアホールの中に導体を配置するステップと、

集積回路チップの積層ペアを形成するように前記第1のチップの上面に前記第2のチップを配置するステップと

を含み、

50

前記第1および第2のチップは、

前記第1および第2のチップが実質的に同一のパッドの配列となっており、

前記第1のチップのトランジスタ配置面が前記第2のチップから見て外方に向いているとともに、前記第2のチップのトランジスタ配置面が前記第1のチップから見て外方に向いている、

ように構成され、

前記第1のチップの信号パッドと前記第2のチップの信号パッドとの間の少なくとも1つの直列接続が前記スルーバイア接続によって形成され、

前記マルチチップ回路を形成するステップは、

集積回路チップの前記積層ペアの上面に絶縁層を堆積させるステップと、

10

別のチップが後で上面に置かれるとき、ある隣接する信号パッドの間の接続を可能とするために、前記絶縁層の中にコンタクトホールを形成するステップと、

前記コンタクトホールの中に導体を堆積させるステップと、

前記コンタクトホールの外側の部分から余分な導体材料を除去するために、導体層をエッチングするステップと、

マルチチップ回路を形成するために、集積回路の前記積層ペアの上面に、次の積層ペアを取り付けるステップと

を含む、方法。

【請求項8】

前記第1および第2のチップは、前記第1のチップの信号パッドと前記第2のチップの信号パッドとの間の少なくとも1つの並列接続が前記スルーバイア接続によって形成されるように、さらに構成されている、請求項7に記載の方法。

20

【請求項9】

パッケージまたは複合体の全体を覆うステップをさらに含む、請求項7に記載の方法。

【請求項10】

集積回路チップの積層ペアを含むマルチチップデバイスを有する装置であって、

前記集積回路チップの積層ペアは、

第1のチップと、第2のチップと、少なくとも1つの直列接続スルーチップバイアとを含み、

前記第1のチップは、

30

少なくとも1つの外部入力信号ための接続部である少なくとも1つの入力信号パッドと

、前記少なくとも1つの入力信号パッドに関して前記第1のチップのセンターラインを中心に対称に配置された少なくとも1つの出力信号パッドと

を有し、

前記第2のチップは、

前記第1のチップに構成されたものと実質的に同一の信号パッドを有し、前記第2のチップは、前記第1のチップの向きとは反対の向きにされており、

前記少なくとも1つの直列接続スルーチップバイアは、前記第2のチップの前記少なくとも1つの入力信号パッドと直列に前記第1のチップの前記少なくとも1つの出力信号パッドを接続している、装置。

40

【請求項11】

前記第1のチップは、複製コモン接続信号パッドに関して前記第1のチップのセンターラインを中心に対称に配置されたコモン接続パッドをさらに有し、

前記装置は、さらに、

上部チップのコモン接続信号パッドと並列に前記第2のチップの複製コモン接続信号パッドを接続している少なくとも1つの並列接続スルーチップバイアを有する、請求項10に記載の装置。

【請求項12】

前記少なくとも1つの入力信号パッドおよび前記少なくとも1つの出力信号パッドは、

50

前記第1のチップの单一の縁部に沿って配置されている、請求項10に記載の装置。

【請求項13】

前記少なくとも1つのコモン接続信号パッドは、前記第1のチップの单一の縁部に沿って配置されている、請求項12に記載の装置。

【請求項14】

少なくとも1つの第1のチップコモン接続信号パッドと並列に前記第2のチップ上の複製コモン接続信号パッドを接続している少なくとも1つの並列接続スルーチップバイアをさらに有する、請求項12に記載の装置。

【請求項15】

前記第1のチップの单一の縁部は、前記第2のチップの対応する縁部と垂直に並んでいる、請求項12に記載の装置。 10

【請求項16】

前記第1のチップの前記少なくとも1つの入力信号パッドは、前記第1のチップの前記センターラインの第1のサイドに配置されており、

前記第1のチップの前記少なくとも1つの出力信号パッドは、前記第1のサイドの反対側である前記第1のチップの前記センターラインの第2のサイドに配置されている、請求項10に記載の装置。

【請求項17】

前記第1のチップおよび前記第2のチップは、実質的にオフセットがないように位置合わせされている、請求項10に記載の装置。 20

【請求項18】

前記第1のチップの前記少なくとも1つの出力信号パッドは、前記第2のチップの前記少なくとも1つの入力信号パッドと実質的に位置合わせされている、請求項10に記載の装置。

【請求項19】

マルチチップデバイスを有する装置であって、

前記マルチチップデバイスは、積層された複数の実質的に同一のチップを有し、

前記複数のチップは、第1のチップと、偶数の数の中間チップと、ラストチップとを含み、

前記複数のチップのそれぞれは、

1つ以上の入力信号パッドと、

各入力信号パッドに関して前記チップのセンターラインを中心に対称に配置された1つ以上の出力信号パッドと

を有し、

前記中間チップのそれぞれの前記入力信号パッドは、1つ以上の第1の直列接続によって第1の隣接チップの対応する出力信号パッドに直列に接続されており、

前記中間チップのそれぞれの前記出力信号パッドは、1つ以上の第2の直列接続によって第2の隣接チップの対応する入力信号パッドに直列に接続されており、

前記第1の直列接続および前記第2の直列接続の一方は、スルーチップバイアを有し、

前記第1の直列接続および前記第2の直列接続の他方は、信号パッドを有し、 40

前記第1のチップの前記入力信号パッドは、1つ以上の外部入力信号パッドに直列に接続されており、

前記第1のチップの前記出力信号パッドは、スルーチップバイアを有する1つ以上の直列接続によって隣接チップの対応する出力信号パッドに直列に接続されており、

前記ラストチップの前記入力信号パッドは、スルーチップバイアを有する1つ以上の直列接続によって隣接チップの対応する出力信号パッドに直列に接続されており、

前記ラストチップの前記出力信号パッドは、1つ以上の外部出力信号パッドに直列に接続されており、

前記複数の実質的に同一のチップは、積層に構成されており、前記積層の構成における交互のチップは、隣接するチップの向きとは反対の向きにされている、装置。 50

## 【請求項 2 0】

前記複数の実質的に同一のチップのそれぞれは、1つ以上のコモン接続信号パッドを有し、

それぞれの前記コモン接続信号パッドは、複製コモン接続信号パッドに関して前記チップのセンターラインを中心に対称に配置されており、

前記コモン接続信号パッドは、外部コモン信号に接続されており、

前記装置は、さらに、

各チップ上の対応するコモン接続信号パッドを並列に共通に接続している並列接続スルーチップバイアを有する、請求項 1 9 に記載の装置。

## 【請求項 2 1】

10

前記偶数の数の中間チップは、多数の中間チップを有し、

前記多数の中間チップは、複数の隣接中間チップの1つ以上の入力信号パッドのそれぞれ接続された前記1つ以上の出力信号パッドを有する、請求項 1 9 に記載の装置。

## 【請求項 2 2】

選択された隣接パッド間の接触を防止するために、隣接中間チップのパッド間に配置された絶縁体さらに有する、請求項 1 9 に記載の装置。

## 【請求項 2 3】

前記並列接続スルーチップバイアは、前記絶縁体を貫通して延びるとともに、前記中間チップの前記対応するコモン接続信号パッドを貫通して延びる、請求項 2 2 に記載の装置。

20

## 【請求項 2 4】

前記中間チップのうちの1つの前記1つ以上の出力信号パッドを、隣接する中間チップの1つ以上の入力信号パッドにそれぞれ接続するために、前記絶縁体を貫通して延びるスルーパッドバイアをさらに有する、請求項 2 2 に記載の装置。

## 【請求項 2 5】

前記複数の実質的に同一のチップへのアクセスを制御するためのコントローラと、

出力信号パッドを、前記ラストチップから前記コントローラの入力側まで接続するためのコントローラ入力接続と、

前記コントローラの出力側を、前記第 1 のチップの前記入力パッドに接続するためのコントローラ出力接続と

30

をさらに有する、請求項 2 2 に記載の装置。

## 【請求項 2 6】

前記コントローラは前記積層チップの下に配置され、前記コントローラの出力接続はワイヤボンディングを有する、請求項 2 5 に記載の装置。

## 【請求項 2 7】

前記コントローラは前記積層チップの上に配置され、前記コントローラの入力接続はワイヤボンディングを有する、請求項 2 5 に記載の装置。

## 【請求項 2 8】

マルチチップデバイスを有する装置であって、

前記マルチチップデバイスは、複数の実質的に同一のチップと、少なくとも1つの直列スルーチップバイアとを有し、

40

前記複数の実質的に同一のチップは、第 1 のチップおよびラストチップを含み、前記実質的に同一のチップは積層されており、前記第 1 のチップおよびラストチップは、実質的に同一の信号パッド構成を有し、前記ラストチップは、前記第 1 のチップの向きとは反対の向きにされており、

前記少なくとも1つの直列スルーチップバイアは、前記第 1 のチップの少なくとも1つの出力信号パッドと前記ラストチップの各入力信号パッドとの間の通信のためのものである、装置。

## 【請求項 2 9】

前記第 1 のチップ上の少なくとも1つのコモン接続信号パッドを前記ラストチップ上の

50

少なくとも 1 つの複製コモン接続信号パッドに接続するための少なくとも 1 つの並列スルーチップバイアをさらに有する請求項 2 8 に記載の装置。

【請求項 3 0】

マルチチップデバイスを有する装置であって、

前記マルチチップデバイスは、複数の実質的に同一のチップと、少なくとも 1 つの直列スルーチップバイアと、少なくとも 1 つの直列接続とを有し、

前記複数の実質的に同一のチップは、第 1 のチップと、偶数の数の中間チップと、ラストチップとを含み、前記マルチチップデバイスにおける前記複数のチップのそれぞれは、実質的に同一の信号パッド構成を有し、前記複数のチップは、積層に構成されており、前記積層の構成における交互のチップは、隣接するチップの向きとは反対の向きにされており、

前記少なくとも 1 つの直列接続は、前記中間チップの 2 つの出力信号パッドと入力信号パッドとの間を接続している、装置。

【請求項 3 1】

少なくとも 1 つの並列スルーチップバイアをさらに有する請求項 3 0 に記載の装置。

【請求項 3 2】

マルチチップパッケージと、少なくとも 1 つの直列スルーチップバイアと、少なくとも 1 つの直列接続と、パッケージ入力コネクタと、パッケージ出力コネクタとを有する装置であって、

前記マルチチップパッケージは、複数の実質的に同一のチップと、偶数の数の中間チップと、ラストチップとを有し、前記マルチチップパッケージの各チップは、実質的に同一の信号パッド構成を有し、前記マルチチップパッケージの複数のチップは、積層に構成されており、前記積層の構成における交互のチップは、隣接するチップの向きとは反対の向きにされており、

前記少なくとも 1 つの直列接続は、前記中間チップの 2 つの出力信号パッドと入力信号パッドとの間を接続しており、

前記パッケージ入力コネクタは、外部入力信号のための接続部であり、

前記パッケージ出力コネクタは、外部出力信号のための接続部である、装置。

【請求項 3 3】

少なくとも 1 つの並列スルーチップバイアをさらに有する請求項 3 2 に記載の装置。

30

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

関連出願の相互参照

本出願は、参照により本明細書にその全体が組み込まれている、2007年12月20日に出願した米国仮出願第61/015345号、2008年2月28日に出願した米国仮出願第61/032203号、2008年7月7日に出願した米国特許出願第12/168354号、および2008年9月24日に出願した米国特許出願第12/236874号の優先権の利益を主張するものである。

【0 0 0 2】

本発明は、一般に集積回路またはチップに関するものである。より詳細には、本発明はチップを積層するためのチップ接続の配列に関するものである。

40

【背景技術】

【0 0 0 3】

本出願は、先に出願した、参照により本明細書にその全体の教示が組み込まれている2005年12月30日に出願した「Multiple Independent Serial Link Memory」という名称の米国特許出願第11/324023号に関する。

【0 0 0 4】

本出願は、先に出願した、参照により本明細書にその全体の教示が組み込まれている2006年11月8日に出願した「Daisy Chain Cascading Devices」という名称の米国一部継続出願第11/594564号に関する。

50

## 【0005】

本出願は、先に出願した、参照により本明細書にその全体の教示が組み込まれている2007年12月12日に出願した「Memory System With Point-To-Point Ring Topology」という名称の米国仮出願第61/013036号に関する。

## 【0006】

本出願は、先に出願した、参照により本明細書にその全体の教示が組み込まれている2007年12月20日に出願した「Method For Stacking Serially-Connected Integrated Circuits And Multi-Chip Device Made From Same」という名称の米国仮出願第61/015345号に関する。

## 【0007】

単一のパッケージに複数のチップを集積することは、市販の製品の体積とコストを削減するための、半導体産業における主要な傾向となっている。これまで、多くのマルチチップのパッケージング方法が紹介され、実際の製品において使用されてきた。

## 【0008】

チップ密度が高まったので、チップのパッケージング自体が、寸法およびピン総数において、著しく変化した。メモリチップの高密度およびスマートフォームファクタの問題によれば、MCP(マルチチップパッケージ)は、任意のシステムをよりコンパクトにするのに、よい解決策である。これまででは、大多数のチップ積層が、ワイヤボンディング技術でなされてきた。しかし、ワイヤボンディング技術は、ボンディングワイヤで接続されるべき各チップ上に、従来のボンディングパッドと同じだけのスペースを必要とする。

## 【0009】

MCPを作るために、より複雑なリードフレームが必要である。また、各チップは、十分な間隔を持つように配置されなければならず、その結果、フォームファクタが増加する。ボンディングワイヤ技術はまた、ワイヤがいろいろな角度を成すため、MCPの機械的耐久性を減ずる可能性がある。

## 【0010】

さらに、ワイヤボンディングは、各チップに対してスペーサを必要とする。このことが、積層体の高さを増加させ、そのことが、スペーサを備えない積層体と比較して、集積化されたデバイスの積層体の取扱いおよび組立てを、より困難にする。また、スペーサを有するチップ積層体の中では、ボンドワイヤの長さがより長く、そのことが、チップ積層体システムの電気的性能の低下を引き起こす。さらに、集積化されたデバイスチップ内にスペーサを有する、集積化されたデバイス積層体の熱抵抗が、増加する。

## 【0011】

従来の集積化されたデバイス積層体は、スペーサ材料を付着する間、および集積化されたデバイスをスペーサ材料上に位置決めする間に、ボンドワイヤの電気的短絡を引き起こす傾向がある。このことが、信頼性および生産の歩留まりを低下させる。従来のボンディングワイヤに基づくダイ積層は、コンパクトなパッケージングを提供しない。大きな負荷効果はまた、ワイヤ長さおよび接続レイアウトに起因する。

## 【0012】

他の手法は、チップ間にバイアを使用することである。スルーチップバイアは、電気的特性によるノイズの問題を解決するための、よりよい手法でありうる。

## 【0013】

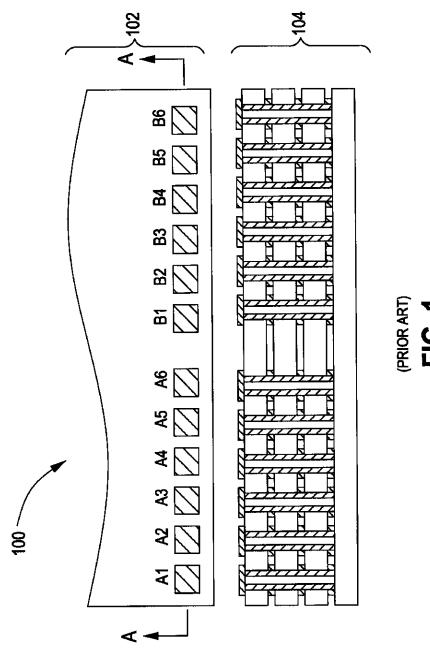

図1は、スルーチップバイア技術を使用して作られた、従来のマルチチップ積層体またはマルチチップデバイス100の部分的な上面図102および断面図104を示す。上面図102において、複数の信号パッドA1～A6およびB1～B6が示され、それらのパッドは、内部信号および外部信号のチップとの接続を容易にする。バイア自体は、上面図では見えない。断面図104は、上面図の線A-Aに沿って取られたものである。図1で使用されるスルーチップバイア法は、コモン入力接続またはコモン出力接続、あるいは並列接続に関連する。このため、唯一の現実の作製問題は、いかに深く、障害物のない孔を穿孔し、コモン接続として同じピンを互いに接続させることができるかであった。同じメモリチップ間のマルチドロッ

10

20

30

40

50

プ接続の場合、各チップの位置合わせが非常に重要なので、マルチチップパッケージングのためのボンディングワイヤ接続で必要なパッドスペーサなしで、全チップが位置合わせされる。

#### 【0014】

他の知られている手法は、チップ間の並列接続のための、スルーチップバイアの使用を対象にする。例えば、米国特許出願第2007/0246257号は、メモリチップが、マルチドロップ技術におけるシリコン基板貫通バイアで接続されるメモリ回路を記載している。しかし、この手法では、バイアは、積層体の全メモリチップを貫通して延び、したがって、提供されうる接続性の種類が限定される。

#### 【先行技術文献】

10

#### 【特許文献】

#### 【0015】

【特許文献1】米国仮出願第61/015345号明細書

【特許文献2】米国仮出願第61/032203号明細書

【特許文献3】米国特許出願第12/168354号明細書

【特許文献4】米国特許出願第12/236874号明細書

【特許文献5】米国特許出願第11/324023号明細書

【特許文献6】米国一部継続出願第11/594564号明細書

【特許文献7】米国仮出願第61/013036号明細書

【特許文献8】米国仮出願第61/015345号明細書

20

【特許文献9】米国特許出願第2007/0246257号明細書

【特許文献10】米国特許出願第2007/0076479号明細書

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0016】

したがって、信号性能を向上させるために、スルーチップバイアを使用し、デイジーチェーン接続用の他の接続をもたらす、マルチチップパッケージまたはチップの積層体を提供することが望ましい。

#### 【課題を解決するための手段】

#### 【0017】

30

従来のマルチチップデバイスの少なくとも1つの欠点を取り除くかまたは緩和することが、本発明の目的である。

#### 【0018】

第1の態様において、本発明は、上部チップおよび下部チップを備える集積回路チップの積層ペアを含む、マルチチップデバイスを提供する。上部チップは、外部入力信号との接続用の1つまたは複数の入力信号パッドと、1つまたは複数のコモン接続信号パッドとを有する。各コモン接続信号パッドは、複製コモン接続信号パッドに対して、上部チップの中心線の上または周りに対称に配置される。1つまたは複数の出力信号パッドは、それぞれの入力信号パッドに対して、上部チップの中心線周りに対称に配置される。下部チップは、上部チップと実質的に同一の信号パッド配列を有し、上部チップに対して向きが裏返されている。デバイスは、上部チップのコモン接続信号パッドを、その複製コモン接続信号パッドと並列に接続する、並列接続スルーチップバイアを含む。デバイスはまた、上部チップ出力信号パッドを、下部チップ上のそのそれぞれの入力信号パッドと直列に接続する、直列接続スルーチップバイアを含む。

40

#### 【0019】

1つまたは複数の入力信号パッドと、1つまたは複数のコモン接続信号パッドと、1つまたは複数の出力信号パッドとが、上部チップの単一の縁部に沿って配置されうる。1つまたは複数の入力信号パッドが、上部チップの中心線の同じ側に配置されうる。デバイスは、上部チップの出力信号パッドを、下部チップ上のそれらそれぞれの入力信号パッドと直列に接続する、複数の直接接続スルーチップバイア、および/または上部チップのコモン

50

接続信号パッドを、下部チップ上のそれら複製コモン接続信号パッドと並列に接続する、複数の並列接続スルーチップバイアを、さらに含むことができる。

#### 【0020】

一実施形態において、積層チップは、実質的にオフセットがないように位置合わせされる。例えば、上部チップの縁部は、下部チップの対応する縁部と垂直に並ぶことができる。他の実施形態において、積層チップは、互いに同じ方向を向く。例えば、選択された信号パッドを有する第1のチップの側は、同じ選択された信号パッドを有する第2のチップの側と同じ方向を向くことができる。

#### 【0021】

他の態様において、本発明は、上部チップと、偶数の中間チップと、下部チップとを含む、複数の実質的に同一のチップを備えるマルチチップデバイスを提供する。各チップは、1つまたは複数の信号パッドと、1つまたは複数のコモン接続信号パッドとを含む。各コモン接続信号パッドは、複製コモン接続信号パッドに対して、チップの中心線の上または周りに対称に配置される。1つまたは複数の出力信号パッドは、それぞれの入力信号パッドに対して、チップの中心線周りに対称に配置される。並列接続スルーチップバイアは、各チップ上の対応するコモン接続信号パッドを共に、並列に接続する。直列接続スルーチップバイアは、1つのチップ上の1つの出力信号パッドを、別のチップ上の、そのそれぞれの入力信号パッドと直列に接続する。

#### 【0022】

この同じ態様において、上部チップは、外部入力信号と接続するための1つまたは複数の入力信号パッドと、外部コモン信号と接続するためのコモン接続信号パッドと、隣接するチップのそれぞれの入力信号パッドに接続される1つまたは複数の出力信号パッドとを有する。下部チップは、外部出力信号と接続するための1つまたは複数の出力信号パッドと、外部コモン信号と接続するためのコモン接続信号パッドと、隣接するチップのそれぞれの出力信号パッドに接続される1つまたは複数の入力信号パッドとを有する。中間チップのうちの少なくとも1つは、隣接する中間チップのそれぞれの1つまたは複数の入力信号パッドに直列に接続された1つまたは複数の出力信号パッドを有する。複数の実質的に同一のチップは、実質的に同一の信号パッド配列を有し、積層体の中に設けられる。積層体の中の交互のチップはそれぞれ、隣接するチップに対して向きが裏返されている。

#### 【0023】

偶数の数の中間チップは、複数の隣接する中間チップの、それぞれの1つまたは複数の入力信号パッドに接続された1つまたは複数の出力信号パッドを有する、偶数の多数の中間チップでありうる。デバイスは、選択された隣接するパッド間の接触を防ぐために、隣接する中間チップのパッドの間に配置された絶縁体を、さらに含むことができる。並列接続スルーチップバイアは、絶縁体を貫通して、また中間チップの対応するコモン接続信号パッドを貫通して延びることができる。スルーパッドバイアは、中間チップのうちの1つの、1つまたは複数の出力信号パッドを、隣接する中間チップのそれぞれの1つまたは複数の入力信号パッドに接続するために、絶縁体を貫通して延びることができる。

#### 【0024】

デバイスは、複数の実質的に同一のチップへのアクセスを制御するためのコントローラをさらに含むことができる。その場合、コントローラの入力接続は、出力信号パッドを、下部チップからコントローラの入力側まで接続するために備えられうる。コントローラの出力接続は、コントローラの出力側を、上部チップの入力パッドに接続するために備えられうる。コントローラは、積層チップの下方に置かれてよく、その場合、コントローラの出力接続は、ワイヤボンディングを備えることができ、または積層チップの上方に置かれてよく、その場合、コントローラの入力接続は、ワイヤボンディングを備えることができる。

#### 【0025】

さらなる態様において、本発明は、以下の段階、すなわち、下部チップになるように、トランジスタを載せる上面が第1の方向を向くように第1のチップを裏返す段階と、裏返さ

10

20

30

40

50

れた第1のチップの上面に第2のチップを置く段階であって、第2のチップがパッドの配列および配置において第1のチップと実質的に同一である、段階と、少なくとも1つの直列接続と少なくとも1つの並列接続を作成するために、上部チップの信号パッドを下部チップの対応する信号パッドに接続することを容易にするための、パッドとチップを貫通するバイアホールを作成する段階と、絶縁層をバイアホール内に配置する段階と、集積回路チップの積層ペアを作成するために、上部チップおよび下部チップの上のパッド間にスルーバイア接続を作成するようにバイアホール内に導体を配置する段階とを含む、直列接続された集積回路を積層する方法を提供する。

【0026】

パッドとチップを貫通するバイアホールを作成する段階は、上部チップのコモン接続信号パッドを、その複製コモン接続信号パッドと並列に接続することを容易にする、第1の、スルーチップバイアホールとスルーパッドバイアホールとを作成する段階を含むことができる。パッドとチップを貫通するバイアホールを作成する段階は、上部チップの出力信号パッドを、下部チップ上のそのそれぞれの入力信号パッドと直列に接続することを容易にする、第2の、スルーチップバイアホールとスルーパッドバイアホールとを作成する段階を含むことができる。

【0027】

その方法は、以下の段階、すなわち、集積回路チップの積層ペアの上面に絶縁層を堆積させる段階と、別のチップが後で上面に置かれるときに、ある隣接する信号パッド間の接続を可能にするために、絶縁層の中にコンタクトホールを形成する段階と、コンタクトホール内に導体を堆積させる段階と、コンタクトホールの外側の部分から余分の導体材料を除去するために導体層をエッティングする段階と、マルチチップパッケージ用のマルチチップ回路を作成するために、2つの予め組み合わされたチップを集積回路チップの積層ペアの上面に取り付ける段階であって、2つの予め組み合わされたチップが、集積回路チップの積層ペアと実質的に同一である、段階とをさらに含むことができる。

【0028】

その方法は、以下の段階、すなわち、複数の実質的に同一のチップへのアクセスを制御するためのメモリコントローラを備える段階と、上部チップの入力信号パッドをコントローラの出力側に接続する段階と、出力信号パッドを下部チップからコントローラの入力側まで接続する段階とをさらに含むことができる。

【0029】

他の態様において、本発明は、上部チップおよび下部チップを含む複数の実質的に同一のチップを備えるマルチチップデバイスを提供する。上部チップおよび下部チップは、実質的に同一の信号パッド配列を有し、下部チップは、上部チップに対して向きが裏返されている。デバイスは、上部チップの少なくとも1つの出力信号パッドを、下部チップのそれぞれの入力信号パッドに接続するために、少なくとも1つの直列スルーチップバイアを含む。少なくとも1つの並列スルーチップバイアが、上部チップ上の少なくとも1つのコモン接続信号パッドを、下部チップ上の少なくとも1つの複製コモン接続信号パッドに接続するために、デバイスの中に設けられる。

【0030】

他の態様において、本発明は、上部チップと、偶数の数の中間チップと、下部チップとを含む複数の実質的に同一のチップを備えるマルチチップデバイスを提供する。デバイスの中の各チップは、実質的に同一の信号パッド配列を有する。チップは、積層体の中に設けられる。積層体の中の交互のチップはそれぞれ、隣接するチップに対して向きが裏返されている。デバイスは、少なくとも1つの並列スルーチップバイアと、少なくとも1つの直列スルーチップバイアと、2つの中間チップの出力パッドと入力パッドの間の少なくとも1つの直列接続とを、さらに含む。

【0031】

他の態様において、本発明は、上部チップと、偶数の数の中間チップと、下部チップとを含む複数の実質的に同一のチップを備えるマルチチップパッケージを提供する。チップ

10

20

30

40

50

は、積層体の中に設けられる。デバイスの中の各チップは、実質的に同一の信号パッド配列を有する。積層体の中の交互のチップはそれぞれ、隣接するチップに対して向きが裏返されている。デバイスはまた、2つの中間チップの出力信号パッドと入力信号パッドの間に、少なくとも1つの並列スルーチップバイアと、少なくとも1つの直列スルーチップバイアと、少なくとも1つの直列接続とを含む。デバイスは、外部入力信号との接続用のパッケージ入力コネクタと、外部出力信号との接続用のパッケージ出力コネクタとを、さらに含む。

【0032】

さらなる態様において、本発明は、以下の段階、すなわち、下部チップになるように、トランジスタを載せる上面が第1の方向を向くように第1のチップを裏返す段階と、裏返された第1のチップの上面に第2のチップを置く段階であって、第2のチップがパッド配列および配置において第1のチップと実質的に同一である段階と、少なくとも1つの直列接続と少なくとも1つの並列接続を作成するために、上部チップの信号パッドを下部チップの対応する信号パッドに接続することを容易にするための、パッドとチップを貫通するバイアホールを作成する段階と、絶縁層をバイアホール内に配置する段階と、集積回路チップの積層ペアを作成するために、上部チップおよび下部チップの上のパッド間にスルーバイア接続を作成するようにバイアホール内に導体を配置する段階とを含む、2対の積層チップを有するマルチチップデバイスを作製する方法を提供する。

【0033】

同じ態様において、方法は、集積回路チップの積層ペアの上面に絶縁層を堆積させる段階と、別のチップが後で上面に置かれるときに、ある隣接する信号パッド間の接続を可能にするために、絶縁層の中にコンタクトホールを形成する段階と、コンタクトホール内に導体を堆積させる段階と、コンタクトホールの外側の部分から余分の導体材料を除去するために導体層をエッティングする段階と、マルチチップ実装用のマルチチップ回路を作成するために、2つの予め組み合わされたチップを集積回路チップの積層ペアの上面に取り付ける段階であって、2つの予め組み合わされたチップが、集積回路チップの積層ペアと同一である段階と、上部チップの入力信号パッドをコントローラの出力側に接続するため、および出力信号パッドを下部チップからコントローラの入力側まで接続するためにワイヤボンディングを付加する段階と、パッケージまたは複合体の全体を覆う段階とをさらに含む。

【0034】

本発明の他の態様および特徴は、本発明の具体的な実施形態の詳細な説明を、添付の図面と併せ読めば、当業者には明らかとなろう。

【0035】

本発明の実施形態が、添付の図面を参照して、例示のみを目的として説明される。

【図面の簡単な説明】

【0036】

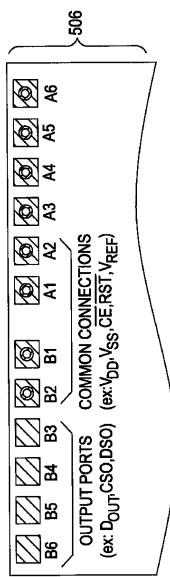

【図1】従来のマルチチップ積層体の部分的上面図および断面図である。

【図2】本発明の一実施形態による作製に適した例示的回路の概略図である。

【図3A】図2に示す回路の一実施形態を含む、簡略化された正投影法の、部分的上面図である。

【図3B】図2に示す回路の一実施形態を含む、簡略化された正投影法の、断面正面図である。

【図3C】図2に示す回路の一実施形態を含む、簡略化された正投影法の、部分的下面図である。

【図4】図3の実施形態の、他の簡略化された部分的上面図である。

【図5A】図2に示す回路の他の実施形態を含む、簡略化された正投影法の、部分的上面図である。

【図5B】図2に示す回路の他の実施形態を含む、簡略化された正投影法の、断面正面図である。

10

20

30

40

50

【図5C】図2に示す回路の他の実施形態を含む、簡略化された正投影法の、部分的下面図である。

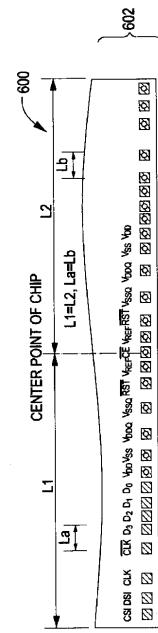

【図6A】図2の回路の実施形態の、詳細な部分的上面図である。

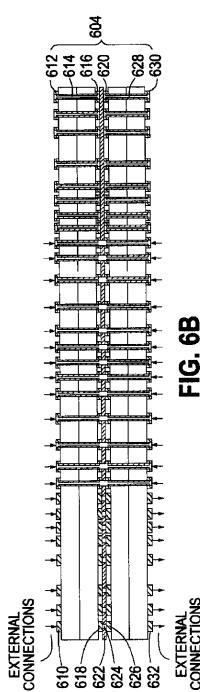

【図6B】図2の回路の実施形態の、詳細な断面正面図である。

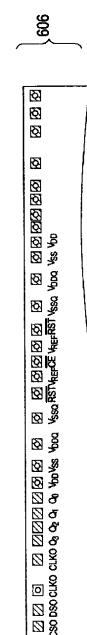

【図6C】図2の回路の実施形態の、詳細な部分的下面図である。

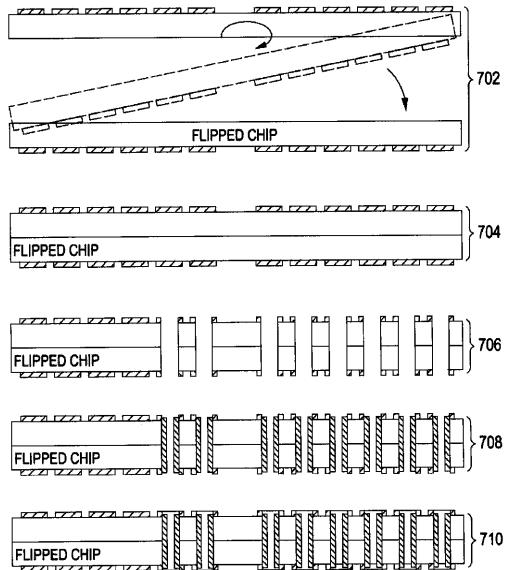

【図7】現在の技術による、図6に示す実施形態を作製する方法の段階を示す図である。

【図8】現在の技術による、図6に示す実施形態を作製する方法の段階を示す図である。

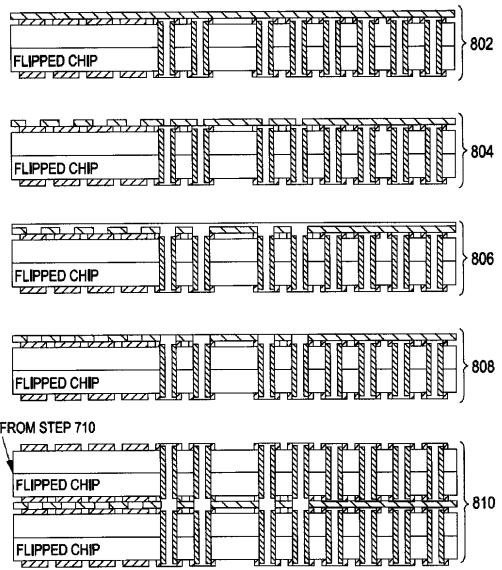

【図9】本発明の実施形態による他のマルチチップ回路の正面断面図である。

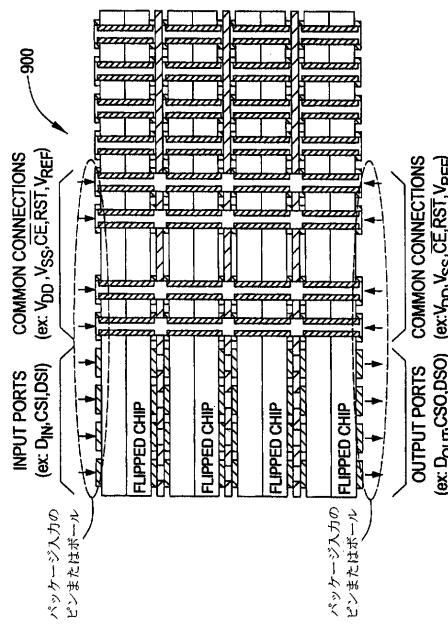

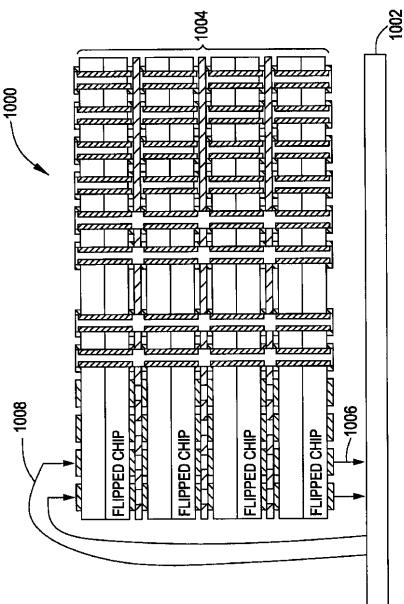

【図10】本発明の他の実施形態によるマルチチップパッケージの正面断面図である。

【発明を実施するための形態】

10

【0037】

一般に、本発明は、デバイスを製作するために複数の実質的に同一のチップを積層する、マルチチップデバイスおよび方法を提供する。マルチチップデバイスまたは回路は、少なくとも2つのチップからの信号パッドの間の並列接続をもたらす少なくとも1つのスルーチップバイアと、少なくとも2つのチップからの信号パッドの間の直列接続またはデイジーチェーン接続をもたらす少なくとも1つのスルーチップバイアとを含む。コモン接続信号パッドは、複製コモン信号パッドに対してチップの中心線周りに対称に配列される。入力信号パッドは、対応する出力信号パッドに対して、チップの中心線周りに対称に配置される。積層体の中のチップは、この配列をもたらすために、実質的に同一のチップが交互に裏返されたバージョンである。2つ以上のチップが積層されるとき、少なくとも1つの直列接続が、積層され、裏返されたチップの信号パッド間にもたらされる。

20

【0038】

スルーホールバイアの短い相互接続が、より小さいインダクタンス、キャパシタンス、およびレジスタンスをもたらし、それにより、MCPの信号強度は、ボンディングワイヤが使用されていた場合より良好である。このことに加えて、スペーサが使用されないことによる低い外形により、パッケージのサイズが、ボンディングワイヤを使用する等価なパッケージに比べて最小化されうる。

【0039】

本発明の一実施形態は、ボンディングワイヤの代わりにスルーチップバイアホールを使用して集積回路を積層する方法を提供する。

30

【0040】

マルチドロップの場合とは違って、単一のパッケージの中の直列に接続された複数の部品が、出力ポートと入力ポートの間を直列接続させるために、前のデバイスの出力を現在のデバイスの入力に接続する異なる手法を提供する。

【0041】

本発明の一実施形態は、直列接続されたマルチチップデバイスを作る方法を提供する。有利には、現在の技術は、スルーシリコンバイア法を使用して短線接続を作る方法を提供する。本明細書で使用される用語「直列接続」およびその変形は、デイジーチェーン接続またはリングトポロジー接続を容易にする任意の接続を示す。直列接続されたチップのリングトポロジーにおいて、最後のチップは、一巡してコントローラに戻ることができる。

40

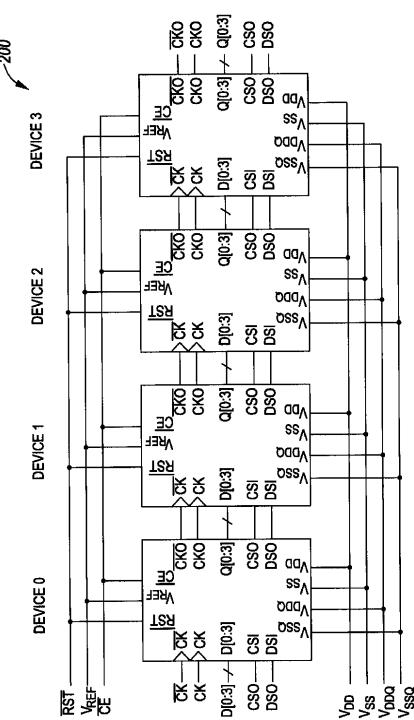

【0042】

次に図2を参照すると、直列接続された集積回路を含む回路200が概略的に示される。この回路200は、4チップのフラッシュメモリ回路を含み、便宜的に一例として使用される。現在の技術はまた、ダイナミックランダムアクセスメモリ(DRAM)、スタティックランダムアクセスメモリ(SRAM)、特定用途向け集積回路(ASIC)、中央処理ユニット(CPU)、または本明細書で以下に記載されるものに類似の直列接続トポロジーを有する、任意の他の種類のマルチチップ回路に適用可能である。

【0043】

回路200の中の各チップは、以下のような3つの接続信号の種類のうちの1つに分類される接続信号を含む：

50

コモン接続信号:

【0044】

【数1】

RST, CE

【0045】

、VREF、および電源(VDD、VSS、など)。

直列入力信号:

【0046】

10

【数2】

CK / CK

【0047】

、D[0:3]、CSI、およびDSI。

直列出力信号:

【0048】

【数3】

CKO / CKO

20

【0049】

、Q[0:3]、CS0、およびDS0。

言い換えれば、並列信号またはコモン接続信号のいくつかは、クロック、リセット、およびチップセレクトを含むことができる。図2に示す信号は例であり、信号の特性および接続の要件に基づいて、他の信号が、これらの群のうちの1つの中に適切に置かれることは、当業者には理解されよう。

【0050】

30

本発明の一実施形態は、並列接続クロックを有する。しかし、他の実施形態において、直列接続が、クロックのために使用される。電力は、並列でなければならない。入力および出力の信号、または信号パッドは、本発明の一実施形態による任意の種類のRAM、任意の論理回路に対して、またはCPUに対してさえ、デイジーチェーンで結ばれうる。

【0051】

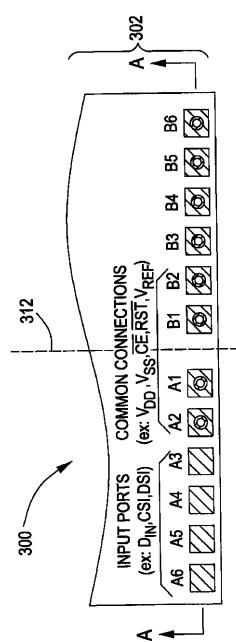

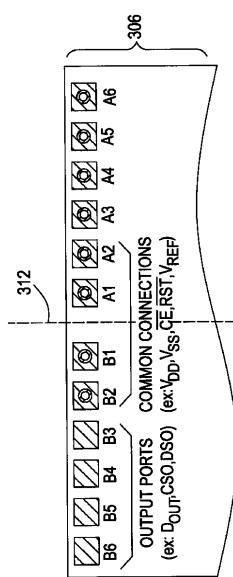

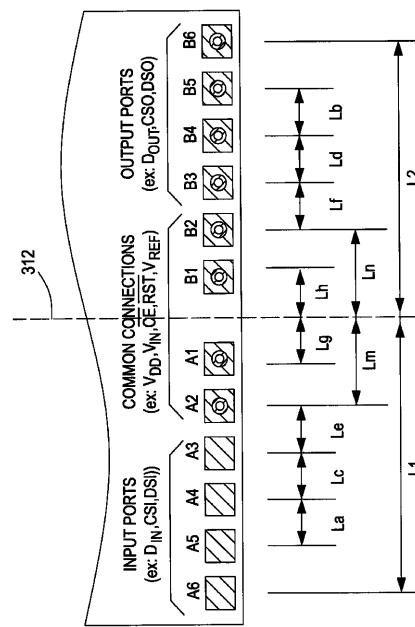

図3A～図3Cを参照すると、図2に示す回路200の一実施形態の部分的上面図302(図3A)、断面正面図304(図3B)、および部分的下面図306(図3C)を含む、簡略化された正投影法の図300が示される。簡明にするために、接続信号のサブセットだけを示す。この実施形態において、2つの実質的に同一のチップが、積層され、接続される。

【0052】

40

図3Aにおける線A-Aに手取られた断面図である図3Bに示すように、積層された集積回路のチップのうちの1対は、上部チップ308と下部チップ310とを含む。下部チップ310は、上部チップ308と実質的に同一の信号パッド配列を有し、上部チップに対して向きが裏返されている。図3Aおよび図3Cに示すように、各チップは、外部入力信号との接続のために、1つまたは複数の入力信号パッドA3～A6を含む。1つまたは複数のコモン接続信号パッドA1～A2が備えられ、各コモン接続信号パッドが、複製コモン信号パッドB1～B2に関して、上部チップの中心線312周りに、対称に配置される。1つまたは複数の出力信号パッドB3～B6が、それぞの、または対応する入力信号パッドA3～A6に関して、チップの中央線周りに、対称に配置される。

【0053】

図3Bに戻って参考すると、並列接続スルーチップバイア314は、上部チップのコモン接

50

続信号パッドを、その複製コモン接続信号パッドと並列に接続する。直列接続スルーチップバイア316が、上部チップの出力信号パッドを、下部チップ上のそのそれぞれの、または対応する入力信号パッドと直列に接続する。

【0054】

図3A～図3Cの異なる図302、304および306が共に並べられるとき、それらの図は、上部チップおよび下部チップの上のコモン接続パッドが、積層されるときに、いかにして互いに並ぶか、また上部チップの入力信号パッドが、下部チップ上のそれらに対応する出力信号パッドと、いかにして並ぶかを示す。このことは、互いに垂直に位置合わせされる、図302および306からのパッドを観察すると、特に明白となる。信号パッドの配列は、同じマルチチップパッケージの中で、並列接続と直列接続の両方、またはデイジーチェーン接続のために、スルーチップバイアを使用することを可能にする。

10

【0055】

一実施形態において、積層チップが、実質的にオフセットがないように位置合わせされる。例えば、上部チップの縁部が、下部チップの対応する縁部と、垂直に並ぶ。一実施形態において、上部チップの縁部のすべてが、下部チップの対応する縁部のすべてと、垂直に並ぶことができる。他の実施形態において、積層チップは、互いに同じ方向に向く。例えば、選択された信号パッドを有する第1のチップの1側面は、同じ選択された信号パッドを有する第2のチップの1側面と同じ方向を向く。また、上部チップおよび下部チップに関して説明したこれらの関係は、複数の積層チップを有する本発明の一実施形態における、隣接するチップを説明することができる。

20

【0056】

図4は、チップの中の信号パッド間の主要な幾何学的関係をより詳細に説明する図3A～図3Cに示す、本実施形態の他の部分的上面図を示す。チップ上のパッドの位置を特定することで、スルーチップバイアを使用して、実質的に同一の裏返されたチップとのデイジーチェーン接続および並列接続が可能になる。信号パッドA3～A6は、信号パッドB3～B6の、チップの中心線312周りの鏡像であり、その逆も成り立つ。信号パッドA3～A6およびB3～B6は、それぞれ、直列入力パッドおよび直列出力パッドでありうる。コモン接続パッドA1およびA2は複製されており、それらのそれぞれの複製であるB1およびB2の、チップの中心線周りの鏡像である。信号パッドA1およびB1は、互いに同じ信号を伝え、信号パッドA2およびB2は、互いに同じ信号を伝える。

30

【0057】

さらに、図4の実施形態でのパッド配列を説明すると、入力パッドA6は、チップの中心線からL1離れて備えられる。関連する、または対応する出力パッドB6は、チップの中心線からL2離れて備えられ、 $L1=L2$ である。同様に、コモン接続パッドA1およびA2は、中心線から、それぞれLgおよびLm離れて備えられ、それらの複製コモン接続パッドB1およびB2は、中心線から、それぞれLhおよびLn離れて備えられ、 $Lg=Lh$ および $Lm=Ln$ である。

【0058】

入力パッドA5は、入力パッドA4から距離Laだけ離れている。出力パッドB5は、出力パッドB4から距離Lbだけ離れており、LbはLaに等しい。同様に、図4に示す他のパッド間の距離に対して、 $Lc=Ld$ および $Le=Lf$ である。

40

【0059】

本発明の一実施形態により、2つのチップだけが積層されるとき、パッドの配置または配列においてある程度の柔軟性が存在する。図4に示す実施形態において、中心線の一方の側のパッドは、すべて入力であり、他方の側のパッドは、すべて出力である。他の実施形態において、入力ポートと出力ポートは、チップの中心線のいずれもの側すなわち両側に備えられうる。その場合、各入力ポートは、その対応する出力ポートから、中心線の反対側にあり、ペアを成す各入力ポートと出力ポートは、中心線から同じ距離だけ離れている。入力パッドと出力パッドは、共に群化されてよいが、各群におけるそれらの相対的な配置および間隔は、多重積層チップが存在するときほどには厳密に管理されない。

【0060】

50

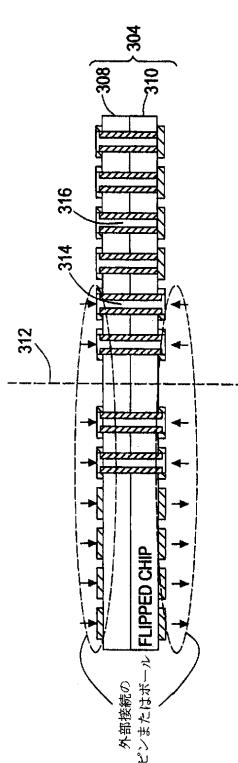

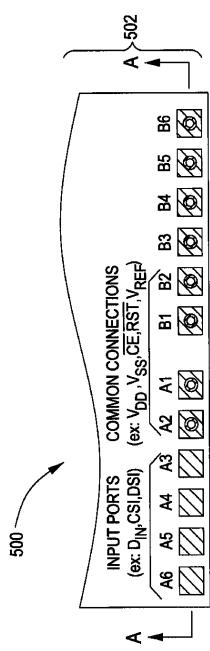

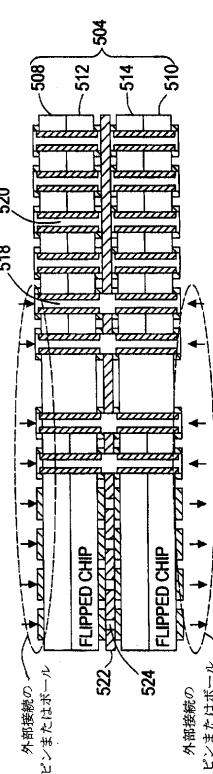

図5A～図5Cは、図2に示す回路200の他の実施形態の、部分的上面図502(図5A)、断面正面図504(図5B)、および部分的下面図(図5C)を含む、簡略化された正投影法の図500を示す。図5Bから明らかなように、この実施形態は、複数の積層チップのペアなど、マルチチップ回路またはパッケージの中の、偶数の多数のチップを示す。積層体の中の交互のチップはそれぞれ、隣接するチップに対して向きが裏替えされている。

#### 【0061】

図5Bに示す実施形態は、上部チップ508と、下部チップ510と、偶数の数の中間チップとを含む、複数の実質的に同一のチップを有する。この場合、第1の中間チップ512と第2の中間チップ514が存在する。積層体の中の各チップは、実質的に同一の信号パッド配列を有し、図3に関して説明したチップと類似の特性を有する。この実施形態において、マルチチップパッケージは、少なくとも1つの並列スルーチップバイアと、少なくとも1つの直列スルーチップバイアと、少なくとも1つの積層され裏返されたチップのパッド間の直列接続とを有する。

#### 【0062】

上部チップ508の入力信号パッドA3～A6、ならびにコモン接続信号パッドA1～A2およびB1からB2(図5Aに示す)は、それぞれ外部入力信号と外部コモン信号への接続用である。上部チップの出力信号パッドのうちの1つまたは複数のパッドは、以下により詳細に説明するように、隣接するチップのそれぞれの入力信号パッドに接続される。

#### 【0063】

下部チップ510の出力信号パッドB3～B6、ならびにコモン接続信号パッドA1～A2およびB1からB2(図5Cに示す)は、それぞれ外部出力信号と外部コモン信号への接続用である。下部チップの入力信号パッドのうちの1つまたは複数のパッドは、以下により詳細に説明するように、隣接するチップのそれぞれの出力信号パッドに接続される。

#### 【0064】

中間チップのうちの少なくとも1つのチップは、隣接する中間チップのそれぞれの1つまたは複数の入力信号パッドに接続された、その出力信号パッドのうちの1つまたは複数のパッドを有する。

#### 【0065】

図5Bに示す実施形態において、絶縁体522が、本来、互いに接触することのない隣接するパッド間の短絡を防止するために備えられる。絶縁体は、パッド間での接続が望まれない隣接パッドなど、選択された隣接パッド間の接触を防止するために、隣接する中間チップのパッド間に配置されうる。それぞれのチップからチップへのコモン接続が、同一直線上でパッド、チップおよび絶縁体を貫通するバイア518を使用して作られる。この場合の並列接続スルーチップバイアは、絶縁体522を貫通し、かつ中間チップの対応するコモン接続信号パッドを貫通して延びる。

#### 【0066】

出力ポートと入力ポートの間のそれぞれの直列接続は、スルーチップバイア520またはスルーパッドバイア524を使用して作られる。絶縁体が存在する中で接続を確保するために、スルーパッドバイア524が、中間チップの1つまたは複数の出力信号パッドを、隣接するチップのそれぞれの1つまたは複数の入力信号パッドに接続するために、絶縁体を貫通して延びる。前述の通り、直列接続は、デイジーチェーン接続またはループトポロジー接続を容易にすることができる。

#### 【0067】

絶縁体がない一実施形態(図示せず)において、入力および出力用のパッドは、積層体の中の「中間」チップ用の接続を作るために、互いに物理的に接触することができる。

#### 【0068】

スルーチップバイアを使用する直列接続に関して、積層体の中の最初の2つのデバイスの入力および出力が共に接続されるが、第2および第3のデバイスは、スルーチップバイアを使用して共に接続されることなく、第2および第3のデバイス間に絶縁が施される。次いで、第3および第4のデバイスが、スルーチップバイアを使用して共に接続される。絶縁

10

20

30

40

50

体を貫通して延びるスルーパッドバイアが、第2と第3のデバイスの間の所望の直列接続を作るために備えられる。

【0069】

積層体の中の上部チップおよび下部チップの上の入力ポートと出力ポートは、他のパッドと接続されることはなく、適当な外部接続と接続される。また、電力接続は、外部から引かれ、スルーチップバイアを使用して、積層体を貫通する直接並列接続を有する。

【0070】

また、コモン接続への外部接続が、積層体の上部チップおよび下部チップの両方の上に見られることに留意されたい。しかし、上部接続、下部接続、および上部と下部両者の接続の任意の有利な組合せは、現在の技術の範囲内にある。例えば、他の実施形態(図示せず)において、

【0071】

【数4】

CE, RST

【0072】

、およびVREFなどの信号は、単一の上部接続または下部接続を有する一方で、VDD、VSS、VDDQおよびVSSQなどの電源は、上部接続と下部接続の両方を有する。

【0073】

一態様において、本発明は、複数の実質的に同一のチップを備える、マルチチップデバイスを提供する。各チップは、1つまたは複数の接続信号パッドを含み、各信号パッドは、チップの中心線上に対称に配置されるか、または、複製コモン信号パッドに対して、チップの中心線周りに対称に配置される。また、1つまたは複数の入力信号パッドが、1つまたは複数の出力信号パッドと共に、各チップの中に設けられる。出力信号パッドが、それぞれの入力信号パッドに対してチップの中心線周りに対称に配置される。各チップ上の各コモン接続信号パッドが、同一直線上のスルーチップバイアにより、他のチップ上のそれぞれのコモン接続信号パッドに接続される。

【0074】

この態様において、複数の実質的に同一のチップが、上部チップおよび下部チップを含む。上部チップは、外部入力信号への接続用の1つまたは複数の入力信号パッドと、外部コモン信号への接続用のコモン接続信号と、隣接するチップのそれぞれの入力信号パッドに接続された、1つまたは複数の出力信号パッドとを有する。下部チップは、外部出力信号への接続用の1つまたは複数の出力信号パッドと、外部コモン信号への接続用のコモン接続信号と、隣接するチップのそれぞれの出力信号パッドに接続された1つまたは複数の入力信号パッドとを有する。偶数の数の中間チップは、隣接するチップのそれぞれの1つまたは複数の入力信号パッドに接続された、1つまたは複数の出力信号パッドを有する。

【0075】

図6A～6Cは、図2に示す回路200の一実施形態であるマルチチップパッケージ600の、詳細な部分的上面図602(図6A)と、断面正面図604(図6B)と、部分的下面図606(図6C)とを含む、簡略化された正投影法の図500を示す。接続信号のすべてを示す。チップの中心線上に

【0076】

【数5】

CE

【0077】

が対称に配置されるので、それは複製されない。上部チップ上の入力パッドCSI(コモンストローブ入力)と下部チップ上の出力ポートCS0(コモンストローブ出力)の間の例示的な

10

20

30

40

50

直列接続またはデイジーチェーン接続が、説明される。このことは、4チップ、または任意の6個以上の偶数個のチップを有する積層体の中の直列接続またはデイジーチェーン接続について、より詳細な内容を提供する。

【0078】

図6Bに示すように、外部接続が、上部チップ上のCSIパッド610の中にコモンストローブ入力信号を伝える。上部チップ内のCSOパッド612が、対応する出力信号を伝える。スルーチップバイア614が、CSOパッド612から出力を取り入れ、その出力を、第1の中間チップのCSIパッド616に入力として接続し、第1の中間チップ内のCSOパッド618が、出力信号を伝える。

【0079】

第2の中間チップのCSOパッド620が、絶縁体622により、第1の中間チップのCSIパッド616から離隔され、積層体の中のこれら2つの隣接するパッド間の接続が防止される。スルーパッドバイア624が、第1の中間チップのCSOパッド618から出力を取り入れ、その出力を、第2の中間チップのCSIパッド626に、入力として接続する。第2の中間チップ内のCSOパッド620が、対応する出力信号を伝える。

【0080】

スルーチップバイア628が、CSOパッド620から出力を取り入れ、その出力を、下部チップのCSIパッド630に、入力として接続する。下部チップの中のCSOパッド632は、出力信号を外部接続に伝える。

【0081】

一実施形態において、コモン接続パッドは、1つまたは複数の電力パッドを含み、そのパッドの数は、入力バッファと出力バッファが同時に実行されるときに、十分な動作電流と安定な電圧レベルを供給するに足るものである。

【0082】

図7および図8は、本発明の一実施形態によるマルチチップデバイスの作製方法における段階を示す。交互にチップを裏返すことにより、トランジスタで形成される面である各チップの上面が、互いに反対を向き、2つのパッドが、スルーシリコンバイアなどのスルーチップバイアで、互いに垂直に接続される。2つのチップに対して第1の接続が作られた後、2つの組み合わされたマルチチップ(合計4チップ)のパッドの間の電気的短絡を防止するために、絶縁層が堆積される。図7は、集積回路チップの積層ペアを作製する段階を示し、一方、図8は、複数のペアの積層チップ、または複数のペアの組み合わされたチップを有するマルチチップデバイスを作製する、さらなる段階を示す。

【0083】

図7において、段階702は、下部チップになるように、トランジスタを載せるその上面が、下など、第1の方向を向くように第1のチップが裏返されることを示す。段階704において、第2のチップが、裏返された第1のチップの上面に置かれ、第2のチップは、パッドの配列および配置において、第1のチップと実質的に同一である。段階706において、少なくとも1つの直列接続と少なくとも1つの並列接続を作成するために、上部チップの信号パッドを、下部チップの対応する信号パッドに接続することを容易にするための、パッドおよびチップを貫通するバイアホールが作成される。

【0084】

2つのチップは実質的に同一の信号パッド配列であるため、段階706は、上部チップのコモン接続信号パッドをその複製コモン接続信号パッドと並列に接続することを容易にするように、第1のスルーチップバイアホールおよびスルーパッドバイアホールを作成する段階を含むことができる。段階706は、上部チップの出力信号パッドを下部チップ上のそのそれぞれの入力信号パッドと直列に接続することを容易にするように、第2のスルーチップバイアホールおよびスルーパッドバイアホールを作成する段階を、さらに含むことができる。

【0085】

段階708において、絶縁層が、バイアホール内に配置される。段階710において、上部チ

10

20

30

40

50

ップおよび下部チップの上のパッド間にスルーバイア接続が作成するために、導体(例えば、銅)が、バイアホール内に配置される。一実施形態において、段階710の最後に、1対の積層チップが作製され、その積層体は、上部チップのコモン接続信号パッドを、その複製コモン接続信号パッドと並列に接続する、少なくとも1つの並列接続スルーチップバイアと、上部チップの出力信号パッドを、下部チップ上の、そのそれぞれの入力信号パッドと直列に接続する、少なくとも1つの直列接続スルーチップバイアとを含む。

#### 【0086】

図8に移ると、2対の積層チップを有するマルチチップデバイスを作製する方法の、さらなる段階が示されている。段階802において、絶縁層が、集積回路チップの第1の積層ペアの上面に配置される。段階804において、他のチップが後で上面に置かれるときに、ある隣接信号パッド間の接続を可能にするために、コンタクトホールが絶縁層の中に形成される。段階806において、導体が、前の段階で形成されたコンタクトホールの中に充填、または堆積される。段階808において、導体層がエッチングされ、それにより、余分な導体材料が、コンタクトホールの外側の部分から除去される。段階810において、図7の段階702～710によって作製された、2つの予め組み合わされたチップが、集積回路チップの第1の積層ペアの上面に取り付けられて、マルチチップパッケージのためのマルチチップ回路を作成する。

10

#### 【0087】

一実施形態において、直列接続された集積回路を積層する方法は、以下の段階、すなわち、第1のチップを裏返す段階と、第2のチップを第1のチップ上に置く段階と、パッドとチップを貫通するバイアホールを、第2のチップのコモン接続と出力ポートの上に作る段階と、絶縁層をバイアホール内に配置する段階と、導体(例えば、銅)をバイアホール内に配置する段階と、絶縁層を堆積させる段階と、コンタクトホールを絶縁層の中に形成する段階と、導体をコンタクトホール内に充填する段階と、導体層をエッチングする段階と、2つのチップを予め組み合わされたチップに取り付ける段階とを含む。

20

#### 【0088】

図9は、本発明の一実施形態による他の回路900の正面図である。この実施形態において、マルチチップ回路を形成する積層体の中に8つのチップが存在する。上部、下部、および中間のチップは、図5および図6で説明したのと同様に、それらのチップ間、および積層体内の接続を有する。図9に示すように、同一のチップの積層体は、パッケージの入力および出力、あるいは、ピン、またはボールグリッドアレー(BGA)などのボール、のいずれかに対する外部接続を有する。例えば、回路は、追加のボンディングワイヤまたはボールグリッドで、パッケージ上のピン、またはリードフレームと連絡することができる。BGAは、CPUパッケージ用など、高性能をもたらすために、メモリ産業でよく知られている。ボールグリッドはシステムバスであり、並列接続または直列(デイジーチェーン)接続に使用されうる。BGAは、ピンベース接続またはTSOP(薄型小型パッケージ)接続と比べて、より小さいキャパシタンスおよび負荷をもたらす。DDR2およびDDR3ならびに他の高速デバイスが、BGAを使用する。BGAは、外部とのインターフェイスのために使用され、チップ間接続には使用されない。

30

#### 【0089】

図10は、本発明の他の実施形態によるマルチチップパッケージ1000の、正面断面図を示す。本発明の態様において、複数のカスケードメモリデバイスを有するメモリシステムが、提供される。メモリデバイスは、直列に接続されてよく、外部メモリコントローラが、データと制御信号を受け、メモリシステムにもたらすことができる。類似の配列が、参照により本明細書に組み込まれている、2005年12月30日に出願され、2007年4月5日に公開された、「Multiple Independent Serial Link Memory」という名称の、本願と同一譲受人に譲渡された米国特許出願第2007/0076479号の中で説明されている。

40

#### 【0090】

NANDフラッシュなど、ある一定の種類のメモリのために本発明の実施形態を使用するときは、同じパッケージの中にメモリコントローラを備え、他のメモリチップと共に積層さ

50

れることが望ましい。図9に示すような多くの種類のメモリチップ(例えば、DRAM、SRAM、または他の論理回路)に対して、コントローラは、積層チップと共に組み込まれない。

#### 【0091】

図10の実施形態において、コントローラ1002が、積層チップ1004の下に置かれる。メモリからの出力信号パッドが、コントローラ入力接続1006により、コントローラの入力側に接続される。コントローラの入力接続1006は、ワイヤボンディング、バイア、ボールグリッド、または任意の他の適当な接続であってよい。コントローラの出力側は、コントローラの出力接続1008により、メモリ積層体の上部チップの入力パッドに接続される。コントローラの出力接続1008は、ワイヤボンディング、または任意の他の適当な接続であってよい。接続の種類および性質を示すために、ほんのわずかの代表的な接続だけを、図10に示す。

10

#### 【0092】

他の実施形態(図示せず)において、コントローラは、コントローラの出力側をメモリの入力側に接続するために、上面に置かれうる。適当なコントローラ出力接続が、これらの接続を作るために備えられ、適当なコントローラ入力接続が、メモリ積層体の出力側を、コントローラの入力に接続するために備えられる。そのような実施形態において、ループ接続が、積層体の中の直列接続によって容易になり、そこでは、最後のデバイスが、一巡してコントローラに戻る。

#### 【0093】

マルチチップパッケージの作製において、図7および図8に関連して説明したようなスルーチップバイアの作成は、製造プロセスの中の段階のうちのいくつかである。追加の段階が、コントローラが関連するときに、含まれうる。パッケージの(または、パッケージ化する)段階において、コントローラの入力接続および出力接続が追加される。このことは、コントローラの出力をメモリの入力に、またはその反対に接続するために、ワイヤボンディングを追加する段階を含むことができる。さらなる段階として、パッケージまたは複合体の全体を覆う段階が含まれる。

20

#### 【0094】

図3～図10に示すチップは、シリコン基板技術を使用して作製される。しかし、ガリウムヒ素、ゲルマニウム、シリコンゲルマニウム、または任意の他の基板技術を使用して作製される実施形態は、現在の技術の範囲内にある。

30

#### 【0095】

図3～図10に示す実施形態においては、例示を明確にまた容易にするために、パッドは、チップの縁部に沿って配置されていることに留意されたい。パッドは、チップの2カ所、3カ所、または4カ所の縁部に沿って配置されてよく、やはり現在の技術の範囲内にある。

#### 【0096】

図2～図10に示すチップの物理的な寸法または比率は、縮尺通りに描かれていない。いくつかの寸法は、図示を明確にするために、拡大または縮小されている。

#### 【0097】

上記の中で、説明を目的として、本発明の実施形態を完全に理解できるように、多くの詳細な内容が示されている。しかし、これらの具体的な詳細が、本発明を実施するために必要とされないことは、当業者には明らかであろう。他の例において、本発明を分かりにくくしないために、よく知られている電気的な構造および回路を、ブロック線図の形で示す。

40

#### 【0098】

本発明の上記の実施形態は、例示だけが目的である。本発明の範囲を逸脱することなく、当業者により、特定の実施形態に対する改変、変更、および変形が達成可能であり、本発明の範囲は、本明細書に添付されている特許請求の範囲によってのみ、定義される。

#### 【符号の説明】

#### 【0099】

50

|                                         |                             |    |

|-----------------------------------------|-----------------------------|----|

| 100                                     | マルチチップ積層体、マルチチップデバイス        |    |

| 102                                     | 部分的上面図                      |    |

| 104                                     | 断面図                         |    |

| 200                                     | 回路                          |    |

| 300                                     | 正投影法の図                      |    |

| 302                                     | 部分的上面図                      |    |

| 304                                     | 断面正面図                       |    |

| 306                                     | 部分的下面図                      |    |

| 308                                     | 上部チップ                       | 10 |

| 310                                     | 下部チップ                       |    |

| 312                                     | 中心線                         |    |

| 314                                     | 並列接続スルーチップバイア               |    |

| 316                                     | 直列接続スルーチップバイア               |    |

| 500                                     | 正投影法の図                      |    |

| 502                                     | 部分的上面図                      |    |

| 504                                     | 断面正面図                       |    |

| 508                                     | 上部チップ                       |    |

| 510                                     | 下部チップ                       |    |

| 512                                     | 第1の中間チップ                    |    |

| 514                                     | 第2の中間チップ                    | 20 |

| 518                                     | 同一直線上でパッド、チップおよび絶縁体を貫通するバイア |    |

| 520                                     | スルーチップバイア                   |    |

| 522                                     | 絶縁体                         |    |

| 524                                     | スルーパッドバイア                   |    |

| 600                                     | マルチチップパッケージ                 |    |

| 602                                     | 部分的上面図                      |    |

| 604                                     | 断面正面図                       |    |

| 606                                     | 部分的下面図                      |    |

| 610                                     | CSIパッド                      |    |

| 612                                     | CSOパッド                      | 30 |

| 614                                     | スルーチップバイア                   |    |

| 616                                     | CSIパッド                      |    |

| 618                                     | CSOパッド                      |    |

| 620                                     | CSOパッド                      |    |

| 622                                     | 絶縁体                         |    |

| 624                                     | スルーパッドバイア                   |    |

| 626                                     | CSIパッド                      |    |

| 628                                     | スルーチップバイア                   |    |

| 630                                     | CSIパッド                      |    |

| 632                                     | CSOパッド                      | 40 |

| 702、704、706、708、710、802、804、806、808、810 | 段階                          |    |

| 900                                     | 回路                          |    |

| 1000                                    | マルチチップパッケージ                 |    |

| 1002                                    | コントローラ                      |    |

| 1004                                    | 積層チップ                       |    |

| 1006                                    | コントローラ入力接続                  |    |

| 1008                                    | コントローラ出力接続                  |    |

【図1】

FIG. 1

【図2】

FIG. 2

【図3A】

FIG. 3A

【図3B】

FIG. 3B

【図 3C】

FIG. 3C

【図 4】

FIG. 4

【図 5A】

FIG. 5A

【図 5B】

FIG. 5B

【図 5 C】

FIG. 5C

【図 6 A】

FIG. 6A

【図 6 B】

FIG. 6B

【図 6 C】

FIG. 6C

【図7】

FIG. 7

【図8】

FIG. 8

【図9】

FIG. 9

【図10】

FIG. 10

---

フロントページの続き

(31)優先権主張番号 12/168,354

(32)優先日 平成20年7月7日(2008.7.7)

(33)優先権主張国 米国(US)

(31)優先権主張番号 12/236,874

(32)優先日 平成20年9月24日(2008.9.24)

(33)優先権主張国 米国(US)

(74)代理人 100108453

弁理士 村山 靖彦

(74)代理人 100064908

弁理士 志賀 正武

(74)代理人 100089037

弁理士 渡邊 隆

(74)代理人 100140534

弁理士 木内 敏二

(72)発明者 ホン・ボム・ピョン

カナダ・オンタリオ・K2M・2E1・カナタ・リヴァーグリーン・クレセント・16

審査官 宮本 靖史

(56)参考文献 特開2006-186091(JP, A)

特開2005-340389(JP, A)

国際公開第2006/019156(WO, A1)

特開2006-140351(JP, A)

特開2004-356284(JP, A)

特開2004-349694(JP, A)

特開2003-197854(JP, A)

特開2001-284097(JP, A)

特開平07-120772(JP, A)

特開平03-291960(JP, A)

(58)調査した分野(Int.Cl. , DB名)

H01L 23/00

H01L 23/52 - 23/538

H01L 25/00 - 25/18