(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6239259号

(P6239259)

(45) 発行日 平成29年11月29日(2017.11.29)

(24) 登録日 平成29年11月10日(2017.11.10)

(51) Int.Cl.

H04L 9/10 (2006.01)

F 1

H 0 4 L 9/00

6 2 1 A

請求項の数 20 (全 18 頁)

(21) 出願番号 特願2013-97518 (P2013-97518)

(22) 出願日 平成25年5月7日 (2013.5.7)

(65) 公開番号 特開2013-236376 (P2013-236376A)

(43) 公開日 平成25年11月21日 (2013.11.21)

審査請求日 平成28年3月17日 (2016.3.17)

(31) 優先権主張番号 10-2012-0047743

(32) 優先日 平成24年5月4日 (2012.5.4)

(33) 優先権主張国 韓国 (KR)

(73) 特許権者 390019839

三星電子株式会社

Samsung Electronics

Co., Ltd.

大韓民国京畿道水原市靈通区三星路 129

129, Samsung-ro, Yeon

gton-gu, Suwon-si, G

yeonggi-do, Republic

of Korea

(74) 代理人 110000051

特許業務法人共生国際特許事務所

(72) 発明者 季 慶洙

大韓民国 京畿道 華城市 石隅洞 禮堂

マウルウミリン第1ブンギヨンチェアパー

ト 122 棟 1402号

最終頁に続く

(54) 【発明の名称】システムオンチップとその動作方法、及びそれを含むシステムインパッケージ

## (57) 【特許請求の範囲】

## 【請求項 1】

システムオンチップ (S o C) の動作方法であって、

前記 S o C に含まれるエンジンが、前記 S o C に含まれるデータバスを介して平文データを受信する段階と、

前記エンジンが、前記 S o C に含まれる C P U によってセキュリティモードで入力された暗号キーを用いて前記平文データを暗号文データに変換する段階と、

前記エンジンが、前記暗号文データを前記 S o C に含まれるメモリコントローラに前記データバスを介すこと無く、直接伝送する段階と、を有し、

前記メモリコントローラは、不揮発性メモリの動作を制御することを特徴とするシステムオンチップの動作方法。 10

## 【請求項 2】

前記平文データを暗号文データに変換する段階の前に、前記平文データを前記 C P U の制御によってメインメモリから前記データバスを介してリードする段階を更に含むことを特徴とする請求項 1 に記載のシステムオンチップの動作方法。

## 【請求項 3】

システムオンチップ (S o C) の動作方法であって、

前記 S o C に含まれるエンジンが、前記 S o C に含まれるメモリコントローラから暗号文データを直接受信する段階と、

前記エンジンが、前記 S o C に含まれる C P U によってセキュリティモードで前記エン

10

20

ジンに入力された暗号キーを用いて前記暗号文データを平文データに変換する段階と、を有し、

前記メモリコントローラは、不揮発性メモリの動作を制御することを特徴とするシステムオンチップの動作方法。

【請求項 4】

前記暗号文データを平文データに変換する段階の前に、前記平文データを前記 S o C に含まれる DMA ( D i r e c t M e m o r y A c c e s s ) ユニットから前記エンジンに伝送する段階を更に含むことを特徴とする請求項 3 に記載のシステムオンチップの動作方法。

【請求項 5】

システムオンチップ ( S o C ) であって、

C P U と、

前記 C P U によってセキュリティモードで入力された暗号キーを用いて、第 1 平文データを第 1 暗号文データに暗号化し、第 2 暗号文データを第 2 平文データに復号化する暗号化 / 復号化エンジンと、

前記暗号化 / 復号化エンジンに直接接続され、前記第 1 暗号文データを不揮発性メモリに伝送し、前記不揮発性メモリから前記第 2 暗号文データを受信するメモリコントローラと、を有し、

前記暗号化 / 復号化エンジンと前記メモリコントローラとは直接接続され、前記暗号化 / 復号化エンジンと前記メモリコントローラとの間にはいかなる装置も接続されないことを特徴とするシステムオンチップ。

【請求項 6】

前記暗号キーを保存するワンタイムプログラマブル ( O T P ) メモリを更に含むことを特徴とする請求項 5 に記載のシステムオンチップ。

【請求項 7】

前記システムオンチップ ( S o C ) の外部にある装置から受信した前記第 1 平文データを前記暗号化 / 復号化エンジンに伝送し、前記暗号化 / 復号化エンジンから受信した前記第 2 平文データを前記装置に伝送する DMA ( D i r e c t M e m o r y A c c e s s ) ユニットを更に含むことを特徴とする請求項 5 に記載のシステムオンチップ。

【請求項 8】

前記 C P U は、前記システムオンチップ ( S o C ) の外部にある装置と前記暗号化 / 復号化エンジンとの間で前記第 1 平文データ又は前記第 2 平文データの伝送を制御することを特徴とする請求項 5 に記載のシステムオンチップ。

【請求項 9】

請求項 5 に記載のシステムオンチップ ( S o C ) と、

前記 S o C の制御によって、不揮発性メモリとデータを通信する装置と、を備えることを特徴とするシステムインパッケージ。

【請求項 10】

請求項 5 に記載のシステムオンチップ ( S o C ) と、

不揮発性メモリと、

前記 S o C の制御によって、前記不揮発性メモリとデータを通信する装置と、を備えることを特徴とするシステムインパッケージ。

【請求項 11】

システムオンチップ ( S o C ) であって、

C P U と、

外部の揮発性メモリから平文データを受信する揮発性メモリコントローラと、

不揮発性メモリコントローラに直接接続され、前記揮発性メモリコントローラから送信された前記平文データを、前記 C P U によってセキュリティモードで入力された暗号キーを用いて暗号文データに暗号化する暗号化エンジンと、

前記 C P U 及び前記揮発性メモリコントローラに接続されたデータバスと、

10

20

30

40

50

不揮発性メモリを制御し、前記平文データを送信するために用いられる前記データバスを介すること無く、前記暗号文データを前記暗号化エンジンから直接受信する不揮発性メモリコントローラと、を有し、

前記S o Cは、前記S o Cの外部にある装置と前記不揮発性メモリとの間のデータの伝送を制御し、

前記不揮発性メモリコントローラ及び前記暗号化エンジンは、前記データを伝送するための第1データバスに該当し、

前記暗号化エンジンと前記不揮発性メモリコントローラとは直接接続され、前記暗号化エンジンと前記不揮発性メモリコントローラとの間にはいかなる装置も接続されないことを特徴とするシステムオンチップ。

10

【請求項12】

暗号キーを保存するためのワンタイムプログラマブル(O T P)メモリを更に含み、

前記暗号化エンジンは、前記O T Pメモリに保存された暗号キーを用いて、前記データを暗号化することを特徴とする請求項11に記載のシステムオンチップ。

【請求項13】

前記第1データバスは、前記装置から受信した前記データを前記暗号化エンジンに伝送し、前記暗号化エンジンから受信した前記データを前記装置に伝送するDMA(Direct Memory Access)ユニットを更に含むことを特徴とする請求項11に記載のシステムオンチップ。

20

【請求項14】

前記DMAユニットは、前記暗号化エンジンに直接接続されることを特徴とする請求項13に記載のシステムオンチップ。

【請求項15】

暗号化されていない前記データを伝送する第2データバスを更に含むことを特徴とする請求項14に記載のシステムオンチップ。

【請求項16】

選択信号に基づいて、前記第1データバス及び前記第2データバスのうちの何れか1つを選択するための選択回路を更に含むことを特徴とする請求項15に記載のシステムオンチップ。

30

【請求項17】

システムオンチップ(S o C)であって、

CPUと、

前記CPUに接続されたデータバスと、

前記データバスに平文データを出力するメインメモリコントローラと、

前記データバスから受信した前記平文データを、前記CPUによってセキュリティモードで入力された暗号キーを用いて暗号文データに暗号化するエンジンと、

前記データバスを介すること無く、前記暗号文データを前記エンジンから直接受信する不揮発性メモリコントローラと、

前記エンジンをバイパスして前記データバスを前記不揮発性メモリコントローラに接続させる第1電気的経路と、

40

前記エンジンを介して前記データバスを前記不揮発性メモリコントローラに接続させる第2電気的経路と、を有し、

前記S o Cは、非セキュリティモードで、前記平文データを前記データバスから前記不揮発性メモリコントローラに伝送するために前記第1電気的経路のみを活性化させ、

前記S o Cは、セキュリティモードで、前記平文データを前記エンジンに伝送し、前記エンジンから受信した前記暗号文データを前記不揮発性メモリコントローラに伝送するために前記第2電気的経路のみを活性化させ、

前記エンジンと前記不揮発性メモリコントローラとは直接接続され、前記エンジンと前記不揮発性メモリコントローラとの間にはいかなる装置も接続されないことを特徴とするシステムオンチップ。

50

## 【請求項 18】

前記第1電気的経路は、マルチプレクサ及びデマルチプレクサを介して前記平文データを前記不揮発性メモリコントローラに伝送するための経路を含むことを特徴とする請求項17に記載のシステムオンチップ。

## 【請求項 19】

前記第2電気的経路は、前記マルチプレクサを介して前記平文データを前記エンジンに伝送するための経路と、前記デマルチプレクサを介して前記暗号文データを前記不揮発性メモリコントローラに伝送するための経路とを含むことを特徴とする請求項18に記載のシステムオンチップ。

## 【請求項 20】

前記エンジンは、前記第2電気的経路を介して前記不揮発性メモリコントローラから受信した暗号文データを復号化することを特徴とする請求項17に記載のシステムオンチップ。

10

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、システムオンチップ (System On Chip: SoC) に係り、より詳細には、暗号化 / 復号化エンジンとメモリコントローラとが直接接続されたシステムオンチップとその動作方法、及びそれを含むシステムインパッケージに関する。

20

## 【背景技術】

## 【0002】

メインメモリは、CPU (Central Processing Unit) が実行するプログラムとCPUで必要なデータを、他の記録媒体、例えば不揮発性メモリ装置から受信する。また、メインメモリは、データを保存するために、データを他の記録媒体、例えば不揮発性メモリ装置に伝送する。

## 【0003】

メインメモリと不揮発性メモリ装置との間のデータ送受信過程で、データがプロービング (probing) されることを防止するために、データ送受信途中でデータを暗号化する過程が含まれ得る。メインメモリと不揮発性メモリ装置とを含むシステムの性能は、メインメモリと不揮発性メモリ装置との間でデータを送受信するためのデータ伝送経路、即ちデータパスによって決定される。

30

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0004】

本発明は、上記従来技術に鑑みてなされたものであって、本発明の目的は、システムオンチップに含まれる暗号化 / 復号化エンジンとメモリコントローラとを直接接続することによって、データ伝送経路を減少させるシステムオンチップとその動作方法、及びそれを含むシステムインパッケージを提供することにある。

## 【課題を解決するための手段】

40

## 【0005】

上記目的を達成するためになされた本発明の一態様によるシステムオンチップ (SoC) の動作方法は、前記SoCに含まれるエンジンによって、暗号キーを用いて平文データを暗号文データに変換する段階と、前記エンジンによって、前記暗号文データを前記SoCに含まれるメモリコントローラに直接伝送する段階と、を有し、前記メモリコントローラは、不揮発性メモリの動作を制御する。

## 【0006】

前記SoCの動作方法は、前記平文データを暗号文データに変換する段階の前に、前記平文データをCPUの制御によってメインメモリからバスを介してリードする段階を更に含み得る。

50

## 【0007】

上記目的を達成するためになされた本発明の他の態様によるシステムオンチップ（S o C）の動作方法は、前記S o Cに含まれるエンジンによって、前記S o Cに含まれるメモリコントローラから暗号文データを直接受信する段階と、前記エンジンによって、暗号キーを用いて前記暗号文データを平文データに変換する段階と、を有し、前記メモリコントローラは、不揮発性メモリの動作を制御する。

## 【0008】

前記S o Cの動作方法は、前記暗号文データを平文データに変換する段階の前に、前記平文データを前記S o Cに含まれるDMA（D i r e c t M e m o r y A c c e s s）ユニットから前記エンジンに伝送する段階を更に含み得る。

10

## 【0009】

上記目的を達成するためになされた本発明の一態様によるシステムオンチップ（S o C）は、暗号キーを用いて、第1平文データ（p l a i n d a t a）を第1暗号文データ（c i p h e r d a t a）に暗号化し、第2暗号文データを第2平文データに復号化する暗号化／復号化エンジンと、前記暗号化／復号化エンジンに直接接続され、前記第1暗号文データを不揮発性メモリに伝送し、該不揮発性メモリから前記第2暗号文データを受信するメモリコントローラと、を有する。

## 【0010】

前記S o Cは、前記暗号キーを保存するワンタイムプログラマブル（O T P）メモリを更に含み得る。

20

前記S o Cは、前記S o Cの外部にある装置から受信した前記第1平文データを前記暗号化／復号化エンジンに伝送し、該暗号化／復号化エンジンから受信した前記第2平文データを前記装置に伝送するDMA（D i r e c t M e m o r y A c c e s s）ユニットを更に含み得る。

前記S o Cは、前記S o Cの外部にある装置と前記暗号化／復号化エンジンとの間で前記第1平文データ又は前記第2平文データの伝送を制御するC P Uを更に含み得る。

## 【0011】

上記目的を達成するためになされた本発明の一態様によるシステムインパッケージ（S y s t e m - i n P a k a g e）は、上記システムオンチップ（S o C）と、前記S o Cの制御によって、不揮発性メモリとデータを通信する装置と、を備える。

30

## 【0012】

上記目的を達成するためになされた本発明の他の態様によるシステムインパッケージは、上記S o Cと、不揮発性メモリと、前記S o Cの制御によって、前記不揮発性メモリとデータを通信する装置と、を備える。

## 【0013】

上記目的を達成するためになされた本発明の他の態様によるシステムオンチップ（S o C）は、不揮発性メモリを制御するメモリコントローラと、前記メモリコントローラに直接接続され、データを暗号化又は復号化する暗号化／復号化エンジン（e n g i n e）と、を有し、前記S o Cは、前記S o Cの外部にある装置と前記不揮発性メモリとの間でデータの伝送を制御し、前記メモリコントローラ及び前記暗号化／復号化エンジンは、前記データを伝送するための第1データパスに該当する。

40

## 【0014】

前記S o Cは、暗号キーを保存するためのワンタイムプログラマブル（O T P）メモリを更に含み、前記暗号化／復号化エンジンは、前記O T Pメモリに保存された暗号キーを用いて、前記データを暗号化又は復号化することができる。

前記第1データパスは、前記装置から受信した前記データを前記暗号化／復号化エンジンに伝送し、該暗号化／復号化エンジンから受信した前記データを前記装置に伝送するDMA（D i r e c t M e m o r y A c c e s s）ユニットを更に含み得る。

前記DMAユニットは、前記暗号化／復号化エンジンに直接接続され得る。

前記S o Cは、暗号化されていない前記データを伝送する第2データパスを更に含み得

50

る。

前記 S o C は、選択信号に基づいて、前記第 1 データバス及び前記第 2 データバスのうちの何れか 1 つを選択するための選択回路を更に含み得る。

【 0 0 1 5 】

上記目的を達成するためになされた本発明の更に他の態様によるシステムオンチップ ( S o C ) は、データバスと、前記データバスに平文データを出力するメインメモリコントローラと、前記データバスから受信した前記平文データを、キー ( k e y ) を使って暗号文データに暗号化するエンジンと、不揮発性メモリコントローラと、前記エンジンをバイパス ( b y p a s s ) して前記データバスを前記不揮発性メモリコントローラに接続させる第 1 電気的経路と、前記エンジンを介して前記データバスを前記不揮発性メモリコントローラに接続させる第 2 電気的経路と、を有し、前記 S o C は、非セキュリティモード ( N o n - S e c u r e M o d e ) で、前記平文データを前記データバスから前記不揮発性メモリコントローラに伝送するために前記第 1 電気的経路のみを活性化させ、前記 S o C は、セキュリティモードで、前記平文データを前記エンジンに伝送し、該エンジンから受信した前記暗号文データを前記不揮発性メモリコントローラに伝送するために前記第 2 電気的経路のみを活性化させる。

【 0 0 1 6 】

前記第 1 電気的経路は、マルチプレクサ ( m u l t i p l e x e r ) とデマルチプレクサ ( d e m u l t i p l e x e r ) とを介して前記平文データを前記不揮発性メモリコントローラに伝送するための経路を含み得る。

前記第 2 電気的経路は、前記マルチプレクサを介して前記平文データを前記エンジンに伝送するための経路と、前記デマルチプレクサを介して前記暗号文データを前記不揮発性メモリコントローラに伝送するための経路とを含み得る。

前記エンジンは、前記第 2 電気的経路を介して前記不揮発性メモリコントローラから受信した暗号文データを復号化することができる。

【 発明の効果 】

【 0 0 1 7 】

本発明のシステムオンチップ ( S o C ) によれば、 S o C の内部でデータを暗号化するため、 S o C の外部からデータをプロービングすることができない。 S o C は、暗号化に必要な暗号キーを S o C の内部に保存するため、暗号キーの露出を防止することができる。

また、 S o C は、暗号化に必要な暗号キーをソフトウェアでアクセスすることができないため、ハッキングによって暗号キーが流出することを防止することができる。 S o C のソフトウェアは、暗号化に介入しないので、ソフトウェアの負担を増加させない。

また、 S o C は、 S o C の内部に具現された暗号化 / 復号化エンジンとメモリコントローラとを直接接続することによって、 S o C の内部のデータ伝送経路を減少させることができる。従って、 S o C の性能が向上する。

【 図面の簡単な説明 】

【 0 0 1 8 】

【 図 1 】本発明の一実施形態によるシステムオンチップを含むシステムのブロック図である。

【 図 2 】図 1 に示したシステムオンチップの一実施形態によるブロック図である。

【 図 3 】図 2 に示した暗号化 / 復号化エンジンに暗号キーを入力するセキュリティモードを説明するための概念図である。

【 図 4 】図 1 に示したシステムオンチップの他の実施形態によるブロック図である。

【 図 5 】図 1 に示したシステムオンチップの更に他の実施形態によるブロック図である。

【 図 6 】図 1 に示したシステムオンチップの更に他の実施形態によるブロック図である。

【 図 7 】図 1 に示したシステムオンチップの更に他の実施形態によるブロック図である。

10

20

30

40

50

【図8】図7に示した選択回路及び暗号化／復号化エンジンのブロック図である。

【図9】図1に示したシステムオンチップの更に他の実施形態によるブロック図である。

【図10】本発明の一実施形態によるシステムオンチップの動作方法を説明するフローチャートである。

【図11】本発明の他の実施形態によるシステムオンチップの動作方法を説明するフローチャートである。

【図12】本発明の更に他の実施形態によるシステムオンチップの動作方法を説明するフローチャートである。

【図13】本発明の更に他の実施形態によるシステムオンチップの動作方法を説明するフローチャートである。

10

【図14】図1に示したシステムを含むデータ処理装置の一実施形態によるブロック図である。

【図15】図1に示したシステムを含むデータ処理装置の他の実施形態によるブロック図である。

【図16】図1に示したシステムを含むデータ処理装置の更に他の実施形態によるブロック図である。

【図17】図1に示したシステムオンチップを含むシステムインパッケージ及び不揮発性メモリ装置のブロック図である。

【図18】図1に示したシステムオンチップを含むシステムインパッケージの他の実施形態によるブロック図である。

20

【発明を実施するための形態】

【0019】

本明細書で“直接伝送する”と言及した場合には、伝送中に他の構成による処理過程を経ずにデータを伝送することを意味する。本明細書で“直接接続される”と言及した場合には、中間に他の構成を置かずに配線(wiring)、マルチプレクサ、及び／又はデマルチプレクサなどを介して接続されることを意味する。

【0020】

以下、本発明を実施するための形態の具体例を、図面を参照しながら詳細に説明する。

【0021】

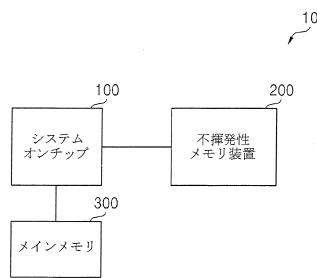

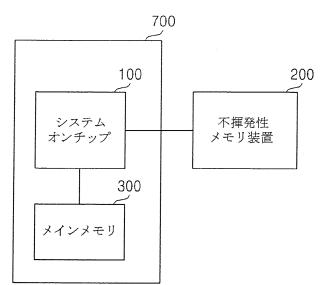

図1は、本発明の一実施形態によるシステムオンチップを含むシステムのブロック図である。図1を参照すると、システム10は、システムオンチップ(SoC)100、不揮発性メモリ装置200、及びメインメモリ300を含む。実施形態として、システム10は、PC(Personal Computer)、データサーバ(Data Server)、又は携帯用電子装置として具現可能である。

30

【0022】

例えば、携帯用電子装置は、ラップトップコンピュータ、携帯電話、スマートフォン、タブレットPC、PDA(Personal Digital Assistant)、EDA(Enterprise Digital Assistant)、デジタルスチルカメラ、デジタルビデオカメラ、PMP(Portable Multimedia Player)、PDN(Personal Navigation Device)又はPortable Navigation Device)、携帯用ゲームコンソール、又は電子ブックなどとして具現可能である。

40

【0023】

SoC100は、不揮発性メモリ装置200とメインメモリ300との間のデータの送受信を制御する。SoC100の構成と動作は、図2、及び図4～図9を参照して詳しく説明する。

【0024】

不揮発性メモリ装置200は、各種のプログラム及びデータを保存する。実施形態として、不揮発性メモリ装置200は、EEPROM(Electrically Erasable Programmable Read-Only Memory)、フラッシュ

50

ユメモリ、MRAM (Magnetic RAM)、スピン注入トルクMRAM (Spin-Transfer Torque MRAM)、Conductive Bridging RAM (CBRAM) : FeRAM (Ferroelectric RAM)、PRAM (Phase change RAM)、抵抗メモリ (Resistive RAM : ReRAM)、ナノチューブReRAM (Nanotube ReRAM)、ポリマーRAM (Polymer RAM : PoRAM)、ナノ浮遊ゲートメモリ (Nano Floating Gate Memory : NFGM)、ホログラフィックメモリ (Holographic Memory)、分子電子メモリ素子 (Molecular Electronics Memory Device)、又は絶縁抵抗変化メモリ (Insulator Resistance Change Memory) などとして具現可能であるが、本発明の範囲はこれに限定されるものではない。10

#### 【0025】

メインメモリ300は、SoC100で実行されるプログラムとSoC100で必要なデータとをSoC100を介して不揮発性メモリ装置200から受信する。メインメモリ300は、保存されるデータを、SoC100を介して不揮発性メモリ装置200に伝送する。実施形態として、メインメモリ300は、揮発性メモリであるRAM (Random Access Memory)、例えばDRAM (Dynamic RAM) 又はSRAM (Static RAM) として具現可能であるが、本発明の範囲はこれに限定されるものではない。20

#### 【0026】

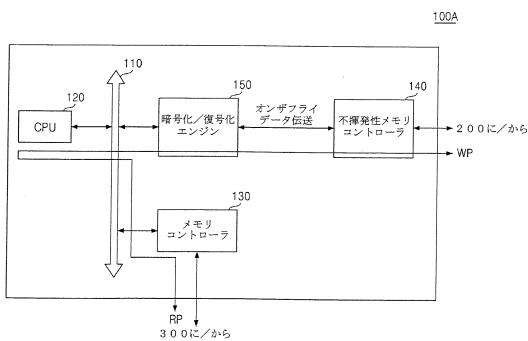

図2は、図1に示したシステムオンチップの一実施形態によるブロック図である。図2を参照すると、図1のSoC100の一実施形態によるSoC100Aは、バス (bus) 110、CPU120、メモリコントローラ130、不揮発性メモリコントローラ140、及び暗号化 / 復号化エンジン150を含む。20

#### 【0027】

CPU120は、バス110に接続され、SoC100Aの全般的な動作を制御する。メモリコントローラ130は、メインメモリ300の動作、例えばリード (read) 動作又はライト (write) 動作を制御する。メモリコントローラ130は、バス110に接続される。30

#### 【0028】

不揮発性メモリコントローラ140は、不揮発性メモリ装置200のデータアクセス動作、例えばリード動作、ライト動作、プログラム (program) 動作、又はイレーズ (erase) 動作などを制御する。30

#### 【0029】

暗号化 / 復号化エンジン150は、メインメモリ300からメモリコントローラ130とバス110とを介して伝送された平文データを暗号文データに変換、即ち暗号化する。暗号化 / 復号化エンジン150は、暗号文データを、バス110を経由せずに不揮発性メモリコントローラ140に直接、例えばオンザフライ (on-the-fly) で伝送する。40

#### 【0030】

暗号化 / 復号化エンジン150は、不揮発性メモリコントローラ140から出力された暗号文データを、バス110を経由せずに直接、例えばオンザフライで受信する。暗号化 / 復号化エンジン150は、暗号文データを平文データに変換、例えば復号化する。40

#### 【0031】

暗号化 / 復号化エンジン150の暗号化過程又は復号化過程には、暗号キーが使われる。暗号化 / 復号化エンジン150は、暗号キーを保存するための記憶媒体 (図示せず) を含む。他の実施形態として、暗号キーは、セキュリティモード (Secure Mode) でのみ記憶媒体にアクセス可能になるように設定し得る。セキュリティモードは、図3を参照して詳しく説明する。50

#### 【0032】

暗号化 / 復号化エンジン 150 は、データを所定サイズ、例えば 64 ビット、128 ビット、又は 256 ビットのブロック (block) 単位で暗号化又は復号化する。この場合、暗号化又は復号化のための暗号キーとアルゴリズム (algorithm) は、ブロック単位で適用可能である。

【0033】

暗号化アルゴリズムは、DES (Data Encryption Standard) アルゴリズム又は AES (Advanced Encryption Standard) アルゴリズムであり得るが、これに限定されるものではない。実施形態として、暗号化 / 復号化エンジン 150 がデータをブロック単位で変換、例えば暗号化又は復号化する方法を決定する暗号モードは、ECB (Electronic Code Book) モード、CBC (Cipher Block Chaining) モード、PCBC (Propagating Cipher Block Chaining) モード、又は CFB (Cipher Feed Back) モードであり得るが、本発明の範囲はこれに限定されるものではない。

10

【0034】

データが、不揮発性メモリ装置 200 にライトされる時のライトデータパス (write data path: WP) を説明すると、メインメモリ 300 から出力された平文データがメモリコントローラ 130 とバス 110 とを介して CPU 120 に伝送された後、平文データは、CPU 120 からバス 110 を介して暗号化 / 復号化エンジン 150 に伝送される。即ち、CPU 120 の制御によって、平文データは、暗号化 / 復号化エンジン 150 に伝送される。

20

【0035】

暗号化 / 復号化エンジン 150 は、暗号キーを用いて平文データを暗号文データに変換する。暗号文データは、不揮発性メモリコントローラ 140 を介して不揮発性メモリ装置 200 に伝送される。

30

【0036】

データが、不揮発性メモリ装置 200 からリードされる時のリードデータパス (read data path: RP) を説明すると、不揮発性メモリ装置 200 から出力された暗号文データは、不揮発性メモリコントローラ 140 を介して暗号化 / 復号化エンジン 150 に直接伝送される。

【0037】

暗号化 / 復号化エンジン 150 は、暗号キーを用いて暗号文データを平文データに変換する。平文データがバス 110 を介して CPU 120 に伝送された後、平文データは、CPU 120 からバス 110 とメモリコントローラ 130 とを介してメインメモリ 300 に伝送される。即ち、CPU 120 の制御によって、平文データは、バス 110 とメモリコントローラ 130 とを介してメインメモリ 300 に伝送される。

【0038】

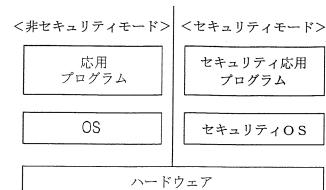

図 3 は、図 2 に示した暗号化 / 復号化エンジンに暗号キーを入力するセキュリティモードを説明するための概念図である。図 2 及び図 3 を参照すると、オペレーティングシステム (Operating System: OS) は、ハードウェアを管理し、応用プログラム (Application Program) を実行させるために、ハードウェアに設けられる。

40

【0039】

セキュリティ (Secure) OS は、セキュリティが要求されるセキュリティ応用プログラム (Secure Application Program) を実行させるために、一般的なオペレーティングシステム (OS) とは別個にハードウェアに設けられる。実施形態として、セキュリティ OS は、所定時間内に実行が完了しなければならない応用プログラム、例えば、セキュリティ応用プログラムを実行させるために、リアルタイムオペレーティングシステム (Real Time Operating System: RTOS) として具現可能である。

50

## 【0040】

非セキュリティモードとは、オペレーティングシステム(OS)によって応用プログラムが実行される場合を意味し、セキュリティモードとは、セキュリティOSによってセキュリティ応用プログラムが実行される場合を意味する。セキュリティモードでセキュリティ応用プログラムが実行されることによって、CPU120は、暗号化/復号化エンジン150に暗号キーを入力するか、或いは暗号化/復号化エンジン150の内部又は外部に保存されている暗号キーにアクセスする。実施形態として、セキュリティモードでセキュリティ応用プログラムが実行されることによって、暗号キーは、変更又は再設定され得る。

## 【0041】

10

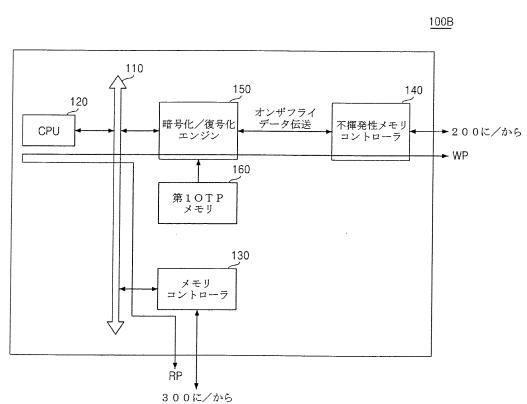

図4は、図1に示したシステムオンチップの他の実施形態によるブロック図である。図1～図4を参照すると、図1のSoC100の他の実施形態によるSoC100Bは、バス110、CPU120、メモリコントローラ130、不揮発性メモリコントローラ140、暗号化/復号化エンジン150、及び第1OTPメモリ(One-Time Programmable Memory)160を含む。第1OTPメモリ160は、暗号化/復号化エンジン150の暗号化過程又は復号化過程で使われる暗号キーを保存する。実施形態として、第1OTPメモリ160は、ヒューズ(fuse)、アンチヒューズ(anti-fuse)、又は電子ヒューズとして具現可能である。

## 【0042】

20

図4のSoC100Bは、図2のSoC100Aとは異なって、セキュリティモードでセキュリティ応用プログラムが実行されても、CPU120は、第1OTPメモリ160に保存された暗号キーにアクセス、例えばリード、ライト、又はイレーズできないように具現される。

## 【0043】

データの暗号化又は復号化に使われる暗号キーが、第1OTPメモリ160から暗号化/復号化エンジン150に供給されることを除けば、図4のSoC100BのライトデータバスWP及びリードデータバスRPのそれぞれは、図2のSoC100AのライトデータバスWP及びリードデータバスRPのそれぞれと実質的に同一である。

## 【0044】

30

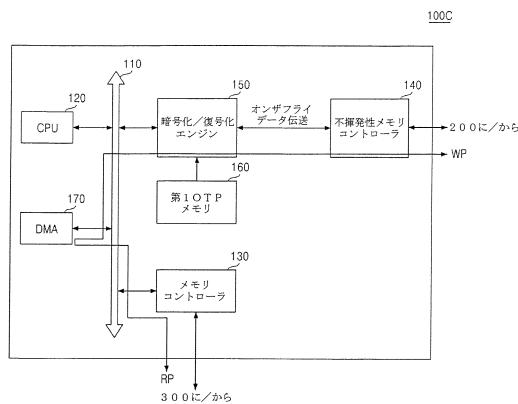

図5は、図1に示したシステムオンチップの更に他の実施形態によるブロック図である。図1及び図5を参照すると、図1のSoC100の更に他の実施形態によるSoC100Cは、バス110、CPU120、メモリコントローラ130、不揮発性メモリコントローラ140、暗号化/復号化エンジン150、第1OTPメモリ160、及びDMAユニット(Direct Memory Access Unit)170を含む。

## 【0045】

DMAユニット170は、CPU120を介さずに必要な構成(例えば、130、140、又は150)を介してメインメモリ300又は不揮発性メモリ装置200にアクセスすることができる。この際、DMAユニット170は、バス110に接続される。

## 【0046】

40

不揮発性メモリ装置200が、データをライトする時のライトデータバスWPを説明すると、メインメモリ300から出力された平文データは、メモリコントローラ130とバス110とを介してDMAユニット170に伝送される。平文データは、DMAユニット170からバス110を介して暗号化/復号化エンジン150に伝送される。

## 【0047】

暗号化/復号化エンジン150は、平文データを暗号文データに変換する。暗号化/復号化エンジン150から出力された暗号文データは、直接不揮発性メモリコントローラ140に伝送された後、不揮発性メモリ装置200に伝送される。即ち、暗号化/復号化エンジン150は、暗号文データを不揮発性メモリコントローラ140に直接、例えばオンザフライで伝送する。

## 【0048】

50

データが、不揮発性メモリ装置 200 からリードされる時のリードデータパス RP を説明すると、不揮発性メモリ装置 200 から出力された暗号文データは、不揮発性メモリコントローラ 140 を介して暗号化 / 復号化エンジン 150 に伝送される。即ち、暗号化 / 復号化エンジン 150 は、不揮発性メモリコントローラ 140 から出力された暗号文データを直接、例えばオンザフライで受信する。

#### 【0049】

暗号化 / 復号化エンジン 150 は、暗号文データを平文データに変換する。平文データは、バス 110 を介して DMA ユニット 170 に伝送される。平文データは、DMA ユニット 170 からバス 110 とメモリコントローラ 130 とを介してメインメモリ 300 に伝送される。

10

#### 【0050】

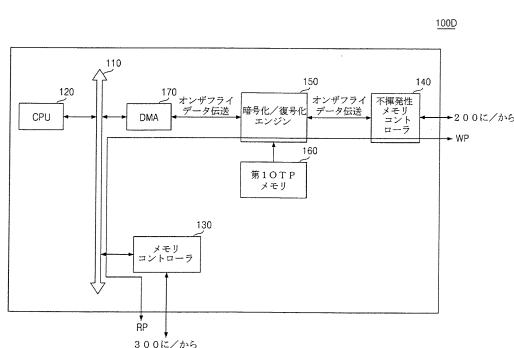

図 6 は、図 1 に示したシステムオンチップの更に他の実施形態によるブロック図である。図 1 及び図 6 を参照すると、図 1 の SoC 100 の更に他の実施形態による SoC 100D は、バス 110、CPU 120、メモリコントローラ 130、不揮発性メモリコントローラ 140、暗号化 / 復号化エンジン 150、第 1OTP メモリ 160、及び DMA ユニット 170 を含む。

#### 【0051】

DMA ユニット 170 は、バス 110 と暗号化 / 復号化エンジン 150 との間に接続される。データは、DMA ユニット 170 と暗号化 / 復号化エンジン 150 との間で、オンザフライで伝送される。

20

#### 【0052】

不揮発性メモリ装置 200 が、データをライトする時のライトデータパス WP を説明すると、メインメモリ 300 から出力された平文データは、メモリコントローラ 130、バス 110、及び DMA ユニット 170 を介して暗号化 / 復号化エンジン 150 に伝送される。

#### 【0053】

暗号化 / 復号化エンジン 150 は、平文データを暗号文データに変換、例えば暗号化する。暗号文データは、不揮発性メモリコントローラ 140 を介して不揮発性メモリ装置 200 に伝送される。この際、暗号化 / 復号化エンジン 150 は、不揮発性メモリコントローラ 140 に暗号文データを直接、例えばオンザフライで伝送する。

30

#### 【0054】

不揮発性メモリ装置 200 が、データをリードする時のリードデータパス RP を説明すると、不揮発性メモリ装置 200 から出力された暗号文データは、不揮発性メモリコントローラ 140 を介して暗号化 / 復号化エンジン 150 に伝送される。この際、暗号化 / 復号化エンジン 150 は、不揮発性メモリコントローラ 140 から暗号文データを直接、例えばオンザフライで受信する。

#### 【0055】

暗号化 / 復号化エンジン 150 は、暗号文データを平文データに変換、例えば復号化する。平文データは、DMA ユニット 170、バス 110、及びメモリコントローラ 130 を介してメインメモリ 300 に伝送される。

40

#### 【0056】

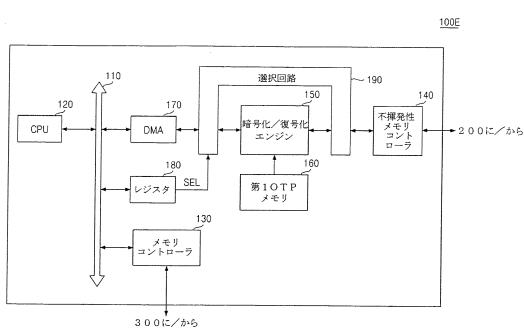

図 7 は、図 1 に示したシステムオンチップの更に他の実施形態によるブロック図である。図 1、図 3、及び図 7 を参照すると、図 1 の SoC 100 の更に他の実施形態による SoC 100E は、バス 110、CPU 120、メモリコントローラ 130、不揮発性メモリコントローラ 140、暗号化 / 復号化エンジン 150、第 1OTP メモリ 160、DMA ユニット 170、レジスタ 180、及び選択回路 190 を含む。

#### 【0057】

レジスタ 180 は、バス 110 に接続される。レジスタ 180 は、選択信号 SEL を発生する選択信号発生器として作動する。レジスタ 180 は、CPU 120 がセキュリティ応用プログラムを実行するか否か、即ちセキュリティモードを指示する指示信号に基づい

50

て選択信号 S E L を変更する。指示信号は、C P U 1 2 0 から出力される。

【 0 0 5 8 】

例えは、セキュリティモードで、指示信号のロジックレベルは、ハイ ( h i g h ) であり、非セキュリティモードで、指示信号のロジックレベルは、ロー ( l o w ) である。選択回路 1 9 0 は、レジスタ 1 8 0 から出力された選択信号 S E L によってデータパスを選択する。選択回路 1 9 0 の構造と動作は、図 8 を参照して詳しく説明する。

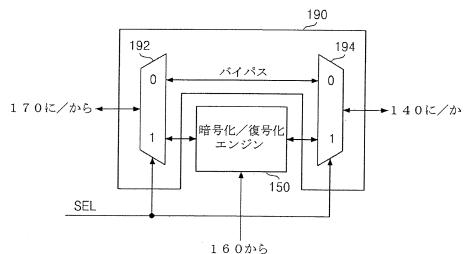

【 0 0 5 9 】

図 8 は、図 7 に示した選択回路及び暗号化 / 復号化エンジンのブロック図である。図 3 、図 7 、及び図 8 を参照すると、選択回路 1 9 0 は、第 1 選択器 1 9 2 と第 2 選択器 1 9 4 とを含む。

10

【 0 0 6 0 】

第 1 選択器 1 9 2 は、デマルチプレクサとして具現可能であり、第 2 選択器 1 9 4 は、マルチプレクサとして具現可能である。

【 0 0 6 1 】

選択回路 1 9 0 は、選択信号 S E L のロジックレベルがハイである時、データが暗号化 / 復号化エンジン 1 5 0 を含むデータパスを選択する。C P U 1 2 0 がセキュリティ応用プログラムを実行する時、即ちセキュリティモードである時、選択回路 1 9 0 は、暗号化 / 復号化エンジン 1 5 0 を含むデータパスを選択する。しかし、選択回路 1 9 0 は、選択信号 S E L のロジックレベルがローである時、暗号化 / 復号化エンジン 1 5 0 を含まないデータパス、即ちバイパスを選択することができる。実施形態として、C P U 1 2 0 が一般応用プログラムを実行する時、即ち非セキュリティモードである時、選択回路 1 9 0 は、暗号化 / 復号化エンジン 1 5 0 を含まないデータパス、即ちバイパスを選択する。

20

【 0 0 6 2 】

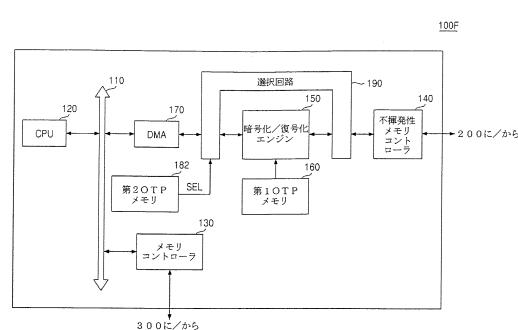

図 9 は、図 1 に示したシステムオンチップの更に他の実施形態によるブロック図である。図 1 、図 8 、及び図 9 を参照すると、図 1 の S o C 1 0 0 の更に他の実施形態による S o C 1 0 0 F は、バス 1 1 0 、C P U 1 2 0 、メモリコントローラ 1 3 0 、不揮発性メモリコントローラ 1 4 0 、暗号化 / 復号化エンジン 1 5 0 、第 1 O T P メモリ 1 6 0 、D M A ユニット 1 7 0 、第 2 O T P メモリ 1 8 2 、及び選択回路 1 9 0 を含む。

【 0 0 6 3 】

第 2 O T P メモリ 1 8 2 は、選択信号 S E L を発生する選択信号発生器として作動する。第 2 O T P メモリ 1 8 2 は、1 つのレベル、例えはハイレベルを有する選択信号 S E L を発生するようにプログラムされる。この際、選択回路 1 9 0 は、暗号化 / 復号化エンジン 1 5 0 を含むデータパスのみを選択する。

30

【 0 0 6 4 】

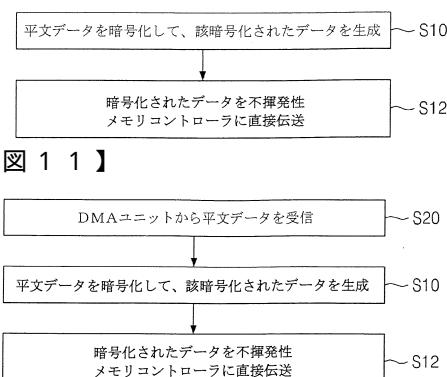

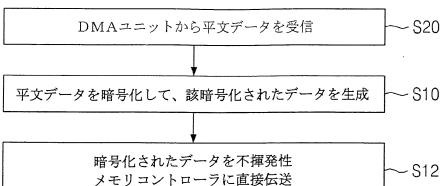

図 1 0 は、本発明の一実施形態によるシステムオンチップの動作方法を説明するフローチャートである。図 2 、図 4 ~ 図 7 、図 9 、及び図 1 0 を参照すると、暗号化 / 復号化エンジン 1 5 0 は、暗号キーを用いて平文データを暗号文データに変換、即ち暗号化する (ステップ S 1 0 )。

【 0 0 6 5 】

暗号化 / 復号化エンジン 1 5 0 は、暗号化データを不揮発性メモリコントローラ 1 4 0 に直接、例えはオンザフライで伝送する (ステップ S 1 2 )。従って、暗号キーと暗号化データは、S o C 1 0 0 の内部に存在するため、プロービングに強い効果がある。

40

【 0 0 6 6 】

図 1 1 は、本発明の他の実施形態によるシステムオンチップの動作方法を説明するフローチャートである。図 5 ~ 図 7 、図 9 、及び図 1 1 を参照すると、暗号化 / 復号化エンジン 1 5 0 は、平文データを D M A ユニット 1 7 0 から受信する (ステップ S 2 0 )。暗号化 / 復号化エンジン 1 5 0 は、平文データを D M A ユニット 1 7 0 から直接、例えはオンザフライで受信する。

【 0 0 6 7 】

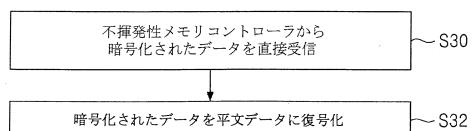

図 1 2 は、本発明の更に他の実施形態によるシステムオンチップの動作方法を説明する

50

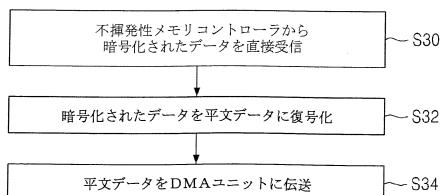

フロー チャートである。図2、図4～図7、図9、及び図12を参照すると、暗号化／復号化エンジン150は、不揮発性メモリコントローラ140から暗号文データを直接、例えばオンザフライで受信する（ステップS30）。暗号化／復号化エンジン150は、暗号文データを平文データに復号化する（ステップS32）。

【0068】

図13は、本発明の更に他の実施形態によるシステムオンチップの動作方法を説明するフロー チャートである。図5～図7、図9、及び図13を参照すると、暗号化／復号化エンジン150は、平文データをDMAユニット170に伝送する（ステップS34）。暗号化／復号化エンジン150は、平文データをDMAユニット170に直接、例えばオンザフライで伝送する。

10

【0069】

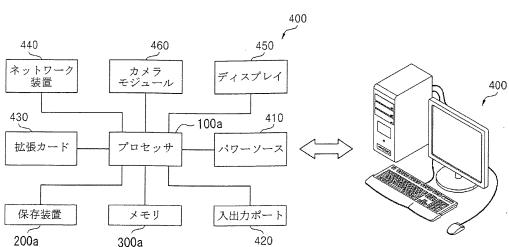

図14は、図1に示したシステムを含むデータ処理装置の一実施形態によるブロック図である。図1及び図14を参照すると、データ処理装置400は、PC又はデータサーバとして具現可能である。

【0070】

データ処理装置400は、プロセッサ100a、保存装置200a、メモリ300a、パワーソース410、入出力ポート420、拡張カード430、ネットワーク装置440、及びディスプレイ450を含む。実施形態として、データ処理装置400は、カメラモジュール460を更に含み得る。

【0071】

プロセッサ100aは、図1に示したSOC100を意味する。プロセッサ100aは、マルチコア（Multi-Core）プロセッサであり得る。実施形態として、プロセッサ100aは、図1に示したSOC100を含む。プロセッサ100aは、構成要素（200a、300a、及び410～460）のうちの少なくとも1つの動作を制御する。

20

【0072】

保存装置200aは、図1に示した不揮発性メモリ装置200を意味する。保存装置200aは、ハードディスクドライブ（Hard Disk Drive）又はSSD（Solid State Drive）として具現可能である。

【0073】

メモリ300aは、図1に示したメインメモリ300を意味する。メモリ300aは、揮発性メモリ又は不揮発性メモリとして具現可能である。メモリ300aに対するデータアクセス動作、例えばリード動作、ライト動作（又は、プログラム動作）、又はイレーズ動作を制御するメモリコントローラ（図2の140）は、プロセッサ100に集積又は内蔵され得る。

30

【0074】

パワーソース410は、構成要素（100a、200a、300a及び420～460）のうちの少なくとも1つに動作電圧を供給する。

【0075】

入出力ポート420は、保存装置200aにデータを伝送するか、保存装置200aから出力されたデータを外部装置に伝送するポートを意味する。例えば、入出力ポート420は、コンピュータマウスのようなポインティング装置（pointing device）を接続するためのポート、プリンターを接続するためのポート、又はUSB（Universal Serial Bus）ドライブを接続するためのポートである。

40

【0076】

拡張カード430は、SD（Secure Digital）カード又はMMC（MultiMedia Card）として具現可能である。実施形態として、拡張カード430は、SIM（Subscriber Identification Module）カード又はUSIM（Universal Subscriber Identity Module）カードであり得る。

【0077】

50

ネットワーク装置 440 は、保存装置 200a を有線ネットワーク又は無線ネットワークに接続させる装置を意味する。

【0078】

ディスプレイ 450 は、保存装置 200a、メモリ 300a、入出力ポート 420、拡張カード 430、又はネットワーク装置 440 から出力されたデータを表示する。カメラモジュール 460 は、光学イメージを電気的なイメージに変換するモジュールを意味する。従って、カメラモジュール 460 から出力された電気的なイメージは、保存装置 200a、メモリ 300a、又は拡張カード 430 に保存される。また、カメラモジュール 460 から出力された電気的なイメージは、ディスプレイ 450 を通じて表示される。

【0079】

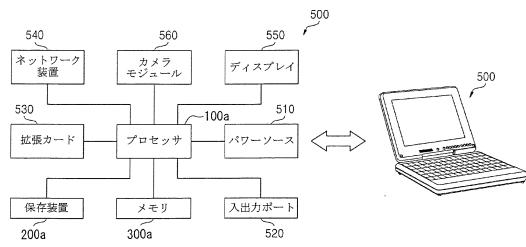

図 15 は、図 1 に示したシステムを含むデータ処理装置の他の実施形態によるブロック図である。図 1 及び図 15 を参照すると、データ処理装置 500 は、ラップトップ (laptop) コンピュータとして具現可能である。

【0080】

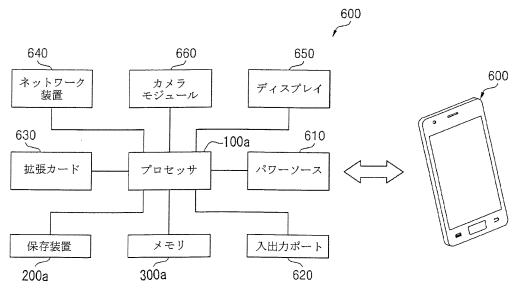

図 16 は、図 1 に示したシステムを含むデータ処理装置の更に他の実施形態によるブロック図である。図 1 及び図 16 を参照すると、データ処理装置 600 は、携帯用装置として具現可能である。携帯用装置 600 は、携帯電話、スマートフォン、タブレット PC、PDA、EDA、デジタルスチルカメラ、デジタルビデオカメラ、PMP、PDN、携帯用ゲームコンソール、又は電子ブックとして具現可能である。

【0081】

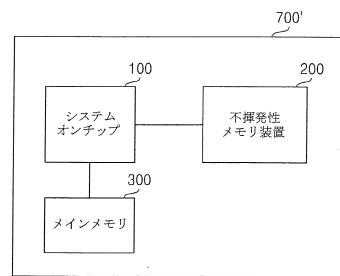

図 17 は、図 1 に示したシステムオンチップを含むシステムインパッケージ及び不揮発性メモリ装置のブロック図であり、図 18 は、図 1 に示したシステムオンチップを含むシステムインパッケージの他の実施形態によるブロック図である。図 1 及び図 17 を参照すると、SoC 100 及びメインメモリ 300 は、システムインパッケージ (SiP) 700 にパッケージングされる。図 1 及び図 18 を参照すると、SoC 100、不揮発性メモリ装置 200、及びメインメモリ 300 は、SiP 700 にパッケージングされる。

【0082】

以上、本発明の実施形態について図面を参照しながら詳細に説明したが、本発明は、上述の実施形態に限定されるものではなく、本発明の技術的範囲から逸脱しない範囲内で多様に変更実施することが可能である。

【符号の説明】

【0083】

|                                   |               |    |

|-----------------------------------|---------------|----|

| 10                                | システム          |    |

| 100、100A、100B、100C、100D、100E、100F | システム          |    |

| オンチップ (SoC)                       |               |    |

| 100a                              | プロセッサ         |    |

| 110                               | バス            |    |

| 120                               | CPU           |    |

| 130                               | メモリコントローラ     |    |

| 140                               | 不揮発性メモリコントローラ | 40 |

| 150                               | 暗号化 / 復号化エンジン |    |

| 160                               | 第 1 OTP メモリ   |    |

| 170                               | DMA ユニット      |    |

| 180                               | レジスタ          |    |

| 182                               | 第 2 OTP メモリ   |    |

| 190                               | 選択回路          |    |

| 192                               | 第 1 選択器       |    |

| 194                               | 第 2 選択器       |    |

| 200                               | 不揮発性メモリ装置     |    |

| 200a                              | 保存装置          | 50 |

|                   |                   |    |

|-------------------|-------------------|----|

| 3 0 0             | メインメモリ            |    |

| 3 0 0 a           | メモリ               |    |

| 4 0 0、5 0 0、6 0 0 | データ処理装置           |    |

| 4 1 0、5 1 0、6 1 0 | パワーソース            |    |

| 4 2 0、5 2 0、6 2 0 | 入出力ポート            |    |

| 4 3 0、5 3 0、6 3 0 | 拡張カード             |    |

| 4 4 0、5 4 0、6 4 0 | ネットワーク装置          |    |

| 4 5 0、5 5 0、6 5 0 | ディスプレイ            |    |

| 4 6 0、5 6 0、6 6 0 | カメラモジュール          |    |

| 7 0 0、7 0 0       | システムインパッケージ (SIP) | 10 |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

〔 9 〕

【 囮 1 0 】

【図 1 1 】

〔圖7〕

〔 四 8 〕

【 义 1 2 】

【 13 】

【图 1-4】

【図15】

【図16】

【図17】

【図18】

---

フロントページの続き

(72)発明者 崔 弘 黙

大韓民国 京畿道 富川市 遠美区 上二洞 ハヤンマウル 2618棟 2103号

(72)発明者 朴 相 ヒョン

大韓民国 ソウル特別市 麻浦区 城山洞 604番地 城山二次イーピヨンハンセサンアパート

201棟 1202号

審査官 宮司 卓佳

(56)参考文献 特開2012-004661 (JP, A)

特表2010-525435 (JP, A)

特開2003-198531 (JP, A)

特開2010-231778 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H04L 9/10