(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4027709号

(P4027709)

(45) 発行日 平成19年12月26日(2007.12.26)

(24) 登録日 平成19年10月19日(2007.10.19)

(51) Int.C1.

F 1

|                |                |                  |         |       |         |

|----------------|----------------|------------------|---------|-------|---------|

| <b>G 1 1 C</b> | <b>11/4076</b> | <b>(2006.01)</b> | G 1 1 C | 11/34 | 3 5 4 C |

| <b>G 1 1 C</b> | <b>11/4093</b> | <b>(2006.01)</b> | G 1 1 C | 11/34 | 3 5 4 P |

| <b>G 1 1 C</b> | <b>11/407</b>  | <b>(2006.01)</b> | G 1 1 C | 11/34 | 3 6 2 S |

請求項の数 3 (全 8 頁)

(21) 出願番号 特願2002-126981 (P2002-126981)

(22) 出願日 平成14年4月26日 (2002.4.26)

(65) 公開番号 特開2003-36674 (P2003-36674A)

(43) 公開日 平成15年2月7日 (2003.2.7)

審査請求日 平成16年8月13日 (2004.8.13)

(31) 優先権主張番号 2001-022982

(32) 優先日 平成13年4月27日 (2001.4.27)

(33) 優先権主張国 韓国 (KR)

(73) 特許権者 390019839

三星電子株式会社

Samsung Electronics

Co., Ltd.

大韓民国京畿道水原市靈通区梅灘洞 416

(74) 代理人 100076428

弁理士 大塚 康徳

(74) 代理人 100112508

弁理士 高柳 司郎

(74) 代理人 100115071

弁理士 大塚 康弘

(74) 代理人 100116894

弁理士 木村 秀二

最終頁に続く

(54) 【発明の名称】半導体メモリ装置の入力回路

## (57) 【特許請求の範囲】

## 【請求項 1】

該当する入力データをそれぞれバッファリングするための複数の入力バッファと、パワーアップされてからモードレジスタセット信号がイネーブルされるまでは第1論理レベルに保持され、その後に第2論理レベルに保持される選択信号に応答して、前記選択信号が前記第1論理レベルである間は第1クロック信号及びデータストローブ信号のうち前記第1クロック信号を選択して第2クロック信号を発生し、前記選択信号が前記第2論理レベルである間は前記第1クロック信号及び前記データストローブ信号のうち前記データストローブ信号を選択して前記第2クロック信号を発生するクロック選択回路と、

前記第2クロック信号に応答してレジスタクロック信号を発生するキャリブレーション回路と、

前記レジスタクロック信号に応答して、バッファリングされた複数の入力データのうち該当する入力データを格納する複数のデータレジスタとを含むことを特徴とする半導体メモリ装置の入力回路。

## 【請求項 2】

前記クロック選択回路は、一端が1供給電圧に接続され、ゲートが前記選択信号に接続された第1PMOSトランジスタと、

第1入力端子に前記データストローブ信号が印加され、第2入力端子に基準電圧が印加され、第3入力端子に前記第1PMOSトランジスタの他端が接続された第1バッファと

10

20

、一端が前記第1バッファの出力端子に接続され、他端が接地に接続され、ゲートに前記選択信号が印加される第1N MOSトランジスタと、

前記第1クロック信号が印加される第1入力端子と、それが反転されたクロック信号を受け入れる第2入力端子を備えた第2バッファと、

前記第1バッファの前記出力端子に接続された入力端子を備えたインバータと、

前記選択信号と前記第2バッファの出力信号とを入力として論理演算をする第1ロジック回路と、

前記第1ロジック回路の出力信号と前記インバータの出力信号とを入力として論理演算をする第2ロジック回路とを含むことを特徴とする請求項1に記載の半導体メモリ装置の10

入力回路。

### 【請求項3】

半導体メモリ装置のための入力回路のクロック信号選択方法において、

パワーアップされてからモードレジスタセット信号がイネーブルされまで第1論理状態にある選択信号に応答して第1クロック信号を第2クロック信号として提供する段階と、

前記モードレジスタセット信号がイネーブルされ前記選択信号が第2論理状態になったことに応答してデータストローブ信号を前記第2クロック信号として提供する段階と、

前記第2クロック信号に応答してレジスタクロック信号を発生する段階と、

前記レジスタクロック信号に応答して前記入力データをレジスタリングする段階とを含むことを特徴とするクロック信号選択方法。20

### 【発明の詳細な説明】

#### 【0001】

#### 【発明の属する技術分野】

本発明は半導体メモリ装置に関連し、特に半導体メモリ装置の入力回路に関する。

#### 【0002】

#### 【従来の技術】

半導体メモリ装置の動作周波数は、関連技術の発展に従って改善され続けている。その結果、データが入力される際のセットアップ／ホールドウインドが減少している。そのような問題を解決するために、DDR (Double Data Rate) SDRAM (Synchronous Dynamic Random Access Memory)においてデータストローブ信号を利用してトラッキングする方法などが考案された。30

#### 【0003】

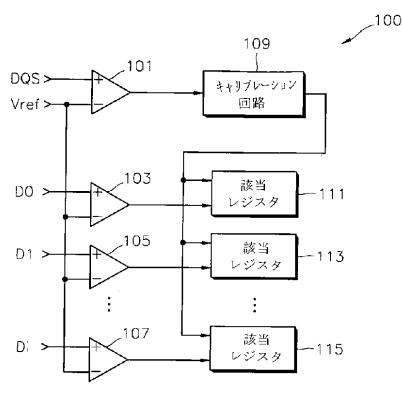

図1は半導体メモリ装置の入力回路100のブロック図である。

#### 【0004】

図1を参照すれば、半導体メモリ装置の入力回路100は、複数の入力バッファ101,...,107、キャリブレーション回路109及び複数のデータレジスタ111,...,115を備える。

#### 【0005】

半導体メモリ装置入力回路100は、複数の入力データD0,D1,...,Diを所定時間内に該当するレジスタ111,...,115にそれぞれ格納する機能を有する。40

#### 【0006】

キャリブレーション回路109は、相異なる遅延特性を同一にする信号伝達回路である。キャリブレーション回路109は、データストローブ信号DQSに応答して、データストローブ信号DQSを制御するための制御クロック信号を発生する。キャリブレーション回路109は、入力経路により相異なる遅延時間を有する入力データD0,D1,...,Diを同期させる。このようなキャリブレーション回路は、大韓民国出願番号第10-2000-0035335号に詳細に説明されている。

#### 【0007】

半導体メモリ装置に入力される入力データD0,D1,...,Diは、回路及び各素子の配置特性のために相異なる遅延時間を持って該当レジスタに伝えられる。前記入力データを50

該当レジスタに格納する制御クロック信号は、キャリブレーション回路 109においてデータストローブ信号 DQS に応答して生成される。従って、入力データ D0, D1, ..., Di は、キャリブレーション回路 109による信号出力に応答して該当レジスタ 111, ..., 115 に格納される。

#### 【0008】

データストローブ信号 DQS は、活性化された書き込み命令（図示せず）に応答してイネーブルされる。従って、データストローブ信号 DQS は最初の書き込み動作まで何らの変化も起きない。そして、所定時間内に該当レジスタ 111, ..., 115 に入力データを格納するための制御クロック信号は、電源がオンされた直後から最初の書き込み動作までは、データストローブ信号 DQS を利用してキャリブレーション回路 109 で生成されることはない。

#### 【0009】

##### 【発明が解決しようとする課題】

本発明が解決しようとする課題は、半導体メモリ装置の短所を克服するところにある。

#### 【0010】

本発明が解決しようとする他の課題は、電源が最初にオンになった後からデータストローブ信号がイネーブルされるまでの入力回路の誤動作を防止するクロック選択部を備えた半導体メモリ装置を提供するところにある。

#### 【0011】

本発明が解決しようとする更に他の課題は、電源が最初にオンになった後、データストローブ信号がイネーブルされるまでの間における入力回路の誤動作を防止するために、半導体メモリ装置の入力回路に適用されるクロック信号の選択方法を提供するところにある。

#### 【0012】

##### 【課題を解決するための手段】

前記課題を達成するための本発明によれば、前記半導体メモリ装置のための入力回路は、該当入力データをバッファリングする複数の入力バッファと、選択信号に応答して第1クロック信号とデータストローブ信号のうち一つを選択して第2クロック信号を発生するクロック選択回路とを備える。前記選択信号は、パワーアップ以後の所定時間、第1ロジックレベルを保持する。キャリブレーション回路は、第2クロック信号に応答してレジスタクロック信号を発生するために使われる。

#### 【0013】

前記クロック選択回路は、前記選択信号が第1ロジックレベルの場合には前記第2クロック信号として前記第1クロック信号を選択して出力し、前記選択信号が第2ロジックレベルの場合には前記第2クロック信号として前記データストローブ信号を出力する。

#### 【0014】

本発明の望ましい実施形態によれば、前記クロック選択回路は、一端が1供給電圧に接続され、ゲートが前記選択信号に接続された第1PMOSトランジスタと、第1入力端子に前記データストローブ信号が印加され、第2入力端子に基準電圧が印加され、第3入力端子に前記第1PMOSトランジスタの他端が接続される第1バッファとを備える。第1NMOSトランジスタは、一端が前記第1バッファの出力端子に接続され、他端が接地に接続され、ゲートに前記選択信号が印加される。第2バッファは、第1クロック信号が印加される第1入力端子と、反転されたクロック信号を受け入れる第2入力端子とを備える。インバータは、前記第1バッファの前記出力端子に接続された入力端子を備える。第1ロジック回路は、前記選択信号と前記第2バッファの出力信号とを入力として論理演算を実行する。そして、第2ロジック回路は、前記第1ロジックゲートの出力信号と前記第1インバータの出力信号とを入力として論理演算を実行する。

#### 【0015】

本発明の望ましい実施形態において、前記所定時間区間は、例えば、パワーアップされてからモードレジスタセット信号がイネーブルされるまでの時間である。

#### 【0016】

10

20

30

40

50

或いは、前記所定時間区間は、例えば、パワーアップされてから前記データストローブ信号がイネーブルされるまでの時間であってもよい。

**【0017】**

半導体メモリ装置のための入力回路のクロック信号選択方法がさらに提供される。前記方法は、第1論理状態にある選択信号に応答して第1クロック信号を第2クロック信号として提供する段階、第2論理状態にある前記選択信号に応答してデータストローブ信号を前記第2クロック信号として提供する段階、前記第2クロック信号に応答してレジスタクロック信号を発生する段階、及び、前記レジスタクロック信号に応答して前記入力データをレジスタリングする段階を含む。

**【0018】**

前記方法は、前記選択信号をパワーアップした後に所定時間、前記第2ロジック状態にセッティングする段階をさらに含むことが望ましい。

**【0019】**

前記方法は、モードセットレジスタ信号がイネーブルされた後に前記選択信号を前記第1論理状態にセッティングする段階、及び、前記データストローブ信号がイネーブルされた後に前記選択信号を前記第2論理状態にセッティングする段階をさらに含むことが望ましい。

**【0020】**

前記方法は、モードセットレジスタ信号のイネーブル後に前記選択信号を前記第1論理状態にセッティングする段階、及び、前記データストローブ信号のイネーブル後に前記選択信号を前記第2論理状態にセッティングする段階をさらに含むことが望ましい。

10

20

**【0021】**

**【発明の実施の形態】**

以下、添付した図面を参照して本発明の望ましい実施形態を説明することにより、本発明を詳細に説明する。各図面について、同じ参照符号は同じ構成要素であることを表す。

**【0022】**

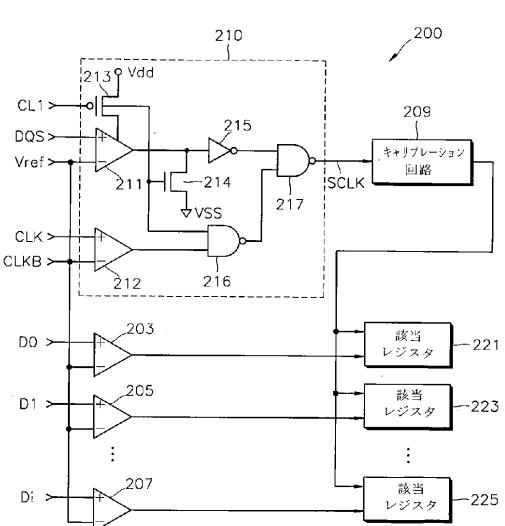

図2は、本発明の一実施形態による半導体メモリ装置入力回路のブロック図である。

**【0023】**

図2を参照すれば、半導体メモリ装置の入力回路200は、複数の入力バッファ203, ..., 207、クロック選択回路210、キャリブレーション回路209及び複数のデータレジスタ221, ..., 225を備える。

30

**【0024】**

入力バッファ203, ..., 207を介して入力される入力データは、キャリブレーション回路209の出力信号に応答して複数のデータレジスタ221, ..., 225のうち該当するデータレジスタにそれぞれ貯蔵される。

**【0025】**

キャリブレーション回路209は、相異なる遅延特性を同一にするための信号伝達回路である。キャリブレーション回路209は、クロック選択回路210の出力信号SCLKを受信し、入力されるバスにより相異なる遅延時間をもって入力される入力データD0, D1, ..., Diを同期させるための制御クロック信号を出力する。

40

**【0026】**

入力データD0, D1, ..., Diは、回路及び各素子の配置特性のために相異なる遅延時間有する。入力データD0, D1, ..., Diは、該当レジスタ221~225に伝えられる。制御クロック信号は、入力データを該当レジスタ内に格納するのに使われる。制御クロック信号は、第2クロック信号SCLKに応答してキャリブレーション回路209により生成される。制御クロック信号は、データが所定時間内に該当レジスタに貯蔵されるように前記入力データに同期させられる。

**【0027】**

複数のデータD0, D1, ..., Diは、キャリブレーション回路209から出力される信号に応答して該当レジスタ221~225に格納される。

50

**【0028】**

クロック選択回路210は、第1PMOSトランジスタ213、第1バッファ211、第1NMOSトランジスタ214、第2バッファ212、第1インバータ215、第1NANDゲート216及び第2NANDゲート217を備える。

**【0029】**

第1PMOSトランジスタ213は、一端が電源供給電圧Vddに接続され、ゲートが選択信号CL1に接続される。データストローブ信号DQSは、第1バッファ211の第1入力端子に印加され、基準電圧Vrefは第2入力端子に印加される。第1バッファ211の動作は、第1PMOSトランジスタ213の他端から供給される電流により制御される。第1NMOSトランジスタ214は、一端が第1バッファ211の出力端子に接続され、他端が接地電圧Vssに接続される。選択信号CL1は、第1NMOSトランジスタ214のゲートに印加される。10

**【0030】**

クロック信号CLKは第2バッファ212の第1入力端子に印加され、反転信号CLKBはその第2入力端子に印加される。第1インバータ215の入力端子は、第1バッファ211の出力端子に接続される。第1NANDゲート216は、選択信号CL1及び第2バッファ212の出力信号に応答する。第2NANDゲート217は、第1インバータ215の出力信号及び第1NANDゲート216の出力信号に応答して第1クロック信号SCLKを出力する。

**【0031】**

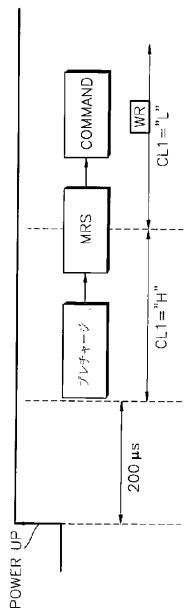

図3は、図2に示された入力回路200の動作を時間別に区分したタイミング図である。20

**【0032】**

図3を参照すれば、電源がオンされた後に所定時間（例えば、約200μs）の非動作期間を経た後にプリチャージされ、信号CL1の値はMRS（Mode Register Set）が所定の値にセッティングされるまでハイ状態Hを保持する。前記MRSが所定の値にセッティングされれば、信号CL1の値がロー状態Lに変化し、この時初めて命令信号COMMAND及び書き込み命令信号WRが活性化される。

**【0033】**

図2及び図3を参照して本発明の望ましい実施形態による半導体メモリ装置入力回路200について説明する。30

**【0034】**

クロック選択回路210は、電源が最初に供給された時から一定の時間区間（例えば、約200μs）の間、所定の第1ロジックレベル(CL1=H)を保持し、前記時間区間後に第1ロジックレベル(CL1=H)と反対の第2ロジックレベル(CL1=L)を有する選択信号CL1を受信する。クロック選択回路210は、選択信号CL1が第1ロジックレベル(CL1=H)である場合にはクロック信号CLKを選択して第1クロック信号SCLKとして出力し、選択信号CL1が第2ロジックレベル(CL1=L)である場合にはデータストローブ信号DQSを選択して第1クロック信号SCLKとして出力する。

**【0035】**

キャリブレーション回路209は、第1クロック信号SCLKを受信し、入力データD0,D1,...,Diとその受信した第1クロック信号SCLKとを同期させるキャリブレーションを行った後に制御クロック信号を出力する。キャリブレーション回路209の制御クロック信号により前記入力バッファを介して入力される入力データを該当するレジスタに格納すれば、高速化された半導体メモリ装置のセットアップ/ホールドウインドが小さい場合にもエラーなく前記入力データを格納できる。40

**【0036】**

図2に示された基準電圧Vref及びクロック信号CLKの反転信号CLKBは、使われない場合もある。

**【0037】****【発明の効果】**

前述の通り、本発明によるクロック選択回路を備える半導体メモリ入力回路及びクロック信号選択方法は、相異なる遅延時間をもって入力される入力データを、半導体メモリ装置が動作している時間区間に関係なく、正確にレジスタに格納することができるという利点がある。

**【図面の簡単な説明】**

【図1】半導体メモリ装置入力回路100のブロック図である。

【図2】本発明の一実施形態による半導体メモリ装置の入力回路のブロック図である。

【図3】図2に示された入力回路の動作を時間別に区分したタイミング図である。

**【符号の説明】**

|             |              |    |

|-------------|--------------|----|

| 200         | 半導体メモリ装置入力回路 | 10 |

| 203、205、207 | 入力バッファ       |    |

| 209         | キャリブレーション回路  |    |

| 210         | クロック選択回路     |    |

| 211         | 第1バッファ       |    |

| 212         | 第2バッファ       |    |

| 213         | 第1PMOSトランジスタ |    |

| 214         | 第1NMOSトランジスタ |    |

| 215         | 第1インバータ      |    |

| 216         | 第1NANDゲート    |    |

| 217         | 第2NANDゲート    | 20 |

| 221~225     | レジスタ         |    |

【図1】

【図2】

【図3】

---

フロントページの続き

(72)発明者 崔東俊

大韓民国ソウル特別市銅雀区新大方1洞686-9番地401号

(72)発明者 鄭大鉉

大韓民国京畿道龍仁市器興邑農書里山7-1番地月桂樹棟814号

(72)発明者 黃祥俊

大韓民国ソウル特別市瑞草区瑞草洞新東亞アパート3棟514号

審査官 堀田 和義

(56)参考文献 特開平10-308093(JP,A)

特開平10-320074(JP,A)

特開2004-103061(JP,A)

(58)調査した分野(Int.Cl., DB名)

G11C 11/4076