(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-63996

(P2004-63996A)

(43) 公開日 平成16年2月26日(2004.2.26)

(51) Int.Cl.<sup>7</sup>

H01L 21/3205

H01L 21/60F 1

H01L 21/88

H01L 21/60T

301Pテーマコード (参考)

5FO33

5FO44

審査請求 未請求 請求項の数 38 O L (全 24 頁)

(21) 出願番号 特願2002-223484 (P2002-223484)

(22) 出願日 平成14年7月31日 (2002.7.31)(71) 出願人 000005821

松下電器産業株式会社

大阪府門真市大字門真1006番地

(74) 代理人 100077931

弁理士 前田 弘

(74) 代理人 100094134

弁理士 小山 廣毅

(74) 代理人 100110939

弁理士 竹内 宏

(74) 代理人 100110940

弁理士 嶋田 高久

(74) 代理人 100113262

弁理士 竹内 祐二

(74) 代理人 100115059

弁理士 今江 克実

最終頁に続く

(54) 【発明の名称】半導体装置及びその製造方法

## (57) 【要約】

【課題】埋め込み配線における腐食の発生を防止し、信頼性の高い半導体装置及びその製造方法を提供する。

【解決手段】半導体装置の製造方法は、基板31上に第1絶縁膜32を形成する工程と、第1絶縁膜32に第1埋め込み配線34を形成する工程と、第1埋め込み配線34を含む基板上に第2絶縁膜35を形成する工程と、第2絶縁膜35から第1絶縁膜32にまたがり、ボンディングパッドとなる第2埋め込み配線42を形成する工程とを含んでいる。第1埋め込み配線34及び第2埋め込み配線42を形成する際のCMP時に第1埋め込み配線34と第2埋め込み配線42とが同時に研磨液に触れないで、第1埋め込み配線34に腐食が発生するのを防ぐことができる。

【選択図】 図2

**【特許請求の範囲】****【請求項 1】**

半導体基板と、上記半導体基板上に設けられた複数の半導体素子と、上記半導体基板及び上記半導体素子の上方に設けられた第1絶縁膜と、上記第1絶縁膜の上に設けられた第2の絶縁膜と、複数の配線層とを備える半導体装置であって、

上記配線層は、

上記第1絶縁膜に設けられた第1トレンチを埋める導電体からなる第1の配線と、

上記第1の配線の一部と異なる配線幅を有し、少なくとも上記第2絶縁膜に設けられた第2トレンチを埋めて、上記第2の配線と電気的に接続される導電体からなる第2の配線と

を有している半導体装置。

10

**【請求項 2】**

請求項1に記載の半導体装置において、

上記第2の配線のうち少なくとも一部はボンディングパッド、電源ライン及び接地ラインのうちのいずれかであることを特徴とする半導体装置。

**【請求項 3】**

請求項2に記載の半導体装置において、

上記第1の配線と上記第2の配線は共に上記配線層のうち最上の配線層内に設けられており、

上記第2の配線のうち少なくとも一部はボンディングパッドであることを特徴とする半導体装置。

20

**【請求項 4】**

請求項2または3に記載の半導体装置において、

上記第1の配線の少なくとも一部と上記第2の配線の少なくとも一部は互いに接触していることを特徴とする半導体装置。

**【請求項 5】**

請求項4に記載の半導体装置において、

上記第1の配線は互いに分離された複数箇所に設けられており、

上記第1の配線のうち少なくとも2つの配線は、上記第2の配線を介して電気的に接続されていることを特徴とする半導体装置。

30

**【請求項 6】**

請求項2～4のうちいずれか1つに記載の半導体装置において、

上記第2の配線は、上記第2絶縁膜から上記第1絶縁膜に亘って設けられていることを特徴とする半導体装置。

**【請求項 7】**

請求項3～6のうちいずれか1つに記載の半導体装置において、

上記第2絶縁膜の上には第3絶縁膜がさらに設けられており、

上記第2埋め込み配線の上には、上記第3絶縁膜を貫通して設けられた導電体からなる接続部材がさらに設けられていることを特徴とする半導体装置。

**【請求項 8】**

請求項2または3に記載の半導体装置において、

上記半導体基板は下層配線をさらに有しており、

上記第1絶縁膜を貫通して設けられ、上記第1の配線と上記下層配線とを結ぶ第1プラグと、

上記第1絶縁膜を貫通して設けられ、上記第2の配線と上記下層配線とを結ぶ第2プラグと

をさらに備えていることを特徴とする半導体装置。

**【請求項 9】**

請求項2または3に記載の半導体装置において、

上記半導体基板は不純物拡散層をさらに有しており、

上記第1絶縁膜を貫通して設けられ、上記第1の配線と上記不純物拡散層とを電気的に接

50

続する第1プラグと、

上記第1絶縁膜を貫通して設けられ、上記第2の配線と上記不純物拡散層とを電気的に接続する第2プラグと

をさらに備えていることを特徴とする半導体装置。

【請求項10】

請求項2または3に記載の半導体装置において、

上記半導体素子はゲート電極を有しており、

上記第1絶縁膜を貫通して設けられ、上記第1の配線と上記ゲート電極とを電気的に接続する第1プラグと、

上記第1絶縁膜を貫通して設けられ、上記第2の配線と上記ゲート電極とを電気的に接続する第2プラグと

10

をさらに備えていることを特徴とする半導体装置。

【請求項11】

請求項2～10のうちいずれか1つに記載の半導体装置において、

上記第2の配線のうちボンディングパッド、電源ライン及び接地ラインのいずれかとして機能する部分の配線幅は20μm以上であることを特徴とする半導体装置。

【請求項12】

請求項1に記載の半導体装置において、

上記第1の配線のうち少なくとも一部はボンディングパッド、電源ライン及び接地ラインのうちのいずれかであることを特徴とする半導体装置。

20

【請求項13】

請求項12に記載の半導体装置において、

上記第1の配線と上記第2の配線は共に上記配線層のうち最上の配線層内に設けられており、

上記第1の配線のうち少なくとも一部はボンディングパッドであることを特徴とする半導体装置。

【請求項14】

請求項12または13に記載の半導体装置において、

上記第1の配線の少なくとも一部と上記第2の配線の少なくとも一部は互いに接触していることを特徴とする半導体装置。

30

【請求項15】

請求項14に記載の半導体装置において、

上記第1の配線は互いに分離された複数箇所に設けられており、

上記第1の配線のうち少なくとも2つの配線は、上記第2の配線を介して電気的に接続されていることを特徴とする半導体装置。

【請求項16】

請求項12～15のうちいずれか1つに記載の半導体装置において、

上記第2の配線は、上記第2絶縁膜から上記第1絶縁膜に亘って設けられていることを特徴とする半導体装置。

【請求項17】

請求項13に記載の半導体装置において、

上記第2絶縁膜の上には第3絶縁膜がさらに設けられており、

上記第1埋め込み配線のうち、ボンディングパッドとなる部分の上には、上記第3絶縁膜を貫通して設けられた導電体からなる接続部材がさらに設けられていることを特徴とする半導体装置。

【請求項18】

請求項12または13に記載の半導体装置において、

上記半導体基板は下層配線をさらに有しており、

上記第1絶縁膜を貫通して設けられ、上記第1の配線と上記下層配線とを電気的に接続する第1プラグと、

40

50

上記第1絶縁膜を貫通して設けられ、上記第2の配線と上記下層配線とを電気的に接続する第2プラグと

をさらに備えていることを特徴とする半導体装置。

【請求項19】

請求項12または13に記載の半導体装置において、

上記半導体基板は不純物拡散層をさらに有しており、

上記第1絶縁膜を貫通して設けられ、上記第1の配線と上記不純物拡散層とを電気的に接続する第1プラグと、

上記第1絶縁膜を貫通して設けられ、上記第2の配線と上記不純物拡散層とを電気的に接続する第2プラグと

をさらに備えていることを特徴とする半導体装置。

【請求項20】

請求項12または13に記載の半導体装置において、

上記半導体素子はゲート電極を有しており、

上記第1絶縁膜を貫通して設けられ、上記第1の配線と上記ゲート電極とを電気的に接続する第1プラグと、

上記第1絶縁膜を貫通して設けられ、上記第2の配線と上記ゲート電極とを電気的に接続する第2プラグと

をさらに備えていることを特徴とする半導体装置。

【請求項21】

請求項12～20のうちいずれか1つに記載の半導体装置において、

上記第1の配線のうちボンディングパッド、電源ライン及び接地ラインのいずれかとして機能する部分の配線幅は20μm以上であることを特徴とする半導体装置。

【請求項22】

請求項1～21のうちいずれか1つに記載の半導体装置において、

上記第1の配線と上記第2の配線とは互いに異なる材料から構成されていることを特徴とする半導体装置。

【請求項23】

請求項1～22のうちいずれか1つに記載の半導体装置において、

上記第1の配線及び上記第2の配線は、タンタル、窒化タンタル、チタン、窒化チタン、タンゲステン、窒化タンゲステン、アルミニウム、銅、銀、金、白金のうち少なくとも1つを含む金属から構成されていることを特徴とする半導体装置。

【請求項24】

複数の配線層を有する半導体基板の上方に設けられた第1絶縁膜に第1トレンチを形成する工程(a)と、

上記第1トレンチを含む上記第1絶縁膜上に第1導電体を堆積する工程(b)と、

化学的機械的研磨により上記第1導電体を研磨し、少なくとも上記第1トレンチを埋める

第1の導電膜を形成する工程(c)と、

上記第1絶縁膜及び上記第1の導電膜の上に第2絶縁膜を形成する工程(d)と、

少なくとも上記第2絶縁膜に第2トレンチを形成する工程(e)と、

上記第2トレンチを含む上記第2絶縁膜上に第2導電体を堆積する工程(f)と、

上記第2導電体を加工することにより、少なくとも上記第2トレンチを埋め、且つ上記第1の導電膜と電気的に接続される第2の導電膜を、上記第1の導電膜と同じ配線層内に形成する工程(g)と

を含む半導体装置の製造方法であって、

上記第1の導電膜のうち少なくとも一部はボンディングパッド、電源ライン及び接地ラインのうちのいずれかとして機能することを特徴とする半導体装置の製造方法。

【請求項25】

請求項24に記載の半導体装置の製造方法において、

上記工程(g)では、化学的機械的研磨を用いて上記第2導電体を研磨し、上記第2の導

10

20

30

40

50

電膜を形成することを特徴とする半導体装置の製造方法。

【請求項 2 6】

請求項 2 4 に記載の半導体装置の製造方法において、

上記工程 ( g ) では、上記第 2 導電体をエッティングすることにより上記第 2 の導電膜を形成することを特徴とする半導体装置の製造方法。

【請求項 2 7】

請求項 2 4 ~ 2 6 のうちいずれか 1 つに記載の半導体装置の製造方法において、

上記第 1 の導電膜と上記第 2 の導電膜とは上記配線層のうち最上の配線層内に設けられ、上記第 1 の導電膜のうち少なくとも一部はボンディングパッドとして機能することを特徴とする半導体装置の製造方法。

10

【請求項 2 8】

請求項 2 4 ~ 2 7 のうちいずれか 1 つに記載の半導体装置の製造方法において、

上記第 2 絶縁膜及び上記第 2 の導電膜の上に第 3 絶縁膜を形成する工程 ( h ) と、

上記第 3 絶縁膜及び上記第 2 絶縁膜のうち上記第 1 の導電膜のうちボンディングパッドとして機能する部分の上方に位置する領域に第 3 トレンチを形成する工程 ( i ) と、

上記第 3 トレンチを埋め、上記ボンディングパッドとして機能する部分に接続される接続部材を形成する工程 ( j ) と

をさらに含むことを特徴とする半導体装置の製造方法。

【請求項 2 9】

請求項 2 4 ~ 2 8 のうちいずれか 1 つに記載の半導体装置の製造方法において、

20

上記工程 ( a ) は、上記第 1 トレンチから下方に延びる第 1 スルーホールを形成する工程をさらに含み、

上記工程 ( c ) は、上記第 1 導電体からなり、上記第 1 スルーホールを埋める第 1 プラグを形成する工程をさらに含み、

上記工程 ( e ) は、上記第 2 トレンチから下方に延びる第 2 スルーホールを形成する工程をさらに含み、

上記工程 ( g ) は、上記第 2 導電体からなり、上記第 2 スルーホールを埋める第 2 プラグを形成する工程をさらに含むことを特徴とする半導体装置の製造方法。

【請求項 3 0】

請求項 2 4 ~ 2 9 のうちいずれか 1 つに記載の半導体装置の製造方法において、

30

上記第 1 の導電膜と上記第 2 の導電膜の構成材料は互いに異なっていることを特徴とする半導体装置の製造方法。

【請求項 3 1】

請求項 2 4 ~ 3 0 のうちいずれか 1 つに記載の半導体装置の製造方法において、

上記第 1 の導電膜及び上記第 2 の導電膜は、タンタル、窒化タンタル、チタン、窒化チタン、タンゲステン、窒化タンゲステン、アルミニウム、銅、銀、金、白金のうち少なくとも 1 つを含む金属から構成されていることを特徴とする半導体装置の製造方法。

【請求項 3 2】

複数の配線層を有する半導体基板の上方に設けられた第 1 絶縁膜に第 1 トレンチを形成する工程 ( a ) と、

40

上記第 1 トレンチを含む上記第 1 絶縁膜上に第 1 導電体を堆積する工程 ( b ) と、

化学的機械的研磨により上記第 1 導電体を研磨し、少なくとも上記第 1 トレンチを埋める第 1 の導電膜を形成する工程 ( c ) と、

上記第 1 絶縁膜及び上記第 1 の導電膜の上に第 2 絶縁膜を形成する工程 ( d ) と、

少なくとも上記第 2 絶縁膜に第 2 トレンチを形成する工程 ( e ) と、

上記第 2 トレンチを含む上記第 2 絶縁膜上に第 2 導電体を堆積する工程 ( f ) と、

上記第 2 導電体を加工することにより、少なくとも上記第 2 トレンチを埋め、且つ上記第 1 の導電膜と電気的に接続された第 2 の導電膜を、上記第 1 の導電膜と同じ配線層内に形成する工程 ( g ) と

を含む半導体装置の製造方法であって、

50

上記第2の導電膜のうち少なくとも一部はボンディングパッド、電源ライン及び接地ラインのうちのいずれかとして機能することを特徴とする半導体装置の製造方法。

【請求項33】

請求項32に記載の半導体装置の製造方法において、

上記第1の導電膜と上記第2の導電膜とは上記配線層のうち最上の配線層内に設けられ、上記第1の導電膜のうち少なくとも一部はボンディングパッドとして機能することを特徴とする半導体装置の製造方法。

【請求項34】

請求項33に記載の半導体装置の製造方法において、

上記第2絶縁膜及び上記第2の導電膜の上に第3絶縁膜を形成する工程(h)と、10

上記第3絶縁膜及び上記第2絶縁膜のうち上記第2の導電膜のうちボンディングパッドとして機能する部分の上方に位置する領域に第3トレンチを形成する工程(i)と、

上記第3トレンチを埋め、上記ボンディングパッドとして機能する部分に接続される接続部材を形成する工程(j)と

をさらに含むことを特徴とする半導体装置の製造方法。

【請求項35】

請求項32～34のうちいずれか1つに記載の半導体装置の製造方法において、

上記工程(a)は、上記第1トレンチから下方に延びる第1スルーホールを形成する工程をさらに含み、

上記工程(c)は、上記第1導電体からなり、上記第1スルーホールを埋める第1プラグを形成する工程をさらに含み、20

上記工程(e)は、上記第2トレンチから下方に延びる第2スルーホールを形成する工程をさらに含み、

上記工程(g)は、上記第2導電体からなり、上記第2スルーホールを埋める第2プラグを形成する工程をさらに含むことを特徴とする半導体装置の製造方法。

【請求項36】

請求項32～35のうちいずれか1つに記載の半導体装置の製造方法において、

上記工程(g)では、上記第2導電体をCMPにより研磨することで上記第2の導電膜を形成することを特徴とする半導体装置の製造方法。

【請求項37】

請求項32～36のうちいずれか1つに記載の半導体装置の製造方法において、

上記第1の導電膜と上記第2の導電膜の構成材料は互いに異なっていることを特徴とする半導体装置の製造方法。

【請求項38】

請求項32～37のうちいずれか1つに記載の半導体装置の製造方法において、

上記第1の導電膜及び上記第2の導電膜は、タンタル、窒化タンタル、チタン、窒化チタン、タンゲステン、窒化タンゲステン、アルミニウム、銅、銀、金、白金のうち少なくとも1つを含む金属から構成されていることを特徴とする半導体装置の製造方法。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は、半導体装置及びその製造方法に関し、特に、埋め込み配線及びボンディングパッド構造に関する。

【0002】

【従来の技術】

半導体装置の微細化が進むにつれ、配線の抵抗や、エレクトロマイグレーションなどの問題が表面化してきている。エレクトロマイグレーションとは、配線材料の金属原子が電子との衝突により振動し、断線などを起こす現象であり、配線抵抗と同様に、配線の断面積が小さくなるほど顕著になる。

【0003】

10

20

30

40

50

このため、微細化した半導体装置では、従来のアルミニウム（A1）に代えてより低抵抗で、マイグレーション耐性のある銅（Cu）が、配線材料として用いられるようになっている。

【0004】

CuはA1に比べてエッチングが難しい材料であるので、Cuを配線材料とする場合、あらかじめ形成したトレンチを埋めることによって配線を形成する。

【0005】

このような埋め込み配線技術は、半導体装置を外部端子等に接続するためのボンディングパッドにも用いられる。

【0006】

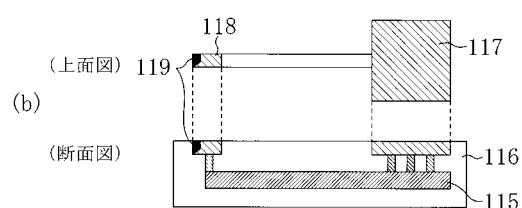

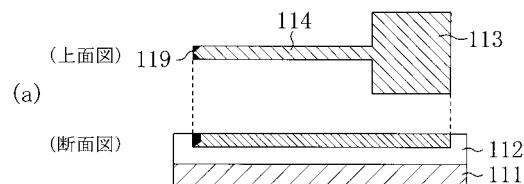

図9(a), (b)は、従来の埋め込み配線技術を用いた半導体装置を示す図である。

【0007】

図9(a)に示す例では、まず半導体素子を有する半導体基板111上に例えば酸化膜を堆積することにより、絶縁膜112を形成する。

【0008】

次に、絶縁膜112にリソグラフィ処理及びドライエッチングを施し、一方の幅が狭く、他方の幅が大きいトレンチを形成する。

【0009】

次いで、図示しないタンタルまたは窒化タンタルを堆積後シード銅を堆積する。その後、電解めっき法により銅（Cu）を堆積する。

【0010】

次に、化学的機械的研磨（CMP）にてタンタルまたは窒化タンタルとCuを、絶縁膜112が露出するまで研磨し、トレンチを埋める埋め込み配線114及びボンディングパッド113を一体として形成する。タンタルまたは窒化タンタルは、Cuが半導体基板中に拡散するのを防ぐためのバリアメタルとして働く。

【0011】

この手法で形成された配線は、一般にシングルダマシン配線と呼ばれ、タングステンなどからなるプラグを介して下層配線や半導体基板に接続するように設けられる。

【0012】

次に、図9(b)に示す例では、まず半導体素子及び下層配線115を有する半導体基板111(図示省略)上に例えば酸化膜を堆積することにより、絶縁膜116を形成する。

【0013】

その後、絶縁膜116にリソグラフィー処理及びドライエッチングを施し、トレンチ及びスルーホールを形成する。続いて、タンタルまたは窒化タンタルを基板上に堆積後、電解めっき法によりCuを堆積する。

【0014】

次に、CMPによりタンタルまたは窒化タンタルとCuとを絶縁膜116が露出するまで研磨し、埋め込み配線118及びボンディングパッド117と、埋め込み配線118及びボンディングパッド117と下層配線115とをそれぞれ接続するプラグとを同時に形成する。

【0015】

この手法により形成された配線は、一般にデュアルダマシン配線と呼ばれる。

【0016】

シングルダマシン及びデュアルダマシンのいずれの場合でも、最上層配線に設けられたボンディングパッドを介して半導体チップの外部にあるプリント基板などとの電気的に接続する必要がある。

【0017】

【発明が解決しようとする課題】

上述のダマシン工程において、最上層に位置する配線層内では、ボンディングパッドと配線とが同時に形成される。その際に、ボンディングパッドと配線とが電気的に接続されて

10

20

30

40

50

いる場合、C M Pによる研磨工程もしくは研磨後の洗浄工程において、配線部に腐食部119(図9(a), (b)参照)が生じるという不具合があった。このような腐食はC M Pで用いる研磨液や洗浄工程で用いる洗浄液によって配線を構成するCuが侵されることにより生じる。すなわち、腐食とは、配線などの構成材料が薬品によって変質あるいは溶出した状態を指す。

【0018】

また、配線の腐食は図9(a)に示すように、配線とボンディングパッドとが直接接している場合だけでなく、図9(b)に示すような、配線とボンディングパッドとが間接的に接続されている場合にも生じる。

【0019】

配線に腐食を生じると、接続不良の他、設計から期待されるよりも配線抵抗が増大する等の不具合が生じ、特に微細化した半導体装置では致命的な故障の原因ともなる。

【0020】

本発明の目的は、埋め込み配線における腐食の発生を防止し、信頼性の高い半導体装置及びその製造方法を提供することにある。

【0021】

【課題を解決するための手段】

本発明の半導体装置は、半導体基板と、上記半導体基板上に設けられた複数の半導体素子と、上記半導体基板及び上記半導体素子の上方に設けられた第1絶縁膜と、上記第1絶縁膜の上に設けられた第2の絶縁膜と、複数の配線層とを備える半導体装置であって、上記配線層は、上記第1絶縁膜に設けられた第1トレンチを埋める導電体からなる第1の配線と、上記第1の配線の一部と異なる配線幅を有し、少なくとも上記第2絶縁膜に設けられた第2トレンチを埋めて、上記第2の配線と電気的に接続される導電体からなる第2の配線とを有している。

【0022】

この構造により、製造工程中に第1の配線または第2の配線に生じる腐食を防ぐことができる。そのため、本発明の半導体装置の信頼性は、従来の半導体装置よりも向上している。また、配線において、腐食による抵抗の増大やマイグレーション耐性の低下を防ぐことができる。

【0023】

上記第2の配線のうち少なくとも一部はボンディングパッド、電源ライン及び接地ラインのうちのいずれかであることにより、配線の腐食を防止する効果が顕著に現れる。

【0024】

特に、上記第1の配線と上記第2の配線は共に上記配線層のうち最上の配線層内に設けられており、上記第2の配線のうち少なくとも一部はボンディングパッドであってもよい。

【0025】

上記第1の配線の少なくとも一部と上記第2の配線の少なくとも一部は互いに接触してもよい。この場合にも、第1の配線を形成するためのC M P工程において、幅の異なる配線が同時に研磨液に触れることがないので、腐食の発生は防止されている。

【0026】

上記第1の配線は互いに分離された複数箇所に設けられており、上記第1の配線のうち少なくとも2つの配線は、上記第2の配線を介して電気的に接続されていることにより、例えば上記第1の配線が配線幅が異なる複数の配線を含んでいる場合にも、C M P工程において、幅の異なる配線が同時に研磨液に触れることがないので、腐食の発生が防止されている。

【0027】

上記第2の配線は、上記第2絶縁膜から上記第1絶縁膜に亘って設けられていることにより、第2の配線の断面積が大きくなるので、電気抵抗を低減することができる。そのため、第2の配線が電源ラインなどの大電流が流れる配線であるときに、特に有効である。

【0028】

10

20

30

40

50

上記第2絶縁膜の上には第3絶縁膜がさらに設けられており、上記第2埋め込み配線の上には、上記第3絶縁膜を貫通して設けられた導電体からなる接続部材がさらに設けられていることにより、第2の配線がボンディングパッドであり、ワイヤやバンプなどとの密着性が悪い場合でも、外部端子に良好に接続することができる。

## 【0029】

上記半導体基板は下層配線をさらに有しており、上記第1絶縁膜を貫通して設けられ、上記第1の配線と上記下層配線とを電気的に接続する第1プラグと、上記第1絶縁膜を貫通して設けられ、上記第2の配線と上記下層配線とを電気的に接続する第2プラグとをさらに備えていてもよい。

## 【0030】

また、上記半導体基板は不純物拡散層をさらに有しており、上記第1絶縁膜を貫通して設けられ、上記第1の配線と上記不純物拡散層とを電気的に接続する第1プラグと、上記第1絶縁膜を貫通して設けられ、上記第2の配線と上記不純物拡散層とを電気的に接続する第2プラグとをさらに備えていてもよい。

## 【0031】

あるいは、上記半導体素子はゲート電極を有しており、上記第1絶縁膜を貫通して設けられ、上記第1の配線と上記ゲート電極とを電気的に接続する第1プラグと、上記第1絶縁膜を貫通して設けられ、上記第2の配線と上記ゲート電極とを電気的に接続する第2プラグとをさらに備えていてもよい。

## 【0032】

上記第2の配線のうちボンディングパッド、電源ライン及び接地ラインのいずれかとして機能する部分の配線幅は $20\text{ }\mu\text{m}$ 以上である場合には、従来の半導体装置に比べて配線の腐食防止効果が特に顕著に見られる。

## 【0033】

上記第1の配線のうち少なくとも一部はボンディングパッド、電源ライン及び接地ラインのうちのいずれかであってもよい。

## 【0034】

上記第1の配線と上記第2の配線は共に上記配線層のうち最上の配線層内に設けられており、上記第1の配線のうち少なくとも一部はボンディングパッドであってもよい。

## 【0035】

上記第1の配線の少なくとも一部と上記第2の配線の少なくとも一部は互いに接触してもよい。この場合にも、C M P工程において配線幅が異なる配線が同時に露出しないので、配線の腐食が効果的に防止される。

## 【0036】

上記第1の配線は互いに分離された複数箇所に設けられており、上記第1の配線のうち少なくとも2つの配線は、上記第2の配線を介して電気的に接続されていることにより、第1の配線を形成するためのC M Pを行なう際に、配線幅の異なる配線同士が接続されていないので、第1の配線における腐食の発生が防止されている。

## 【0037】

上記第2の配線は、上記第2絶縁膜から上記第1絶縁膜に亘って設けられていることによって、第2の配線における電気抵抗を低減することができる。

## 【0038】

上記第2絶縁膜の上には第3絶縁膜がさらに設けられており、上記第1埋め込み配線のうち、ボンディングパッドとなる部分の上には、上記第3絶縁膜を貫通して設けられた導電体からなる接続部材がさらに設けられていることにより、第1の配線がボンディングパッドであり、ワイヤやバンプなどとの密着性が悪い場合でも、外部端子に良好に接続することができる。

## 【0039】

上記半導体基板は下層配線をさらに有しており、上記第1絶縁膜を貫通して設けられ、上記第1の配線と上記下層配線とを電気的に接続する第1プラグと、上記第1絶縁膜を貫通

10

20

30

40

50

して設けられ、上記第2の配線と上記下層配線とを電気的に接続する第2プラグとをさらに備えていてもよい。

【0040】

上記半導体基板は不純物拡散層をさらに有しており、上記第1絶縁膜を貫通して設けられ、上記第1の配線と上記不純物拡散層とを電気的に接続する第1プラグと、上記第1絶縁膜を貫通して設けられ、上記第2の配線と上記不純物拡散層とを電気的に接続する第2プラグとをさらに備えていてもよい。

【0041】

上記半導体素子はゲート電極を有しており、上記第1絶縁膜を貫通して設けられ、上記第1の配線と上記ゲート電極とを電気的に接続する第1プラグと、上記第1絶縁膜を貫通して設けられ、上記第2の配線と上記ゲート電極とを電気的に接続する第2プラグとをさらに備えていてもよい。

10

【0042】

上記第1の配線のうちボンディングパッド、電源ライン及び接地ラインのいずれかとして機能する部分の配線幅は $20\text{ }\mu\text{m}$ 以上である場合には、従来の半導体装置に比べて配線の腐食防止効果が特に顕著に見られる。

【0043】

上記第1の配線と上記第2の配線とは互いに異なる材料から構成されていることにより、例えば配線部分はCuで、パッド部分はAlなど、必要に応じた材料で構成することができ、より性能のよい半導体装置を提供することができる。

20

【0044】

上記第1の配線及び上記第2の配線は、タンタル、窒化タンタル、チタン、窒化チタン、タングステン、窒化タングステン、アルミニウム、銅、銀、金、白金のうち少なくとも1つを含む金属から構成されていることが好ましい。

30

【0045】

本発明の第1の半導体装置の製造方法は、複数の配線層を有する半導体基板の上方に設けられた第1絶縁膜に第1トレンチを形成する工程(a)と、上記第1トレンチを含む上記第1絶縁膜上に第1導電体を堆積する工程(b)と、化学的機械的研磨により上記第1導電体を研磨し、少なくとも上記第1トレンチを埋める第1の導電膜を形成する工程(c)と、上記第1絶縁膜及び上記第1の導電膜の上に第2絶縁膜を形成する工程(d)と、少なくとも上記第2絶縁膜に第2トレンチを形成する工程(e)と、上記第2トレンチを含む上記第2絶縁膜上に第2導電体を堆積する工程(f)と、上記第2導電体を加工することにより、少なくとも上記第2トレンチを埋め、且つ上記第1の導電膜と電気的に接続される第2の導電膜を、上記第1の導電膜と同じ配線層内に形成する工程(g)とを含む半導体装置の製造方法であって、上記第1の導電膜のうち少なくとも一部はボンディングパッド、電源ライン及び接地ラインのうちのいずれかとして機能する。

30

【0046】

この方法により、工程(c)の化学的機械的研磨(CMP)時に第1の導電膜のうち、幅の異なる部分が互いに接続されていないので、第1の導電膜における腐食の発生を防止することができる。特に、第1の導電膜の一部が配線幅の広いボンディングパッドや電源ライン、接地ラインなどである場合には有効である。従って、本発明の方法によれば、信頼性の高い半導体装置を高い歩留まりで製造することが可能になる。

40

【0047】

上記工程(g)では、化学的機械的研磨を用いて上記第2導電体を研磨し、上記第2の導電膜を形成することにより、特にCuなど、エッティングが困難な材料を用いても第2の導電膜を形成することができる。このとき、第1の導電膜の上には第2絶縁膜が形成されているので、CMP時に第1の導電膜と第2の導電膜のうち幅が異なる部分が同時に研磨液に触れることがない。このため、第1の導電膜または第2の導電膜の腐食が抑えられている。

【0048】

50

上記工程 ( g ) では、上記第 2 導電体をエッティングすることにより上記第 2 の導電膜を形成してもよい。

【 0 0 4 9 】

上記第 1 の導電膜と上記第 2 の導電膜とは上記配線層のうち最上の配線層内に設けられ、上記第 1 の導電膜のうち少なくとも一部はボンディングパッドとして機能する場合にも第 1 の導電膜や第 2 の導電膜に腐食を生じることがない。

【 0 0 5 0 】

上記第 2 絶縁膜及び上記第 2 の導電膜の上に第 3 絶縁膜を形成する工程 ( h ) と、上記第 3 絶縁膜及び上記第 2 絶縁膜のうち上記第 1 の導電膜のうちボンディングパッドとして機能する部分の上方に位置する領域に第 3 トレンチを形成する工程 ( i ) と、上記第 3 トレンチを埋め、上記ボンディングパッドとして機能する部分に接続される接続部材を形成する工程 ( j ) とをさらに含むことにより、ボンディングパッドである第 1 の導電膜がワイヤやバンプなどとの密着性が悪い場合にも、外部端子などと良好に接続することができる。すなわち、この方法によれば、信頼性の高い半導体装置を製造することができる。

【 0 0 5 1 】

上記工程 ( a ) は、上記第 1 トレンチから下方に延びる第 1 スルーホールを形成する工程をさらに含み、上記工程 ( c ) は、上記第 1 導電体からなり、上記第 1 スルーホールを埋める第 1 プラグを形成する工程をさらに含み、上記工程 ( e ) は、上記第 2 トレンチから下方に延びる第 2 スルーホールを形成する工程をさらに含み、上記工程 ( g ) は、上記第 2 導電体からなり、上記第 2 スルーホールを埋める第 2 プラグを形成する工程をさらに含むことにより、第 1 導電体と第 1 プラグ及び第 2 導電体と第 2 プラグをそれぞれ同時に形成することができるので、工程数を少なくすることができます。

【 0 0 5 2 】

上記第 1 の導電膜と上記第 2 の導電膜の構成材料は互いに異なっていることにより、必要に応じて最適な材料を用いることで、より性能の良い半導体装置を製造することができる。

【 0 0 5 3 】

上記第 1 の導電膜及び上記第 2 の導電膜は、タンタル、窒化タンタル、チタン、窒化チタン、タンゲステン、窒化タンゲステン、アルミニウム、銅、銀、金、白金のうち少なくとも 1 つを含む金属から構成されていることが好ましい。

【 0 0 5 4 】

本発明の半導体装置の第 2 の製造方法は、複数の配線層を有する半導体基板の上方に設けられた第 1 絶縁膜に第 1 トレンチを形成する工程 ( a ) と、上記第 1 トレンチを含む上記第 1 絶縁膜上に第 1 導電体を堆積する工程 ( b ) と、化学的機械的研磨により上記第 1 導電体を研磨し、少なくとも上記第 1 トレンチを埋める第 1 の導電膜を形成する工程 ( c ) と、上記第 1 絶縁膜及び上記第 1 の導電膜の上に第 2 絶縁膜を形成する工程 ( d ) と、少なくとも上記第 2 絶縁膜に第 2 トレンチを形成する工程 ( e ) と、上記第 2 トレンチを含む上記第 2 絶縁膜上に第 2 導電体を堆積する工程 ( f ) と、上記第 2 導電体を加工することにより、少なくとも上記第 2 トレンチを埋め、且つ上記第 1 の導電膜と電気的に接続された第 2 の導電膜を、上記第 1 の導電膜と同じ配線層内に形成する工程 ( g ) とを含む半導体装置の製造方法であって、上記第 2 の導電膜のうち少なくとも一部はボンディングパッド、電源ライン及び接地ラインのうちのいずれかとして機能する。

【 0 0 5 5 】

この方法により、工程 ( c ) 及び工程 ( g ) の CMP 時に第 1 の導電膜と第 2 の導電膜とが同時に研磨液に触れないで、いずれの導電膜においても腐食の発生を防止することができる。また、第 2 の導電膜の一部が広い配線幅を有し、ボンディングパッドや電源ライン、接地ラインなどとして機能する場合であっても、第 2 の導電膜の各部が互いに分離しているので、第 2 の導電膜に腐食が生じることがない。

【 0 0 5 6 】

上記第 1 の導電膜と上記第 2 の導電膜とは上記配線層のうち最上の配線層内に設けられ、

10

20

30

40

50

上記第1の導電膜のうち少なくとも一部はボンディングパッドとして機能する場合にも、第1の導電膜及び第2の導電膜に生じる腐食を防止することができる。

#### 【0057】

上記第2絶縁膜及び上記第2の導電膜の上に第3絶縁膜を形成する工程(h)と、上記第3絶縁膜及び上記第2絶縁膜のうち上記第2の導電膜のうちボンディングパッドとして機能する部分の上方に位置する領域に第3トレンチを形成する工程(i)と、上記第3トレンチを埋め、上記ボンディングパッドとして機能する部分に接続される接続部材を形成する工程(j)とをさらに含むことにより、第2の導電膜がワイヤやバンプなどの密着性が悪い材料で構成されている場合であっても、外部端子などと良好に接続することができる。

10

#### 【0058】

上記工程(a)は、上記第1トレンチから下方に延びる第1スルーホールを形成する工程をさらに含み、上記工程(c)は、上記第1導電体からなり、上記第1スルーホールを埋める第1プラグを形成する工程をさらに含み、上記工程(e)は、上記第2トレンチから下方に延びる第2スルーホールを形成する工程をさらに含み、上記工程(g)は、上記第2導電体からなり、上記第2スルーホールを埋める第2プラグを形成する工程をさらに含むことにより、第2の導電膜の一部がボンディングパッド、電源ライン、接地ラインなどとして機能する場合にも、少ない工程で本発明の半導体装置を製造することが可能になる。

20

#### 【0059】

上記工程(g)では、上記第2導電体をCMPにより研磨することで上記第2の導電膜を形成してもよい。この際に、第1の導電膜は研磨液に触れることがないので、第1の導電膜が腐食されることはない。

#### 【0060】

上記第1の導電膜と上記第2の導電膜の構成材料は互いに異なっていることにより、より性能の良い半導体装置を製造することができる。

#### 【0061】

上記第1の導電膜及び上記第2の導電膜は、タンタル、窒化タンタル、チタン、窒化チタン、タンゲステン、窒化タンゲステン、アルミニウム、銅、銀、金、白金のうち少なくとも1つを含む金属から構成されていることが好ましい。

30

#### 【0062】

##### 【発明の実施の形態】

埋め込み配線における腐食を防止するため、本願発明者らは、配線が腐食する原因を調べることから始めた。腐食はCMP時の研磨液または洗浄液にCuが溶け出すことにより生じることが分かっていたので、どのような条件下で腐食が起こるのかを調べた。

#### 【0063】

種々の形状の最上層配線について調べた結果、面積の広い部分と狭い部分が接続された状況で、面積の狭い配線に腐食が生じることが分かった。例えば、長さ80μmで幅0.22μmの配線に一辺が50μmのパッドが接続された条件では、配線側に腐食が生じた。

40

#### 【0064】

さらに、配線幅を一定にし、パッド面積を大きくした場合、腐食部分はさらに大きくなることが確認された。逆に、パッド面積を小さくした場合、一辺が20μm以上になると腐食が顕著になることが分かった。

#### 【0065】

これに対し、配線とパッドとが接続されない場合には、腐食が生じなかった。また、幅が均一な配線を形成しても、腐食は生じなかった。

#### 【0066】

これらの結果から、本願発明者らは、腐食の生じる機構について以下のよう推論を立てた。

#### 【0067】

50

まず、配線を構成する Cu が研磨液に触れると、配線全体で  $Cu - Cu^{2+} + 2e^-$  のように Cu がイオン化する。この CMP の際に、配線を構成する Cu が、周囲のバリア膜を除去されるなどで電気的にフロー・ティングな状態になった場合には、配線とパッドで面積の大きさが違うために電位差が生じ、その結果、細い部分でイオン化が進み、腐食が生じる。配線とパッドとの電位差は、両部分が間接的に接続される場合でも生じるので、この時にも腐食が生じると考えられる。

#### 【0068】

この仮説から、配線の腐食を防ぐためには、CMP 時及び洗浄時において、配線とパッドとを同時に露出させないこと、または、配線とパッドとが電気的に接続されない状態にすることの 2 つが有効であると考えられた。以下に説明する本発明は、この考えに基づいてなされたものである。10

#### 【0069】

##### (第 1 の実施形態)

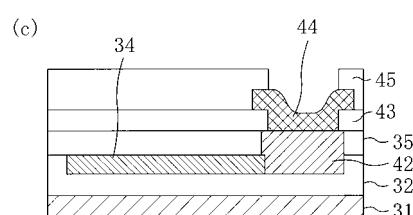

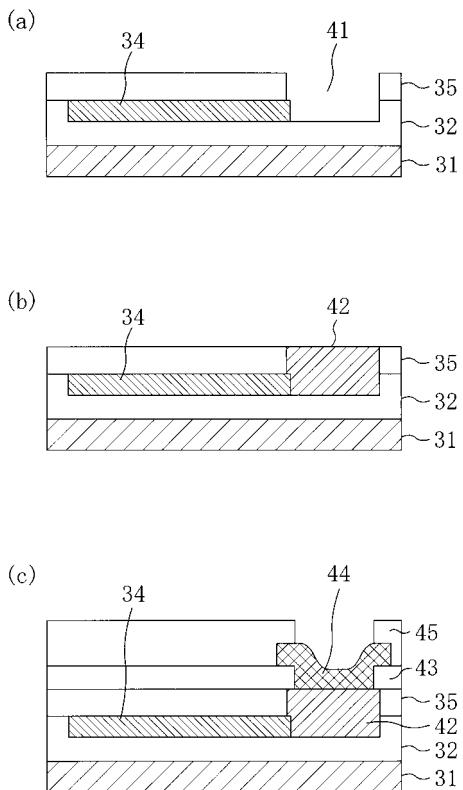

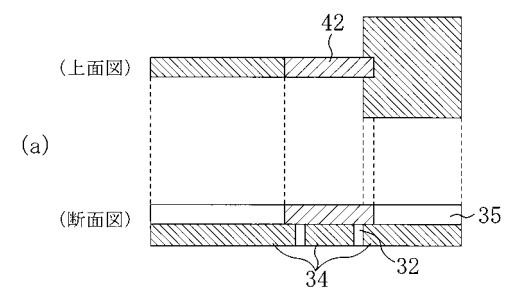

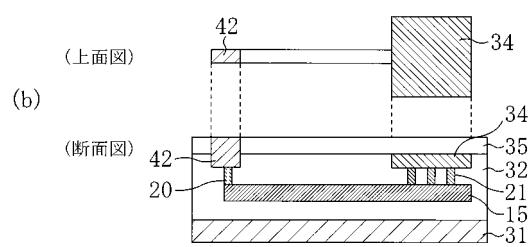

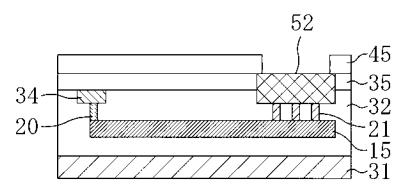

図 1 (a) ~ (c), 図 2 (a) ~ (c) は、本発明の第 1 の実施形態に係る半導体装置の製造方法を示す断面図である。

#### 【0070】

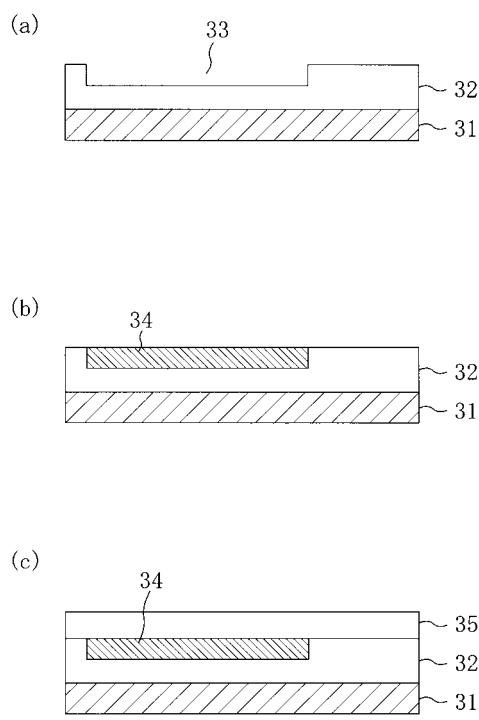

まず、図 1 (a) に示す工程で、半導体素子と、複数の配線層と、Cu 配線との接続を目的とするプラグとが設けられた基板 31 を準備する。基板 31 は半導体基板でもよいし、SOI (Silicon on Insulator) 基板でもよい。なお、図 1 では、最上の配線層のみを示しており、他の配線層や半導体素子は省略している。20

#### 【0071】

次に、基板 31 上に例えばシリコン酸化膜を堆積して第 1 絶縁膜 32 を形成する。その後、第 1 のマスクを用いて第 1 絶縁膜 32 をリソグラフィー処理及びドライエッチングすることにより、配線用の第 1 トレンチ 33 を形成する。例えば、図示している第 1 トレンチ 33 の深さは約 400 nm で、幅は 0.22 μm、長さは 80 μm とする。

#### 【0072】

次に、図 1 (b) に示す工程で、第 1 トレンチ 33 を含む第 1 絶縁膜 32 上にタンタルまたは窒化タンタルを堆積後、シード銅を堆積する。次いで、電解めっき法により基板上に Cu を堆積して、厚さ 600 nm の Cu 膜を形成する。このときのめっき条件は、幅の狭いトレンチを埋めるため、埋め込み性の良好な条件を選択する。30

#### 【0073】

その後、CMP により第 1 絶縁膜 32 が露出するまでタンタルまたは窒化タンタルと、Cu 膜とを研磨し、第 1 トレンチ 33 を覆うバリアメタル（図示せず）と第 1 トレンチ 33 を埋める Cu からなる第 1 埋め込み配線 34 とを形成する。

#### 【0074】

次に、図 1 (c) に示す工程で、例えばシリコン酸化膜を基板上に堆積し、厚さ 400 nm の第 2 絶縁膜 35 を形成する。

#### 【0075】

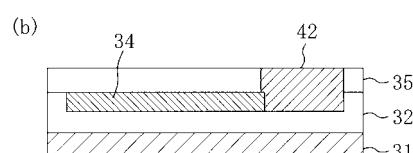

続いて、図 2 (a) に示す工程で、第 2 のマスクを用いて第 1 絶縁膜 32 及び第 2 絶縁膜 35 にリソグラフィー処理及びドライエッチングを施すことにより、深さ 800 nm で幅と長さが共に 50 μm の第 2 トレンチ 41 を形成する。なお、ドライエッチングの際にはシリコン酸化膜を選択的にエッチングするため、第 2 トレンチ 41 内では第 1 埋め込み配線 34 の一部が露出する。40

#### 【0076】

次に、図 2 (b) に示す工程で、タンタルまたは窒化タンタルと、シード銅を順次堆積する。次いで、電解めっき法により、基板上に Cu を堆積し、厚さ 1000 μm の Cu 膜を形成する。ここで、電解めっき法の条件は、埋め込み性よりも表面段差を小さくすることを優先する条件で行なう。

#### 【0077】

その後、CMP により第 2 絶縁膜 35 が露出するまでタンタルまたは窒化タンタルと、C50

u 膜とを研磨することにより、第2トレンチ41を覆うバリアメタル（図示せず）と第2トレンチ41を埋めるCuからなる第2埋め込み配線42を形成する。この第2埋め込み配線42は、ボンディングパッドとなっている。なお、加工圧力、研磨パッドとウエハとの相対速度、パッド硬度などのCMPの条件は、最も大きいボンディングパッドでのディッシングが小さくなるような条件とする。ここで、ディッシングとは、埋め込み配線の中央部がCMP工程によってへこむことで生じる表面段差のことである。

#### 【0078】

次に、図2(c)に示す工程で、第2絶縁膜35及び第2埋め込み配線42の上にシリコン酸化膜を堆積して第3絶縁膜43を形成する。

#### 【0079】

次いで、第3絶縁膜43のうち第2埋め込み配線42（ボンディングパッド）の上に位置する部分を開口し、スパッタ法によりアルミ合金を堆積する。その後、アルミ合金をリソグラフィー処理及びエッチングすることによりアルミ合金からなる接続部材44を形成する。次に、例えばシリコン酸化膜を基板上に堆積してから接続部材44が露出するようにシリコン酸化膜を開口することで、保護膜45を形成する。

#### 【0080】

以上の工程により、本発明の半導体装置が作製される。

#### 【0081】

本実施形態の半導体装置の製造方法によれば、図1(b)、図2(b)に示すいずれのCMP工程においても幅の狭い配線と幅の広いパッド部分が同時に研磨液に接触することができないので、第1埋め込み配線34の終端部で腐食が発生することはない。また、研磨後の洗浄工程についても同様である。そのため、本実施形態の方法によれば、所定の配線面積を確保することができるので、配線抵抗の増大とマイグレーションによる断線とを効果的に防ぐことができる。このため、本実施形態の方法によれば、信頼度が高い半導体装置を従来よりも高い歩留まりで製造することができる。

#### 【0082】

また、ボンディングパッドの厚みを配線の深さによらず任意に設定することができるので、CMP工程で多少のディッシングが生じても、必要な断面積を確保することができるので、抵抗の増大を防ぎ、マイグレーション耐性を向上させることができる。

#### 【0083】

以上のように製造される本実施形態の半導体装置は、図2(c)に示すように、半導体素子及び複数の配線層を有する基板31と、基板31上に設けられた第1絶縁膜32と、第1絶縁膜32上に設けられた第2絶縁膜35と、第1絶縁膜32に設けられ、Cuからなる第1埋め込み配線34と、第1絶縁膜32及び第2絶縁膜35に設けられ、Cuからなるボンディングパッドとして機能する第2埋め込み配線42と、第2絶縁膜35上に設けられ、第2埋め込み配線42の上に位置する領域が開口した第3絶縁膜43と、第2埋め込み配線42の上に設けられアルミ合金からなる接続部材44と、第3絶縁膜43上に設けられ、接続部材44の上方が開口した保護膜45とを備えている。また、第1埋め込み配線34と第2埋め込み配線42とは共に最上の配線層内に設けられている。

#### 【0084】

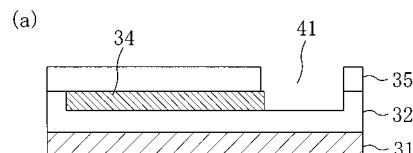

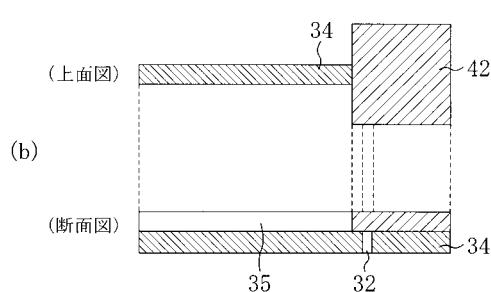

なお、図3(a)、(b)は、本実施形態の半導体装置の変形例を示す図である。

#### 【0085】

図3(a)に示すように、接続部材44を設けずに、ボンディングパッドである第2埋め込み配線42が直接ワイヤまたはBGA(Ball Grid Array)のバンプなど、外部の接続部材と接続していてよい。ただし、Cuは酸化しやすく、酸化銅は接続部材との密着性が悪いため、第2埋め込み配線42の上面に生じる酸化銅は、あらかじめ除去しておかなければならない。この例においても、本実施形態の半導体装置と同様、ボンディングパッドの膜厚を厚くすることができるので、CMP工程で多少のディッシングが生じても、所定の断面積を確保することができる。このため、従来の半導体装置に比べ抵抗を低減し、マイグレーション耐性を向上させることができる。

## 【0086】

また、図3(b)に示すように、第1埋め込み配線34が2つに分断されて設けられ、分断された第1埋め込み配線34がその上に設けられた第2埋め込み配線42を介して接続される構造であってもよい。この変形例でも、第1埋め込み配線34と第2埋め込み配線42とは同一の最上配線層内に設けられる。

## 【0087】

なお、第1埋め込み配線34のうち、第2埋め込み配線42の直下のものは、配線幅を任意に設定できる。例えば、配線幅を第2埋め込み配線42と同じとしてもよいし、も一方の第1埋め込み配線34の幅と同じとしてもよい。

## 【0088】

この変形例の場合、図3(a)に示す例に比べて第1埋め込み配線34が第2トレンチ41の形成時に受けるエッチングダメージを低減することができる。これは、第2トレンチ41が浅い場合には、エッチング量が少なくなるためである。

## 【0089】

また、第2埋め込み配線42の直下に位置する第1埋め込み配線34の幅が広い場合、ボンディングパッド部が積層構造となり、第2トレンチ41上にCuを堆積する際の堆積膜厚を薄くすることができる。これにより、Cuを堆積した時の表面段差を小さくすることができるので、CMP時にオーバー研磨をする必要がなくなり、研磨時間の短縮を図ることができる。結果として、ボンディングパッドに生じるディッシングを低減することができる。

10

20

30

40

## 【0090】

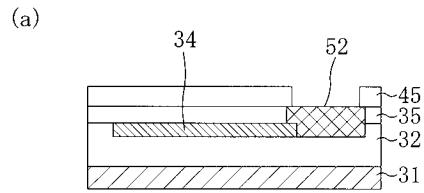

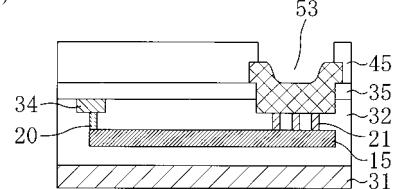

また、図7(a), (b)は、本発明の半導体装置において、第1埋め込み配線と第2埋め込み配線の構成材料が互いに異なっている例を示す断面図である。

## 【0091】

同図(a)に示す例では、第1埋め込み配線34がCuからなり、第2埋め込み配線はAlまたはAl合金からなっている。

## 【0092】

埋め込み配線がCuから構成される場合、第3絶縁膜43を開口して第2埋め込み配線42(図2参照)を露出させる際に露出部に酸化銅が生じてしまう。本変形例では、第2埋め込み配線52をAlまたはAl合金で形成しているので、Alの接続部材を用いなくても直接ワイヤやバンプと接続させることができる。なお、この場合の第2埋め込み配線52は、スパッタ法により基板上にAlを堆積し、それをCMPで研磨することにより形成する。この場合、バリアメタルは不要である。

## 【0093】

また、図8(a), (b)は、ボンディングパッドの形成後にCMPを行わない場合の本発明の半導体装置を示す断面図である。

## 【0094】

同図(a)に示す半導体装置では、図2(b)に示す工程において、第2トレンチ41上にAl合金をスパッタ法により堆積した後、Al合金にリソグラフィー処理とエッチングを施してCMPを用いずに第2埋め込み配線53を形成する。この第2埋め込み配線53はボンディングパッドとしてワイヤやバンプなどと直接接続される。このような方法でも、埋め込み配線での腐食を防ぐことができる。

## 【0095】

なお、第2埋め込み配線52の材料はAlやAl合金に限らず、銀、金、白金などの酸化しにくい材料、あるいはワイヤ等との密着性のよい材料であってもよい。また、第1埋め込み配線34の材料もCuに限らず銀、金、白金、Al、タンゲステンやこれらのうちいずれかを含む合金であってもよい。

## 【0096】

また、本実施形態の半導体装置において、このバリアメタルの材料としては、タンタル、窒化タンタルの他に、チタン、窒化チタン、タンゲステン、窒化タンゲステンなどが挙げ

50

られる。また、配線材料がCu以外の場合は、バリアメタルは必ずしも必要ではない。

【0097】

なお、本実施形態の半導体装置において、1つのボンディングパッドを例にとって説明したが、実際の第2埋め込み配線は、同時に形成される複数のボンディングパッドとなっている。ただし、腐食を防ぐため、各ボンディングパッドのサイズが異なる場合には、CMP時に、ボンディングパッド同士が接続されないようにする。

【0098】

以上の説明では、第2埋め込み配線がボンディングパッドとして機能する例を示したが、配線幅が20μmを越えるものとして、ボンディングパッドの他に電源ラインや接地ラインが考えられる。従来では電源ラインや接地ラインが通常の配線と同時に形成されていたために、配線側に腐食が起こっていたが、本実施形態の方法によれば、電源ラインまたは接地ラインを埋め込み配線と別工程で形成するので、腐食の発生を抑えることができる。この場合には、電源ラインまたは接地ラインは最上の配線層以外の配線層内にも設けられる。

【0099】

また、本実施形態の方法は、幅が広い方の配線幅が20μm以上の場合に特に有効であるが、それ以下でもある程度の腐食抑制効果は期待できる。

【0100】

(第2の実施形態)

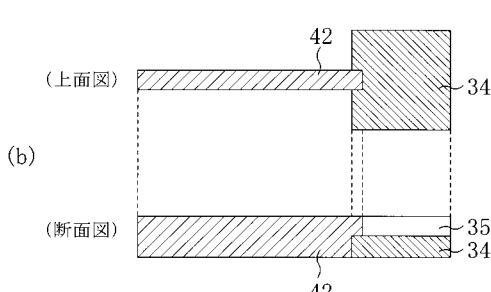

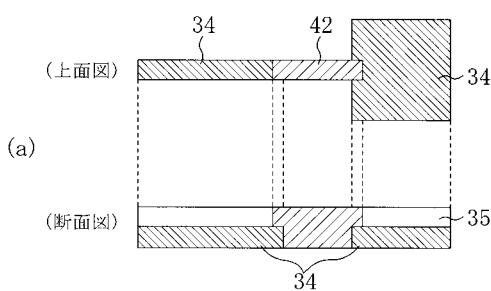

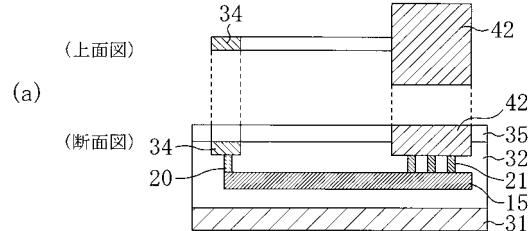

本発明の第2の実施形態として、第1埋め込み配線がボンディングパッドとなる半導体装置を説明する。

【0101】

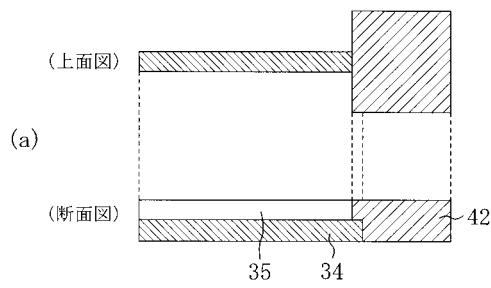

図4(a), (b)は、本発明の第2の実施形態に係る半導体装置の例を示す断面図である。

【0102】

同図(a)に示すように、本実施形態の半導体装置は、半導体素子と複数の配線層が設けられた基板(図示せず)と、基板上に設けられた第1絶縁膜32と、第1絶縁膜32に設けられ、Cuから構成される複数の第1埋め込み配線34と、第1埋め込み配線34上に設けられた第2絶縁膜35と、第2絶縁膜35に設けられたCuからなる第2埋め込み配線42とを備えている。

【0103】

第1埋め込み配線34は、3つに分割されて形成され、それぞれの第1埋め込み配線34は、第2埋め込み配線42を介して互いに接続されている。また、第1埋め込み配線34の厚みは400nmで、第1埋め込み配線34のうち図4(a)の中央部と左側に位置する部分は配線として機能し、その幅は、例えば0.22μmである。第1埋め込み配線34のうち、右側に位置する部分は、ボンディングパッドとして機能し、その幅は50μmとなっている。

【0104】

また、図示しないが、実際にはボンディングパッドの上にAl合金からなる接続部材が設けられ、これがワイヤやバンプなどと接続するようになっている。これは、図5及び図6についても同様である。

【0105】

通常の半導体装置において、特にボンディングパッドが電源入力パッドである場合、該ボンディングパッドから伸びる配線で電流密度が非常に大きくなる。図4(a)に示す半導体装置によれば、第2埋め込み配線42の下に第1埋め込み配線34の一部が設けられているので、電流が集中する部分の配線の断面積を大きくすることができる。そのため、配線における電流密度の勾配を緩やかにすることができる、マイグレーション耐性を向上させることができる。

【0106】

また、第2埋め込み配線42の下に第1埋め込み配線34の一部が設けられていること

10

20

30

40

50

、第2トレンチを形成するためのエッティングの際に、第1埋め込み配線34が受ける損傷を低減することができる。

【0107】

加えて、この半導体装置において、埋め込み配線のバリアメタル材料及びCuを堆積する際のプロセスウインドウを広げることができる。

【0108】

なお、本実施形態の半導体装置は、第1の実施形態と同様の工程により製造される。ただ形成する第1埋め込み配線34及び第2埋め込み配線42の形状が異なるだけである。

【0109】

次に、図4(b)には、本実施形態の半導体装置のもう1つの例が示している。この半導体装置と図4(a)に示す例とは、第1埋め込み配線34及び第2埋め込み配線42の形状が異なっている。この例では、第1埋め込み配線34が2つに分割されて形成され、各第1埋め込み配線34は第2埋め込み配線42を介して接続されている。この例に係る半導体装置でも、第1埋め込み配線34のうち、ボンディングパッドになる部分と配線になる部分とが分割されて形成されるので、配線端部における腐食が防がれている。

【0110】

この半導体装置によっても、第2埋め込み配線42の下に第1埋め込み配線34の一部が設けられているので、配線の断面積を大きくすることができます。そのため、配線における電流密度を低減することができ、マイグレーション耐性を向上させることができます。

【0111】

また、第2埋め込み配線42の下に第1埋め込み配線34の一部が設けられていることで、第2トレンチを形成するためのエッティングの際に、第1埋め込み配線34が受ける損傷を低減することができる。

【0112】

加えて、この半導体装置においても、埋め込み配線のバリアメタル材料及びCuを堆積する際のプロセスウインドウを広げることができます。

【0113】

また、図5(a), (b)は、本実施形態の半導体装置の変形例を示す図である。

【0114】

同図(a)に示す半導体装置では、本実施形態の半導体装置と同様に、第1埋め込み配線34の配線部とボンディングパッド部とが分離して設けられている。そして、第1埋め込み配線34の両部分は第2埋め込み配線42を介して電気的に接続されている。

【0115】

本変形例が図4(a), (b)に示す半導体装置と異なる点は、第1埋め込み配線34と第2埋め込み配線42の底面が同じ高さにあることである。このような構造でも、配線の端部に腐食を生じることがない。また、電流が集中する部分の配線の断面積を大きくすることができます。そのため、配線における電流密度の勾配を緩やかにすることができます、マイグレーション耐性を向上させることができます。

【0116】

次に、図5(b)に示す半導体装置では、第1埋め込み配線34はボンディングパッドとなっており、第2埋め込み配線42はボンディングパッドに直接接触した配線となっている。そして、第1埋め込み配線34と第2埋め込み配線42の底面は同じ高さ位置にあり、第2埋め込み配線42の深さは第1埋め込み配線34の深さよりも深くなっている。

【0117】

この半導体装置によれば、配線となる第2埋め込み配線42の断面積が図2(c)に示す本実施形態の半導体装置に比べて大きくなっているので、配線抵抗を低減することができます。なお、第2埋め込み配線42の底面位置は第1埋め込み配線34の底面位置よりも高くしてもよい。

【0118】

なお、本実施形態の半導体装置では、第1埋め込み配線34をボンディングパッドとする

10

20

30

40

50

例を説明したが、第1埋め込み配線34を電源ラインや接地ラインに用いることもできる。

### 【0119】

また、図4(a), (b)及び図5(a), (b)に示す半導体装置において、第2埋め込み配線42をめっき及びCMPにより形成する例を示したが、第2埋め込み配線42の材料がCu以外であるときは、該第2埋め込み配線42を、スパッタとそれに続くドライエッティングによって形成してもよい。

### 【0120】

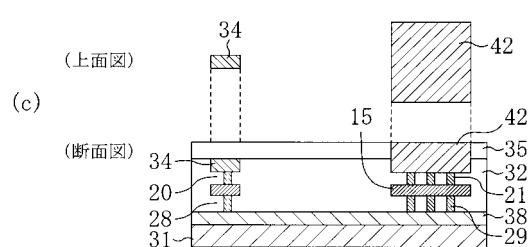

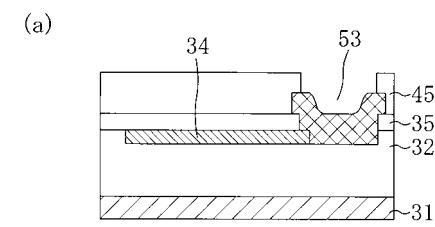

#### (第3の実施形態)

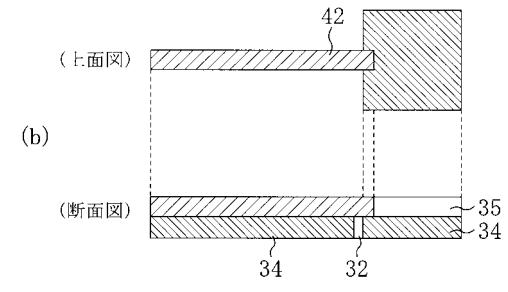

本発明の第3の実施形態に係る半導体装置として、プラグと配線とを同時に形成する例を 10 説明する。

### 【0121】

図6(a)は、本実施形態の半導体装置を示す図であり、図6(b)は、本実施形態の半導体装置の第1の変形例を示す図であり、図6(c)は、本実施形態の半導体装置の第2の変形例を示す図である。

### 【0122】

図6(a)に示すように、本実施形態の半導体装置は、半導体素子及び複数の配線層を有する基板31と、基板31上に設けられた第1絶縁膜32と、第1絶縁膜32内に設けられた下層配線15と、第1絶縁膜32に設けられた第1埋め込み配線34と、第1絶縁膜32及び第1埋め込み配線34の上に設けられた第2絶縁膜35と、第1絶縁膜32から第2絶縁膜35にかけて設けられた第2埋め込み配線42と、第1埋め込み配線34-下層配線15間を接続する第1プラグ20と、第2埋め込み配線42-下層配線15間を接続する第2プラグ21とを備えている。また、第1埋め込み配線34と第2埋め込み配線42は共に最上の配線層内に設けられ、第2埋め込み配線42はボンディングパッドとなっている。

### 【0123】

各配線の幅は、第1埋め込み配線34が0.22μmで、第2埋め込み配線42が50μmである。また、第1埋め込み配線34の深さは400nmで、第2埋め込み配線42の深さは800nmである。

### 【0124】

また、第1埋め込み配線34、第2埋め込み配線42、第1プラグ20及び第2プラグ21はCuで構成されており、図示されないバリアメタルで囲まれている。

### 【0125】

次に、本実施形態の半導体装置の製造方法を簡単に説明する。

### 【0126】

まず、半導体素子と複数の配線層と下層配線15とが設けられた基板31を準備する。

### 【0127】

次に、基板31上に例えばシリコン酸化膜を堆積して第1絶縁膜32を形成する。その後、第1のマスクを用いて第1絶縁膜32をリソグラフィー処理及びドライエッティングすることにより、配線用の第1トレンチと、第1トレンチから下層配線15に至る第1スルーホールとを形成する。

### 【0128】

次に、第1トレンチと第1スルーホールを含む基板上にタンタルまたは窒化タンタルとシード銅を堆積した後、電解めっき法によりCuを堆積する。

### 【0129】

次いで、CMPを行って第1スルーホールを埋める第1プラグ20と第1トレンチを埋める第1埋め込み配線34とを同時に形成する。

### 【0130】

次に、基板上に第2絶縁膜35を形成した後、第1絶縁膜32及び第2絶縁膜35にリソグラフィ処理とエッティングを施して第2トレンチと第2スルーホールを形成する。

10

20

30

40

50

## 【0131】

その後、タンタルまたは窒化タンタルと、Cuとを順次堆積した後、CMPを行なうことにより、第2スルーホールを埋める第2プラグ21と第2トレーナーを埋める第2埋め込み配線42とを同時に形成する。

## 【0132】

以上のように、本実施形態の半導体装置は製造される。この工程は、いわゆるデュアルダマシン工程である。

## 【0133】

本実施形態の方法によれば、第1の実施形態の方法に比べてプラグと配線とを同時に形成できるので、製造工程を少なくすることができる。

10

## 【0134】

また、幅の広い配線と幅の狭い配線とが別工程により形成されているので、第2埋め込み配線42を形成する際のCMP時に第1埋め込み配線34が研磨液に触れることがない。そのため、本実施形態の半導体装置の製造方法によれば、第1埋め込み配線34に腐食を生じることがない。

## 【0135】

このように、本実施形態の方法によれば、配線とボンディングパッドとが間接的に接続されている場合にも、配線の腐食を防ぐことができる。

## 【0136】

なお、図6(b)に示す例のように、第1埋め込み配線34がボンディングパッドとなり、第2埋め込み配線42が配線となる構成をとることもできる。この変形例では、第1埋め込み配線34の幅が50μm、第2埋め込み配線42の幅が0.22μmとなっている。

20

## 【0137】

また、図6(c)に示す変形例のように、第1埋め込み配線34と第2埋め込み配線42とが基板上に設けられた不純物拡散層38を介して電気的に接続されてもよい。この際には、下層配線15や下層の第3プラグ28及び第4プラグ29などを介して第1埋め込み配線34及び第2埋め込み配線42が不純物拡散層38に電気的に接続されてもよい。また、第1プラグ20と第2プラグ21とが複数の配線層をまたいで不純物拡散層38に直接接続されてもよい。このような場合でも、第1埋め込み配線34の腐食は防がれている。

30

## 【0138】

なお、第1埋め込み配線34と第2埋め込み配線42とが半導体素子のゲート電極を介して接続されているような構成であってもよい。このような場合でも、第2埋め込み配線42に代えて第1埋め込み配線34をボンディングパッドとして設けることができる。

## 【0139】

また、図7(b)に示す半導体装置の変形例のように、デュアルダマシン工程によっても第1埋め込み配線34と第2埋め込み配線52とを互いに異なる材料で構成することができる。例えば、本変形例において、第1埋め込み配線34及び第1プラグ20はCuからなり、第2埋め込み配線52及び第2プラグ21は例えればAl合金からなっている。

40

## 【0140】

このように、ボンディングパッドとなる第2埋め込み配線52をAl合金で構成することにより、パッドの表面酸化によってワイヤやバンプとの接続が不良となることがなくなるので、製品の信頼性を高め、且つ歩留まりを上げることができる。

## 【0141】

なお、本変形例においても、第1埋め込み配線34及び第2埋め込み配線52の材料としてCuの他、銀、金、白金、Al、タンゲステンであってもよい。

## 【0142】

また、図8(b)に示す本実施形態の半導体装置の変形例のように、デュアルダマシン工程を用いる場合でも、CMPを用いずに第2埋め込み配線53を形成することができる。

50

**【 0 1 4 3 】**

具体的には、図 6 ( a ) に示す半導体装置と同様の方法で第 1 埋め込み配線 3 4 及び第 1 プラグ 2 0 の形成後、第 2 絶縁膜 3 5 を堆積する。次に、第 1 絶縁膜 3 2 及び第 2 絶縁膜 3 5 にリソグラフィー処理とエッティングを施して第 2 トレンチと第 2 スルーホールを形成する。

**【 0 1 4 4 】**

次に、スパッタ法により Al 合金を基板上に堆積後、リソグラフィ処理及びエッティングにより第 2 埋め込み配線 5 3 を形成する。次いで、基板上に保護膜 4 5 を形成してから保護膜 4 5 の一部を開口して第 2 埋め込み配線 5 3 を露出させる。

**【 0 1 4 5 】**

このような方法であっても、埋め込み配線の腐食を防止することができる。また、 Al などの接続部材を設けなくとも、直接ワイヤなどに接続することが可能になる。

**【 0 1 4 6 】****【発明の効果】**

本発明の半導体装置の製造方法によれば、ボンディングパッドや電源ライン、接地ラインなどとして機能する幅の広い配線と通常の埋め込み配線とを形成するための CMP 工程において、通常の配線と幅の広い配線とを分離して形成することにより、通常の配線の端部に腐食が生じるのを防ぐことができる。そのため、本発明の半導体装置は、埋め込み配線が腐食されないので、配線抵抗が設計通りとなっており、動作の信頼性が向上している。

**【図面の簡単な説明】**

【図 1】( a ) ~ ( c ) は、本発明の第 1 の実施形態に係る半導体装置の製造方法のうち、第 2 絶縁膜の形成工程までを示す断面図である。

【図 2】( a ) ~ ( c ) は、第 1 の実施形態に係る半導体装置の製造方法のうち、保護膜を形成する工程までを示す断面図である。

【図 3】( a ), ( b ) は、第 1 の実施形態に係る半導体装置の変形例を示す図である。

【図 4】( a ), ( b ) は、本発明の第 2 の実施形態に係る半導体装置の例を示す断面図である。

【図 5】( a ), ( b ) は、第 2 の実施形態に係る半導体装置の変形例を示す図である。

【図 6】( a ) は、本発明の第 3 の実施形態に係る半導体装置を示す図であり、図 6 ( b ) は、該半導体装置の第 1 の変形例を示す図であり、図 6 ( c ) は、該半導体装置の第 2 の変形例を示す図である

【図 7】( a ), ( b ) は、本発明の半導体装置において、第 1 埋め込み配線と第 2 埋め込み配線の構成材料が互いに異なっている例を示す断面図である。

【図 8】( a ), ( b ) は、ボンディングパッドの形成後に CMP を行わない場合の本発明の半導体装置を示す断面図である。

【図 9】( a ), ( b ) は、従来の埋め込み配線技術を用いた半導体装置を示す図である。

**【符号の説明】**

|     |            |

|-----|------------|

| 1 5 | 下層配線       |

| 2 0 | 第 1 プラグ    |

| 2 1 | 第 2 プラグ    |

| 2 8 | 第 3 プラグ    |

| 2 9 | 第 4 プラグ    |

| 3 1 | 基板         |

| 3 2 | 第 1 絶縁膜    |

| 3 3 | 第 1 トレンチ   |

| 3 4 | 第 1 埋め込み配線 |

| 3 5 | 第 2 絶縁膜    |

| 3 8 | 不純物拡散層     |

| 4 1 | 第 2 トレンチ   |

10

20

30

40

50

- 4 2 第 2 埋め込み配線

4 3 第 3 絶縁膜

4 4 接続部材

4 5 保護膜

【図 1】

【図 2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

(b)

(b)

【図9】

---

フロントページの続き

(74)代理人 100115510

弁理士 手島 勝

(74)代理人 100115691

弁理士 藤田 篤史

(72)発明者 松本 宗之

大阪府門真市大字門真 1006番地 松下電器産業株式会社内

F ターム(参考) 5F033 HH07 HH08 HH09 HH11 HH13 HH14 HH18 HH19 HH21 HH32

HH33 HH34 JJ01 JJ09 JJ11 JJ21 JJ32 KK11 KK21 KK32

MM01 MM02 MM12 MM13 MM17 NN06 NN07 PP15 PP27 QQ08

QQ09 QQ11 QQ37 QQ48 VV04 VV05 VV07 WW01 XX01 XX05

XX18

5F044 EE08 EE14 EE21