(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-201502

(P2007-201502A)

(43) 公開日 平成19年8月9日(2007.8.9)

|                         |              |             |

|-------------------------|--------------|-------------|

| (51) Int.C1.            | F 1          | テーマコード (参考) |

| HO 1 L 21/02 (2006.01)  | HO 1 L 27/12 | B 5 F 1 1 O |

| HO 1 L 27/12 (2006.01)  | HO 1 L 29/78 | 6 2 6 C     |

| HO 1 L 29/786 (2006.01) |              |             |

審査請求 有 請求項の数 6 O L (全 18 頁)

|            |                              |            |                                                                                                                                                                                                                                                                                            |

|------------|------------------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (21) 出願番号  | 特願2007-111191 (P2007-111191) | (71) 出願人   | 000153878                                                                                                                                                                                                                                                                                  |

| (22) 出願日   | 平成19年4月20日 (2007.4.20)       |            | 株式会社半導体エネルギー研究所                                                                                                                                                                                                                                                                            |

| (62) 分割の表示 | 特願平9-337670の分割               |            | 神奈川県厚木市長谷398番地                                                                                                                                                                                                                                                                             |

| 原出願日       | 平成9年11月22日 (1997.11.22)      | (72) 発明者   | 山崎 舜平                                                                                                                                                                                                                                                                                      |

|            |                              |            | 神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内                                                                                                                                                                                                                                                        |

|            |                              | F ターム (参考) | 5F110 AA30 BB01 BB04 CC02 DD02<br>DD07 DD08 DD13 DD14 DD15<br>DD18 DD24 EE03 EE06 EE09<br>EE31 FF02 FF03 FF04 FF23<br>FF24 FF32 GG02 GG12 GG25<br>GG32 GG51 GG52 HJ01 HJ06<br>HJ12 HJ13 HJ23 HL03 HL04<br>HL12 HM15 NN03 NN04 NN22<br>NN23 NN24 NN27 NN34 NN35<br>NN46 NN72 NN73 QQ04 QQ17 |

(54) 【発明の名称】半導体装置およびその作製方法

## (57) 【要約】

【課題】高性能な電気光学装置や半導体回路、さらにはそれらを搭載した電子機器を低価格で提供する。

【解決手段】スマートカット法を利用して得られる単結晶シリコン薄膜を、高耐熱性ガラスである結晶化ガラス上に形成する。その際、成分物質による汚染を防ぐために結晶化ガラス全面を絶縁性シリコン膜で保護する。こうすることで高性能な半導体装置を低価格で提供することが可能となる。

【選択図】図 1

## 【特許請求の範囲】

## 【請求項 1】

歪点が 750 以上であるガラス基板と、

前記ガラス基板の少なくとも表面及び裏面に対して形成された絶縁性シリコン膜と、

前記絶縁性シリコン膜上に形成された単結晶シリコン薄膜をチャネル形成領域とする TFT と、

を構成に含むことを特徴とする半導体装置。

## 【請求項 2】

歪点が 750 以上であるガラス基板と、

前記ガラス基板の外周囲を覆って形成された絶縁性シリコン膜と、

前記絶縁性シリコン膜上に形成された単結晶シリコン薄膜をチャネル形成領域とする TFT と、

を構成に含むことを特徴とする半導体装置。

## 【請求項 3】

請求項 1 または請求項 2 において、前記ガラス基板は結晶化ガラスであることを特徴とする半導体装置。

## 【請求項 4】

歪点が 750 以上であるガラス基板の全面に対して非晶質半導体薄膜を形成する工程と、

第 1 の加熱処理により前記非晶質半導体薄膜を酸化し、完全に熱酸化膜に変成させる工程と、

スマートカット法により前記ガラス基板の主表面側に単結晶シリコン薄膜を形成する工程と、

を含むことを特徴とする半導体装置の作製方法。

## 【請求項 5】

歪点が 750 以上であるガラス基板の全面に対して減圧熱 CVD 法により絶縁性シリコン膜を形成する工程と、

スマートカット法により前記ガラス基板の主表面側に単結晶シリコン薄膜を形成する工程と、

を含むことを特徴とする半導体装置の作製方法。

## 【請求項 6】

請求項 4 または請求項 5 において、前記ガラス基板とは結晶化ガラスであることを特徴とする半導体装置の作製方法。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本明細書で開示する発明は、絶縁表面を有する基板上に形成された単結晶半導体薄膜を利用した半導体装置に関する。特に、基板として安価で耐熱性の高い結晶化ガラス（セラミックスガラスとも呼ばれる）を用いる。

## 【0002】

なお、本明細書中では薄膜トランジスタ（以下、TFT）、半導体回路、電気光学装置および電子機器を全て「半導体装置」に範疇に含めて扱う。即ち、半導体特性を利用して機能しうる装置全てを半導体装置と呼ぶ。

## 【0003】

従って、上記特許請求の範囲に記載された半導体装置は、TFT 等の単体素子だけでなく、それを集積化した半導体回路や電気光学装置およびそれらを部品として搭載した電子機器をも包含する。

## 【背景技術】

## 【0004】

近年、絶縁表面を有する基板上に形成された半導体薄膜（厚さ数十～数百 nm 程度）を用

10

20

30

40

50

いて薄膜トランジスタ（TFT）を構成する技術が注目されている。薄膜トランジスタは特に画像表示装置（例えば液晶表示装置：LCD）のスイッチング素子としての開発が急がれている。

【0005】

また、液晶表示装置においてはマトリクス状に配列された画素を個々に制御する画素マトリクス回路、画素マトリクス回路を制御するドライバー回路、さらに外部からのデータ信号を処理するロジック回路（演算回路、メモリ回路、クロックジェネレータなど）等を同一基板上に作り込む試みがなされている。

【0006】

その様なモノリシック型LCDを実現するために、さらに動作速度の速いTFT回路が必要とされ、そのために極めてキャリア移動度の高い半導体層が必要となってきた。 10

【0007】

その様な流れの中で、SOI技術が注目されている。特に、単結晶シリコン薄膜を合成石英などの基板上に形成する技術としてスマートカット法と呼ばれる技術が注目されている。

【0008】

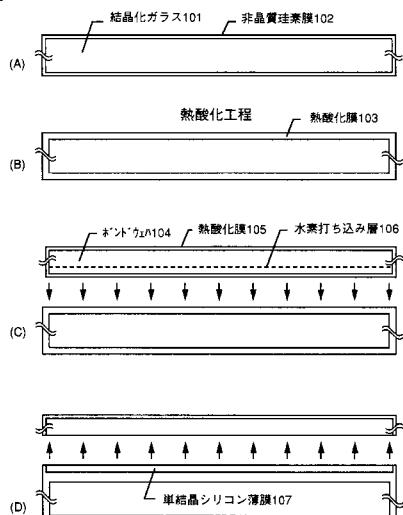

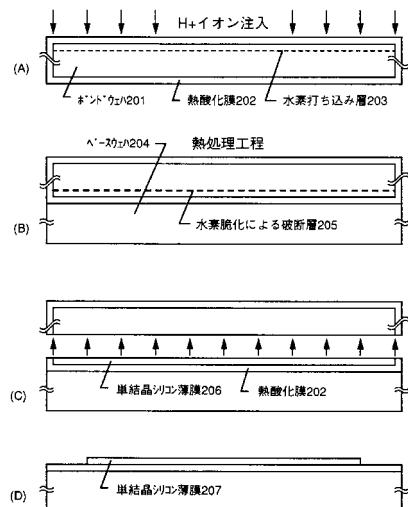

スマートカット法（1996年、フランスのSOITEC社が発表）とは貼り合わせSOI技術の一つであり、水素脆化を積極的に利用するものである。ここでスマートカット法の簡単な手順を図2に説明する。

【0009】

まず、ボンドウェハ201を熱酸化することで熱酸化膜202を形成し、その後、イオンインプランテーション法により水素イオン（H<sup>+</sup>）を添加する。水素イオンの添加工程によってボンドウェハ201内には、水素で終端された微小な空洞（micro cavity）203が形成される。本明細書では、この微小な空洞203を水素打ち込み層と呼ぶことにする。（図2（A）） 20

【0010】

次に、上記処理を終えたボンドウェハ201と、後に薄膜の支持基板となるベースウェハ204とを室温で貼り合わせ、500程度の加熱処理を施す。この加熱処理によって上述の水素打ち込み層では水素脆化が生じ、水素脆化による破断層205が形成される。（図2（B）） 30

【0011】

こうして水素脆化によ破断層205が形成されると単結晶シリコン薄膜206のみを残して容易にボンドウェハ201が剥がれる。（図2（C））

【0012】

従って、ベースウェハ204上には下地となる熱酸化膜202と単結晶シリコン薄膜206が形成される。なお、この時の単結晶シリコン薄膜206の膜厚は図2（A）における熱酸化膜202の膜厚と水素イオン注入の打ち込み深さによって決定される。

【0013】

こうして図2（C）の状態が得られたら、10nmオーダーの浅い研磨（タッチポリッシュ）を行い、さらに1000~1100程度の温度で2時間ぐらいの加熱処理を行って結合力の強い単結晶シリコン薄膜207を得る。（図2（D）） 40

【0014】

以上の様に、スマートカット法は非常に簡易な手段で単結晶シリコン薄膜を得られるという利点を有している。また、これまでの貼り合わせSOI基板ほど単結晶シリコン層の膜厚が研磨精度に影響されないので、非常に膜厚の均一性が高い。

【0015】

また、最近ではこのスマートカット法を利用して合成石英の上に単結晶シリコン薄膜を形成する試みもなされている。（阿部孝夫：第24回アモルファス物質の物性と応用セミナー・テキスト，p.25-32,1997）

【非特許文献1】第24回アモルファス物質の物性と応用セミナー・テキスト，p.25-32,1997 50

：阿部孝夫

【0016】

しかしながら、この報告によると合成石英とシリコンウェハ（ボンドウェハ）とを貼り合わせると熱膨張係数の差が大きいため300<sup>10</sup>程度の加熱で破壊が起こる。従って、同報告ではボンドウェハを200<sup>10</sup>前後で貼り合わせた後、50 $\mu$ mまで平面研磨（またはエッチング）して、その後で500<sup>10</sup>の加熱処理を施して貼り合わせを完了している。

【発明の開示】

【発明が解決しようとする課題】

【0017】

以上の様に、合成石英上にスマートカット法を利用して単結晶シリコン層を形成するには、熱膨張係数の差という問題があって貼り合わせ工程が煩雑になるという欠点がある。<sup>10</sup>

【0018】

また、単結晶シリコン層を利用してTFTを形成し、モノリシック型LCDを実現するという目的を考えると、高価な石英基板を用いることは全体のコストを増加させるため、好ましいものではない。

【0019】

本願発明は上記問題点を鑑みてなされたものであり、スマートカット法で得られる単結晶シリコン薄膜を用いた半導体装置を、安価な製造コストで実現するための技術を提供することを課題とする。

【課題を解決するための手段】

【0020】

本明細書で開示する発明の構成は、

歪点が750<sup>20</sup>以上であるガラス基板と、

前記ガラス基板の少なくとも表面及び裏面に対して形成された絶縁性シリコン膜と、

前記絶縁性シリコン膜上に形成された単結晶シリコン薄膜をチャネル形成領域とするTFTと、

を構成に含むことを特徴とする。

【0021】

また、他の発明の構成は、

歪点が750<sup>30</sup>以上であるガラス基板と、

前記ガラス基板の外周囲を覆って形成された絶縁性シリコン膜と、

前記絶縁性シリコン膜上に形成された単結晶シリコン薄膜をチャネル形成領域とするTFTと、

を構成に含むことを特徴とする。

【0022】

また、他の発明の構成は、

歪点が750<sup>40</sup>以上であるガラス基板の全面に対して非晶質半導体薄膜を形成する工程と、

第1の加熱処理により前記非晶質半導体薄膜を酸化し、完全に熱酸化膜に変成させる工程と、

スマートカット法により前記ガラス基板の主表面側に単結晶シリコン薄膜を形成する工程と、

を含むことを特徴とする。

【0023】

また、他の発明の構成は、

歪点が750<sup>50</sup>以上であるガラス基板の全面に対して減圧熱CVD法により絶縁性シリコン膜を形成する工程と、

スマートカット法により前記ガラス基板の主表面側に単結晶シリコン薄膜を形成する工程と、

を含むことを特徴とする。

## 【0024】

本願発明の重要な構成要件としては、

(1) 基板として 750 以上の温度に耐えうる耐熱性を有するガラス基板（歪点が 750 以上であるガラス基板）を用いる。

(2) 上記高耐熱性ガラス基板の外周面（少なくとも表面及び裏面、好ましくは全面）を絶縁性シリコン膜で保護する。

(3) 絶縁性シリコン膜で包まれた上記高耐熱性ガラス基板上に、スマートカット法を用いて単結晶シリコン薄膜を形成する。

という 3 点が挙げられる。

## 【0025】

スマートカット法により基板上に貼り合わされた単結晶シリコン薄膜は 800~1200（好ましくは 900~1100）の加熱処理を施すことで完全な結合力が得られる。そのため、ベース基板としては歪点が少なくとも 750 以上である基板を用いる必要がある。

## 【0026】

その様な基板としては石英基板がまず考えられるが、前述の様に石英基板は高価であるため全体的なコストを上げてしまう。また、石英の熱膨張係数は  $0.48 \times 10^{-6} \text{ }^{\circ}\text{C}^{-1}$  であり、シリコンの熱膨張係数（約  $4.15 \times 10^{-6} \text{ }^{\circ}\text{C}^{-1}$ ）の 1/10 程度と小さい。即ち、シリコンとの間に応力を発生しやすく、加熱処理の際にシリコンのピーリング（膜剥がれ）などを引き起こしやすい。

## 【0027】

そこで、本願発明では歪点が 750 以上（代表的には 800~1200、好ましくは 900~1100）である耐熱性の高い結晶化ガラスを基板として用いる。結晶化ガラスは石英よりも薄くできるため、LCD の製造コストを安く抑えられる。また、ガラス基板であるため大版化が可能であり、多面取りによるコストダウンも図れる。

## 【0028】

さらに、熱膨張係数は結晶化ガラスを構成する成分組成を適切なものとすることで容易に変えることができるため、単結晶シリコン薄膜の熱膨張係数に近いものを選択することができる。即ち、熱膨張係数の差を極めて小さくすることができるので従来の様な膜剥がれなどがなくなり、従来例で述べた様な煩雑な工程を行う必要がない。

## 【0029】

ただし、結晶化ガラスは様々な成分組成を持つため、半導体装置の製造過程における成分物質の流出が懸念される。そのため、結晶化ガラスを絶縁膜（単結晶シリコン薄膜との相性を考慮すると絶縁性シリコン膜が好ましい）で保護することが重要となる。そのためには、全プロセス過程において結晶化ガラスの少なくとも表面（素子が形成される側）及び裏面を絶縁膜で保護する必要がある。

## 【0030】

なお、結晶化ガラスの側面は全体から見ると非常に小さい面積であるので露出していてもさほど問題とはならない。しかし、表面、側面及び裏面を絶縁膜で完全に包み込んでしまい、成分物質の流出を完全に防ぐことが最も好ましいことは言うまでもない。

## 【0031】

ただし、絶縁膜を成膜する際の基板支持部（ツッシャーピン等）の部分には成膜されない部分ができる。しかしながら、全体の面積と比較すると非常に微小な領域なので問題とはならない。

## 【0032】

以上の点を考慮して、本願発明者らは絶縁性シリコン膜で外周面（好ましくは全面）を保護された高耐熱性ガラス基板上に、スマートカット法により形成された単結晶シリコン薄膜を設ける、という本願発明の構成に至ったのである。

## 【発明の効果】

## 【0033】

本願発明では安価で大版化の可能な結晶化ガラスを使用し、且つ、結晶化ガラスを安全

10

20

30

40

50

に（汚染の心配なく）活用するためにガラスの少なくとも表面及び裏面（好ましくは外周面）を絶縁性シリコン膜で保護するといった構成を採用している。

【0034】

そして、その上にスマートカット法を利用して形成した単結晶シリコン薄膜を用いて TFTを作製することでシステム・オン・パネルを実現し、高性能な電気光学装置や半導体回路、さらにはそれらを搭載した電子機器を低価格で提供することができる。

【発明を実施するための最良の形態】

【0035】

本願発明の実施形態について、以下に示す実施例でもって詳細な説明を行うこととする。

10

【実施例1】

【0036】

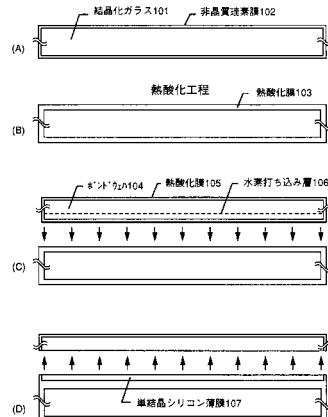

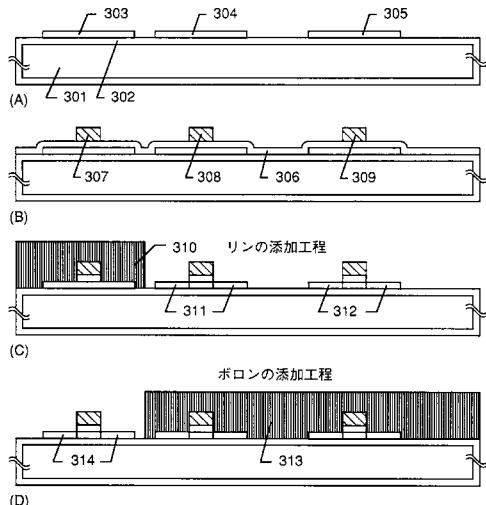

本実施例では、スマートカット法を利用して結晶化ガラス上に単結晶シリコン薄膜を形成する所までの工程について図1を用いて説明する。

【0037】

まず、基板として0.5~1.1mm厚（代表的には0.7mm厚）の結晶化ガラス基板101を用意する。結晶化ガラスはガラスセラミックスとも呼ばれ、ガラス生成の段階で微小な結晶を均一に成長させて得られたガラス基板と定義される。この様な結晶化ガラスは耐熱性が高く、熱膨張係数が小さいという特徴がある。

【0038】

本願発明で用いるガラス基板には750以上、好ましくは900~1100の歪点温度を有する高い耐熱性が要求される。現状ではその様な耐熱性を実現するガラス材料は結晶化ガラスしかないが、結晶化ガラスの定義に入らないガラス基板（例えば非晶質状態の高耐熱性ガラス基板等）であっても上記耐熱性を有する基板であれば本願発明に利用することができる。

20

【0039】

なお、結晶化ガラスに関する詳細は「ガラスハンドブック；作花済夫 他, pp.197~217, 朝倉書店, 1975」を参考にすると良い。

【0040】

結晶化ガラスの種類も様々であるが、基本的には石英(SiO<sub>2</sub>)、アルミナ(Al<sub>2</sub>O<sub>3</sub>)を中心としたアルミニノケイ酸塩ガラス、ホウケイ酸塩ガラス(B<sub>2</sub>O<sub>3</sub>が含まれる)などが実用的と言える。しかしながら、半導体装置用の基板として用いることを考慮すれば無アルカリガラスであることが望ましく、そういう意味で、MgO-Al<sub>2</sub>O<sub>3</sub>-SiO<sub>2</sub>系、PbO-ZnO-B<sub>2</sub>O<sub>3</sub>系、Al<sub>2</sub>O<sub>3</sub>-B<sub>2</sub>O<sub>3</sub>-SiO<sub>2</sub>系、ZnO-B<sub>2</sub>O<sub>3</sub>-SiO<sub>2</sub>系などが好ましい。

30

【0041】

MgO-Al<sub>2</sub>O<sub>3</sub>-SiO<sub>2</sub>系の高絶縁結晶化ガラスは、核形成剤として、TiO<sub>2</sub>、SnO<sub>2</sub>、ZrO<sub>2</sub>などを含み、コーデュライト(2MgO·2Al<sub>2</sub>O<sub>3</sub>·5SiO<sub>2</sub>)を主結晶相とする結晶化ガラスである。このタイプの結晶化ガラスは耐熱性が高く、電気絶縁性が高周波域でも優れている点に特徴がある。コーデュライト系結晶化ガラスの組成例及び熱膨張係数を表1に示す。

【0042】

40

【表1】

| ガラス組成 (wt%)      |                                |       |                  | 熱膨張係数<br>×10 <sup>-6</sup> (°C) <sup>-1</sup> |

|------------------|--------------------------------|-------|------------------|-----------------------------------------------|

| SiO <sub>2</sub> | Al <sub>2</sub> O <sub>3</sub> | MgO   | TiO <sub>2</sub> |                                               |

| 40~60            | 20~30                          | 13~14 | 9~13             | 1.5~6.5                                       |

【0043】

50

熱膨張係数は小さいほど熱によるシュリンケージ（熱による縮み）の影響が小さくなるため、微細パターン加工を行う半導体用基板としては好ましい。しかし、半導体薄膜の熱膨張係数との差が大きいと膜剥がれなどを起こしやすくなるため、なるべく半導体薄膜の熱膨張係数に近いものを用いることが望ましい。この様なことを考慮すると、 $\text{SiO}_2$ が45~57%、 $\text{Al}_2\text{O}_3$ が20~27%、 $\text{MgO}$ が11~18%、 $\text{TiO}_2$ が9~12%のコーデュライト系結晶化ガラスが好ましいと言える。

#### 【0044】

また、例えば透過型LCDを作製する場合には結晶化ガラスには透光性が要求される。その様な場合には無アルカリの透明結晶化ガラスを用いると良い。例えば、結晶相が充填石英固溶体で、熱膨張係数が $1.1 \sim 3.0 \times 10^{-6} \text{ }^{\circ}\text{C}^{-1}$ の結晶化ガラスとして、表2に示す様な結晶化ガラスがある。

#### 【0045】

#### 【表2】

| ガラス組成 (wt%)    |                         |              |              |                | 熱膨張係数<br>$\times 10^{-6} \text{ }^{\circ}\text{C}^{-1}$ |

|----------------|-------------------------|--------------|--------------|----------------|---------------------------------------------------------|

| $\text{SiO}_2$ | $\text{Al}_2\text{O}_3$ | $\text{MgO}$ | $\text{ZnO}$ | $\text{ZrO}_2$ |                                                         |

| 64~75          | 16~25                   | 3~10         | 0~7          | 3~10           | 1.1~3.0                                                 |

10

20

#### 【0046】

本願発明の構成要件の第1は、以上の様な結晶化ガラスを基板として用いることである。勿論、適切な工夫（本願発明の様に絶縁膜で完全に保護する等）を施せばアルカリ系結晶化ガラス（ $\text{Na}_2\text{O}$ - $\text{Al}_2\text{O}_3$ - $\text{SiO}_2$ 系、 $\text{Li}_2\text{O}$ - $\text{Al}_2\text{O}_3$ - $\text{SiO}_2$ 系等）を用いることもできる。また、熱膨張係数が非常に小さい（またはゼロに近い）結晶化ガラスでも、 $2.0 \sim 3.0 \times 10^{-6} \text{ }^{\circ}\text{C}^{-1}$ の熱膨張係数を有するガラスをコーティングして、半導体薄膜との熱膨張係数の差を緩和することも可能である。

#### 【0047】

以上の様な構成の結晶化ガラス101を用意したら、結晶化ガラス101に対して非晶質シリコン膜102を成膜する。成膜は減圧熱CVD法で行い、成膜ガスとしてはシラン（ $\text{SiH}_4$ ）又はジシラン（ $\text{Si}_2\text{H}_6$ ）を用いる。なお、膜厚は50~250 nm（代表的には100~150 nm）とすれば良い。（図1（A））

30

#### 【0048】

この様に減圧熱CVD法で成膜すると基板101を包み込む様にして表面、裏面及び側面に対して非晶質シリコン膜102を成膜することができる。なお、厳密には基板を保持するためのブッシャーピンが接する部分に非晶質シリコン膜102は成膜されない。しかし、全体の面積から見れば微々たるものである。

#### 【0049】

次に、加熱処理を行い、非晶質シリコン膜102を完全に熱酸化することで熱酸化膜103を形成する。この場合、非晶質シリコン膜102は完全に熱酸化して熱酸化膜103に変化するため、熱酸化膜103の膜厚は100~500 nm（代表的には200~300 nm）となる。

40

#### 【0050】

また、加熱処理の条件は公知のドライ $\text{O}_2$ 酸化、ウェット $\text{O}_2$ 酸化、スチーム酸化、パイロジェニック酸化、酸素分圧酸化、塩酸（HCl）酸化のいずれの手段によっても構わない。処理温度及び処理時間はプロセスを考慮した上で適切な条件を設定すれば良い。

#### 【0051】

なお、この加熱処理は結晶化ガラスの歪点以上、徐冷点以下の温度で行い、その温度で保持した後、徐冷するといった処理を行うことが好ましい。この様な処理を行うと熱酸化

50

膜の形成と同時にガラスのシュリンケージ対策を行うことができる。即ち、上述の処理によって予め基板を十分に縮ませておくことでその後の加熱処理による基板のシュリンケージ量を低減することができる。これに関連した技術は特開平8-250744号公報に記載されている。

【0052】

以上の様にして、熱酸化膜（酸化シリコン膜）103が形成されるが、前述の様に非晶質シリコン膜102は基板101を包み込む様にして形成されているので、熱酸化膜103も基板101を包み込む様にして形成される。即ち、結晶化ガラス基板101は完全に絶縁性シリコン膜で包まれるので、成分物質の流出を防止することが可能となる。

【0053】

なお、ここでは $\text{Si}_x\text{O}_y$ で表される酸化シリコン膜を絶縁性シリコン膜として用いているが、他にも $\text{Si}_x\text{Ny}$ で表される窒化シリコン膜や $\text{Si}_0\text{xNy}$ で表される酸化窒化シリコン膜などの絶縁性シリコン膜を用いることも可能である。

【0054】

こうして、本願発明の重要な構成のうちの二つ、結晶化ガラスを用いる点と結晶化ガラスを絶縁性シリコン膜で包み込む点とが達成される。

【0055】

次に、ボンドウェハ104を用意する。ボンドウェハ104はその表面が熱酸化膜105で覆われ、イオンインプランテーション法による水素イオン（ $\text{H}^+$ イオン）打ち込みによって水素打ち込み層106が形成されている。

【0056】

なお、熱酸化膜105の膜厚は200~700 nm（代表的には400~500 nm）とし、水素イオンのドーズ量は $5 \times 10^{15} \sim 1 \times 10^{17} \text{ ions/cm}^2$ （好ましくは $1 \times 10^{16} \sim 5 \times 10^{16} \text{ ions/cm}^2$ ）とする。これ以下のドーズ量では破断層の形成が困難になり、これ以上の濃度ではイオン注入と同時に破断してしまう恐れがある。

【0057】

そして、上述の結晶化ガラス101の主表面側（TFTを形成する側）に対してボンドウェハ104を室温で貼り合わせ、その後、400~600（典型的には500）の温度で加熱処理を施す。この時、結晶化ガラス101とボンドウェハ104の熱膨張係数に差があまりないので、熱応力によるピーリング（膜剥がれ）などの問題を防ぐことができる。

【0058】

こうして、加熱処理工程が終了したら、ボンドウェハ104を引き離し、結晶化ガラス101上にボンドウェハ104の一部であった熱酸化膜105と、単結晶シリコン薄膜107を残存させる。（図2（D））

【0059】

この熱酸化膜105は図2（B）の工程で形成された熱酸化膜103と一体化して下地膜として機能する。

【0060】

その後、10 nm前後のタッチポリッシュ工程を行い、900~1200（代表的には950~1050）の加熱処理を行って単結晶シリコン薄膜107の結合力を高める。こうして、熱酸化膜103で外周囲を完全に保護された結晶化ガラス101上に単結晶シリコン薄膜107を形成することができる。

【0061】

本実施例に従って作製された図1（D）に示す結晶化ガラス基板は、従来の様に石英基板を用いるよりも大幅に製造コストが安価である。また、基板外周囲を完全に酸化シリコン膜で保護しているため、後工程でガラス成分による汚染が発生することもない。

【実施例2】

【0062】

本実施例では、本願発明の構成を有する半導体装置の作製工程について図3を用いて説明する。具体的にはN TFT（Nチャネル型TFT）とP TFT（Pチャネル型TFT）

10

20

30

40

50

とを相補的に組み合わせたC M O S回路で構成される駆動回路及びロジック回路と、N T F Tで構成される画素マトリクス回路とを同一基板上に一体形成する例を示す。

#### 【0063】

なお、ロジック回路とは、シフトレジスタなどに代表される駆動回路とは別の機能を有する信号処理回路であり、D/Aコンバータ回路、メモリ回路、補正回路、さらには演算処理回路など、従来外付けI Cで行っていた様な信号処理を行う回路の総称を意味する。

#### 【0064】

まず、図1を用いて説明した作製工程に従って、単結晶シリコン薄膜の形成までを終了させる。そして、得られた単結晶シリコン薄膜をパターニングして活性層303～305を形成する。303はC M O S回路のP T F Tの活性層、304はC M O S回路のN T F Tの活性層、305は画素マトリクス回路の活性層であり、それぞれの膜厚は30nmとなる様に調節してある。

#### 【0065】

なお、本実施例では基板301としてSiO<sub>2</sub>:65%、Al<sub>2</sub>O<sub>3</sub>:25%、MgO:10%、ZrO<sub>2</sub>:10%の組成を有する結晶化ガラスを用いる。この基板301は透明である点に特徴がある。また、302は非晶質シリコン膜を熱酸化させて得た酸化シリコン膜であり、膜厚は400nmである。

#### 【0066】

こうして図3(A)の状態が得られる。次に、酸化シリコン膜から構成されるゲイト絶縁膜306を120nmの膜厚に形成する。なお、他にも酸化窒化シリコン膜又は窒化シリコン膜を用いることができる。さらに、これら絶縁性シリコン膜を自由に組み合わせて積層構造としても良い。

#### 【0067】

ゲイト絶縁膜306を形成したら、その状態で800～1100(好ましくは1000～1150)の温度範囲で熱酸化工程を行う。この時、活性層とゲイト絶縁膜との界面で熱酸化反応が進行するため、活性層は薄膜化され、ゲイト絶縁膜の膜厚は増加する。この構成はエッジシニング現象(活性層端部で熱酸化膜が極端に薄くなる現象)によるゲイト絶縁膜の絶縁破壊を抑える上で効果的である。

#### 【0068】

また、この時、加熱処理の雰囲気は不活性雰囲気でも酸化雰囲気でも良いが、ドライO<sub>2</sub>雰囲気が最も安定な界面特性を得る上で好ましい。また、高温で加熱処理を行うことによりゲイト絶縁膜自体の膜質も向上する。

#### 【0069】

次に、ゲイト絶縁膜306の上にN型導電性を呈する結晶性シリコン膜からなるゲイト電極307～309を形成する。ゲイト電極307～309の膜厚は200～300nmの範囲で選択すれば良い。(図3(B))

#### 【0070】

ゲイト電極307～309を形成したら、ゲイト電極307～309をマスクとしてドライエッチング法によりゲイト絶縁膜306をエッチングする。本実施例では酸化シリコン膜をエッチングするためにCHF<sub>3</sub>ガスを用いる。

#### 【0071】

この工程によりゲイト電極(及びゲイト配線)の直下のみにゲイト絶縁膜が残存する状態となる。勿論、ゲイト電極の下に残った部分が実際にゲイト絶縁膜として機能する部分である。

#### 【0072】

次に、P T F Tとなる領域をレジストマスク310で隠し、N型を付与する不純物(本実施例ではリン)をイオンインプランテーション法またはプラズマドーピング法により添加する。この時形成される低濃度不純物領域311、312の一部は後にL D D(Lightly Doped Drain)領域となるので、 $1 \times 10^{17} \sim 5 \times 10^{18} \text{ atoms/cm}^3$ の濃度でリンを添加し

10

20

30

40

50

ておく。（図3（C））

【0073】

次に、レジストマスク310を除去した後、N TFTとなる領域をレジストマスク313で隠し、P型を付与する不純物（本実施例ではボロン）をイオンインプランテーション法またはプラズマドーピング法により添加する。この時も、リンの場合と同様に低濃度不純物領域314を形成する。（図3（D））

【0074】

こうして図3（D）の状態が得られたら、レジストマスク313を除去した後、エッチバック法を用いてサイドウォール315～317を形成する。本実施例ではサイドウォール315～317を窒化シリコン膜を用いて構成する。

10

【0075】

なお、サイドウォールの材料として酸化シリコン膜を用いる場合、結晶化ガラス301の側面を保護する酸化シリコン膜302の膜厚が薄いとエッチバック工程でなくなってしまう場合も起こりうる。ガラス側面は全体の面積よりも十分に小さいためガラス成分の流出はさほど問題とならないが、予め酸化シリコン膜302の膜厚を厚くしてエッチバック工程後も残る様にしておいても良い。

【0076】

こうしてサイドウォール315～317を形成したら、再びP TFTとなる領域をレジストマスク318で隠し、リンを添加する。この時は先程の添加工程よりもドーズ量を高くする。

20

【0077】

このリンの添加工程によりCMOS回路を構成するN TFTのソース領域319、ドレイン領域320、低濃度不純物領域（LDD領域）321、チャネル形成領域322が画定する。また、画素マトリクス回路を構成するN TFTのソース領域323、ドレイン領域324、低濃度不純物領域（LDD領域）325、チャネル形成領域326が画定する。（図4（A））

【0078】

次に、レジストマスク315を除去した後、レジストマスク327でN TFTとなる領域を隠し、ボロンを先程よりも高いドーズ量で添加する。このボロンの添加工程によりCMOS回路を構成するP TFTのソース領域328、ドレイン領域329、低濃度不純物領域（LDD領域）330、チャネル形成領域331が画定する。（図4（B））

30

【0079】

以上の様にして、活性層への不純物の添加工程が終了したら、ファーネスアニール、レーザーアニールまたはランプアニールによって熱処理を行い、添加した不純物の活性化を行う。また、この時、不純物の添加時に活性層が受けた損傷も回復される。

【0080】

なお、チャネル形成領域322、326、331は全く不純物元素が添加されず、真性または実質的に真性な領域である。ここで実質的に真性であるとは、N型又はP型を付与する不純物濃度がチャネル形成領域のスピンドル以下であること、或いは同不純物濃度が $1 \times 10^{14} \sim 1 \times 10^{17} \text{ atoms/cm}^3$ の範囲に収まっていることを指す。

40

【0081】

次に、25nm厚の窒化シリコン膜と900nm厚の酸化シリコン膜との積層膜からなる第1の層間絶縁膜332を形成する。そして、Ti/Al/Ti（膜厚は順に100/500/100 nm）からなる積層膜で構成されるソース電極333～335、ドレイン電極336、337を形成する。

【0082】

次に、50nm厚の窒化シリコン膜338、20nm厚の酸化シリコン膜（図示せず）、1  $\mu\text{m}$ 厚のポリイミド膜339の積層構造からなる第2の層間絶縁膜を形成する。なお、ポリイミド以外にもアクリル、ポリアミド等の他の有機性樹脂膜を用いることができる。また、この場合の20nm厚の酸化シリコン膜はポリイミド膜339をドライエッチングする際の工

50

ツチングストッパーとして機能する。

【0083】

第2の層間絶縁膜を形成したら、後に補助容量を形成する領域においてポリイミド膜339をエッチングして開口部を設ける。この時、開口部の底部には窒化シリコン膜338のみ残すか、窒化シリコン膜338と酸化シリコン膜(図示せず)を残すかのいずれかの状態とする。

【0084】

そして、300nm厚のチタン膜を成膜し、パターニングによりブラックマスク340を形成する。このブラックマスク340は画素マトリクス回路上において、TFTや配線部など遮光を要する部分に配置される。

【0085】

この時、前述の開口部では画素マトリクス回路のドレイン電極337とブラックマスク340とが窒化シリコン膜338(又は窒化シリコン膜と酸化シリコン膜との積層膜)を挟んで近接した状態となる。本実施例ではブラックマスク340を固定電位に保持して、ドレイン電極337を下部電極、ブラックマスク340を上部電極とする補助容量341を構成する。この場合、誘電体が非常に薄く比誘電率が高いため、大きな容量を確保することが可能である。

【0086】

こうしてブラックマスク340及び補助容量341を形成したら、1μm厚のポリイミド膜を形成して第3の層間絶縁膜342とする。そして、コンタクトホールを形成して透明導電膜(代表的にはITO)で構成される画素電極343を120nmの厚さに形成する。

【0087】

最後に、水素雰囲気中で350~2時間程度の加熱処理を行い、素子全体の水素化を行う。こうして図4(C)に示す様なアクティブマトリクス基板が完成する。本実施例で形成されたTFTは活性層として単結晶シリコン薄膜を用いているため、非常に高い性能を有する。

【0088】

例えば、サブスレッショルド係数(S値)はNTFT、PTFT共に60~80mV/decadeであり、NTFTの電界効果移動度(モビリティ)は300~700cm<sup>2</sup>/Vs、PTFTのモビリティは200~400cm<sup>2</sup>/Vsを実現する。

【0089】

また、単結晶シリコン薄膜をスマートカット法で形成しているので基板上における活性層の膜厚の均一性を高めることができる。特に、高い均一性を要求される画素TFT(画素マトリクス回路を構成するTFT)の特性バラツキを抑える上で本願発明は非常に有効である。

【0090】

また、アクティブマトリクス基板が完成したら、公知のセル組み工程によって対向基板との間に液晶層を挟持すればアクティブマトリクス型の液晶表示装置(透過型)が完成する。

【0091】

なお、アクティブマトリクス基板の構造は本実施例に限定されず、あらゆる構造とすることができる。即ち、本願発明の構成要件を満たしうる構造であれば、TFT構造や回路配置等は実施者が自由に設計することができる。

【0092】

例えば、本実施例では画素電極として透明導電膜を用いているが、これをアルミニウム合金膜など反射性の高い材料に変えれば容易に反射型のアクティブマトリクス型液晶表示装置を実現することができる。また、この場合、アクティブマトリクス基板の母体となる結晶化ガラスは透明である必要はなく、遮光性の基板を用いても構わない。

【0093】

また、本実施例ではアクティブマトリクス基板として結晶化ガラスを用いているので対

10

20

30

40

50

向基板としてガラス基板を用いる場合に相性がいい。仮にアクティブマトリクス基板をして石英を用いると、石英とガラスの熱膨張係数の違いからアクティブマトリクス基板と対向基板との間で反りが生じる場合がある。

【実施例3】

【0094】

本実施例では実施例1、2の構成において結晶化ガラスを保護するための絶縁性シリコン膜を減圧熱CVD法により形成する場合の例について説明する。

【0095】

まず、基板として $\text{SiO}_2$ : 52.5、 $\text{Al}_2\text{O}_3$ : 26.5、 $\text{MgO}$ : 11.9、 $\text{TiO}_2$ : 11.4を組成成分とする結晶化ガラスを用意する。これは核形成剤として $\text{TiO}_2$ を利用した無アルカリのコーデュライト系結晶化ガラスである。

【0096】

次に、結晶化ガラスの表面、裏面及び側面に対して酸化窒化シリコン膜を形成する。本実施例では成膜ガスとしてシラン( $\text{SiH}_4$ )と亜酸化窒素( $\text{N}_2\text{O}$ )を用いた減圧熱CVD法により酸化窒化シリコン膜を形成する。

【0097】

この場合、成膜温度は800~850 (本実施例では850)で行い、それぞれの成膜ガスの流量は $\text{SiH}_4$ : 10~30sccm、 $\text{N}_2\text{O}$ : 300~900sccmとする。また、反応圧力は0.5~1.0torrとすれば良い。

【0098】

また、成膜ガスとしてシランと二酸化窒素( $\text{N}_2\text{O}$ )又は一酸化窒素( $\text{NO}$ )を用いれば600~650の温度で酸化窒化シリコン膜を形成することもできる。その場合、反応圧力は0.1~1.0torrとし、それぞれのガス流量は $\text{SiH}_4$ : 10~30sccm、 $\text{NO}$ 又は $\text{NO}_2$ : 300~900sccmとすれば良い。

【0099】

本実施例の場合、減圧熱CVD法により酸化窒化シリコン膜を形成するため、結晶化ガラスの全面が絶縁膜で包まれる形となる。また、成膜ガスを異なるものとすることで結晶化ガラスの保護膜として窒化シリコン膜を形成することもできる。

【0100】

その場合、成膜ガスとして40~50sccmのジクロールシラン( $\text{SiH}_2\text{Cl}_2$ )と200~250sccmのアンモニア( $\text{NH}_3$ )とを用い、成膜温度を750~800、反応圧力を0.1~0.5torrとすれば良い。

【0101】

窒化シリコン膜はガラス成分の流出を阻止するには最適な絶縁膜であるが応力が強いのでTFTの下地膜としては不向きであった。しかしながら、本願発明では結晶化ガラスの少なくとも表面及び裏面に窒化シリコン膜が形成されるので窒化シリコン膜の応力が基板の裏表で相殺され、基板の反り等は発生しない。

【実施例4】

【0102】

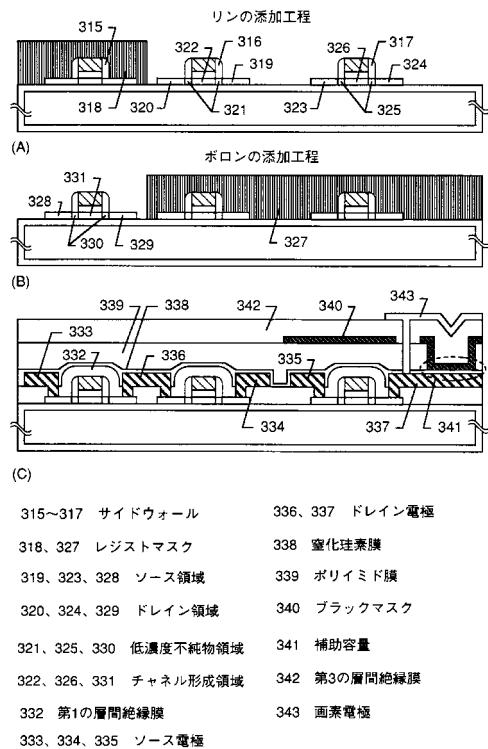

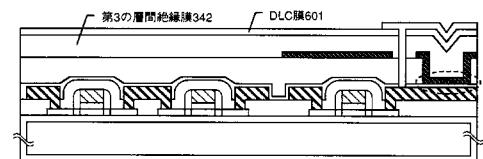

本実施例では、実施例1乃至実施例2においてゲイト絶縁膜として減圧熱CVD法により成膜した絶縁性シリコン膜を用いる場合の例を示す。説明には図5を用いる。図5に示す状態は、ゲイト電極を形成した後にゲイト絶縁膜をエッティングした直後の状態である。

【0103】

図5において、501は結晶化ガラス、502は結晶化ガラスからの成分物質の流出を阻止するための保護膜(下地膜)となる酸化窒化シリコン膜である。結晶化ガラス501の表面側には活性層503~505が形成され、ゲイト絶縁膜を成膜した後、ゲイト電極506~508が形成される。

【0104】

このゲイト電極506~508をマスクとしてドライエッティングを行うことでゲイト電極直下にゲイト絶縁膜509~511が残存する。

10

20

30

40

50

## 【0105】

本実施例の最も重要な構成は、ゲイト絶縁膜として減圧熱CVD法により成膜した絶縁性シリコン膜（本実施例では酸化窒化シリコン膜）を用いる点にある。即ち、ゲイト絶縁膜も結晶化ガラス501の表面、裏面及び側面側の全ての面に成膜される点が特徴である。

## 【0106】

従って、ゲイト絶縁膜（酸化窒化シリコン膜）のエッティング工程が終了した時点（図5の状態）では基板の表面側はゲイト電極でマスクされた部分以外は完全に除去され、基板の裏面及び側面にはそのまま酸化窒化シリコン膜512が残る。なお、側面に形成された酸化窒化シリコン膜は条件によっては除去されてしまうが、側面は除去されてしまっても問題ない。

## 【0107】

本実施例の構成では、後の工程で裏面及び側面が酸化窒化シリコン膜をエッティングしうるエッチャント又はエッティングガスに曝されることがあっても結晶化ガラス501に直接成膜した酸化窒化シリコン膜502を残すことができる。即ち、ガラス基板からの成分物質の流出を徹底的に阻止することが可能である。

## 【実施例5】

## 【0108】

実施例2ではゲイト電極としてN型導電性を呈する結晶性シリコン膜を利用しているが、導電性を有する材料であればあらゆる材料を用いることができる。特に、直視用の液晶表示装置を作製する場合には、画素マトリクス回路の面積が大きくなるため配線抵抗の小さい材料を用いることが好ましい。

## 【0109】

その様な場合には、ゲイト電極としてアルミニウムまたはアルミニウムを主成分とする材料を用いることが望ましい。本実施例ではゲイト電極として2wt%のスカンジウムを含有したアルミニウム膜を用いる。

## 【0110】

アルミニウムを主成分とする材料をゲイト電極として利用する場合には、本発明者らによる特開平7-135318号公報に記載された技術を利用すると良い。同公報では実施例1で用いたサイドウォールの代わりにゲイト電極を陽極酸化して得られる陽極酸化膜を利用している。

## 【0111】

本実施例の様にゲイト電極としてアルミニウムまたはアルミニウムを主成分とする材料を用いることで配線抵抗の小さいゲイト配線を形成することが可能となり、応答速度の速いアクティブマトリクス基板を作製することができる。

## 【0112】

なお、本実施例は実施例1～4の構成と組み合わせることが可能である。

## 【実施例6】

## 【0113】

実施例2において、活性層中にTFTのしきい値電圧（V<sub>th</sub>）を制御するための不純物元素を添加することは有効である。この不純物元素は少なくともチャネル形成領域にさえ添加されていれば良いので、ゲイト電極の形成前であれば何時添加しても良い。

## 【0114】

成膜時以外に添加する場合には、イオンインプランテーション法またはプラズマドーピング法による添加、気相中からの拡散による添加、固相中からの拡散による添加などの手段を用いることができる。これらの手段は、例えばNTFTとPTFTとで添加する不純物を異なせるといった具合に選択的な添加が可能であるため有効である。

## 【0115】

また、添加する不純物元素としては、V<sub>th</sub>をプラス側に移動させるのであれば13族元素（ボロン、ガリウム又はインジウム）を用い、マイナス側に移動させるのであれば15

10

20

30

40

50

元素（リン、砒素又はアンチモン）を用いる。

【0116】

なお、本実施例は実施例1～5の構成と組み合わせることが可能である。

【実施例7】

【0117】

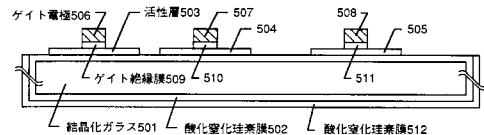

本実施例では、実施例1で説明したアクティブマトリクス基板において、第3の層間絶縁膜342（図4（C）参照）の上にヒートシンクとしてDLC（Diamond Like Carbon）膜を利用する場合の例について説明する。

【0118】

図6に示す構造は、基本的には図4（C）の構造と同じであるが第3の層間絶縁膜342上にDLC膜601が設けられている点が異なる。

【0119】

DLCとは、ダイヤモンドの如き物性を示す炭素または炭素を主成分とする硬度の高い材料である。また、i-カーボンとも呼ばれ、sp<sup>3</sup>結合を主体として構成されている。

【0120】

ダイヤモンドは室温において最も熱伝導率の高い材料（室温で約10～20W/cm·k）であり、それと同等の物性を示すDLC膜も高い熱伝導率を示す。本実施例ではその熱伝導率の高さを利用してヒートシンクとして機能させている。

【0121】

また、DLC膜は有機性樹脂膜との密着性に優れているため、層間絶縁膜として有機性樹脂膜を用い、その上にヒートシンクを設ける場合には非常に有効な材料である。

【0122】

なお、DLC膜の成膜手段としてはプラズマCVD法、ECRプラズマCVD法、スパッタ法、イオンビームスパッタ法、イオン化蒸着法等の気相成膜法を用いることができる。

【0123】

また、DLC膜を形成する際の原料ガスとしては炭化水素が用いられる。炭化水素としてはメタン、エタン、プロパン等の飽和炭化水素、エチレン、アセチレン等の不飽和炭化水素が挙げられる。また、炭化水素分子の水素のうち1個若しくは複数個がハロゲン元素に置換したハロゲン化炭化水素を用いても良い。

【0124】

また、炭化水素の他に水素を添加することは有効である。水素を添加するとプラズマ中の水素ラジカルが増加し、膜中の余分な水素を引き抜き、膜質を向上させる効果が期待できる。この時、全ガス流量に対する水素ガス流量の比は30～90%、好ましくは50～70%が良い。この比が多すぎると成膜速度が減少し、少なすぎると余分な水素の引き抜き効果がなくなる。

【0125】

さらに、原料ガスを希釈するキャリアガスとしてヘリウムを添加することもできるし、スパッタ法の場合にはスパッタリングガスとしてアルゴンを添加する場合もある。また、特開平6-208721号公報に記載される様に13～15族の元素を添加することも有効である。

【0126】

また、反応圧力は5～1000mTorr、好ましくは10～100mTorrが良い。高周波電力は通常13.56MHzを用いる。この時、印加するRF電力は0.01～1W/cm<sup>2</sup>、好ましくは0.05～0.5W/cm<sup>2</sup>とする。さらに、原料ガスの分解を助長するために2.45GHzのマイクロ波による励起効果を付加したり、その励起空間に対して875ガウスの磁場を形成し、電子スピニ共鳴を利用することも有効である。

【0127】

本実施例ではプラズマCVD装置の反応空間に原料ガスとしてメタンガスを50sccm、水素ガスを50sccmを導入し、成膜圧力は10mTorr、RF電力は100W、反応空間の温度は室温

10

20

30

40

40

50

とする。また、基板バイアスとして 200V の直流バイアスを加え、プラズマ中の粒子（イオン）が被形成面上に入射する様な電界を形成することで膜質の緻密化と硬度の向上を図っている。

#### 【0128】

また、DLC 膜は膜厚が 10nm 程度でも非常に高い耐摩耗性を持っている。そのため、図 7 に示した構造では第 3 の層間絶縁膜 342 を機械的な衝撃から保護する効果が得られる。これは、ラビング工程等による摩擦工程に対して非常に効果的である。

#### 【0129】

なお、摩擦係数は DLC 膜厚に依存性を有し、 DLC 膜厚が厚くなる程小さくなる。従って、 DLC 膜の膜厚は 10nm 以上あれば良いことになるが、厚すぎると液晶に印加される電界が弱くなるので 10 ~ 50nm 程度が良い。

#### 【0130】

なお、 DLC 膜のさらに詳細な成膜方法および成膜装置等については、本発明者らによる特公平 3-72711 号公報、同 4-27690 号公報、同 4-27691 号公報を参考にすると良い。

#### 【0131】

以上の様な構成で得られた図 7 の構造では、 TFT で発生した熱が高い効率で逃がされるので、蓄熱による動作不良を防ぐことができる。特に、プロジェクションタイプの電子機器に用いる液晶表示装置には、この様な耐熱構造を利用した方が良い。

#### 【実施例 8】

#### 【0132】

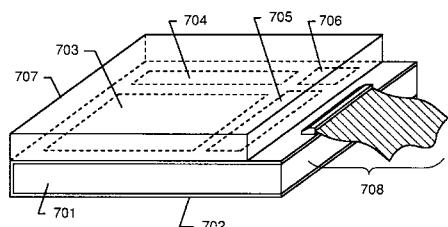

実施例 1 ~ 7 に示した構成を有するアクティブマトリクス基板を用い、液晶表示装置を構成した例を図 7 に示す。図 7 は液晶表示装置の本体に相当する部位であり、液晶モジュールとも呼ばれる。

#### 【0133】

図 7 において、 701 は結晶化ガラス、 702 は結晶化ガラスの全面を包む様にして形成された絶縁性シリコン膜である。大版基板から多面取りによって複数枚のアクティブマトリクス基板を切り出す場合には切断面となる側面には絶縁性シリコン膜が存在しないが、それ以外の側面には絶縁性シリコン膜が残るというのが本願発明の特徴である。勿論、アクティブマトリクス基板として完成してしまっているので絶縁性シリコン膜で保護されていなくても成分物質が流出する心配はない。

#### 【0134】

そして、この様な構成の基板上に単結晶シリコン薄膜でもって複数の TFT が形成されている。これらの TFT は基板上に画素マトリクス回路 703 、ゲイト側駆動回路 704 、ソース側駆動回路 705 、ロジック回路 706 を構成する。そして、その様なアクティブマトリクス基板に対して対向基板 707 が貼り合わされる。アクティブマトリクス基板と対向基板 707 との間には液晶層（図示せず）が挟持される。

#### 【0135】

また、図 7 に示す構成では、アクティブマトリクス基板の側面と対向基板の側面とをある一辺を除いて全て揃えることが望ましい。こうすることで大版基板からの多面取り数を効率良く増やすことができる。また、前述の一辺では、対向基板の一部を除去してアクティブマトリクス基板の一部を露出させ、そこに FPC (フレキシブル・プリント・サーキット) 708 を取り付ける。ここには必要に応じて IC チップ（単結晶シリコン上に形成された MOSFET で構成される半導体回路）を搭載しても構わない。

#### 【0136】

本実施例の回路を構成する TFT は極めて高い動作速度を有しているため、数百 MHz ~ 数 GHz の高周波数で駆動する信号処理回路を画素マトリクス回路と同一の基板上に一体形成することが可能である。即ち、図 7 に示す液晶モジュールはシステム・オン・パネルを具現化したものである。

#### 【0137】

なお、本実施例では本願発明を液晶表示装置に適用した場合について記載しているが、

10

20

30

40

50

アクティブマトリクス型 E L (エレクトロルミネッセンス) 表示装置などを構成することも可能である。また、光電変換層を具備したイメージセンサ等を同一基板上に形成することも可能である。

【0138】

なお、上述の液晶表示装置、E L 表示装置及びイメージセンサの様に光学信号を電気信号に変換する、又は電気信号を光学信号に変換する機能を有する装置を電気光学装置と定義する。本願発明は絶縁表面を有する基板上に半導体薄膜を利用して形成しうる電気光学装置ならば全てに適用することができる。

【実施例9】

【0139】

本願発明は実施例8に示した様な電気光学装置だけでなく、機能回路を集積化した薄膜集積回路（または半導体回路）を構成することもできる。例えば、マイクロプロセッサ等の演算回路や携帯機器用の高周波回路（M M I C：マイクロウェイブ・モジュール・I C）などを構成することもできる。

【0140】

さらには、薄膜を用いるT F T の利点を生かして三次元構造の半導体回路を構成し、超高密度に集積化されたV L S I 回路を構成することも可能である。この様に、本願発明のT F T を用いて非常に機能性に富んだ半導体回路を構成することが可能である。なお、本明細書中において、半導体回路とは半導体特性を利用して電気信号の制御、変換を行う電気回路と定義する。

【実施例10】

【0141】

本実施例では、実施例8や実施例9に示された電気光学装置や半導体回路を搭載した電子機器（応用製品）の一例を図8に示す。なお、電子機器とは半導体回路および/または電気光学装置を搭載した製品と定義する。

【0142】

本願発明を適用しうる電子機器としてはビデオカメラ、電子スチルカメラ、プロジェクター、ヘッドマウントディスプレイ、カーナビゲーション、パソコンコンピュータ、携帯情報端末（モバイルコンピュータ、携帯電話、P H S 等）などが挙げられる。

【0143】

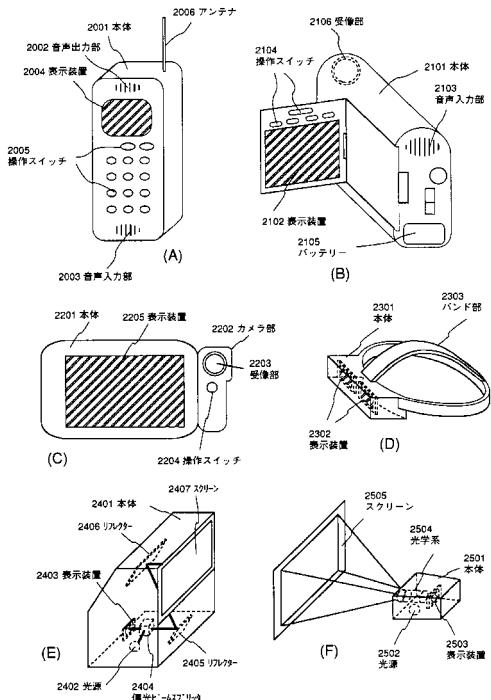

図8（A）は携帯電話であり、本体2001、音声出力部2002、音声入力部2003、表示装置2004、操作スイッチ2005、アンテナ2006で構成される。本願発明は音声出力部2002、音声入力部2003、表示装置2004等に適用することができる。

【0144】

図8（B）はビデオカメラであり、本体2101、表示装置2102、音声入力部2103、操作スイッチ2104、バッテリー2105、受像部2106で構成される。本願発明は表示装置2102、音声入力部2103、受像部2106等に適用することができる。

【0145】

図8（C）はモバイルコンピュータ（モービルコンピュータ）であり、本体2201、カメラ部2202、受像部2203、操作スイッチ2204、表示装置2205で構成される。本願発明はカメラ部2202、受像部2203、表示装置2205等に適用できる。

【0146】

図8（D）はヘッドマウントディスプレイであり、本体2301、表示装置2302、バンド部2303で構成される。本発明は表示装置2302に適用することができる。

【0147】

図8（E）はリア型プロジェクターであり、本体2401、光源2402、表示装置2403、偏光ビームスプリッタ2404、リフレクター2405、2406、スクリーン

10

20

30

40

50

2407で構成される。本発明は表示装置2403に適用することができる。

【0148】

図8(F)はフロント型プロジェクターであり、本体2501、光源2502、表示装置2503、光学系2504、スクリーン2505で構成される。本発明は表示装置2503に適用することができる。

【0149】

以上の様に、本願発明の適用範囲は極めて広く、あらゆる分野の電子機器に適用することが可能である。また、電気光学装置や半導体回路を必要とする製品であれば全てに適用できる。

【図面の簡単な説明】

【0150】

【図1】単結晶シリコン薄膜の作製工程を示す図。

【図2】スマートカット法の工程を示す図。

【図3】薄膜トランジスタの作製工程を示す図。

【図4】薄膜トランジスタの作製工程を示す図。

【図5】薄膜トランジスタの構成を示す図。

【図6】薄膜トランジスタの構成を示す図。

【図7】液晶モジュールの構成を示す図。

【図8】電子機器の構成を示す図。

10

【図1】

【図2】

prior art

【図3】

301 結晶化ガラス 310、313 レジストマスク

302 絶縁性珪素膜 311、312 低濃度不純物領域（リン）

303~305 活性層 314 低濃度不純物領域（ボロン）

306 ゲイト絶縁膜

307~309 ゲート電極

【図4】

【図5】

【図6】

【図7】

701 結晶化ガラス 705 ソース側駆動回路

702 絶縁性珪素膜 706 ロジック回路

703 画素マトリクス回路 707 対向基板

704 ゲイト側駆動回路 708 FPC

【図8】