(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7200476号**

**(P7200476)**

(45)発行日 令和5年1月10日(2023.1.10)

(24)登録日 令和4年12月26日(2022.12.26)

(51)国際特許分類

|        |                |     |        |      |   |

|--------|----------------|-----|--------|------|---|

| H 03 M | 1/08 (2006.01) | F I | H 03 M | 1/08 | A |

| H 03 M | 1/46 (2006.01) |     | H 03 M | 1/46 |   |

| H 03 F | 3/38 (2006.01) |     | H 03 F | 3/38 |   |

請求項の数 10 (全28頁)

|          |                             |

|----------|-----------------------------|

| (21)出願番号 | 特願2017-254044(P2017-254044) |

| (22)出願日  | 平成29年12月28日(2017.12.28)     |

| (65)公開番号 | 特開2019-121851(P2019-121851) |

|          | A)                          |

| (43)公開日  | 令和1年7月22日(2019.7.22)        |

| 審査請求日    | 令和2年11月20日(2020.11.20)      |

|          |                                              |

|----------|----------------------------------------------|

| (73)特許権者 | 000002369<br>セイコーホームズ株式会社<br>東京都新宿区新宿四丁目1番6号 |

| (74)代理人  | 100104710<br>弁理士 竹腰 昇                        |

| (74)代理人  | 100090479<br>弁理士 井上 一                        |

| (74)代理人  | 100124682<br>弁理士 黒田 泰                        |

| (74)代理人  | 100166523<br>弁理士 西河 宏晃                       |

| (74)代理人  | 100187539<br>弁理士 藍原 由和                       |

| (72)発明者  | 田中 敦嗣<br>長野県諏訪市大和3丁目3番5号 セイ<br>最終頁に続く        |

(54)【発明の名称】 回路装置、振動デバイス、電子機器及び移動体

**(57)【特許請求の範囲】****【請求項1】**

第1～第nの電圧（nは2以上の整数）が入力されるセレクターと、

電荷再分配型のD/A変換回路を有し、前記セレクターの出力電圧が入力電圧として入力され、前記D/A変換回路を用いた逐次比較動作により前記入力電圧のA/D変換を行うA/D変換回路と、

前記第1～第nの電圧の前記A/D変換における量子化誤差に対応する電荷を保持する第1～第nの量子化誤差保持回路と、

を含み、

前記A/D変換回路は、

前記入力電圧に対応する電圧から、第iの電圧（iは1以上n以下の整数）のk-1回目（kは2以上の整数）のA/D変換における量子化誤差に対応する電荷として第iの量子化誤差保持回路に保持された電荷に対応する電圧を減算した電圧を出力する加算回路を有し、

前記D/A変換回路は、

前記加算回路の出力電圧と逐次比較データのD/A変換電圧との差分電圧を出力し、

前記A/D変換回路は、

前記差分電圧に基づいて、前記第iの電圧についてのk回目のA/D変換を行い、量子化誤差がノイズシェーピングされたA/D変換結果データを出力し、

前記第iの量子化誤差保持回路は、

10

20

前記第 i の電圧についての前記逐次比較動作を終了した後の前記差分電圧に対応する電荷を保持し、

前記 D / A 変換回路は、

正極側のキャパシターアレイ回路と負極側のキャパシターアレイ回路とを有する差動型の D / A 変換回路であり、

前記加算回路は、

全差動型の演算増幅器と、

前記演算増幅器の反転出力ノードと非反転入力ノードとの間に設けられる正極側の帰還用キャパシターと、

前記演算増幅器の非反転出力ノードと反転入力ノードとの間に設けられる負極側の帰還用キャパシターと、

を有し、

前記第 i の量子化誤差保持回路は、

正極側の保持回路と負極側の保持回路とを有し、

前記正極側の保持回路は、

正極側の保持用キャパシターと、

前記正極側の保持用キャパシターの一端を、前記正極側のキャパシターアレイのサンプリングノードとコモン電圧のノードとのいずれかに接続する第 1 の正極側スイッチと、

前記正極側の保持用キャパシターの他端を、前記コモン電圧のノードと前記反転入力ノードとのいずれかに接続する第 2 の正極側スイッチと、

を有し、

前記負極側の保持回路は、

負極側の保持用キャパシターと、

前記負極側の保持用キャパシターの一端を、前記負極側のキャパシターアレイのサンプリングノードと前記コモン電圧のノードとのいずれかに接続する第 1 の負極側スイッチと、

前記負極側の保持用キャパシターの他端を、前記コモン電圧のノードと前記非反転入力ノードとのいずれかに接続する第 2 の負極側スイッチと、

を有することを特徴とする回路装置。

#### 【請求項 2】

請求項 1 に記載の回路装置において、

前記加算回路は、

前記演算増幅器の前記非反転入力ノード及び前記反転入力ノードに入力される電圧に対してチョッピングの変調を行うチョッピング変調回路と、

前記演算増幅器の前記反転出力ノード及び前記非反転出力ノードから出力される電圧に対してチョッピングの復調を行うチョッピング復調回路と、

を有することを特徴とする回路装置。

#### 【請求項 3】

請求項 1 又は 2 に記載の回路装置において、

前記 A / D 変換回路は、

前記加算回路の出力電圧と前記逐次比較データの D / A 変換電圧との間の比較判定を、前記 D / A 変換回路からの前記差分電圧に基づいて行う比較回路と、

前記比較回路による比較結果に基づいて前記逐次比較データを更新し、前記 D / A 変換回路に出力する制御回路と、

を有することを特徴とする回路装置。

#### 【請求項 4】

第 1 ~ 第 n の電圧 ( n は 2 以上の整数 ) が入力されるセレクターと、

電荷再分配型の D / A 変換回路及び加算回路を有し、前記セレクターの出力電圧が入力電圧として入力され、前記 D / A 変換回路を用いた逐次比較動作により前記入力電圧の A / D 変換を行う A / D 変換回路と、

前記第 1 ~ 第 n の電圧の前記 A / D 変換における量子化誤差に対応する電荷を保持する

10

20

30

40

50

第 1 ~ 第 n の量子化誤差保持回路と、

を含み、

第 i の量子化誤差保持回路は、保持用キャパシター、第 1 のスイッチ及び第 2 のスイッチを有し、

リセット期間において、前記第 1 のスイッチは、第 i の電圧 ( i は 1 以上 n 以下の整数 ) の k - 1 回目 ( k は 2 以上の整数 ) の A / D 変換における量子化誤差に対応する電荷を保持した前記保持用キャパシターの一端を、フローティング状態に設定し、前記第 2 のスイッチは、前記保持用キャパシターの他端をコモン電圧のノードに接続し、

前記リセット期間の後の加算期間、サンプリング期間及び逐次比較期間において、前記第 1 のスイッチは、前記保持用キャパシターの一端を前記コモン電圧のノードに接続し、前記第 2 のスイッチは、前記保持用キャパシターの他端を前記加算回路の入力ノードに接続し、前記加算回路は、前記入力電圧に対応する電圧から、前記第 i の量子化誤差保持回路に保持された電荷に対応する電圧を減算した電圧を出力し、前記 D / A 変換回路は、前記加算回路の出力電圧と逐次比較データの D / A 変換電圧との差分電圧を出力し、前記 A / D 変換回路は、前記差分電圧に基づいて、前記第 i の電圧についての k 回目の A / D 変換を行い、量子化誤差がノイズシェーピングされた A / D 変換結果データを出力し、

前記加算期間、前記サンプリング期間及び前記逐次比較期間の後の量子化誤差保持期間において、前記第 1 のスイッチは、前記保持用キャパシターの一端を、前記 D / A 変換回路のキャパシターアレイのサンプリングノードに接続し、前記第 2 のスイッチは、前記保持用キャパシターの他端を、前記コモン電圧のノードに接続し、前記保持用キャパシターは、前記第 i の電圧の k 回目の A / D 変換における量子化誤差に対応する電荷を保持することを特徴とする回路装置。

#### 【請求項 5】

請求項 1 乃至 4 のいずれか一項に記載の回路装置において、

温度検出電圧である前記入力電圧に対応する前記 A / D 変換結果データに基づく周波数制御データを出力する処理回路と、

前記周波数制御データに対応する発振周波数の発振信号を、振動子を用いて生成する発振信号生成回路と、

を含むことを特徴とする回路装置。

#### 【請求項 6】

請求項 1 乃至 5 のいずれか一項に記載の回路装置において、

前記セレクターには、第 1 ~ 第 m の温度センサー ( m は 1 以上 n 以下の整数 ) からの第 1 ~ 第 m の温度検出電圧が、前記第 1 ~ 第 n の電圧の第 1 ~ 第 m の電圧として入力されることを特徴とする回路装置。

#### 【請求項 7】

請求項 1 乃至 6 のいずれか一項に記載の回路装置と、

前記回路装置に接続される振動子と、

を含むことを特徴とする振動デバイス。

#### 【請求項 8】

請求項 7 に記載の振動デバイスにおいて、

第 1 ~ 第 m の温度センサー ( m は 1 以上 n 以下の整数 ) を含み、

前記セレクターには、前記第 1 ~ 第 m の温度センサーからの第 1 ~ 第 m の温度検出電圧が、前記第 1 ~ 第 n の電圧の第 1 ~ 第 m の電圧として入力されることを特徴とする振動デバイス。

#### 【請求項 9】

請求項 1 乃至 6 のいずれか一項に記載された回路装置を含むことを特徴とする電子機器。

#### 【請求項 10】

請求項 1 乃至 6 のいずれか一項に記載された回路装置を含むことを特徴とする移動体。

#### 【発明の詳細な説明】

#### 【技術分野】

10

20

30

40

50

**【 0 0 0 1 】**

本発明は、回路装置、振動デバイス、電子機器及び移動体等に関する。

**【背景技術】****【 0 0 0 2 】**

従来より、入力信号の電圧と逐次比較データのD/A変換電圧とを比較し、その比較結果に基づいて逐次比較データを更新し、この比較及び更新を例えればバイナリーサーチ等の手法により繰り返し行うことで、入力信号をA/D変換する逐次比較型のA/D変換回路が知られている。逐次比較型のA/D変換回路は、低消費電力である一方で、例えばデルタシグマ型のA/D変換回路等に比べて高精度化（例えれば有効ビット数の拡大）が難しい。

**【 0 0 0 3 】**

逐次比較型のA/D変換回路を高精度化する技術として、例えれば特許文献1に開示される技術がある。特許文献1では、逐次比較型のA/D変換回路にデルタシグマ型の構成を取り入れてハイブリッド型のA/D変換回路を構成し、ノイズシェーピング効果により低周波数帯域での量子化雑音を低減し、高精度化を図っている。

10

**【先行技術文献】****【特許文献】****【 0 0 0 4 】**

**【文献】特開平11-4166号公報**

**【発明の概要】****【発明が解決しようとする課題】**

20

**【 0 0 0 5 】**

複数の入力信号がA/D変換回路に入力される場合、マルチチャンネル入力に対応したA/D変換回路が必要である。ハイブリッド型ではない逐次比較型のA/D変換回路では、複数の入力信号を時分割にA/D変換することで、マルチチャンネル入力のA/D変換回路を実現できる。しかしながら、高精度化のためにデルタシグマ型の構成を取り入れた従来のハイブリッド型のA/D変換回路では、マルチチャンネル入力に対応していない。例えは上述の特許文献1には、1チャンネル入力のみのハイブリッド型のA/D変換回路が開示されている。このため、従来のハイブリッド型のA/D変換回路では、A/D変換の高精度化とマルチチャンネル入力とを両立できなかった。

**【課題を解決するための手段】**

30

**【 0 0 0 6 】**

本発明は、上記の課題の少なくとも一部を解決するためになされたものであり、以下の形態又は態様として実現することが可能である。

**【 0 0 0 7 】**

本発明の一態様は、第1～第nの電圧（nは2以上の整数）が入力されるセレクターと、電荷再分配型のD/A変換回路を有し、前記セレクターの出力電圧が入力電圧として入力され、前記D/A変換回路を用いた逐次比較動作により前記入力電圧のA/D変換を行うA/D変換回路と、前記第1～第nの電圧の前記A/D変換における量子化誤差に対応する電荷を保持する第1～第nの量子化誤差保持回路と、を含み、前記A/D変換回路は、第iの電圧（iは1以上n以下の整数）のk-1回目（kは2以上の整数）のA/D変換における量子化誤差に対応する電荷として第iの量子化誤差保持回路に保持された電荷を用いて、前記第iの電圧についてのk回目のA/D変換を行い、量子化誤差がノイズシェーピングされたA/D変換結果データを出力する回路装置に関係する。

40

**【 0 0 0 8 】**

本発明の一態様によれば、電荷再分配型のD/A変換回路を用いた逐次比較動作により第iの電圧のA/D変換を行うことで、逐次比較動作が終了した後に、D/A変換回路が、第iの電圧についてのk-1回目のA/D変換における量子化誤差に対応した電圧を出力することが可能になる。この電圧に基づいて第iの量子化誤差保持回路が電荷を保持することで、第iの電圧についてのk-1回目のA/D変換における量子化誤差に対応した電圧を保持できる。そして、この電荷を用いて第iの電圧についてのk回目のA/D変換

50

を行うことで、量子化誤差のノイズシェーピングが可能となっている。本発明の一態様では、各チャンネルに対応した量子化誤差保持回路を設けることで、マルチチャンネル入力に対応することが可能である。以上のようにして、ノイズシェーピング効果によるA/D変換の高精度化と、マルチチャンネル入力とを両立できる。

#### 【0009】

また本発明の一態様では、前記A/D変換回路は、前記入力電圧に対応する電圧から、前記第*i*の量子化誤差保持回路に保持される電荷に対応する電圧を減算した電圧を出力する加算回路を有し、前記D/A変換回路は、前記加算回路の出力電圧と逐次比較データのD/A変換電圧との差分電圧を出力し、前記第*i*の量子化誤差保持回路は、前記第*i*の電圧についての前記逐次比較動作を終了した後の前記差分電圧に対応する電荷を保持してもよい。

10

#### 【0010】

本発明の一態様によれば、逐次比較の対象は加算回路の出力電圧である。この出力電圧は、入力電圧に対応する電圧から、第*i*の量子化誤差保持回路に保持される電荷に対応する電圧を減算した電圧である。即ち、第*i*の量子化誤差保持回路により第*i*の電圧に対して量子化誤差がフィードバックされている。これにより、デルタシグマ型の構成を取り入れたハイブリッド型のA/D変換回路を実現できる。

#### 【0011】

また本発明の一態様では、前記A/D変換回路は、前記加算回路の出力電圧と前記逐次比較データのD/A変換電圧との間の比較判定を、前記D/A変換回路からの前記差分電圧に基づいて行う比較回路と、前記比較回路による比較結果に基づいて前記逐次比較データを更新し、前記D/A変換回路に出力する前記逐次比較動作を行う制御回路と、を有してもよい。

20

#### 【0012】

本発明の一態様によれば、電荷再分配型のD/A変換回路を用いた逐次比較による入力電圧のA/D変換を実現できる。即ち、加算回路の出力電圧と逐次比較データのD/A変換電圧との間の比較判定に基づいて逐次比較データを更新し、その更新された逐次比較データをD/A変換回路に出力し、これらの動作を逐次に繰り返してA/D変換結果データを決定することで、逐次比較動作を実現できる。本発明の一態様では、第*i*の量子化誤差保持回路により第*i*の電圧に対して量子化誤差がフィードバックされるので、デルタシグマ型の構成を取り入れたハイブリッド型のA/D変換回路を実現できる。

30

#### 【0013】

また本発明の一態様では、前記D/A変換回路は、正極側のキャパシターアレイ回路と負極側のキャパシターアレイ回路とを有する差動型のD/A変換回路であり、前記加算回路は、全差動型の演算増幅器と、前記演算増幅器の反転出力ノードと非反転入力ノードとの間に設けられる正極側の帰還用キャパシターと、前記演算増幅器の非反転出力ノードと反転入力ノードとの間に設けられる負極側の帰還用キャパシターと、を有し、前記第*i*の量子化誤差保持回路は、正極側の保持回路と負極側の保持回路とを有し、前記正極側の保持回路は、正極側の保持用キャパシターと、前記正極側の保持用キャパシターの一端を、前記正極側のキャパシターアレイのサンプリングノードとコモン電圧のノードとのいずれかに接続する第1の正極側スイッチと、前記正極側の保持用キャパシターの他端を、前記コモン電圧のノードと前記反転入力ノードとのいずれかに接続する第2の正極側スイッチと、を有し、前記負極側の保持回路は、負極側の保持用キャパシターと、前記負極側の保持用キャパシターの一端を、前記負極側のキャパシターアレイのサンプリングノードと前記コモン電圧のノードとのいずれかに接続する第1の負極側スイッチと、前記負極側の保持用キャパシターの他端を、前記コモン電圧のノードと前記非反転入力ノードとのいずれかに接続する第2の負極側スイッチと、を有してもよい。

40

#### 【0014】

本発明の一態様によれば、第1の正極側スイッチが正極側の保持用キャパシターの一端を正極側のキャパシターアレイのサンプリングノードに接続し、第2の正極側スイッチが

50

正極側の保持用キャパシターの他端をコモン電圧のノードに接続することで、正極側の保持用キャパシターが量子化誤差に対応する電荷を保持できる。第1の負極側スイッチが負極側の保持用キャパシターの一端を負極側のキャパシターアレイのサンプリングノードに接続し、第2の負極側スイッチが負極側の保持用キャパシターの他端をコモン電圧のノードに接続することで、負極側の保持用キャパシターが量子化誤差に対応する電荷を保持できる。そして、第1の正極側スイッチが正極側の保持用キャパシターの一端をコモン電圧のノードに接続し、第2の正極側スイッチが正極側の保持用キャパシターの他端を演算増幅器の反転入力ノードに接続することで、正極側の保持用キャパシターが保持する電荷が、正極側の保持用キャパシターと負極側の帰還用キャパシターとの間で再分配される。第1の負極側スイッチが負極側の保持用キャパシターの一端をコモン電圧のノードに接続し、第2の負極側スイッチが負極側の保持用キャパシターの他端を演算増幅器の非反転入力ノードに接続することで、負極側の保持用キャパシターが保持する電荷が、負極側の保持用キャパシターと正極側の帰還用キャパシターとの間で再分配される。これにより、量子化誤差に対応する電圧を、A/D変換回路の入力電圧から減算することが可能になる。

#### 【0015】

また本発明の一態様では、前記加算回路は、全差動型の演算増幅器と、前記演算増幅器の非反転入力ノード及び反転入力ノードに入力される電圧に対してチョッピングの変調を行うチョッピング変調回路と、前記演算増幅器の反転出力ノード及び非反転出力ノードから出力される電圧に対してチョッピングの復調を行うチョッピング復調回路と、を有してもよい。

#### 【0016】

本発明の一態様では、ノイズシェーピング機構を有するため、A/D変換回路にDC信号が入力されたときにA/D変換結果データが特定の時間変化パターンになり、A/D変換結果データに不要周波数成分が発生する可能性がある。この現象をアイドルトーンと呼ぶ。本発明の一態様によれば、演算増幅器のオフセットによるA/D変換結果データの変化が、チョッピングの周波数の分だけ高周波数になり、上記のようなアイドルトーンを低減できる。

#### 【0017】

また本発明の一態様では、回路装置は、温度検出電圧である前記入力電圧に対応する前記A/D変換結果データに基づく周波数制御データを出力する処理回路と、前記周波数制御データに対応する発振周波数の発振信号を、振動子を用いて生成する発振信号生成回路と、を含んでもよい。

#### 【0018】

温度の変化は緩やかなので、温度検出電圧の信号帯域は低周波数の帯域になる。このため、逐次比較型のような比較的低速なA/D変換回路であっても、信号帯域より十分に高い変換レートでA/D変換できる。本発明の一態様では、ハイブリッド型のA/D変換回路を構成することで、上述したようなノイズシェーピング効果を伴うA/D変換を実現でき、温度センサーの信号帯域においてS/Nの高い測定が可能となる。

#### 【0019】

また本発明の一態様では、前記セレクターには、前記第1～第mの温度センサー（mは1以上n以下の整数）からの第1～第mの温度検出電圧が、前記第1～第nの電圧の第1～第mの電圧として入力されてもよい。

#### 【0020】

温度検出データ（温度検出電圧のA/D変換結果データ）を用いた処理として、振動デバイスにおける種々の処理を想定できる。例えばTCXOやOCXO等のデジタル方式の発振器における発振周波数の温度補償処理が考えられる。或いは物理量測定装置における温度依存誤差を補正する処理（例えばジャイロセンサーにおけるゼロ点補正）が考えられる。このとき、発振器や物理量測定装置の複数の位置に複数の温度センサーを設けることで、振動子の温度を高精度に推定できる可能性がある。本発明の一態様では、マルチチャネル入力に対応したハイブリッド型のA/D変換回路を構成できるので、複数の温度セ

ンサーからのマルチチャンネル入力に対して高精度な A / D 変換（高精度な温度検出）が可能となる。

**【 0 0 2 1 】**

また本発明の他の態様は、上記のいずれかに記載された回路装置と、前記回路装置に接続される振動子と、を含む振動デバイスに関する。

**【 0 0 2 2 】**

また本発明の他の態様では、振動デバイスは、第 1 ~ 第 m の温度センサー（m は 1 以上 n 以下の整数）を含み、前記セレクターには、前記第 1 ~ 第 m の温度センサーからの第 1 ~ 第 m の温度検出電圧が、前記第 1 ~ 第 n の電圧の第 1 ~ 第 m の電圧として入力されてもよい。

10

**【 0 0 2 3 】**

また本発明の更に他の態様では、上記のいずれかに記載された回路装置を含む電子機器に関する。

**【 0 0 2 4 】**

また本発明の更に他の態様では、上記のいずれかに記載された回路装置を含む移動体に関する。

**【 図面の簡単な説明 】**

**【 0 0 2 5 】**

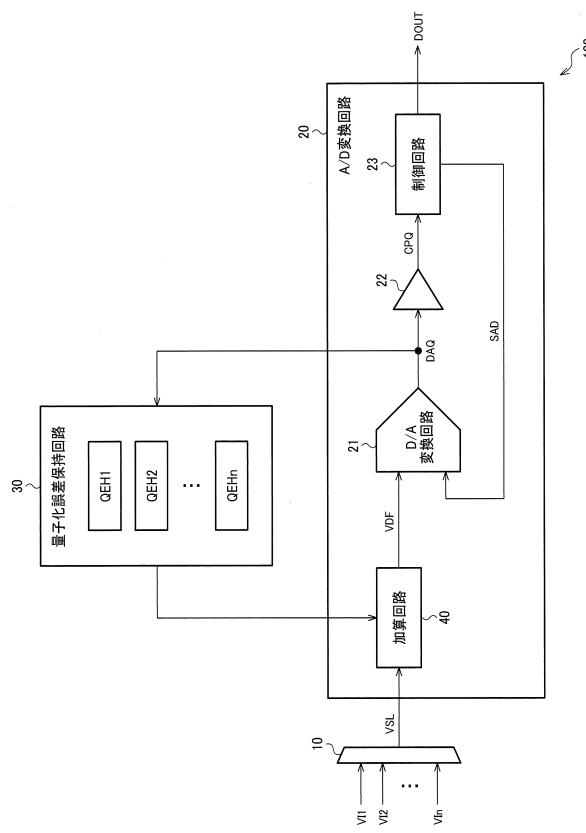

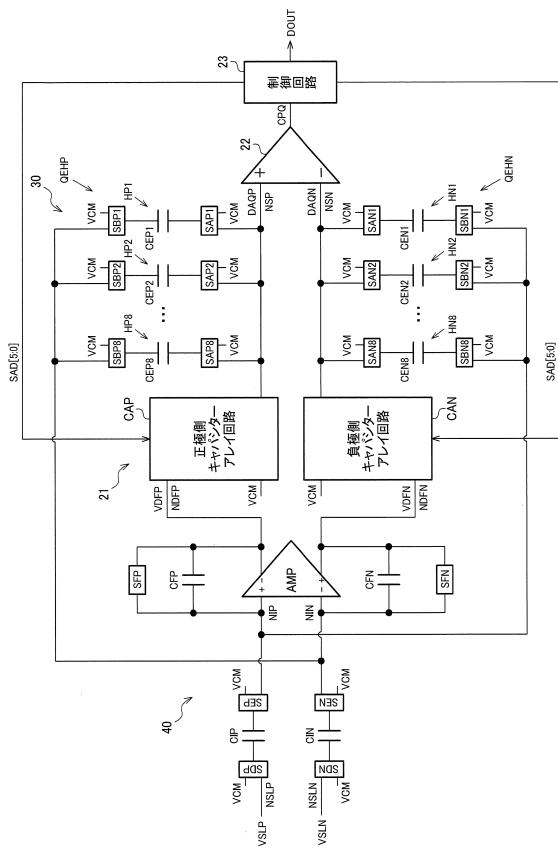

**【 図 1 】回路装置の構成例。**

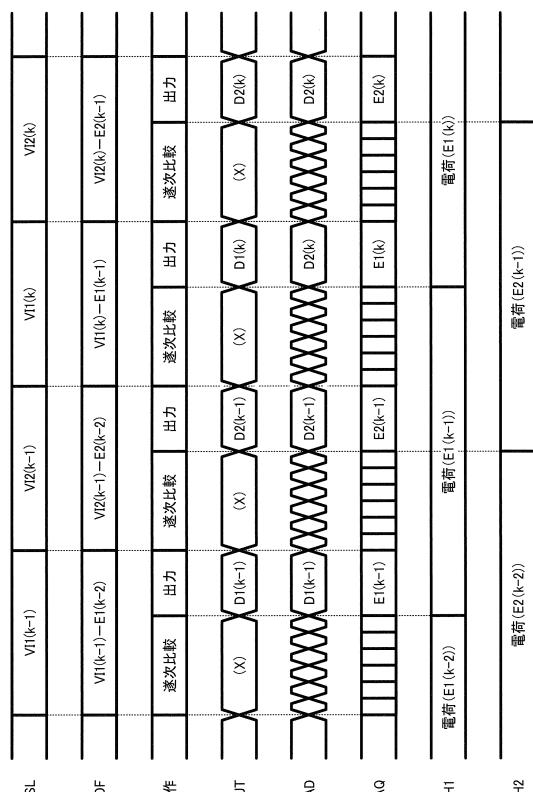

**【 図 2 】回路装置の基本的な動作を説明するタイミングチャート。**

20

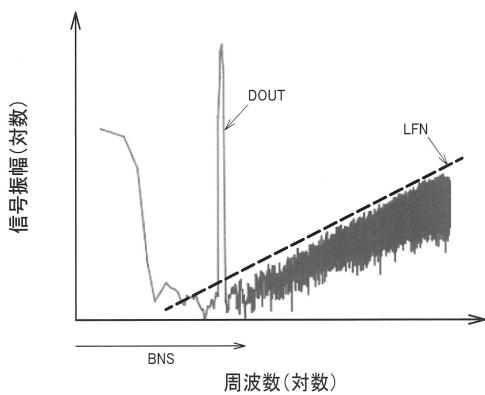

**【 図 3 】本実施形態における A / D 変換結果データの周波数特性の例。**

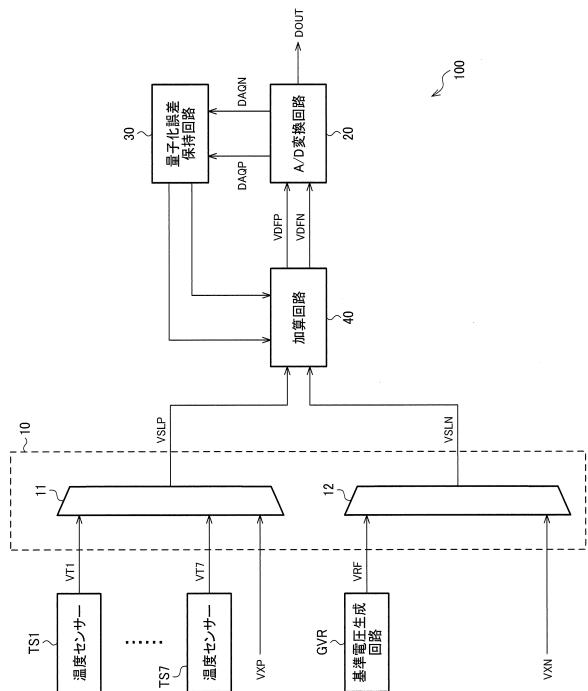

**【 図 4 】回路装置の第 1 の詳細な構成例。**

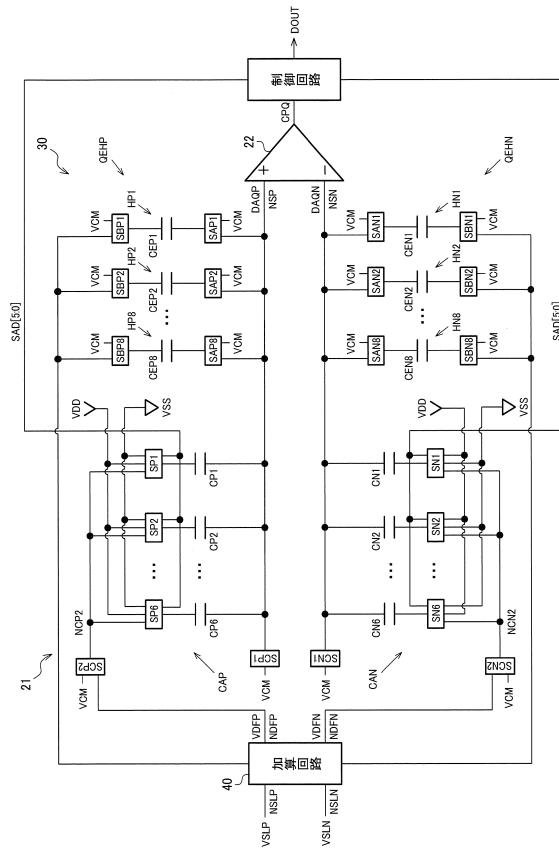

**【 図 5 】回路装置の第 2 の詳細な構成例。**

**【 図 6 】回路装置の第 2 の詳細な構成例。**

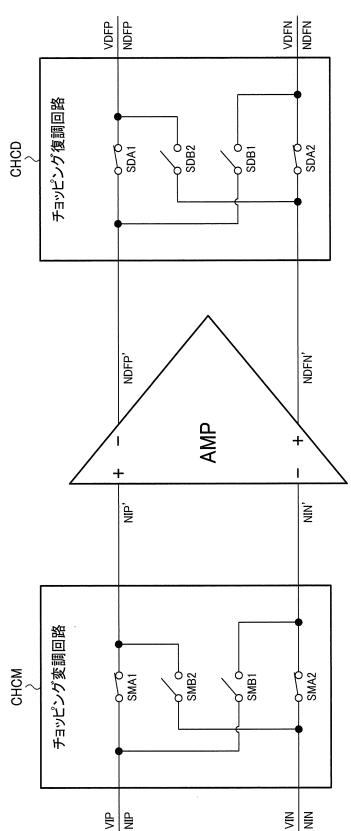

**【 図 7 】加算回路においてチョッピング変調を行う場合のチョッピング変調回路とチョッピング復調回路の構成例。**

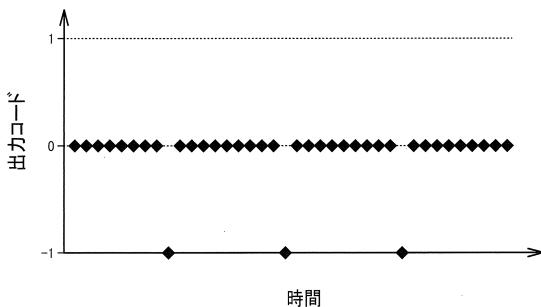

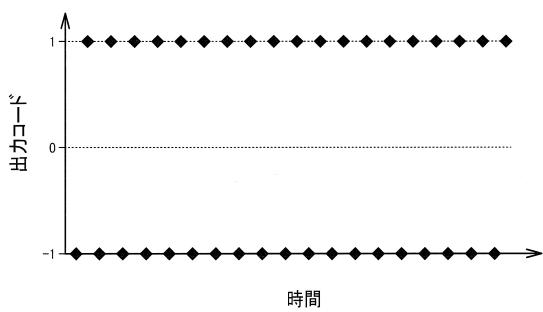

**【 図 8 】チョッピング変調を行わない場合に、0 V を入力したときの A / D 変換結果データ（出力コード）の時間変化の例。**

**【 図 9 】本実施形態において、0 V を入力したときの A / D 変換結果データ（出力コード）の時間変化の例。**

30

**【 図 1 0 】回路装置を含む振動デバイスの第 1 の構成例。**

**【 図 1 1 】回路装置を含む振動デバイスの第 2 の構成例。**

**【 図 1 2 】電子機器の構成例。**

**【 図 1 3 】移動体の例。**

**【 発明を実施するための形態 】**

**【 0 0 2 6 】**

以下、本発明の好適な実施の形態について詳細に説明する。なお以下に説明する本実施形態は特許請求の範囲に記載された本発明の内容を不当に限定するものではなく、本実施形態で説明される構成の全てが本発明の解決手段として必須であるとは限らない。

**【 0 0 2 7 】**

**1 . 回路装置の第 1 の構成例**

図 1 は、回路装置 1 0 0 の構成例である。回路装置 1 0 0 は、セレクター 1 0 と、A / D 変換回路 2 0 と、量子化誤差保持回路 3 0 と、を含む。また、回路装置 1 0 0 は、加算回路 4 0 を含むことができる。

40

**【 0 0 2 8 】**

セレクター 1 0 には、電圧 V I 1 ~ V I n （第 1 ~ 第 n の電圧（n は 2 以上の整数））が入力され、セレクター 1 0 は、電圧 V I 1 ~ V I n のいずれかを選択して出力電圧 V S L として出力する。具体的には、セレクター 1 0 は、電圧 V I 1 ~ V I n を順次に時分割に選択し、その時分割に選択した電圧を出力電圧 V S L として出力する。電圧 V I 1 ~ V I n は A / D 変換対象の電圧であり、例えばセンサーの出力電圧信号等である。

50

**【 0 0 2 9 】**

A / D 変換回路 2 0 には、セレクター 1 0 の出力電圧 V S L が入力電圧として入力される。A / D 変換回路 2 0 は、電荷再分配型の D / A 変換回路 2 1 を用いた逐次比較により入力電圧の A / D 変換を行い、入力電圧に対応する A / D 変換結果データ D O U T を出力する。D / A 変換回路 2 1 は、逐次比較データ S A D に基づくキャパシター間での電荷再分配により、逐次比較データ S A D の D / A 変換を行う。具体的には、D / A 変換回路 2 1 は、逐次比較データ S A D の D / A 変換電圧と逐次比較対象の電圧 ( V D F ) との差分を、D / A 変換結果 ( D A Q ) として出力する。

**【 0 0 3 0 】**

量子化誤差保持回路 3 0 は、電圧 V I 1 ~ V I n の A / D 変換における量子化誤差に対応する電荷を保持する量子化誤差保持回路 Q E H 1 ~ Q E H n で構成されている。具体的には、セレクター 1 0 が電圧 V I i ( 第 i の電圧 ( i は 1 以上 n 以下の整数 ) ) を選択したときの A / D 変換における量子化誤差に対応する電荷を、量子化誤差保持回路 Q E H i ( 第 i の量子化誤差保持回路 ) が保持する。量子化誤差は、逐次比較対象の電圧 ( V D F ) と、A / D 変換結果データ D O U T の D / A 変換電圧との差分であり、D / A 変換回路 2 1 に S A D = D O U T を入力したときの D / A 変換回路 2 1 の出力電圧 ( D A Q ) である。量子化誤差保持回路 Q E H i は、D / A 変換回路 2 1 の出力電圧をキャパシターで保持することで、量子化誤差に対応する電荷を保持する。

10

**【 0 0 3 1 】**

A / D 変換回路 2 0 は、電圧 V I i の k - 1 回目 ( k は整数 ) の A / D 変換における量子化誤差に対応する電荷として量子化誤差保持回路 Q E i に保持された電荷を用いて、電圧 V I i についての k 回目の A / D 変換を行う。そして A / D 変換回路 2 0 は、量子化誤差がノイズシェーピングされた、電圧 V I i に対応する A / D 変換結果データ D O U T を出力する。即ち、セレクター 1 0 が電圧 V I i を選択したときに、量子化誤差保持回路 Q E H i が、量子化誤差に対応する電荷を保持し、次にセレクター 1 0 が電圧 V I i を選択したときに、量子化誤差保持回路 Q E H i が保持する電荷を用いて入力電圧 ( V S L ) の A / D 変換を行う。A / D 変換回路 2 0 は、入力電圧 ( 又はそれにゲインを乗じた電圧 ) と、量子化誤差保持回路 Q E H i が保持する電荷に対応する電圧と、の差分電圧に対応した A / D 変換結果データ D O U T を求める。これにより、量子化誤差に対して 1 次のノイズシェーピング効果が生じる。

20

**【 0 0 3 2 】**

以上の実施形態によれば、A / D 変換における量子化誤差がノイズシェーピングされた、電圧 V I i に対応する A / D 変換結果データ D O U T を得ることができる。即ち、逐次比較型の A / D 変換回路にデルタシグマ型の構成を取り入れたハイブリッド型の A / D 変換回路を実現できる。

30

**【 0 0 3 3 】**

また、電圧 V I 1 ~ V I n の A / D 変換における量子化誤差に対応する電荷を保持する量子化誤差保持回路 Q E H 1 ~ Q E H n を設けることで、ハイブリッド型の A / D 変換回路においてマルチチャンネル入力を実現できる。具体的には、電荷再分配型の D / A 変換回路 2 1 は、逐次比較対象の電圧と逐次比較データ S A D の D / A 変換電圧とが等しくなるように逐次比較動作を行うので、その逐次比較動作が終了した後に、量子化誤差に対応した電圧を D / A 変換回路 2 1 に出力させることができる。この量子化誤差に対応した電圧により、量子化誤差に対応した電荷を保持できるようになる。この保持を、電圧 V I 1 ~ V I n の各々について行うことで、チャンネル毎に量子化誤差に対応した電荷を量子化誤差保持回路 Q E H 1 ~ Q E H n に保持することができる。

40

**【 0 0 3 4 】**

以下、A / D 変換回路 2 0 の詳細な構成について説明する。A / D 変換回路 2 0 は、加算回路 4 0 と、D / A 変換回路 2 1 と、比較回路 2 2 ( コンパレーター ) と、制御回路 2 3 ( ロジック回路 ) と、を含む。

**【 0 0 3 5 】**

50

加算回路 4 0 は、入力電圧 (V S L) に対応する電圧から、量子化誤差保持回路 Q E H i に保持される電荷に対応する電圧を減算した電圧 (V D F) を、D / A 変換回路 2 1 に出力する。例えば、入力電圧 (V S L) と、量子化誤差保持回路 Q E H i に保持される電荷に対応する電圧を逆符号にした（例えば - 1 倍した）電圧とを、加算する。量子化誤差保持回路 Q E H i に保持される電荷に対応する電圧は、電圧 V I i の前回の A / D 変換において逐次比較動作が終了した後の D / A 変換回路 2 1 の出力電圧 (D A Q) である。

#### 【 0 0 3 6 】

D / A 変換回路 2 1 は、加算回路 4 0 の出力電圧 V D F と逐次比較データ S A D の D / A 変換電圧との差分電圧 D A Q を出力する。具体的には、加算回路 4 0 の出力電圧 V D F をサンプルホールドし、電荷再分配により逐次比較データ S A D を D / A 変換する。これにより、逐次比較データ S A D の D / A 変換電圧から加算回路 4 0 の出力電圧 V D F が減算された差分電圧 D A Q が出力される。10

#### 【 0 0 3 7 】

量子化誤差保持回路 Q E H i は、電圧 V I i についての逐次比較動作を終了した後の差分電圧 D A Q に対応する電荷を保持する。例えば、コモン電圧（所与の電圧）を基準として差分電圧 D A Q をキャパシターで保持することで、コモン電圧と差分電圧 D A Q の電位差でキャパシターにチャージされる電荷を保持する。

#### 【 0 0 3 8 】

以上の構成では、逐次比較動作が終了した後に S A D = D O U T とすることで、D / A 変換回路 2 1 の出力電圧 (D A Q) が、量子化誤差による残差電圧となる。量子化誤差保持回路 Q E H i は、この残差電圧に対応した電荷を保持するだけで、量子化誤差に対応した電荷を保持できる。そして、この電荷を用いて、量子化誤差による残差電圧を入力側にフィードバックすることで、量子化誤差のノイズシェーピングが可能となっている。本実施形態の構成では、量子化誤差による残差電圧が過去の残差電圧の影響を受けたものとなるので、デルタシグマ動作における積分に相当する動作が実現されており、積分器を設ける必要がない。このため、マルチチャンネル入力に対応する際に量子化誤差保持回路をチャンネル数分だけ設けるだけでよい。チャンネル数分の積分器（アンプ）を設ける必要がないので、マルチチャンネル入力化による消費電力の増大や回路規模の増大を低減することが可能である。20

#### 【 0 0 3 9 】

比較回路 2 2 は、加算回路 4 0 の出力電圧 V D F と逐次比較データ S A D の D / A 変換電圧との間の比較判定を、D / A 変換回路 2 1 からの差分電圧 D A Q に基づいて行う。例えば差分電圧 D A Q がシングルエンド出力である場合、基準電圧（差分ゼロを示す電圧）に対する差分電圧 D A Q の大小を判定し、その判定結果を信号 C P Q として出力する。或は、差分電圧 D A Q が差動出力である場合、差分電圧 D A Q (差動電圧信号) の正負を判定し、その判定結果を信号 C P Q として出力する。30

#### 【 0 0 4 0 】

制御回路 2 3 は、比較回路 2 2 による比較結果 (C P Q) に基づいて逐次比較データ S A D を更新し、その更新された逐次比較データ S A D を D / A 変換回路 2 1 に出力する。具体的には、制御回路 2 3 は、逐次比較データ S A D を記憶するレジスターを有する。制御回路 2 3 は、レジスターに比較用の逐次比較データ S A D を設定し、その比較用の逐次比較データ S A D を D / A 変換回路 2 1 に出力し、そのときの比較回路 2 2 による比較結果に基づいて逐次比較データ S A D を決定する。これを 1 回の比較動作として、例えばバイナリーサーチ等の手法によりレジスターの逐次比較データ S A D を逐次に更新していく、この逐次比較動作が終了したときに A / D 変換結果データ D O U T が決定する。制御回路 2 3 は、A / D 変換結果データ D O U T をレジスターに設定して S A D = D O U T を D / A 変換回路 2 1 に出力する。40

#### 【 0 0 4 1 】

以上の構成によれば、電荷再分配型の D / A 変換回路 2 1 を用いた逐次比較による入力電圧の A / D 変換を実現できる。逐次比較の対象は加算回路 4 0 の出力電圧 V D F であり50

、この出力電圧  $VDF$  は量子化誤差保持回路  $QEHi$  により量子化誤差がフィードバックされた電圧となっている。これにより、デルタシグマ型の構成を取り入れたハイブリッド型の A / D 変換回路が実現されている。

#### 【0042】

図 2 は、図 1 の回路装置 100 の基本的な動作を説明するタイミングチャートである。以下、 $n = 2$  の場合を説明するが、 $n = 2$  に限定されない。なお、図 2 の動作に加えて、更に加算回路 40 のリセット動作やサンプリング動作、量子化誤差保持回路  $QEHi$ 、 $QEH2$  のリセット動作やサンプリング動作等を含んでもよい。

#### 【0043】

k - 1 回目の A / D 変換における第 1 の期間では、セレクター 10 が電圧  $VI_1$  を電圧  $VSL$  として選択し、加算回路 40 が、その電圧  $VSL = VI_1$  をサンプルホールドする。このホールドされた電圧を  $VI_1(k - 1)$  とする。量子化誤差保持回路  $QEHi$  は、k - 2 回目の A / D 変換において逐次比較動作が終了した後の D / A 変換回路 21 の出力電圧 ( $E_1(k - 2)$ ) に対応した電荷を保持している。加算回路 40 は、その電荷に基づいて、 $VDF = VI(k - 1) - E_1(k - 2)$  を出力する。なお、ここでは電圧  $VSL$  に対する加算回路 40 のゲインを 1 とするが、ゲインは 1 に限定されない。D / A 変換回路 21 及び比較回路 22、制御回路 23 が、逐次比較動作を行って加算回路 40 の出力電圧  $VDF$  を A / D 変換し、A / D 変換結果データ  $DOUT = D_1(k - 1)$  を出力する。なお、 $DOUT$  の (X) はドントケアを示す。制御回路 23 が  $SAD = D_1(k - 1)$  を出力し、D / A 変換回路 21 が量子化誤差に対応する電圧  $E_1(k - 1)$  を出力し、量子化誤差保持回路  $QEHi$  が、その電圧  $E_1(k - 1)$  に対応する電荷を保持する。

10

#### 【0044】

次に、k - 1 回目の A / D 変換における第 2 の期間では、セレクター 10 が電圧  $VI_2$  を電圧  $VSL$  として選択し、加算回路 40 が、その電圧  $VSL = VI_2$  をサンプルホールドする。このホールドされた電圧を  $VI_2(k - 1)$  とする。上記と同様の動作により、D / A 変換回路 21 が量子化誤差に対応する電圧  $E_2(k - 1)$  を出力し、量子化誤差保持回路  $QEHi$  が、その電圧  $E_2(k - 1)$  に対応する電荷を保持する。

20

#### 【0045】

次に、k 回目の A / D 変換における第 1 の期間では、セレクター 10 が電圧  $VI_1$  を電圧  $VSL$  として選択し、加算回路 40 が、その電圧  $VSL = VI_1$  をサンプルホールドする。このホールドされた電圧を  $VI_1(k)$  とする。上記と同様の動作により、D / A 変換回路 21 が量子化誤差に対応する電圧  $E_1(k)$  を出力し、量子化誤差保持回路  $QEHi$  が、その電圧  $E_1(k)$  に対応する電荷を保持する。

30

#### 【0046】

次に、k 回目の A / D 変換における第 2 の期間では、セレクター 10 が電圧  $VI_2$  を電圧  $VSL$  として選択し、加算回路 40 が、その電圧  $VSL = VI_2$  をサンプルホールドする。このホールドされた電圧を  $VI_2(k)$  とする。上記と同様の動作により、D / A 変換回路 21 が量子化誤差に対応する電圧  $E_2(k)$  を出力し、量子化誤差保持回路  $QEHi$  が、その電圧  $E_2(k)$  に対応する電荷を保持する。以下、 $k + 1$  回目以降の A / D 変換においても同様の動作を繰り返す。

40

#### 【0047】

以上の動作により実現される伝達関数を下式 (1) に示す。 $V(D_i)$  は、電圧  $VI_i$  の A / D 変換結果データ  $DOUT = Di$  を電圧で表したものであり、具体的には  $Di$  の D / A 変換電圧である。下式 (1) では、量子化誤差である電圧  $E_i$  に対して 1 次のハイパスフィルター ( $1 - z^{-1}$ ) の効果が発生している。即ち、A / D 変換結果データ  $DOUT = Di$  において、量子化誤差によるノイズに対して 1 次のノイズシェーピング効果が発生している。

#### 【数 1】

50

20

30

40

50

$$V(Di) = Vi + (1 - z^{-1}) \times Ei \quad (1)$$

### 【0048】

図3は、本実施形態におけるA/D変換結果データDOUTの周波数特性の例である。図3の例では、入力信号として所定周波数の信号を入力しており、それが周波数特性のピークとして示されている。入力信号は、この所定周波数の信号に限らず、信号帯域BNSの周波数成分を含んだ信号を想定できる。この信号帯域BNSがA/D変換の変換レートよりも低いとき、信号帯域BNSに対して高い変換レートでオーバーサンプリングした状態となる。例えば、変換レートは、信号帯域BNSの上限周波数の5倍以上、或いは10倍以上である。直線FLNで示すように、ノイズシェーピング効果によって低周波数帯域のフロアノイズ（量子化ノイズ）が低減されるので、ローパスフィルターで信号帯域BNSより高周波数のノイズを低減させることで、S/Nを向上できる。これにより、A/D変換結果データの高精度化（例えば有効ビット数の拡大）を実現できる。

10

### 【0049】

#### 2. 第1の詳細な構成例

図4は、回路装置100の第1の詳細な構成例である。図4の回路装置100は、セレクター10とA/D変換回路20と量子化誤差保持回路30と加算回路40とを含む。また回路装置100は、基準電圧生成回路GVRを含むことができる。なお以下ではn=8の場合を説明するが、n=8に限定されない。

20

### 【0050】

温度センサーTS1～TS7は、温度測定対象の温度を測定するためのセンサーである。温度センサーTS1～TS7として、例えばPN接合のバンドギャップ電圧の温度依存性を利用した温度センサーや、或いは抵抗の抵抗値の温度依存性を利用したサーミスター等を用いることができる。温度センサーTS1～TS7のうち一部が回路装置100に内蔵され、残りが回路装置100の外部（例えば回路装置100を含む発振デバイス等の内部）に設けられる。或いは、温度センサーTS1～TS7の全てが回路装置100に内蔵されてもよいし、温度センサーTS1～TS7の全てが回路装置100の外部に設けられてもよい。

30

### 【0051】

セレクター10は、セレクター11（正極側のセレクター、第1のセレクター）と、セレクター12（負極側のセレクター、第2のセレクター）と、を含む。

### 【0052】

セレクター11には、セレクター11には、温度センサーTS1～TS7からの温度検出電圧VT1～VT7（第1～第7の正極側電圧）が入力される。またセレクター11には、例えばテスト等に用いられる任意電圧VXP（第8の正極側電圧）が入力されてもよい。セレクター12には、基準電圧生成回路GVRからの基準電圧VRF（第1の負極側電圧）が入力される。またセレクター12には、例えばテスト等に用いられる任意電圧VXN（第2の負極側電圧）が入力されてもよい。例えば、基準電圧生成回路GVRはバンドギャップリファレンス回路であり、基準電圧VRFはバンドギャップリファレンス電圧（温度依存性がない電圧）である。

40

### 【0053】

セレクター11は、温度検出電圧VT1～VT7及び任意電圧VXPを順次に選択し、時分割の出力電圧VSLPとして出力する。セレクター12は、セレクター11が温度検出電圧VT1～VT7を出力しているとき、基準電圧VRFを選択し、出力電圧VSLNとして出力する。またセレクター11が任意電圧VXPを選択しているとき、任意電圧VXNを選択し、出力電圧VSLNとして出力する。

### 【0054】

50

本構成例において、(V T 1, V R F)で構成される差動電圧信号が図1の電圧V I 1に対応する。同様に、(V T 2, V R F)、(V T 3, V R F)、(V T 4, V R F)、(V T 5, V R F)、(V T 6, V R F)、(V T 7, V R F)、(V X P, V X N)で構成される差動電圧信号が図1の電圧V I 2、V I 3、V I 4、V I 5、V I 6、V I 7、V I 8に対応する。

#### 【0055】

加算回路40は、セレクター10からの差動電圧信号(V S L P, V S L N)を差動増幅し、量子化誤差保持回路30からの正極側の電荷と負極側の電荷を電荷電圧変換(差動のQ V変換)し、それらの差動電圧信号を加算した差動電圧信号(V D F P, V D F N)を出力する。

10

#### 【0056】

A / D変換回路20は、差動入力のA / D変換回路20である。即ち、加算回路40の出力電圧V D F P、V D F Nで構成される差動電圧信号をA / D変換し、出力電圧V D F P、V D F Nの差分に対応するA / D変換結果データD O U Tを出力する。

#### 【0057】

量子化誤差保持回路30は、A / D変換回路20の逐次比較動作が終了した後のD / A変換回路21の出力信号である差動電圧信号(D A Q P, D A Q N)を保持する。具体的には、差動電圧信号を構成する電圧D A Q Pに対応する電荷と、電圧D A Q Nに対応する電荷とを保持する。

20

#### 【0058】

本実施形態によれば、セレクター10には、温度センサーT S 1 ~ T S 7からの温度検出電圧V T 1 ~ V T 7が、電圧V I 1 ~ V I 8の電圧V I 1 ~ V I 7として入力される。なお、温度センサーの個数は7に限定されない。即ち、セレクター10には、第1 ~ 第mの温度センサー(mは1以上n以下の整数)からの第1 ~ 第mの温度検出電圧が、第1 ~ 第nの電圧の第1 ~ 第mの電圧として入力されればよい。

#### 【0059】

温度の変化は緩やかなので、温度センサーT S 1 ~ T S 7が出力する温度検出電圧V T 1 ~ V T 7の信号帯域は低周波数の帯域(例えば100 Hz以下)になる。このため、逐次比較型のような比較的低速なA / D変換回路であっても、信号帯域より十分に高い変換レートでA / D変換できる。本実施形態では、ハイブリッド型のA / D変換回路を構成することで、上述したようなノイズシェーピング効果を伴うオーバーサンプリング状態を実現でき、温度センサーの信号帯域においてS / Nの高い測定が可能となる。

30

#### 【0060】

温度検出データ(温度検出電圧のA / D変換結果データ)を用いた処理として、例えばT C X O(Temperature Compensated Crystal Oscillator)やO C X O(Oven Controlled Crystal Oscillator)等のデジタル方式の発振器における温度補償処理が考えられる。T C X OやO C X Oは、例えば携帯通信端末、G P S関連機器、ウェアラブル機器、又は車載機器などにおける基準信号源等として用いられている。このようなT C X O等の発振器では、高い周波数安定度が望まれているが、高い周波数安定度を実現するためには高精度な温度検出が必要となる。発振器の内部(或いは内部及び外部)の複数の位置に設けた複数の温度センサーを用いることで、振動子(例えば水晶振動子等)の温度を高精度に推定できる可能性がある。振動子の温度を高精度の推定できることで、温度補償の精度が向上し、発振周波数の安定度を向上できる。従来のハイブリッド型のA / D変換回路をT C X OやO C X Oにおける温度検出データを用いた処理に採用した場合は、複数の温度センサーからのマルチチャンネル入力に対応できなかったのに対し、本実施形態では、マルチチャンネル入力に対応したハイブリッド型のA / D変換回路を構成できるので、複数の温度センサーからのマルチチャンネル入力に対して高精度なA / D変換が可能となる。

40

#### 【0061】

##### 3 . 第2の詳細な構成例

図5、図6は、回路装置100の第2の詳細な構成例である。なお、第2の詳細な構成

50

例を図 5 と図 6 に分けて図示しており、同一の構成要素には同一の符号を付している。以下では  $n = 8$  の場合を説明するが、 $n = 8$  に限定されない。

#### 【 0 0 6 2 】

図 5 に示すように、加算回路 4 0 はキャパシター C I P (正極側の入力キャパシター) と、キャパシター C I N (負極側の入力キャパシター) と、キャパシター C F P (正極側の帰還用キャパシター) と、キャパシター C F N (負極側の帰還用キャパシター) と、スイッチ S D P、S D N、S E P、S E N、S F P、S F N と、全差動型の演算増幅器 A M P と、を含む。全差動型の演算増幅器とは、差動入力且つ差動出力の演算増幅器のことである。

#### 【 0 0 6 3 】

スイッチ S D P は、キャパシター C I P の一端を、セレクター 1 1 の出力ノード N S L P (セレクター 1 0 の第 1 の出力ノード) 及びコモン電圧 V C M のノードの一方に接続する。スイッチ S D N は、キャパシター C I N の一端を、セレクター 1 2 の出力ノード N S L N (セレクター 1 0 の第 2 の出力ノード) 及びコモン電圧 V C M のノードの一方に接続する。スイッチ S E P は、キャパシター C I P の他端を、演算増幅器 A M P の非反転入力ノード N I P 及びコモン電圧 V C M のノードの一方に接続する。スイッチ S E N は、キャパシター C I N の他端を、演算増幅器 A M P の反転入力ノード N I N 及びコモン電圧 V C M のノードの一方に接続する。キャパシター C F P の一端及びスイッチ S F P の一端は、演算増幅器 A M P の非反転入力ノード N I P に接続され、キャパシター C F P の他端及びスイッチ S F P の他端は、演算増幅器 A M P の反転出力ノード N D F P に接続される。キャパシター C F N の一端及びスイッチ S F N の一端は、演算増幅器 A M P の反転入力ノード N I N に接続され、キャパシター C F N の他端及びスイッチ S F N の他端は、演算増幅器 A M P の非反転出力ノード N D F N に接続される。スイッチ S D P、S D N、S E P、S E N、S F P、S F N は、例えばトランジスターで構成されるアナログスイッチである。

#### 【 0 0 6 4 】

図 5、図 6 に示すように、D / A 変換回路 2 1 は差動型の D / A 変換回路である。D / A 変換回路 2 1 は、キャパシターアレイ回路 C A P (正極側のキャパシターアレイ回路) と、キャパシターアレイ回路 C A N (負極側のキャパシターアレイ回路) と、を含む。

#### 【 0 0 6 5 】

図 6 に示すように、キャパシターアレイ回路 C A P は、キャパシター C P 1 ~ C P 6 と、スイッチ S P 1 ~ S P 6、S C P 1、S C P 2 と、を含む。スイッチ S C P 1 の一端はキャパシターアレイ回路 C A P のサンプリングノード N S P に接続され、他端はコモン電圧 V C M のノードに接続される。キャパシター C P j (j は 1 以上 6 以下の整数) の一端はサンプリングノード N S P に接続される。スイッチ S P j は、キャパシター C P j の他端を、ノード N C P 2 及び電圧 V D D (電源電圧、第 1 の電圧) のノード、電圧 V S S (接地電圧、第 2 の電圧) のノードのいずれかに接続する。スイッチ S C P 2 は、ノード N C P 2 を、演算増幅器 A M P の反転出力ノード N D F P 及びコモン電圧 V C M のノードの一方接続する。キャパシター C P j の容量値は  $C P 1 \times 2^{j-1}$  である。スイッチ S P 1 ~ S P 6、S C P 1、S C P 2 は、例えばトランジスターで構成されるアナログスイッチである。

#### 【 0 0 6 6 】

キャパシターアレイ回路 C A N は、キャパシター C N 1 ~ C N 6 と、スイッチ S N 1 ~ S N 6、S C N 1、S C N 2 と、を含む。スイッチ S C N 1 の一端はキャパシターアレイ回路 C A N のサンプリングノード N S N に接続され、他端はコモン電圧 V C M のノードに接続される。キャパシター C N j の一端はサンプリングノード N S N に接続される。スイッチ S N j は、キャパシター C N j の他端を、ノード N C N 2 及び電圧 V D D のノード、電圧 V S S のノードのいずれかに接続する。スイッチ S C N 2 は、ノード N C N 2 を、演算増幅器 A M P の非反転出力ノード N D F N 及びコモン電圧 V C M のノードの一方接続する。キャパシター C N j の容量値は  $C N 1 \times 2^{j-1}$  である。スイッチ S N 1 ~ S N 6、S C N 1、S C N 2 は、例えばトランジスターで構成されるアナログスイッチである。

10

20

30

40

50

**【 0 0 6 7 】**

なお、キャパシターアレイ回路 C A P 、 C A N が含むキャパシターの個数は 6 に限定されず、キャパシターアレイ回路 C A P が、第 1 ~ 第 k の正極側キャパシター ( k は 2 以上の整数 ) を含み、キャパシターアレイ回路 C A N が、第 1 ~ 第 k の負極側キャパシターを含んでいればよい。このとき、 j は 1 以上 k 以下の整数である。また、逐次比較データは k ビットのデータ S A D [ k - 1 : 0 ] である。

**【 0 0 6 8 】**

図 5 、図 6 に示すように、量子化誤差保持回路 3 0 は、量子化誤差保持回路 Q E H P ( 正極側の量子化誤差保持回路 ) と、量子化誤差保持回路 Q E H N ( 負極側の量子化誤差保持回路 ) と、を含む。

10

**【 0 0 6 9 】**

図 5 に示すように、量子化誤差保持回路 Q E H P は、保持回路 H P 1 ~ H P 8 ( 第 1 ~ 第 n の正極側の保持回路 ) を含む。保持回路 H P i ( 第 i の正極側の保持回路 ) は、キャパシター C E P i ( 正極側の保持用キャパシター ) と、スイッチ S A P i ( 第 1 の正極側スイッチ ) と、スイッチ S B P i ( 第 2 の正極側スイッチ ) と、を含む。スイッチ S A P i は、キャパシター C E P i の一端を、サンプリングノード N S P 及びコモン電圧 V C M のノードの一方に接続する、又はフローティング状態に設定する。スイッチ S B P i は、キャパシター C E P i の他端を、演算増幅器 A M P の反転入力ノード N I N 及びコモン電圧 V C M のノードの一方に接続する。キャパシター C E P 1 ~ C E P 8 の容量値は同一である。スイッチ S A P 1 ~ S A P 8 、 S B P 1 ~ S B P 8 は、例えばトランジスターで構成されるアナログスイッチである。

20

**【 0 0 7 0 】**

量子化誤差保持回路 Q E H N は、保持回路 H N 1 ~ H N 8 ( 第 1 ~ 第 n の負極側の保持回路 ) を含む。保持回路 H N i ( 第 i の負極側の保持回路 ) は、キャパシター C E N i ( 負極側の保持用キャパシター ) と、スイッチ S A N i ( 第 1 の負極側スイッチ ) と、スイッチ S B N i ( 第 2 の負極側スイッチ ) と、を含む。スイッチ S A N i は、キャパシター C E N i の一端を、サンプリングノード N S N 及びコモン電圧 V C M のノードの一方に接続する、又はフローティング状態に設定する。スイッチ S B N i は、キャパシター C E N i の他端を、演算増幅器 A M P の非反転入力ノード N I P 及びコモン電圧 V C M のノードの一方に接続する。キャパシター C E N 1 ~ C E N 8 の容量値は同一である。スイッチ S A N 1 ~ S A N 8 、 S B N 1 ~ S B N 8 は、例えばトランジスターで構成されるアナログスイッチである。

30

**【 0 0 7 1 】**

なお、図 5 、図 6 の保持回路 H P i 及び保持回路 H N i が、図 1 の量子化誤差保持回路 Q E H i に対応する。

**【 0 0 7 2 】**

比較回路 2 2 は、差動入力シングルエンド出力のコンパレーターである。比較回路 2 2 の非反転入力ノードはサンプリングノード N S P に接続され、反転入力ノードはサンプリングノード N S N に接続される。サンプリングノード N S P 、 N S N の電圧には、 D / A 変換電圧である電圧 D A Q P 、 D A Q N が出力される。 D A Q P - D A Q N > 0 V のとき比較回路 2 2 はハイレベルの信号 C P Q を出力し、 D A Q P - D A Q N < 0 V のとき比較回路 2 2 はローレベルの信号 C P Q を出力する。制御回路 2 3 は、信号 C P Q に基づいて逐次比較データ S A D [ 5 : 0 ] を更新し、その逐次比較データ S A D [ 5 : 0 ] をスイッチ S P 1 ~ S P 6 、 S N 1 ~ S N 6 に出力する。また制御回路 2 3 は、加算回路 4 0 、 D / A 変換回路 2 1 、量子化誤差保持回路 3 0 に含まれるスイッチの制御を行う。

40

**【 0 0 7 3 】**

以下、図 5 、図 6 の回路装置 1 0 0 の動作を説明する。なお以下では、セレクター 1 0 が電圧 V I i を選択しているときの k 回目の A / D 変換における動作を説明する。各期間において言及しないスイッチの状態は、その前の期間における状態と同じである。

**【 0 0 7 4 】**

50

リセット期間（初期化期間）では、加算回路40のスイッチSFP、SFNがオンである。これにより、キャパシターCFP、CFNの両端が接続され、キャパシターCFP、CFNの電荷がリセット（初期化）される。また、キャパシターアレイ回路CAP、CANのスイッチSCP1、SCN1がオンになり、スイッチSCP2、SCN2がコモン電圧VCMのノードを選択し、スイッチSP1～SP6、SN1～SN6がノードNCP2、NCN2を選択する。これにより、キャパシターCP1～CP6、CN1～CN6の両端がコモン電圧VCMとなり、キャパシターCP1～CP6、CN1～CN6の電荷がリセットされる。また、量子化誤差保持回路QEHP、QEHNのスイッチSAP1～SAP8、SAN1～SAN8がフローティング状態を選択し、スイッチSBP1～SBP8、SBN1～SBN8がコモン電圧VCMのノードを選択する。これにより、キャパシタ-CEPi、CENiが、電圧VIPiについてのk-1回目のA/D変換における量子化誤差に対応する電荷を保持している。即ち、k-1回目のA/D変換の逐次比較動作が終了した後にDAQP=EPi、DAQN=ENiであったとすると、キャパシタ-CEPi、CENiは、量子化誤差に対応する電圧EPi、ENiを、コモン電圧VCMを基準として保持する。但し、下式(2)で説明するように、電圧EPi、ENiが減衰した電圧が保持される。

#### 【0075】

リセット期間の後の第1の加算動作期間では、加算回路40のスイッチSFP、SFNがオフであり、量子化誤差保持回路QEHP、QEHNのスイッチSBPi、SBNiが、演算増幅器AMPの入力ノードNIN、NIPを選択し、スイッチSAPI、SANiがコモン電圧VCMのノードを選択する。これにより、キャパシタ-CEPiが保持する電荷がキャパシタ-CEPi、CFNで再分配され、キャパシタ-CENiが保持する電荷がキャパシタ-CENi、CFPで再分配される。即ち、k-1回目のA/D変換における量子化誤差に対応する電圧EPi、ENi（の減衰電圧）で構成される差動電圧信号が、負のゲインで差動増幅される。また、第1の加算動作期間では、加算回路40のスイッチSDP、SDNがセレクター10の出力ノードNSLP、NSLNを選択し、スイッチSEP、SENがコモン電圧VCMのノードを選択する。これにより、キャパシタ-CIP、CINがコモン電圧VCMを基準とする入力電圧(VSLP、VSLN)をサンプリングする。

#### 【0076】

第1の加算動作期間の後の第2の加算動作期間では、スイッチSDP、SDNがコモン電圧VCMのノードを選択し、スイッチSEP、SENが演算増幅器AMPの入力ノードNIP、NINを選択する。これにより、入力電圧(VSLP、VSLN)で構成される差動電圧信号が正のゲインで差動増幅される。以上の動作により、入力電圧(VSLP、VSLN)で構成される差動電圧信号が正のゲインで差動増幅された差動電圧信号と、電圧EPi、ENi（の減衰電圧）で構成される差動電圧信号が負のゲインで差動増幅された差動電圧信号とが加算される。その加算結果は、出力電圧VDFP、VDFNで構成される差動電圧信号として出力される。第2の加算動作期間が終了すると、加算回路40のスイッチSDP、SDNがセレクター10の出力ノードNSLP、NSLNを選択し、スイッチSEP、SENがコモン電圧VCMのノードを選択する。即ち、キャパシタ-CIP、CINがコモン電圧VCMを基準とする入力電圧(VSLP、VSLN)を再びサンプリングする。

#### 【0077】

第2の加算動作期間の後のサンプリング期間では、キャパシターアレイ回路CAP、CANのスイッチSCP1、SCN1がオンであり、スイッチSCP2、SCN2が加算回路40の出力ノードNDFP、NDFNを選択する。これにより、キャパシタ-CP1～CP6、CN1～CN6はコモン電圧VCMを基準として加算回路40の出力電圧VDFP、VDFNをサンプリングする。

#### 【0078】

サンプリング期間の後の逐次比較動作期間では、キャパシターアレイ回路CAP、CA

10

20

30

40

50

NのスイッチSCP1、SCN1がオフであり、スイッチSP1～SP6、SN1～SN6が逐次比較データSAD[5:0]に基づいて電圧VDD又は電圧VSSを選択する。具体的には、SAD[j]=1のときスイッチSPjが電圧VDDを選択し、スイッチSNjが電圧VSSを選択する。SAD[j]=0のときスイッチSPjが電圧VSSを選択し、スイッチSNjが電圧VDDを選択する。これにより、DAQP-DAQN=V(SAD[5:0])- (VDFP-VDFN)となる電圧DAQP、DAQNがサンプリングノードNSP、NSNに出力される。比較回路22は、DAQP-DAQNの正負を判定し、その結果を信号CPQとして出力する。制御回路23は、信号CPQに基づいて逐次比較データSAD[5:0]を更新する。以上の動作を、A/D変換結果データが決定されるまで逐次に繰り返す。

10

## 【0079】

逐次比較動作期間の次の量子化誤差保持期間では、制御回路23が、A/D変換結果データを逐次比較データSAD[5:0]として出力する。これにより、電圧VIiについてのk回目のA/D変換における量子化誤差に対応する電圧EPi、ENiがサンプリングノードNSP、NSNに出力される。量子化誤差保持回路QEHP、QEHNのスイッチSAPi、SANiは、サンプリングノードNSP、NSNを選択し、スイッチSBPi、SBNiは、コモン電圧VCMのノードを選択する。これにより、キャパシターCEPi、CENiは、電圧VIiについてのk回目のA/D変換における量子化誤差に対応する電荷を保持する。即ち、キャパシターCEPi、CENiがコモン電圧VCMを基準として電圧EPi、ENiを保持する。但し、下式(2)で説明するように、電圧EPi、ENiが減衰した電圧が保持される。

20

## 【0080】

量子化誤差保持期間の後は、電圧VIi+1についてのk回目のA/D変換を行う。電圧VINについてのk回目のA/D変換が終了した後、電圧VI1についてのk+1回目のA/D変換を行う。

## 【0081】

以上の動作において、加算回路40の出力電圧は下式(2)となる。kは、k回目のA/D変換動作での電圧であることを表す。VDF(k)は、第2の加算動作期間後のVDFP-VDFNである。CIは、キャパシターCIPの容量値であり、キャパシターキャニンの容量値もCIである。CFは、キャパシターキャンの容量値であり、キャパシターキャンの容量値もCFである。VSL(k)は、第1の加算動作期間後のVSLP-VSLNである。CEは、キャパシターCEPiの容量値であり、キャパシターキャンの容量値もCEである。Ctotalは、キャパシターCP1～CP6の容量値の合計である。E(k-1)は、k-1回目のA/D変換におけるEPi-ENiである。

30

## 【数2】

$$VDF(k) = \frac{CI}{CF} \times VSL(k) - \frac{CE}{CF} \times \frac{C_{total}}{C_{total} + CE} \times E(k-1) \quad (2)$$

40

## 【0082】

上式(2)において、E(k-1)のゲインが-1となるように、容量値CE、CF、Ctotalを設定する。E(k-1)は、キャパシターCP1～CP6(Ctotal)とキャパシターCEPi(CE)との間の電荷再分配、及びキャパシターキャン1～キャン6(Ctotal)とキャパシターキャン(CE)との間の電荷再分配により、ゲインCtotal/(Ctotal+CE)で減衰する。加算回路40が加算動作を行うとき、ゲインCE/CFが乗算されるので、減衰されたE(k-1)を増幅できる。これにより、E(k-1)のゲインを-1にすることが可能となり、上式(1)のようなノイズシェーピング特性を有する伝達関数を実現できる。

## 【0083】

50

以上の本実施形態によれば、スイッチSAPiがキャパシターCEPiの一端をサンプリングノードNSPに接続し、スイッチSBPiがキャパシターCEPiの他端をコモン電圧VCMのノードに接続することで、キャパシターCEPiが量子化誤差に対応する電荷を保持できる。同様に、スイッチSANiがキャパシターCENiの一端をサンプリングノードNSNに接続し、スイッチSBNiがキャパシターCENiの他端をコモン電圧VCMのノードに接続することで、キャパシターCENiが量子化誤差に対応する電荷を保持できる。そして、スイッチSAPiがキャパシターCEPiの一端をコモン電圧VCMのノードに接続し、スイッチSBPiがキャパシターCEPiの他端を演算増幅器AMPの反転入力ノードNINに接続することで、キャパシターCEPiが保持する電荷が、キャパシターCEPi、CFNの間で再分配される。スイッチSANiがキャパシターCENiの一端をコモン電圧VCMのノードに接続し、スイッチSBNiがキャパシターCENiの他端を演算増幅器AMPの非反転入力ノードNIPに接続することで、キャパシターCENiが保持する電荷が、キャパシターCENi、CFPの間で再分配される。これにより、量子化誤差に対応する電圧を、A/D変換回路20の入力電圧(VSLP、VS LN)から減算できる。

#### 【0084】

##### 4. チョッピング変調

図7は、加算回路40においてチョッピング変調を行う場合のチョッピング変調回路とチョッピング復調回路の構成例である。図7では、加算回路40がチョッピング変調回路CHCMと、チョッピング復調回路CHCDと、を含む。図7の構成を図5に適用する場合、図7のノードNIP、NIN、NDFP、NDFNが、図5のノードNIP、NIN、NDFP、NDFNに対応する。

#### 【0085】

チョッピング変調回路CHCMは、演算増幅器AMPの非反転入力ノードNIP'及び反転入力ノードNIN'に入力される電圧に対してチョッピングの変調を行う。即ち、チョッピング変調回路CHCMは、ノードNIP、NINの電圧VIP、VINをチョッピング変調し、その変調後の電圧をノードNIP'、NIN'に出力する。

#### 【0086】

チョッピング変調回路CHCMは、スイッチSMA1、SMA2、SMB1、SMB2を含む。スイッチSMA1、SMB1の一端はノードNIPに接続され、スイッチSMA2、SMB2の一端はノードNINに接続される。スイッチSMA1、SMB2の他端はノードNIP'に接続され、スイッチSMA2、SMB1の他端はノードNIN'に接続される。スイッチSMA1、SMA2、SMB1、SMB2は、例えばトランジスターで構成されるアナログスイッチである。非反転動作では、スイッチSMA1、SMA2がオンであり、スイッチSMB1、SMB2がオフであり、ノードNIP'、NIN'に電圧VIP、VINが入力される。反転動作では、スイッチSMA1、SMA2がオフであり、スイッチSMB1、SMB2がオンであり、ノードNIP'、NIN'に電圧VIN、VIPが入力される。

#### 【0087】

チョッピング復調回路CHCDは、演算増幅器AMPの反転出力ノードNDFP'及び非反転出力ノードNDFN'から出力される電圧に対してチョッピングの復調を行う。即ち、チョッピング復調回路CHCDは、ノードNDFP'、NDFN'の電圧をチョッピング復調し、その復調後の電圧VDFP、VDFNをノードNDFP、NDFNに出力する。

#### 【0088】

チョッピング復調回路CHCDは、スイッチSDA1、SDA2、SDB1、SDB2を含む。スイッチSDA1、SDB1の一端はノードNDFP'に接続され、スイッチSDA2、SDB2の一端はノードNDFN'に接続される。スイッチSDA1、SDB2の他端はノードNDFDに接続され、スイッチSDA2、SDB1の他端はノードNDFNに接続される。非反転動作では、スイッチSDA1、SDA2がオンであり、スイッチSDB1、SDB2がオフであり、ノードNDFP'、NDFN'の電圧がノードNDFP、N

DFNに電圧VDFP、VDFNとして出力される。スイッチSDA1、SDA2、SDB1、SDB2は、例えばトランジスターで構成されるアナログスイッチである。反転動作では、スイッチSDA1、SDA2がオフであり、スイッチSDB1、SDB2がオンであり、ノードNDFN'、NDFP'の電圧がノードNDFP、NDFNに電圧VDFP、VDFNとして出力される。

#### 【0089】

演算増幅器AMPは、オフセットを有する。例えば、演算増幅器AMPの差動対を構成する2つのトランジスターのサイズを異ならせることで、ノードNIP'、NIN'間にオフセットを発生させる。

#### 【0090】

チョッピング変調回路CHCM及びチョッピング復調回路CHCDは、反転動作と非反転動作とを交互に繰り返す。具体的には、k-1回目のA/D変換では反転動作及び非反転動作の一方を行い、k回目のA/D変換では反転動作及び非反転動作の他方を行う。これにより、チョッピングの周波数で演算増幅器AMPのオフセットが変調される。具体的には、k-1回目のA/D変換とk回目のA/D変換とで、オフセットの極性が反転される。

#### 【0091】

図8は、チョッピング変調を行わない場合に、0Vを入力したときのA/D変換結果データ（出力コード）の時間変化の例である。本実施形態では、1次のノイズシェーピング機構を有するため、A/D変換回路20にDC信号が入力されたときにA/D変換結果データDOUTが特定の時間変化パターンになり、A/D変換結果データDOUTに不要周波数成分が発生する可能性がある。この現象をアイドルトーンと呼ぶ。例えばTCXOの温度補償処理に、温度検出電圧のA/D変換結果データを用いたとする。このとき、一定周期でA/D変換結果データが変化すると、その周期で発振周波数が補正されることになり、発振特性を低下させるおそれがある。

#### 【0092】

図9は、本実施形態において、0Vを入力したときのA/D変換結果データ（出力コード）の時間変化の例である。本実施形態では、チョッピングの変調を行っているので、A/D変換毎にオフセットの極性が反転する。このため、オフセットによるA/D変換結果データの変化が、チョッピングの周波数の分だけ高周波数になり、上記のようなアイドルトーンを低減できる。例えば、TCXOの温度補償処理において、アイドルトーンにより発振特性が低下する可能性を低減できる。

#### 【0093】

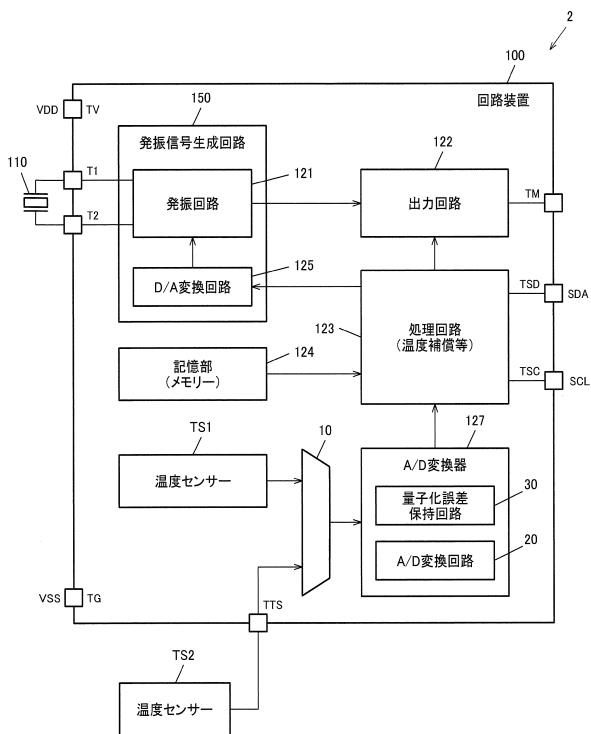

##### 5. 振動デバイス

以下、回路装置100を含む振動デバイス2の構成例について説明する。図10は、回路装置100を含む振動デバイス2の第1の構成例である。図10では、振動デバイス2が発振器である場合を例にとり説明する。具体的には、温度補償型の発振器であるTCXOへの適用例について説明する。なお温度補償型の発振器はOCXOであってもよい。

#### 【0094】

振動デバイス2（発振器）は、振動子110と回路装置100とを含む。また振動デバイス2は、温度センサーTS2を含むことができる。例えば、振動子110及び回路装置100、温度センサーTS2がパッケージに収納されることで、振動デバイス2が構成される。

#### 【0095】

振動子110の一端は端子T1に接続され、他端は端子T2に接続される。振動子110(resonator)は、電気的な信号により機械的な振動を発生する素子(振動素子)である。振動子110は、例えば水晶振動片などの振動片(圧電振動片)により実現できる。例えばカット角がATカットやSCカットなどの厚みすべり振動する水晶振動片などにより実現できる。例えば振動子110は、恒温槽を備えない温度補償型発振器(TCXO)に内蔵されている振動子である。或いは振動子110は、恒温槽を備える恒温槽型発振器

10

20

30

40

50

(O C X O) に内蔵されている振動子などであってもよい。なお本実施形態の振動子 110 は、例えば厚みすべり振動型以外の振動片や、水晶以外の材料で形成された圧電振動片などの種々の振動片により実現できる。例えば振動子 110 として、SAW (Surface Acoustic Wave) 共振子や、シリコン基板を用いて形成されたシリコン製振動子としてのMEMS (Micro Electro Mechanical Systems) 振動子等を採用してもよい。

#### 【0096】

回路装置 100 は、処理回路 123 と発振信号生成回路 150 とセレクター 10 と A/D 変換器 127 を含む。また回路装置 100 は、記憶部 124 (メモリー) と、温度センサー TS1 と出力回路 122 と、端子 T1、T2 と、出力端子 TM と、センサー入力端子 TTS と、信号端子 TSD、TSC と、電源供給用の電源端子 TV、TG と、を含むことができる。回路装置 100 は集積回路装置 (IC、半導体チップ) である。端子 T1、T2 や出力端子 TM、センサー入力端子 TTS、信号端子 TSD、TSC、電源端子 TV、TG は、例えば集積回路装置のパッドと呼ばれるものである。

10

#### 【0097】

発振信号生成回路 150 は、周波数制御データに対応する発振周波数の発振信号を、振動子 110 を用いて生成する。発振信号生成回路 150 は、振動子 110 を発振させる発振回路 121 を含む。また発振信号生成回路 150 は、後述する D/A 変換回路 125 を更に含んでもよい。

#### 【0098】

発振回路 121 は、駆動回路を有し、端子 T1、T2 を介して駆動回路により振動子 110 を駆動して振動子 110 を発振させる回路である。発振回路 121 としては例えばピアース型の発振回路を採用できる。この場合、駆動回路はバイポーラトランジスターと、バイポーラトランジスターのベース - コレクター間に接続される抵抗と、を含む。バイポーラトランジスターのベースが駆動回路の入力ノードとなり、コレクターが駆動回路の出力ノードとなる。駆動回路の出力ノード、入力ノードの少なくとも一方の接続ノードに対して可変容量回路が設けられる。可変容量回路は、例えば制御電圧に基づき容量値が変化するバラクターや、周波数制御データに基づいて、接続ノードに接続されるキャパシターの数が切り替わるキャパシターアレイなどにより実現できる。

20

#### 【0099】

出力回路 122 は、発振回路 121 からの出力信号であるクロック信号をバッファリングして、そのバッファリングされたクロック信号を出力端子 TM から回路装置 100 の外部に出力する。例えば出力回路 122 は、発振回路 121 からの出力信号であるクロック信号をバッファリングするバッファー回路で構成される。

30

#### 【0100】

温度センサー TS1、TS2 は、環境 (例えば回路装置 100 や振動子 110) の温度に応じて変化する温度依存電圧を、温度検出電圧として出力する。例えば温度センサー TS1、TS2 は、温度依存性を有する回路素子を利用して温度依存電圧を生成し、温度に非依存の電圧 (例えばバンドギャップリフレンス電圧) を基準として温度依存電圧を出力する。例えば、PN 接合の順方向電圧を温度依存電圧として出力する。温度センサー TS2 からの温度検出電圧は、センサー入力端子 TTS を介してセレクター 10 に入力される。

40

#### 【0101】

セレクター 10 は、温度センサー TS1、TS2 からの温度検出電圧を順次に選択し、その時分割の温度検出電圧を A/D 変換器 127 に出力する。なお、振動デバイス 2 が含む温度センサーの個数は 2 に限定されず、振動デバイス 2 は第 1 ~ 第 m の温度センサー (m は 1 以上 n 以下の整数) を含むことができる。このとき、セレクター 10 には第 1 ~ 第 n の電圧が入力されてもよく、その第 1 ~ 第 n の電圧の第 1 ~ 第 m の電圧として第 1 ~ 第 m の温度センサーからの第 1 ~ 第 m の温度検出電圧が入力されてもよい。セレクター 10 は、第 1 ~ 第 n の電圧を順次に選択し、その時分割の温度検出電圧を A/D 変換器 127 に出力する。

50

**【0102】**

A / D 変換器 127 は、セレクター 10 の出力電圧を A / D 変換する。即ち、セレクター 10 が時分割に出力する温度センサー TS1、TS2 からの温度検出電圧を A / D 変換し、その結果を時分割の温度検出データとして出力する。A / D 変換器 127 は、図 1 等で説明した A / D 変換回路 20 と量子化誤差保持回路 30 とを含む。

**【0103】**

処理回路 123（デジタル信号処理回路）は種々の信号処理を行う。例えば処理回路 123（温度補償部）は、温度検出データに基づいて、振動子 110 の発振周波数の温度特性を補償する温度補償処理を行い、発振周波数を制御するための周波数制御データを出力する。具体的には処理回路 123 は、温度に応じて変化する温度検出データ（温度依存データ）と、温度補償処理用の係数データ（近似関数の係数のデータ）などに基づいて、温度変化による発振周波数の変動をキャンセル又は低減する（温度変化があった場合にも発振周波数を一定にする）ための温度補償処理を行う。温度補償処理用の係数データは記憶部 124 に記憶される。記憶部 124 は、RAM（SRAM、DRAM）などの半導体メモリーにより実現してもよいし、不揮発性メモリーにより実現してもよい。処理回路 123 は、温度補償処理を含む種々の信号処理を時分割に実行する DSP（Digital Signal Processor）により実現できる。或いは処理回路 123 は、ゲートアレイ等の自動配置配線による ASIC 回路により実現してもよいし、プロセッサー（例えば CPU、MPU 等）とプロセッサー上で動作するプログラムにより実現してもよい。また処理回路 123 は温度補償以外の補正処理（例えばエーディング補正）を行ってもよい。また処理回路 123 は、恒温槽型発振器（OCXO）における恒温槽のヒーター制御（オープン制御）などを行ってもよい。1020

**【0104】**

なお処理回路 123 は、クロック信号 SCL、データ信号 SDA を用いて外部デバイスとの間でシリアル通信を行うインターフェース回路を有している。インターフェース回路は例えば I2C や SPI などのインターフェース回路である。信号端子 TSC、TSD は、これらのクロック信号 SCL、データ信号 SDA 用の端子である。

**【0105】**

D / A 変換回路 125 は、周波数制御データを D / A 変換し、周波数制御データに対応する制御電圧を発振回路 121 に出力する。発振回路 121 に設けられる可変容量回路は、この制御電圧に基づいて容量値が可変に制御される。この場合の可変容量回路は、前述のバラクターなどにより実現できる。30

**【0106】**

電源端子 TV には高電位側の電源電圧 VDD が供給され、電源端子 TG には低電位側の電源電圧 VSS（例えば接地電圧）が供給される。回路装置 100 は、これらの電源電圧 VDD、VSS が供給されて動作する。

**【0107】**

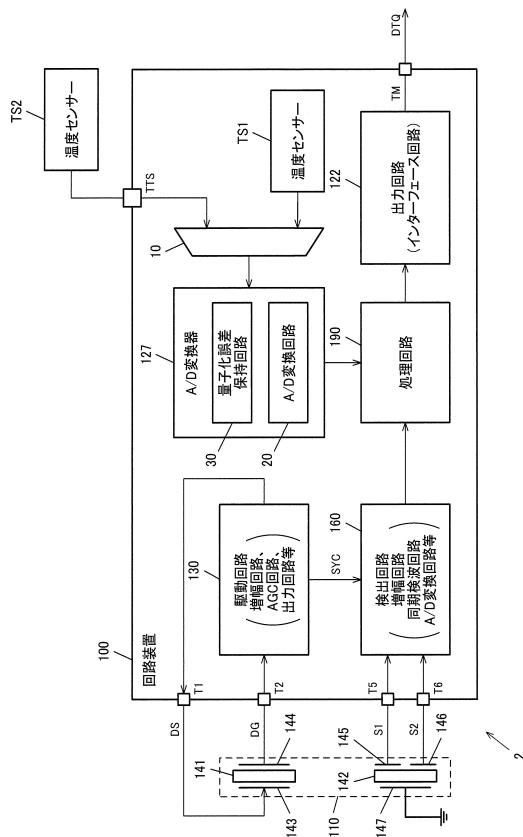

図 11 は、回路装置 100 を含む振動デバイス 2 の第 2 の構成例である。図 11 では、振動デバイス 2 が、物理量を測定するための物理量測定装置（物理量検出装置）である場合を例に説明する。測定される物理量としては角速度、加速度、角加速度、速度、距離又は時間等の種々の物理量を想定できる。なお以下では、角速度を検出するジャイロセンサー（振動ジャイロセンサー）を例にとって説明する。40

**【0108】**

図 11 の振動デバイス 2 は、振動子 110 と回路装置 100 と温度センサー TS2 とを含む。回路装置 100 は、駆動回路 130 と、検出回路 160 と、出力回路 122 と、処理回路 190 と、温度センサー TS1 と、セレクター 10 と、A / D 変換器 127 と、端子 T1、T2、T5、T6 と、センサー入力端子 TTS と、出力端子 TM と、を含む。

**【0109】**

振動子 110（センサー素子、物理量トランスデューサー）は、物理量を検出するための素子であり、振動片 141、142 と、駆動電極 143、144 と、検出電極 145、50

146と、接地電極147を有する。振動片141、142は、例えば水晶などの圧電材料の薄板から形成される圧電型振動片である。具体的には、振動片141、142は、Zカットの水晶基板により形成された振動片である。なお振動片141、142の圧電材料は、水晶以外のセラミックスやシリコン等の材料であってもよい。

#### 【0110】

駆動電極143には、回路装置100の駆動回路130からの駆動信号DS（広義には出力信号）が端子T1を介して供給され、これにより駆動用の振動片141が振動する。振動片141は例えば振動子110の駆動アームである。そして駆動電極144からのフィードバック信号DG（広義には入力信号）が端子T2を介して駆動回路130に対して入力される。例えば振動片141が振動することによるフィードバック信号DGが駆動回路130に入力される。10

#### 【0111】

そして駆動用の振動片141が振動することにより検出用の振動片142が振動し、この振動により発生した電荷（電流）が検出信号S1、S2として検出電極145、146から端子T5、T6を介して検出回路160に入力される。ここで接地電極147は接地電位に設定されている。検出回路160は、これらの検出信号S1、S2に基づいて、検出信号S1、S2に対応する物理量情報（角速度等）を検出する。ここでは、振動子110がジャイロセンサー素子である場合を主に例にとり説明するが、本実施形態はこれに限定されるものではなく、加速度等の他の物理量を検出する素子であってもよい。また振動子110としては例えばダブルT型構造の振動片を用いることができるが、音叉型又はH型等の振動片であってもよい。20

#### 【0112】

駆動回路130は、振動子110からのフィードバック信号DGが入力されて信号増幅を行う増幅回路や、自動ゲイン制御を行うAGC回路（ゲイン制御回路）や、駆動信号DSを振動子110に出力する出力回路などを含むことができる。例えばAGC回路は、振動子110からのフィードバック信号DGの振幅が一定になるように、ゲインを可変に自動調整する。AGC回路は、増幅回路からの信号を全波整流する全波整流器や、全波整流器の出力信号の積分処理を行う積分器などにより実現できる。出力回路は、例えば矩形波の駆動信号DSを出力する。この場合には出力回路はコンパレーターとバッファー回路などにより実現できる。なお出力回路は正弦波の駆動信号DSを出力してもよい。また駆動回路130は、例えば増幅回路の出力信号に基づいて同期信号SYCを生成して、検出回路160に出力する。30

#### 【0113】

検出回路160は、駆動回路130により駆動される振動子110からの検出信号S1、S2に基づいて、検出信号S1、S2に対応する物理量情報を検出する。検出回路160は、増幅回路、同期検波回路、調整回路等を含むことができる。増幅回路には、振動子110からの検出信号S1、S2が端子T1、T2を介して入力されて、検出信号S1、S2の電荷・電圧変換や信号増幅を行う。検出信号S1、S2は差動信号を構成している。具体的には増幅回路は、検出信号S1を増幅する第1のQ/V変換回路と、検出信号S2を増幅する第2のQ/V変換回路と、第1、第2のQ/V変換回路の出力信号を差動増幅する差動アンプを含むことできる。同期検波回路は、駆動回路130からの同期信号SYCを用いた同期検波を行う。例えば検出信号S1、S2から所望波を抽出するための同期検波を行う。調整回路は、ゼロ点補正のためのオフセット調整や、感度調整のためのゲイン補正を行う。また検出回路160は、A/D変換回路を有する。A/D変換回路は、同期検波後の信号をA/D変換し、その結果であるデジタルの検出データを処理回路190に出力する。また検出回路160は、同期検波等によって除去しきれなかった不要信号を減衰させるフィルター回路を含むことができる。40

#### 【0114】

温度センサーTS1、TS2、セレクター10、A/D変換器127の構成及び動作は図10と同様なので、ここでは説明を省略する。50

**【 0 1 1 5 】**

処理回路 190 は、検出回路 160 からの検出データに基づいて、オフセット調整のための補正処理や感度調整のための補正処理などの各種の補正処理を行う。例えば、処理回路 190 は、A / D 変換器 127 からの温度検出データに基づいて物理量（角速度）のゼロ点補正処理を行う。即ち、ゼロ点の温度依存性をキャンセル（又は低減）する補正值を温度検出データに基づいて求め、その補正值によって物理量を補正する。

**【 0 1 1 6 】**

出力回路 122 は、処理回路 190 からの補正処理後の検出データ D T Q を、出力端子 T M を介して回路装置 100 の外部に出力する。この場合の出力回路 122 は、例えば I 10

2 C や S P I などのインターフェース回路により実現してもよい。

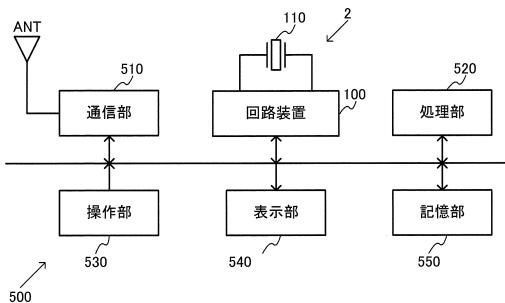

**【 0 1 1 7 】****6 . 電子機器、移動体**

図 12 に、本実施形態の振動デバイス 2 (回路装置 100) を含む電子機器 500 の構成例を示す。この電子機器 500 は、回路装置 100 と振動子 110 を有する振動デバイス 2 と、処理部 520 を含む。また通信部 510、操作部 530、表示部 540、記憶部 550、アンテナ A N T を含むことができる。

**【 0 1 1 8 】**

電子機器 500 としては、例えば基地局又はルーター等のネットワーク関連機器、距離、時間、流速又は流量等の物理量を計測する高精度の計測機器、生体情報を測定する生体情報測定機器（超音波測定装置、脈波計、血圧測定装置等）、車載機器（自動運転用の機器等）などを想定できる。また電子機器 500 として、頭部装着型表示装置や時計関連機器などのウェアラブル機器、ロボット、印刷装置、投影装置、携帯情報端末（スマートフォン等）、コンテンツを配信するコンテンツ提供機器、或いはデジタルカメラ又はビデオカメラ等の映像機器などを想定できる。

**【 0 1 1 9 】**

通信部 510（通信インターフェース）は、アンテナ A N T を介して外部からデータを受信したり、外部にデータを送信する処理を行う。処理部 520（プロセッサー）は、電子機器 500 の制御処理や、通信部 510 を介して送受信されるデータの種々のデジタル処理などを行う。処理部 520 の機能は、例えばマイクロコンピューターなどのプロセッサーにより実現できる。操作部 530（操作インターフェース）は、ユーザーが入力操作を行うためのものであり、操作ボタンやタッチパネルディスプレイなどにより実現できる。表示部 540 は、各種の情報を表示するものであり、液晶や有機 E L などのディスプレイにより実現できる。記憶部 550 は、データを記憶するものであり、その機能は R A M や R O M などの半導体メモリーや H D D（ハードディスクドライブ）などにより実現できる。

**【 0 1 2 0 】**

図 13 に、本実施形態の振動デバイス 2 (回路装置 100) を含む移動体の例を示す。本実施形態の振動デバイス 2 (発振器、物理量測定装置) は、例えば、車、飛行機、バイク、自転車、ロボット、或いは船舶等の種々の移動体に組み込むことができる。移動体は、例えばエンジンやモーター等の駆動機構、ハンドルや舵等の操舵機構、各種の電子機器（車載機器）を備えて、地上や空や海上を移動する機器・装置である。図 13 は移動体の具体例としての自動車 206 を概略的に示している。自動車 206 には、本実施形態の振動デバイス 2 が組み込まれる。制御装置 208 は、この振動デバイス 2 により生成されたクロック信号や測定された物理量情報に基づいて種々の制御処理を行う。例えば物理量情報として、自動車 206 の周囲の物体の距離情報が測定された場合に、制御装置 208 は、測定された距離情報を用いて自動運転のための種々の制御処理を行う。制御装置 208 は、例えば車体 207 の姿勢に応じてサスペンションの硬軟を制御したり、個々の車輪 209 のブレーキを制御する。なお本実施形態の振動デバイス 2 が組み込まれる機器は、このような制御装置 208 には限定されず、自動車 206 やロボット等の移動体に設けられる種々の機器に組み込むことができる。

10

20

30

40

50

## 【0121】

なお、上記のように本実施形態について詳細に説明したが、本発明の新規事項および効果から実体的に逸脱しない多くの変形が可能であることは当業者には容易に理解できるであろう。従って、このような変形例はすべて本発明の範囲に含まれるものとする。例えば、明細書又は図面において、少なくとも一度、より広義または同義な異なる用語と共に記載された用語は、明細書又は図面のいかなる箇所においても、その異なる用語に置き換えることができる。また本実施形態及び変形例の全ての組み合わせも、本発明の範囲に含まれる。また回路装置、振動デバイス、電子機器、移動体の構成及び動作等も本実施形態で説明したものに限定されず、種々の変形実施が可能である。

## 【符号の説明】

10

## 【0122】

2 ... 振動デバイス、 1 0 , 1 1 , 1 2 ... セレクター、 2 0 ... A / D 変換回路、 2 1 ... D / A 変換回路、 2 2 ... 比較回路、 2 3 ... 制御回路、 3 0 ... 量子化誤差保持回路、 4 0 ... 加算回路、 1 0 0 ... 回路装置、 1 1 0 ... 振動子、 1 2 1 ... 発振回路、 1 2 2 ... 出力回路、 1 2 3 ... 処理回路、 1 2 4 ... 記憶部、 1 2 5 ... D / A 変換回路、 1 2 7 ... A / D 変換器、 1 3 0 ... 駆動回路、 1 4 1 , 1 4 2 ... 振動片、 1 4 3 , 1 4 4 ... 駆動電極、 1 4 5 , 1 4 6 ... 検出電極、 1 4 7 ... 接地電極、 1 5 0 ... 発振信号生成回路、 1 6 0 ... 検出回路、 1 9 0 ... 処理回路、 2 0 6 ... 自動車（移動体）、 2 0 7 ... 車体、 2 0 8 ... 制御装置、 2 0 9 ... 車輪、 5 0 0 ... 電子機器、 5 1 0 ... 通信部、 5 2 0 ... 処理部、 5 3 0 ... 操作部、 5 4 0 ... 表示部、 5 5 0 ... 記憶部、 A M P ... 演算増幅器、 C A N , C A P ... キャパシターアレイ回路、 C E N 1 ~ C E N 8 , C E P 1 ~ C E P 8 ... キャパシター（保持用キャパシター）、 C F N , C F P ... キャパシター（帰還用キャパシター）、 C H C D ... チョッピング復調回路、 C H C M ... チョッピング変調回路、 D O U T ... A / D 変換結果データ、 H N 1 ~ H N 8 , H P 1 ~ H P 8 ... 保持回路、 N S N , N S P ... サンプリングノード、 Q E H 1 ~ Q E H n ... 量子化誤差保持回路、 S A D ... 逐次比較データ、 T S 1 ~ T S 7 ... 温度センサー、 V I 1 ~ V I n ... 電圧

20

30

40

50

【図面】

【図 1】

【図 2】

10

20

30

40

【図 3】

【図 4】

50

【図 5】

【図 6】

【図 7】

【図 8】

10

20

30

40

50

【図9】

【図 10】

【図 1 1】

【図 1 2】

【図 1 3】

10

20

30

40

50

---

フロントページの続き

コーエプソン株式会社内

審査官 小林 正明

- (56)参考文献

- 特開2015-211391 (JP, A)

- 特開2017-017665 (JP, A)

- 特開2014-216705 (JP, A)

- 特開2017-092744 (JP, A)

- 特開平04-227118 (JP, A)

- 特開2011-082879 (JP, A)

(58)調査した分野 (Int.Cl., DB名)

H03M 1 / 08

H03M 1 / 46