República Federativa do Brasil

Ministério da Economia

Instituto Nacional da Propriedade Industrial

**(11) BR 112017004693-8 B1**

**(22) Data do Depósito: 20/08/2015**

**(45) Data de Concessão: 21/06/2022**

**(54) Título:** CIRCUITOS DE REDE DE TENSÃO DISTRIBUÍDA EMPREGANDO MÉDIA DE TENSÃO, E SISTEMAS E MÉTODOS RELACIONADOS

**(51) Int.Cl.:** G01R 31/30; H01L 21/66.

**(30) Prioridade Unionista:** 10/09/2014 US 14/482,456.

**(73) Titular(es):** QUALCOMM INCORPORATED.

**(72) Inventor(es):** BURT LEE PRICE; YESHWANT NAGARAJ KOLLA; DHAVAL RAJESHBHAI SHAH.

**(86) Pedido PCT:** PCT US2015046067 de 20/08/2015

**(87) Publicação PCT:** WO 2016/039962 de 17/03/2016

**(85) Data do Início da Fase Nacional:** 09/03/2017

**(57) Resumo:** CIRCUITOS DE REDE DE TENSÃO DISTRIBUÍDA EMPREGANDO MÉDIA DE TENSÃO, E SISTEMAS E MÉTODOS RELACIONADOS. São descritos circuitos de rede de tensão distribuída empregando média de tensão, e sistemas métodos e relacionados. Em um aspecto, como a tensão em uma área de um circuito de carga distribuída pode variar de tensão em uma segunda área, um circuito de rede de tensão distribuída é configurado para derivar tensões de múltiplas áreas para calcular a tensão média no circuito de carga distribuída. O circuito de rede de tensão distribuída inclui um componente de fonte de distribuição de tensão tendo nós fonte. A tensão é distribuída a partir de cada nó fonte para um nó de carga de tensão correspondente através de interconexões resistivas. Os nós de derivação de tensão acessam a tensão de cada nó de carga de tensão correspondente. Cada nó de derivação de tensão é acoplado a um nó de entrada de um elemento resistivo correspondente no circuito de média de tensão. Um nó de saída de cada elemento resistivo é conectado a um nó de saída de tensão do circuito de tensão média, gerando a tensão média do circuito de carga distribuída no nó de saída de tensão.

**"CIRCUITOS DE REDE DE TENSÃO DISTRIBUÍDA EMPREGANDO MÉDIA DE TENSÃO, E SISTEMAS E MÉTODOS RELACIONADOS"**

**Pedido de Prioridade**

[0001] O presente pedido reivindica prioridade ao Pedido de Patente Norte-Americano No. 14/482,456, depositado em 10 de setembro de 2014 e intitulado "CIRCUITOS DE REDE DE TENSÃO DISTRIBUÍDA EMPREGANDO MÉDIA DE TENSÃO, E SISTEMAS E MÉTODOS RELACIONADOS", que é aqui incorporado por referência em sua totalidade.

**FUNDAMENTOS**

**I. Campo da Descrição**

[0002] A tecnologia da descrição refere-se no geral a circuitos de rede de tensão distribuída e, mais especificamente, a medição de tensão e corrente dentro de tais circuitos.

**II. Fundamentos**

[0003] As emissões térmicas são um problema de crescente preocupação em projetos de circuito integrado (IC). Altas temperaturas em um IC podem causar degradação de mobilidade de portador (carrier), que pode retardar o funcionamento do IC, aumentar a resistividade, e/ou causar falhas no circuito. Este problema tornou-se especialmente crítico na medida em que a graduação (scaling) de tensão diminuiu e o número de componentes ativos por unidade de área aumentou. A este respeito, a temperatura de um IC fabricado em uma pastilha (die) semicondutora, como um microprocessador ou uma memória cache, pode ser determinada ou estimada com base na medição de corrente dentro do IC. Como um exemplo não limitador, a medição de corrente dentro de um IC pode ser usada para determinar se a corrente dentro do IC excede a um limite de corrente definido. Se a corrente medida dentro do IC exceder o limite de corrente definido, um sistema de controle correspondente ao IC pode

ser configurado para realizar certas funções que melhoram o desempenho do IC, tal como prevenir o IC do superaquecimento.

[0004] Embora a medição de corrente em pastilha (on-die) de um IC em uma pastilha semicondutora possa ser utilizada para estimar a temperatura do IC, pode ser difícil medir com precisão a corrente dentro do IC. Em particular, devido a distribuição de tensão e, por conseguinte, a distribuição de corrente, poder diferir entre os elementos de circuitos distribuídos dentro de um IC, o perfil de corrente de uma determinada área de um IC não é necessariamente indicativo do perfil de corrente de outras áreas do IC ou de todo o IC. Por exemplo, uma primeira corrente distribuída para uma primeira área de um IC pode ser diferente de uma segunda corrente distribuída para uma segunda área do IC. Deste modo, a medição da corrente em uma área particular de um IC pode não fornecer uma representação precisa da corrente total dentro do IC. Medições imprecisas de corrente dentro do IC resultam em estimativas imprecisas de temperatura dentro do IC, o que pode então reduzir a eficácia das funções baseadas em temperatura configuradas para melhorar o desempenho de um IC.

[0005] A este respeito, seria vantajoso medir com mais precisão a corrente em pastilha, em vista da variação de tensão e dos perfis corrente através dos elementos distribuídos dentro de um IC. Em particular, fornecer medições de corrente em pastilha mais precisas pode melhorar os resultados gerados por funções dentro de um sistema de controle correspondente que utilizam a medição de corrente para aumentar o desempenho do sistema.

#### SUMÁRIO DA DESCRIÇÃO

[0006] Os aspectos descritos na descrição detalhada incluem circuitos de rede de tensão distribuída empregando média de tensão. São também descritos sistemas e métodos relacionados. Em um aspecto, como uma tensão distribuída para uma área de um circuito de carga distribuída dentro de um circuito integrado (IC) pode variar de uma tensão distribuída para uma segunda área do mesmo circuito de carga distribuída, um circuito de rede de tensão distribuída é configurado para derivar tensões a partir de múltiplas áreas para calcular uma tensão média distribuída no circuito de carga distribuída. O circuito de rede de tensão distribuída inclui um componente de fonte de distribuição de tensão tendo múltiplos nós fonte. A tensão é distribuída a partir de cada nó fonte para um nó de carga de tensão correspondente do circuito de carga distribuída através de interconexões resistivas dentro de uma rede de distribuição. Nós de derivação de tensão são empregados dentro da rede de distribuição para acessar a tensão a partir de cada nó de carga de tensão correspondente. Para calcular a tensão média no circuito de carga distribuída, cada nó de derivação de tensão é acoplado a um nó de entrada de um elemento resistivo correspondente em um circuito de média de tensão. Além disso, um nó de saída de cada elemento resistivo é acoplado a um nó de saída de tensão do circuito de média de tensão. O acoplamento dos nós de saída de cada elemento resistivo enquanto o nó de entrada de cada elemento resistivo é acoplado a um nó de derivação de tensão correspondente gera a tensão média do circuito de carga distribuída no nó de saída de tensão.

[0007] Como a tensão em um nó de carga de tensão particular pode variar em comparação com a tensão em outro nó de carga de tensão, a tensão média determinada proporciona uma medição mais precisa da tensão ao longo de

todo circuito de carga distribuída. Assim, a tensão média pode ser utilizada para calcular com mais precisão a corrente no circuito de carga distribuída, em comparação com o cálculo da corrente utilizando uma tensão em uma área específica ou em um único nó de carga de tensão do IC. Uma medição de corrente mais precisa pode melhorar as funções dentro de um sistema de controle correspondente que utilizam a medição de corrente para aumentar o desempenho do sistema.

[0008] A este respeito em um aspecto, um circuito de rede de tensão distribuída é descrito. O circuito de rede de tensão distribuída compreende um componente de fonte de distribuição de tensão. O componente de fonte de distribuição de tensão compreende uma pluralidade de nós fonte. O circuito de rede de tensão distribuída compreende ainda um circuito de carga distribuída, compreendendo uma pluralidade de nós de carga de tensão. O circuito de rede de tensão distribuída compreende ainda uma rede de distribuição de fonte distribuída. A rede de distribuição de fonte distribuída compreende uma pluralidade de interconexões resistivas interconectando cada nó fonte dentre a pluralidade de nós fonte a um nó de carga de tensão correspondente dentre a pluralidade de nós de carga de tensão. A rede de distribuição de fonte distribuída compreende ainda uma pluralidade de nós de derivação de tensão, em que cada nó de derivação de tensão corresponde a um nó de carga de tensão dentre a pluralidade de nós de carga de tensão. O circuito de rede distribuída tensão compreende ainda um circuito de média de tensão. O circuito de média de tensão compreende uma pluralidade de elementos resistivos. Cada elemento resistivo dentre a pluralidade de elementos resistivos compreende um nó de entrada acoplado a um nó de

derivação de tensão correspondente dentre a pluralidade de nós de derivação de tensão e um nó de saída. O circuito de média de tensão compreende ainda um nó de saída de tensão acoplado ao nó de saída de cada elemento resistivo dentre a pluralidade de elementos resistivos. O nó de saída de tensão é configurado para fornecer uma tensão média no circuito de carga distribuída.

[0009] Em outro aspecto, é descrito um circuito de rede tensão distribuída. O circuito de rede de tensão distribuída compreende meios para distribuir uma tensão fonte para uma pluralidade de nós de carga de tensão através de uma rede de distribuição de fonte distribuída, em que a rede de distribuição de fonte distribuída compreende uma pluralidade de interconexões resistivas interconectando cada nó fonte de uma pluralidade de nós fonte a um nó de carga de tensão correspondente dentre a pluralidade de nós de carga de tensão. O circuito de rede de tensão distribuída compreende ainda meios para receber a tensão fonte em uma pluralidade de nós de carga de tensão. O circuito de rede de tensão distribuída compreende ainda meios para determinar uma tensão presente em cada nó de carga de tensão dentre a pluralidade de nós de carga de tensão através de um nó de derivação de tensão correspondente dentre uma pluralidade de nós de derivação de tensão. O circuito de rede de tensão distribuída compreende ainda meios para fornecer a tensão presente em cada nó de derivação de tensão dentre a pluralidade de nós de derivação de tensão a um elemento resistivo correspondente dentre uma pluralidade de elementos resistivos. O circuito de rede de tensão distribuída compreende ainda meios para fornecer uma tensão de saída de cada elemento resistivo dentre a pluralidade de elementos resistivos para um nó de saída de tensão configurado para

fornecer uma tensão média através da pluralidade de nós de carga de tensão.

[0010] Em outro aspecto, é descrito um método para calcular uma tensão média de um circuito de rede de tensão distribuída. O método compreende distribuir uma tensão fonte para uma pluralidade de nós de carga de tensão através de uma rede de distribuição de fonte distribuída, onde a rede de interconexão resistiva compreende uma pluralidade de interconexões resistivas interconectando cada nó fonte dentre uma pluralidade de nós fonte a um nó de carga de tensão correspondente dentre a pluralidade de nós de carga de tensão. O método compreende ainda receber a tensão fonte na pluralidade de nós de carga de tensão. O método compreende ainda determinar uma tensão presente em cada nó de carga de tensão dentre a pluralidade de nós de carga de tensão através de um nó de derivação tensão de uma pluralidade de nós de derivação de tensão. O método compreende ainda fornecer a tensão presente em cada nó de derivação de tensão dentre a pluralidade de nós de derivação de tensão de um elemento resistivo correspondente dentre uma pluralidade de elementos resistivos. O método compreende ainda fornecer uma tensão de saída de cada elemento resistivo dentre a pluralidade de elementos resistivos a um nó de saída de tensão configurado para fornecer uma tensão média através da pluralidade de nós de carga de tensão.

[0011] Em outro aspecto, é descrito um sistema de medição de corrente em pastilha. O sistema de medição de corrente em pastilha compreende uma fonte de tensão. O sistema de medição de corrente em pastilha compreende ainda um circuito de carga distribuída compreendendo uma pluralidade de nós de carga de tensão. O sistema de medição de corrente em pastilha compreende ainda uma pluralidade de

transistores cascode. O sistema de medição de corrente em pastilha compreende ainda uma pluralidade de transistores headswitch, em que cada transistor headswitch dentre a pluralidade de transistores headswitch é acoplado à fonte de tensão. O sistema de medição de corrente em pastilha compreende ainda uma pluralidade de transistores espelho, em que cada transistor espelho dentre a pluralidade de transistores espelho é acoplado à fonte de tensão. O sistema de medição de corrente em pastilha compreende ainda uma rede de distribuição de fonte distribuída. A rede de distribuição de fonte distribuída compreende uma pluralidade de interconexões resistivas headswitch interconectando cada transistor headswitch dentre a pluralidade de transistores headswitch a um nó de carga de tensão correspondente dentre a pluralidade de nós de carga de tensão. A rede de distribuição de fonte distribuída compreende ainda uma pluralidade de interconexões resistivas espelho interconectando cada transistor espelho dentre a pluralidade de transistores espelho a uma fonte de um transistor cascode correspondente entre a pluralidade de transistores cascode. A rede de distribuição de fonte distribuída compreende ainda uma pluralidade de nós de derivação de tensão headswitch, em que cada nó de derivação de tensão headswitch corresponde a um nó de carga de tensão dentre a pluralidade de nós de carga de tensão. A rede de distribuição de fonte distribuída compreende ainda uma pluralidade de nós de derivação de tensão espelho, em que cada nó de derivação de tensão espelho corresponde a um transistor cascode dentre a pluralidade de transistores cascode.

[0012] O sistema de medição de corrente em pastilha compreende ainda um circuito de média de tensão headswitch compreendendo uma pluralidade de resistores.

Cada resistor dentre a pluralidade de resistores compreende um nó de entrada acoplado a um nó de derivação de tensão headswitch correspondente dentre a pluralidade de nós de derivação de tensão headswitch e um nó de saída. O circuito de média de tensão headswitch compreende ainda um nó de saída de tensão headswitch acoplado ao nó de saída de cada resistor, o nó de saída de tensão configurado para fornecer uma tensão headswitch média presente no circuito de carga distribuída. O sistema de medição de corrente em pastilha compreende ainda um circuito de média de tensão espelho compreendendo uma pluralidade de resistores. Cada resistor dentre a pluralidade de resistores compreende um nó de entrada acoplado a um transistor espelho correspondente dentre a pluralidade de transistores espelho, e um nó de saída. O circuito de média de tensão espelho compreende ainda um nó de saída de tensão espelho acoplado ao nó de saída de cada resistor, o nó de saída de tensão configurado para fornecer uma tensão espelho média presente na pluralidade de transistores cascode. O sistema de medição de corrente em pastilha compreende ainda um dreno de cada transistor cascode dentre a pluralidade de transistores cascode acoplado a um resistor de sentido (sense resistor), o resistor de sentido configurado para fornecer uma tensão para um conversor analógico/digital (ADC). O sistema de medição de corrente em pastilha compreende ainda o ADC configurado para converter a tensão a partir do um resistor de sentido em um sinal digital representativo de uma corrente de fonte de alimentação do circuito de carga distribuída. O sistema de medição de corrente em pastilha compreende ainda um amplificador operacional. O amplificador operacional compreende uma primeira entrada acoplada ao nó de saída de tensão headswitch. O amplificador operacional compreende ainda uma segunda

entrada acoplada ao nó de saída de tensão espelho. O amplificador operacional compreende ainda um nó de saída acoplado a uma porta (gate) correspondente à pluralidade de transistores cascode.

#### BREVE DESCRIÇÃO DAS FIGURAS

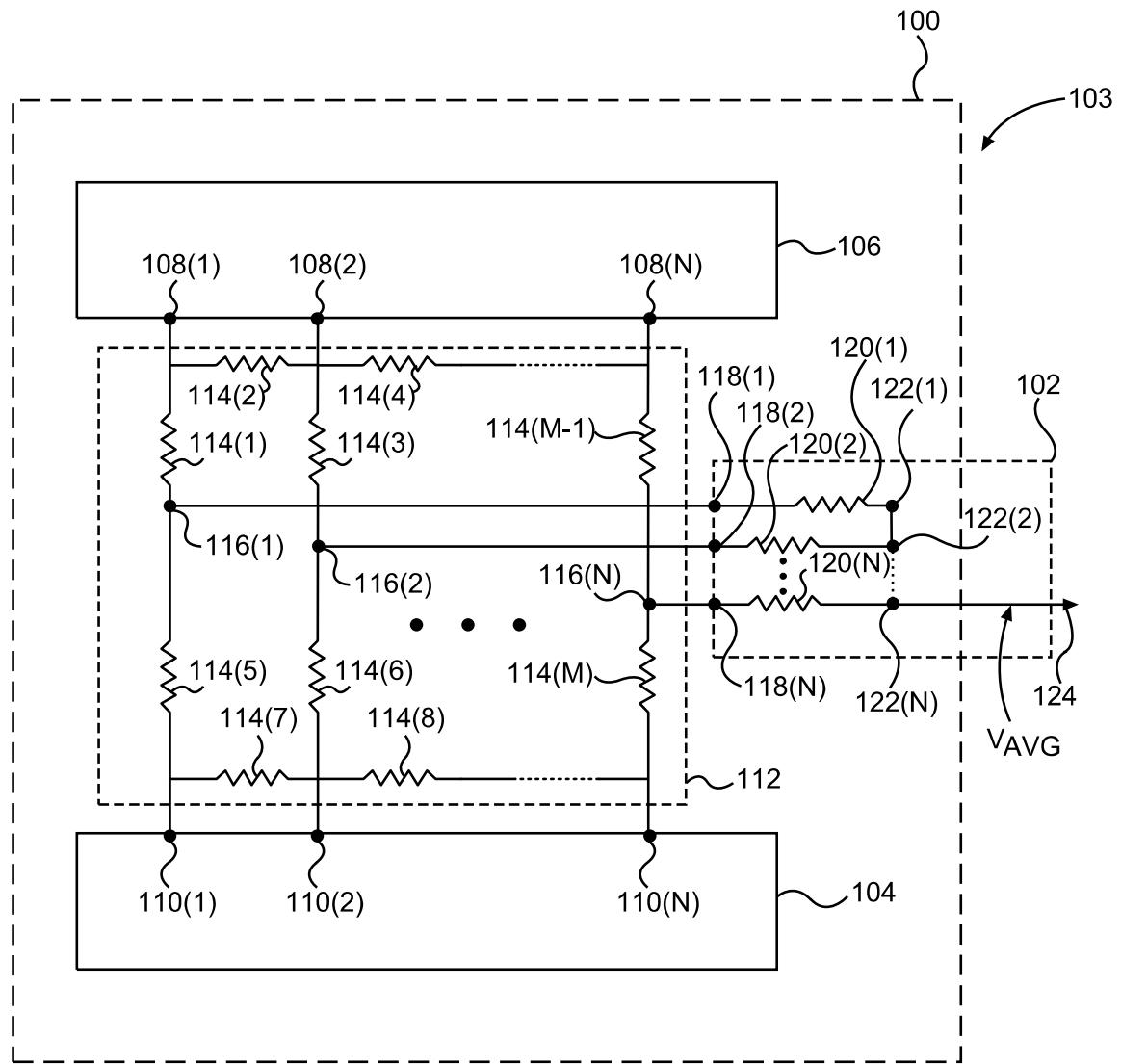

[0013] A Figura 1 é um diagrama de blocos de um circuito de rede tensão distribuída exemplar dentro de um circuito integrado (IC) empregando um circuito de média de tensão configurado para calcular uma tensão média de um circuito de carga distribuída através da média das tensões em múltiplas áreas do circuito de carga distribuída;

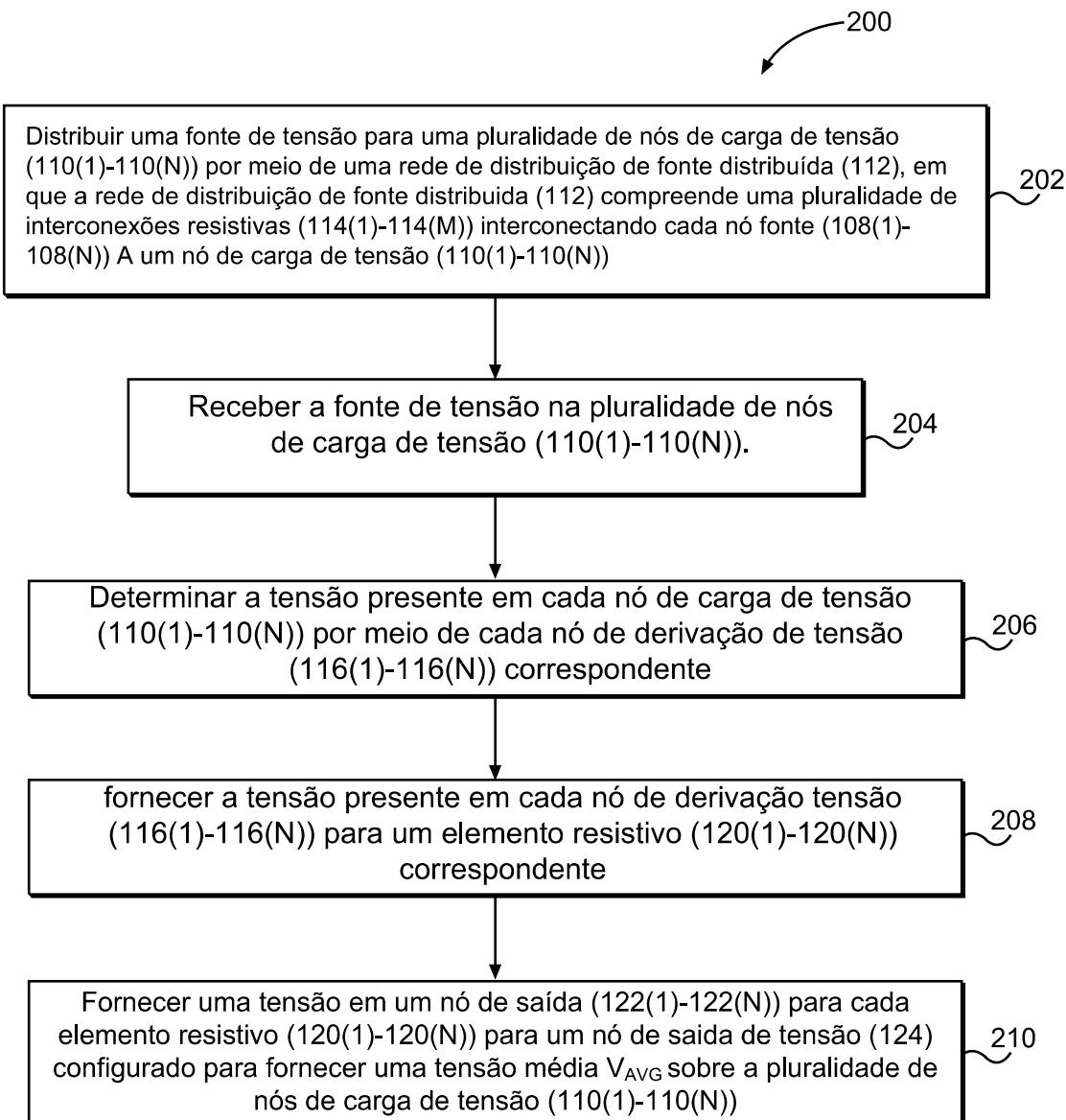

[0014] A Figura 2 é um fluxograma de um processo exemplar empregado pelo circuito de rede de tensão distribuída na Figura 1 para calcular uma tensão média do circuito de carga distribuída;

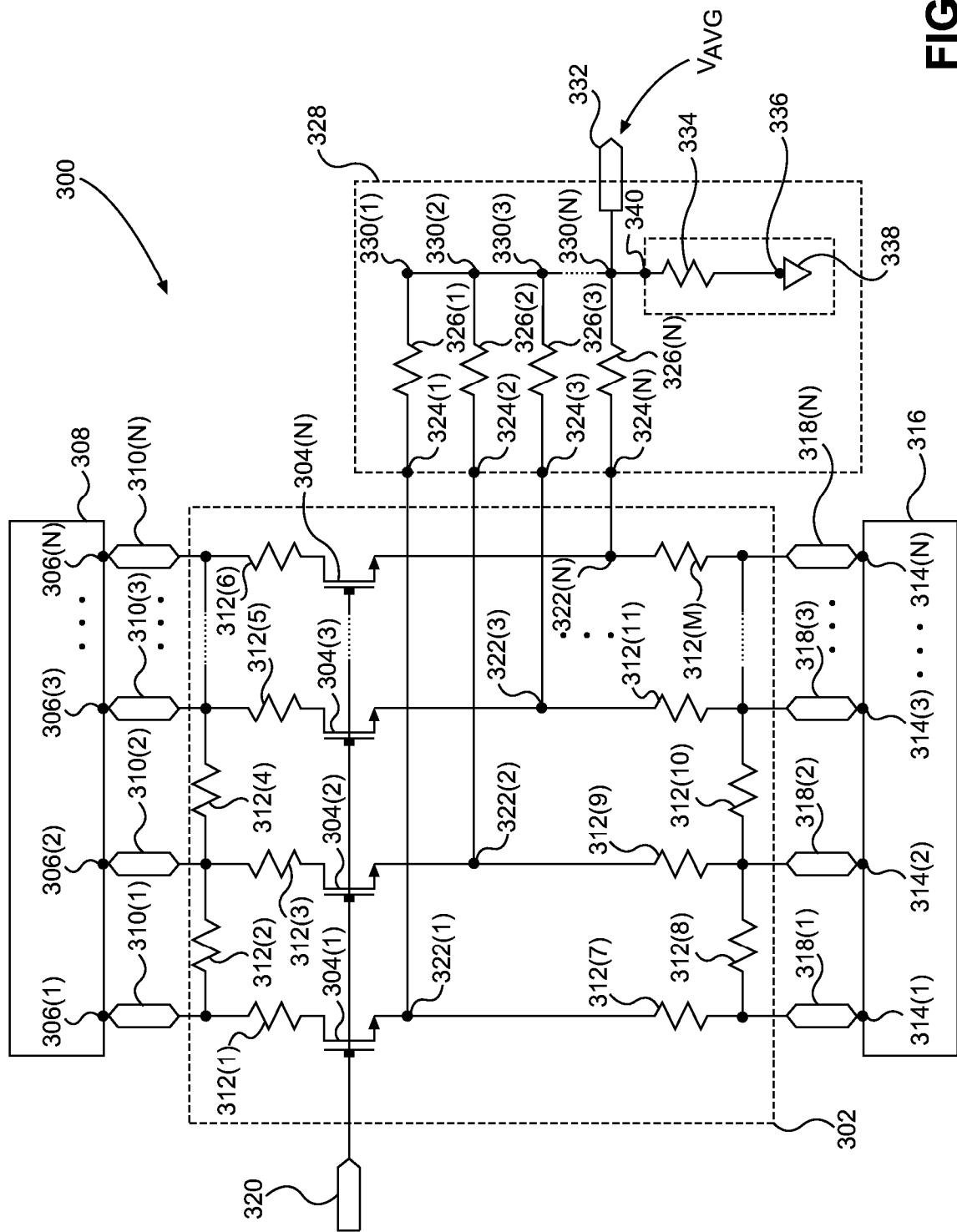

[0015] A Figura 3 é um diagrama de circuito de outro circuito de rede de tensão distribuída exemplar semelhante ao circuito de rede de tensão distribuída na Figura 1, mas empregando transistores semicondutores de óxido metálico tipo n (NMOS) em uma rede de distribuição de fonte distribuída;

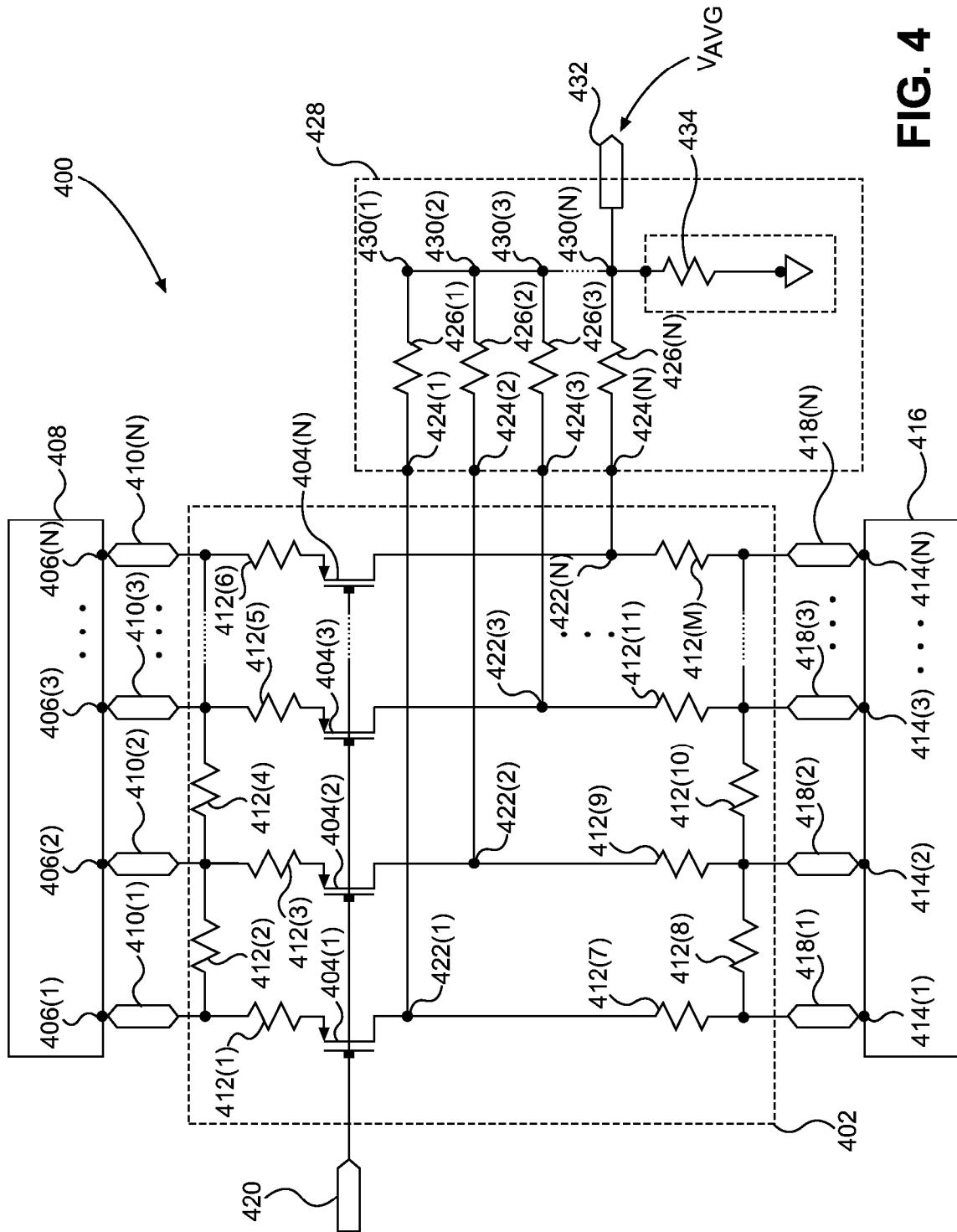

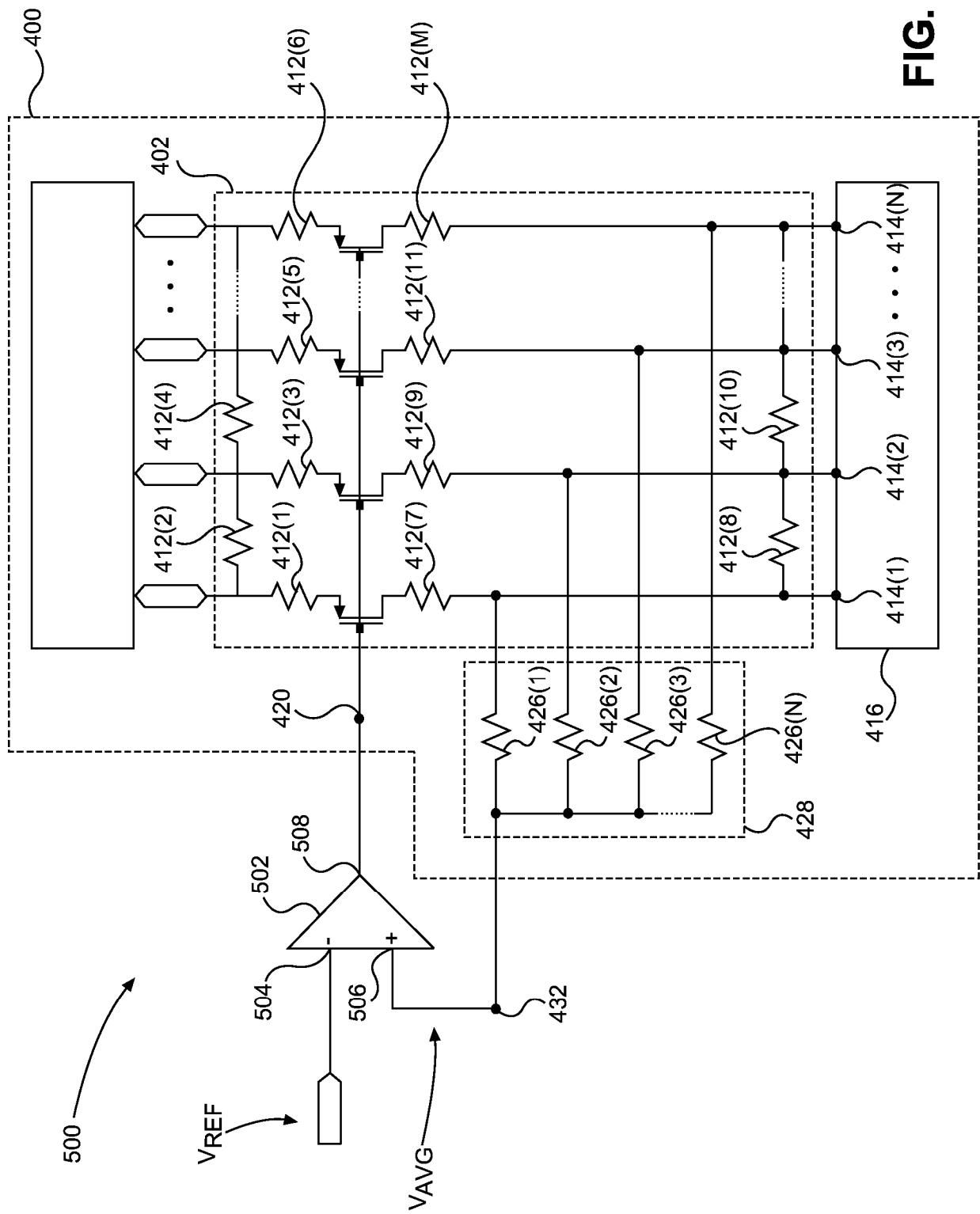

[0016] A Figura 4 é um diagrama de circuito de outro circuito de rede de tensão distribuída exemplar semelhante ao circuito de rede de tensão distribuída na Figura 1, mas empregando transistores semicondutores de óxido metálico tipo p (PMOS) em uma rede de distribuição de fonte distribuída;

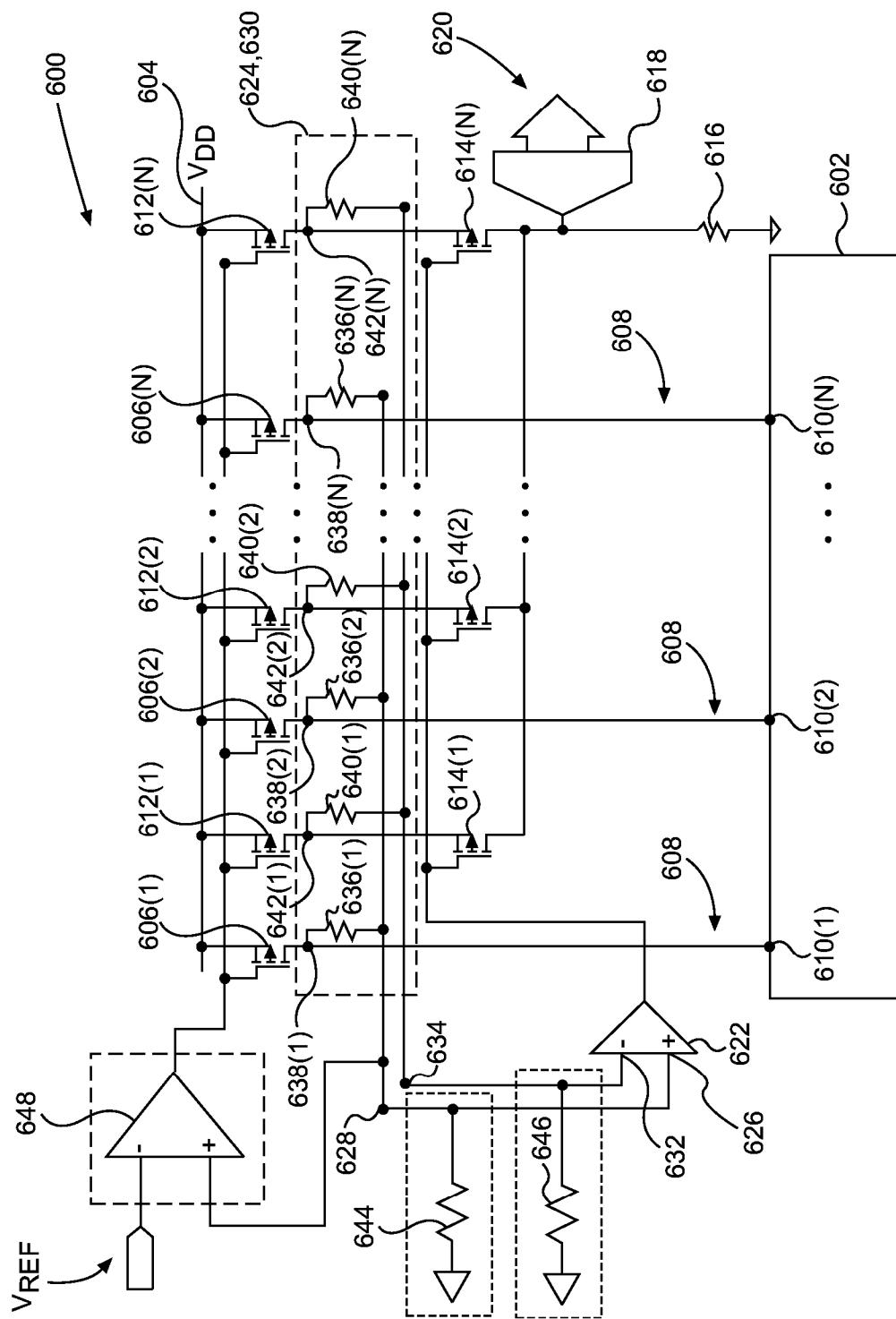

[0017] A Figura 5 é um diagrama de circuito do circuito de rede de tensão distribuída empregando transistores PMOS na Figura 4, em que uma saída de circuito de média de tensão é fornecida a um regulador de tensão configurado para controlar uma tensão média através dos nós de carga de tensão do circuito de carga distribuída;

[0018] A Figura 6 é um diagrama de circuito de um sistema de medição de corrente em pastilha exemplar empregando os circuitos de média de tensão semelhantes ao circuito de média de tensão na Figura 1 em relação aos transistores headswitch e transistores espelho, e que pode empregar um regulador de tensão configurado para regular as cargas de tensão e corrente;

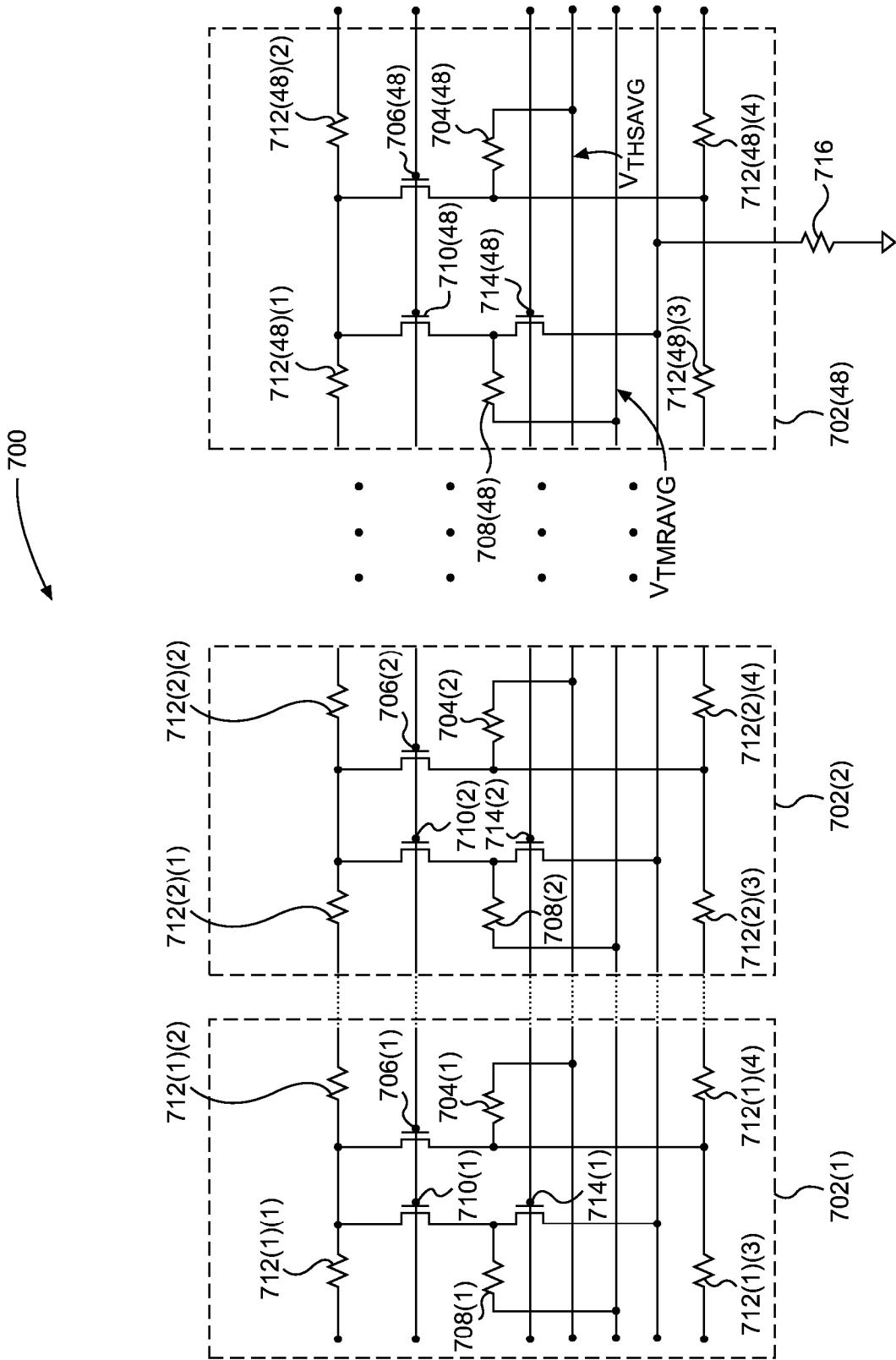

[0019] A Figura 7A é um diagrama de um circuito de teste exemplar que emprega uma pluralidade de ladrilhos (tiles) headswitch que incluem o circuito de média de tensão semelhante ao circuito de média de tensão na Figura 1;

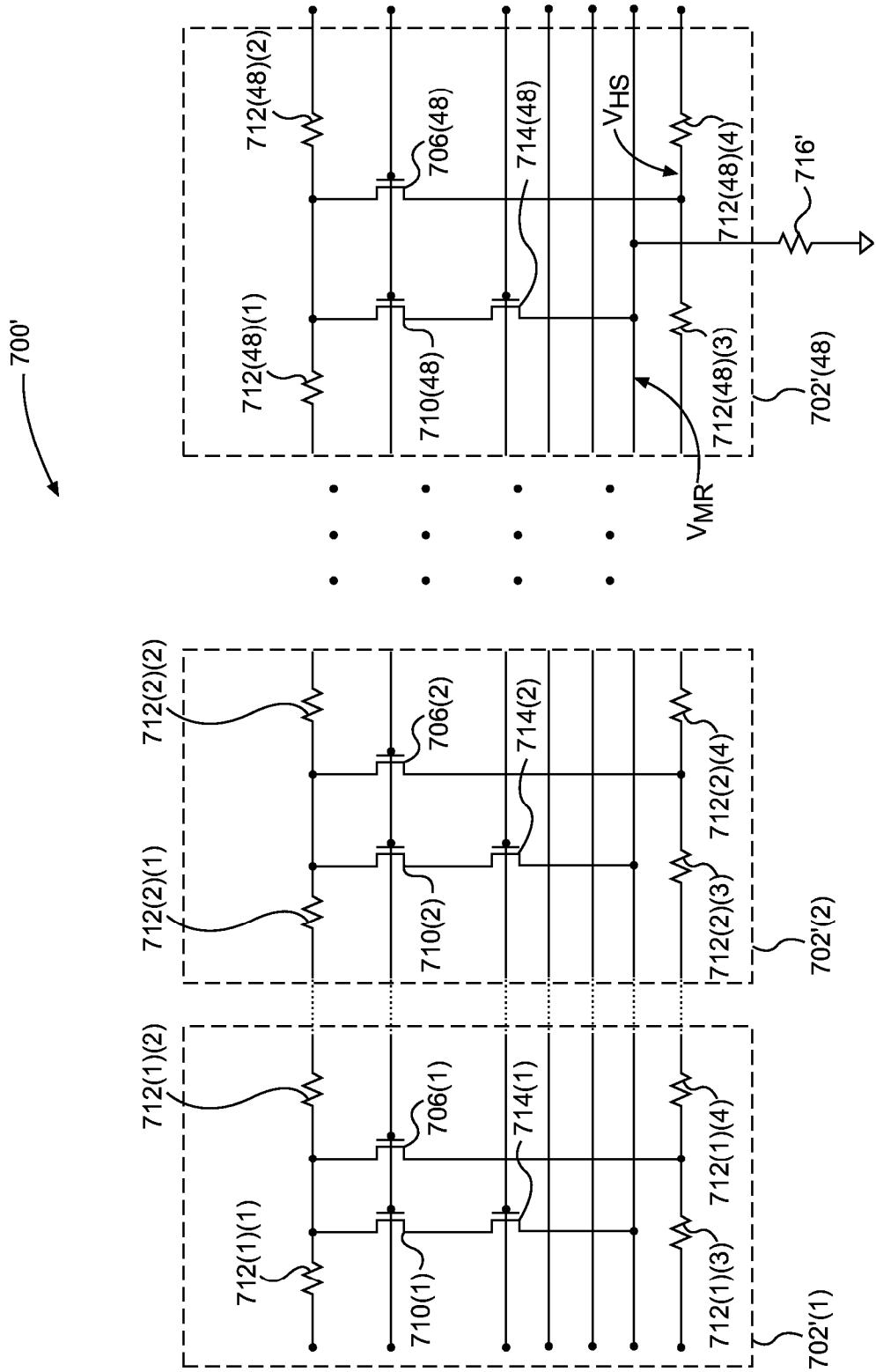

[0020] A Figura 7B é um diagrama de um circuito de teste exemplar que emprega uma pluralidade de ladrilhos headswitch, no qual uma tensão é medida em um único ladrilho headswitch ao invés de medir uma tensão média de todo o circuito de teste;

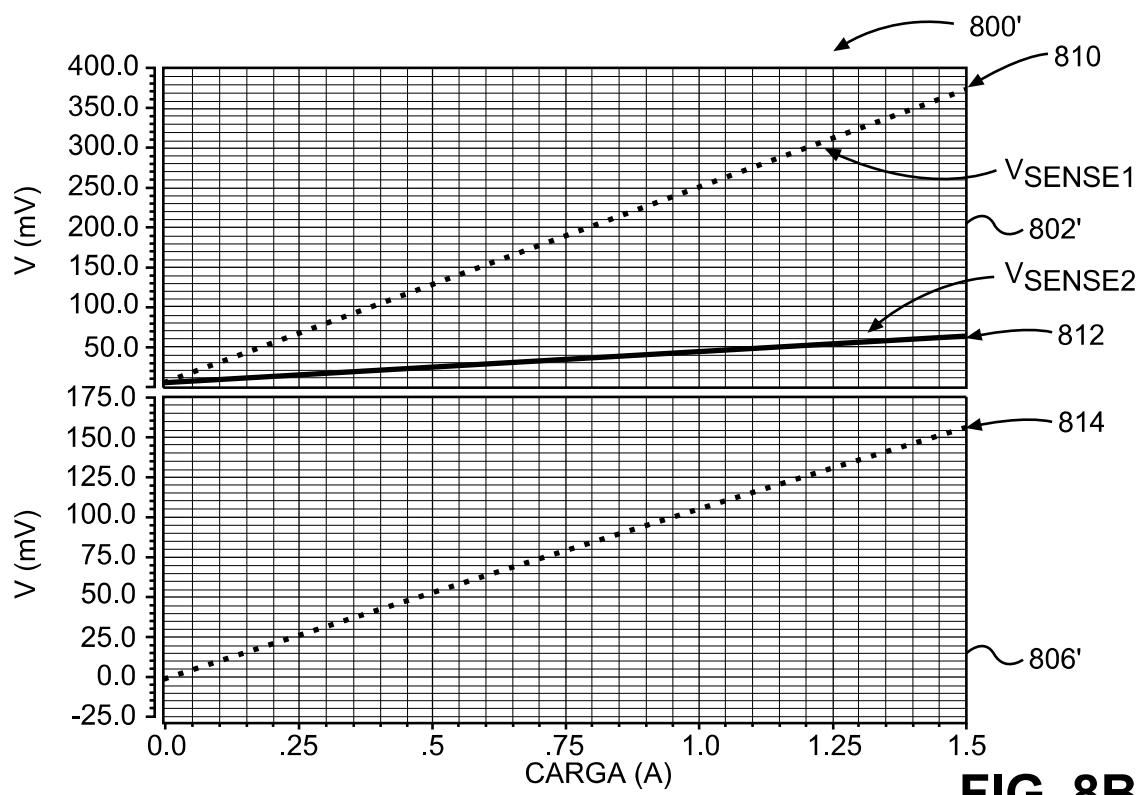

[0021] A Figura 8A é um gráfico ilustrando um conjunto exemplar de sinais correspondendo à tensão média medida através dos circuitos de teste nas figuras 7A e 7B com interconexões metálicas não resistivas ideais;

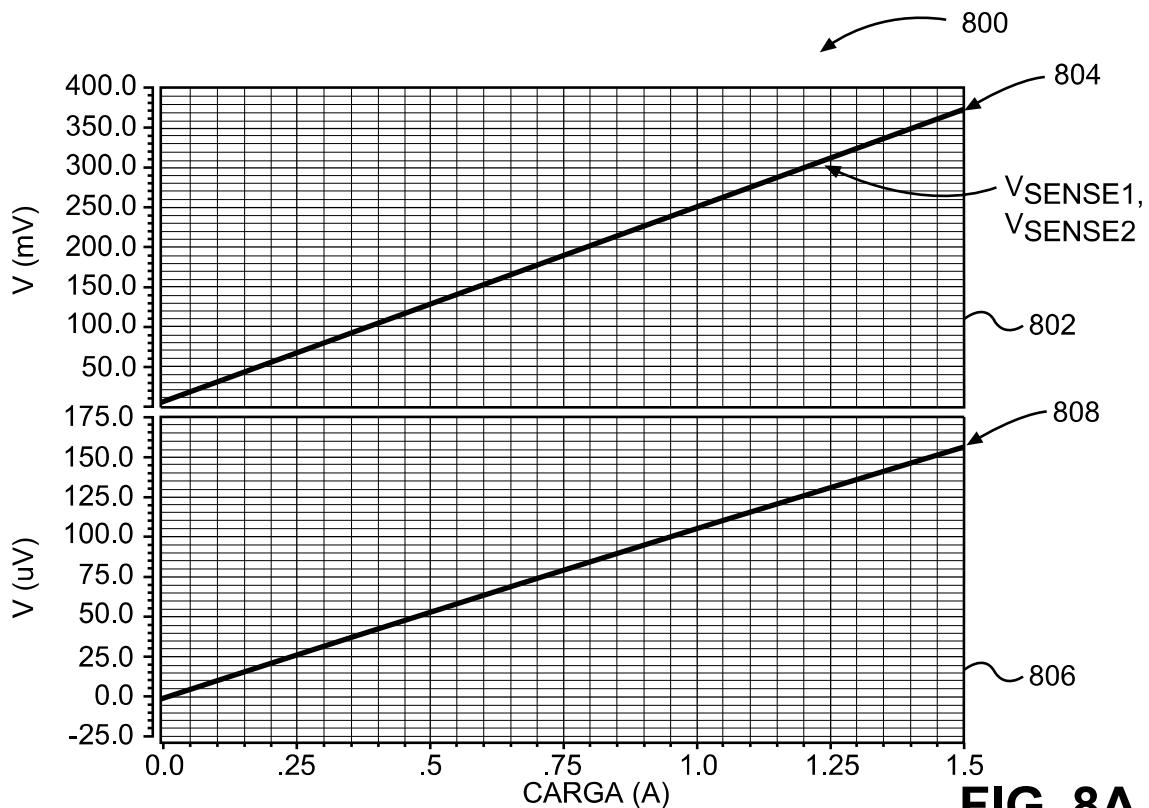

[0022] A Figura 8B é um gráfico ilustrando um conjunto exemplar de sinais correspondendo à tensão média medida através dos circuitos de teste nas figuras 7A e 7B com interconexões metálicas resistivas não ideais;

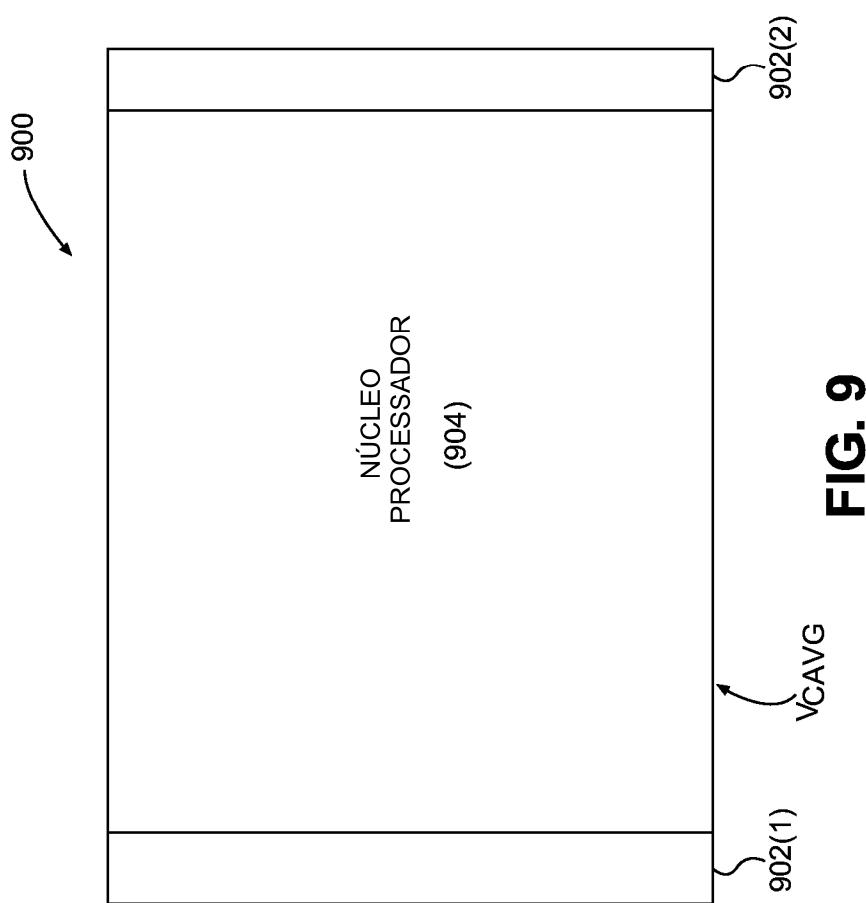

[0023] A Figura 9 é um diagrama de blocos de uma pluralidade exemplar de ladrilhos headswitch acoplados a um núcleo de processador de modo a medir a corrente de carga média do núcleo de processador empregando o circuito de média de tensão na Figura 1; e

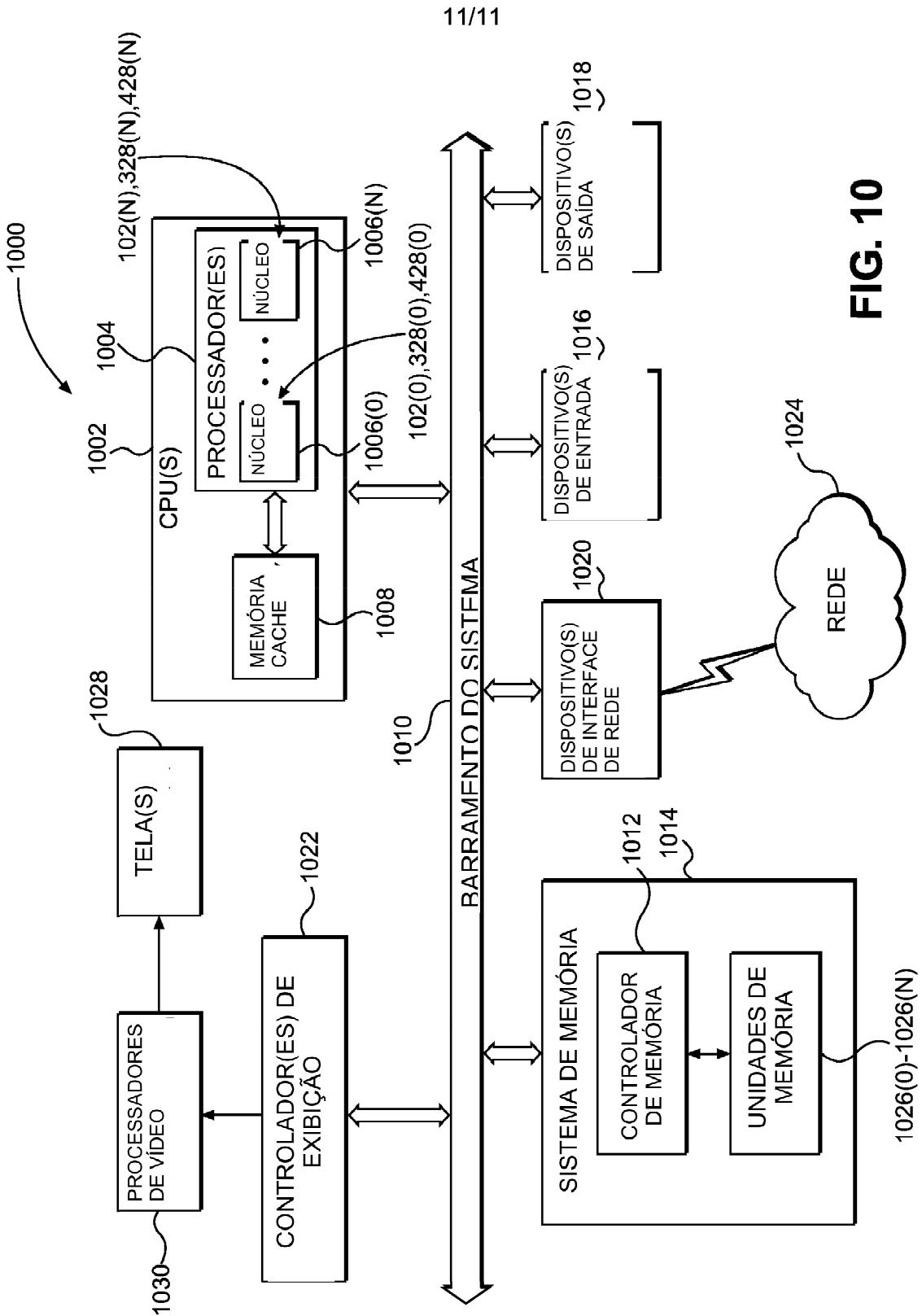

[0024] A Figura 10 é um diagrama de blocos de um sistema baseado em processador exemplar que pode incluir

o circuito de rede de tensão distribuída empregando os circuitos de média de tensão nas Figuras 1, 3 e 4.

#### DESCRIÇÃO DETALHADA

[0025] Com referência às figuras agora, são descritos vários aspectos exemplares da presente descrição. A palavra "exemplar" é usada aqui para significar "servindo como um exemplo, instância ou ilustração". Qualquer aspecto aqui descrito como "exemplar" não deve ser necessariamente interpretado como preferencial ou vantajoso sobre outros aspectos.

[0026] Os aspectos descritos na descrição detalhada incluem circuitos de rede tensão distribuída empregando média de tensão. São descritos também sistemas e métodos relacionados. Em um aspecto, como uma tensão distribuída para uma área de um circuito de carga distribuída dentro de um circuito integrado (IC) pode variar a partir de uma tensão distribuída para uma segunda área do mesmo circuito de carga distribuída, um circuito de rede de tensão distribuída é configurado para derivar tensões de múltiplas áreas para calcular uma tensão média distribuída no circuito de carga distribuída. O circuito de rede de tensão distribuída inclui um componente de fonte de distribuição de tensão tendo múltiplos nós fonte. A tensão é distribuída a partir de cada nó fonte para um nó de carga de tensão correspondente do circuito de carga distribuída através de interconexões resistivas dentro de uma rede de distribuição. Nós de derivação de tensão são empregados dentro da rede de distribuição para acessar a tensão a partir de cada nó de carga de tensão correspondente. Para calcular a tensão média no circuito de carga distribuída, cada nó de derivação de tensão é acoplado a um nó de entrada de um elemento resistivo correspondente em um circuito de média de tensão. Além disso, um nó de saída de

cada elemento resistivo é acoplado a um nó de saída de tensão do circuito de média de tensão. O acoplamento de nós de saída de cada elemento resistivo enquanto o nó de entrada de cada elemento resistivo é acoplado a um nó de derivação de tensão correspondente gera a tensão média do circuito de carga distribuída no nó de saída de tensão.

[0027] Como a tensão em um nó de carga tensão particular pode variar quando comparada com a tensão em outro nó de carga de tensão, a tensão média determinada fornece uma medição de tensão mais precisa através de todo circuito carga distribuída. Assim, a tensão média pode ser usada para calcular a corrente no circuito de carga distribuída com mais precisão, em comparação com o cálculo de corrente utilizando uma tensão em uma área específica ou em um único nó de carga de tensão do IC. Uma medição de corrente mais precisa pode melhorar as funções dentro de um sistema de controle correspondente que utiliza a medição de corrente para aumentar o desempenho do sistema.

[0028] Neste contexto, a Figura 1 é um diagrama de blocos de um circuito de rede de tensão distribuída 100 exemplar empregando um circuito de média de tensão 102. Neste exemplo, o circuito de rede de tensão distribuída 100 é fornecido em um circuito integrado (IC) 103 em uma pastilha semicondutora. O circuito de média de tensão 102 é configurado para calcular uma tensão média ( $V_{AVG}$ ) de um circuito de carga distribuída 104 através da média das tensões fornecidas para múltiplas áreas do circuito de carga distribuída 104. Mais especificamente, o circuito de rede de tensão distribuída 100 é configurado para derivar as tensões de múltiplas áreas para calcular a tensão média ( $V_{AVG}$ ) distribuída para o circuito de carga distribuída 104. Assim, como um exemplo, a tensão média ( $V_{AVG}$ ) pode ser utilizada para calcular a corrente no

círcuito de carga distribuída 104 com mais precisão, em comparação com o cálculo da corrente utilizando uma tensão presente em um único nó de carga de tensão do circuito de carga distribuída 104. A corrente calculada pode ser utilizada para estimar a temperatura dentro do IC 103.

[0029] Continuando com referência à Figura 1, o circuito de rede de tensão distribuída 100 inclui um componente de fonte de distribuição de tensão 106 que emprega uma pluralidade de nós fonte 108(1)-108(N). A tensão é distribuída a partir de cada nó fonte 108(1)-108(N) para um nó de carga de tensão correspondente 110(1)-110(N) do circuito de carga distribuída 104 através de uma rede de distribuição de fonte distribuída 112. A rede de distribuição de fonte distribuída 112 inclui uma pluralidade de interconexões resistivas 114(1)-114(M) que conectam cada nó fonte 108(1)-108(N) ao nó de carga de tensão correspondente 110(1)-110(N). Notavelmente, enquanto este aspecto emprega um resistor separado para cada interconexão resistiva 114(1)-114(M), outros aspectos podem usar elementos de circuito alternativos para cada interconexão resistiva 114(1)-114(M), tal como, para um exemplo não limitador, um comprimento de fio que tem um determinado valor resistivo. Além disso, os nós de derivação de tensão 116(1)-116(N) são empregados dentro da rede de distribuição de fonte distribuída 112 para acessar a tensão de cada nó de carga de tensão correspondente 110(1)-110(N).

[0030] Continuando com referência à Figura 1, para calcular a tensão média no circuito de carga distribuída 104, cada nó de derivação de tensão 116(1)-116(N) é acoplado a um nó de entrada 118(1)-118(N) de um elemento resistivo correspondente 120(1)-120(N) no circuito de média de tensão 102. Notavelmente, embora cada elemento

resistivo 120(1)-120(N) neste aspecto seja um único resistor, outros aspectos podem empregar outros elementos de circuito para cada elemento resistivo 120(1)-120(N) para alcançar funcionalidade semelhante. Um nó de saída 122(1)-122(N) de cada elemento resistivo 120(1)-120(N) é acoplado a um nó de saída de tensão 124 do circuito de média de tensão 102. O acoplamento de cada nó de saída 122(1)-122(N) enquanto cada nó de entrada 118(1)-118(N) é acoplado a um nó de derivação de tensão correspondente 116(1)-116(N) gera a tensão média ( $V_{AVG}$ ) do circuito de carga distribuída 104 no nó de saída de tensão 124. Mais especificamente, a tensão média ( $V_{AVG}$ ) pode ser calculada utilizando uma resistência ( $R$ ) de cada elemento resistivo 120(1)-120(N) e uma tensão ( $V$ ) de cada nó de derivação de tensão 116(1)-116(N) por meio da seguinte equação:

$$V_{AVG} = (R(120(1)) || R(120(2)) || \dots R(120(N))) * (V(116(1))/R(120(1)) + V(116(2))/R(120(2)) + \dots V(116(N))/R(120(N)))$$

[0031] Desta forma, uma vez que a tensão em cada nó de carga de tensão 110(1)-110(N) pode variar em comparação com qualquer outro nó de carga de tensão 110(1)-110(N), a tensão média ( $V_{AVG}$ ) fornece uma medição mais precisa da tensão fornecida para todo o circuito de carga distribuída 104. Assim, a tensão média ( $V_{AVG}$ ) pode ser utilizada para calcular a corrente no circuito de carga distribuída 104 com mais precisão, em comparação com o cálculo da corrente utilizando uma tensão em somente um dos nós de carga de tensão 110(1)-110(N). Uma medição mais precisa da corrente pode melhorar as funções dentro de um sistema de controle correspondente que utiliza a medição de corrente para aumentar o desempenho do sistema.

[0032] Neste contexto, a Figura 2 ilustra um processo exemplar 200 empregado pelo circuito de rede de

tensão distribuída 100 na Figura 1 para calcular a tensão média ( $V_{AVG}$ ) do circuito de carga distribuída 104 através da média das tensões fornecidas para múltiplas áreas do circuito de carga distribuída 104. Com referência à figura 2, o componente de fonte de distribuição de tensão 106 distribui uma tensão fonte para a pluralidade de nós de carga de tensão 110(1)-110(N) através da rede de distribuição de fonte distribuída 112 (bloco 202). Em particular, a rede de distribuição de fonte distribuída 112 inclui a pluralidade de interconexões resistivas 114(1)-114(M) interconectando cada nó fonte 108(1)-108(N) a um nó de carga de tensão correspondente 110(1)-110(N). Devido a essas interconexões, cada nó de carga de tensão 110(1)-110(N) recebe a tensão fonte (bloco 204). O circuito de rede de tensão distribuída 100 determina uma tensão presente em cada nó de carga de tensão 110(1)-110(N) através de cada nó de derivação de tensão correspondente 116(1)-116(N) empregado dentro da rede de distribuição de fonte distribuída 112 (bloco 206). A tensão em cada nó de derivação de tensão 116(1)-116(N) é fornecida para o nó de entrada 118(1)-118(N) de cada elemento resistivo correspondente 120(1)-120(N) no circuito de média de tensão 102 (bloco 208). O circuito de média de tensão 102 fornece a tensão no nó de saída 122(1)-122(N) de cada elemento resistivo 120(1)-120(N) para o nó de saída de tensão 124, que é configurado para fornecer a tensão média ( $V_{AVG}$ ) em todos os nós de carga de tensão 110(1)-110(N) do circuito de carga distribuída 104 (bloco 210). A utilização do processo 200 permite que o circuito de rede de tensão distribuída 100 calcule a tensão média ( $V_{AVG}$ ), que pode ser utilizada para calcular a corrente no circuito de carga distribuída 104 com mais precisão, em comparação com o

cálculo da corrente utilizando uma tensão presente em apenas um dentre os nós de carga de tensão 110(1)-110(N).

[0033] Vários tipos de circuitos distribuídos semelhantes ao circuito de rede de tensão distribuída 100 na Figura 1 podem utilizar a tensão média ( $V_{AVG}$ ) como uma métrica valiosa. Como um exemplo não limitador, um circuito de rede de tensão distribuída semelhante ao circuito de rede de tensão distribuída 100 pode empregar transistores distribuídos, no qual uma rede de distribuição de fonte distribuída semelhante à rede de distribuição de fonte distribuída 112 inclui múltiplos transistores. Neste contexto, a Figura 3 ilustra um circuito de rede de tensão distribuída semicondutor de óxido metálico tipo n (NMOS) 300, em que uma rede de distribuição de fonte distribuída 302 emprega transistores NMOS 304(1)-304(N). Notavelmente, enquanto os transistores NMOS 304(1)-304(N) estão na rede de distribuição de fonte distribuída 302 neste aspecto, os transistores NMOS 304(1)-304(N) podem ser localizados em outros elementos em outros aspectos. Cada transistor NMOS 304(1)-304(N) é acoplado a um nó fonte 306(1)-306(N) correspondente de um componente de fonte de distribuição de tensão 308 através de um dreno 310(1)-310(N) correspondente. A rede de distribuição de fonte distribuída 302 inclui uma pluralidade de interconexões resistivas 312(1)-312(M) que, em conjunto com os transistores NMOS 304(1)-304(N), conectam cada nó fonte 306(1)-306(N) a um nó de carga de tensão correspondente 314(1)-314(N) de um circuito de carga distribuída 316. Particularmente, uma fonte 318(1)-318(N) de cada transistor NMOS 304(1)-304(N) correspondente se acopla ao nó de carga de tensão 314(1)-314(N) correspondente. Além disso, a tensão fornecida a uma porta 320 do circuito de rede de tensão distribuída NMOS 300 controla cada transistor NMOS 304(1)-304(N). Os nós de

derivação de tensão 322(1)-322(N) são empregados dentro da rede de distribuição de fonte distribuída 302 para acessar a tensão de cada fonte 318(1)-318(N) correspondente, e por extensão, cada nó de carga de tensão 314(1)-314(N).

[0034] Continuando com referência à Figura 3, para calcular a tensão média ( $V_{AVG}$ ) no circuito de carga distribuída 316, cada nó de derivação de tensão 322(1)-322(N) é acoplado a um nó de entrada 324(1)-324(N) de um resistor 326(1)-326(N) correspondente em um circuito de média de tensão 328. Um nó de saída 330(1)-330(N) de cada resistor 326(1)-326(N) é acoplado a um nó de saída de tensão 332 do circuito de média de tensão 328. O acoplamento de cada nó de saída 330(1)-330(N) enquanto cada nó de entrada 324(1)-324(N) é acoplado a um nó de derivação de tensão 322(1)-322(N) correspondente gera a tensão média ( $V_{AVG}$ ) do circuito de carga distribuída 316 em um nó de saída tensão 332. Como descrito anteriormente, a seguinte equação descreve a tensão média ( $V_{AVG}$ ) em termos da resistência  $R$  de cada resistor 326(1)-326(N) e da tensão  $V$  em cada nó de derivação de tensão 322(1)-322(N):

$$V_{AVG} = (R(326(1)) || R(326(2)) || \dots || R(326(N))) * (V(322(1))/R(326(1)) + V(322(2))/R(326(2)) + \dots + V(322(N))/R(326(N)))$$

[0035] Desta forma, a equação acima descreve a tensão média ( $V_{AVG}$ ) no nó de saída de tensão 332 quando a largura de porta de um ou mais transistores NMOS 304(1)-304(N) não é aproximadamente igual à largura de porta de todos os outros transistores NMOS 304(N)-304(N), bem como quando cada transistor NMOS 304(1)-304(N) tem uma largura de porta aproximadamente igual. Notavelmente, se a largura de porta de um ou mais transistores NMOS 304(1)-304(N) não é aproximadamente igual à largura de porta de todos os outros transistores NMOS 304(1)-304(N), cada resistor

326(1)-326(N) pode não ter uma resistência R aproximadamente igual. Em vez disso, cada resistor 326(1)-326(N) deve ter uma resistência R apropriada em relação à largura de porta do transistor NMOS 304(1)-304(N) correspondente para que a equação acima descrita calcule a tensão média ( $V_{AVG}$ ) com precisão. Além disso, se cada transistor NMOS 304(1)-304(N) tem uma largura de porta aproximadamente igual, cada resistor 326(1)-326(N) deve ter uma resistência R aproximadamente igual para calcular a tensão média ( $V_{AVG}$ ) com precisão. Em particular, se cada transistor NMOS 304(1)-304(n) tem uma largura de porta aproximadamente igual, e assim cada resistor 326(1)-326(n) tem uma resistência R aproximadamente igual, a equação descrita acima pode ser simplificada para a seguinte equação:

$$V_{AVG} = (1/N) * (V(322(1)) + V(322(2)) + \dots V(322(N)))$$

[0036] Continuando com referência à Figura 3, além dos resistores 326(1)-326(N), o circuito de média de tensão 328 também pode utilizar um resistor de escala (scaling resistor) 334. O resistor de escala 334 tem um nó de entrada 336 acoplado a uma fonte de aterramento 338, e um nó de saída 340 acoplado ao nó de saída 330(1)-330(N) de cada resistor 326(1)-326(N). Desta forma, o resistor de escala 334 pode ser utilizado para graduar a tensão média ( $V_{AVG}$ ) por um fator de escala correspondente à resistência do resistor de escala 334 em comparação com a tensão média ( $V_{AVG}$ ) gerada quando o resistor de escala 334 não é empregado. Se o resistor de escala 334 é ou não empregado no circuito de média de tensão 328, a tensão média ( $V_{AVG}$ ) pode ser utilizada para calcular a corrente no circuito de carga distribuída 316 com mais precisão, em comparação com o cálculo da corrente utilizando uma tensão em somente um

dos nós de carga de tensão 314(1)-314(N). Uma medição de corrente mais precisa pode melhorar as funções dentro de um sistema de controle correspondente que utilizam a medição de corrente para aumentar o desempenho do sistema.

[0037] Embora o circuito de rede de tensão distribuída NMOS 300 na Figura 3 empregue os transistores NMOS 304(1)-304(N) como elementos distribuídos na rede de distribuição de fonte distribuída 302, outros circuitos de rede distribuída tensão podem empregar tipos de transistor alternativos. Neste contexto, a Figura 4 ilustra um circuito de rede de tensão distribuída semicondutor de óxido metálico tipo p (PMOS) 400, em que uma rede de distribuição de fonte distribuída 402 emprega transistores PMOS 404(1)-404(N). Notavelmente, enquanto os transistores PMOS 404(1)-404(N) estão na rede de distribuição de fonte distribuída 402 neste aspecto, os transistores PMOS 404(1)-404(N) podem ser localizados em outros elementos em outros aspectos. Cada transistor PMOS 404(1)-404(N) é acoplado a um nó fonte correspondente 406(1)-406(N) de um componente de fonte de distribuição de tensão 408 através de uma fonte 410(1)-410(N) correspondente. De forma semelhante à rede de distribuição de fonte distribuída 302 na Figura 3, a rede de distribuição de fonte distribuída 402 emprega uma pluralidade de interconexões resistivas 412(1)-412(M) que, em conjunto com o transistor PMOS 404(1)-404(N), conecta cada nó fonte 406(1)-406(N) a um nó de carga de tensão correspondente 414(1)-414(N) de um circuito de carga distribuída 416. Particularmente, um dreno 418(1)-418(N) de cada transistor PMOS 404(1)-404(N) correspondente é acoplado ao nó de carga de tensão 414(1)-414(N) correspondente. Além disso, a tensão fornecida a uma porta 420 do circuito de rede de tensão distribuída PMOS 400 controla cada transistor PMOS 404(1)-404(N). Os nós de

derivação de tensão 422(1)-422(N) são empregados dentro da rede de distribuição de fonte distribuída 402 para acessar a tensão de cada dreno 418(1)-418(N) correspondente, e assim, cada nó de carga de tensão 414(1)-414(N).

[0038] Continuando com referência à figura 4, cada nó de derivação de tensão 422(1)-422(N) é acoplado a um nó de entrada 424(1)-424(N) de um resistor correspondente 426(1)-426(N) em um circuito de média de tensão 428. Um nó de saída 430(1)-430(N) de cada resistor 426(1)-426(N) é acoplado a um nó de saída de tensão 432 do circuito de média de tensão 428. Assim, o acoplamento de cada nó de saída 430(1)-430(N) enquanto cada nó de entrada 424(1)-424(N) é acoplado a um nó de derivação de tensão 422(1)-422(N) correspondente gera a tensão média ( $V_{AVG}$ ) do circuito de carga distribuída 416 no nó de saída tensão 432. Um resistor de escala 434 semelhante ao resistor de escala 334 na Figura 3 pode ser empregado no circuito de rede de tensão distribuída PMOS 400 para graduar a tensão média ( $V_{AVG}$ ). Além disso, as equações e as relações de largura de porta/resistência associadas descritas anteriormente em relação à Figura 3 também se aplicam para calcular a tensão média ( $V_{AVG}$ ) na Figura 4. Desta forma, a tensão média ( $V_{AVG}$ ) pode ser utilizada para calcular a corrente no circuito de carga distribuída 416 com mais precisão, em comparação com o cálculo da corrente utilizando uma tensão em somente um dentre os nós de carga de tensão 414(1)-414(N).

[0039] Adicionalmente à utilização da tensão média ( $V_{AVG}$ ) para calcular a corrente em um circuito de carga distribuída, a tensão média ( $V_{AVG}$ ) pode ser empregada para ajudar a regular a tensão fornecida a um circuito de carga distribuída, tal como os circuitos de carga distribuída 104, 316, e 416 descritos acima. A este

respeito, a Figura 5 ilustra um circuito de rede de tensão distribuída PMOS 500, em que a porta 420 do circuito de rede de tensão distribuída PMOS 400 na Figura 4 é acoplada a um circuito regulador de tensão 502. Em particular, uma tensão de referência  $V_{REF}$  é fornecida para uma primeira entrada 504 do circuito regulador de tensão 502, enquanto o nó de saída de tensão 432 do circuito de média de tensão 428 é acoplado a uma segunda entrada 506 do circuito regulador de tensão 502. Um nó de saída 508 do circuito regulador de tensão 502 é acoplado à porta 420 do circuito de rede de tensão distribuída PMOS 400. Os resistores 426(1)-426(N) amostram as tensões através do circuito de carga distribuída 416 conforme descrito anteriormente, fornecendo, assim a tensão média ( $V_{AVG}$ ) do circuito de carga distribuída 416 ao circuito regulador de tensão 502. O circuito regulador de tensão 502, que é um amplificador operacional ("op-amp") neste aspecto, força a tensão média ( $V_{AVG}$ ) fornecida ao circuito de carga distribuída 416 ser igual a  $V_{REF}$ . Em particular, ao fornecer a tensão média ( $V_{AVG}$ ) ao circuito regulador de tensão 502, o nó de saída 508 fornece uma tensão para a porta 420 de modo que a tensão fornecida para o circuito de carga distribuída 416 é regulada para  $V_{REF}$ . As tensões nos nós de carga de tensão 414(1)-414(n) podem variar dependendo de fatores como a resistência das interconexões resistivas 412(0)-412(M) e do tamanho físico e da disposição (layout) do circuito de carga distribuída 416. Assim, ao fornecer a tensão média ( $V_{AVG}$ ) ao circuito de regulador de tensão 502 dessa maneira, em vez de fornecer uma tensão em qualquer nó de carga de tensão 414(1)-414(N), ajuda-se a regular a tensão fornecida para o circuito de carga distribuída 416 de modo a refletir a distribuição de tensão de todo o circuito de carga distribuída 416.

[0040] Como descrito anteriormente, a tensão média ( $V_{AVG}$ ) pode ser utilizada para calcular a corrente com mais precisão em um circuito de carga distribuída. A este respeito, a Figura 6 ilustra um sistema de medição de corrente em pastilha 600 que proporciona um melhor desempenho quando se empregam circuitos de média de tensão semelhantes aos circuitos de média de tensão 102, 328, e 428 nas Figuras 1, 3 e 4, respectivamente. O sistema de medição de corrente em pastilha 600 é utilizado para medir uma corrente de fonte de alimentação (não mostrada) de um circuito de carga distribuída 602, em que o circuito de carga distribuída 602 pode ser, como exemplos não limitadores, um núcleo do processador ou uma memória cache. Para medir essa corrente, o sistema de medição de corrente em pastilha 600 inclui uma fonte de tensão ( $V_{dd}$ ) 604 que fornece uma tensão de entrada para uma fonte de cada transistor headswitch 606(1)-606(N). Os transistores headswitch 606(1)-606(N) fornecem controle de energia para o circuito de carga distribuída 602, permitindo que um sinal de tensão 608 alcance nós de carga de tensão 610(1)-610(N) correspondentes no circuito de carga distribuída 602. A fonte de tensão 604 também fornece uma tensão de entrada para uma fonte de cada transistor espelho 612(1)-612(N). Cada largura do transistor espelho 612(1)-612(N) é uma fração ( $f$ ) da largura do transistor headswitch 606(1)-606(N) correspondente. Os transistores headswitch 606(1)-606(N) e os transistores espelho 612(1)-612(N) são profundamente polarizados na região de triodo de transistor de efeito de campo (FET), efetivamente fazendo com que funcionem como resistores de baixo valor. Notavelmente, embora os transistores headswitch 606(1)-606(N) e os transistores espelho 612(1)-612(N) sejam empregados como transistores PMOS neste aspecto, outros aspectos podem

empregar os transistores headswitch 606(1)-606(N) e os transistores espelho 612(1)-612(N) como transistores NMOS. Além disso, uma tensão fornecida por cada transistor espelho 612(1)-612(N) percorre um transistor cascode correspondente 614(1)-614(N) em um resistor de sentido 616. Uma tensão a partir do resistor de sentido 616 é fornecida para um conversor analógico digital (ADC) 618, que converte a tensão em um fluxo de dados digitais 620 que representa a corrente de fonte de alimentação do circuito de carga distribuída 602.

[0041] Continuando com referência à Figura 6, para que o sistema de medição de corrente em pastilha 600 funcione corretamente, os transistores headswitch 606(1)-606(N) e os transistores espelho 612(1)-612(N) precisam ter as tensões dreno-fonte precisamente iguais. Desta forma, um op-amp 622, juntamente com os transistores cascode 614(1)-614(N), força a tensão dreno fonte dos transistores espelho 612(1)-612(N) a ser igual a dos transistores headswitch 606(1)-606(N). Mais especificamente, o op-amp 622 controla os transistores cascode 614(1)-614(N) a fim de manter a corrente nos transistores espelho 612(1)-612(N) igual a uma fração (f) da corrente nos transistores headswitch 606(1)-606(N). Fazendo isto, as tensões dreno fonte dos transistores espelho 612(1)-612(N) e dos transistores headswitch 606(1)-606(N) são mantidas iguais umas as outras. Notavelmente, este aspecto ilustra os transistores headswitch 606(1)-606(N), os transistores espelho 612(1)-612(N) e os transistores cascode 614(1)-614(N) como transistores PMOS na Figura 6, mas outros aspectos podem empregar outros tipos de transistores para obter funcionalidade semelhante.

[0042] Continuando com referência à Figura 6, os transistores headswitch 606(1)-606(N) são distribuídos

de modo a se acoplarem ao circuito de carga distribuída 602 nos nós de carga de tensão 610(1)-610(N) correspondentes através de interconexões resistivas headswitch (não mostradas) dentro de uma rede de distribuição de fonte distribuída (não mostrada). Assim, um circuito de média de tensão headswitch 624 é empregado para fornecer uma tensão headswitch média ( $V_{HSAVG}$ ) (não mostrada) para uma primeira entrada 626 do op-amp 622 por meio de um nó de saída de tensão headswitch 628. De forma semelhante, cada um dentre os transistores espelho 612(1)-612(N) se acoplada ao transistor cascode correspondente 614(1)-614(N) através de interconexões resistivas espelho (não mostradas) dentro da rede de distribuição de fonte distribuída. Assim, um circuito de média de tensão espelho 630 é empregado para fornecer uma tensão espelho média ( $V_{MRAVG}$ ) (não mostrada) para uma segunda entrada 632 do op-amp 622 por meio de um nó de saída de tensão espelho 634. Tanto o circuito de média de tensão headswitch 624 quanto o circuito de média de tensão espelho 630 incluem elementos semelhantes aos circuitos de média de tensão 102, 328 e 428 nas Figuras 1, 3 e 4, respectivamente. Em particular, os resistores 636(1)-636(N) no circuito de média de tensão headswitch 624 se acoplam a um nó de derivação de tensão headswitch 638(1)-638(N) correspondente dentro da rede de distribuição de fonte distribuída e são configurados para fornecer a tensão headswitch média ( $V_{HSAVG}$ ) para a primeira entrada 626 do op-amp 622. Os resistores 640(1)-640(N) no circuito de média de tensão espelho 630 se acoplam aos nós de derivação de tensão espelho 642(1)-642(N) correspondentes dentro da rede distribuição de fonte distribuída, e são configurados para fornecer a tensão espelho média ( $V_{MRAVG}$ ) para a segunda entrada 632 do op-amp 622. Ao fornecer a tensão headswitch média ( $V_{HSAVG}$ ) e a tensão espelho média ( $V_{MRAVG}$ ) para o op-amp

622 desta forma, o resistor de sentido 616 recebe uma tensão a partir da qual calcula a corrente no circuito de carga distribuída 602 com mais precisão, em comparação com o cálculo da corrente utilizando uma tensão de um dentre os nós de carga de tensão 610(1)-610(N).

[0043] Continuando com referência à Figura 6, cada um entre o circuito de média de tensão headswitch 624 e o circuito de média de tensão espelho 630 pode empregar um resistor adicional para graduar a tensão headswitch média ( $V_{HSAVG}$ ) e a tensão espelho média ( $V_{MRAVG}$ ), respectivamente, se desejado. Mais especificamente, o circuito de média de tensão headswitch 624 pode empregar um resistor de escala 644, semelhante ao resistor de escala 334 na Figura 3. Desta forma, o resistor de escala 644 pode ser usado para graduar a tensão headswitch média ( $V_{HSAVG}$ ) por um fator de escala correspondente à resistência do resistor de escala 644 em comparação com a tensão headswitch média ( $V_{HSAVG}$ ) gerada quando o resistor de escala 644 não é empregado. O circuito de média de tensão espelho 630 pode empregar um resistor de escala 646 de uma maneira semelhante ao circuito de média de tensão headswitch 624 para graduar a tensão espelho média ( $V_{MRAVG}$ ).

[0044] Adicionalmente à medição de corrente do circuito de carga distribuída 602, o sistema de medição de corrente em pastilha 600 pode também ser configurado para regular a tensão de carga e a corrente fornecida ao circuito de carga distribuída 602. A este respeito, um circuito regulador de tensão 648 que é configurado para regular a tensão e, portanto, a corrente, fornecida sobre o circuito de carga distribuída 602 pode ser empregado no sistema de medição de corrente em pastilha 600. O circuito regulador de tensão 648 é configurado para operar de forma semelhante ao circuito regulador de tensão 502 na Figura 5.

Desta forma, ao receber a tensão de referência  $V_{REF}$  e a tensão headswitch média ( $V_{HSAVG}$ ), o circuito regulador de tensão 648 fornece uma tensão ao circuito de carga distribuída 602 que é aproximadamente igual à tensão de referência  $V_{REF}$ . Regular a tensão de carga fornecida para o circuito de carga distribuída 602 desta maneira pode ajudar a garantir que a tensão de carga do circuito de carga distribuída 602 seja mantida aproximadamente em um nível desejado.

[0045] Para ilustrar as medições tensão e de corrente mais precisas que podem ser realizadas empregando os circuitos de média de tensão 102, 328 e 428 nas Figuras 1, 3 e 4, respectivamente e o circuito de média de tensão headswitch 624 e o circuito de média de tensão espelho 630 na Figura 6, circuitos de teste podem ser utilizados para gerar dados de amostra. A este respeito, a Figura 7A ilustra um primeiro circuito de teste 700 que emprega ladrilhos headswitch 702(1)-702(48). Um resistor 704(1)-704(48) é acoplado a um transistor headswitch 706(1)-706(48) correspondente para gerar uma tensão headswitch de teste média ( $V_{THSAVG}$ ) de forma semelhante ao circuito de média de tensão headswitch 624 na Figura 6. Além disso, um resistor 708(1)-708(48) é acoplado a um transistor espelho 710(1)-710(48) correspondente para gerar uma tensão espelho de teste média ( $V_{TMRAVG}$ ) de forma semelhante ao circuito de média de tensão espelho 630 na Figura 6. Uma pluralidade de resistores parasitas 712(1)(1)-712(48)(4) são incluídos no primeiro circuito de teste 700 para simular a resistência de interconexão. Um transistor cascode 714(1)-714(48) correspondente a cada transistor espelho 710(1)-710(48) é também incluído em cada ladrilho headswitch 702(1)-702(48). Desta maneira, as correntes dos transistores cascode

714(1)-714(48) são somadas e fornecidas a um resistor de sentido 716'.

[0046] Adicionalmente, a Figura 7B ilustra um segundo circuito de teste 700' que emprega ladrilho headswitch 702'(1)-702'(48). Cada ladrilho headswitch 702'(1)-702'(48) inclui um transistor headswitch 706(1)-706(48) correspondente e um transistor espelho 710(1)-710(48) correspondente similar ao primeiro circuito de teste 700 na figura 7A. A pluralidade de resistores parasitas 712(1)(1)-712(48)(4), bem como a de transistores cascode 714(1)-714(48), estão também incluídos no segundo circuito de teste 700'. No entanto, os ladrilhos headswitch 702'(1)-702'(48) não incluem resistores 704(1)-704(48) e 708(1)-708(48) acoplados aos transistores headswitch 706(1)-706(48) e transistores espelho 710(1)-710(48) correspondentes, respectivamente, como no primeiro circuito de teste 700 na figura 7A. Desta forma, o segundo circuito de teste 700' não gera uma tensão headswitch de teste média ( $V_{THSAVG}$ ) e uma tensão espelho de teste média ( $V_{TMRAVG}$ ). Pelo contrário, uma tensão headswitch ( $V_{HS}$ ) e uma tensão espelho ( $V_{MR}$ ) são medidas no ladrilho headswitch 702'(48). As correntes a partir dos transistores cascode 714(1)-714(48) são somadas e fornecidas a um resistor de sentido 716'.

[0047] A este respeito, a Figura 8A ilustra um conjunto exemplar de sinais 800 correspondente à corrente média medida através do primeiro e do segundo circuitos de teste 700, 700' nas figuras 7A e 7B com interconexões metálicas não resistivas ideais. Particularmente, cada resistor parasita 712(1)(1)-712(48)(4) tem uma resistência igual a zero Ohms ( $0 \Omega$ ) a fim de remover qualquer efeito que as resistências parasitas 712(1)(1)-712(48)(4) possam ter sobre a tensão distribuída. Além disso, cada resistor de sentido 716, 716' tem uma resistência igual a 300 Ohms

( $\Omega$ ). Uma tensão ( $V_{SENSE1}$ ) através do resistor de sentido 716 e uma tensão ( $V_{SENSE2}$ ) através do resistor de sentido 716', são ambas ilustradas em um primeiro gráfico 802. Notavelmente, a tensão ( $V_{SENSE1}$ ) e a tensão  $V_{SENSE2}$  são aproximadamente iguais em múltiplos valores de corrente. Por exemplo, em uma corrente máxima de 1,5 A, conforme indicado pela seta 804, ambas ( $V_{SENSE1}$ ) e ( $V_{SENSE2}$ ) são aproximadamente iguais a 374 mV. Isto é evidenciado em um segundo gráfico 806 que ilustra a diferença de valores entre ( $V_{SENSE1}$ ) e ( $V_{SENSE2}$ ). Mais especificamente, a máxima diferença existente entre ( $V_{SENSE1}$ ) e ( $V_{SENSE2}$ ) ocorre em 1,5 A, em que a diferença é aproximadamente de somente 160  $\mu$ V (micro Volts), conforme indicado pela seta 808. Assim, com os efeitos dos resistores parasitas 712(1)(1)-712(48)(4) efetivamente removidos, o primeiro circuito de teste 700 e o segundo circuito de teste 700' geram uma tensão próxima da tensão eficazmente ideal através dos respectivos resistores de sentido 716, 716' de aproximadamente 374 mV.

[0048] A este respeito, a Figura 8B ilustra um conjunto exemplar de sinais 800' correspondente à corrente média medida através do primeiro e do segundo circuitos de teste 700, 700' nas Figuras 7A e 7B com interconexões metálicas resistivas não ideais. Particularmente, cada resistor parasita 712(1)(1)-712(48)(4) tem uma resistência Ohm não zero neste aspecto. A tensão ( $V_{SENSE1}$ ) e a tensão ( $V_{SENSE2}$ ) são ambas ilustradas em um primeiro gráfico 802'. Notavelmente, os valores de ( $V_{SENSE1}$ ) e ( $V_{SENSE2}$ ) não são iguais em níveis de corrente variáveis, como na figura 8A. Por exemplo, em uma corrente de 1,5 A, ( $V_{SENSE1}$ ) tem um valor aproximadamente igual a 374 mV, conforme indicado pela seta 810, que é o mesmo valor de ( $V_{SENSE1}$ ) no caso ideal descrito na figura 8A. No entanto, em uma corrente de 1,5 A, ( $V_{SENSE2}$ ) tem um valor aproximadamente igual a 63 mV, conforme

indicado pela seta 812. Esta diferença de valores é ilustrada ainda em um segundo gráfico 806', que mostra que a diferença máxima existente entre ( $V_{SENSE1}$ ) e ( $V_{SENSE2}$ ) ocorre novamente em 1,5 A, em que a diferença é de aproximadamente 311 mV, conforme indicado pela seta 814. Utilizando fatores de escala nominais, um valor de 63 mV para ( $V_{SENSE2}$ ) representa uma corrente "medida" de 252 mA, em comparação com a corrente real de 1,5 A.

[0049] A este respeito, comparar o caso ideal ilustrado na Figura 8A com o caso mais realista ilustrado na figura 8B demonstra que empregar média de tensão no primeiro circuito de teste 700 elimina essencialmente as variações de tensão e de corrente medidas com base em perfis de distribuição de corrente variáveis através de um circuito de carga. Mais especificamente, sob as condições realistas na Figura 8B, o segundo circuito de teste 700' fornece uma tensão e uma corrente que são muito abaixo daquelas geradas sob as condições ideais na Figura 8A. No entanto, sob as condições realistas na Figura 8B, o primeiro circuito de teste 700 gera uma tensão e uma corrente que são aproximadamente iguais àquelas geradas sob as condições ideais na Figura 8A. Em outras palavras, o primeiro circuito de teste 700 mede a tensão média, enquanto o segundo circuito de teste 700' mede uma tensão em um único nó de carga de tensão. Deste modo, o primeiro circuito de teste 700 fornece uma medição de tensão média consistente, enquanto o segundo circuito de teste 700' fornece tensões variáveis dependendo do nó de carga de tensão em que a tensão é medida. Por conseguinte, empregar média de tensão conforme descrito neste documento pode ser utilizado para calcular a corrente em um circuito de carga distribuída com mais precisão, em comparação com o cálculo

de corrente utilizando uma tensão presente em um único nó de carga de tensão.

[0050] Neste contexto, a Figura 9 ilustra um sistema 900 em que circuitos headswitch 902(1), 902(2) são distribuídos em torno de um núcleo do processador 904 de modo a medir a tensão de carga média do núcleo do processador 904. Cada circuito headswitch 902(1), 902(2) inclui uma pluralidade de ladrilhos headswitch semelhantes aos ladrilhos headswitch 702 na figura 7A. O núcleo do processador 904 inclui uma pluralidade de circuitos digitais, cada um deles pode estar ativo em tempos variáveis. Como os vários circuitos digitais dentro do núcleo do processador 904 podem estar ativos em tempos variáveis, a distribuição de tensão e de corrente em todo o núcleo do processador 904 e nos circuitos headswitch 902(1), 902(2) pode variar drasticamente ao longo do tempo. O mecanismo de média tensão incluído nos circuitos headswitch 902(1), 902(2), conforme descrito nas figuras anteriores e, particularmente na Figura 7A, mede a tensão de núcleo média ( $V_{C_{AVG}}$ ) distribuída no núcleo do processador 904. Por conseguinte, a tensão de núcleo média ( $V_{C_{AVG}}$ ) pode ser utilizada para calcular a corrente distribuída no núcleo do processador 904 com mais precisão, em comparação com o cálculo da corrente utilizando uma tensão em apenas um local em um único ponto no tempo.

[0051] Os circuitos de rede de tensão distribuída empregando média de tensão de acordo com aspectos descritos neste documento podem ser fornecidos ou integrados a qualquer dispositivo baseado em processador. Exemplos, sem limitação, incluem um set-top box, uma unidade de entretenimento, um dispositivo de navegação, um dispositivo de comunicação, uma unidade de dados de localização fixa, uma unidade de dados de localização

móvel, um telefone móvel, telefone celular, um computador, um computador portátil, um computador desktop, um assistente digital pessoal (PDA), um monitor, um monitor de computador, uma televisão, um sintonizador, um rádio, um rádio via satélite, um reproduutor de música, um reproduutor de música digital, um reproduutor de música portátil, um reproduutor de vídeo digital, um reproduutor de vídeo, um reproduutor de disco de vídeo digital (DVD) e um reproduutor de vídeo digital portátil.

[0052] Neste contexto, a Figura 10 ilustra um exemplo de um sistema baseado em processador 1000 que pode empregar os circuitos de média de tensão 102, 328 e 428 ilustrados nas figuras 1, 3 e 4, respectivamente. Neste exemplo, o sistema baseado em processador 1000 inclui uma ou mais unidades de processamento central (CPUs) 1002, cada uma, incluindo um ou mais processadores 1004. Cada um dentre os um ou mais processadores 1004 pode empregar uma pluralidade de núcleos 1006(0)-1006(N), em que a tensão de carga média e a corrente de carga de cada núcleo 1006(0)-1006(N) podem ser calculadas utilizando um circuito de média de tensão 102(0)-102(N), 328(0)-328(N) ou 428(0)-428(N). A(s) CPU(s) 1002 pode(m) ser um dispositivo mestre. A(s) CPU(s) 1002 pode(m) ter uma memória cache 1008 acoplada ao(s) processador(es) 1004 para acesso rápido aos dados armazenados temporariamente. A(s) CPU(s) 1002 é(são) acoplada(s) a um barramento de sistema 1010 e pode(m) interacoplar dispositivos mestre e escravo incluídos no sistema baseado em processador 1000. Como é bem conhecido, a(s) CPU(s) 1002 comunica(m)-se com esses outros dispositivos através do intercâmbio de informações de endereço, controle e dados sobre o barramento de sistema de 1010. Por exemplo, a(s) CPU(s) 1002 pode(m) comunicar as

solicitações de transação de barramento para um controlador de memória 1012 como um exemplo de um dispositivo escravo. Embora não ilustrado na Figura 10, múltiplos sistemas de barramento 1010 poderiam ser fornecidos, em que cada sistema de barramento 1010 constitui uma estrutura (fabric) diferente.

[0053] Outros dispositivos mestre e escravo podem ser conectados ao sistema de barramento 1010. Conforme ilustrado na Figura 10, esses dispositivos podem incluir um sistema de memória 1014, um ou mais dispositivos de entrada 1016, um ou mais dispositivos de saída 1018, um ou mais dispositivos de interface de rede 1020 e um ou mais controladores de exibição 1022, como exemplos. O(s) dispositivo(s) de entrada 1016 pode(m) incluir qualquer tipo de dispositivo de entrada, incluindo, mas não ficando limitado, a chaves de entrada, interruptores, processadores de voz, etc. O(s) dispositivo(s) de saída 1018 pode(m) incluir qualquer tipo de dispositivo de saída, incluindo, mas não ficando limitado, a áudio, vídeo, outros indicadores visuais, etc. O(s) dispositivo(s) de interface de rede 1020 pode(m) ser qualquer dispositivo configurado para permitir a troca de dados a partir de e para uma rede 1024. A rede 1024 pode ser qualquer tipo de rede, incluindo mas não ficando limitado a uma rede cabeada ou sem fio, uma rede pública ou privada, uma rede de área local (LAN), uma rede de área local ampla (WLAN), e a Internet. O(s) dispositivo(s) de interface de rede 1020 pode(m) ser configurado(s) para suportar qualquer tipo de protocolo de comunicação desejado. O sistema de memória 1014 pode compreender uma ou mais unidades de memória 1026(0)-1026(N).

[0054] A(s) CPU(s) 1002 pode(m) também ser configurada(s) para acessar o(s) controlador(es) de

exibição 1022 sobre o sistema de barramento 1010 para controlar informações enviadas para uma ou mais telas 1028. O(s) controlador(es) de exibição 1022 envia(m) informações para a(s) tela(s) 1028 para serem exibidas através de um ou mais processadores de vídeo 1030, que processam a informação a ser exibida em um formato apropriado para a(s) tela(s) 1028. A(s) tela(s) 1028 pode incluir qualquer tipo de tela, incluindo mas não ficando limitado a um tubo de raios catódicos (CRT), uma tela de cristal líquido (LCD), uma tela de plasma, etc.

[0055] Aqueles versados na técnica apreciarão ainda que vários blocos lógicos, módulos, circuitos e algoritmos ilustrativos descritos em relação aos aspectos descritos neste documento podem ser implementados como hardware eletrônico, instruções armazenadas em memória ou em outro meio legível por computador e executados por um processador ou outro dispositivo de processamento, ou pela combinações de ambos. Os dispositivos mestre e escravo aqui descritos podem ser empregados em qualquer circuito, componente de hardware, circuito integrado (IC) ou chip IC, como exemplos. A memória descrita neste documento pode ser de qualquer tipo e tamanho e pode ser configurada para armazenar qualquer tipo de informação desejada. Para ilustrar com mais clareza essa intercambialidade, vários componentes, blocos, módulos, circuitos, e etapas ilustrativas foram descritos acima geralmente em termos de sua funcionalidade. Como essa funcionalidade é implementada depende da aplicação específica, opções de projeto, e/ou restrições de projeto, impostas sobre o sistema como um todo. Os versados na técnica podem implementar a funcionalidade descrita em maneiras diferentes para cada aplicação particular, mas essas decisões de implementação

não devem ser interpretadas como um afastamento do escopo da presente descrição.

[0056] Os vários blocos lógicos, módulos e circuitos ilustrativos descritos em relação aos aspectos descritos neste documento podem ser implementados ou realizados com um processador, um Processador de Sinal Digital (DSP), um Circuito Integrado de Aplicação Específica (ASIC), um Arranjo de Portas Programável em Campo (FPGA) ou outro dispositivo de lógica programável, porta discreta ou transistor lógico, componentes de hardware distintos ou qualquer combinação dos mesmos projetada para realizar as funções descritas neste documento. Um processador pode ser um microprocessador, mas alternativamente, o processador pode ser qualquer processador convencional, controlador, microcontrolador ou máquina de estado. Um processador também pode ser implementado como uma combinação de dispositivos de computação, por exemplo, uma combinação de um DSP e um microprocessador, uma pluralidade de microprocessadores, um ou mais microprocessadores em conjunto com um núcleo DSP, ou qualquer outra configuração.

[0057] Os aspectos descritos neste documento podem ser incorporados em hardware e nas instruções que são armazenadas em hardware, e podem residir, por exemplo, em Memória de Acesso Aleatório (RAM), Memória Flash, Memória Somente de Leitura (ROM), ROM Eletricamente Programável (EPROM), ROM Programável e Apagável Eletricamente (EEPROM), registros, um disco rígido, um disco removível, um CD-ROM ou qualquer outra forma de meio legível por computador conhecida na técnica. Um meio de armazenamento exemplar é acoplado ao processador de tal modo que o processador possa ler informação a partir de, e escrever informação no meio de armazenamento. Como alternativa, o meio de armazenamento

pode ser parte integrante do processador. O processador e o meio de armazenamento podem residir em um ASIC. O ASIC pode residir em uma estação remota. Como alternativa, o processador e o meio de armazenamento podem residir como componentes discretos em um servidor, em uma estação base ou em uma estação remota.

[0058] Deve também ser notado que as etapas operacionais descritas em qualquer dentre os aspectos exemplares neste documento são descritas para fornecer exemplos e discussão. As operações descritas podem ser realizadas em numerosas sequências diferentes das sequências ilustradas. Além disso, as operações descritas em uma única etapa operacional na verdade podem ser realizadas em várias etapas diferentes. Adicionalmente, podem ser combinadas uma ou mais etapas operacionais discutidas nos aspectos exemplares. É para ser entendido que as etapas operacionais ilustradas nos fluxogramas podem estar sujeitas a inúmeras diferentes modificações como ficará facilmente evidente para aqueles versados na técnica. Os versados na técnica também entenderão que informações e sinais podem ser representados utilizando qualquer uma dentre uma variedade de diferentes tecnologias e técnicas. Por exemplo, dados, instruções, comandos, informações, sinais, bits, símbolos e chips que podem ser referenciados em toda a descrição acima podem ser representados por tensões, correntes, ondas eletromagnéticas, campos ou partículas magnéticos, campos ou partículas ópticos ou qualquer combinação dos mesmos.

[0059] A descrição anterior da revelação é fornecida para permitir a qualquer pessoa versada na técnica fabricar ou utilizar a descrição. Várias modificações à descrição ficarão prontamente evidentes para aqueles versados na técnica, e os princípios genéricos

definidos neste documento podem ser aplicados a outras variações sem se afastar do espírito e do escopo da descrição. Deste modo, a descrição não se destina a ser limitada aos exemplos e aos projetos aqui descritos, mas deve ser concedido o mais amplo escopo consistente com os princípios e características inovadoras descritos neste documento.

## REIVINDICAÇÕES

1. Circuito de rede de tensão distribuída (300, 400), **caracterizado** pelo fato de que compreende:

um componente de fonte de distribuição de tensão (308, 408) compreendendo uma pluralidade de nós fonte (306, 406);

um circuito de carga distribuída (316, 416) compreendendo uma pluralidade de nós de carga de tensão (314, 414);

uma rede de distribuição de fonte distribuída (302, 402), compreendendo:

uma pluralidade de interconexões resistivas (312, 412) interconectando cada nó fonte dentre a pluralidade de nós fonte a um nó de carga de tensão correspondente dentre a pluralidade de nós de carga de tensão;

uma pluralidade de transistores (304, 404), cada transistor dentre a pluralidade de transistores correspondendo a um nó fonte dentre a pluralidade de nós fonte e a um nó de carga de tensão dentre a pluralidade de nós de carga de tensão; e

uma pluralidade de nós de derivação de tensão (322, 422), em que um único nó de derivação de tensão corresponde a cada nó de carga de tensão dentre a pluralidade de nós de carga de tensão; e

um circuito de média de tensão (328, 428), compreendendo:

uma pluralidade de elementos resistivos (326, 426), cada elemento resistivo dentre a pluralidade de elementos resistivos compreendendo:

um nó de entrada (324, 424) acoplado a um nó de derivação de tensão correspondente dentre a pluralidade de nós de derivação de tensão; e

um nó de saída (330, 430);

em que cada elemento resistivo possui uma resistência baseada na largura de porta do transistor correspondente ao nó de carga de tensão do nó de derivação de tensão correspondente; e

um nó de saída de tensão (332, 432) acoplado ao nó de saída de cada elemento resistivo dentre a pluralidade de elementos resistivos, o nó de saída de tensão configurado para fornecer uma tensão média do circuito de carga distribuída.

2. Circuito de rede de tensão distribuída, de acordo com a reivindicação 1, caracterizado pelo fato de que o circuito de média de tensão compreende adicionalmente:

um resistor de escala (334, 434) acoplado entre uma fonte de aterramento e o nó de saída de cada elemento resistivo dentre a pluralidade de elementos resistivos;

o resistor de escala configurado para graduar a tensão média no nó de saída de tensão.

3. Circuito de rede de tensão distribuída, de acordo com a reivindicação 1, caracterizado pelo fato de que cada transistor dentre a pluralidade de transistores possui uma largura de porta aproximadamente igual.

4. Circuito de rede de tensão distribuída, de acordo com a reivindicação 3, caracterizado pelo fato de que cada elemento resistivo dentre a pluralidade de elementos resistivos no circuito de média de tensão possui uma resistência aproximadamente igual.

5. Circuito de rede de tensão distribuída, de acordo com a reivindicação 1, caracterizado pelo fato de que pelo menos dois transistores dentre a pluralidade de transistores possuem larguras de porta diferentes.

6. Circuito de rede de tensão distribuída, de acordo com a reivindicação 1, caracterizado pelo fato de que cada transistor dentre a pluralidade de transistores compreende um transistor semicondutor tipo n de óxido metálico, NMOS.

7. Circuito de rede de tensão distribuída, de acordo com a reivindicação 1, caracterizado pelo fato de que cada transistor dentre a pluralidade de transistores compreende um transistor semicondutor tipo p de óxido metálico, PMOS.

8. Circuito de rede de tensão distribuída, de acordo com a reivindicação 1, caracterizado pelo fato de que compreende adicionalmente um circuito regulador de tensão (502) configurado para regular uma tensão fornecida ao circuito de carga distribuída, o circuito regulador de tensão compreendendo:

uma primeira entrada (504) acoplada a uma fonte de tensão de referência;

uma segunda entrada (506) acoplada ao nó de saída de tensão (432) do circuito de média de tensão; e

uma saída (508) acoplada à rede de distribuição de fonte distribuída.

9. Método (200) para calcular uma tensão média de um circuito de carga distribuída, caracterizado pelo fato de que compreende:

distribuir (202) uma tensão fonte para uma pluralidade de nós de carga de tensão do circuito de carga distribuída através de uma rede de distribuição de fonte distribuída, em que a rede de distribuição de fonte distribuída compreende uma pluralidade de interconexões resistivas interconectando cada nó fonte dentre uma pluralidade de nós fonte a um nó de carga de tensão correspondente dentre a pluralidade de nós de carga de

tensão e a uma pluralidade de transistores, cada transistor dentre uma pluralidade de transistores correspondendo a um nó fonte dentre uma pluralidade de nós fonte e a um nó de carga de tensão dentre a pluralidade de nós de carga de tensão;

receber (204) a tensão fonte na pluralidade de nós de carga de tensão;

determinar (206) uma tensão presente em cada nó de carga de tensão dentre a pluralidade de nós de carga de tensão através de um nó de derivação de tensão correspondente dentre uma pluralidade de nós de derivação de tensão, em que um único nó de derivação de tensão corresponde a cada nó de carga de tensão dentre a pluralidade de nós de carga de tensão;

fornecer (208) a tensão presente em cada nó de derivação de tensão dentre a pluralidade de nós de derivação de tensão para um elemento resistivo correspondente dentre uma pluralidade de elementos resistivos, cada elemento resistivo possuindo uma resistência com base na largura de porta do transistor correspondendo ao nó de carga de tensão do nó de derivação de tensão correspondendo; e

fornecer (210) uma tensão de saída de cada elemento resistivo dentre a pluralidade de elementos resistivos para um nó de saída de tensão configurado para fornecer a tensão média do circuito de carga distribuída.

10. Sistema de medição de corrente na pastilha (600) **caracterizado** pelo fato de que compreende um circuito de rede de tensão distribuída, conforme definido em qualquer uma das reivindicações 2 a 10, o sistema compreendendo adicionalmente:

uma fonte de tensão (604);

uma pluralidade de transistores cascode (614);

uma pluralidade de transistores headswitch (606), em que cada transistor headswitch dentre a pluralidade de transistores headswitch é acoplado à fonte de tensão;

uma pluralidade de transistores espelho (612), em que cada transistor espelho dentre a pluralidade de transistores espelho é acoplado à fonte de tensão; e

em que a rede de distribuição de fonte distribuída compreende:

uma pluralidade de interconexões resistivas headswitch (636) interconectando cada transistor headswitch dentre a pluralidade de transistores headswitch a um nó de carga de tensão correspondente (610) dentre a pluralidade de nós de carga de tensão;

uma pluralidade de interconexões resistivas espelho (640) interconectando cada transistor espelho dentre a pluralidade de transistores espelho a uma fonte de um transistor cascode correspondente dentre a pluralidade de transistores cascode;

uma pluralidade de nós de derivação de tensão headswitch (638), em que cada nó de derivação de tensão headswitch corresponde a um nó de carga de tensão dentre a pluralidade de nós de carga de tensão; e

uma pluralidade de nós de derivação de tensão espelho (640), em que cada nó de derivação de tensão espelho corresponde a um transistor cascode dentre a pluralidade de transistores cascode; e

em que o circuito de média de tensão é um circuito de média de tensão headswitch (624), compreendendo:

uma pluralidade de resistores (636), cada resistor dentre a pluralidade de resistores compreendendo:

um nó de entrada acoplado a um nó de derivação de tensão headswitch correspondente dentre a pluralidade de nós de derivação de tensão headswitch; e

um nó de saída; e

um nó de saída de tensão headswitch (628) acoplado ao nó de saída de cada resistor, o nó de saída de tensão headswitch configurado para fornecer uma tensão headswitch média presente no circuito de carga distribuída; e

compreendendo adicionalmente um circuito de média de tensão espelho (630), compreendendo:

uma pluralidade de resistores (640), cada resistor dentre a pluralidade de resistores compreendendo:

um nó de entrada (642) acoplado a um transistor espelho correspondente dentre a pluralidade de transistores espelho; e

um nó de saída; e

um nó de saída de tensão espelho (634) acoplado ao nó de saída de cada resistor, o nó de saída de tensão espelho configurado para fornecer uma tensão espelho média presente na pluralidade de transistores cascode;

um dreno de cada transistor cascode dentre a pluralidade de transistores cascode acoplado a um resistor de sentido (616);

o resistor de sentido configurado para fornecer uma tensão para um conversor analógico/digital (ADC) (618);

o ADC configurado para converter a tensão do resistor de sentido em um sinal digital (620) representativo de uma corrente de fonte de alimentação do circuito de carga distribuída; e

um amplificador operacional (622), compreendendo:

uma primeira entrada de amplificador operacional (626) acoplada ao nó de saída de tensão headswitch;

uma segunda entrada de amplificador operacional (632) acoplada ao nó de saída da tensão espelho; e

um nó de saída de amplificador operacional acoplado a uma porta correspondente à pluralidade de transistores cascode.

11. Sistema de medição de corrente na pastilha, de acordo com a reivindicação 10, **caracterizado** pelo fato de que o circuito de média de tensão headswitch comprehende adicionalmente:

um resistor de escala (644) acoplado entre uma fonte de aterramento e o nó de saída de cada resistor dentre a pluralidade de resistores no circuito de média de tensão headswitch;

o resistor de escala configurado para graduar a tensão headswitch média no nó de saída de tensão headswitch.

12. Sistema de medição de corrente na pastilha, de acordo com a reivindicação 10, **caracterizado** pelo fato de que comprehende adicionalmente um circuito regulador de tensão (648) configurado para regular uma tensão fornecida para o circuito de carga distribuída, o circuito regulador de tensão comprehendendo:

uma primeira entrada de regulador de tensão acoplada a uma fonte de tensão de referência;

uma segunda entrada de regulador de tensão acoplada ao nó de saída de tensão headswitch do circuito de média de tensão headswitch; e

uma saída de regulador de tensão acoplada a uma porta de cada transistor headswitch dentre a pluralidade de

transistores headswitch e uma porta de cada transistor espelho dentre a pluralidade de transistores espelho.

**FIG. 1**

**FIG. 2**

FIG. 3

**FIG. 4**

FIG. 5

**FIG. 6**

FIG. 7A

FIG. 7B

**FIG. 9**

**FIG. 10**