(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2009-94457

(P2009-94457A)

(43) 公開日 平成21年4月30日(2009.4.30)

(51) Int.Cl.

H01L 25/00 (2006.01)

F 1

H01L 25/00

テーマコード (参考)

A

審査請求 未請求 請求項の数 11 O L (全 13 頁)

(21) 出願番号 特願2008-91636 (P2008-91636)

(22) 出願日 平成20年3月31日 (2008.3.31)

(31) 優先権主張番号 特願2007-240785 (P2007-240785)

(32) 優先日 平成19年9月18日 (2007.9.18)

(33) 優先権主張国 日本国 (JP)

(71) 出願人 000000376

オリンパス株式会社

東京都渋谷区幡ヶ谷2丁目43番2号

(74) 代理人 100123962

弁理士 斎藤 圭介

中村 幹夫

東京都渋谷区幡ヶ谷2丁目43番2号 オ

リンパス株式会社内

(72) 発明者 近藤 雄

東京都渋谷区幡ヶ谷2丁目43番2号 オ

リンパス株式会社内

(54) 【発明の名称】積層実装構造体及び積層実装構造体の製造方法

(57) 【要約】 (修正有)

【課題】狭ピッチ化を実現できるとともに、被実装部品を実装することのできる高さを確保することのできる積層実装構造体及び積層実装構造体の製造方法を提供する。

【解決手段】少なくとも一方の主面20a上に被実装部品を設置、動作するために必要な実装領域、及び、被実装部品が動作するための信号伝達のための接続用領域、を備える複数の部材と、対向する部材との間の接続用領域に配置された導電部材21と、を有し、導電部材21の断面は、接続用領域と同じ又はそれより小さく、導電部材21の端部は一方の部材主面から他方の部材主面に達し、導電部材21の高さは、実装領域の間隔を規定する。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

少なくとも一方の主面上に被実装部品を設置、動作するために必要な実装領域、及び、前記被実装部品が動作するための信号伝達のための接続用領域、を備える複数の部材と、対向する前記部材との間の前記接続用領域に配置された導電部材と、を有し、

前記導電部材の断面は、前記接続用領域と同じ又はそれより小さく、前記導電部材の端部は前記一方の部材主面から他方の部材主面に達し、前記導電部材の高さは、前記実装領域の間隔を規定することを特徴とする積層実装構造体。

**【請求項 2】**

前記導電部材の周囲に補強部材が設置されていることを特徴とする請求項 1 に記載の積層実装構造体。 10

**【請求項 3】**

前記実装領域には前記被実装部品が実装されており、前記複数の部材間の実装領域の間隔は前記被実装部品の高さより高いことを特徴とする請求項 1 又は請求項 2 に記載の積層実装構造体。

**【請求項 4】**

前記補強部材は、対向する前記部材の間の実装領域に充填されていることを特徴とする請求項 1 から請求項 3 のいずれか一項に記載の積層実装構造体。 20

**【請求項 5】**

前記導電部材が棒形状であることを特徴とする請求項 1 から請求項 4 のいずれか一項に記載の積層実装構造体。 20

**【請求項 6】**

前記導電部材は、一方の端部が連結された状態において、他方の端部を前記部材に実装した後、前記連結された部分を除去してなることを特徴とする請求項 1 から請求項 5 のいずれか一項に記載の積層実装構造体。

**【請求項 7】**

前記補強部材の一方の端部に、少なくとも一部が導電部材と電気的に接続された導電パターンが形成されていることを特徴とする請求項 1 から請求項 6 のいずれか一項に記載の積層実装構造体。

**【請求項 8】**

第 1 の部材に、被実装部品及び前記被実装部品の高さより高い導電部材を実装する工程と、 30

前記第 1 の部材上の前記導電部材の周囲に、前記導電部材の前記第 1 の部材と逆側の端部を露出させて補強部材を形成する補強工程と、を備え、

前記補強工程において、前記補強部材の前記第 1 の部材と逆の面を研磨して平坦化すると共に導電部材の端部を露出させることを特徴とする積層実装構造体の製造方法。

**【請求項 9】**

前記導電部材の前記第 1 の部材と逆側の端部を露出させて前記補強部材を形成した後、露出した前記導電部材の端部表面に金属膜を形成する工程と、

前記導電部材端部表面の金属膜上にバンプを形成する工程と、を備えることを特徴とする請求項 8 に記載の積層実装構造体の製造方法。 40

**【請求項 10】**

前記導電部材の一方の端部を、複数の前記導電部材が連結された状態に形成する連結工程をさらに備えることを特徴とする請求項 8 または請求項 9 に記載の積層実装構造体の製造方法。

**【請求項 11】**

前記第 1 の部材は複数のモジュールに相当する大きさであり、絶縁材料形成工程の後に個片化工程を備える請求項 8 から請求項 10 のいずれか一項に記載の積層実装構造体の製造方法。

**【発明の詳細な説明】**

50

30

50

40

**【技術分野】****【0001】**

本発明は、積層実装構造体及び積層実装構造体の製造方法に関するものである。

**【背景技術】****【0002】**

従来、積層された電子回路基板を接続する基板間接続部材として、特許文献1（特開2001-144399号公報）に記載された基板間接続部材があった。この基板間接続部材は、剛性を有する導体からなる芯体を弾性体で覆うとともに、弾性体の周囲を導電性を有する材料で被覆するものである。基板間接続部材をこのように構成することにより、補修作業に際して電子回路基板を分離するのに加熱が必要でないという効果がある。

10

**【0003】**

また、別の従来例として、電子部品を内蔵しながら小型で高密度の基板を実現するために、配線基板本体の貫通穴に樹脂により電子部品を固定した後、樹脂に研磨や穴あけの加工を行うことで電子部品の電極を露出させ、さらに配線基板本体の表裏面に配線層を形成するものが提案されていた。

**【0004】****【特許文献1】特開2001-144399号公報****【発明の開示】****【発明が解決しようとする課題】****【0005】**

しかしながら、特許文献1に記載の基板間接続部材は、狭ピッチ化が可能であったとしても以下の課題があった。すなわち、（1）積層された電子回路基板を互いに着脱することを前提としたものであり、（2）接続部材を複数形成する場合の凹部への位置あわせ及び組み立てが困難であり、（3）電子回路基板を多数積層することは考慮されていない、（4）少なくとも芯体と弾性体という二つの部材が必要であるため小型化が困難であった。

20

**【0006】**

また、上記別の従来例は、基板厚さ内に内蔵できる電子部品は基板厚さより高さが小さい部品に限られている上に、基板本体表裏面の配線層を電子部品を介して接続しなければならず、配線層の設計上の制約が大きいという課題があった。基板本体表裏面の配線層を電子部品を介さずに接続する場合には、スルーホールを介して接続することはできるが、スルーホール径よりも大きな電極パッド（ランド電極）を設ける必要があり、基板接続部の狭ピッチ化が難しいため、基板正面の面積を小さくするのには限界があった。

30

**【0007】**

本発明は、上記に鑑みてなされたものであって、狭ピッチ化を実現できるとともに、被実装部品を実装することのできる高さを確保することのできる積層実装構造体及び積層実装構造体の製造方法を提供することを目的とする。また、本発明のさらなる目的は、基板の配線自由度が高く、基板接続部の狭ピッチ化が可能なことにより、基板正面の面積が小さい積層実装構造体を提供することにある。

40

**【課題を解決するための手段】****【0008】**

上述した課題を解決し、目的を達成するために、本発明の積層実装構造体は、少なくとも一方の正面に被実装部品を設置、動作するために必要な実装領域、及び、被実装部品が動作するための信号伝達のための接続用領域、を備える複数の部材と、対向する部材との間の接続用領域に配置された導電部材と、を有し、導電部材の断面は、接続用領域と同じ又はそれより小さく、導電部材の端部は一方の部材正面から他方の部材正面に達し、導電部材の高さは、実装領域の間隔を規定することを特徴としている。

**【0009】**

本発明の積層実装構造体において、導電部材の周囲に補強部材が設置されていることが好ましい。

50

## 【0010】

本発明の積層実装構造体において、実装領域には被実装部品が実装されており、複数の部材間の実装領域の間隔は被実装部品の高さより高いことが望ましい。

## 【0011】

本発明の積層実装構造体において、補強部材は、対向する部材の間の実装領域に充填されているとよい。

## 【0012】

本発明の積層実装構造体において、導電部材が棒形状であることが好ましい。

## 【0013】

本発明の積層実装構造体において、導電部材は、一方の端部が連結された状態において、他方の端部を前記部材に実装した後、前記連結された部分を除去してなることが望ましい。

10

## 【0014】

本発明の積層実装構造体において、補強部材の一方の端部に、少なくとも一部が導電部材と電気的に接続された導電パターンが形成されていることが好ましい。

## 【0015】

また、本発明の積層実装構造体の製造方法は、第1の部材に、被実装部品及び被実装部品の高さより高い導電部材を実装する工程と、第1の部材上の導電部材の周囲に、導電部材の第1の部材と逆側の端部を露出させて補強部材を形成する補強工程と、を備え、補強工程において、補強部材の第1の部材と逆の面を研磨して平坦化すると共に導電部材の端部を露出させることを特徴としている。

20

## 【0016】

本発明の積層実装構造体の製造方法において、導電部材の一方の端部を、複数の前記導電体が連結された状態に形成する連結工程をさらに備えることが望ましい。

## 【0017】

本発明の積層実装構造体の製造方法において、導電部材の第1の部材と逆側の端部を露出させて補強部材を形成した後、露出した導電部材の端部表面に金属膜を形成する工程と、導電部材端部表面の金属膜上にバンプを形成する工程と、を備えることが好ましい。

## 【0018】

本発明の積層実装構造体の製造方法において、第1の部材は複数のモジュールに相当する大きさであり、絶縁材料形成工程の後に個片化工程を備えるとよい。

30

## 【発明の効果】

## 【0019】

本発明にかかる積層実装構造体及び積層実装構造体の製造方法によれば、狭ピッチ化を実現できるとともに、被実装部品を実装することのできる高さを確保することのできる積層実装構造体及び積層実装構造体の製造方法を提供することができるという効果を奏する。

40

## 【発明を実施するための最良の形態】

## 【0020】

以下に、本発明にかかる積層実装構造体及び積層実装構造体の製造方法の実施例を図面に基づいて詳細に説明する。なお、この実施例によりこの発明が限定されるものではない。

50

本発明に係る積層実装構造体の製造方法は、回路基板上に被実装部品を実装すると同時に、その中の最も背の高い部品より長い導電部材を、回路基板上の電極に基板と垂直に固定・接続し、導電部材と被実装部品の間隙に樹脂を充填した後、研磨によって導電部材の頭部のみを露出させる。露出した導電部材に対して、第2の基板を接続、もしくは研磨面に印刷によって回路を形成することで、上下の回路基板を電気的、機械的に接続固定するものであって、これにより本発明に係る積層実装構造体が形成される。以下に具体的な実施例について説明する。

## 【実施例1】

50

## 【0021】

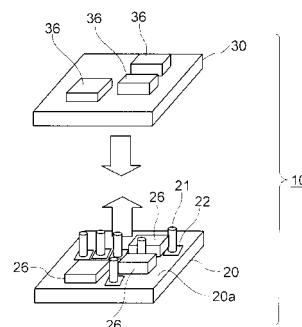

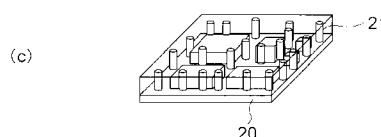

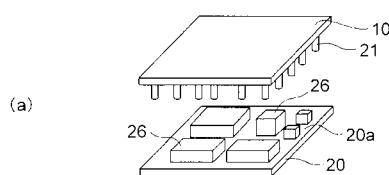

図1は、本発明にかかる積層実装構造体の実施例1の構成を、第1の基板20と第2の基板30に分離して示す斜視図である。図2は、実施例1に係る積層実装構造体10の構成を示す断面図である。

## 【0022】

図1に示すように、第1の基板20の正面20aには電子部品26が実装されている。また、第2の基板30には電子部品36が実装されている。第1の基板20と第2の基板30は対向して配置される。第1の基板20及び第2の基板30には多層基板や電子部品内蔵基板を用いても良い。

## 【0023】

第1の基板20の電子部品26の間には電極22が設けられており、電極22上に略円柱状の導電部材21が設置されている。導電部材21の長さは全て略同一であり、第1の基板20に実装された電子部品26の中で最も高い高さよりも大きい。また、導電部材21の長さ方向と垂直な直交断面積は電極22の面積と同等以下となっている。

10

## 【0024】

導電部材21は、円柱状の部品を用いれば、線材から切り出すことで容易に作成できる。このとき、導電部材21の第1の基板20に実装する側の端部の径を大きくしておけば、第1の基板20への実装を容易かつ確実に行うことができる。一方、導電部材の第1の基板20と逆側の端部は、いくつかの導電部材がつながった状態で実装することもできる。

20

## 【0025】

導電部材21は、電気抵抗の低い材料（例えばCu（銅））を用いることが好ましい。また、導電部材21の表面には、母材の酸化を防止するために、例えばAu（金）メッキを施すことが好ましい。さらに、導電部材21には、はんだづけを容易にするための表面処理が施されており、導電部材21の一方の端部と電極22ははんだづけで導電接合されている。なお、はんだづけに代えて、例えば、異方導電性材料を用いたACP工法やACF工法、NCP工法による接触導電によって導通をとることもできる。

## 【0026】

図2に示すように、第1の基板20及び第2の基板30には配線層24、34がそれぞれ形成されている。第1の基板20上の電子部品26と導電部材21の周囲には、樹脂の絶縁材料（補強部材）が充填硬化されて絶縁層23が形成されている。この絶縁層23においては、第2の基板30側の面（上面）23aから、導電部材21の第2の基板30側の端部21aのみが露出している。

30

## 【0027】

第2の基板30の第1の基板20と対向する面30aの導電部材21と対向する位置には、電極32が設置されている。第2の基板30は、第1の基板20の導電部材21の端部21aと電極32とが電気的に接続されるように、絶縁材料23表面に接合される。なお、第2の基板30の露出面上の電極（不図示）に導電部材（不図示）を設置するなどし、積層数を更に増やしてもよい。

## 【0028】

実施例1では、上下の回路基板を接続する導電部材は電子部品間に自由に配置できるため、各基板の配線設計の制約となることがない。さらに、導電部材を実装する電極はスルーホール電極でないためランド電極が必要なく、導電部材を狭ピッチで配置することができるため、基板正面の面積が小さい積層実装構造体を提供することができる。また、基板への貫通穴加工や、凹部加工を必要としないため、低価格でかつ基板正面の面積が小さい積層実装構造体を提供することができる。

40

## 【実施例2】

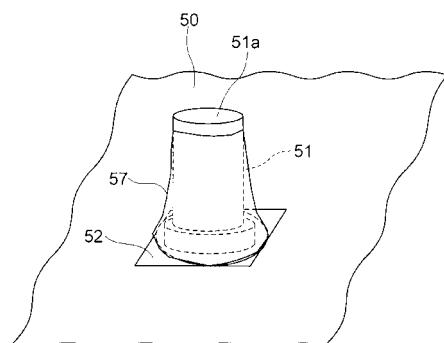

## 【0029】

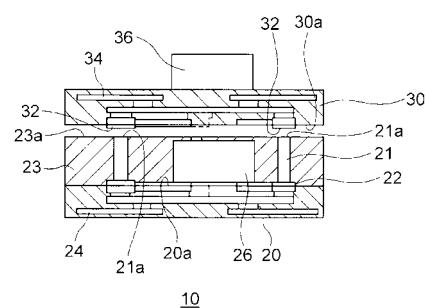

図3は、本発明にかかる積層実装構造体の実施例2の構成を、第1の基板50と第2の基板60に分離して示す斜視図である。図4は、実施例2に係る導電部材と補強部材の関

50

係を示す拡大斜視図である。

【0030】

実施例2においては、導電部材51の周囲に実装領域の一部又は全部を露出させた状態で補強部材57を形成している点が実施例1と異なる。すなわち、実施例1の積層実装構造体10における第1の基板20、導電部材21、電極22、電子部品26、第2の基板30、電子部品36が、実施例2の積層実装構造体40における第1の基板50、導電部材51、電極52、電子部品56、第2の基板60、電子部品66に、それぞれ対応する。また、図示しないが、実施例2の積層実装構造体40においても、実施例1の積層実装構造体10の配線層24、34と同様の配線層が形成されている。

【0031】

実施例2では、補強部材形成後において電子部品が露出しているため、第2の基板を接続する直前に電子部品の検査を行うことができ、積層実装構造体の不良品を減らすことが出来る。

【0032】

図4に例示するように、導電部材51の周囲には、第2の基板60側の端部51aを残すように補強部材57を配置している。補強部材57としては、例えば、導電部材51の周囲に配置するときには液状であって、配置の後に硬化する物質を用いる。

【実施例3】

【0033】

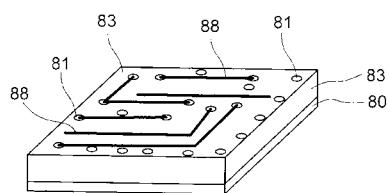

図5は、本発明に係る積層実装構造体の実施例3の構成を示す斜視図である。

実施例3の積層実装構造体70においては、実施例1の絶縁層23と同様に、第1の基板80上の電子部品(不図示)と導電部材81の周囲に樹脂の絶縁材料による絶縁層83が形成されるとともに、この絶縁層83のうち、第1の基板80から遠い面において、導電部材81を接続するように配線88が形成されている。すなわち実施例3においては、実施例1の第2の基板30及び実施例2の第2の基板60のような第2の基板を載置することなく、絶縁層83上に直接配線88を形成している。なお、配線88の形成方法はメッキ、スパッタ、蒸着やインクジェットやディスペンスによる印刷配線を用いれば良い。このような構成としたことにより、第2の基板の基材部分が不要となるため、設計の自由度を上げることができるとともに、積層高さが低くかつ基板主面の面積が小さい積層実装構造体を提供することができる。

【0034】

(変形例)

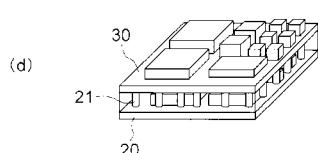

次に、積層実装構造体の変形例を説明する。図11(a)、(b)、(c)、(d)は、変形例にかかる積層実装構造体の構成を示している。

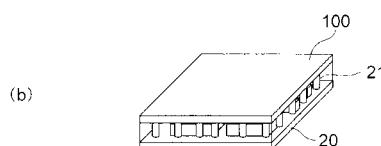

上述したように、導電部材21の第1の基板20と逆側の端部は、いくつかの導電部材21がつながった状態で実装することもできる。いくつかの導電部材がつながった状態は、基材100上にCuなどのメッキで導電部材21を形成すること、またはCuなどの導電材料の板100にプレス加工を行うこと等で形成できる(図11(a))。

本例では、連結した導電部材21を第1の基板20と別に製作して、第1の基板20に接続している。図11(b)は、ピン基板接合の状態を示している。そして、図11(c)に示すように、第1の基板20と導電部材21が連結された部分の間に樹脂を塗布、硬化させる。ここで、先に第1の基板20に樹脂を塗布しておいても良い。

【0035】

第1の基板20と導電部材21とが連結された部分を研磨で除去して、各導電部材21を露出させる。露出した導電部材21の端部に導電部材21の酸化を防ぐ金属膜を形成する。最後に、図11(d)に示すように第2の基板30を積層して、基板20、30間を接続する。これにより、積層実装構造体を形成する。このため、電子部品26の高さが、例えば0.3mmから1mmなど比較的高い場合において、電子部品26の高さよりも長い導電部材21を第1の基板20の主面20aに自在に配置して、第1の基板20と第2の基板30を接続できる。また、接続ピッチを狭ピッチ化できる。

10

20

30

40

50

## 【0036】

このように、導電部材21は、一方の端部が複数連結された状態で第1の基板20に一括して実装している。このため、導電部材21を容易に実装できる。また、突起電極は一括して製作できるため、より狭いピッチ化が可能である。この結果、積層実装構造体を容易に小さく製造できる。

## 【0037】

つづいて、本発明に係る積層実装構造体の製造方法について、実施例4から実施例6を挙げて説明する。

## 【実施例4】

## 【0038】

10

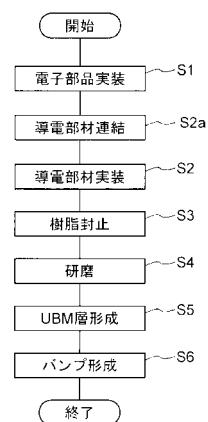

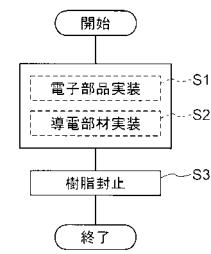

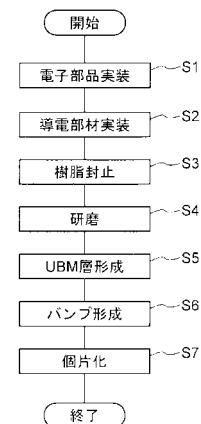

図6は、実施例4に係る積層実装構造体の製造方法の流れを示すフローチャートである。実施例4の製造方法は、実施例1から実施例3及び変形例に適用することができ、実施例4から実施例6の説明においては、実施例1の符号を用いることとする。

## 【0039】

まず、第1の基板20に電子部品26を実装する(ステップS1)と同時に、第1の基板20の電極22上に導電部材21を実装する(ステップS2)。前者の実装は、一般的な表面実装プロセス等を用いればよい。また、後者の実装を例えればはんだづけで行う場合は、電極22上にクリームハンダとフラックスを印刷法等により供給しておき、実装装置や治具を用いて導電部材を電極22上に位置決め固定して加熱することで、導電部材21を実装することができる。なお、第1の基板20への電子部品26及び導電部材21の実装は、電子部品26を実装した後に導電部材21を実装してもよいし(実施例5又は実施例6を参照)、その逆でもよい。

20

## 【0040】

次に、電子部品26と導電部材21が実装された第1の基板20上に、導電部材21の第1の基板20と逆側(第2の基板30側)の端面21aが露出する様に、液状封止樹脂等を塗布し、硬化させることで、第1の基板20上の電子部品26と導電部材21の周囲に絶縁層23を形成する。これにより、導電部材21及び電子部品26を封止する(ステップS3)。樹脂の硬化方法は熱硬化や2液混合などがある。第1の基板20の外形や所望の硬化後形状に合わせた型を用いれば硬化後の樹脂形状を容易に整えることが出来る。なお、実施例4を実施例2に適用する場合は、ステップS3において、樹脂の封止に代えて、補強部材を導電部材の周囲に配置する。

30

## 【0041】

その後、導電部材21の第1の基板20と逆側の端面上に形成した金属膜状のバンプを介して、第2の基板30を第1の基板20に対して積層接続する。なお、実施例4を実施例3に適用する場合は、第2の基板30を積層することなく、絶縁層23の第1の基板20と逆側の面23aに直接配線を形成する。

## 【0042】

以上の工程により積層実装構造体を製造するため、非常に少ない工程で、基板主面の面積が小さい積層実装構造体を提供することができる。

## 【実施例5】

40

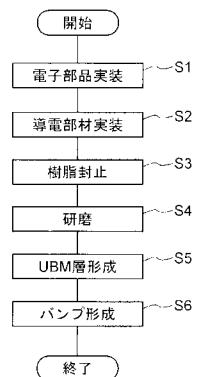

## 【0043】

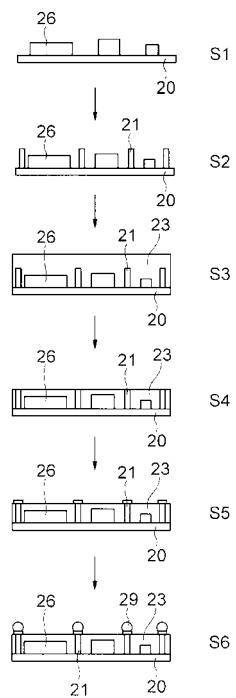

図7は、実施例5に係る積層実装構造体の製造方法の流れを示すフローチャートである。実施例5は、電子部品実装(ステップS1)、導電部材実装(ステップS2)、及び樹脂封止(ステップS3)の各工程が実施例4と共通しているため、これらの工程についての説明は省略する。

## 【0044】

樹脂封止(ステップS3)の後に、絶縁層23の第1の基板20の主面20aと平行を保つように、絶縁層23の上面23aを研磨し、平坦化するとともに導電部材21の第1の基板20と逆側の端面21aを各々露出させる(ステップS4)。

## 【0045】

50

次に、露出した導電部材 21 の端面 21a 上に金属膜 (UBM 層) を形成する (ステップ S5)。金属膜を形成することにより、導電部材 21 の酸化等を防ぐことができ、後の工程のバンプ形成時に電気抵抗が低く、高い強度のバンプを形成することができる。

#### 【0046】

つづいて、露出した導電部材 21 の端面 21a 上に形成した金属膜上にバンプを形成する (ステップ S6)。バンプ材質としては、はんだや Au を用いることができる。

その後、導電部材 21 の端面 21a 上に形成した金属膜上のバンプ 29 (図 9、図 10) を介して第 2 の基板 30 を積層接続する。

#### 【0047】

このような方法で積層実装構造体を製造することにより、絶縁層 23 の上面 23a が平坦化され、かつ、確実に第 1 の基板 20 の正面 20a と平行になるため、導電部材 21 の端面 21a は、第 2 の基板 30 が接続しやすいような構造となる。したがって、第 1 の基板 20 と第 2 の基板 30 との接続品質が高く、かつ、基板正面の面積が小さい積層実装構造体を提供することができる。

#### 【実施例 6】

#### 【0048】

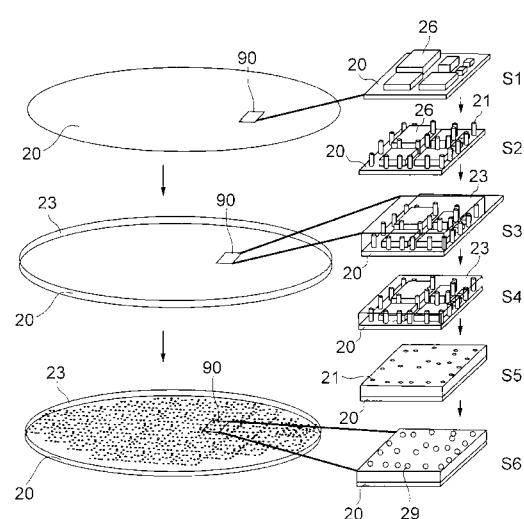

図 8 は、実施例 6 に係る積層実装構造体の製造方法の流れを示すフローチャートである。図 9 は、右側が図 8 の S1 ~ S6 の工程に対応した積層実装構造体の構成を示す拡大斜視図であり、左側は右側図の個片化された積層実装構造体の集合状態を示す斜視図である。図 10 は、図 8 の S1 ~ S6 の工程に対応した積層実装構造体の構成を示す側面図である。

#### 【0049】

実施例 6 は、電子部品実装 (ステップ S1)、導電部材実装 (ステップ S2)、樹脂封止 (ステップ S3)、研磨 (ステップ S4)、UBM 層形成 (ステップ S5)、及びバンプ形成 (ステップ S6) の各工程が実施例 5 と共に通している。バンプ 29 の形成後に、第 1 の基板 20 には、複数のモジュール 90 が形成されており、ダイシングなどの個片化工程により個別モジュール化する (ステップ S7)。

#### 【0050】

このような製造方法によれば、複数のモジュールを一度に製作できるため、モジュール製造のコストが低くかつ基板正面の面積が小さい積層実装構造体を提供することができる。

#### 【0051】

##### (変形例)

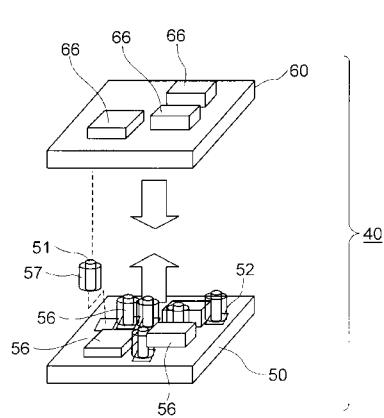

図 12 は、変形例に係る積層実装構造体の製造方法の流れを示すフローチャートである。すでに上述している各実施例の工程と同じ内容については、同一の符号を付し、重複する説明は省略する。まず、本変形例において、まず第 1 の基板 20 に電子部品 26 を実装する (ステップ S1)。

基材 100 上の第 1 の基板 20 の電子部品 26 の間に設けられた電極と対向する位置に、Cu をメッキで成長させる。これにより、いくつかの導電部材 21 の一方の端部が連結された状態を形成する (ステップ S2a)。

#### 【0052】

導電部材 21 の一方の端部がつながった状態は、基材 100 へ Cu をメッキで形成すること、さらには Cu 等の導電材料の板 100 にプレス加工を行う等で導電部材 21 を形成すること、棒状の電導部材 21 を治具に並べた状態で端面にメッキすること等の種々の方法を用いることができる。導電部材 21 の高さ (長さ) は、電子部品 26 の高さよりも大きいように形成されている。

#### 【0053】

導電部材 21 の連結されていない側の端部を第 1 の基板 20 の正面 20a の電極にはんだ等で接合する (ステップ S2)。導電部材 21 の一方の端部が連結された状態で、その表面に Au メッキ等を施しておけば、Cu の酸化を防止してはんだづけを確実に行うこと

10

20

30

40

50

ができる。

【0054】

第1の基板20と導電部材21が連結された部分の間に樹脂を塗布、硬化させる(ステップS3)。ここで、先に第1の基板20に樹脂を塗布しておいても良い。

【0055】

第1の基板20と導電部材21とが連結された部分を研磨で除去して、各導電部材21を露出させる(ステップS4)。導電部材21の周囲は樹脂で補強されている。このため、安定して導電部材21を研磨できる。さらに、研磨により導電部材21の高さ(長さ)を精密に揃えることができる。このため、用いる導電部材21の長さの公差を広げることが出来る。

10

【0056】

電子部品26の高さが、例えば0.3mmから1mmなど比較的高い場合において、電子部品26の高さよりも長い導電部材21を第1の基板20の主面20aに自在に配置して、第1の基板20と第2の基板30を接続できる。また、接続ピッチを狭ピッチ化できる。

【0057】

その後、露出した導電部材21の端部に導電部材21の酸化を防ぐ金属膜を形成する。そして、第2の基板30を接続することで積層実装構造体を形成する。

【0058】

このように、導電部材21は、一方の端部が複数連結された状態で第1の基板20に一括して実装している。このため、導電部材21を容易に実装できる。また、突起電極は一括して製作できるため、より狭いピッチ化が可能である。この結果、積層実装構造体を容易に小さく製造できる。

20

【0059】

以上説明したように、本発明によれば、上下の回路基板を接続する導電部材は電子部品間に自由に配置できるため、各基板の配線設計の制約となることがない。さらに、導電部材を実装する電極はスルーホール電極でないためランド電極が必要なく、導電部材を狭ピッチで配置することができるため、基板主面の面積が小さい積層実装構造体を提供することができる。

30

【産業上の利用可能性】

【0060】

以上のように、本発明にかかる積層実装構造体及び積層実装構造体の製造方法は、実装構造体の小型化に有用であり、特に、内視鏡先端撮像ユニットの高密度実装に適している。

【図面の簡単な説明】

【0061】

【図1】実施例1にかかる積層実装構造体の構成を、第1の基板と第2の基板に分離して示す斜視図である。

【図2】実施例1に係る積層実装構造体の構成を示す断面図である。

【図3】実施例2にかかる積層実装構造体の構成を、第1の基板と第2の基板に分離して示す斜視図である。

40

【図4】実施例2に係る導電部材と補強部材の関係を示す拡大斜視図である。

【図5】実施例3に係る積層実装構造体の構成を示す斜視図である。

【図6】実施例4に係る積層実装構造体の製造方法の流れを示すフローチャートである。

【図7】実施例5に係る積層実装構造体の製造方法の流れを示すフローチャートである。

【図8】実施例6に係る積層実装構造体の製造方法の流れを示すフローチャートである。

【図9】右側が図8のS1～S6の工程に対応した積層実装構造体の構成を示す拡大斜視図であり、左側は右側図の個片化された積層実装構造体の集合状態を示す斜視図である。

【図10】図8のS1～S6の工程に対応した積層実装構造体の構成を示す側面図である。

50

【図11】変形例に係る積層実装構造体の構成を示す斜視図である。

【図12】変形例に係る積層実装構造体の製造方法の流れを示すフローチャートである。

【符号の説明】

【0062】

10 積層実装構造体

20 第1の基板

20a 主面

21 導電部材

21a 端部

22 電極

23 絶縁層

23a 上面

24 配線層

26 電子部品

29 バンプ

30 第2の基板

32 電極

34 配線層

36 電子部品

40 積層実装構造体

50 第1の基板

51 導電部材

52 電極

56 電子部品

57 補強部材

60 第2の基板

66 電子部品

70 積層実装構造体

80 第1の基板

81 導電部材

83 絶縁層

88 配線

90 モジュール

10

20

30

【図1】

【図2】

【図3】

【図4】

【図5】

70

【図6】

【図7】

【図8】

【図 9】

【図 10】

【図 11】

【図 12】