(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6176990号

(P6176990)

(45) 発行日 平成29年8月9日(2017.8.9)

(24) 登録日 平成29年7月21日(2017.7.21)

(51) Int.Cl.

F 1

H04N 5/374 (2011.01)

H04N 5/374

H04N 5/357 (2011.01)

H04N 5/357

H04N 5/341 (2011.01)

H04N 5/341

請求項の数 8 (全 26 頁)

(21) 出願番号 特願2013-92968 (P2013-92968)

(22) 出願日 平成25年4月25日 (2013.4.25)

(65) 公開番号 特開2014-216859 (P2014-216859A)

(43) 公開日 平成26年11月17日 (2014.11.17)

審査請求日 平成28年4月11日 (2016.4.11)

(73) 特許権者 000000376

オリンパス株式会社

東京都八王子市石川町2951番地

(74) 代理人 100106909

弁理士 棚井 澄雄

(74) 代理人 100064908

弁理士 志賀 正武

(74) 代理人 100094400

弁理士 鈴木 三義

(74) 代理人 100086379

弁理士 高柴 忠夫

(74) 代理人 100129403

弁理士 増井 裕士

(74) 代理人 100139686

弁理士 鈴木 史朗

最終頁に続く

(54) 【発明の名称】 固体撮像装置および撮像装置

## (57) 【特許請求の範囲】

## 【請求項 1】

画素を構成する回路要素が配置された第1の基板と第2の基板とが電気的に接続されている固体撮像装置であって、

前記画素は、

前記第1の基板に配置され、入射した光に基づく信号を出力する光電変換部と、

前記第2の基板に配置され、ゲート端子、ソース端子、ドレイン端子を有し、前記ソース端子および前記ドレイン端子の一方である第1の端子に、前記光電変換部から出力された信号が入力され、前記第1の端子に入力された信号をサンプルホールドし、サンプルホールドした信号を前記ソース端子および前記ドレイン端子の他方である第2の端子から出力するサンプリングトランジスタと、

前記第2の基板に配置され、前記サンプリングトランジスタの前記第2の端子から出力された信号を保持する容量と、

前記容量に保持された信号を読み出す読み出し期間に、前記第1の端子の電位を、所定の固定電位に応じた電位に固定する電位固定回路と、

を備える

ことを特徴とする固体撮像装置。

## 【請求項 2】

画素を構成する回路要素が配置された第1の基板と第2の基板とが電気的に接続されている固体撮像装置であって、

10

20

前記画素は、

前記第1の基板に配置され、入射した光に基づく信号を出力する光電変換部と、

前記第1の基板に配置され、ゲート端子、ソース端子、ドレイン端子を有し、前記ソース端子および前記ドレイン端子の一方である第1の端子に、前記光電変換部から出力された信号が入力され、前記第1の端子に入力された信号をサンプルホールドし、サンプルホールドした信号を前記ソース端子および前記ドレイン端子の他方である第2の端子から出力するサンプリングトランジスタと、

前記第2の基板に配置され、前記サンプリングトランジスタの前記第2の端子から出力された信号を保持する容量と、

前記容量に保持された信号を読み出す読み出し期間に、前記第1の端子の電位を、所定の固定電位に応じた電位に固定する電位固定回路と、

を備える

ことを特徴とする固体撮像装置。

#### 【請求項3】

前記画素は、

前記第1の基板または前記第2の基板に配置され、前記光電変換部から出力された信号をクランプするクランプ容量と、

前記クランプ容量が配置されている基板と同一の基板に配置され、第2のゲート端子、第2のソース端子、および第2のドレイン端子を有し、前記第2のソース端子および前記第2のドレイン端子の一方である第3の端子が前記クランプ容量および前記サンプリングトランジスタの前記第1の端子に接続され、前記第2のソース端子および前記第2のドレイン端子の他方である第4の端子が、前記固定電位を供給する電圧源に接続されるクランプトランジスタと、

を備え、

前記クランプトランジスタは、前記電位固定回路に含まれ、前記読み出し期間に、前記サンプリングトランジスタの前記第1の端子の電位を、前記電圧源から供給される前記固定電位に応じた電位に固定する

ことを特徴とする請求項1に記載の固体撮像装置。

#### 【請求項4】

前記画素は、

前記第1の基板に配置され、前記光電変換部から出力された信号をクランプするクランプ容量と、

前記第1の基板に配置され、第2のゲート端子、第2のソース端子、および第2のドレイン端子を有し、前記第2のソース端子および前記第2のドレイン端子の一方である第3の端子が前記クランプ容量および前記サンプリングトランジスタの前記第1の端子に接続され、前記第2のソース端子および前記第2のドレイン端子の他方である第4の端子が、前記固定電位を供給する電圧源に接続されるクランプトランジスタと、

を備え、

前記クランプトランジスタは、前記電位固定回路に含まれ、前記読み出し期間に、前記サンプリングトランジスタの前記第1の端子の電位を、前記電圧源から供給される前記固定電位に応じた電位に固定する

ことを特徴とする請求項2に記載の固体撮像装置。

#### 【請求項5】

複数の前記画素を備え、

複数の前記画素の間で1つの前記クランプ容量および1つの前記クランプトランジスタが共有される

ことを特徴とする請求項3または請求項4に記載の固体撮像装置。

#### 【請求項6】

前記画素は、

前記第1の基板に配置され、前記光電変換部から出力された信号が入力される第2のゲ

10

20

30

40

50

ート端子、第2のソース端子、および第2のドレイン端子を有し、前記第2のゲート端子に入力された信号を増幅し、増幅した信号を前記第2のソース端子および前記第2のドレイン端子の一方から出力する増幅トランジスタと、

前記第1の基板に配置され、第3のゲート端子、第3のソース端子、および第3のドレイン端子を有し、前記第3のソース端子および前記第3のドレイン端子の一方である第3の端子が、前記固定電位を供給する電圧源に接続され、前記第3のソース端子および前記第3のドレイン端子の他方である第4の端子が前記光電変換部に接続され、前記光電変換部をリセットするリセットトランジスタと、

を備え、

前記リセットトランジスタは、前記電位固定回路に含まれ、前記読み出し期間に、前記增幅トランジスタの前記第2のゲート端子の電位を、前記電圧源から供給される前記固定電位に応じた電位に固定することにより、前記サンプリングトランジスタの一端の電位を固定する

ことを特徴とする請求項1に記載の固体撮像装置。

#### 【請求項7】

前記画素は、

前記第1の基板に配置され、前記光電変換部から出力された信号が入力される第2のゲート端子、第2のソース端子、および第2のドレイン端子を有し、前記第2のゲート端子に入力された信号を増幅し、増幅した信号を前記第2のソース端子および前記第2のドレイン端子の一方から出力する増幅トランジスタと、

前記第1の基板または前記第2の基板に配置され、前記増幅トランジスタの前記第2のソース端子および前記第2のドレイン端子の一方に接続される一端と、他端とを有する電流源と、

を備え、

前記読み出し期間に、前記電流源の前記他端に前記固定電位が入力され、前記一端と前記他端との電位が略同一となる

ことを特徴とする請求項1に記載の固体撮像装置。

#### 【請求項8】

請求項1に記載の固体撮像装置を有する撮像装置。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、画素を構成する回路素子が配置された第1の基板と第2の基板とが電気的に接続されている固体撮像装置、およびこの固体撮像装置を備えた撮像装置に関する。

##### 【背景技術】

##### 【0002】

近年、ビデオカメラや電子スチルカメラなどが広く一般に普及している。これらのカメラには、CCD (Charge Coupled Device) 型や増幅型の固体撮像装置が使用されている。増幅型の固体撮像装置は、光が入射する画素の光電変換部が生成・蓄積した信号電荷を、画素に設けられた増幅部に導き、増幅部が増幅した信号を画素から出力する。増幅型の固体撮像装置では、このような画素が二次元マトリクス状に複数配置されている。増幅型の固体撮像装置には、例えばCMOS (Complementary Metal Oxide Semiconductor) トランジスタを用いたCMOS型固体撮像装置等がある。

##### 【0003】

従来、一般的なCMOS型固体撮像装置は、二次元マトリクス状に配列された各画素の光電変換部が生成した信号電荷を行毎に順次読み出す方式を採用している。この方式では、各画素の光電変換部における露光のタイミングは、信号電荷の読み出しの開始と終了によって決まるため、行毎に露光のタイミングが異なる。このため、このようなCMOS型固体撮像装置を用いて動きの速い被写体を撮像すると、撮像した画像内で被写体が歪んでしまう。

##### 【0004】

10

20

30

40

50

この被写体の歪みを無くすために、信号電荷の蓄積の同時性を実現する同時撮像機能（グローバルシャッタ機能）が提案されている。また、グローバルシャッタ機能を有するCMOS型固体撮像装置の用途が多くなりつつある。グローバルシャッタ機能を有するCMOS型固体撮像装置では、通常、光電変換部が生成した信号電荷を、読み出しが行われるまで蓄えておくために、遮光性を持った蓄積容量部を有することが必要となる。このような従来のCMOS型固体撮像装置は、全画素を同時に露光した後、各光電変換部が生成した信号電荷を全画素で同時に各蓄積容量部に転送して一旦蓄積しておき、この信号電荷を所定の読み出しタイミングで順次画素信号に変換して読み出している。

#### 【0005】

ただし、従来のグローバルシャッタ機能を有するCMOS型固体撮像装置では、光電変換部と蓄積容量部とを同一基板の同一平面上に作りこまねばならず、チップ面積の増大が避けられない。さらに、蓄積容量部に蓄積された信号電荷を読み出すまでの待機期間中に、光に起因するノイズや、蓄積容量部で発生するリーク電流（暗電流）に起因するノイズにより信号の品質が劣化してしまうという問題がある。

10

#### 【0006】

この問題を解決するために、光電変換部が形成された第1の基板と、蓄積容量部が形成された第2の基板とを貼り合わせ、第1の基板と第2の基板をマイクロバンプにより電気的に接続した固体撮像装置が特許文献1に開示されている。

#### 【先行技術文献】

#### 【特許文献】

20

#### 【0007】

#### 【特許文献1】特開2013-9294号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0008】

特許文献1に開示された固体撮像装置では、第1の基板の光電変換部で発生した信号電荷に基づく電圧を固定するためのクランプ容量と、信号電荷を第2の基板の蓄積容量部（特許文献1におけるアナログメモリ110）にサンプルホールドするためのサンプリングトランジスタ（特許文献1におけるサンプルトランジスタ108）とが設けられている。クランプ容量に接続されているサンプリングトランジスタの一端（ドレイン端子またはソース端子）は、サンプリングトランジスタがオフしている間、電位が固定されていないフローティング状態である。このため、 $1/f$  ノイズなどのノイズがサンプリングトランジスタの一端に混入すると、サンプリングトランジスタの一端の電位が変動する。さらに、このノイズによる電位の変動が、サンプリングトランジスタのドレイン端子とソース端子との間の容量結合により、サンプリングトランジスタの他端に接続された蓄積容量部に伝搬する。これによって、蓄積容量部に蓄積された信号電荷にノイズが混入しやすい。

30

#### 【0009】

また、特許文献1に開示された固体撮像装置では、クランプ容量に增幅信号を出力する增幅トランジスタ（特許文献1における第1增幅トランジスタ105）が設けられていると共に、增幅トランジスタとソースフォロワ回路を構成する電流源（特許文献1における負荷トランジスタ106）が設けられている。蓄積容量部に蓄積された信号電荷を読み出す期間（読み出し期間）の間、電流源はオフとなっているため、增幅トランジスタに接続されている電流源の一端はフローティング状態である。したがって、電流源の一端に混入したノイズによる電位の変動が、クランプ容量を介してサンプリングトランジスタに伝搬し、上記のようにサンプリングトランジスタを介して蓄積容量部に伝搬する。これによって、蓄積容量部に蓄積された信号電荷にノイズが混入しやすい。

40

#### 【0010】

本発明は、上述した課題に鑑みてなされたものであって、ノイズ耐性を向上することができる固体撮像装置および撮像装置を提供することを目的とする。

#### 【課題を解決するための手段】

50

## 【0011】

本発明は、上記の課題を解決するためになされたもので、画素を構成する回路要素が配置された第1の基板と第2の基板とが電気的に接続されている固体撮像装置であって、前記画素は、前記第1の基板に配置され、入射した光に基づく信号を出力する光電変換部と、前記第2の基板に配置され、ゲート端子、ソース端子、ドレイン端子を有し、前記ソース端子および前記ドレイン端子の一方である第1の端子に、前記光電変換部から出力された信号が入力され、前記第1の端子に入力された信号をサンプルホールドし、サンプルホールドした信号を前記ソース端子および前記ドレイン端子の他方である第2の端子から出力するサンプリングトランジスタと、前記第2の基板に配置され、前記サンプリングトランジスタの前記第2の端子から出力された信号を保持する容量と、前記容量に保持された信号を読み出す読み出し期間に、前記第1の端子の電位を、所定の固定電位に応じた電位に固定する電位固定回路と、を備えることを特徴とする固体撮像装置である。

10

## 【0012】

また、本発明は、画素を構成する回路要素が配置された第1の基板と第2の基板とが電気的に接続されている固体撮像装置であって、前記画素は、前記第1の基板に配置され、入射した光に基づく信号を出力する光電変換部と、前記第1の基板に配置され、ゲート端子、ソース端子、ドレイン端子を有し、前記ソース端子および前記ドレイン端子の一方である第1の端子に、前記光電変換部から出力された信号が入力され、前記第1の端子に入力された信号をサンプルホールドし、サンプルホールドした信号を前記ソース端子および前記ドレイン端子の他方である第2の端子から出力するサンプリングトランジスタと、前記第2の基板に配置され、前記サンプリングトランジスタの前記第2の端子から出力された信号を保持する容量と、前記容量に保持された信号を読み出す読み出し期間に、前記第1の端子の電位を、所定の固定電位に応じた電位に固定する電位固定回路と、を備えることを特徴とする固体撮像装置である。

20

## 【0013】

また、本発明は、上記の固体撮像装置を有する撮像装置である。

## 【発明の効果】

## 【0014】

本発明によれば、読み出し期間に、サンプリングトランジスタの第1の端子の電位が、所定の固定電位に応じた電位に固定されるので、ノイズの混入によるサンプリングトランジスタの第1の端子の電位の変動を抑制することが可能となり、ノイズ耐性を向上することができる。

30

## 【図面の簡単な説明】

## 【0015】

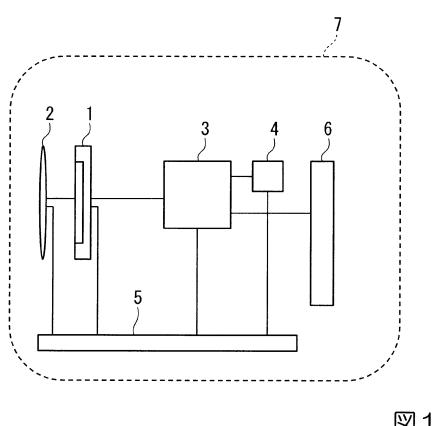

【図1】本発明の第1の実施形態によるデジタルカメラの構成を示すブロック図である。

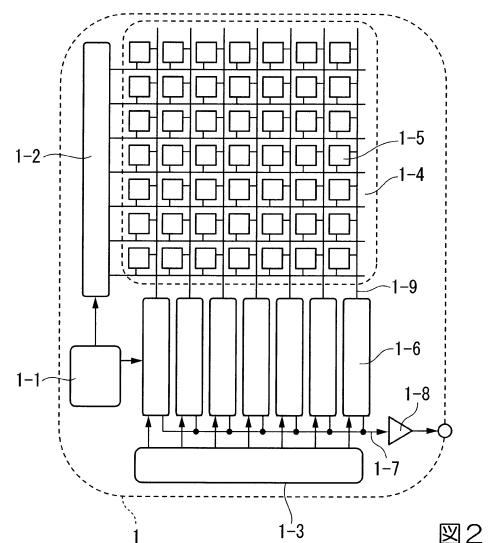

【図2】本発明の第1の実施形態による固体撮像装置の構成を示すブロック図である。

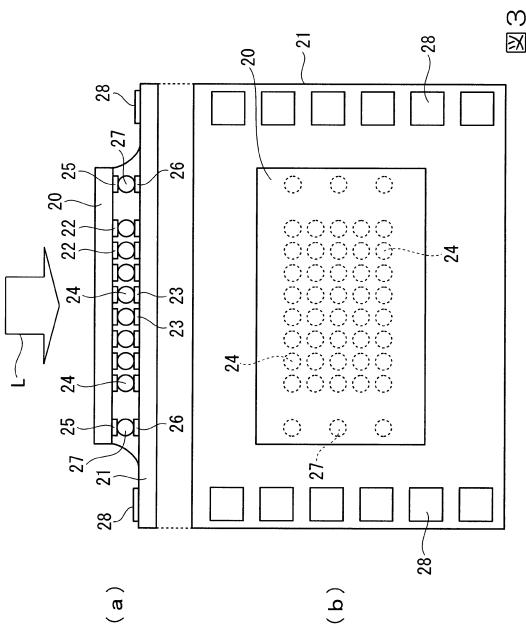

【図3】本発明の第1の実施形態による固体撮像装置の断面図および平面図である。

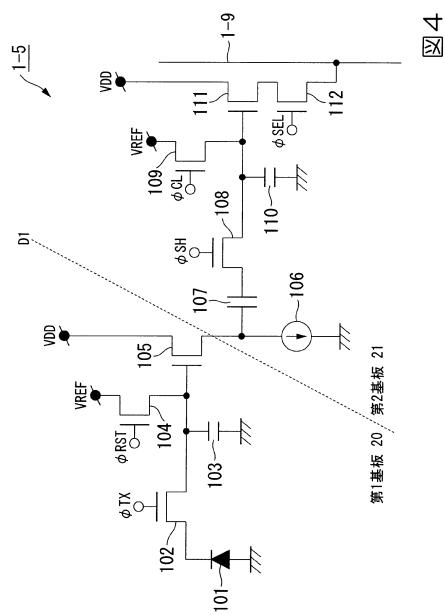

【図4】本発明の第1の実施形態による固体撮像装置が備える単位画素の回路構成を示す回路図である。

【図5】本発明の第1の実施形態による固体撮像装置が備える単位画素の回路構成を示す回路図である。

40

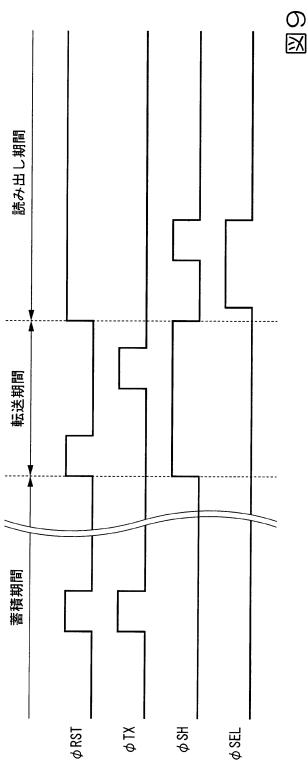

【図6】本発明の第1の実施形態による固体撮像装置が備える単位画素の動作を示すタイミングチャートである。

【図7】本発明の第1の実施形態による固体撮像装置が備える単位画素の回路構成を示す回路図である。

【図8】本発明の第1の実施形態による固体撮像装置が備える単位画素の回路構成を示す回路図である。

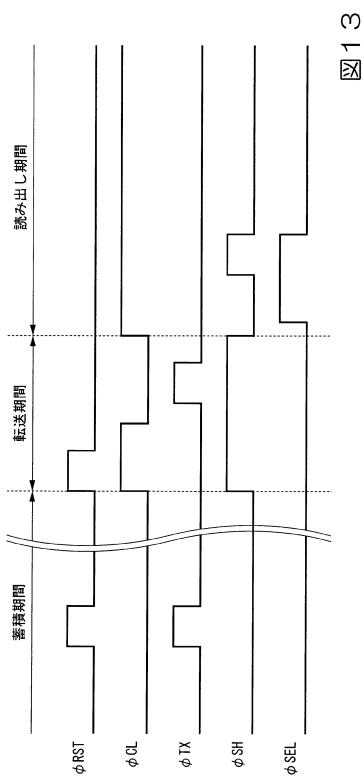

【図9】本発明の第1の実施形態による固体撮像装置が備える単位画素の動作を示すタイミングチャートである。

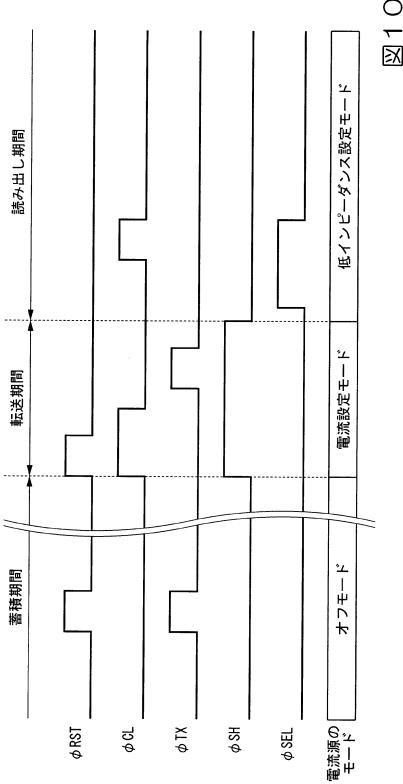

【図10】本発明の第2の実施形態による固体撮像装置が備える単位画素の動作を示すタ

50

イミングチャートである。

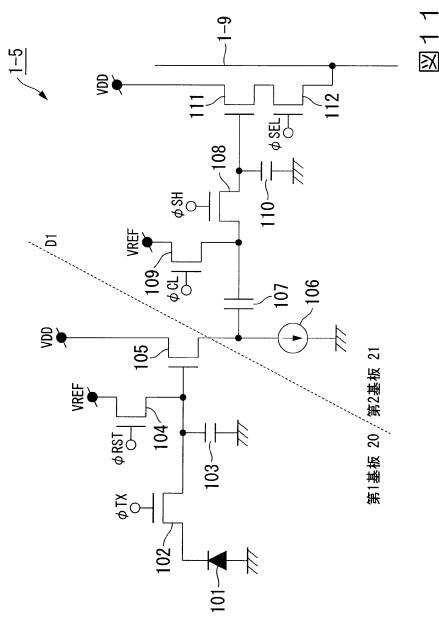

【図11】本発明の第3の実施形態による固体撮像装置が備える単位画素の回路構成を示す回路図である。

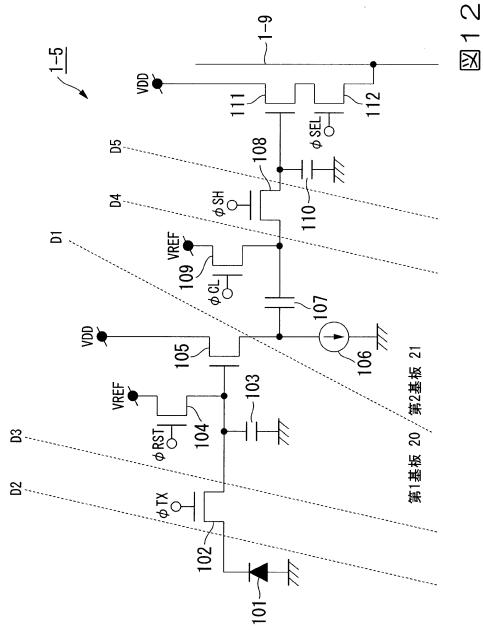

【図12】本発明の第3の実施形態による固体撮像装置が備える単位画素の回路構成を示す回路図である。

【図13】本発明の第3の実施形態による固体撮像装置が備える単位画素の動作を示すタイミングチャートである。

【図14】本発明の第4の実施形態による固体撮像装置が備える単位画素の回路構成を示す回路図である。

【図15】本発明の第4の実施形態による固体撮像装置が備える単位画素の回路構成を示す回路図である。 10

【図16】本発明の第4の実施形態による固体撮像装置が備える単位画素の動作を示すタイミングチャートである。

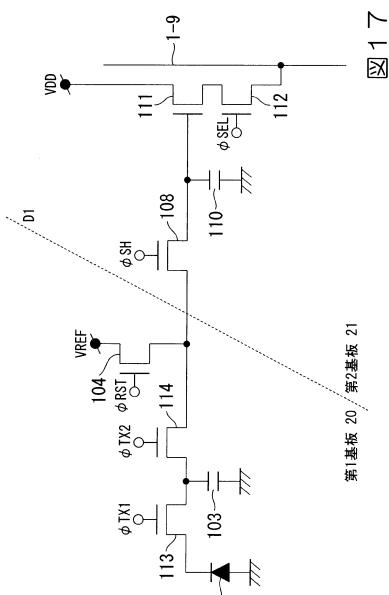

【図17】本発明の第5の実施形態による固体撮像装置が備える単位画素の回路構成を示す回路図である。

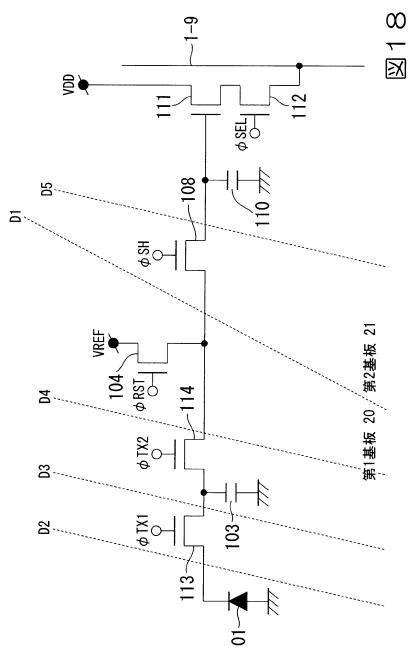

【図18】本発明の第5の実施形態による固体撮像装置が備える単位画素の回路構成を示す回路図である。

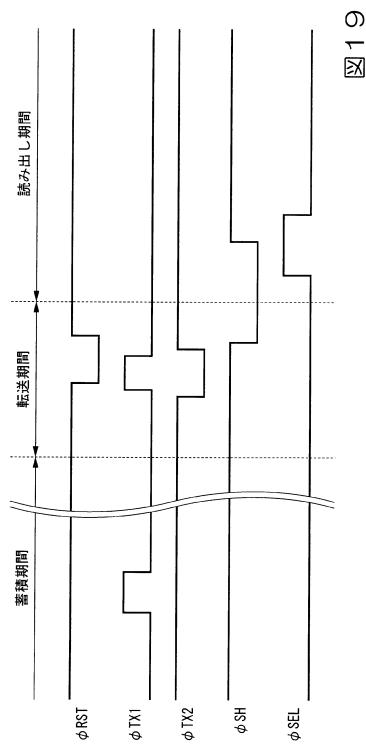

【図19】本発明の第5の実施形態による固体撮像装置が備える単位画素の動作を示すタイミングチャートである。 20

#### 【発明を実施するための形態】

##### 【0016】

以下、図面を参照し、本発明の実施形態を説明する。

##### 【0017】

###### (第1の実施形態)

まず、本発明の第1の実施形態を説明する。図1は、本実施形態による撮像装置の一例であるデジタルカメラの構成を示している。図1に示すように、デジタルカメラ7は、固体撮像装置1と、レンズユニット部2と、画像処理装置3と、記録装置4と、カメラ制御装置5と、表示装置6とを有する。

##### 【0018】

レンズユニット部2は、レンズ等の光学系を有し、被写体からの光が形成する被写体像を固体撮像装置1に結像させる。レンズユニット部2のズーム、フォーカス、絞りなどの駆動はカメラ制御装置5によって制御される。固体撮像装置1は、レンズユニット部2を介してデジタルカメラ7内に入射した被写体の光を画像信号に変換するMOS型撮像装置である。固体撮像装置1の駆動はカメラ制御装置5によって制御される。この固体撮像装置1に関する詳細な説明については、後述する。 30

##### 【0019】

画像処理装置3は固体撮像装置1から出力された画像信号に対して信号の増幅や画像データへの変換などの処理を行い、変換された画像データに対して各種の補正や圧縮などの処理を行う。記録装置4は、半導体メモリなどの着脱可能な記録媒体であり、画像データの記録および読み出しを行う。表示装置6は、固体撮像装置1から出力された画像信号に基づく画像データ、または記録装置4から読み出された画像データに基づく画像を表示する液晶などの表示装置である。 40

##### 【0020】

図2は、固体撮像装置1の構成を示している。図2に示すように、固体撮像装置1は、制御信号発生回路1-1と、垂直読み出し制御回路1-2と、水平読み出し制御回路1-3と、複数の単位画素1-5で構成された画素アレイ部1-4と、カラム信号処理部1-6と、出力回路1-8とを有する。

##### 【0021】

制御信号発生回路1-1は、垂直読み出し制御回路1-2、水平読み出し制御回路1-3、およびカラム信号処理部1-6を制御するための制御信号を発生し、これらに制御信号を供給す 50

る。垂直読み出し制御回路1-2は、画素アレイ部1-4内のそれぞれの単位画素1-5を行単位で制御し、各単位画素1-5の画素信号を、列毎に設けられている垂直信号線1-9に出力させる。垂直読み出し制御回路1-2が行う単位画素1-5の制御には、単位画素1-5のリセット動作、蓄積動作、信号読み出し動作などが含まれる。この制御を行うため、垂直読み出し制御回路1-2は、それぞれの単位画素1-5へ制御信号（制御パルス）を出力し、単位画素1-5を行毎に独立して制御する。

#### 【0022】

画素アレイ部1-4では、複数の単位画素1-5が2次元の行列状に配列されている。図2では、7行×7列の49個の単位画素1-5が配列されているが、図2に示す単位画素1-5の配列は一例であり、行数および列数は2以上であればよい。

10

#### 【0023】

カラム信号処理部1-6は、列毎に設けられている垂直信号線1-9に接続されており、垂直信号線1-9に出力された画素信号に対してノイズ抑圧やA/D変換前の信号増幅などの信号処理を行う。水平読み出し制御回路1-3は、カラム信号処理部1-6の出力信号を水平信号線1-7に順次読み出す。水平信号線1-7に読み出された信号は、出力回路1-8を介して固体撮像装置1の外部へ出力される。

#### 【0024】

図3は固体撮像装置1の断面構造（図3(a)）および平面構造（図3(b)）を示している。固体撮像装置1は、単位画素1-5を構成する回路要素（光電変換部や、トランジスタ、容量等）が配置された2枚の基板（第1基板20、第2基板21）が重なった構造を有する。単位画素1-5を構成する回路要素は第1基板20と第2基板21に分配して配置されている。第1基板20と第2基板21は、単位画素1-5の駆動時に2枚の基板間で電気信号を授受可能なよう電気的に接続されている。

20

#### 【0025】

第1基板20の2つの主面（側面よりも相対的に表面積が大きい表面）のうち、光Lが照射される側の主面側に光電変換部が形成されており、第1基板20に照射された光は光電変換部に入射する。第1基板20の2つの主面のうち、光Lが照射される側の主面とは反対側の主面には、第2基板21との接続用の電極である多数のマイクロパッド22が形成されている。1画素毎あるいは複数画素毎に1つのマイクロパッド22が配置される。また、第2基板21の2つの主面のうち、第1基板20と対向する側の主面において、マイクロパッド22と対応する位置には、第1基板20との接続用の電極である多数のマイクロパッド23が形成されている。

30

#### 【0026】

マイクロパッド22とマイクロパッド23の間にはマイクロバンプ24が形成されている。第1基板20と第2基板21は、マイクロパッド22とマイクロパッド23が互いに対向するように重ねて配置され、マイクロパッド22とマイクロパッド23間がマイクロバンプ24によって電気的に接続されるように一体化されている。マイクロパッド22、マイクロバンプ24、マイクロパッド23は、第1基板20と第2基板21を電気的に接続する接続部を構成する。第1基板20に配置されている光電変換部で発生した信号電荷に基づく信号は、マイクロパッド22、マイクロバンプ24、マイクロパッド23を介して第2基板21へ出力される。

40

#### 【0027】

第1基板20の2つの主面のうち、光Lが照射される側の主面とは反対側の主面の周辺部には、マイクロパッド22と同様の構造を有するマイクロパッド25が形成されている。第2基板21の2つの主面のうち、第1基板20と対向する側の主面において、マイクロパッド25と対応する位置には、マイクロパッド23と同様の構造を有するマイクロパッド26が形成されている。マイクロパッド25とマイクロパッド26の間にはマイクロバンプ27が形成されている。第1基板20に配置された回路要素、または第2基板21に配置された回路要素を駆動するための電源電圧等は、マイクロパッド25、マイクロバンプ27、マイクロパッド26を介して第1基板20から第2基板21へ、または第2基板21から第1基板20へ供給される。

#### 【0028】

50

第2基板21の2つの主面のうち一方の主面の周辺部には、第1基板20、第2基板21以外の系とのインターフェースとして使用されるパッド28が形成されている。パッド28に代えて、第2基板21を貫通する貫通電極を設け、貫通電極を外部接続用の電極として使用してもよい。図3に示す例では第1基板20と第2基板21の主面の面積が異なるが、第1基板20と第2基板21の主面の面積が同じであってもよい。また、マイクロバンプを設げずに、第1基板20の表面に設けたマイクロパッド（第1の電極）と、第2基板21の表面に設けたマイクロパッド（第2の電極）とを直接貼り合わせることにより第1基板20と第2基板21を接続してもよい。

#### 【0029】

単位画素1-5を構成する回路要素は第1基板20と第2基板21に分散して配置されている。単位画素1-5以外の制御信号発生回路1-1、垂直読み出し制御回路1-2、水平読み出し制御回路1-3、カラム信号処理部1-6、出力回路1-8に関しては、それぞれ第1基板20と第2基板21のどちらに配置されていてもよい。また、制御信号発生回路1-1、垂直読み出し制御回路1-2、水平読み出し制御回路1-3、カラム信号処理部1-6、出力回路1-8のそれぞれを構成する回路要素が第1基板20と第2基板21に分散して配置されていてもよい。単位画素1-5以外の構成についても第1基板20と第2基板21の間で信号の授受が必要となる場合があるが、単位画素1-5と同様にマイクロパッドとマイクロバンプを使用して第1基板20と第2基板21を接続したり、マイクロパッド同士を直接接続して第1基板20と第2基板21を接続したりすることが可能である。

#### 【0030】

図4は、単位画素1-5の構成を示している。単位画素1-5は、光電変換部101と、転送トランジスタ102と、FD（フローティングディフュージョン）103と、FDリセットトランジスタ104と、第1増幅トランジスタ105と、電流源106と、クランプ容量107と、サンプリングトランジスタ108と、クランプトランジスタ109と、アナログメモリ110と、第2増幅トランジスタ111と、選択トランジスタ112とを有する。

#### 【0031】

光電変換部101の一端は接地されている。転送トランジスタ102のドレイン端子は光電変換部101の他端に接続されている。転送トランジスタ102のゲート端子は垂直読み出し制御回路1-2に接続されており、転送パルス TXが供給される。

#### 【0032】

FD103の一端は転送トランジスタ102のソース端子に接続されており、FD103の他端は接地されている。FDリセットトランジスタ104のドレイン端子は、基準電圧VREFを供給する基準電圧源に接続されており、FDリセットトランジスタ104のソース端子は転送トランジスタ102のソース端子に接続されている。FDリセットトランジスタ104のゲート端子は垂直読み出し制御回路1-2に接続されており、FDリセットパルス RSTが供給される。

#### 【0033】

第1増幅トランジスタ105のドレイン端子は、電源電圧VDDを供給する電源に接続されている。第1増幅トランジスタ105の入力部であるゲート端子は転送トランジスタ102のソース端子に接続されている。電流源106の一端は第1増幅トランジスタ105のソース端子に接続されており、電流源106の他端は接地されている。一例として、ドレイン端子が第1増幅トランジスタ105のソース端子に接続され、ソース端子が接地され、ゲート端子が垂直読み出し制御回路1-2に接続されたトランジスタで電流源106を構成してもよい。クランプ容量107の一端は第1増幅トランジスタ105のソース端子および電流源106の一端に接続されている。

#### 【0034】

サンプリングトランジスタ108のドレイン端子はクランプ容量107の他端に接続されている。サンプリングトランジスタ108のゲート端子は垂直読み出し制御回路1-2に接続されており、サンプルパルス SHが供給される。

#### 【0035】

クランプトランジスタ109のドレイン端子は、基準電圧VREFを供給する基準電圧源に接

10

20

30

40

50

続されており、クランプトランジスタ109のソース端子はサンプリングトランジスタ108のソース端子に接続されている。クランプトランジスタ109のゲート端子は垂直読み出し制御回路1-2に接続されており、クランプ&メモリリセットパルス CLが供給される。

#### 【 0 0 3 6 】

アナログメモリ110の一端はサンプリングトランジスタ108のソース端子に接続されており、アナログメモリ110の他端は接地されている。第2增幅トランジスタ111のドレイン端子は、電源電圧VDDを供給する電源に接続されている。第2增幅トランジスタ111の入力部であるゲート端子はサンプリングトランジスタ108のソース端子に接続されている。選択トランジスタ112のドレイン端子は第2增幅トランジスタ111のソース端子に接続されており、選択トランジスタ112のソース端子は垂直信号線1-9に接続されている。選択トランジスタ112のゲート端子は垂直読み出し制御回路1-2に接続されており、選択パルス SELが供給される。上述した各トランジスタに関しては極性を逆にし、ソース端子とドレイン端子を上記と逆にしてもよい。10

#### 【 0 0 3 7 】

光電変換部101は、例えばフォトダイオードであり、入射した光に基づく信号電荷を生成（発生）し、生成（発生）した信号電荷を保持・蓄積し、所定の期間の経過後に信号電荷を出力する。転送トランジスタ102は、光電変換部101に蓄積された信号電荷をFD103に転送するトランジスタである。転送トランジスタ102のオン／オフは、垂直読み出し制御回路1-2からの転送パルス TXによって制御される。FD103は、光電変換部101から転送された信号電荷を一時的に保持・蓄積する容量である。20

#### 【 0 0 3 8 】

FDリセットトランジスタ104は、FD103をリセットするトランジスタである。FDリセットトランジスタ104のオン／オフは、垂直読み出し制御回路1-2からのFDリセットパルス RS Tによって制御される。FDリセットトランジスタ104と転送トランジスタ102を同時にオンにすることによって、光電変換部101をリセットすることも可能である。FD103／光電変換部101のリセットは、FD103／光電変換部101に蓄積されている電荷量を制御してFD103／光電変換部101の状態（電位）を基準状態（基準電位、リセットレベル）に設定することである。

#### 【 0 0 3 9 】

第1增幅トランジスタ105は、ゲート端子に入力される、FD103に蓄積されている信号電荷に基づく信号を増幅した増幅信号をソース端子から出力するトランジスタである。電流源106は、第1增幅トランジスタ105の負荷として機能し、第1增幅トランジスタ105を駆動する電流を第1增幅トランジスタ105に供給する。第1增幅トランジスタ105と電流源106はソースフォロワ回路を構成する。30

#### 【 0 0 4 0 】

クランプ容量107は、第1增幅トランジスタ105から出力される増幅信号の電圧レベルをクランプ（固定）する容量である。サンプリングトランジスタ108は、クランプ容量107の他端の電圧レベルをサンプルホールドし、アナログメモリ110に蓄積するトランジスタである。サンプリングトランジスタ108のオン／オフは、垂直読み出し制御回路1-2からのサンプルパルス SHによって制御される。40

#### 【 0 0 4 1 】

クランプトランジスタ109は、アナログメモリ110をリセットするトランジスタである。アナログメモリ110のリセットは、アナログメモリ110に蓄積されている電荷量を制御してアナログメモリ110の状態（電位）を基準状態（基準電位、リセットレベル）に設定することである。アナログメモリ110は、サンプリングトランジスタ108によってサンプルホールドされたアナログ信号を保持・蓄積する容量である。

#### 【 0 0 4 2 】

アナログメモリ110の容量値は、FD103の容量値よりも大きな値に設定される。アナログメモリ110には、単位面積当たりのリーク電流（暗電流）の少ない容量であるMIM（Metal Insulator Metal）容量やMOS（Metal Oxide Semiconductor）容量を使用することがより50

望ましい。これによって、ノイズに対する耐性が向上し、高品質な信号が得られる。

**【0043】**

第2增幅トランジスタ111は、ゲート端子に入力される信号であって、アナログメモリ10に蓄積されている信号電荷に基づく信号を増幅した増幅信号をソース端子から出力するトランジスタである。選択トランジスタ112は、単位画素1-5を選択し、第2增幅トランジスタ111によって増幅された信号を垂直信号線1-9に出力するトランジスタである。選択トランジスタ112のオン／オフは、垂直読み出し制御回路1-2からの選択パルス SELによって制御される。

**【0044】**

図4の破線D1は第1基板20と第2基板21の境界線を示している。第1基板20には、光電変換部101と、転送トランジスタ102と、FD103と、FDリセットトランジスタ104と、第1增幅トランジスタ105とが配置されている。第2基板21には、電流源106と、クランプ容量107と、サンプリングトランジスタ108と、クランプトランジスタ109と、アナログメモリ110と、第2增幅トランジスタ111と、選択トランジスタ112とが配置されている。

10

**【0045】**

第1基板20の第1增幅トランジスタ105から出力された増幅信号は、マイクロパッド22、マイクロバンプ24、およびマイクロパッド23を介して第2基板21へ出力される。また、電源電圧VDDおよび基準電圧VREFは、マイクロパッド25、マイクロバンプ27、およびマイクロパッド26を介して第1基板20と第2基板21の間で授受される。

20

**【0046】**

図4では、マイクロパッド22、マイクロバンプ24、マイクロパッド23を含む接続部が第1增幅トランジスタ105のソース端子と、電流源106のドレイン端子およびクランプ容量107の一端との間の経路に配置されているが、これに限らない。接続部は、光電変換素子101からアナログメモリ110までの電気的に接続された経路上のどこに配置されていてもよい。

**【0047】**

図5は、第1基板20と第2基板21の境界線の例を示している。破線D1～D5は、第1基板20と第2基板21の境界線として可能な例を示している。第1基板20と第2基板21の境界線は、破線D1～D5のいずれであってもよく、第1の基板20に光電変換素子101が配置され、第2の基板にアナログメモリ110が配置されれば良い。破線D1については上述した通りである。破線D2が示す例では、光電変換素子101の他端と、転送トランジスタ102のドレイン端子との間の経路に接続部が配置される。破線D3が示す例では、転送トランジスタ102のソース端子と、FD103の一端、FDリセットトランジスタ104のソース端子、および第1增幅トランジスタ105のゲート端子との間の経路に接続部が配置される。

30

**【0048】**

破線D4が示す例では、クランプ容量107の他端と、サンプリングトランジスタ108のドレイン端子との間の経路に接続部が配置される。破線D5が示す例では、サンプリングトランジスタ108のソース端子と、クランプトランジスタ109のソース端子、アナログメモリ110の一端、および第2增幅トランジスタ111のゲート端子との間の経路に接続部が配置される。

40

**【0049】**

サンプリングトランジスタ108およびアナログメモリ110は、光電変換部101から出力された信号を保持する信号保持部を構成する。サンプリングトランジスタ108のドレイン端子（第1の端子）に、光電変換部101から出力された信号電荷に対応する信号が入力されると、サンプリングトランジスタ108は、ドレイン端子に入力された信号をサンプルホールドし、サンプルホールドした信号をソース端子（第2の端子）から出力する。アナログメモリ110は、サンプリングトランジスタ108のソース端子から出力された信号を保持する。

**【0050】**

上述したように、FDリセットトランジスタ104は、ドレイン端子（第3の端子）が、基

50

準電圧VREFを供給する基準電圧源に接続され、ソース端子（第4の端子）が、転送トランジスタ102を介して光電変換部101に接続され、光電変換部101をリセットする。また、以下で詳細に説明するように、FDリセットトランジスタ104は、アナログメモリ110に蓄積された信号電荷に基づく信号を読み出す読み出し期間に、FD103の一端および第1増幅トランジスタ105のゲート端子の電位を、基準電圧源から供給される固定電位（VREF）に応じた電位に固定することにより、サンプリングトランジスタ108のドレイン端子の電位を固定する。このため、 $1/f$ ノイズなどのノイズによるサンプリングトランジスタ108のドレイン端子の電位の変動を抑制することが可能となり、ノイズ耐性を向上することができる。

#### 【0051】

10

次に、図6を参照し、単位画素1-5の動作を説明する。図6は、垂直読み出し制御回路1-2から行毎に単位画素1-5に供給される制御信号を示している。以下では、全ての単位画素1-5を指す場合、全画素と記載する。

#### 【0052】

##### [蓄積期間の動作]

蓄積期間は全画素で共通の期間であり、全画素で同時に動作が行われる。まず、転送パルス TX、FDリセットパルス RSTがL（Low）レベルからH（High）レベルに変化することで、転送トランジスタ102とFDリセットトランジスタ104がオンとなる。これによって、全画素の光電変換部101がリセットされる。続いて、転送パルス TXとFDリセットパルス RSTがHレベルからLレベルに変化することで、転送トランジスタ102とFDリセットトランジスタ104がオフとなる。これによって、全画素のリセットが終了し、全画素の露光（信号電荷の蓄積）が一括して開始される（露光期間の開始）。

20

#### 【0053】

##### [転送期間の動作]

転送期間は全画素で共通の期間であり、全画素で同時に動作が行われる。まず、FDリセットパルス RSTがLレベルからHレベルに変化することで、FDリセットトランジスタ104がオンとなる。これによって、全画素のFD103がリセットされる。同時に、クランプ＆メモリリセットパルス CLがLレベルからHレベルに変化することで、クランプトランジスタ109がオンとなる。これによって、全画素のアナログメモリ110がリセットされる。

30

#### 【0054】

同時に、サンプルパルス SHがLレベルからHレベルに変化することで、サンプリングトランジスタ108がオンとなる。これによって、全画素のクランプ容量107の他端の電位が基準電圧VREFにリセットされると共に、全画素のサンプリングトランジスタ108がクランプ容量107の他端の電位のサンプルホールドを開始する。

#### 【0055】

続いて、FDリセットパルス RSTがHレベルからLレベルに変化することで、FDリセットトランジスタ104がオフとなる。これによって、全画素のFD103のリセットが終了する。続いて、クランプ＆メモリリセットパルス CLがHレベルからLレベルに変化することで、クランプトランジスタ109がオフとなる。これによって、全画素のアナログメモリ110のリセットが終了する。この時点でクランプ容量107は、第1増幅トランジスタ105から出力される増幅信号（FD103のリセット後の増幅信号）をクランプしている。

40

#### 【0056】

続いて、転送パルス TXがLレベルからHレベルに変化することで、転送トランジスタ102がオンとなる。これによって、全画素の光電変換部101に蓄積されている信号電荷が、転送トランジスタ102を介してFD103に転送され、FD103に蓄積される。これによって、全画素の露光（信号電荷の蓄積）が終了する。続いて、転送パルス TXがHレベルからLレベルに変化することで、転送トランジスタ102がオフとなる。

#### 【0057】

続いて、サンプルパルス SHがHレベルからLレベルに変化することで、サンプリングトランジスタ108がオフとなる。これによって、全画素のサンプリングトランジスタ108がク

50

ランプ容量107の他端の電位のサンプルホールドを終了する。この時点でクランプ容量107は、第1増幅トランジスタ105から出力される増幅信号（光電変換部101からFD103に信号電荷が転送された後の増幅信号）をクランプしている。

#### 【0058】

クランプ容量107およびサンプリングトランジスタ108の働きにより、光電変換部101で発生した信号電荷に基づくFD103の一端の電位の変動に相当する分の信号電荷がアナログメモリ110に蓄積される。これによって、FDリセットトランジスタ104の動作によるリセットノイズや、第1増幅トランジスタ105の回路閾値のばらつきによるノイズ等の、第1基板20で発生するノイズを除去することができる。

#### 【0059】

10

##### [読み出し期間の動作]

読み出し期間では、アナログメモリ110に蓄積されている信号電荷に基づく信号が行毎に順次読み出される。まず、FDリセットパルス RSTがLレベルからHレベルに変化することで、FDリセットトランジスタ104がオンとなる。これによって、FD103の一端および第1増幅トランジスタ105のゲート端子の電位が、基準電圧源から供給される固定電位（VREF）に応じた電位に固定される。

#### 【0060】

20

クランプ容量107の一端に接続されている第1増幅トランジスタ105のゲート端子の電位が固定されるため、クランプ容量の一端の電位も固定され、サンプリングトランジスタ108のドレイン端子の電位も固定される。読み出し期間中、FDリセットトランジスタ104はオンのままである。

#### 【0061】

続いて、選択パルス SELがLレベルからHレベルに変化することで、選択トランジスタ112がオンとなる。これによって、アナログメモリ110に蓄積された信号電荷に基づく画素信号レベルが垂直信号線1-9へ出力される。

#### 【0062】

続いて、クランプ&メモリリセットパルス CLがLレベルからHレベルに変化することで、クランプトランジスタ109がオンとなる。これによって、アナログメモリ110がリセットされ、垂直信号線1-9へリセットレベルが出力される。

#### 【0063】

30

続いて、選択パルス SELがHレベルからLレベルに変化することで、選択トランジスタ112がオフとなる。同時に、クランプ&メモリリセットパルス CLがHレベルからLレベルに変化することで、クランプトランジスタ109がオフとなる。

#### 【0064】

カラム信号処理部1-6は、読み出された画素信号レベルとリセットレベルとの差分を演算することで、アナログメモリ110から画素信号の読み出しを行う際に発生する読み出しノイズの除去を行う。上記の動作が1行ずつ順次行われることで、全画素の画素信号が読み出される。上記の動作では、全画素の光電変換部101に蓄積された信号電荷が一括して転送されるので、信号電荷の蓄積の同時性を実現することができる。

#### 【0065】

40

上述したように、本実施形態によれば、FDリセットトランジスタ104が、読み出し期間に、FD103の一端および第1増幅トランジスタ105のゲート端子の電位を固定電位に応じた電位に固定することにより、サンプリングトランジスタ108のドレイン端子の電位が固定される。このため、 $1/f$ ノイズなどのノイズによるサンプリングトランジスタ108のドレイン端子の電位の変動を抑制することが可能となり、ノイズ耐性を向上することができる。

#### 【0066】

次に、本実施形態の変形例を説明する。図7は、単位画素1-5の構成の他の例を示している。図4に示した構成と比較すると、図7ではクランプ容量107とクランプトランジスタ109が削除されており、サンプリングトランジスタ108のドレイン端子は第1増幅トランジス

50

タ105のソース端子および電流源106の一端に接続されている。上記以外の構成は、図4に示した構成と同一である。

#### 【 0 0 6 7 】

図7では、マイクロパッド22、マイクロバンプ24、マイクロパッド23を含む接続部が第1増幅トランジスタ105のソース端子と、電流源106のドレイン端子およびサンプリングトランジスタ108のドレイン端子との間の経路に配置されているが、これに限らない。接続部は、光電変換素子101からアナログメモリ110までの電気的に接続された経路上のどこに配置されていてもよい

#### 【 0 0 6 8 】

図8、第1基板20と第2基板21の境界線の例を示している。破線D1～D5は、第1基板20と第2基板21の境界線として可能な例を示している。第1基板20と第2基板21の境界線は、破線D1～D5のいずれであってもよく、第1の基板20に光電変換素子101が配置され、第2の基板にアナログメモリ110が配置されれば良い。破線D1については前述した通りである。破線D2が示す例では、光電変換素子101の他端と、転送トランジスタ102のドレイン端子との間の経路に接続部が配置される。破線D3が示す例では、転送トランジスタ102のソース端子と、FD103の一端、FDリセットトランジスタ104のソース端子、および第1増幅トランジスタ105のゲート端子との間の経路に接続部が配置される。

10

#### 【 0 0 6 9 】

破線D4が示す例では、増幅トランジスタ105のソース端子および電流源106の一端と、サンプリングトランジスタ108のドレイン端子との間の経路に接続部が配置され、破線D5が示す例では、サンプリングトランジスタ108のソース端子と、アナログメモリ110の一端および第2増幅トランジスタ111のゲート端子との間の経路に接続部が配置される。

20

#### 【 0 0 7 0 】

次に、図9を参照し、図7に示す単位画素1-5の動作を説明する。図9は、垂直読み出し制御回路1-2から行毎に単位画素1-5に供給される制御信号を示している。以下では、図6に示した動作とは異なる動作を中心に説明する。

#### 【 0 0 7 1 】

蓄積期間における動作は、図6に示した動作と同一である。転送期間では、全画素のFD103がリセットされた後、光電変換部101に蓄積されている信号電荷が、転送トランジスタ102を介してFD103に転送され、FD103に蓄積される。同時に、このときの第1増幅トランジスタ105のソース端子から出力される増幅信号がアナログメモリ110に入力され、増幅信号に基づく信号電荷がアナログメモリ110に蓄積される。

30

#### 【 0 0 7 2 】

読み出し期間では、まず、FDリセットパルス RSTがLレベルからHレベルに変化することで、FDリセットトランジスタ104がオンとなる。これによって、FD103の一端および第1増幅トランジスタ105のゲート端子の電位が、基準電圧源から供給される固定電位 (VREF) に応じた電位に固定される。前述したように、サンプリングトランジスタ108のドレイン端子の電位も固定される。

#### 【 0 0 7 3 】

続いて、選択パルス SELがLレベルからHレベルに変化することで、選択トランジスタ102がオンとなる。これによって、アナログメモリ110に蓄積された信号電荷に基づく画素信号レベルが垂直信号線1-9へ出力される。

40

#### 【 0 0 7 4 】

続いて、サンプルパルス SHがLレベルからHレベルに変化することで、サンプリングトランジスタ108がオンとなる。このとき、FDリセットトランジスタ104がオンとなっており、FD103がリセットされているので、リセット後のFD103の一端の電位に基づく増幅信号が第1増幅トランジスタ105のソース端子から出力される。増幅信号はアナログメモリ110に入力され、増幅信号に基づく信号電荷がアナログメモリ110に蓄積される。このとき、選択トランジスタ102がオンとなっているので、リセット後のFD103の一端の電位に基づくりセットレベルが垂直信号線1-9へ出力される。

50

**【0075】**

続いて、選択パルス SELがHレベルからLレベルに変化することで、選択トランジスタ12がオフとなる。同時に、サンプルパルス SHがHレベルからLレベルに変化することで、サンプリングトランジスタ108がオフとなる。

**【0076】**

上記の変形例においても、サンプリングトランジスタ108のドレイン端子の電位が固定されるため、 $1/f$  ノイズなどのノイズによるサンプリングトランジスタ108のドレイン端子の電位の変動を抑制することが可能となり、ノイズ耐性を向上することができる。

**【0077】**

(第2の実施形態) 10

次に、本発明の第2の実施形態を説明する。本実施形態による撮像装置の構成は、第1の実施形態による撮像装置の構成と同様である。ただし、本実施形態では、電流源106は、オフモード、電流設定モード、低インピーダンス設定モードの3つのモードを切り替えて動作することが可能である。

**【0078】**

以下、図10を参照し、単位画素1-5の動作を説明する。図10は、垂直読み出し制御回路1-2から行毎に単位画素1-5に供給される制御信号と電流源106のモードを示している。以下では、図6に示した動作とは異なる動作を中心に説明する。

**【0079】**

蓄積期間では、電流源106はオフモードに設定され、動作を停止している。転送期間では、電流源106は電流設定モードに設定され、第1增幅トランジスタ105を駆動する電流を出力する。電流設定モードに設定されたときの電流源106のインピーダンスは、低インピーダンス設定モードに設定されたときの電流源106のインピーダンスよりも高くなる。 20

**【0080】**

読み出し期間では、FDリセットトランジスタ104はオフである。また、電流源106は低インピーダンス設定モードに設定される。このとき、第1增幅トランジスタ105のソース端子およびクランプ容量107の一端に接続された電流源106の一端の電位は電流源106の他端の電位と略同一となる。例えば、電流源106がトランジスタで構成されている場合、電流源106のドレイン端子とソース端子のそれぞれの電位が略同一となる。これによって、クランプ容量107の一端の電位は、電流源106の他端の電位すなわちグランド電位と略同一の電位に固定される。したがって、サンプリングトランジスタ108のドレイン端子の電位も固定される。 30

**【0081】**

上述したように、本実施形態によれば、読み出し期間に、電流源106の一端と他端の電位が略同一の電位に固定されることにより、サンプリングトランジスタ108のドレイン端子の電位が固定される。このため、 $1/f$  ノイズなどのノイズによるサンプリングトランジスタ108のドレイン端子の電位の変動を抑制することが可能となり、ノイズ耐性を向上することができる。

**【0082】**

本実施形態の変形例として、図7に示す単位画素1-5において、読み出し期間に、FDリセットトランジスタ104がオンとなる代わりに電流源106が低インピーダンス設定モードで動作してもよい。 40

**【0083】**

(第3の実施形態)

次に、本発明の第3の実施形態を説明する。本実施形態による撮像装置の構成は、単位画素1-5を除いて、第1の実施形態による撮像装置の構成と同様である。

**【0084】**

図11は、本実施形態における単位画素1-5の構成を示している。図11に示す単位画素1-5では、クランプトランジスタ109が配置されている位置が、図4に示す単位画素1-5とは異なる。図11では、クランプトランジスタ109のソース端子(第3の端子)はクランプ容量1 50

07の他端およびサンプリングトランジスタ108のドレイン端子に接続され、クランプトランジスタ109のドレイン端子（第4の端子）は、基準電圧VREFを供給する基準電圧源に接続されている。上記以外の構成は、図4に示す単位画素1-5の構成と同一である。

#### 【0085】

図11では、マイクロパッド22、マイクロバンプ24、マイクロパッド23を含む接続部が第1増幅トランジスタ105のソース端子と、電流源106のドレイン端子およびクランプ容量107の一端との間の経路に配置されているが、これに限らない。接続部は、光電変換素子101からアナログメモリ110までの電気的に接続された経路上のどこに配置されていてもよい。

#### 【0086】

図12は、第1基板20と第2基板21の境界線の例を示している。破線D1～D5は、第1基板20と第2基板21の境界線として可能な例を示している。第1基板20と第2基板21の境界線は、破線D1～D5のいずれであってもよく、第1の基板20に光電変換素子101が配置され、第2の基板にアナログメモリ110が配置されれば良い。破線D1については前述した通りである。破線D2が示す例では、光電変換素子101の他端と、転送トランジスタ102のドレイン端子との間の経路に接続部が配置される。破線D3が示す例では、転送トランジスタ102のソース端子と、FD103の一端、FDリセットトランジスタ104のソース端子、および第1増幅トランジスタ105のゲート端子との間の経路に接続部が配置される。

#### 【0087】

破線D4が示す例では、クランプトランジスタ109のソース端子およびクランプ容量107の他端と、サンプリングトランジスタ108のドレイン端子との間の経路に接続部が配置され、破線D5が示す例では、サンプリングトランジスタ108のソース端子と、アナログメモリ110の一端および第2増幅トランジスタ111のゲート端子との間の経路に接続部が配置される。

以下で詳細に説明するように、クランプトランジスタ109は、読み出し期間に、サンプリングトランジスタのドレイン端子の電位を、基準電圧源から供給される固定電位（VREF）に応じた電位に固定する。

#### 【0088】

以下、図13を参照し、単位画素1-5の動作を説明する。図13は、垂直読み出し制御回路1-2から行毎に単位画素1-5に供給される制御信号を示している。以下では、図6に示した動作とは異なる動作を中心に説明する。

#### 【0089】

蓄積期間および転送期間における動作は、図6に示した動作と同一である。読み出し期間では、FDリセットトランジスタ104はオフである。また、クランプ&メモリリセットパルス CLがLレベルからHレベルに変化することで、クランプトランジスタ109がオンとなる。これによって、サンプリングトランジスタ108のドレイン端子の電位が、基準電圧源から供給される固定電位（VREF）に応じた電位に固定される。

#### 【0090】

続いて、選択パルス SELがLレベルからHレベルに変化することで、選択トランジスタ112がオンとなる。これによって、アナログメモリ110に蓄積された信号電荷に基づく画素信号レベルが垂直信号線1-9へ出力される。

#### 【0091】

続いて、サンプルパルス SHがLレベルからHレベルに変化することで、サンプリングトランジスタ108がオンとなる。これによって、アナログメモリ110がリセットされ、垂直信号線1-9へリセットレベルが出力される。

#### 【0092】

続いて、選択パルス SELがHレベルからLレベルに変化することで、選択トランジスタ112がオフとなる。同時に、サンプルパルス SHがHレベルからLレベルに変化することで、サンプリングトランジスタ108がオフとなる。

#### 【0093】

10

20

30

40

50

上述したように、本実施形態によれば、クランプトランジスタ109が、読み出し期間に、サンプリングトランジスタ108のドレイン端子の電位を固定電位に応じた電位に固定する。このため、 $1/f$ ノイズなどのノイズによるサンプリングトランジスタ108のドレイン端子の電位の変動を抑制することが可能となり、ノイズ耐性を向上することができる。

#### 【0094】

##### (第4の実施形態)

次に、本発明の第4の実施形態を説明する。本実施形態による撮像装置の構成は、単位画素1-5を除いて、第3の実施形態による撮像装置の構成と同様である。

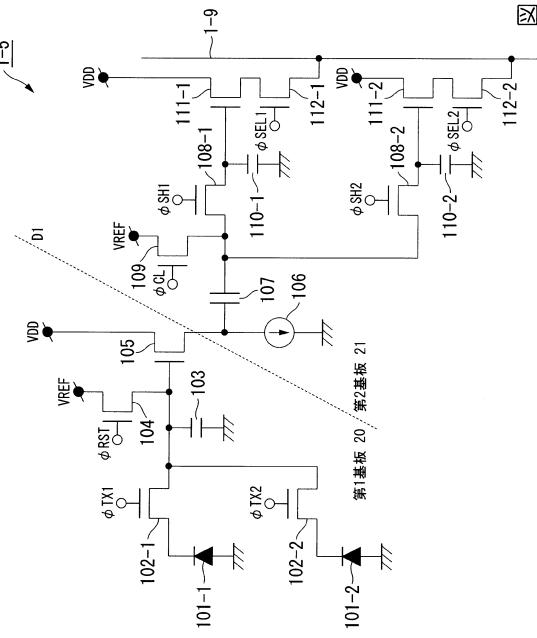

#### 【0095】

図14は、垂直方向に隣接した2つの単位画素1-5の回路構成を示している。単位画素1-5(2つ)は、光電変換部101-1, 101-2と、転送トランジスタ102-1, 102-2と、FD103と、FDリセットトランジスタ104と、第1增幅トランジスタ105と、電流源106と、クランプ容量107と、サンプリングトランジスタ108-1, 108-2と、クランプトランジスタ109と、アナログメモリ110-1, 110-2と、第2增幅トランジスタ111-1, 111-2と、選択トランジスタ112-1, 112-2とを有する。10

#### 【0096】

図14には第1の単位画素の回路要素と第2の単位画素の回路要素とが含まれる。第1の単位画素は、光電変換部101-1と、転送トランジスタ102-1と、FD103と、FDリセットトランジスタ104と、第1增幅トランジスタ105と、電流源106と、クランプ容量107と、サンプリングトランジスタ108-1と、クランプトランジスタ109と、アナログメモリ110-1と、第2增幅トランジスタ111-1と、選択トランジスタ112-1とを有する。第2の単位画素は、光電変換部101-2と、転送トランジスタ102-2と、FD103と、FDリセットトランジスタ104と、第1增幅トランジスタ105と、電流源106と、クランプ容量107と、サンプリングトランジスタ108-2と、クランプトランジスタ109と、アナログメモリ110-2と、第2增幅トランジスタ111-2と、選択トランジスタ112-2とを有する。FD103と、FDリセットトランジスタ104と、第1增幅トランジスタ105と、電流源106と、クランプ容量107と、クランプトランジスタ109とは、第1の単位画素と第2の単位画素とで共有されている。20

#### 【0097】

2つの単位画素1-5のそれぞれを単独で見た場合に、それぞれの単位画素1-5を構成する回路要素の接続関係は、図11に示す単位画素1-5における回路要素の接続関係と同一である。転送トランジスタ102-1, 102-2のそれぞれのソース端子は、FD103の一端、FDリセットトランジスタ104のソース端子、第1增幅トランジスタ105のゲート端子に共通に接続されている。また、サンプリングトランジスタ108-1, 108-2のそれぞれのドレイン端子は、クランプ容量107の他端およびクランプトランジスタ109のソース端子に共通に接続されている。30

#### 【0098】

転送トランジスタ102-1のゲート端子には垂直読み出し制御回路1-2から転送パルス TX1が供給され、転送トランジスタ102-2のゲート端子には垂直読み出し制御回路1-2から転送パルス TX2が供給される。サンプリングトランジスタ108-1のゲート端子には垂直読み出し制御回路1-2からサンプルパルス SH1が供給され、サンプリングトランジスタ108-2のゲート端子には垂直読み出し制御回路1-2からサンプルパルス SH2が供給される。選択トランジスタ112-1のゲート端子には垂直読み出し制御回路1-2から選択パルス SEL1が供給され、選択トランジスタ112-2のゲート端子には垂直読み出し制御回路1-2から選択パルス SEL2が供給される。40

#### 【0099】

図14では、マイクロパッド22、マイクロバンプ24、マイクロパッド23を含む接続部が第1增幅トランジスタ105のソース端子と、電流源106のドレイン端子およびクランプ容量107の一端との間の経路に配置されているが、これに限らない。接続部は、光電変換素子101からアナログメモリ110までの電気的に接続された経路上のどこに配置されていてもよい。50

**【 0 1 0 0 】**

図15は、第1基板20と第2基板21の境界線の例を示している。破線D1～D5は、第1基板20と第2基板21の境界線として可能な例を示している。第1基板20と第2基板21の境界線は、破線D1～D5のいずれであってもよく、第1の基板20に光電変換素子101-1, 101-2が配置され、第2の基板にアナログメモリ110-1, 110-2が配置されれば良い。破線D1については前述した通りである。破線D2が示す例では、光電変換素子101-1, 101-2の他端と、転送トランジスタ102のドレイン端子との間の経路に接続部が配置される。破線D3が示す例では、転送トランジスタ102-1, 102-2のソース端子と、FD103の一端、FDリセットトランジスタ104のソース端子、および第1増幅トランジスタ105のゲート端子との間の経路に接続部が配置される。

10

**【 0 1 0 1 】**

破線D4が示す例では、クランプトランジスタ109のソース端子およびクランプ容量107の他端と、サンプリングトランジスタ108-1, 108-2のドレイン端子との間の経路に接続部が配置され、破線D5が示す例では、サンプリングトランジスタ108-1, 108-2のソース端子と、アナログメモリ110-1, 110-2の一端および第2増幅トランジスタ111-1, 111-2のゲート端子との間の経路に接続部が配置される。

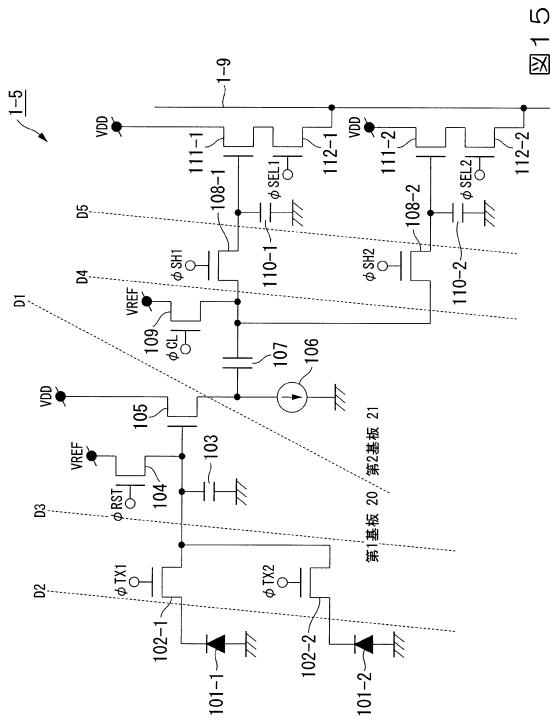

**【 0 1 0 2 】**

次に、図16を参照し、単位画素1-5の動作を説明する。図16は、垂直読み出し制御回路1-2から行毎に単位画素1-5に供給される制御信号を示している。以下では、図14に示した2つの単位画素1-5の単位で動作を説明する。

20

**【 0 1 0 3 】****[ 蓄積期間の動作 ]**

蓄積期間では、2つの単位画素1-5のそれぞれの光電変換部101-1, 101-2のリセットが単位画素毎に行われる。第1の単位画素の光電変換部101-1のリセットが行われた後、第2の単位画素の光電変換部101-2のリセットが行われる。蓄積期間におけるそれぞれの単位画素1-5の動作は、図13に示す蓄積期間における単位画素1-5の動作と同一である。

**【 0 1 0 4 】****[ 転送期間の動作 ]**

転送期間では、2つの単位画素1-5で共通のFD103のリセットと、2つの単位画素1-5のそれぞれの光電変換部101-1, 101-2に蓄積されている信号電荷の転送とを含む動作が単位画素毎に行われる。FD103のリセットと第1の単位画素の信号電荷の転送とが行われた後、FD103のリセットと第2の単位画素の信号電荷の転送とが行われる。転送期間におけるそれぞれの単位画素1-5の動作は、図13に示す転送期間における単位画素1-5の動作と同一である。

30

**【 0 1 0 5 】****[ 読み出し期間の動作 ]**

読み出し期間では、2つの単位画素1-5のそれぞれの信号の読み出しが単位画素毎に行われる。第1の単位画素の信号の読み出しが行われた後、第2の単位画素の信号の読み出しが行われる。読み出し期間におけるそれぞれの単位画素1-5の動作は、図13に示す読み出し期間における単位画素1-5の動作と同一である。読み出し期間中、クランプトランジスタ109はオンのままである。これによって、サンプリングトランジスタ108-1, 108-2のそれぞれのドレイン端子の電位が、基準電圧源から供給される固定電位(VREF)に応じた電位に固定される。

40

**【 0 1 0 6 】**

上述したように、本実施形態によれば、クランプトランジスタ109が、読み出し期間に、サンプリングトランジスタ108-1, 108-2のそれぞれのドレイン端子の電位を固定電位に応じた電位に固定する。このため、 $1/f$ ノイズなどのノイズによるサンプリングトランジスタ108-1, 108-2のそれぞれのドレイン端子の電位の変動を抑制することが可能となり、ノイズ耐性を向上することができる。

**【 0 1 0 7 】**

50

また、FD103、FDリセットトランジスタ104、第1増幅トランジスタ105、電流源106、クランプ容量107に加えて、クランプトランジスタ109を複数の単位画素1-5が共有するので、回路面積を縮小することができる。本実施形態では、2つの単位画素1-5が、クランプトランジスタ109を含む一部の回路要素を共有する例を示したが、3つ以上の単位画素1-5が一部の回路要素を共有してもよい。

#### 【0108】

##### (第5の実施形態)

次に、本発明の第5の実施形態を説明する。本実施形態による撮像装置の構成は、単位画素1-5を除いて、第1の実施形態による撮像装置の構成と同様である。

#### 【0109】

図17は、本実施形態における単位画素1-5の構成を示している。図17に示す単位画素1-5では、第1増幅トランジスタ105、電流源106、クランプ容量107、クランプトランジスタ109が削除され、第2転送トランジスタ114が追加され、転送トランジスタ102が第1転送トランジスタ113に変更されている点が、図4に示す単位画素1-5とは異なる。

#### 【0110】

図17では、第2転送トランジスタ114のドレイン端子は第1転送トランジスタ113のソース端子およびFD103の一端に接続され、第2転送トランジスタ114のソース端子はサンプリングトランジスタ108のドレイン端子に接続されている。第2転送トランジスタ113のゲート端子は垂直読み出し制御回路1-2に接続されており、転送パルス TX2が供給される。また、第1転送トランジスタ113のゲート端子には垂直読み出し制御回路1-2から転送パルス TX1が供給される。上記以外の構成は、図4に示す単位画素1-5の構成と同一である。

#### 【0111】

図17では、マイクロパッド22、マイクロバンプ24、マイクロパッド23を含む接続部が第2転送トランジスタ114のソース端子と、FDリセットトランジスタ104のソース端子と、サンプリングトランジスタ108のドレイン端子との間の経路に配置されているが、これに限らない。接続部は、光電変換素子101からアナログメモリ110までの電気的に接続された経路上のどこに配置っていてもよい。

#### 【0112】

図18は、第1基板20と第2基板21の境界線の例を示している。破線D1～D5は、第1基板20と第2基板21の境界線として可能な例を示している。第1基板20と第2基板21の境界線は、破線D1～D5のいずれであってもよく、第1の基板20に光電変換素子101が配置され、第2の基板にアナログメモリ110が配置されれば良い。破線D1については前述した通りである。破線D2が示す例では、光電変換素子101の他端と、第1転送トランジスタ113のドレイン端子との間の経路に接続部が配置される。破線D3が示す例では、第1転送トランジスタ113のソース端子と、FD103の一端および第2転送トランジスタ114のドレイン端子との間の経路に接続部が配置される。

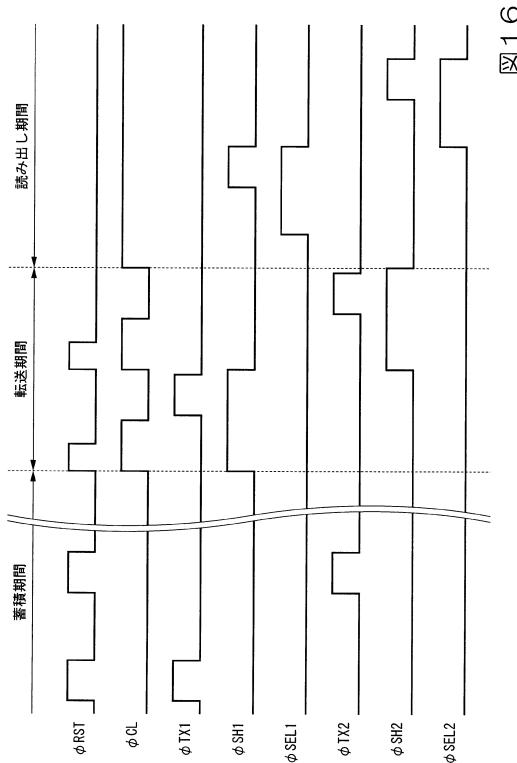

#### 【0113】

破線D4が示す例では、第2転送トランジスタ114のソース端子と、FDリセットトランジスタ104のソース端子およびサンプリングトランジスタ108のドレイン端子との間の経路に接続部が配置され、破線D5が示す例では、サンプリングトランジスタ108のソース端子と、アナログメモリ110の一端および第2増幅トランジスタ111のゲート端子との間の経路に接続部が配置される。

#### 【0114】

次に、図19を参照し、単位画素1-5の動作を説明する。図19は、垂直読み出し制御回路1-2から行毎に単位画素1-5に供給される制御信号を示している。

#### 【0115】

##### [蓄積期間の動作]

蓄積期間は全画素で共通の期間であり、全画素で同時に動作が行われる。蓄積期間の開始時にFDリセットパルス RST、転送パルス TX2、サンプルパルス SHはHレベルになつており、FDリセットトランジスタ104、第2転送トランジスタ114、サンプリングトランジ

10

20

30

40

50

スタ108はオンになっている。これによって、全画素のFD103およびアナログメモリ110はリセットされている。

#### 【 0 1 1 6 】

まず、転送パルス TX1がLレベルからHレベルに変化することで、第1転送トランジスタ113がオンとなる。これによって、全画素の光電変換部101がリセットされる。続いて、転送パルス TX1がHレベルからLレベルに変化することで、第1転送トランジスタ113がオフとなる。これによって、全画素のリセットが終了し、全画素の露光（信号電荷の蓄積）が一括して開始される（露光期間の開始）。

#### 【 0 1 1 7 】

[ 転送期間の動作 ] 10

転送期間は全画素で共通の期間であり、全画素で同時に動作が行われる。まず、転送パルス TX2がHレベルからLレベルに変化することで、第2転送トランジスタ114がオフとなる。続いて、転送パルス TX1がLレベルからHレベルに変化することで、第1転送トランジスタ113がオンとなる。これによって、光電変換部101に蓄積されている信号電荷が、第1転送トランジスタ113を介してFD103に転送され、FD103に蓄積される。これによって、全画素の露光（信号電荷の蓄積）が終了する。

#### 【 0 1 1 8 】

続いて、FDリセットパルス RSTがHレベルからLレベルに変化することで、FDリセットトランジスタ104がオフとなる。続いて、転送パルス TX1がHレベルからLレベルに変化することで、第1転送トランジスタ113がオフとなる。続いて、転送パルス TX2がLレベルからHレベルに変化することで、第2転送トランジスタ114がオンとなる。これによって、FD103に蓄積されている信号電荷が、第2転送トランジスタ114およびサンプリングトランジスタ108を介してアナログメモリ110に転送され、アナログメモリ110に蓄積される。 20

#### 【 0 1 1 9 】

続いて、サンプルパルス SHがHレベルからLレベルに変化することで、サンプリングトランジスタ108がオフとなる。続いて、FDリセットパルス RSTがLレベルからHレベルに変化することで、FDリセットトランジスタ104がオンとなる。これによって、サンプリングトランジスタ108のドレイン端子の電位が、基準電圧源から供給される固定電位（VREF）に応じた電位に固定される。

#### 【 0 1 2 0 】

[ 読み出し期間の動作 ] 30

読み出し期間では、アナログメモリ110に蓄積されている信号電荷に基づく信号が行毎に順次読み出される。読み出し期間中、FDリセットトランジスタ104はオンのままであり、サンプリングトランジスタ108のドレイン端子の電位は固定されている。

#### 【 0 1 2 1 】

まず、選択パルス SELがLレベルからHレベルに変化することで、選択トランジスタ112がオンとなる。これによって、アナログメモリ110に蓄積された信号電荷に基づく画素信号レベルが垂直信号線1-9へ出力される。

#### 【 0 1 2 2 】

続いて、サンプルパルス SHがLレベルからHレベルに変化することで、サンプリングトランジスタ108がオンとなる。これによって、アナログメモリ110がリセットされ、垂直信号線1-9へリセットレベルが出力される。続いて、選択パルス SELがHレベルからLレベルに変化することで、選択トランジスタ112がオフとなる。 40

#### 【 0 1 2 3 】

カラム信号処理部1-6は、読み出された画素信号レベルとリセットレベルとの差分を演算することで、アナログメモリ110から画素信号の読み出しを行う際に発生する読み出しノイズの除去を行う。上記の動作が1行ずつ順次行われることで、全画素の画素信号が読み出される。上記の動作では、全画素の光電変換部101に蓄積された信号電荷が一括して転送されるので、信号電荷の蓄積の同時性を実現することができる。

#### 【 0 1 2 4 】

50

上述したように、本実施形態によれば、FDリセットトランジスタ104が、読み出し期間に、サンプリングトランジスタ108のドレイン端子の電位を固定電位に応じた電位に固定する。このため、 $1/f$ ノイズなどによるサンプリングトランジスタ108のドレイン端子の電位の変動を抑制することが可能となり、ノイズ耐性を向上することができる。

#### 【0125】

以上、図面を参照して本発明の実施形態について詳述してきたが、具体的な構成は上記の実施形態に限られるものではなく、本発明の要旨を逸脱しない範囲の設計変更等も含まれる。上記では、2枚の基板が接続部で接続されている固体撮像装置の構成を示したが、3枚以上の基板が接続部で接続されていてもよい。3枚以上の基板が接続部で接続される固体撮像装置の場合、3枚以上の基板のうち2枚の基板が第1の基板と第2の基板に相当する

10

。

#### 【符号の説明】

#### 【0126】

1 固体撮像装置、2 レンズユニット部、3 画像処理装置、4 記録装置、5 カメラ制御装置、6 表示装置、7 デジタルカメラ、1-1 制御信号発生回路、1-2 垂直読み出し制御回路、1-3 水平読み出し制御回路、1-4 画素アレイ部、1-5 単位画素、1-6 カラム信号処理部、1-8 出力回路、101 光電変換部、102 転送トランジスタ、103 FD、104 FDリセットトランジスタ、105 第1増幅トランジスタ、106 電流源、107 クランプ容量、108 サンプリングトランジスタ、109 クランプトランジスタ、110 アナログメモリ、111 第2増幅トランジスタ、112 選択トランジスタ、113 第1転送トランジスタ、114 第2転送トランジスタ

20

【図1】

図1

【図2】

図2

【図3】

【図4】

【図5】

【図6】

【図 7】

【図 8】

【図 9】

【図 10】

【図 10】

【図11】

【図12】

【図13】

【図14】

【図 15】

【図 16】

【図 17】

【図 18】

【図19】

---

フロントページの続き

(74)代理人 100161702

弁理士 橋本 宏之

(72)発明者 加藤 秀樹

東京都渋谷区幡ヶ谷2丁目43番2号 オリンパス株式会社内

審査官 鈴木 明

(56)参考文献 特開2013-009301(JP,A)

特開2012-253593(JP,A)

特開2012-248952(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04N 5/30 - 5/378