(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-134912

(P2006-134912A)

(43) 公開日 平成18年5月25日(2006.5.25)

(51) Int.C1.

H01L 23/12

(2006.01)

F 1

H01L 23/12

501F

テーマコード(参考)

審査請求 未請求 請求項の数 35 O L (全 26 頁)

(21) 出願番号

特願2004-318891 (P2004-318891)

(22) 出願日

平成16年11月2日 (2004.11.2)

(71) 出願人 000005821

松下電器産業株式会社

大阪府門真市大字門真1006番地

(74) 代理人 100086405

弁理士 河宮 治

(74) 代理人 100100158

弁理士 鮫島 睦

(72) 発明者 辛島 靖治

大阪府門真市大字門真1006番地 松下

電器産業株式会社内

(72) 発明者 山下 嘉久

大阪府門真市大字門真1006番地 松下

電器産業株式会社内

最終頁に続く

(54) 【発明の名称】半導体モジュールおよびその製造方法、ならびにフィルムインターポーラ

## (57) 【要約】

【課題】 新規な微細ピッチ接続技術が用いられた半導体モジュールを提供すること。

【解決手段】 素子電極が形成された主面を有する半導体素子と、表面および裏面を有する絶縁樹脂層、ならびに前記絶縁樹脂層の裏面に形成された配線パターンを有するフィルム部材とを備える半導体モジュールであって、半導体素子の主面とフィルム部材の表面とが接するように、半導体素子とフィルム部材とが重ねられており、フィルム部材の配線パターンの一部分は、絶縁樹脂層を貫通して半導体素子の素子電極に接触している半導体モジュールを提供する。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

素子電極が形成された主面を有する半導体素子と、

表面および当該表面に対向する裏面を有する絶縁樹脂層、ならびに前記絶縁樹脂層の裏面に形成された配線パターンを有するフィルム部材と

を備える半導体モジュールであって、

前記半導体素子の主面と前記フィルム部材の絶縁樹脂層の表面とが接するように、前記半導体素子と前記フィルム部材とが重ねられており、

前記フィルム部材の配線パターンの一部分は、前記絶縁樹脂層を貫通して前記半導体素子の素子電極に接触している、半導体モジュール。

10

**【請求項 2】**

前記絶縁樹脂層は、透明樹脂から成る、請求項 1 に記載の半導体モジュール。

**【請求項 3】**

前記絶縁樹脂層は、ポリイミドまたはアラミドから成る、請求項 1 または 2 に記載の半導体モジュール。

**【請求項 4】**

前記絶縁樹脂層は、前記半導体素子の主面に絶縁樹脂を塗布して形成された塗布膜である、請求項 1 ~ 3 のいずれかに記載の半導体モジュール。

**【請求項 5】**

前記半導体素子は、半導体ペアチップまたはチップ・サイズ・パッケージである、請求項 1 ~ 4 のいずれかに記載の半導体モジュール。

20

**【請求項 6】**

前記配線パターンは、前記絶縁樹脂層の裏面に埋め込まれている、請求項 1 ~ 5 のいずれかに記載の半導体モジュール。

**【請求項 7】**

前記絶縁樹脂層を貫通した状態の配線パターンの一部分は、配線パターンの一部分が前記絶縁樹脂層の内部へと押し込まれることによって形成されている、請求項 1 ~ 6 のいずれかに記載の半導体モジュール。

**【請求項 8】**

前記配線パターンの一部分の断面は、略 U 形状を有する、請求項 1 ~ 7 のいずれかに記載の半導体モジュール。

30

**【請求項 9】**

前記接触によって形成される接合部位は、配線パターンと素子電極とを電気的に接続する機能を有する、請求項 1 ~ 8 のいずれかに記載の半導体モジュール。

**【請求項 10】**

前記接触により形成される接合部位が、超音波接合されている、請求項 1 ~ 9 のいずれかに記載の半導体モジュール。

40

**【請求項 11】**

前記接合部位は、複数種の金属から成る合金を含んで成る、請求項 1 0 に記載の半導体モジュール。

**【請求項 12】**

前記複数種の金属は、アルミニウム、金、銀、プラチナおよびバナジウムから成る群から選択される、請求項 1 1 に記載の半導体モジュール。

**【請求項 13】**

前記半導体素子は、複数の前記半導体素子から成る、請求項 1 ~ 1 2 のいずれかに記載の半導体モジュール。

**【請求項 14】**

前記フィルム部材の表面および前記表面に対向する裏面の寸法は、前記半導体素子の主面の寸法と略同じである、請求項 1 ~ 1 3 のいずれかに記載の半導体モジュール。

50

**【請求項 15】**

前記フィルム部材の表面および前記表面に対向する裏面の寸法は、前記半導体素子の正面の寸法よりも大きい、請求項1～13のいずれかに記載の半導体モジュール。

【請求項16】

半田ボールが、前記フィルム部材の裏面に形成されている、請求項1～15のいずれかに記載の半導体モジュール。

【請求項17】

配線基板に電気的に接続されているインターポーザを更に備える半導体モジュールであって、前記フィルム部材が前記インターポーザに電気的に接続されている、請求項1～16のいずれかに記載の半導体モジュール。

【請求項18】

前記フィルム部材に重ねられるように、更なるフィルム部材が積層している、請求項1～17のいずれかに記載の半導体モジュール。

【請求項19】

前記半導体素子は、半導体ウェハである、請求項18に記載の半導体モジュール。

【請求項20】

素子電極が形成された正面および前記正面に対向する裏面を有する半導体素子と、表面および当該表面に対向する裏面を有する絶縁樹脂層、ならびに前記絶縁樹脂層の裏面に形成された配線パターンを有するフィルム部材と、

配線基板と

を備える半導体モジュールであって、

前記半導体素子の裏面が前記配線基板と接するように、前記半導体素子が前記配線基板に載置されており、

前記フィルム部材の表面および前記表面に対向する裏面の寸法が、前記半導体素子の正面の寸法よりも大きく、前記半導体素子の正面と前記フィルム部材の絶縁樹脂層の表面とが接するように、前記フィルム部材が前記半導体素子に載置され、前記フィルム部材の少なくとも一部が前記配線基板にまで延在しており、

前記フィルム部材の配線パターンの一部分の少なくとも1つが、前記絶縁樹脂層を貫通した状態で前記半導体素子の素子電極に接触している一方、前記フィルム部材の配線パターンの一部分の残りの少なくとも1つが、前記絶縁樹脂層を貫通して前記配線基板上に形成された電極に接触している、半導体モジュール。

【請求項21】

前記絶縁樹脂層は、透明樹脂から成る、請求項20に記載の半導体モジュール。

【請求項22】

前記絶縁樹脂層は、ポリイミドまたはアラミドから成る、請求項20または21に記載の半導体モジュール。

【請求項23】

前記半導体素子は、半導体ベアチップまたはチップ・サイズ・パッケージである、請求項20～22のいずれかに記載の半導体モジュール。

【請求項24】

素子電極が形成された正面および前記正面に対向する裏面を有する半導体素子と、表面および当該表面に対向する裏面を有する絶縁樹脂層、ならびに前記絶縁樹脂層の裏面に形成された配線パターンを有するフィルム部材と

を備える半導体モジュールであって、

前記フィルム部材が、前記半導体素子の正面から前記半導体素子の側面を経由して前記半導体素子の裏面に延在するように、前記フィルム部材の絶縁樹脂層の表面と、前記半導体素子の正面および裏面とが接しており、

前記フィルム部材の配線パターンの一部分は、前記絶縁樹脂層を貫通して前記半導体素子の正面および裏面の素子電極に接触している、半導体モジュール。

【請求項25】

前記絶縁樹脂層は、透明樹脂から成る、請求項24に記載の半導体モジュール。

10

20

30

40

50

**【請求項 2 6】**

前記絶縁樹脂層は、ポリイミドまたはアラミドから成る、請求項 2 4 または 2 5 に記載の半導体モジュール。

**【請求項 2 7】**

前記半導体素子は、複数の半導体素子から構成されている、請求項 2 4 ~ 2 6 のいずれかに記載の半導体モジュール。

**【請求項 2 8】**

表面および当該表面に対向する裏面を有する絶縁樹脂層、ならびに前記絶縁樹脂層の一方の面に配線パターンが形成されているフィルムインターポーラーであって、

前記配線パターンの一部分は、前記絶縁樹脂層を貫通して他方の面に露出している、フィルムインターポーラー。10

**【請求項 2 9】**

前記配線パターンが、前記絶縁樹脂層の前記一方の面に埋め込まれている、請求項 2 8 に記載のフィルムインターポーラー。

**【請求項 3 0】**

前記配線パターンの一部分の断面は、略 U 形状を有する、請求項 2 8 または 2 9 に記載のフィルムインターポーラー。20

**【請求項 3 1】**

( a ) 素子電極が形成された主面を有する半導体素子を用意する工程と、

( b ) 表面および当該表面に対向する裏面を有する絶縁樹脂層、ならびに前記絶縁樹脂層の裏面に形成された配線パターンを有するフィルム部材を用意する工程と、20

( c ) 前記半導体素子の主面と前記フィルム部材の絶縁樹脂層の表面とが接するよう、前記半導体素子と前記フィルム部材とを重ねる工程と、

( d ) 前記フィルム部材の配線パターンの一部分を前記絶縁樹脂層の内部に押し込んで前記半導体素子の素子電極に接触させる工程と

を含んで成る、半導体モジュールの製造方法。

**【請求項 3 2】**

前記フィルム部材は透明であり、

目視することによって前記工程 ( d ) を実施する、請求項 3 1 に記載の半導体モジュールの製造方法。30

**【請求項 3 3】**

前記接触により形成される接合部位に、超音波を印加する、請求項 3 1 または 3 2 に記載の半導体モジュールの製造方法。

**【請求項 3 4】**

前記超音波の印加に際して、前記配線パターンの一部分の物理的特性を測定する、請求項 3 3 に記載の半導体モジュールの製造方法。

**【請求項 3 5】**

前記物理的特性は、前記配線パターンの一部分の抵抗値である、請求項 3 4 に記載の半導体モジュールの製造方法。

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

本発明は、半導体モジュールおよびその製造方法に関する。特に、配線パターンが形成されたフィルム部材と半導体素子とを重ね合わせた半導体モジュールに関する。また、本発明は、透明なシート状フィルムから成るフィルムインターポーラーにも関する。

**【背景技術】****【0 0 0 2】**

近年の電子機器の小型化および高機能化に伴って、電子機器を構成する半導体素子の多ピン化および各種部品の小型化が進み、かかる半導体を搭載するプリント基板の配線数および密度が飛躍的に増加している。特に、半導体素子（例えば半導体チップ）から引き出

されるリード数または端子数が急速に増加したことによって、プリント基板（配線基板）の微細化が進んでいるため、微細ピッチ接続技術が重要となってきた。

#### 【0003】

微細ピッチ接続技術を大別すると、(i)ワイヤボンディング(WB)法、(ii)フリップチップボンディング(FC)法、(iii)TAB(Tape Automated Bonding)法がある。以下、それらの手法について簡単に説明する。

#### 【0004】

ワイヤボンディング法は、例えば特許文献1に開示されている。このワイヤボンディング法では、主として金ワイヤ（直径20～25μm）を用いて、半導体チップの電極とリードフレームの電極とを繋いでおり、双方の電極と金ワイヤとを、熱や超音波を与えて固相拡散させることによって接続している。

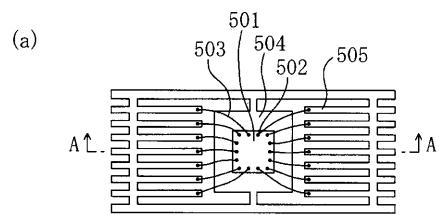

#### 【0005】

以下にて、特許文献1に開示されているワイヤボンディング法を、図19(a)および(b)を参照しながら説明する。なお、図19(a)は、上方からのワイヤボンディング状態を示しており、図19(b)は、図19(a)中の線A-Aに沿って切り取った断面を示している。

#### 【0006】

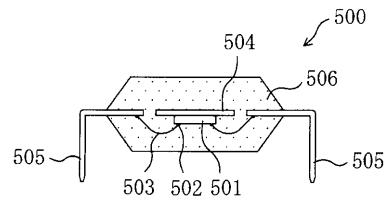

かかる手法では、まず、半導体チップ501をリードフレーム504の一部（ダイパッド）にダイボンディングした後、ボンディングワイヤ503を用いて半導体チップ501のワイヤボンディングパッド502と、リードフレーム504の外部端子505（インナーリード部）とをワイヤボンディングする。次いで、半導体チップ501および外部端子505のインナーリード部を含む領域を封止樹脂506によって封止する。これによって、例えば図20に示すような樹脂封止体（半導体モジュール）500が得られる。封止樹脂506から露出する外部端子505は、配線基板（図示せず）に接続され、その結果、半導体チップ501と配線基板とが電気的に接続されることになる。

#### 【0007】

このようなワイヤボンディング法では、以下のようないくつかの問題を有している。まず、半導体素子部品（図20において半導体チップ501を含むモジュール500）の実装面積が大きいことが挙げられる。つまり、かかる手法では、半導体チップ501を配線基板に直接的に実装するのではなく、ボンディングワイヤ503を介してリードフレーム504の外部端子505へと半導体チップ501を接続するので、必然的に半導体モジュール500のサイズ（素子サイズまたは部品サイズ）が半導体チップ501よりも大きくなり、従つて、半導体モジュール500の実装面積が大きくなってしまう。

#### 【0008】

また、ワイヤボンディング法では、半導体チップ501のワイヤボンディングパッド502と、リードフレーム504の外部端子505とを一つずつボンディングワイヤ503により接続するので、端子の数が多くなるほど、それだけ作業の手間が多くなってしまう。更に、かかる手法では、図19(b)に示すように、ボンディングワイヤ502が半導体チップ501の上面よりも上方に延在するように外部端子505に接続された後で、図20に示すように封止樹脂506によって樹脂封止が行われるので、半導体素子部品500の薄型化に限界がある。その上、リードフレーム504に配列された外部端子505のピッチによって、半導体素子500のピッチが規定されてしまうので、狭ピッチ化にも限界がある。

#### 【0009】

次にフリップチップボンディング法について説明する。フリップチップボンディング法は、例えば特許文献2に開示されている。この手法では、半導体チップにバンプ（即ち、突起電極）を形成した後、そのバンプを配線基板の電極に接続している。かかる手法の特徴は、半導体チップの電極形成面と配線基板の電極形成面とが対向した形態を有していることである。

#### 【0010】

10

20

30

40

50

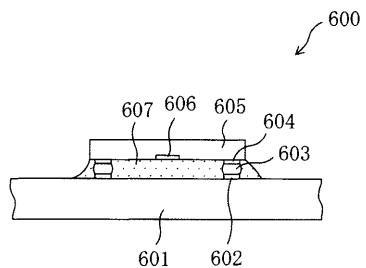

以下にて、特許文献 2 に開示されたフリップチップボンディング法を、図 2 1 を参照して説明する。なお、図 2 1 は、フリップチップボンディング法を用いて実装された半導体デバイス 600 の断面構成を示している。

#### 【0011】

このようなフリップチップボンディング法では、まず、トランジスタ等が形成されたセンシティブエリア 606 を有する半導体チップ 605 の電極 604 を、バンプ 603 を介在させて、基板 601 に設けられた所定の配線パターン 602 に接続する。このような接続によって、基板 601 と半導体チップ 605 との間に隙間が残されることになる。従って、配線パターン 602、バンプ 603、および電極 604 が埋設されるように、基板 601 と半導体チップ 605 との間の隙間に樹脂を流し込んで封止する（これにより封止樹脂 607 が得られる）。これによって、図 2 1 にて 600 で示されるような構成を有する半導体デバイス 600 が得られることになる。

#### 【0012】

このようなフリップチップボンディング法では、以下のような問題を有している。まず、基板 601 に対して半導体チップ 605 の位置合わせを行うことが困難となっていることが挙げられる。なぜなら、半導体チップ 605 を基板 601 に実装するに際しては、半導体チップ 605 の電極形成面が下向きになるような状態で半導体チップ 605 を基板 601 上に重ね合わせるため、半導体チップ 605 のバンプ 603 を外側から直接的に見ることができないからである。また、フリップチップボンディング法での半導体チップ 605 の電極 604 のピッチは、ワイヤボンディング法での外部端子ピッチよりも狭くなっている。20

#### 【0013】

また、フリップチップボンディング法では、基板 601 が高価になりやすいという問題も存在する。なぜならば、半導体チップ 605 の電極 604 のピッチに対応したファインパターンの配線パターン 602 が形成された基板 601 が必要となるからであり、その上、入出力端子の数が多い場合には基板 601 を多層化させる傾向があるからである。更に、フリップチップボンディング法では、半導体チップ 605 と基板 601 とがバンプ 603 を介して接続されるので、半導体チップ 605 と基板 601 との線膨張係数をできるだけ一致させないとバンプ 603 等に応力が加わってしまうことになる。従って、半導体チップ 605 と基板 601 との線膨張係数を合わせる必要があるが、線膨張係数のマッチングは難しく、基板 601 の製造コストが上がってしまう。

#### 【0014】

そして、フリップチップボンディング法では、バンプ 603 を介して半導体チップ 605 と基板 601 とを接続した後、半導体チップ 605 と基板 601 との隙間に樹脂（アンダーフィル剤）607 を入れる必要があるので、その分だけコストがかかってしまうと共に、工程数が増えてしまう。更に、半導体チップ 605 はバンプ 603 を介して基板 601 に接続されているので、放熱性が悪くなっている。即ち、半導体チップ 605 は、ワイヤボンディング法の場合のような面ではなく、点によって基板 601 上に配置されているので、放熱性が悪くなっている。また、フリップチップボンディング法では、バンプ 603 を形成しなければならないこと自体が手間となっている。

#### 【0015】

次に TAB 法について説明する。TAB 法は、例えば特許文献 3 に開示されている。この TAB 法では、半導体チップをリード配線付きの長尺テープに一旦接続した後、その半導体チップをリード付きチップ状態でテープから打ち抜くことによって、基板にリードを接続させる。TAB 法においては、かかるプロセスをリール・ツー・リール方式で自動的に行うことを基本としている。

#### 【0016】

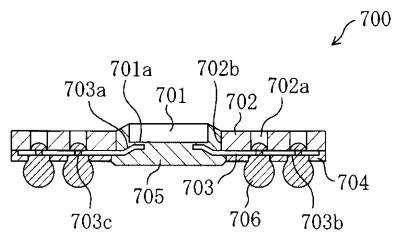

以下にて、図 2 2 および図 2 3 を参照しながら、特許文献 3 に開示された TAB 法を説明する。なお、図 2 2 は、TAB 法を用いて形成された半導体装置 700 の断面構成を示

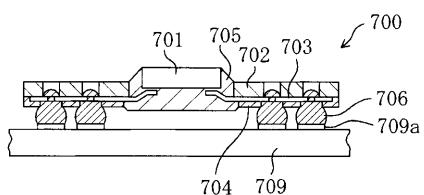

しており、図23は、かかる半導体装置700を実装基板709に実装させた構成を示している。

【0017】

図22に示す半導体装置700は、フィルムキャリアテープのベースフィルム702と、ベースフィルム702に開孔されたデバイスホール702bに配置された半導体ICチップ701とから構成されている。ベースフィルム702上には銅箔配線703が形成されており、半導体ICチップ701の電極701aが、銅箔配線703の内側先端部に設けられたインナーリード703aに接続されている。銅箔配線703のうちインナーリード703aの外側の部分には外部接続用のランド703bが設けられており、ランド703b上に半田バンプ706が形成されている。ベースフィルム702にはスルーホール702aが開孔されており、ランド703bの中央部には透孔703cが開設されている。ランド703bを除くフィルムキャリアテープ上にカバーレジスト704が形成されており、半導体ICチップ701を保護する封止樹脂705がデバイスホール702bに形成されている。

10

【0018】

このような半導体装置700では、半田バンプ706がアウターリードの役割を果たしている。従って、図23に示すように、半田バンプ706が実装基板709上のパッド709aに接続されており、一括リフロー方式によって、TAB法で得られた半導体装置700が実装基板709に実装されている。

20

【0019】

このようなTAB法では、以下のような問題を有している。まず、インナーリードボンディング(ILB)工程と、アウターリードボンディング(OLB)工程とが別工程であるので、TAB法の実施に手間がかかってしまう。つまり、図22に示す態様では、半導体ICチップ701の電極701aにインナーリード703aを接続する工程と、ランド703bに半田バンプ706を形成する工程との2工程が必要とされる。また、デバイスホール702bに配置された半導体ICチップ701を封止樹脂705で封止する必要もあり、これも手間となっている。更に、半導体ICチップ701の面積よりも大きいベースフィルム702が用いられるので、実装面積が大きくなってしまうという別の側面の問題も存在する。

30

【特許文献1】特開平4-286134号公報

【特許文献2】特開2000-36504号公報

【特許文献3】特開平8-88245号公報

【発明の開示】

【発明が解決しようとする課題】

【0020】

本発明の主な課題は、ワイヤボンディング法、フリップチップボンディング法およびTAB法とは異なる狭ピッチ接続技術が用いられた半導体モジュールおよびその製造方法を提供することにある。また、本発明の他の課題は、そのような新規な狭ピッチ接続技術に好適に適用可能なフィルムインターポーザを提供することにある。

40

【課題を解決するための手段】

【0021】

上記課題を解決するため、本発明は、

素子電極が形成された主面を有する半導体素子(または複数の半導体素子)と、表面および当該表面に対向する裏面を有する絶縁樹脂層から成り、絶縁樹脂層の裏面に配線パターンが形成されている(または埋め込まれている)フィルム部材とを備える半導体モジュールであって、

半導体素子の主面とフィルム部材の絶縁樹脂層の表面とが接するように、半導体素子とフィルム部材とが重ねられており、

フィルム部材の配線パターンの一部分は、絶縁樹脂層を貫通した状態で半導体素子の素子電極に接触している、半導体モジュールを提供する。かかる半導体モジュールでは、フ

50

イルム部材の配線パターンによってピッチを規定することができるので、微細ピッチに対応することが比較的容易となっている。なお、前記接触により形成される接合部位は、配線パターンと素子電極とを電気的に接続機能を有しており、従って、用いられるフィルム部材は、半導体素子にとって配線基板（例えばマザーボード）との中間基板の役割を果たすので、本明細書では、かかるフィルム部材をフィルムインターポーザとも呼ぶ。

#### 【0022】

このような半導体モジュールは、

(a) 素子電極が形成された主面を有する半導体素子（または複数の半導体素子）を用意する工程と、

(b) 表面および当該表面に対向する裏面を有する絶縁樹脂層から成り、絶縁樹脂層の裏面に配線パターンが形成されているフィルム部材を用意する工程と、

(c) 半導体素子の主面とフィルム部材の絶縁樹脂層の表面とが接するように、半導体素子とフィルム部材とを重ねる工程と、

(d) フィルム部材の配線パターンの一部分を絶縁樹脂層の内部に押し込んで半導体素子の素子電極に接触させる工程と

を含んで成る方法によって製造される。従って、従来技術のワイヤボンディング法、フリップチップボンディング法およびTAB法とは異なる半導体モジュールの製造方法、ならびに、それより得られる半導体モジュールおよびフィルムインターポーザが提供されることになる。

#### 【0023】

ある好適な実施形態では、フィルム部材は透明であることが好ましく、例えばポリイミドまたはアラミド等の透明樹脂から形成されている。従って、本発明では、目視することによって前記工程(d)を実施することができるようになっている。なお、フィルム部材の絶縁樹脂層は、半導体素子の主面に樹脂を塗布して形成された塗布膜であってもよい。

#### 【0024】

例えばニードル状部材等の圧接ツール（または押圧ツール）で配線パターンの一部分が絶縁樹脂の内部へと押し込まれることによって、配線パターンの一部分が絶縁樹脂層を貫通した状態で半導体素子の素子電極に接することになり、従って、配線パターンの一部分の断面は略U形状を有し得る。

#### 【0025】

かかる接合部位には超音波を印加することが好ましく、接合部位が超音波接合されることが好ましい、なお、接合部位の周囲に、アルミニウム、金、銀、プラチナおよびバナジウムから成る群から選択される複数種の金属を設けてよく、超音波接合された部位が、かかる複数種の金属が溶融して成る合金を含むものであってもよい。なお、超音波の印加に際しては、配線パターンの一部分の抵抗値等の物理的特性を測定することが好ましい。これにより、接合部位の強度を知ることができるので、所望の超音波を印加することができ、その結果、所望の強度を有する接合部位を形成することができる。

#### 【0026】

ある好適な実施形態では、フィルム部材の表面および裏面の寸法は、半導体素子の主面の寸法と略同じである、これにより、実装面積が比較的小さい半導体モジュールを実現することができる。

#### 【0027】

また、ある好適な実施形態では、フィルム部材の表面および裏面の寸法は、前記半導体素子の主面の寸法よりも大きくてよく、フィルム部材の裏面には半田ボールが形成されていることが好ましい。

#### 【0028】

更に、ある好適な実施形態では、本発明の半導体モジュールは、配線基板に電気的に接続されている常套のインターポーザを更に備えており、フィルム部材が当該インターポーザに電気的に接続されていることが好ましい。

#### 【0029】

10

20

30

40

50

また、ある好適な実施形態では、前記フィルム部材の裏面に接するように、更なるフィルム部材が積層していることが好ましく、かかるフィルム部材がフィルムインターポーザとして見なされることから、多層のフィルムインターポーザを有して成る半導体モジュールを実現することが可能となっている。なお、その際、半導体素子は、半導体ウェハであつてよい。

#### 【0030】

なお、上述した半導体モジュールおよびフィルムインターポーザの第1変更態様として、

素子電極が形成された主面および前記主面に対向する裏面を有する半導体素子と、

表面および当該表面に対向する裏面を有する絶縁樹脂層から成り、前記絶縁樹脂層の裏面に配線パターンが形成されているフィルム部材と、

配線基板と

を備える半導体モジュールであつて、

前記半導体素子の裏面が前記配線基板と接するように、前記半導体素子が前記配線基板に載置されており、

前記フィルム部材の表面および裏面の寸法は、前記半導体素子の主面の寸法よりも大きく、前記半導体素子の主面と前記フィルム部材の絶縁樹脂層の表面とが接するように、前記フィルム部材が前記半導体素子に載置されると共に、前記フィルム部材の少なくとも一部分が前記配線基板にまで延在し、

前記フィルム部材の配線パターンの一部分の少なくとも1つが、前記絶縁樹脂層を貫通した状態で前記半導体素子の素子電極に接触している一方、前記フィルム部材の配線パターンの一部分の残りの少なくとも1つが、前記絶縁樹脂層を貫通した状態で前記配線基板上に形成された電極に接触している、半導体モジュールが提供される。

#### 【0031】

また、上述した半導体モジュールの第2変更態様として、

主面および前記主面に対向する裏面を有し、前記主面および裏面に素子電極を有する半導体素子と、

表面および当該表面に対向する裏面を有する絶縁樹脂層から成り、前記裏面に配線パターンが形成されているフィルム部材と

を備える半導体モジュールであつて、

前記フィルム部材が、前記半導体素子の主面から前記半導体素子の側面を経由して前記半導体素子の裏面に延在するように、前記フィルム部材の絶縁樹脂層の表面と、前記半導体素子の主面および裏面とが接しており、

前記フィルム部材の配線パターンの一部分は、前記絶縁樹脂層を貫通した状態で前記半導体素子の主面および裏面の素子電極に接触している、半導体モジュールが提供される。

#### 【発明の効果】

#### 【0032】

本発明によれば、絶縁樹脂層の裏面に配線パターンが形成されて成るフィルム部材の表面に半導体素子の主面が載置され、フィルム部材の配線パターンの一部分が絶縁樹脂層を貫通した状態で半導体素子の素子電極に接合された半導体モジュールが提供されるので、ワイヤボンディング法、フリップチップボンディング法およびTAB法で製造される半導体モジュールとは異なる新規な半導体モジュールが提供されることになる。

#### 【発明を実施するための形態】

#### 【0033】

以下、図面を参照しながら、本発明の実施形態を説明する。以下の図面では、説明を簡素化するために、実質的に同一の機能を有する構成要素を同一の参照符号で示している。なお、本発明は以下の実施形態に限定されることはない。

#### 【0034】

#### (実施形態1)

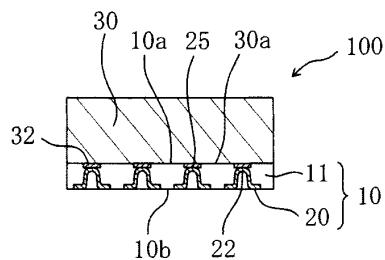

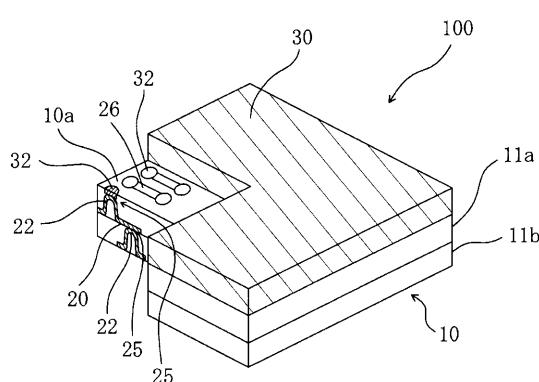

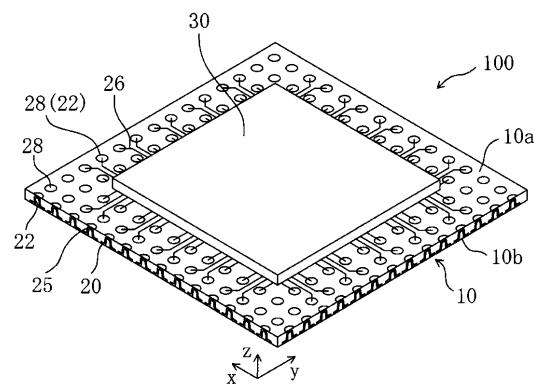

まず、図1を参照しながら、本発明の実施形態に係る半導体モジュール100について

10

20

30

40

50

説明する。図1は、本実施形態の半導体モジュール100の断面構成を模式的に示している。

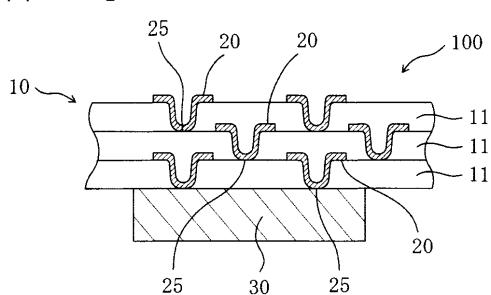

【0035】

図1に示す半導体モジュール100は、半導体素子30とフィルム部材10とから成っている。半導体素子30は、その表面30aに素子電極32を有している。なお、本明細書では、そのように半導体素子30の素子電極32が形成される表面30aを正面と呼ぶ。フィルム部材10は、絶縁樹脂層11と配線パターン20とから成っており、絶縁樹脂層11の裏面10b（即ち、フィルム部材の裏面）に配線パターン20が形成された様子を有している。なお、かかる配線パターン20は、裏面10bにおいて絶縁樹脂層11に埋め込まれてもよく、かかる場合、配線パターン20の表面が、好ましくは絶縁樹脂層11の裏面と面一（または略面一）となっていることが好ましい。

【0036】

半導体モジュール100は、図1に示すように、半導体素子30の正面30aとフィルム部材の表面（即ち、絶縁樹脂層の表面）10aとが接するように、半導体素子30とフィルム部材10とが重ねられて構成されており、フィルム部材10の配線パターン20の一部分22が、絶縁樹脂層11を貫通した状態で半導体素子30の素子電極32に接触している。

【0037】

本発明の半導体モジュール100に用いられる半導体素子30は、例えば半導体ベアチップまたはチップ・サイズ・パッケージ（CPS）であってよい。かかる半導体素子30の厚さは、例えば20～400μmであってよく、好ましくは50～400μmである。より具体的には、半導体素子30は、メモリICチップ、ロジックICチップまたはシステムLSIチップであってよく、更には発光ダイオード（LED）チップであってよい。

【0038】

本発明の半導体モジュール100の正面30aに形成される素子電極32は、A1またはA2から形成されることが好ましく、その厚さは例えば0.01～0.1μmであってよく、好ましくは0.05～0.1μmである。

【0039】

本発明の半導体モジュール100に用いられるフィルム部材10の絶縁樹脂層11は、一般的な半導体モジュールに用いられる絶縁樹脂から形成されるものであってよいが、好ましくは透明な絶縁樹脂から形成されている。従って、本実施形態では、絶縁樹脂層11はポリイミドまたはアラミドから成るフィルム（またはコアフィルム）であることが好ましい。なお、絶縁樹脂層11は、ポリフェニレンサルファイド（PPS）、ポリプロピレンまたはポリメタクリル酸メチルから形成してもよい。絶縁樹脂層11の厚さは、例えば1～30μmであり、好ましくは1～10μmである。

【0040】

本発明の半導体モジュール100に用いられるフィルム部材10の配線パターン20は、例えば銅から形成されることが好ましく、その厚さは、好ましくは1～35μmであり、より好ましくは1～12μmである。

【0041】

図1に示す態様の半導体モジュール100では、フィルム部材10の表面10aおよびそれに対向する裏面10bの寸法は、半導体素子32の正面30aの寸法と略同じとなつており、半導体素子30の正面30aとフィルム部材の表面10aとが接するように、半導体素子30とフィルム部材10とが重ねられている。かかるフィルム部材10の表面10aおよび裏面10bの寸法は、例えば1～10mm×1～10mmであり、好ましくは3～10mm×3～10mmである。従って、半導体素子30の正面30aの寸法も同様に、例えば1～10mm×1～10mmであり、好ましくは3～10mm×3～10mmである。

【0042】

10

20

30

40

50

図1に示す半導体モジュール100では、配線パターン20の一部分22が例えばニードル状部材で押圧されることによって、当該配線パターン20の一部分22が絶縁樹脂層11の内部に押し込まれ、その結果、当該配線パターン20の一部分22が絶縁樹脂層11を貫通した状態となっている。従って、かかる配線パターンの一部分の断面は、略U形状となり得るもの、配線パターン20の一部分22が絶縁樹脂層の内部へと押し込まれる様に応じて種々の形状となり得る。

#### 【0043】

なお、半導体モジュール100では、配線パターン20の一部分22と半導体素子30の素子電極32とが相互に接触しており、好ましくは接合または圧接されている。従って、かかる接触、接合または圧接により形成される接合部位25は、半導体素子20の素子電極32とフィルム部材10の配線パターン20とを電気的に接続する機能を有する。それゆえ、本明細書では、かかる接合部位25を「層間接続部位」ともいう。そして、上述したように、フィルム部材10は、半導体素子30を基準にすると配線基板（例えば、マザーボード）との中間基板の役割を有するので、フィルムインターポーザ（またはフィルム製インターポーザ）と称することができる。従って、本発明のフィルムインターポーザは、絶縁樹脂層から成るシート状のフィルム（例えば、透光性のフィルム）11と、フィルム11の一方の面に形成された配線パターン20とから構成されており、配線パターン20の一部分22が、フィルム11を貫通した状態でフィルム11の表面（10a）に露出した様子を有している。フィルム11を貫通した配線パターン20の一部分22の断面は略U形状を有しており、当該略U形状の底部が半導体素子30の素子電極32に接触または接続されることになる。

#### 【0044】

このように、本実施形態の半導体モジュール100は、フィルムインターポーザ10を用いた接続方法であり、上述した従来のワイヤボンディング法、フリップチップボンディング法およびTAB法とは異なる新たな接続方法となっている。

#### 【0045】

以下、上述の本発明の半導体モジュールの応用例または変更例等について説明する。

#### 【0046】

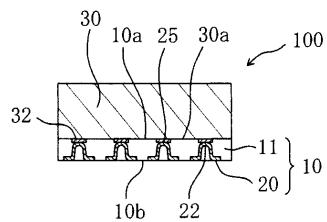

本実施形態の半導体モジュール100では、フィルム部材10の裏面に半田ボール40を形成することができる。なお、かかる半田ボール40は二次元的に配列されることが好ましい。半田ボール40は、図2に示すように、フィルムインターポーザ10の配線パターン20のランド24に載置してよい。半導体モジュール100は、かかる半田ボール40を介して、配線基板（図2では図示せず）に実装されることになる。なお、半田ボール40が載置されるランド24は、所定の配線（図2では図示せず）を介して、略U形状の層間接続部位25と電気的に接続されている。

#### 【0047】

かかる図2に示す様において、フィルムインターポーザ（即ち、フィルム部材）10の寸法は、半導体素子30の主面30aの寸法よりも大きくなるように設計されている。そのため、半導体素子30の素子電極32のピッチよりも広い間隔を、フィルムインターポーザ10のランド24で実現することができ、いわゆるファンアウトを容易に実行することができる。なお、かかる様のフィルム部材10の表面10aおよび裏面10bの寸法は、例えば3～15mm×3～15mmであり、好ましくは5～15mm×5～15mmである。その一方、半導体素子30の主面30aの寸法は、例えば3～15mm×3～15mmであり、好ましくは5～15mm×5～15mmの範囲で設定する。

#### 【0048】

なお、図1に示す様では半導体素子30の主面30aと略同じ寸法の表面10aおよび裏面10bを有するフィルムインターポーザ10が用いられているが、かかるフィルムインターポーザ10に対しても半田ボール40を載置することが可能である。その場合、ランド24は、フィルムインターポーザ10の裏面10bに位置する配線パターン20の所定箇所に形成すればよい。

10

20

30

40

50

## 【0049】

なお、半導体素子30の表面30aと略同じ寸法の表面10aを有するフィルムインターポーザ10であっても、半導体素子30において素子電極12がペリフェラル状に配列されている場合において、フィルムインターポーザ10にてランド24が行列状になるように配線パターン20を形成すれば、半導体素子30の素子電極32のピッチよりも広い間隔を実現することができる。

## 【0050】

更に、半導体素子30が半導体ベアチップの場合に、ランド24が二次元的（典型的には、行列状）に配列された配線パターン20を有するフィルムインターポーザ10を組み合わせれば、簡便に、PGA（ピン・グリッド・アレイ）パッケージ、または、BGA（ボール・グリッド・アレイ）パッケージを実現することができる。なお、図1に示す構成を有する半導体モジュール100の場合では、簡便にCSP（例えば、BGA型CSP）にすることも可能である。

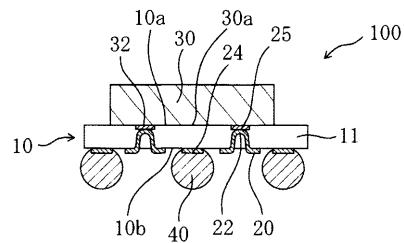

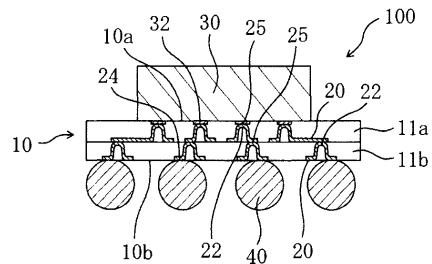

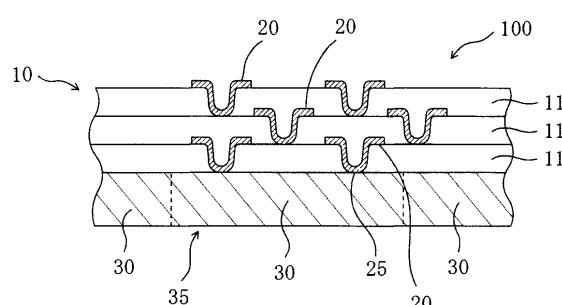

## 【0051】

図3に示す半導体モジュール100では、例えば図1に示すようなフィルム部材10の裏面に接するように、更なるフィルム部材が積層した態様が示されている。従って、かかる半導体モジュール100は、多層のフィルムインターポーザ10を有している。かかるフィルムインターポーザ10は、第1フィルム11aと第2フィルム11bとから構成されている。第1フィルム11aおよび第2フィルム11bとも、配線パターン20が形成されており、各配線パターン20には層間接続部位25が形成されている。フィルムインターポーザ10の裏面10bには、ランド24が形成されており、かかるランド24に半田ボール40が載置されている。なお、かかる態様を有する半導体モジュールでは、半導体素子が半導体ウェハであることが好ましい。

## 【0052】

図4は、本発明の半導体モジュール100の一例の構成を模式的に示した一部切り欠き斜視図である。かかる態様のフィルムインターポーザ10は、第1フィルム11aと第2フィルム11bとから成る多層構造を有している。なお、図示される半導体モジュール100では、フィルムインターポーザ10の表面10aの寸法と、半導体素子30の表面30aの寸法とは略同じになっている。

## 【0053】

図4に示す構成では、層間接続部位25の構造が示されている。なお、理解しやすいように半導体素子30の素子電極32をフィルムインターポーザ10側に明示している。図4に示すように、フィルムインターポーザ10の表面10aに配線（または配線パターン）26を形成して、かかる面10aで電気的な線路を形成することが可能である。

## 【0054】

図5も、図4と同様に、半導体モジュール100の一例の構成を模式的に示した一部切り欠き斜視図である。かかる図では、層間接続部位25の構造を見やすいように、フィルムインターポーザ10の外縁領域の一部を切り欠いて示している。図5に示す半導体モジュール100は、端子が100ピン以上のBGAモジュール（またはPGAモジュール）であり、半導体素子30の素子電極が、フィルムインターポーザ10によってファンアウトされている。

## 【0055】

なお、かかる図5に示す態様では、層間接続部位25の配線パターン20の一部分22を、フィルムインターポーザ10の表面10aに直接露出させてなく、フィルムインターポーザ10の表面10aに端子（例えば、ランド）28を形成し、かかる端子28を介して配線パターン20の一部分22を露出させている。かかる端子28は、フィルムインターポーザ10の表面10aに形成された配線26に接続されている。なお、半導体素子30の表面30aが位置する領域では、直接、配線パターン20の一部分22を露出させて半導体素子の素子電極に接合すればよい。

## 【0056】

10

20

30

40

50

図5に示す態様では、フィルムインターポーザ10の表面10aに配線26および端子28を形成してファンアウトを行っているが、フィルムインターポーザ10の表面10aに配線26および端子28を形成せずに、層間接続部位25を介して、フィルムインターポーザ10の裏面10bの配線パターン20によってファンアウトを行うことも可能である。

#### 【0057】

なお、層間接続部位に関して説明すると、層間接続部位25を構成する配線パターン20の一部分22は、配線パターン20と継ぎ目なく同一材料で連続して形成されているので、例えば層間接続部位25が導電性ペーストのようなビアから構成されている場合と比較すると、ビア（層間接続部位）と配線（配線パターン）との間のインピーダンスの不整合の問題を回避することができるようになっている。また、配線パターン20と層間接続部位25を構成する一部分22とは同じ材料から構成されているので、双方の熱膨張係数が等しく、接続信頼性に優れている。

#### 【0058】

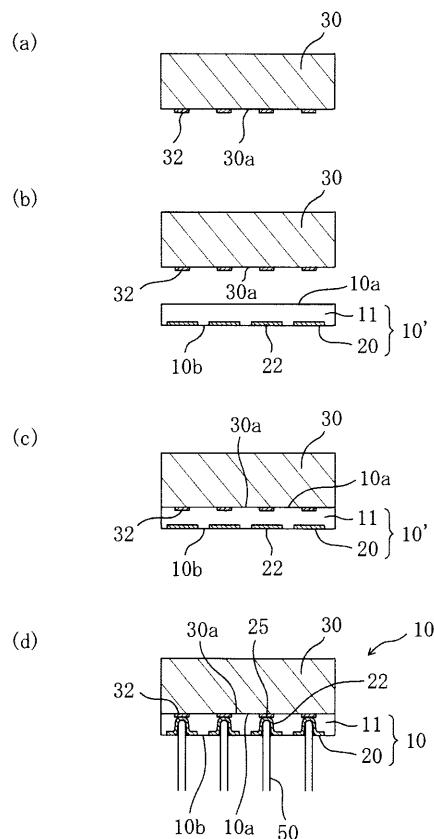

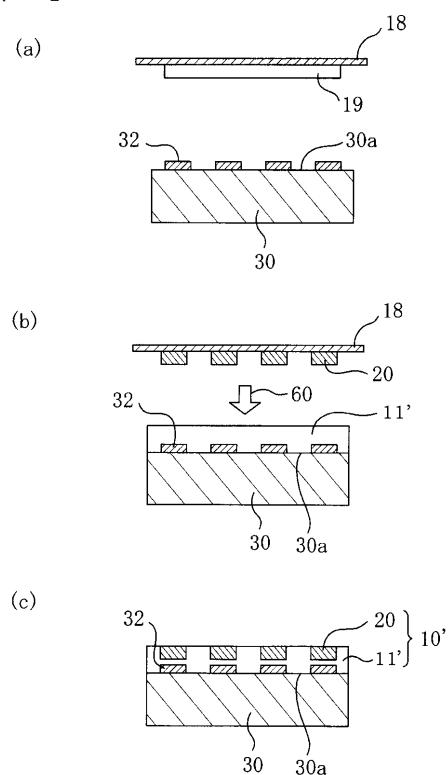

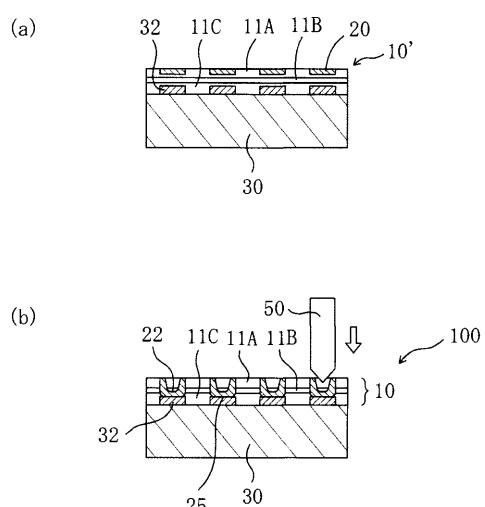

次に、図1に示す半導体モジュール100を製造するための工程断面図を示す図6(a)～(d)を参照しながら、本発明の半導体モジュール100の製造方法を説明する。

#### 【0059】

まず、図6(a)に示すように、主面30aに素子電極32が形成された半導体素子（例えばペアチップ）30を用意する。次いで、図6(b)に示すように、半導体素子30と組み合わせるフィルム部材10'を用意する。かかるフィルム部材10'の裏面10bには、配線パターン20が形成されており、配線パターン20の一部分22が、半導体素子30の素子電極32に対応して形成されている。

#### 【0060】

次に、図6(c)に示すように、半導体素子30の表面30aと、フィルム部材10'の表面10aとを接触させるように、半導体素子30とフィルム部材10'を重ね合わせる。その後、図6(d)に示すように、フィルム部材10'の配線パターン20の一部分22を、フィルム部材10'の絶縁樹脂層11の内部に押し込んで、かかる絶縁樹脂層11を貫通させることによって、配線パターン20の一部分を半導体素子30の素子電極32に接合させる。かかる態様では、例えばニードル状部材等の圧接ツール50を用いて、配線パターン20の一部分22をフィルム部材10'の絶縁樹脂層11の内部に押し込んでいる。従って、形成される層間接続部位25の断面は、略U形状を有している。なお、ニードル状部材の場合は、その押圧部（即ち先端部）が半球面を有していることが好ましく、その直径は例えば10～200μmであり、好ましくは10～50μmである。なお、かかるニードル状部材の押圧部が平面状であってもかまわない。

#### 【0061】

以上の工程により、本実施形態の半導体モジュール100を得ることができる。なお、図6(d)に示すように、かかる半導体モジュール100の製造方法では、フィルムインターポーザ10も得ることができることを理解されよう。

#### 【0062】

本実施形態において、フィルム部材10'のフィルム11は、例えばポリイミドまたはアラミドから成り、実質的に透明となっている。従って、半導体素子30とフィルム部材10'を重ね合わせる工程において素子電極32と配線パターン20の一部分22との位置合わせを実施するに際して、素子電極32をフィルム11越しに見ることが可能であり、かかる位置合わせが容易となっている。

#### 【0063】

また、圧接ツール50による接合の際に、超音波を印加することも可能である。かかる超音波の印加によって、層間接続部位25の接触箇所または接合箇所は、超音波接合され得、従って、接続信頼性がより良好な半導体モジュールを製造することができる。例えば圧接ツール50に超音波印加機能を設けた場合には、圧接ツール50によって押込みと超音波接合とを同時に実施することができる。なお、超音波の印加による接合をより強固な

ものにするために、例えば配線パターンを成す銅とは別の金属（例えば、アルミニウム、金、銀、プラチナまたはバナジウムなど）を配線パターン20の一部分22の周囲に設けてよく、その結果、超音波を用いた層間接続部位25の形成に際して、複数の種類の金属が溶融して成る合金を層間接続部位25に存在させることが可能となる。

#### 【0064】

なお、印加される超音波の周波数は、例えば40KHz～1MHzであり、好ましくは40～800kHzである。また、印加させる超音波の出力パワーは、例えば10～50Wであり、好ましくは、20～40Wである。更に、印加時間は、例えば0.1～1(s)であり、好ましくは0.1～0.5(s)である。

#### 【0065】

なお、超音波の印加は、配線パターン20の一部分の物理的特性を測定しながら実行することが好ましい。そのような物理的特性としては、配線パターン20の一部分の抵抗値または配線パターンの絶縁部材に対する押込み量等が挙げられる。例えば抵抗値等の物理的特性を測定しながら、超音波接合を行うと、層間接続部位25の強度をリアルタイムで知ることができ、当該強度が所望の値となるまで超音波を印加することが可能となる。また、物理的特性を測定しながらの超音波の印加は、最初の一回または数回のみの実施で足り得、以後は、それから得られる結果を用いることによって、例えば印加時間または超音波のエネルギー量等を調整することができる。

#### 【0066】

上述の本発明の半導体モジュールおよびその製造方法では、配線パターン20の一部分22の接合によって半導体素子30との電気的な接続を確保するので、ワイヤボンディング法のように一つずつ金属細線（金ワイヤ）を用いて結線しなくてもよい。従って、ワイヤボンディング法と比べて作業の手間を軽減させることができる。更に詳細に説明すると、半導体素子のピン数（入出力端子数）は近年大幅に増加する傾向を有しており、当該ピン数は2006年には1000ピン、2010年には2000ピンにまで達すると言われている。従って、そのような多ピン化する半導体素子に対して、ワイヤボンディング法を用いて一つずつ結線するのは非常に手間であるのに対し、本発明の半導体モジュールおよびその製造方法では、例えば複数のニードル状部材で一括して層間接続部位を形成することができるので、そのような問題に対処することができるようになっている。

#### 【0067】

また、本発明の半導体モジュールおよびその製造方法では、配線パターン20によってピッチを規定できるので、ワイヤボンディング法と比べて、より微細なピッチで接続を行うことができる。半導体素子30のピンのピッチは、2006年には40μm、2010μmには20μmにまで達すると言われており、金ワイヤの直径等を考慮すれば、ワイヤボンディング法を用いてそのような微細ピッチに対応するのは非常に困難となり得るか、または事実上不可能となり得る。一方、本発明の半導体モジュールおよびその製造方法では、配線パターンによってピッチを規定することができるので、そのような微細ピッチに対応することができるようになっている。

#### 【0068】

更に、本発明の半導体モジュールおよびその製造方法では、半導体素子（例えばベアチップ）の周囲の適切な範囲にフィルムインターポーザを配置すればよいので、ワイヤボンディング法で製造される半導体モジュールと比べて、実装面積も小さくすることができる。例えば、図1に示す半導体モジュール100では、半導体素子（ベアチップ）30の正面30aと同じ寸法のリアルサイズのCSPを実現することができる。また、フィルムインターポーザ10によって接続を行うので、ワイヤボンディング法と比べて、高さがより低い半導体モジュールを得ることができる。従って、半導体モジュールの薄型化に寄与し得ることになる。

#### 【0069】

また、本実施形態の構成の場合、半導体素子30とフィルム部材10'を重ね合わせる際に透明なフィルム11を通して半導体素子30の素子電極32の位置を確認すること

10

20

30

40

50

ができるので、フリップチップボンディング法と比較して、位置合わせを容易に行うことができる。従って、フリップチップボンディング法よりも、半導体素子との実装公差ズレを減少させることができることがより容易となっている。

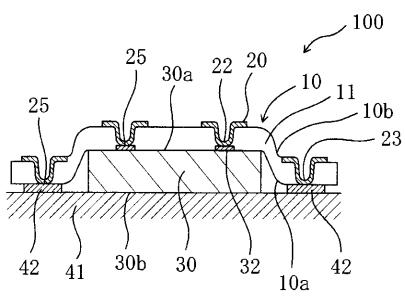

### 【0070】

特に、図7に示すように、半導体素子30の裏面30b（主面30aと対向する面）を配線基板41の上に載置すると共に、フィルムインターポーザ（即ちフィルム部材）10の配線パターン20の一部分23が絶縁樹脂層を貫通して配線基板41の電極42に電気的に接続する構成を有する半導体モジュールの場合、素子電極32との位置合わせも、配線基板41の電極42との位置合わせも、透明なフィルム11を通して目視確認により行うことができるので、技術的な価値が高い。ここで、目視による確認とは、作業者の目による確認だけでなく、画像認識装置（例えば、CCDやCMOSセンサーを含む装置）による確認も含んでいる。なお、かかる図7に示す態様では、半導体モジュール100は、素子電極32を有する主面30aおよび前記主面30aに対向する裏面30bを有する半導体素子30と、

表面10aおよび当該表面10aに対向する裏面10bを有する絶縁樹脂層11から成り、前記絶縁樹脂層の裏面10bに配線パターン20が形成されているフィルム部材10と、

配線基板41と

を備えており、

半導体素子30の裏面30bが配線基板41と接するように、半導体素子30が配線基板41に載置されており、

フィルム部材10の表面10aおよび裏面10bの寸法は、半導体素子30の主面30aの寸法よりも大きく、半導体素子30の主面30aとフィルム部材10の表面10aとが接するように、フィルム部材10が半導体素子30に載置されていると共に、フィルム部材10の少なくとも一部分が配線基板41上にまで延在しており、

フィルム部材10の配線パターン20の一部分22の少なくとも1つが、前記絶縁樹脂層11を貫通した状態で半導体素子30の素子電極32に接触している一方、フィルム部材10の配線パターン20の一部分の残り23の少なくとも1つが、絶縁樹脂層11を貫通した状態で配線基板41上に形成された電極42に接触している。

### 【0071】

更に、フリップチップボンディング法の場合、半導体素子の電極形成面が配線基板の方を向いてしまうので、半導体素子と配線基板との接続状況を目視により確認することが困難であるが、例えば図7に示す構成を有する半導体モジュールでは、半導体素子30と配線基板41との接続の確認が容易に行うことができるようになっている。

### 【0072】

更に、本発明の半導体モジュールおよびその製造方法では、フリップチップボンディング法で配線基板に形成されるファインパターンをフィルムインターポーザ（即ちフィルム部材）の配線パターンに形成すればよいので、フリップチップボンディング法と比べて、配線基板のコストアップを抑制することができる。また、フリップチップボンディング法の場合には特定の領域（即ち、半導体素子の主面と対向する配線基板の領域）に数多くの端子が集中することに伴って、配線基板の層数を多くしなければならない場合が多かったが、本発明の半導体モジュールおよびその製造方法では、フィルムインターポーザの配線パターンによって配線の引き回しを行うことができるので、フリップチップボンディング法の場合と比べて配線基板の層数を少なくすることができる。従って、かかる理由からも配線基板のコストアップを抑制することができる。なお、図3および図4に示すように、フィルムインターポーザ10自体の多層化も比較的容易に実現することが可能となっている。また、図2、図3および図5に示すように、フィルムインターポーザ10によるファンアウトによって、配線基板41のファインピッチ（または微細ピッチ）の度合いを下げてコストアップを抑えることも可能である。

### 【0073】

10

20

30

40

50

更に、本発明の半導体モジュールおよびその製造方法では、フリップチップボンディング法での半導体素子と配線基板との線熱膨張係数のマッチングと比べて、半導体素子30とフィルムインターポーザ10との線熱膨張係数のマッチングの必要性が比較的緩和されている利点を有する。即ち、本発明のフィルムインターポーザ（又はフィルム）は薄いので半導体素子に大きい影響をあまり与えない。また、フィルムの可撓性によって線熱膨張係数の差異に起因する応力を吸収することも可能となっている。

【0074】

そして、本発明の半導体モジュール（特に、図7に示す構成を有する半導体モジュール）およびその製造方法では、フリップチップボンディング法で使用されるアンダーフィル10剤（封止樹脂）を用いずに、半導体素子と配線基板との接続を行うことができるので、その点でも有利である。また、本発明の半導体モジュールでは、フィルムインターポーザによって、素子電極が形成された半導体素子の正面を保護することができる。

【0075】

なお、本発明の半導体モジュールおよびその製造方法において、半導体素子の素子電極は、バンプ（例えば、半田バンプまたは金バンプ）が形成されたものを使用してよいし、または、バンプが形成されていないものを使用してもよい。従って、フリップチップボンディング法の場合と異なって、素子電極にバンプを形成せずに、半導体素子と配線基板とを電気的に接続することができる。

【0076】

次にTAB法の場合との比較について検討する。かかるTAB法ではインナーリード工程とアウターリード工程とを別々に実施する必要があったが、本発明の半導体モジュールの製造方法では、そのような別々の工程を実施しなくてもよい。更に、本発明の半導体モジュールでは、TAB法のように封止樹脂を用いなくてもよく、加えて、実装面積も小さくすることができる。

【0077】

なお、図1等に示す例では、分かり易いように、素子電極12の数が少ないものを示したが、素子電極12の数は特に限定されていない。図6（d）に示すような圧接ツール50を用いれば、素子電極12が多い場合であっても、一括して接合工程を実施することができる。従って、半導体素子の素子電極が多ければ多いほど、本発明の半導体モジュールは、例えばワイヤボンディング法と比べて技術的価値が高くなる。また、本明細書では素子電極がペリフェラル状に配列した半導体素子の例を多く示したが、これに限定されず、アレイ状に配列した半導体素子を用いることも可能である。更に、図7に示す構成を有する半導体モジュールでは、素子電極32との接合にのみ略U形の層間接続部位25を用いる一方、配線基板41の電極42との接合には、他の公知の接合手法（例えば、はんだなどの低融点金属）を用いることも可能である。

【0078】

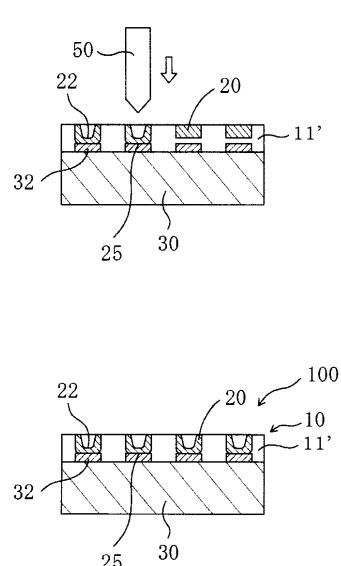

次に、図8～図12を参照しながら、本発明の半導体モジュールの別の製造方法およびそれにより得られる半導体モジュールについて説明する。

【0079】

図6（a）～（d）を参照して説明した製造方法では、絶縁樹脂層11に配線パターン20が形成されたフィルム部材10'を用いたが、そのような態様に限らず、半導体素子30の正面30aに絶縁樹脂を塗布して、その塗布膜を絶縁樹脂層11として使用することも可能である。以下、その手法について説明する。

【0080】

まず、図8（a）に示すように、正面30aに素子電極32を有する半導体素子30と、キャリアシート18上に形成された金属層（典型的には銅箔）19とを用意する。ここでキャリアシートは、例えばPET（ポリエチレンテレフタレート）、PEN（ポリエチレンナフタレート）から形成されることが好ましく、その厚さは、例えば5～15μmである。

【0081】

10

20

30

40

50

次に、図 8 ( b ) に示すように、キャリアシート 18 上の金属層 19 をパターニングして、配線パターン 20 を形成すると共に、半導体素子 30 の正面 30a には素子電極 32 が覆われるよう絶縁樹脂を塗布して塗布膜 11' を形成する。なお、絶縁樹脂は、粘着材または接着層が好ましい。次いで、矢印 60 に示すように、キャリアシート 18 上の配線パターン 20 を塗布膜 11' に転写すると、図 8 ( c ) に示すように、半導体素子 30 の正面 30a 上に、配線パターン 20 を有するフィルム部材 10' が形成されることになる。

#### 【 0 0 8 2 】

その後、図 9 ( a ) に示すように、配線パターン 20 の一部分 22 を圧接ツール 50 で塗布膜 11' 内部へと押し込み、層間接続部位 25 を形成すると、図 9 ( b ) に示すよう 10 な形態の半導体モジュール 100 が得られる。

#### 【 0 0 8 3 】

かかる製造方法は、塗布膜 11' によってフィルム 11 を形成するので、予め、配線パターン 20 付きのフィルム部材 10' を用意しておく必要がなく、従って、転写工程を行うことができる設備が完備されていれば、比較的便利な手法となり得る。

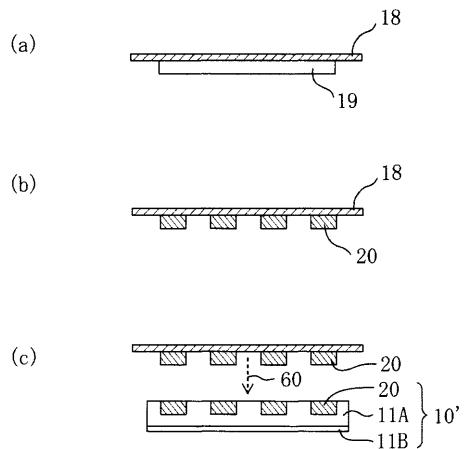

#### 【 0 0 8 4 】

また、転写工程を用いて本発明の半導体モジュールを製造する場合、図 10 ( a ) ~ 図 12 ( b ) に示すような方法で製造することも可能である。

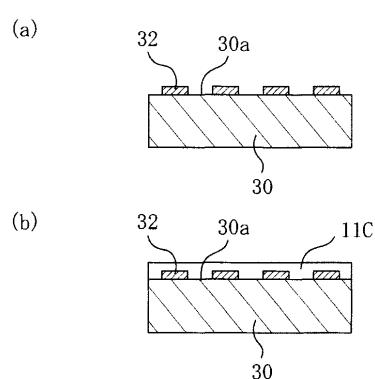

#### 【 0 0 8 5 】

まず、図 10 ( a ) に示すようなキャリアシート 18 上の金属層 19 をパターニングして、図 10 ( b ) に示すような配線パターン 20 を得る。次いで、その配線パターン 20 を矢印 60 に示すように、フィルム 11B 上に形成された絶縁樹脂層 11A へと転写して、配線パターン 20 が形成されたフィルム部材 10' を形成する。絶縁樹脂層 11A は、接着層または粘着層が好ましく、例えばエポキシから成るものであってよい。その一方、フィルム 11B は、例えば、ポリイミドまたはアラミドから成るものであってよい。

#### 【 0 0 8 6 】

それと並行して、図 11 ( a ) に示す半導体素子 30 を用意し、その正面 30a 上に絶縁樹脂層 11C を形成し、かかる樹脂層によって素子電極 32 を覆う ( 図 11 ( b ) 参照 )。絶縁樹脂層 11C は、接着層または粘着層が好ましく、例えばエポキシから成るものであってよい。

#### 【 0 0 8 7 】

次いで、図 12 ( a ) に示すように、フィルム部材 10' のフィルム 11B を、樹脂層 11C の上に載せた後、図 12 ( b ) に示すように、圧接ツール 50 によって層間接続部位 25 を形成すれば半導体モジュール 100 を作製することができる。

#### 【 0 0 8 8 】

なお、図 11 ( b ) に示した工程を経ずに、図 10 ( c ) に示したフィルム部材 10' のフィルム 11B の下面 ( 露出面 ) に絶縁樹脂層 11C を形成し、次いで、それを半導体素子 30 の正面 30a 上に載せて、図 12 ( a ) に示す構造を有する半導体モジュール 100 を形成してもよい。

#### 【 0 0 8 9 】

かかる態様では、上述したように、フィルム 11B としてアラミドフィルムを用いることが好ましい。これは、ポリイミドフィルムよりも、所定強度において薄いフィルムを実現し易いからであり、また、アラミドフィルムは、ポリイミドフィルムよりも安価であるからである。更に詳細に説明すると、アラミドフィルムは、ポリイミドよりも高弾性強度を有しており、薄層化に適している。例えば、厚さが約 1.2 . 5  $\mu\text{m}$  のポリイミドフィルムの強度に相当するアラミドフィルムの厚さは約 4  $\mu\text{m}$  である。また、アラミドは低コストであることに加えて、低吸湿を有しており、寸法変化が少ないという利点も兼ね備えている。

#### 【 0 0 9 0 】

なお、ポリイミドフィルムは耐熱性に優れているので、耐熱性が要求される場合には、

10

20

30

40

50

アラミドフィルムよりもポリイミドフィルムを用いた方が好ましい。

【0091】

上記転写工程を用いた製造方法によると、配線パターン20は、転写により樹脂層11(または11A)に埋設されて形成されるので、平坦性に優れているという利点を有している。なお、上記例では、転写法を用いた銅箔から成る配線パターン20を形成するので、ウェットエッティングを用いて形成した配線パターンよりもファインピッチなものにすることができるという別の利点も有している。例えば、ウェットエッティングを用いて形成した配線パターンのライン/スペース(L/S)が40μm/40μm程度である場合に、転写法を用いた配線パターンのL/Sは15μm/15μm(30μmピッチ)にまで微細化することが可能である。

10

【0092】

ただし、このことは、ウェットエッティングを用いてパターニングされた配線パターン20を用いることができないことを意味していない。例えば、図6(b)に示すフィルム部材10'を、フィルム11上に銅層(金属層)が積層された銅張積層板(CCL)に対してエッティングを施して作製することも可能である。銅張積層板(CCL)には、フィルム11の上に直接、銅層が形成されたもの(二層CCL)、または、接着層を介して銅層が形成されたもの(三層CCL)があるが、双方とも利用することができる。なお、銅張積層板(CCL)を用いた場合には、銅張積層板自体が典型的なフレキシブル基板の製造に多く使用されており、一般に流通しているので、材料のコストダウンが達成され得るという利点がある。

20

【0093】

(実施形態2)

次に、図13～図17を参照しながら、本発明の実施形態に係る更なる改変例について説明する。なお、説明を簡素化するために、上記実施形態1と同様の点については省略または簡略する。

【0094】

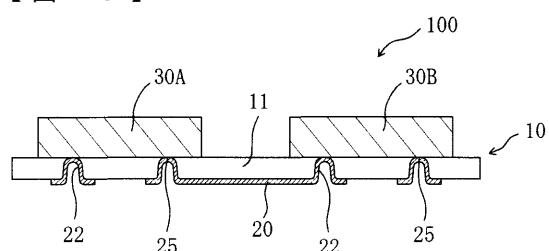

上記実施形態1では、1つのフィルムインターポーザ10の上に1つの半導体素子30を搭載したが、図13に示すように、1つのフィルムインターポーザ10に複数の半導体素子30Aおよび30Bを搭載して、本発明の実施形態に係る半導体モジュール100をマルチチップモジュールにすることも可能である。

30

【0095】

図13に示す構成では、フィルムインターポーザ10に形成された連続した配線パターン20によって、半導体素子30Aと半導体素子30Bとを接続することができる。従って、フィルムインターポーザ10によるLSIチップ間の高速配線接続を実現することができる。なお、図13では素子電極32が省略して描かれている。

【0096】

図13に示した例では、半導体素子30Aと30Bとの組み合わせを示したが、半導体素子30Aと受動部品とを組み合わせた半導体モジュール100を実現することも可能である。また、図13に示す例に受動部品を組み合わせることも可能である。

40

【0097】

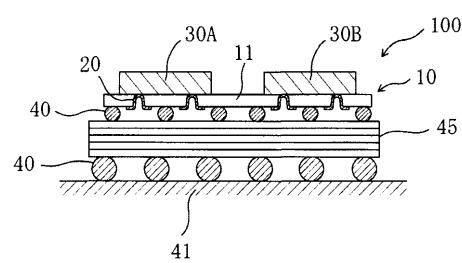

また、図14に示すように、図13に示す半導体モジュール100を通常のインターポーザ45を介して配線基板41に実装することも可能である。ここでは、半導体素子30Aと30Bとの相互の信号のやり取りは、フィルムインターポーザ10の配線パターン20を介して行っており、高速処理が実現されている。かかる箇所以外の少なくとも一部の電気的なやり取りは、インターポーザ45及び配線基板41を介して実行することが可能となる。なお、フィルムインターポーザ10によって既に一度ファンアウトがなされているので、通常のインターポーザ45のファインピッチの度合いを下げて、コストを下げることが可能となる。

【0098】

50

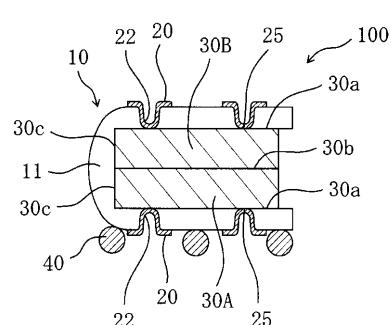

また、フィルムインターポーザ 10 は、図 15 に示すように用いることもできる。即ち、図 15 に示す例では、半導体素子 30A および 30B の裏面 30b 同士を合わせた様となつてあり、半導体素子 30A と 30B との電気的接続がフィルムインターポーザ 10 によって行われている。フィルムインターポーザ 10 は、半導体素子 30A および 30B の側面 30c の周囲を経由して半導体素子 30A の表面から半導体素子 30B の表面まで延在しており、フィルムインターポーザ 10 の配線パターン 20 の一部分 22 が、絶縁樹脂層 11 の内部に押し込まれることによって半導体素子 30A および 30B の素子電極（図示せず）に接続されている。

#### 【0099】

従つて、別の見方をすれば、図 15 に示す半導体モジュール 100 は、10

主面および裏面に素子電極を有する半導体素子（即ち、両面に素子電極を有する半導体素子）と、

表面および裏面を有する絶縁樹脂層から成り、その裏面に配線パターンが形成されているフィルム部材と

を備えており、

フィルム部材が、半導体素子の主面から半導体素子の側面を経由して半導体素子の裏面に延在するように、フィルム部材の表面と、半導体素子の主面および裏面とが接しており、

フィルム部材の配線パターンの一部分は、絶縁樹脂層を貫通した状態で半導体素子の主面および裏面の素子電極に接している。20

#### 【0100】

なお、かかる図 15 に示すような半導体モジュールおよびフィルムインターポーザは、

図 6 (a) ~ (d) の製造方法で得られる半導体モジュールおよびフィルムインターポーザと同様の特徴を有し、それらの応用例または変更例等についても同様であることを理解されよう。従つて、かかる同様の点については省略または簡略する。

#### 【0101】

図 3 を参照して説明したように、本実施形態のフィルムインターポーザ 10 は、多層化することが比較的容易であり、図 16 に示すように、各層のフィルム 11 に形成された配線パターン 20 を層間接続部位 25 で接続することによって、多層のフィルムインターポーザ 10 を形成することができる。30

#### 【0102】

更に、図 16 に示す構成を有するフィルムインターポーザ 10 は、個片の半導体素子 30 にだけ搭載されるのではなく、複数の半導体素子（ペアチップ）が配列された半導体ウェハ上にも搭載することができる。ペアチップ 30 が個片に切断される前の半導体ウェハ 35 にフィルムインターポーザ 10 を搭載すれば、ウェハレベル CSP (WL - CSP) を簡便に製造することができ、利便性が非常に高くなる。

#### 【0103】

以上、本発明を好適な実施形態により説明してきたが、こうした記述は限定事項ではなく、勿論、種々の改変が可能である。

#### 【0104】

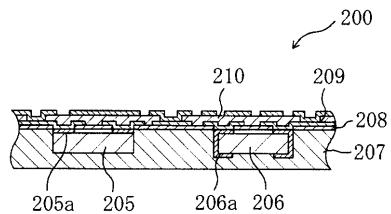

なお、本発明の実施形態の半導体モジュールと本質的に構成を異にするものであるが、

関連する構造を有するものとして、特開平 4-283987 号公報に開示された電子回路装置がある。その電子回路装置の構造を図 18 に示す。

#### 【0105】

図 18 に示す電子回路装置 200 は、絶縁樹脂層 207 に埋設された回路素子（例えば、半導体 IC）205、206 の外部電極端子層 205a、206a が配線回路導体層 209 によって電気的に接続された構造を有している。配線回路導体層 209 は、無電解めつき法によって形成された金属銅配線であり、直接、外部電極端子層 205a、206a に接続されている。なお、符合「208」は接着剤層で、符合「210」は層間絶縁樹脂層である。この電子回路装置 200 は、いわゆるビルドアップ層の技術が適用されたもの

40

50

であり、同公報には、本発明の実施形態に係る半導体モジュールの層間接続部位に関する技術およびフィルムインターポーザに関する技術は開示されていない。

#### 【0106】

また同様に、本発明の技術的思想と本質的に異なるものであるが、金属基板（例えば、アルミニウム基板）との電気的な接続を確保するために、ネジを用いずに、配線パターンの一部が絶縁層を突き破って金属基板と接続させるものが、特開平4-283987号公報および特開昭49-27866号公報に開示されている。双方とも、金属基板と接続させるために、接続用工具を用いて、比較的軟らかいアルミニウム基板の表面が完全に変形するまで深く陥没させている。従って、かかる手法を半導体素子の素子電極に対して行うと半導体素子が破壊されてしまうことになる。もちろん、同公報に開示されているものは、ワイヤボンディング法、フリップチップボンディング法およびTAB法のような微細ピッチ接続技術ではなく、ネジによる接続の代替技術であり、本発明の実施形態のものと本質的に異なる技術である。

#### 【産業上の利用可能性】

#### 【0107】

本発明によれば、ワイヤボンディング法、フリップチップボンディング法およびTAB法とは異なる新規な微細ピッチ接続技術を用いた半導体モジュールおよびその製造方法が提供される。

#### 【0108】

本発明の半導体モジュールは、その特徴を利用して、極めて実装面積が制限されるような薄型および小型の電子機器に搭載することができる。例えば、携帯電話に搭載することができる。また、携帯電話に限らず、PDAまたはノートパソコンに用いることが可能である。更に、例えば、デジタルスチルカメラまたは薄型テレビ（FPD；フラットパネルディスプレイ）等の他の用途にも適用することが可能である。

#### 【0109】

また、半導体素子としてLEDチップを用いると、フィルムインターポーザの配線パターンによって導通が確保され、フィルムを通過して光が出射する半導体モジュールまたは半導体装置（発光デバイス）を構築することができる。

#### 【0110】

更に、半導体素子をLEDチップとした場合に、フィルム内に蛍光体を分散させると、LEDチップからの出射光と蛍光体から発せられる光との双方の光を利用した発光デバイスを構築することができる。なお、本発明の実施形態の半導体モジュールを白色発光デバイスとして利用したい場合、半導体素子として、青色の光を出射する青色LEDチップを用い、そして、フィルムに分散させる蛍光体として、黄色の光に変換する黄色蛍光体を用いればよい。かかる場合、LEDチップとして、窒化ガリウム（GaN）系材料から成るLEDチップ、そして、蛍光体として、YAG系の蛍光体等を好適に用いることができる。

#### 【0111】

また、青色LEDチップを用いるだけでなく、紫外光を発する紫外LEDチップを用いることも可能であり、この場合、紫外LEDチップからの光で励起して、赤（R）、緑（G）および青（B）の光を発する蛍光体をフィルムに分散させるようすれば、白色発光デバイスを構築することができる。もちろん、白色以外にもLEDチップの種類と蛍光体の種類とを適宜選択することによって所望の色を発する発光デバイスを構築することができる。

#### 【図面の簡単な説明】

#### 【0112】

【図1】図1は、本発明の実施形態に係る半導体モジュール100の構成を模式的に示す断面図である。

【図2】図2は、本発明の実施形態に係る半導体モジュール100の構成を模式的に示す断面図である。

10

20

30

40

50

【図3】図3は、本発明の実施形態に係る半導体モジュール100の構成を模式的に示す断面図である。

【図4】図4は、本発明の実施形態に係る半導体モジュール100の構成を模式的に示す斜視図である。

【図5】図5は、本発明の実施形態に係る半導体モジュール100の構成を模式的に示す斜視図である。

【図6】図6(a)～(d)は、半導体モジュール100の製造方法を説明するための工程断面図である。

【図7】図7は、本発明の実施形態に係る半導体モジュール100の構成を模式的に示す断面図である。

【図8】図8(a)～(c)は、半導体モジュール100の製造方法を説明するための工程断面図である。

【図9】図9(a)および(b)は、半導体モジュール100の製造方法を説明するための工程断面図である。

【図10】図10(a)～(c)は、半導体モジュール100の製造方法を説明するための工程断面図である。

【図11】図11(a)および(b)は、半導体モジュール100の製造方法を説明するための工程断面図である。

【図12】図12は(a)および(b)は、半導体モジュール100の製造方法を説明するための工程断面図である。

【図13】図13は、本発明の実施形態に係る半導体モジュール100の改変例を模式的に示す断面図である。

【図14】図14は、本発明の実施形態に係る半導体モジュール100の改変例を模式的に示す断面図である。

【図15】図15は、本発明の実施形態に係る半導体モジュール100の改変例を模式的に示す断面図である。

【図16】図16は、本発明の実施形態に係る半導体モジュール100の改変例を模式的に示す断面図である。

【図17】図17は、本発明の実施形態に係る半導体モジュール100の改変例を模式的に示す断面図である。

【図18】図18は、公報に開示された電子回路装置200の断面図である。

【図19】図19(a)は、従来技術を用いて形成されたワイヤボンディング状態を示す上面図であり、図19(b)は、図19(a)の線A-Aに沿って切り取った断面図である。

【図20】図20は、従来技術における樹脂封止体(半導体モジュール)500の断面図である。

【図21】図21は、従来技術のフリップチップボンディング法を用いて実装された半導体デバイス600の断面図である。

【図22】図22は、従来技術のTAB法を用いて製造された半導体装置700の断面図である。

【図23】図23は、図22に示す従来の半導体装置700を実装基板709に実装した構成を示す断面図である。

#### 【符号の説明】

##### 【0113】

10 フィルムインター ポーラ (フィルム部材)

11 絶縁樹脂層

11' 塗布膜

12 素子電極

18 キャリアシート

19 金属層

10

20

30

40

50

- 2 0 配線パターン

2 2 配線パターンの一部

2 4 ランド

2 5 層間接続部位

2 6 配線

2 8 端子

3 0 半導体素子

3 0 a 半導体素子の正面(電極形成面)

3 2 素子電極

3 5 半導体ウェハ

4 0 半田ボール

4 1 配線基板

4 2 配線基板の電極

4 5 インターポーヴ

5 0 圧接ツール

1 0 0 半導体モジュール

2 0 0 電子回路装置

2 0 5 a 外部電極端子層

2 0 7 絶縁樹脂層

2 0 9 配線回路導体層

5 0 0 半導体モジュール(半導体素子部品)

6 0 0 半導体デバイス

7 0 0 半導体装置。

10

20

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図14】

【図15】

【図12】

【図13】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

## フロントページの続き

- (72)発明者 中谷 誠一

大阪府門真市大字門真1006番地 松下電器産業株式会社内

- (72)発明者 小島 俊之

大阪府門真市大字門真1006番地 松下電器産業株式会社内

- (72)発明者 小松 慎五

大阪府門真市大字門真1006番地 松下電器産業株式会社内

- (72)発明者 留河 悟

大阪府門真市大字門真1006番地 松下電器産業株式会社内