(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5799380号

(P5799380)

(45) 発行日 平成27年10月21日(2015.10.21)

(24) 登録日 平成27年9月4日(2015.9.4)

(51) Int.Cl.

A63F 7/02 (2006.01)

F 1

A 6 3 F 7/02 3 2 6 Z

A 6 3 F 7/02 3 0 4 D

請求項の数 1 (全 75 頁)

(21) 出願番号 特願2013-57721 (P2013-57721)

(22) 出願日 平成25年3月21日 (2013.3.21)

(62) 分割の表示 特願2009-221418 (P2009-221418)

原出願日 平成21年9月25日 (2009.9.25)

(65) 公開番号 特開2013-116405 (P2013-116405A)

(43) 公開日 平成25年6月13日 (2013.6.13)

審査請求日 平成25年4月19日 (2013.4.19)

(73) 特許権者 000132747

株式会社ソフィア

群馬県桐生市境野町7丁目201番地

(74) 代理人 100075513

弁理士 後藤 政喜

(74) 代理人 100120260

弁理士 飯田 雅昭

(74) 代理人 100142468

弁理士 高山 裕志

(72) 発明者 田中 雅也

群馬県太田市吉沢町990番地 株式会社

ソフィア内

(72) 発明者 松橋 光一

群馬県太田市吉沢町990番地 株式会社

ソフィア内

最終頁に続く

(54) 【発明の名称】遊技機

## (57) 【特許請求の範囲】

## 【請求項 1】

演算処理手段を有し、遊技の演出を行う複数の演出装置を制御する演出制御手段を備え、

前記演出装置の系統の各々を複数グループに分割し、該分割されたグループに属する演出装置を制御するためのグループ単位制御手段をグループ毎に設け、

前記演出制御手段を、グループ単位制御手段を統括的に制御するグループ統括制御手段として構成し、

前記グループ統括制御手段は、

前記演算処理手段からの指令に基づいて、前記グループ単位制御手段との間でデータを伝達するためのデータ線の信号レベルを制御する複数の信号レベル制御手段を備え、

前記グループ単位制御手段には、各グループ単位制御手段の間で共通となる共通アドレスと、各グループ単位制御手段同士で相違する個別アドレスと、が予め割り当てられ、

前記グループ統括制御手段が伝達するデータには、前記共通アドレス又は前記個別アドレスを示す第1アドレス情報と、前記グループ単位制御手段に設けられた記憶領域のうちの所定のアドレスを示す第2アドレス情報と、複数の制御データと、前記記憶領域の範囲内においてアドレスを更新する際の上限アドレスと戻りアドレスを特定可能なアドレス更新情報と、が含まれ、

前記グループ単位制御手段は、

遊技機に備わる可動部材を動作させることにより遊技機の装飾を行う可動装置のグル

10

20

プを制御する可動グループ単位制御手段と、

発光することにより遊技機の装飾を行う発光装置のグループを制御する発光グループ単位制御手段と、を含み、

前記第1アドレス情報が共通アドレスを示す場合に、初期化指示データに基づいて自身を初期化し、

前記第1アドレス情報が個別アドレスを示す場合に、前記第2アドレス情報が示すアドレスを記憶先の開始アドレスとして、受信した制御データを記憶し、制御データを記憶する毎に記憶先のアドレスを順次更新するとともに、

前記上限アドレスが示す記憶領域に制御データを記憶した場合は、記憶先のアドレスを前記戻りアドレスとなるように更新し、

前記可動グループ単位制御手段は、前記グループ統括制御手段から初期化を指示された場合、当該可動グループ単位制御手段が制御する前記可動部材を初期位置に戻すために前記可動装置に初期位置動作を実行させ、

該可動部材が初期位置に戻される間であっても、当該可動グループ単位制御手段に接続される信号レベル制御手段と異なる信号レベル制御手段は、前記発光グループ単位制御手段に対して発光制御データの伝達を行い、

前記可動グループ単位制御手段に接続される信号レベル制御手段と前記発光グループ単位制御手段に接続される信号レベル制御手段は、互いに異なる周期で接続されているグループ単位制御手段にデータの伝達を行うことを特徴とする遊技機。

【発明の詳細な説明】

10

【技術分野】

【0001】

グループに分割された演出装置を制御する複数のグループ単位制御手段と、複数のグループ単位制御手段を制御するグループ統括制御手段とを備える遊技機に関する。

【背景技術】

【0002】

サブ中継基板と電飾基板との間の配線を簡素化することができる遊技機として、トップ電飾領域の中央部に配置されたトップLED中央基板をサブ中継基板とシリアル接続し、トップ電飾領域の右側部に配置されたトップLED右基板及びトップ電飾領域の左側部に配置されたトップLED左基板をトップLED中央基板から分離して配線により接続した構成の遊技機が知られている。これにより、サブ中継基板からトップ電飾領域への配線数を減らして配線を簡素化することができる（例えば、特許文献1参照）。

20

【0003】

また、信号線の数を削減することができると共に不正行為の発見を容易に行うことができる遊技機として、主基板と副基板との間での信号送信をI<sup>2</sup>Cバス方式により行い、主基板及び副基板にそれぞれ双方向バスバッファを設けたものがある。この双方向バスバッファは、I<sup>2</sup>Cバスを構成する二つの双方向シリアルライン（SDA、SCL）をそれぞれ二つの片方向シリアルラインに分岐させるためのものであり、主基板に設けられた双方向バスバッファと副基板に設けられた双方向バスバッファとの間を、それらによって分岐された片方向シリアルラインの信号伝送方向が互いに一致するようにして、四つのシリアル線で接続した構成としている（例えば、特許文献2参照）。

30

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2008-212271号公報

【特許文献2】特開2006-15036号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

特許文献1に記載された遊技機では、配線を十分に削減することができなかった。

40

50

## 【0009】

本発明は、グループ統括制御手段とグループ単位制御手段とを接続する接続線の数を削減することのできる遊技機を提供することを目的とする。

## 【課題を解決するための手段】

## 【0010】

本発明は、演算処理手段を有し、遊技の演出を行う複数の演出装置を制御する演出制御手段を備え、前記演出装置の系統の各々を複数グループに分割し、該分割されたグループに属する演出装置を制御するためのグループ単位制御手段をグループ毎に設け、前記演出制御手段を、グループ単位制御手段を統括的に制御するグループ統括制御手段として構成し、前記グループ統括制御手段は、前記演算処理手段からの指令に基づいて、前記グループ単位制御手段との間でデータを伝達するためのデータ線の信号レベルを制御する複数の信号レベル制御手段を備え、前記グループ単位制御手段には、各グループ単位制御手段の間で共通となる共通アドレスと、各グループ単位制御手段同士で相違する個別アドレスと、が予め割り当てられ、前記グループ統括制御手段が伝達するデータには、前記共通アドレス又は前記個別アドレスを示す第1アドレス情報と、前記グループ単位制御手段に設けられた記憶領域のうちの所定のアドレスを示す第2アドレス情報と、複数の制御データと、前記記憶領域の範囲内においてアドレスを更新する際の上限アドレスと戻りアドレスを特定可能なアドレス更新情報と、が含まれ、前記グループ単位制御手段は、遊技機に備わる可動部材を動作させることにより遊技機の装飾を行う可動装置のグループを制御する可動グループ単位制御手段と、発光することにより遊技機の装飾を行う発光装置のグループを制御する発光グループ単位制御手段と、を含み、前記第1アドレス情報が共通アドレスを示す場合に、初期化指示データに基づいて自身を初期化し、前記第1アドレス情報が個別アドレスを示す場合に、前記第2アドレス情報が示すアドレスを記憶先の開始アドレスとして、受信した制御データを記憶し、制御データを記憶する毎に記憶先のアドレスを順次更新するとともに、前記上限アドレスが示す記憶領域に制御データを記憶した場合は、記憶先のアドレスを前記戻りアドレスとなるように更新し、前記可動グループ単位制御手段は、前記グループ統括制御手段から初期化を指示された場合、当該可動グループ単位制御手段が制御する前記可動部材を初期位置に戻すために前記可動装置に初期位置動作を実行させ、該可動部材が初期位置に戻される間であっても、当該可動グループ単位制御手段に接続される信号レベル制御手段と異なる信号レベル制御手段は、前記発光グループ単位制御手段に対して発光制御データの伝達を行い、前記可動グループ単位制御手段に接続される信号レベル制御手段と前記発光グループ単位制御手段に接続される信号レベル制御手段は、互いに異なる周期で接続されているグループ単位制御手段にデータの伝達を行う。

## 【発明の効果】

## 【0016】

本発明によると、グループ統括制御手段とグループ単位制御手段とを接続する接続線の数を削減することができる。

## 【図面の簡単な説明】

## 【0022】

【図1】本発明の第1実施形態の遊技機の説明図である。

【図2】本発明の第1実施形態の遊技盤の正面図である。

【図3】本発明の第1実施形態の遊技機の構成を示すブロック図である。

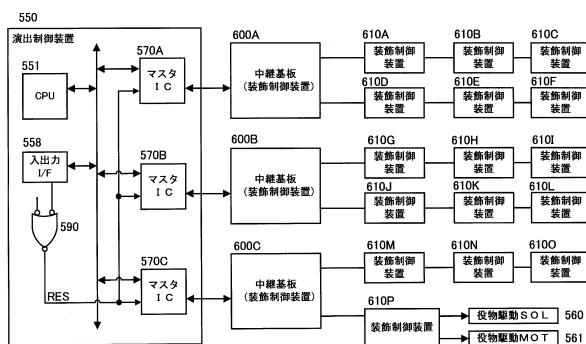

【図4】本発明の第1実施形態の演出制御装置の構成を示すブロック図である。

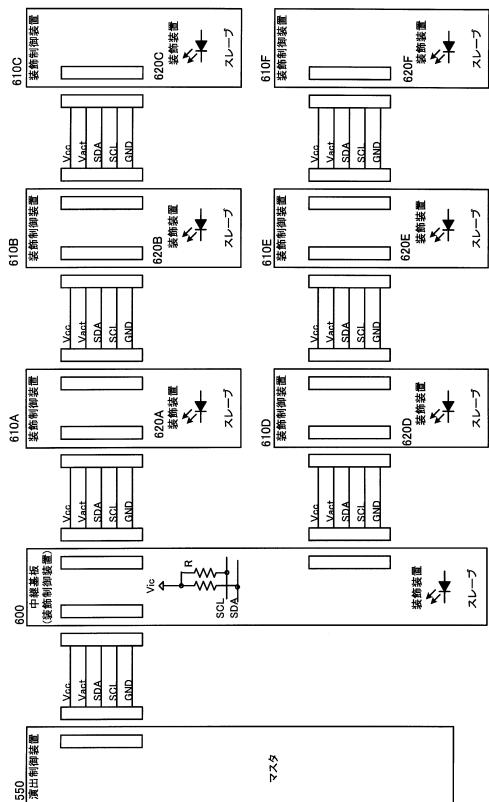

【図5】本発明の第1実施形態の装飾制御装置の接続の説明図である。

【図6】本発明の第1実施形態の装飾制御装置のブロック図である。

【図7】本発明の第1実施形態のI<sup>2</sup>C I/Oエクスパンダのブロック図である。

【図8A】本発明の第1実施形態の装飾装置を制御する装飾制御装置のI<sup>2</sup>C I/Oエクスパンダ周辺の回路図である。

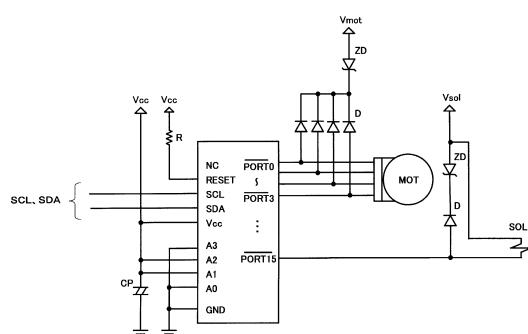

【図8B】本発明の第1実施形態の役物駆動MOT及び役物駆動SOLを制御する装飾制御装置のI<sup>2</sup>C I/Oエクスパンダ周辺の回路図である。

10

20

30

40

50

【図9】本発明の第1実施形態の中継基板の入出力に関する接続線の回路図である。

【図10】本発明の第1実施形態の装飾制御装置の入出力に関する接続線の回路図である。

【図11】本発明の第1実施形態の演出制御装置から装飾制御装置に出力されるデータに含まれるスレーブアドレスの説明図である。

【図12】本発明の第1実施形態のI<sup>2</sup>C I/Oエクスパンダアドレステーブルの説明図である。

【図13】本発明の第1実施形態のI<sup>2</sup>C I/Oエクスパンダに備わる出力設定レジスタに割り当てられたワークレジスタを説明するための図である。

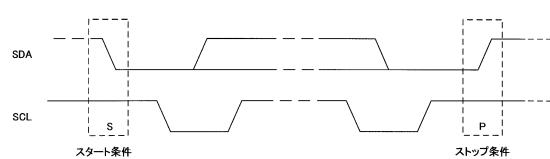

【図14】本発明の第1実施形態のマスタI Cが接続線SDA及び接続線SCLを介して出力するデータのスタート条件及びストップ条件の説明図である。 10

【図15】本発明の第1実施形態のマスタI Cから出力されたデータが入力された装飾制御装置が返答信号を出力するタイミングチャートである。

【図16】本発明の第1実施形態のマスタI Cが演出制御データを出力する場合の接続線SDA及び接続線SCLの信号レベルのタイミングチャートである。

【図17】本発明の第1実施形態のマスタI Cが、スレーブの個別アドレスを指定して装飾制御装置に演出制御データを設定する場合において、マスタI CとI<sup>2</sup>C I/Oエクスパンダとの間で授受されるデータのフォーマットを説明する図である。

【図18】本発明の第1実施形態のマスタI Cが、スレーブの個別アドレスを指定して装飾制御装置に演出制御データを設定する場合において、マスタI CとI<sup>2</sup>C I/Oエクスパンダとの間で授受される演出制御データに具体的な数値を適用したものである。 20

【図19】本発明の第1実施形態の演出制御データの別の形態を説明する図である。

【図20】本発明の第1実施形態のマスタI CがI<sup>2</sup>C I/Oエクスパンダを初期化するときに、マスタI CからI<sup>2</sup>C I/Oエクスパンダへ送信される初期化指示データのデータフォーマットを説明する図である。

【図21】本発明の第1実施形態の異常判定テーブルを説明する図である。

【図22】本発明の第1実施形態の演出制御装置による処理のフローチャートである。

【図23】本発明の第1実施形態のI<sup>2</sup>C初期リセット処理のフローチャートである。

【図24】本発明の第1実施形態のスレーブリセット処理のフローチャートである。

【図25】本発明の第1実施形態の発光制御スレーブ出力処理のフローチャートである。 30

【図26】本発明の第1実施形態のスレーブ連続処理のフローチャートである。

【図27】本発明の第1実施形態のI<sup>2</sup>C随時リセット処理のフローチャートである。

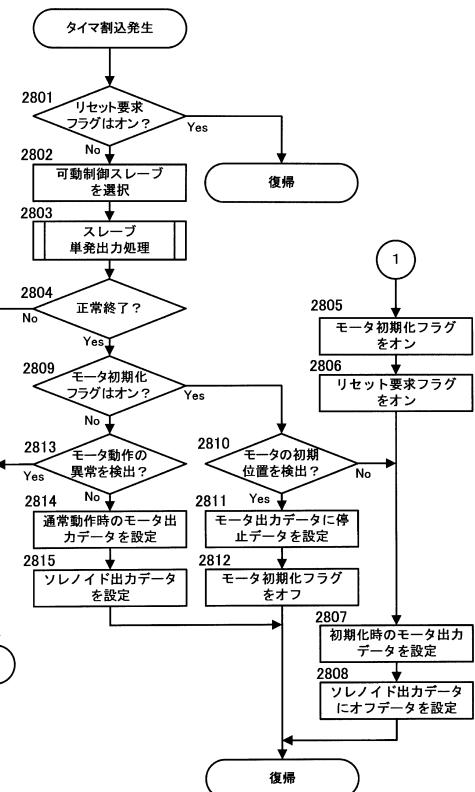

【図28】本発明の第1実施形態のタイマ割込が発生した場合に実行されるタイマ割込処理のフローチャートである。

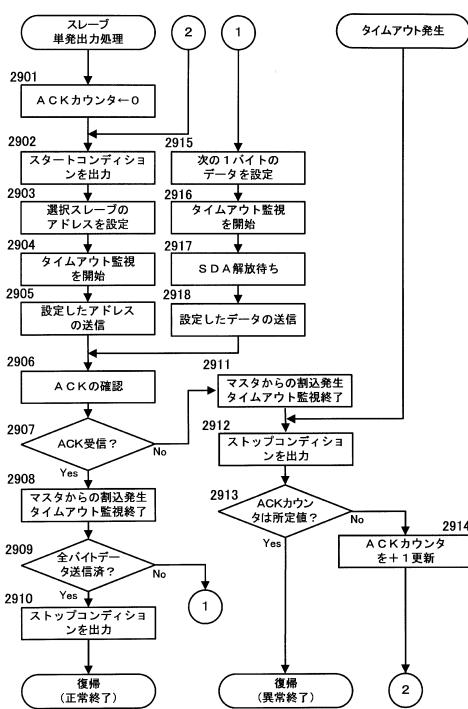

【図29】本発明の第1実施形態のスレーブ単発出力処理のフローチャートである。

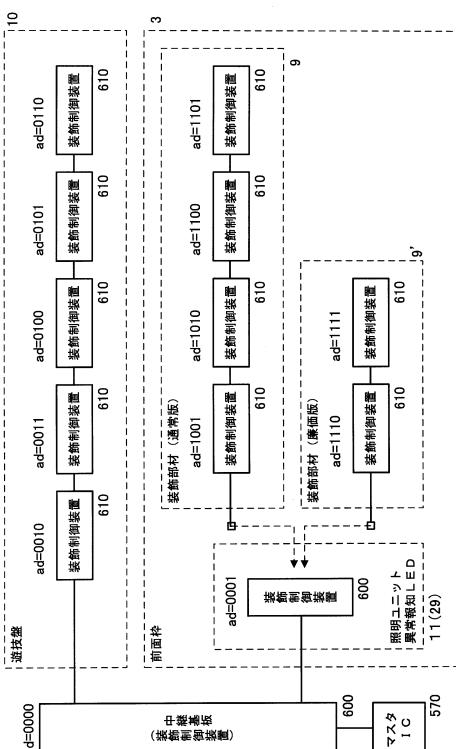

【図30】本発明の第1の実施形態の遊技機全体に設けられる装飾制御装置の接続形態を示す図である。

【図31】本発明の第2実施形態の演出制御装置と装飾制御装置との接続の説明図である。

【図32】本発明の第2実施形態の異常判定テーブルの説明図である。 40

【図33】本発明の第2実施形態のI<sup>2</sup>C初期リセット処理のフローチャートである。

【図34】本発明の第2実施形態のI<sup>2</sup>C随時リセット処理のフローチャートである。

【図35】本発明の第2実施形態の電源投入によるマスタI Cの初期化前後のタイミングチャートである。

【図36】本発明の第2実施形態の異常が発生したマスタI Cの初期化前後のタイミングチャートである。

【発明を実施するための形態】

【0023】

(第1実施形態)

以下、本発明の第1実施形態について、図1～図32を参照して説明する。

10

20

30

40

50

**【 0 0 2 4 】**

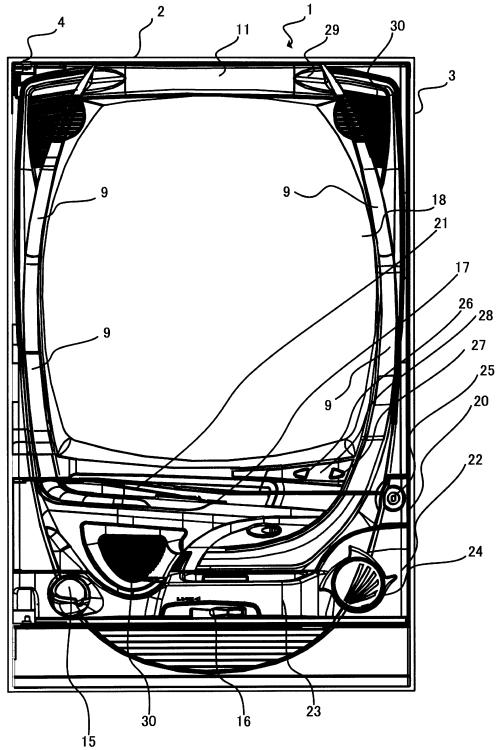

図1は、本発明の第1実施形態の遊技機1の説明図である。

**【 0 0 2 5 】**

遊技機1の前面枠(遊技枠)3は本体枠(外枠)2にヒンジ4を介して、遊技機1の前面に開閉回動可能に組み付けられる。前面枠3の表側には、遊技盤10(図2参照)が収装される。また、前面枠3には、遊技盤10の前面を覆うカバーガラス(透明部材)を備えたガラス枠18が取り付けられている。

**【 0 0 2 6 】**

ガラス枠18のカバーガラスの周囲には、装飾光が発光される装飾部材9が備えられている。この装飾部材9の内部にはランプやLED等からなる装飾装置620(図3参照)が備えられている。この装飾装置620を所定の発光態様によって発光することによって、装飾部材9が所定の発光態様によって発光する。

10

**【 0 0 2 7 】**

ガラス枠18の左右には、音響(例えば、効果音)を発するスピーカ30が備えられている。また、ガラス枠18の上方には照明ユニット11が備えられている。照明ユニット11の内部には、前述した装飾装置620が備えられている。

**【 0 0 2 8 】**

照明ユニット11の右側には、遊技機1において異常が発生したことを報知するための異常報知LED29が備えられている。

**【 0 0 2 9 】**

20

前面枠3の下部の開閉パネル20には図示しない打球発射装置に遊技球を供給する上皿21が、固定パネル22には灰皿15、下皿23及び打球発射装置の操作部24等が備えられる。下皿23には、下皿23に貯まった遊技球を排出するための下皿球抜き機構16が備えられる。前面枠3下部右側には、ガラス枠18を施錠するための鍵25が備えられている。

**【 0 0 3 0 】**

また、遊技者が操作部24を回動操作することによって、打球発射装置は、上皿21から供給される遊技球を発射する。

**【 0 0 3 1 】**

30

また、上皿21の上縁部には、遊技者からの操作入力を受け付けるための演出ボタン17が備えられている。

**【 0 0 3 2 】**

遊技者が演出ボタン17を操作することによって、遊技盤10に設けられた表示装置53(図2参照)における特図変動表示ゲームの演出内容を選択して、表示装置53における特図変動表示ゲームに、遊技者の操作を介入させた演出を行うことができる。

**【 0 0 3 3 】**

なお、特図変動表示ゲームは、発射された遊技球が遊技盤10に備わる第1始動入賞口45(図2参照)又は普通変動入賞装置36(図2参照)の第2始動入賞口に入賞した場合に開始される。特図変動表示ゲームでは、表示装置53において複数の識別情報が変動表示する。そして、変動表示していた識別情報が停止し、停止した識別情報の結果態様が特定の結果態様である場合に、遊技機1の状態が遊技者に有利な状態(特典が付与される状態)である特別遊技状態に遷移する。

40

**【 0 0 3 4 】**

上皿21の右上部には、遊技者が遊技球を借りる場合に操作する球貸ボタン26、及び、図示しないカードユニットからプリペイドカードを排出させるために操作される排出ボタン27が設けられている。これらのボタン26、27の間には、プリペイドカードの残高を表示する残高表示部28が設けられる。

**【 0 0 3 5 】**

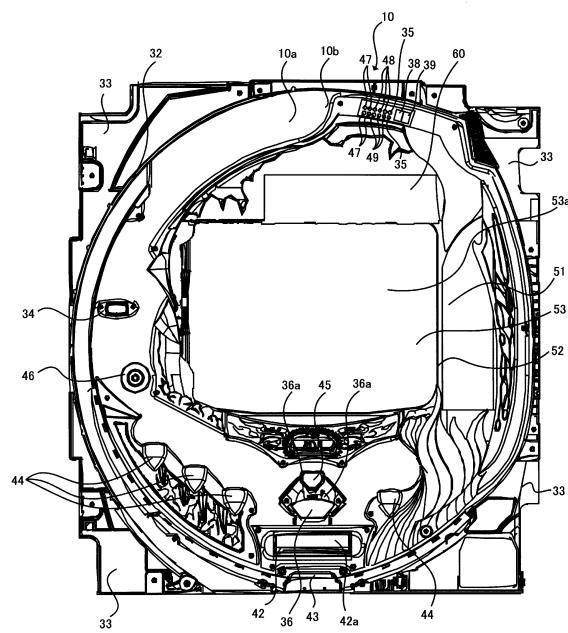

図2は、本発明の第1実施形態の遊技盤10の正面図である。

**【 0 0 3 6 】**

50

図1に示す遊技機1は、内部の遊技領域10a内に遊技球を発射して（弾球して）遊技を行うもので、ガラス枠18のカバーガラスの奥側には、遊技領域10aを構成する遊技盤10が設置されている。

【0037】

遊技盤10は、各種部材の取付ベースとなる平板状の遊技盤本体10b（木製又は合成樹脂製）を備え、該遊技盤本体10bの前面にガイドレール32で囲まれた遊技領域10aを有している。また、遊技盤本体10bの前面であってガイドレール32の外側には、前面構成部材33、33、…が取り付けられている。そして、このガイドレール32で囲まれた遊技領域10a内に発射装置から遊技球（打球；遊技媒体）を発射して遊技を行うようになっている。

10

【0038】

遊技領域10aの略中央には、特図変動表示ゲームの表示領域となる窓部52を形成するセンターケース51が取り付けられている。このセンターケース51に形成された窓部52の後方には、複数の識別情報を変動表示する特図変動表示ゲームの演出を実行可能な演出表示装置としての表示装置53が配されるようになっている。この表示装置53は、例えば、液晶ディスプレイを備え、表示内容が変化可能な表示部53aがセンターケース51の窓部52を介して遊技盤10の前面側から視認可能となるように配されている。なお、表示装置53は、液晶ディスプレイを備えるものに限らず、EL、CRT等のディスプレイを備えるものであってもよい。

20

【0039】

センターケース51の窓部52の上端付近には、遊技状態に基づいて動作可能な可動役物60が取り付けられる。

【0040】

また、遊技盤10には、普図始動ゲート34と、普図変動表示ゲームの未処理回数を表示する普図記憶表示器47、普図変動表示ゲームを表示する普図表示器35が設けられている。また、遊技領域10a内には、第1の始動入賞領域をなす第1始動入賞口45と、第2の始動入賞領域をなす第2始動入賞口を有する普通変動入賞装置36と、が設けられている。そして、遊技球が第1始動入賞口45に入賞した場合は、補助遊技として第1特図変動表示ゲームが実行され、遊技球が普通変動入賞装置36に入賞した場合は、補助遊技として第2特図変動表示ゲームが実行されるようになっている。

30

【0041】

また、遊技盤10には、第1特図変動表示ゲームを表示する第1特図表示器38と、第2特図変動表示ゲームを表示する第2特図表示器39と、が設けられている。また、第1特図変動表示ゲームの未処理回数（第1特図始動記憶）を表示する第1特図記憶表示器48と、第2特図変動表示ゲームの未処理回数（第2特図始動記憶）を表示する第2特図記憶表示器49が設けられている。なお、普図記憶表示器47、普図表示器35、第1特図表示器38、第2特図表示器39、第1特図記憶表示器48、第2特図記憶表示器49は、遊技状態を表す遊技状態表示LED（図示略）と併せて、セグメントLEDとして一体に設けられている。

【0042】

さらに遊技領域10aには、上端側が手前側に倒れる方向に回動して開放可能になっているアタッカ形式の開閉扉42aを有し、第1特図変動表示ゲーム、第2特図変動表示ゲームの結果如何によって大入賞口を閉じた状態（遊技者にとって不利な状態）から開放状態（遊技者にとって有利な状態）に変換する特別変動入賞装置42、入賞口などに入賞しなかった遊技球を回収するアウト穴43が設けられている。この他、遊技領域10aには、一般入賞口44、44、…、打球方向変換部材としての風車46、多数の障害釘（図示略）などが配設されている。

40

【0043】

普図始動ゲート34内には、該普図始動ゲート34を通過した遊技球を検出するためのゲートSW34a（図3参照）が設けられている。そして、遊技領域10a内に打ち込ま

50

れた遊技球が普図始動ゲート34内を通過すると、普図変動表示ゲームが行われる。

【0044】

また、普図変動表示ゲームを開始できない状態中に、普図始動ゲート34を遊技球が通過すると、普図始動記憶数が上限数未満であるならば、普図始動記憶数が1加算されて、当該普図変動表示ゲームが当りとなるか否かを示す乱数が普図始動記憶として一つ記憶される。

【0045】

普図変動表示ゲームが開始できない状態とは、例えば、普図変動表示ゲームが既に行われ、その普図変動表示ゲームが終了していない状態や、普図変動表示ゲームが当って普通変動入賞装置36が開状態に変換されている状態のことをいう。

10

【0046】

なお、普図変動表示ゲームの始動記憶数は、LEDを備える普図記憶表示器47にて表示される。

【0047】

普図変動表示ゲームは、遊技盤10に設けられた普図表示器35で実行されるようになっている。なお、表示装置53の表示領域の一部で普図変動表示ゲームを表示するようにもよく、この場合は識別図柄として、例えば、数字、記号、キャラクタ図柄などを用い、この識別図柄を所定時間変動表示させた後、停止表示させることにより行うようとする。

【0048】

この普図変動表示ゲームの停止表示が特別の結果態様となれば、普図変動表示ゲームが当りとなって、普通変動入賞装置36の開閉部材36a、36aが所定時間（例えば、0.5秒間）開放される。これにより、普通変動入賞装置36に遊技球が入賞しやすくなり、第2特図変動表示ゲームの始動が容易となる。

20

【0049】

普通変動入賞装置36は左右一対の開閉部材36a、36aを具備し、第1始動入賞口45の下部に配設される。この開閉部材36a、36aは、常時は遊技球の直径程度の間隔をおいて閉じた状態（遊技者にとって不利な状態）を保持しているが、普図変動表示ゲームの結果が所定の停止表示態様となった場合（普図変動表示ゲームが当りとなった場合）には、駆動装置としてのソレノイド（普電SOL36b、図3参照）によって、逆「八」の字状に開いて普通変動入賞装置36に遊技球が流入し易い状態（遊技者にとって有利な状態）に変化させられるようになっている。

30

【0050】

また、本実施形態の遊技機1は、特図変動表示ゲームの結果態様に基づき、遊技状態として、表示装置53における特図変動表示ゲームの変動表示時間を短縮する時短動作状態（第2動作状態）を発生可能となっている。この時短動作状態（第2動作状態）は、普通変動入賞装置36の動作状態が、通常動作状態（第1動作状態）に比べて開放状態となりやすい状態である。

【0051】

この時短動作状態においては、上述の普図変動表示ゲームの実行時間が、通常動作状態における長い実行時間よりも短くなるように制御され（例えば、10秒が1秒）、これにより、単位時間当りの普通変動入賞装置36の開放回数が実質的に多くなるように制御される。また、時短動作状態においては、普図変動表示ゲームが当り結果となって普通変動入賞装置36が開放される場合に、開放時間が通常動作状態の短い開放時間より長くされるように制御される（例えば、0.3秒が1.8秒）。また、時短動作状態においては、普図変動表示ゲームの1回の当り結果に対して、普通変動入賞装置36が1回ではなく、複数回（例えば、2回）開放される。さらに、時短動作状態においては普図変動表示ゲームの当り結果となる確率が通常動作状態より高くなるように制御される。すなわち、通常動作状態よりも普通変動入賞装置36の開放回数が増加され、普通変動入賞装置36に遊技球が入賞しやすくなり、第2特図変動表示ゲームの始動が容易となる。

40

50

**【 0 0 5 2 】**

第1始動入賞口45の内部には第1始動口SW45a(図3参照)が備えられ、この第1始動口SW45aによって遊技球を検出することに基づき、補助遊技としての第1特図変動表示ゲームを開始する始動権利が発生するようになっている。また、普通変動入賞装置36の内部には第2始動口SW36d(図3参照)が備えられ、この第2始動口SW36dによって遊技球を検出することに基づき、補助遊技としての第2特図変動表示ゲームを開始する始動権利が発生するようになっている。

**【 0 0 5 3 】**

この第1特図変動表示ゲームを開始する始動権利は、所定の上限数(例えば4)の範囲内で第1始動記憶(特図1始動記憶)として記憶される。そして、この第1始動記憶数は、第1特図記憶表示器48に表示される。また、第2特図変動表示ゲームを開始する始動権利は、所定の上限数(例えば4)の範囲内で第2始動記憶(特図2始動記憶)として記憶される。そして、この第2始動記憶数は、第2特図記憶表示器49にて表示される。

10

**【 0 0 5 4 】**

そして、第1特図変動表示ゲームが開始可能な状態(第1始動記憶数及び第2始動記憶数が0の状態)で、第1始動入賞口45に遊技球が入賞すると、始動権利の発生に伴って抽出された乱数が第1始動記憶として記憶されて、第1始動記憶数が1加算されるとともに、直ちに第1始動記憶に基づいて、第1特図変動表示ゲームが開始され、この際に第1始動記憶数が1減算される。

**【 0 0 5 5 】**

20

また、第2特図変動表示ゲームは第1特図変動表示ゲームよりも優先して実行されるため、第1始動記憶数が0でなくとも、第2始動記憶数が0であれば、第2始動入賞口をなす普通変動入賞装置36に遊技球が入賞すると、始動権利の発生に伴って抽出された乱数が第2始動記憶として記憶されて、第2始動記憶数が1加算されるとともに、実行中の第1特図変動表示ゲームが終了後直ちに第2始動記憶に基づいて、第2特図変動表示ゲームが開始され、この際に第2始動記憶数が1減算される。

**【 0 0 5 6 】**

一方、第1特図変動表示ゲーム又は第2特図変動表示ゲームが直ちに開始できない状態、例えば、既に第1特図変動表示ゲーム又は第2特図変動表示ゲームが行われ、その特図変動表示ゲームが終了していない状態や、特別遊技状態となっている場合に、第1始動入賞口45に遊技球が入賞すると、第1始動記憶数が上限数未満(例えば、4個未満)ならば、第1始動記憶数が1加算されて、第1始動入賞口45に遊技球が入賞したタイミングで抽出された乱数が第1始動記憶として一つ記憶される。

30

**【 0 0 5 7 】**

同様に、この場合に第2始動入賞口をなす普通変動入賞装置36に遊技球が入賞すると、第2始動記憶数が上限数未満(例えば、4個未満)ならば、第2始動記憶数が1加算されて、第2始動入賞口に遊技球が入賞したタイミングで抽出された乱数が第2始動記憶として一つ記憶される。

**【 0 0 5 8 】**

40

そして、第1特図変動表示ゲーム又は第2特図変動表示ゲームが開始可能な状態となると、第1始動記憶又は第2始動記憶に基づき第1特図変動表示ゲーム又は第2特図変動表示ゲームが開始される。このとき、第1特図変動表示ゲームと第2特図変動表示ゲームは同時に実行されることなく、第2特図変動表示ゲームが第1特図変動表示ゲームよりも優先して実行されるようになっている。

**【 0 0 5 9 】**

すなわち、第1始動記憶と第2始動記憶がある場合には、第2特図変動表示ゲームが実行される。

**【 0 0 6 0 】**

補助遊技としての第1特図変動表示ゲーム、第2特図変動表示ゲームは、遊技盤10に設けられた第1特図表示器38、第2特図表示器39で実行されるようになっており、複

50

数の識別情報を変動表示したのち、所定の結果態様を停止表示することで行われる。また、表示装置 53 にて各特図変動表示ゲームに対応して複数種類の識別情報（例えば、数字、記号、キャラクタ図柄など）を変動表示させる特図変動表示ゲームが実行される。そして、この特図変動表示ゲームの結果として、第1特図表示器 38 又は第2特図表示器 39 の表示態様が特別結果態様となった場合には、大当たりとなって特別遊技状態（いわゆる、大当たり状態）となる。また、これに対応して表示装置 53 の表示態様も特別結果態様（例えば、「7, 7, 7」等のゾロ目数字の何れか）となる。なお、遊技機に第1特図表示器 38、第2特図表示器 39 を備えずに、表示装置 53 のみで特図変動表示ゲームを実行するようにしてもよい。

## 【0061】

10

また、本実施形態の遊技機 1 は、特図変動表示ゲームの結果態様に基づき、遊技状態として確変状態（第2確率状態）を発生可能となっている。この確変状態（第2確率状態）は、特図変動表示ゲームでの当り結果となる確率が、通常確率状態（第1確率状態）に比べて高い状態である。なお、第1特図変動表示ゲームと第2特図変動表示ゲームのどちらの特図変動表示ゲームの結果態様に基づき確変状態となても、第1特図変動表示ゲーム及び第2特図変動表示ゲームの両方が確変状態となる。また、確変状態と上述した時短動作状態はそれぞれ独立して発生可能であり、両方を同時に発生することも可能であるし、一方のみを発生させることも可能である。

## 【0062】

20

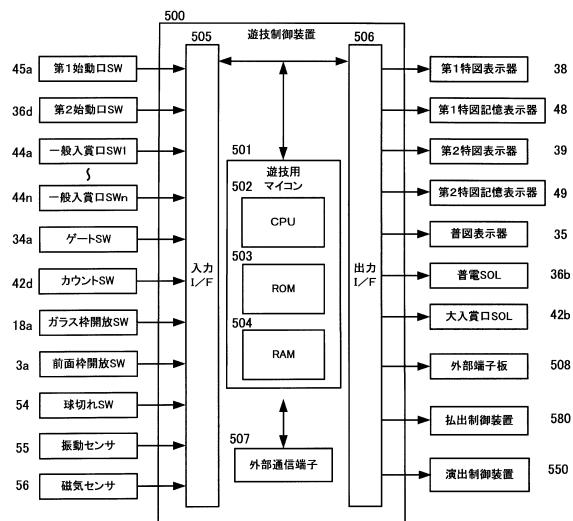

図3は、本発明の第1実施形態の遊技機1の構成を示すブロック図である。

## 【0063】

遊技機1は、遊技を統括的に制御する遊技制御装置500、各種演出を行うために表示装置53及びスピーカ30等を制御する演出制御装置550、遊技球を払い出すために図示しない払出モータを制御する払出制御装置580を備える。

## 【0064】

まず、遊技制御装置500について説明する。図4では、演出制御装置550について説明する。

## 【0065】

遊技制御装置500は、遊技用マイコン501、入力I/F（Interface）505、出力I/F（Interface）506、及び外部通信端子507を備える。

30

## 【0066】

遊技用マイコン501は、CPU502、ROM（Read Only Memory）503及びRAM（Random Access Memory）504を備える。

## 【0067】

CPU502は、遊技を統括的に制御する主制御装置であって、遊技制御を司る。ROM503は、遊技制御のための不变の情報（プログラム、データ等）を記憶している。RAM504は、遊技制御時にワークエリアとして利用される。

## 【0068】

外部通信端子507は、遊技制御装置500の設定情報等を検査する検査装置等の外部機器に遊技制御装置500を接続する。

40

## 【0069】

CPU502は、入力I/F505を介して各種入力装置（第1始動口SW45a、第2始動口SW36d、一般入賞口SW44a、ゲートSW34a、カウントSW42d、ガラス枠開放SW18a、前面枠開放SW3a、球切れSW54、振動センサ55、及び磁気センサ56）からの検出信号を受けて、大当たり抽選等、種々の処理を行う。

## 【0070】

第1始動口SW45aは、第1始動入賞口45に遊技球が入賞したことを検出するスイッチである。第2始動口SW36dは、普通変動入賞装置36の第2始動入賞口に遊技球が入賞したことを検出するスイッチである。

## 【0071】

50

一般入賞口 SW a 4 4 a ~ 4 4 n は、一般入賞口 4 4 に遊技球が入賞したことを検出するスイッチである。ゲート SW 3 4 a は、普図始動ゲート 3 4 を遊技球が通過したことを検出するスイッチである。

【 0 0 7 2 】

カウント SW 4 2 d は、特別変動入賞装置 4 2 の大入賞口に遊技球が入賞したことを検出するスイッチである。

【 0 0 7 3 】

ガラス枠開放 SW 1 8 a は、ガラス枠 1 8 が開放されたことを検出するスイッチである。前面枠開放 SW 3 a は、前面枠 3 が開放されたことを検出するスイッチである。

【 0 0 7 4 】

球切れ SW 5 4 は、遊技機 1 の内部に貯留され、払い出しに用いられる遊技球の数が所定数以下になったことを検出するスイッチである。

【 0 0 7 5 】

振動センサ 5 5 は、遊技機 1 に与えられた振動を検出するセンサであり、遊技機 1 に振動を与えて、不当に遊技球を獲得する不正を検出する。磁気センサ 5 6 は、第 1 始動入賞口 4 5 、普通変動入賞装置 3 6 の第 2 始動入賞口、一般入賞口 4 4 、特別変動入賞装置 4 2 の大入賞口、及び普図始動ゲート 3 4 付近に設けられ、磁力を検出するセンサである。磁気センサ 9 3 は、各入賞口付近に磁石を近づけて、遊技領域 1 0 a に発射された遊技球を各入賞口に導く不正を検出する。

【 0 0 7 6 】

また、CPU 5 0 2 は、出力 I / F 5 0 6 を介して、第 1 特図表示器 3 8 、第 1 特図記憶表示器 4 8 、第 2 特図表示器 3 9 、第 2 特図記憶表示器 4 9 、普図表示器 3 5 、普電 SOL 3 6 b 、大入賞口 SOL 4 2 b 、払出制御装置 5 8 0 、及び演出制御装置 5 5 0 に指令信号を送信して、遊技を統括的に制御する。

【 0 0 7 7 】

第 1 特図表示器 3 8 には、第 1 始動入賞口 4 5 に遊技球が入賞した場合に補助遊技として実行される第 1 特図変動表示ゲームが表示される。第 1 特図記憶表示器 4 8 には、所定の上限数の範囲内で記憶される第 1 特図変動表示ゲームを開始する始動権利である第 1 始動記憶数が表示される。

【 0 0 7 8 】

第 2 特図表示器 3 9 には、普通変動入賞装置 3 6 の大入賞口に遊技球が入賞した場合に補助遊技として実行される第 2 特図変動表示ゲームが表示される。第 2 特図記憶表示器 4 9 には、所定の上限数の範囲内で記憶される第 2 特図変動表示ゲームを開始する始動権利である第 2 始動記憶数が表示される。

【 0 0 7 9 】

普図表示器 3 5 には、遊技球が普図始動ゲート 3 4 を通過した場合に行われる普図変動表示ゲームが表示される。

【 0 0 8 0 】

普電 SOL 3 6 b は、普図表示器 3 5 で実行される普図変動表示ゲームの停止表示が特別の結果態様となった場合に、開閉部材 3 6 a 、 3 6 a を開放し、普通変動入賞装置 3 6 の第 2 始動入賞口を遊技球が入賞しやすい状態にする。

【 0 0 8 1 】

大入賞口 SOL 4 2 b は、第 1 特図変動表示ゲーム又は第 2 特図変動表示ゲームの結果が特別の結果態様となり、特別遊技状態となった場合に、特別変動入賞装置 4 2 の開閉扉 4 2 a を開放して、大入賞口を遊技球が入賞しやすい状態に変換する。

【 0 0 8 2 】

また、遊技制御装置 5 0 0 は、遊技機データを、外部情報端子 5 0 8 を介して、図示しない情報収集端末装置を介して、図示しない遊技場管理装置に出力する。遊技場管理装置は、遊技場に設置された遊技機 1 の遊技データを収集管理する計算機である。

【 0 0 8 3 】

10

20

30

40

50

また、払出制御装置 580 は、遊技球が一般入賞口 44 又は大入賞口に入賞した場合に、入賞した入賞口に対応する数の遊技球の払い出し、又は球貸ボタン 26 が操作された場合に、所定数の遊技球の払い出しを行う払出指令を遊技制御装置 500 から受信した場合に、受信した払出指令に基づいて、図示しない払出モータを制御する。なお、払出指令には、払い出す遊技球の数が含まれる。

【0084】

遊技制御装置 500 は、変動開始コマンド、客待ちデモコマンド、ファンファーレコマンド、確率情報コマンド、及びエラー指定コマンド等を、遊技の状況を示す遊技データとして、出力 I/F 506 を介して、演出制御装置 550 へ送信する。

【0085】

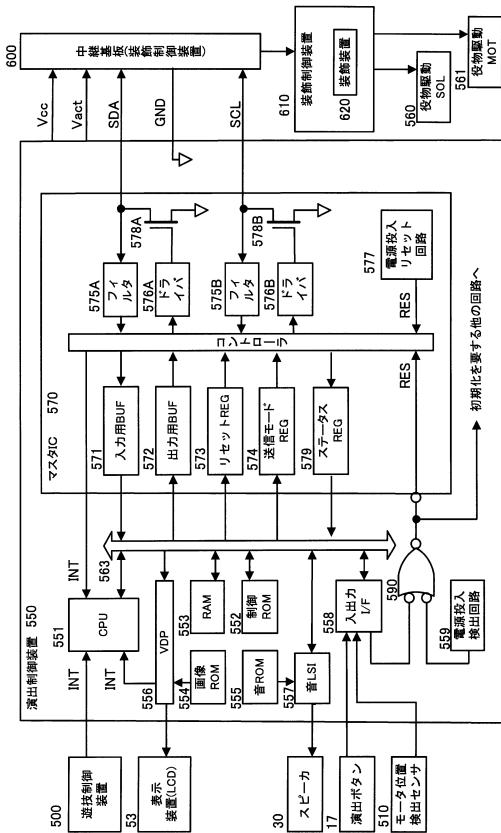

図 4 は、本発明の第 1 の実施形態の演出制御装置 550 の構成を示すブロック図である。

【0086】

演出制御装置 550 は、遊技制御装置 500 から入力される遊技データ（表示制御指令）に基づいて、演出内容を決定して、表示装置 53、及びスピーカ 30 を制御するとともに、装飾制御装置 610 を介して装飾装置 620、役物駆動 SOL 560（ソレノイド）、及び役物駆動 MOT（モータ）561 を制御する。詳細は後述するが、これら装飾装置 620、役物駆動 SOL 560、及び役物駆動 MOT 561（総称して演出装置という）によって、遊技の演出が行われる。また、演出制御装置 550 は、演出ボタン 17 から当該演出ボタン 17 が操作されたことを示す信号が入力される。

【0087】

演出制御装置 550 は、CPU 551、制御 ROM 552、RAM 553、画像 ROM 554、音 ROM 555、VDP 556、音 LSI 557、入出力 I/F 558、電源投入検出回路 559、マスター IC 570、及び NOR ゲート回路 590 を備える。

【0088】

CPU 551 は、遊技制御装置 500 に接続され、遊技制御装置 500 から指令信号が割込信号（INT）として入力され、入力された指令信号に基づいて、各種演出を制御する主制御装置である。また、CPU 551 には、マスター IC 570 の後述するコントローラから割込信号が入力されるとともに、VDP 556 から割込信号が入力される。

【0089】

なお、CPU 551 に割込信号が入力されると、CPU 551 は、現在実行中の処理を中断して、入力された割込信号に対応する処理を実行する。

【0090】

制御 ROM 552 には、演出制御のための不变の情報（プログラム、データ等）が格納されている。RAM 553 は、演出制御時にワークエリアとして利用される。

【0091】

画像 ROM 554 には、表示装置 53 に表示される画像データが格納され、画像 ROM 554 は VDP 556 に接続されている。音 ROM 555 には、スピーカ 30 から出力される音データが格納され、音 ROM 555 は音 LSI 557 に接続されている。

【0092】

VDP 556 は、表示装置 53 への画像出力を制御するプロセッサである。音 LSI 557 は、スピーカ 30 からの音声出力を制御する回路である。

【0093】

なお、VDP 556 は、表示装置 53 に表示される画像を更新する周期（33ms 周期）と同期する同期信号を発生させる同期信号発生手段を備える。同期信号発生手段は、同期信号を発生させるごとに、発生させた同期信号を CPU 551 に割込信号として入力する。

【0094】

入出力 I/F 558 は、演出ボタン 17、モータ位置検出センサ 510、及び NOR ゲート回路 590 に接続されるインターフェースであり、演出ボタン 17 からの操作信号、及

10

20

30

40

50

びモータ位置検出センサ 510 からのモータ位置検出信号を C P U 551 へ伝達するとともに、C P U 551 からのリセット信号を N O R ゲート回路 590 へ伝達する。

【0095】

なお、演出ボタン 17 は、上皿 21 の上縁部に設けられ、表示装置 53 で実行される第 1 特図変動表示ゲーム又は第 2 特図変動表示ゲームにおける演出で、遊技者によって操作される。

【0096】

また、モータ位置検出センサ 510 は、役物駆動 M O T 561 の回転軸が初期位置まで回転したことを検出した場合に、モータ位置検出信号を出力するセンサである。

【0097】

なお、N O R ゲート回路 590 は、マスタ I C 570 のコントローラに備わる R E S E T 端子、及び初期化を必要とする他の回路に接続される。初期化を必要とする他の回路とは、例えば、V D P 556 や音 L S I 557 などである。これらは、演出制御装置 550 に電源が投入されて起動したときに、C P U 551 により初期化されるものである。

【0098】

C P U 551、V D P 556、R A M 553、制御 R O M 552、音 L S I 557、及び入出力 I / F 558 はバス 563 を介してそれぞれ接続されている。

【0099】

電源投入検出回路 559 は、演出制御装置 550 に電源が投入された場合に、マスタ I C 570 の図示しないレジスタをデフォルト状態（すべて 0）に初期化するリセット信号を発生させ、発生させたリセット信号を N O R ゲート回路 590 へ出力する。

【0100】

また、C P U 551 は、所定の条件が成立した場合に、リセット信号をバス 563 を介して入出力 I / F 558 に出力し、入出力 I / F 558 は入力されたリセット信号を N O R ゲート回路 590 へ出力する。

【0101】

なお、電源投入検出回路 559 から N O R ゲート回路 590 へ入力されるリセット信号、及び C P U 551 から入出力 I / F 558 を介して N O R ゲート回路 590 へ入力されるリセット信号は、いずれの場合にもロウレベルの状態である場合にリセットを指令する信号として機能する。そのため、電源投入検出回路 559 及び C P U 551 の少なくとも一方から N O R ゲート回路 590 にリセット信号が出力されていれば、N O R ゲート回路 590 を介してリセット信号がマスタ I C 570 に入力される。

【0102】

上述したように、N O R ゲート回路 590 は、マスタ I C 570 及び初期化を必要とする他の回路に接続されるため、N O R ゲート回路 590 にリセットが入力されると、マスタ I C 570 及び当該 N O R ゲート回路 590 に接続される初期化を必要とする他の回路が初期化される。

【0103】

なお、初期化を必要とする他の回路がない場合には、N O R ゲート回路 590 は、マスタ I C 570 にのみ接続される。

【0104】

次に、マスタ I C 570 について説明する。

【0105】

マスタ I C 570 は、制御対象となる演出装置の装飾制御装置 610 のアドレスを指定して、指定したアドレスの装飾制御装置 610 に演出装置の制御内容を出力する。

【0106】

マスタ I C 570 は、接続線 V c c 、接続線 V a c t 、接続線 S D A 、接続線 S C L 、及び接続線 G N D (図 5 参照) の 5 本の接続線を介して、中継基板 (装飾制御装置) 600 に接続される。

【0107】

10

20

30

40

50

接続線 Vcc は、中継基板 600 及び装飾制御装置 610 に、ロジック用の電源を供給するための接続線である。接続線 Vact は、演出装置を駆動させるための電源（例えば、LED を発光させるための電源）を供給するための接続線である。接続線 SDA は、演出制御装置 550 と装飾制御装置 610 との間でデータを通信するための接続線であり、本実施形態におけるデータ線として機能する。接続線 SCL は、接続線 SDA でのデータ通信に用いられるクロック信号を入出力するための接続線であり、本実施形態におけるタイミング信号線として機能する。図 5 に示す接続線 GND は、接続線 Vcc 及び接続線 Vact で供給される電源のグランドである。

【0108】

中継基板 600 と装飾制御装置 610 との間は、マスタ IIC570 と中継基板 600 の間と同じく、接続線 Vcc、接続線 Vact、接続線 SDA、接続線 SCL、及び接続線 GND を介して接続される。 10

【0109】

マスタ IIC570 と装飾制御装置 610 とは、接続線 SDA 及び接続 SCL によって 2 ライン双方向通信を行う。 2

【0110】

マスタ IIC570 は、中継基板 600 及び装飾制御装置 610 にデータを送信する場合には、まず、接続線 SCL の信号レベルを HIGH に維持したまま、接続線 SDA の信号レベルを HIGH から LOW に変化させることにより、装飾制御装置 610 へのデータ出力を開始するためのスタート条件を成立させる（装飾制御装置 610 に対してスタートコンディションを発行する）。 20

【0111】

この後、マスタ IIC570 は、接続線 SCL の信号レベルを LOW に変更し、接続線 SCL の信号レベルが LOW である間に接続線 SDA の信号レベルを送信データの最初のビットのレベルに設定し、所定時間後に接続線 SCL の信号レベルを LOW から HIGH に変化させる。接続線 SCL の信号レベルが HIGH に変化すると、装飾制御装置 610 は接続線 SDA の信号レベルを取り込んで、送信データの最初のビットとして認識する。次いで、マスタ IIC570 は、接続線 SCL の信号レベルを HIGH から LOW に戻す。 30

【0112】

この手順を 1 回実行すると、マスタ IIC570 から装飾制御装置 610 へ 1 ビットのデータが送信され、最終的にはこの手順が 8 回繰り返されることで、送信データの単位ビットである 8 ビット全てがマスタ IIC570 から装飾制御装置 610 へ送信される（1 バイト分のデータが送信される）。 30

【0113】

そして、マスタ IIC570 は、最後の 8 ビット目のデータを送信し終えて、接続線 SCL の信号レベルを HIGH から LOW に戻した際に、接続線 SDA を解放して装飾制御装置 610 からの返答信号を受信することを待機する受信待機状態にする。 40

【0114】

受信待機状態になると、装飾制御装置 610 は、接続線 SDA を介して 1 ビットの返答信号（後述する ACK 又は NACK）をマスタ IIC570 に返す。次いで、マスタ IIC570 は、接続線 SCL の信号レベルを LOW から HIGH に変化させて返答信号のレベルを取り込み、所定時間後に接続線 SCL の信号レベルを HIGH から LOW に変化させると、装飾制御装置 610 は接続線 SDA を解放する。 40

【0115】

マスタ IIC570 は、このような 1 バイト分のデータ送信と 1 ビット分の返答信号の受信とを交互に繰り返し、装飾制御装置 610 へ出力すべきデータがすべて出力されるまで継続する。マスタ IIC570 は、出力すべきデータの出力が終了した場合には、接続線 SCL の信号レベルを HIGH に維持したまま、接続線 SDA の信号レベルを LOW から HIGH に変更させることにより、装飾制御装置 610 へのデータ出力を終了するためのストップ条件を成立させる（装飾制御装置 610 に対してストップコンディションを発行す 50

る)。

【0116】

入力用 B U F 5 7 1 は、装飾制御装置 6 1 0 から接続線 S D A を介して入力されたデータが一時的に記憶される記憶装置である。

【0117】

具体的には、マスタ I C 5 7 0 が入力モードに設定された場合において、装飾制御装置 6 1 0 からマスタ I C 5 7 0 に送信されたデータが、フィルタ 5 7 5 A によりノイズが除去されて入力用 B U F 5 7 1 に一時的に記憶される。

【0118】

出力用 B U F 5 7 2 は、装飾制御装置 6 1 0 に接続線 S D A を介して出力するデータが 10 一時的に記憶される。

【0119】

リセット R E G 5 7 3 は、本実施形態の初期化指示データ記憶領域として機能するもので、バス 5 6 3 に接続され、C P U 5 5 1 からの指令を受けてリセット信号をコントローラに出力する。コントローラは、マスタ I C 5 7 0 を統括的に制御し、各種処理を実行する。

【0120】

送信モード R E G 5 7 4 は、I<sup>2</sup>C I / O エクスパンダ 6 1 5 へデータを送信するモードを、バイトモード又はバッファモードにするかを選択するためのレジスタである。

【0121】

バイトモードは、マスタ I C 5 7 0 が、I<sup>2</sup>C I / O エクスパンダ 6 1 5 へデータを 1 バイト送信する毎に、I<sup>2</sup>C I / O エクスパンダ 6 1 5 から A C K 又は N A C K を受信し、A C K 及び N A C K の何れを受信した場合でも、マスタ I C 5 7 0 から C P U 5 5 1 に割込信号を出力するモードである。

【0122】

バッファモードは、マスタ I C 5 7 0 が、出力用 B U F 5 7 2 に格納された複数バイトのデータを、I<sup>2</sup>C I / O エクスパンダ 6 1 5 へ 1 バイト毎送信し、その送信の都度、I<sup>2</sup>C I / O エクスパンダ 6 1 5 から A C K 又は N A C K を受信するととともに、N A C K を受信した場合には、その時点で、割込信号を C P U 5 5 1 に出力するモードである。

【0123】

但し、バッファモードでは、A C K を受信した場合には、出力用 B U F 5 7 2 に格納されたすべてのデータが送信完了となった場合にのみ、割込信号を C P U 5 5 1 に出力し、マスタ I C 5 7 0 は、出力用 B U F 5 7 2 に未送信のデータが残っている状態で I<sup>2</sup>C I / O エクスパンダ 6 1 5 から A C K を受信したときには、割込信号を C P U 5 5 1 に出力せずに、出力用 B U F 5 7 2 から次の送信すべきデータを取り出して、I<sup>2</sup>C I / O エクスパンダ 6 1 5 へ出力する制御が繰り返される。

【0124】

なお、バイトモードは、マスタ I C 5 7 0 が、後述する初期化指示データ及び可動制御データを I<sup>2</sup>C I / O エクスパンダ 6 1 5 へ出力する場合に用いられる。バッファモードは、マスタ I C 5 7 0 が、後述する発光制御データを I<sup>2</sup>C I / O エクスパンダ 6 1 5 へ出力する場合に用いられる。

【0125】

ステータス R E G 5 7 9 は、マスタ I C 5 7 0 が I<sup>2</sup>C I / O エクスパンダ 6 1 5 から受信した返答信号が、A C K であったのか N A C K であったのかを識別するレジスタである。マスタ I C 5 7 0 は、C P U 5 5 1 に割込信号を出力する際に、I<sup>2</sup>C I / O エクスパンダ 6 1 5 から受信した返答信号に対応して、ステータス R E G 5 7 9 の値を設定する。

【0126】

フィルタ 5 7 5 A は、接続線 S D A から入力されたデータのノイズを除去する。ドライバ 5 7 6 A は、接続線 S D A からデータを出力する場合に、トランジスタ 5 7 8 A が動作

10

20

30

40

50

可能な電圧をトランジスタ 578A に印加する。

【0127】

図9に示すように接続線 SDA には、プルアップ抵抗 R によって所定の電圧が印加されて、接続線 SDA はフィルタ 575A 及びトランジスタ 578A に接続されている。

【0128】

トランジスタ 578A は、電力消費を抑えるために電界効果トランジスタ (FET) が用いられており、トランジスタ 578A のゲートはドライバ 576A に接続され、ドレインはプルアップ抵抗 R により所定の電圧が印加された接続線 SDA に接続され、ソースは接地されている。

【0129】

10

トランジスタ 578A のゲートに印加される電圧がトランジスタ 578A を動作させる所定値よりも小さければ、ドレインとソースとの間に電流が流れないので、接続線 SDA に印加された電圧は降下せず、その結果、接続線 SDA は HIGH レベルとなる。一方、トランジスタ 578A のゲートに印加される電圧がトランジスタ 578A を動作させる所定値以上であれば、所定値の電圧が印加されたドレインから接地されているソースへ電流が流れることによって、接続線 SDA の電圧が低下し、その結果、接続線 SDA は LOW レベルとなる。

【0130】

なお、トランジスタ 578A は、10ミリアンペア程度の電流をドレインからソースへ流しても破損しない仕様のものを用いている。このため、接続線 SDA には、通常の  $I^2$  C バス使用で用いられる電流値よりもはるかに大きい10ミリアンペア程度の電流を流すことが可能であり、演出制御装置 550 と装飾制御装置 610 との間のデータ送信が、ノイズによる障害に耐えうる構成となっている。

20

【0131】

ドライバ 576A は、データを接続線 SDA から出力する場合に、トランジスタ 578A にドレインとソースとの間に電流を流すためにトランジスタ 578A のゲートにトランジスタ 578A が動作可能な値の電圧を印加する。そして、ドライバ 576A は、接続線 SDA の電圧を、HIGH レベル又は LOW レベルに設定することによって、データを接続線 SDA から出力する。

【0132】

30

また、フィルタ 575B は、接続線 SCL から入力されたデータのノイズを除去する。ドライバ 576B は、接続線 SCL からデータを出力する場合に、トランジスタ 578B が動作可能な電圧をトランジスタ 578B に印加する。

【0133】

図9に示すように接続線 SCL は、プルアップ抵抗 R によって所定の電圧が印加されて、接続線 SDA はフィルタ 575B 及びトランジスタ 578B に接続されている。

【0134】

トランジスタ 578B は、電力消費を抑えるために電界効果トランジスタ (FET) が用いられており、トランジスタ 578B のゲートはドライバ 576B に接続され、ドレインはプルアップ抵抗 R により所定の電圧が印加された接続線 SCL に接続され、ソースは接地されている。

40

【0135】

トランジスタ 578B のゲートに印加される電圧がトランジスタ 578B を動作させる所定値よりも小さければ、ドレインとソースとの間に電流が流れないので、接続線 SCL に印加された電圧は降下せず、その結果、接続線 SCL は HIGH レベルとなる。一方、トランジスタ 578B のゲートに印加される電圧がトランジスタ 578B を動作させる所定値以上であれば、所定値の電圧が印加されたドレインから接地されているソースへ電流が流れることによって、接続線 SCL の電圧が低下し、その結果、接続線 SCL は LOW レベルとなる。

【0136】

50

なお、トランジスタ 578B は、10ミリアンペア程度の電流をドレインからソースへ流しても破損しない仕様のものを用いている。そのため、接続線 SCL には、通常の I<sup>2</sup>C バス使用で用いられる電流値よりもはるかに大きい 10ミリアンペア程度の電流を流すことが可能であり、演出制御装置 550 と装飾制御装置 610 との間のデータ送信が、ノイズによる障害に耐えうる構成となっている。

【0137】

ドライバ 576B は、クロック信号を接続線 SCL から出力する場合に、トランジスタ 578B にドレインとソースとの間に電流を流すためにトランジスタ 578B のゲートにトランジスタ 578B が動作可能な値の電圧を印加する。そして、ドライバ 576B は、接続線 SCL の電圧を、HIGH レベルと LOW レベルとに繰り返し変化させることによって、クロック信号を接続線 SCL から出力する。

10

【0138】

電源投入リセット回路 577 は、マスタ I C 570 に電源が投入されて、電源投入リセット回路 577 内の電圧が所定値に達した場合に、入力用 BUF571 及び出力用 BUF572 などの記憶領域をデフォルト状態にするためのリセット信号をコントローラに出力する。

【0139】

次に、中継基板 600 及び装飾制御装置 610 について説明する。

【0140】

なお、中継基板 600 は、装飾制御装置 610 のうちマスタ I C 570 に直接接続される、つまり最も上流側に位置するものである。

20

【0141】

装飾装置 620 は、装飾制御装置 610 に設けた I<sup>2</sup>C I/O エクスパンダ 615 (図 6 で後述) によって制御され、電流を流すことによって光が点滅して演出を行う発光装置であり、例えば LED などで構成される。役物駆動ソレノイド (SOL) 560 は、電流が流れると往復動作する装置であり、遊技盤 10 に配置される図示しない装飾のための役物を可動させて演出を行う。役物駆動モータ (MOT) 561 は、電流が流れると回転動作する装置であり、可動役物 60 を可動させて演出を行う。役物駆動ソレノイド (SOL) 560 及び役物駆動モータ (MOT) 561 も、装飾制御装置 610 に設けた I<sup>2</sup>C I/O エクスパンダ 615 によって制御される。

30

【0142】

なお、役物駆動 SOL 560 が可動役物 60 を可動させててもよいし、役物駆動 MOT 561 が図示しない役物を可動させててもよい。

【0143】

演出制御装置 550 と中継基板 600 との接続方法、及び中継基板 600 と中継基板 600 以外の装飾制御装置 610 との接続方法は、図 5 で詳細を説明する。装飾制御装置 610 は、図 6 ~ 図 10 で詳細を説明する。

【0144】

図 5 は、本発明の第 1 の実施形態の装飾制御装置 610A ~ 610F の接続の説明図である。なお、説明の都合上、装飾制御装置 610 として、1 個の中継基板 600 と、6 個の装飾制御装置 610A ~ 610F を図示しているが、実際には、遊技機の仕様に対応して必要な数の装飾制御装置 610 が接続されている。

40

【0145】

演出制御装置 550 は、接続線 Vcc、接続線 Vact、接続線 SDA、接続線 SCL、及び接続線 GND (以下、この 5 本の接続線を一つのハーネスという) を介して演出制御装置 550 と接続される。

【0146】

中継基板 600 には、二つの装飾制御装置 610A 及び 610D がそれぞれハーネスによって並列に接続される。

【0147】

50

装飾制御装置 610A にはハーネスを介して装飾制御装置 610B が接続され、装飾制御装置 610B にはハーネスを介して装飾制御装置 610C が接続される。

【0148】

一方、装飾制御装置 610D にはハーネスを介して装飾制御装置 610E が接続され、装飾制御装置 610E にはハーネスを介して装飾制御装置 610F が接続される。

【0149】

各装飾制御装置 610 は、ハーネスを自身に接続するための取付口となるコネクタを備える。このコネクタは各装飾制御装置 610 で共通であるので、接続線を接続順の誤配線を防止できる。

【0150】

ここで、装飾制御装置 610 に設けた I<sup>2</sup>C I / O エクスパンダ 615 ( 図 6 で後述 ) が装飾装置 620 を制御する方法について説明する。

【0151】

演出制御装置 550 は、遊技制御装置 500 から入力された遊技データに基づいて、演出装置の出力態様を決定する。そして、演出制御装置 550 は、決定された出力態様となるように、制御対象となる装飾制御装置 610 の個別アドレス ( I<sup>2</sup>C I / O エクスパンダ 615 の個別アドレス ) を含む演出制御データ ( 演出制御情報 ) を中継基板 600 に出力する。このとき、演出制御データは、中継基板 600 を介して演出制御装置 550 に接続されるすべての装飾制御装置 610 に対して接続線 SDA から出力される。このため、マスタ I C 570 は、マスタ I C 570 に接続されるすべての装飾制御装置 610 を制御可能である。

【0152】

なお、本実施形態では演出装置として LED 等の発光装置を例示しているので、 LED の発光態様が演出装置の出力態様に相当する。この場合、演出制御データによって、 LED の点灯 / 点滅 / 消灯が指示され、同時に、 LED の点滅周期や点灯輝度も指示される。

【0153】

各装飾制御装置 610 には、一意な個別アドレスが予め設定されているので、演出制御データが入力されると、入力された演出制御データに含まれるアドレスと設定されている個別アドレスとが一致するか否かを判定する。そして、入力された演出制御データに含まれるアドレスと設定されている個別アドレスとが一致すると判定された場合には、装飾制御装置 610 の I<sup>2</sup>C I / O エクスパンダ 615 は、演出制御データを取り込んで、対応する装飾装置 620 の出力態様を制御するとともに、 8 ビット目のデータが入力された直後に返答信号をマスタ I C 570 に出力する。

【0154】

なお、各装飾制御装置 610 には、個別アドレス以外にも、装飾制御装置 610 の I<sup>2</sup>C I / O エクスパンダ 615 を初期化するためのリセット用アドレスが設定されている。このリセットアドレスは、すべての I<sup>2</sup>C I / O エクスパンダ 615 に対して共通に設けられたアドレスであり、個別アドレスとして使用することは不可能となっている。また、このリセットアドレスの値を変更することもできないようになっている ( 詳細は後述する ) 。

【0155】

演出制御装置 550 は、装飾制御装置 610 ( 正確には、装飾制御装置 610 の I<sup>2</sup>C I / O エクスパンダ 615 ) を初期化する場合に、このリセット用の共通アドレスを含んだ初期化指示データを、中継基板 600 に出力する。このとき、初期化指示データ演出制御データは、中継基板 600 を介して、演出制御装置 550 に接続されるすべての装飾制御装置 610 に対して接続線 SDA から出力される。

【0156】

各装飾制御装置 610 には、リセット用の共通アドレスが予め設定されているので、入力されたデータに含まれるアドレスと、予め設定されているリセット用の共通アドレスとが一致するか否かを判定する。入力されたデータに含まれるアドレスと、予め設定されて

10

20

30

40

50

いるリセット用の共通アドレスとが一致すると判定された場合には、装飾制御装置 610 の I<sup>2</sup>C I / O エクスパンダ 615 は、返答信号をマスタ I C 570 に出力するとともに、入力されたデータを初期化指示データとして取り込み、I<sup>2</sup>C I / O エクスパンダ 615 自身を初期化する。

【0157】

なお、I<sup>2</sup>C I / O エクスパンダ 615 が初期化されると、当該初期化された I<sup>2</sup>C I / O エクスパンダ 615 によって制御される演出装置はオフ状態となる。

【0158】

このように、装飾制御装置 610 は、演出制御装置 550 からの指令に基づく制御を行うので、演出制御装置 550 と装飾制御装置 610 との関係は、演出制御装置 550 のマスタ I C 570 がマスタであり、装飾制御装置 610 の I<sup>2</sup>C I / O エクスパンダ 615 がスレーブである。

10

【0159】

図 5 では、装飾制御装置 610 の制御対象が装飾装置 620 である場合について説明したが、装飾制御装置 610 の制御対象が役物駆動 S O L 560 や役物駆動 M O T 561 であってもよい。この場合、演出装置がモータやソレノイドなどの駆動源となることから、これらの駆動源の動作様が、演出装置の出力様に相当することになる。この場合、演出制御データによって、駆動源の作動 / 停止が指示され、同時に動作速度も指示される。

【0160】

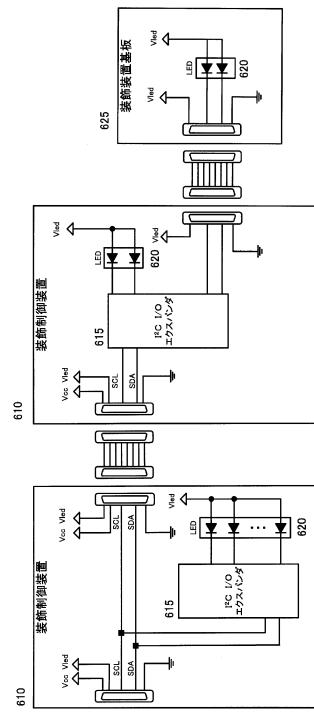

図 6 は、本発明の第 1 の実施形態の装飾制御装置 610 のブロック図である。

20

【0161】

図 6 では、装飾制御装置 610 の内部に装飾装置 620 である LED を備える装飾制御装置 610 (図 6 の下側の装飾制御装置 610) と、外部の装飾装置 620 に接続される装飾制御装置 610 (図 6 の中央の装飾制御装置 610) と、について説明する。

【0162】

まず、装飾制御装置 610 の内部に LED を備える装飾制御装置 610 について説明する。

【0163】

図 6 の下側の装飾制御装置 610 は、I<sup>2</sup>C I / O エクスパンダ 615 及び LED (装飾装置 20) を備える。接続線 SDA 及び接続線 SCL は、装飾制御装置 610 内で二つに分岐し、一方は、そのまま次の装飾制御装置 610 に出力される。他方は、I<sup>2</sup>C I / O エクスパンダ 615 に接続される。

30

【0164】

また、I<sup>2</sup>C I / O エクスパンダ 615 の出力側には、制御対象となる装飾装置 620 が接続される。I<sup>2</sup>C I / O エクスパンダ 615 の出力側は、図 7 で説明するポート 0 ~ 15 によって構成される。さらに、装飾制御装置 610 のすべてのポートが、図 8 A で後述する電流制限抵抗 R0 ~ R15 を介して、内部の LED に接続されている。なお、この電流制限抵抗 R0 ~ R15 も、装飾制御装置 610 に備えられている。

【0165】

前述したように、I<sup>2</sup>C I / O エクスパンダ 615 は、演出制御装置 550 から入力された演出制御データに含まれるアドレスと、当該 I<sup>2</sup>C I / O エクスパンダ 615 に設定されている個別アドレスとが一致する場合にのみ、演出制御データに含まれる装飾データに基づいて、I<sup>2</sup>C I / O エクスパンダ 615 に接続されている装飾装置 620 を制御する。

40

【0166】

なお、図中の電源 V<sub>LED</sub> は、図 5 で前述した接続線 V<sub>act</sub> により供給される電源 (LED を発光させるための電源) に相当するものである。

【0167】

次に、外部の装飾装置 620 に接続される装飾制御装置 610 について説明する。

【0168】

図6の中央の装飾制御装置610は、I<sup>2</sup>C I/Oエクスパンダ615及びLED(装飾装置20)を備え、装飾制御装置610の外部に接続される装飾装置基板625に備わるLEDに電流を流すための接続線、装飾装置基板625のLEDに電源電圧Vledを供給する接続線、及び、グランドに接地する接続線を介して、装飾制御装置610と装飾装置基板625とが接続される。

【0169】

装飾装置基板625は、I<sup>2</sup>C I/Oエクスパンダ615を備えておらず、LEDのみを備えた基板である。この場合、装飾装置基板625に備えたLEDに接続される電流制限抵抗(図8A)を、装飾装置基板625に設けることになるが、I<sup>2</sup>C I/Oエクスパンダ615が備えられた装飾制御装置610に設けてもよい。

10

【0170】

なお、装飾装置基板625に設けたLEDの数に対応して、装飾制御装置610から装飾装置基板625へ渡されることになる、これらのLEDに電流を流すための接続線の数が決定される。例えば、装飾装置基板625に二つのLEDを備えた場合には、I<sup>2</sup>C I/Oエクスパンダ615のポートと対応するLEDとを接続するための2本の制御線と、Vledを供給する電源線が1本とが、少なくとも必要となる。

【0171】

そして、中央の装飾制御装置610に設けられたI<sup>2</sup>C I/Oエクスパンダ615も、演出制御装置550から入力された演出制御データに含まれるアドレスと、当該I<sup>2</sup>C I/Oエクスパンダ615に設定されている個別アドレスとが一致する場合にのみ、演出制御データに含まれる装飾データに基づいて、I<sup>2</sup>C I/Oエクスパンダ615に接続されている装飾装置620を制御する。この場合、中央の装飾制御装置610に設けられた装飾装置620と、装飾装置基板625に設けられた装飾装置620の両方が、I<sup>2</sup>C I/Oエクスパンダ615によって制御される。

20

【0172】

このように、装飾装置基板625を設けて、装飾制御装置610から一部の装飾装置(LED)を分離させることで、離れた箇所に配置されたLEDであっても、共通のI<sup>2</sup>C I/Oエクスパンダ615により制御することができる。

【0173】

なお、装飾制御装置610は、装飾装置620の代わりに、役物駆動SOL560や役物駆動MOT561を接続し、これらを制御してもよいが、詳細は、図8Bで後述する。

30

【0174】

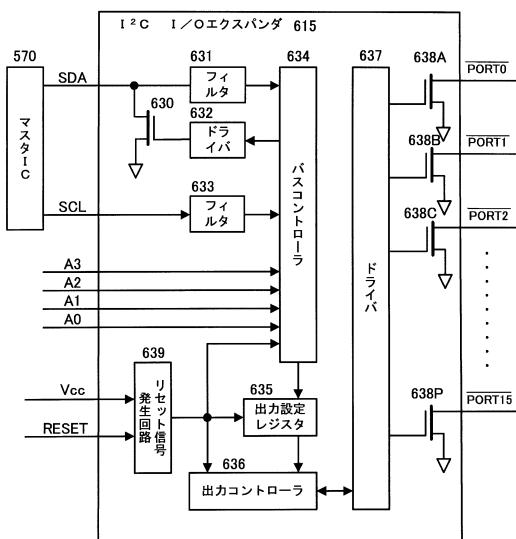

図7は、本発明の第1の実施形態のI<sup>2</sup>C I/Oエクスパンダ615のブロック図である。

【0175】

I<sup>2</sup>C I/Oエクスパンダ615は、接続線SDAに接続されるトランジスタ630、接続線SDAに接続されるフィルタ631、接続線SDAに接続されるドライバ632、接続線SCLに接続されるフィルタ633、バスコントローラ634、出力設定レジスタ635、出力コントローラ636、I<sup>2</sup>C I/Oエクスパンダ615の出力側の各ポート0~15に接続されるドライバ637、各ポート0~15に接続されるトランジスタ638A~638P、及びリセット信号発生回路639を備える。

40

【0176】

フィルタ631は、接続線SDAに接続され、接続線SDAから入力されたデータのノイズを除去し、ノイズが除去されたデータをバスコントローラ634に出力する。ドライバ632は、返答信号を接続線SDAから出力する場合に、トランジスタ630が動作可能な電圧をトランジスタ630に印加する。

【0177】

ドライバ632は、接続線SDAからデータ(返答信号)を出力する場合に、トランジスタ630が動作可能な電圧をトランジスタ630に印加する。

【0178】

50

トランジスタ 630 は、電力消費を抑えるために電界効果トランジスタ (FET) が用いられており、トランジスタ 630 のゲートはドライバ 632 に接続され、ドレインはブルアップ抵抗 R (図4 参照) により所定の電圧が印加された接続線 SDA に接続され、ソースは接地されている。

#### 【0179】

トランジスタ 630 のゲートに印加される電圧がトランジスタ 630 を動作させる所定値よりも小さければ、ドレインとソースとの間に電流が流れない。一方、トランジスタ 630 のゲートに印加される電圧がトランジスタ 630 を動作させる所定値以上であれば、所定値の電圧が印加されたドレインから接地されているソースへ電流が流れることによって、接続線 SDA の電圧が低下する。なお、トランジスタ 630 は、10 ミリアンペア程度の電流をドレインからソースへ流しても破損しない仕様のものを用いている。10

#### 【0180】

ドライバ 632 は、データ (返答信号) を接続線 SDA から出力する場合に、トランジスタ 630 にドレインとソースとの間に電流を流すためにトランジスタ 630 のゲートにトランジスタ 630 が動作可能な値の電圧を印加する。そして、ドライバ 632 は、接続線 SDA の電圧を HIGH から LOW へ繰り返し変化させることによって、データを接続線 SDA から出力する。

#### 【0181】

フィルタ 633 は、接続線 SCL に接続され、接続線 SCL から入力されたデータのノイズを除去し、ノイズが除去されたデータをバスコントローラ 634 に出力する。20

#### 【0182】

また、I<sup>2</sup>C I / O エクスパンダ 615 には、当該 I<sup>2</sup>C I / O エクスパンダ 615 に備わるアドレス設定用端子 A0 ~ A3 によって固有のアドレスが設定されており、バスコントローラ 634 に入力されている。さらに、I<sup>2</sup>C I / O エクスパンダ 615 をリセットするためのアドレスも、予め設定されている。

#### 【0183】

バスコントローラ 634 は、接続線 SDA から入力されたデータのアドレスが I<sup>2</sup>C I / O エクスパンダ 615 に設定された固有のアドレスと一致するか否かを判定し、一致している場合に当該データを演出制御データとして取り込む。

#### 【0184】

また、バスコントローラ 634 は、接続線 SDA から入力されたデータのアドレスが I<sup>2</sup>C I / O エクスパンダ 615 に予め設定されたリセット用のアドレスと一致するか否かを判定し、入力されたデータのアドレスと I<sup>2</sup>C I / O エクスパンダ 615 に予め設定されたリセット用のアドレスとが一致している場合に当該データを初期化指示データとして取り込み、当該 I<sup>2</sup>C I / O エクスパンダ 615 を初期化する。30

#### 【0185】

また、バスコントローラ 634 は、SCL 接続線の信号レベルの LOW から HIGH への変化回数が 8 回に達し 8 ビット目のデータを取り込んだ後、SCL 接続線の信号レベルが HIGH から LOW へ変化すると、返答信号を接続線 SDA からマスター I C 570 に出力する。さらに、SCL 接続線の信号レベルが LOW から HIGH へ変化することが確認され、再度 SCL 接続線の信号レベルが HIGH から LOW へ変化すると、接続線 SDA を開放する。つまり、SCL 接続線の信号レベルの LOW から HIGH への変化回数が 9 回になるタイミングで返答信号を出力する。40

#### 【0186】

出力設定レジスタ 635 には、当該 I<sup>2</sup>C I / O エクスパンダ 615 の動作モードやポート 0 ~ 15 の出力状態が設定される。バスコントローラ 634 が接続線 SDA から初期化指示データを取り込んで、当該 I<sup>2</sup>C I / O エクスパンダ 615 が初期化された場合には、出力設定レジスタ 635 は、すべてのポート 0 ~ 15 に電流が流れないように初期状態に設定される。

#### 【0187】

10

20

30

40

50

出力コントローラ 636 は、出力設定レジスタ 635 に設定されたデータに基づいて、ポートドライバ 637 を介して、各ポート 0 ~ 15 に接続された演出装置に電流を流すことによって、演出装置の出力状態を実際に制御する。この出力状態は、バスコントローラ 634 が接続線 SDA から演出制御データを取り込むと、取り込んだ演出制御データに指定されている内容に更新される。

【0188】

ドライバ 637 は、ポートに電流を流す場合に、電流を流すポートに接続されるトランジスタ 638A ~ 638P が動作可能な電圧を当該トランジスタに印加する。

【0189】

トランジスタ 638A ~ 638P のゲートはドライバ 637 に接続され、ドレインは図 8A 及び図 8B に示すように演出装置を動作させるための電圧が印加された接続線に接続するポート端子に接続され、ソースは接地されている。

【0190】

トランジスタ 638A ~ 638P のゲートに印加される電圧がトランジスタ 638A ~ 638P を動作させる所定値よりも小さければ、ドレインとソースとの間に電流が流れない。一方、638A ~ 638P のゲートに印加される電圧がトランジスタ 638 を動作させる所定値以上であれば、図 8A に示す電源 Vled、又は図 8B に示す電源 Vmot や電源 Vsol からゲートに印加されている所定の電圧が、トランジスタ 638 のドレインを介して接地されているソースへ電流が流れることによって、ポート端子に接続された演出装置の出力状態を制御できる。

10

20

【0191】

また、装飾制御装置 610 の I<sup>2</sup>C I / O エクスパンダ 615 は、I<sup>2</sup>C I / O エクスパンダ 615 のポート端子に接続された全ての演出装置を同時期に制御することが可能であるので、I<sup>2</sup>C I / O エクスパンダ 615 のポート端子に接続された一つの演出装置を一つのグループとして制御することができる。

【0192】

そして、各装飾制御装置 610 に備わる I<sup>2</sup>C I / O エクスパンダ 615 同士は、互いに異なる個別アドレスが割り当てられているので、演出装置が複数のグループに分割された形態となっている。即ち、各装飾制御装置 610 に備わる I<sup>2</sup>C I / O エクスパンダ 615 は、演出装置をグループ単位で制御可能なグループ単位制御手段として構成されているものである。

30

【0193】

従って、装飾制御装置 610 を統括する演出制御装置 550 は、グループ単位制御手段を統括して制御するグループ統括制御手段として機能している。

【0194】

リセット信号発生回路 639 には、I<sup>2</sup>C I / O エクスパンダ 615 に電源を供給する接続線 Vcc と接続される Vcc 端子、及び外部からのリセット信号を受け付ける RESET 端子が接続されている。

【0195】

リセット信号発生回路 639 は、I<sup>2</sup>C I / O エクスパンダ 615 に電源が投入され、電圧が所定値まで立ち上がった場合、リセット信号を発生させ、発生させたリセット信号をバスコントローラ 634、出力設定レジスタ 635、及び出力コントローラ 636 に入力する。

40

【0196】

なお、外部から LOW レベルのリセット信号が入力された場合には、リセット信号発生回路 639 はリセット信号を出力するので、演出制御装置 550 の CPU551 から、NOR ゲート回路 590 を経由して、RESET 端子からリセット信号を入力するようにしてもよい。RESET 端子を使用しない場合は、図 8A 及び図 8B に示すように RESET 端子は HIGH にプルアップされていてもよい。

【0197】

50

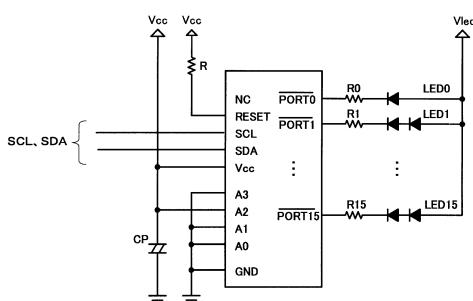

図8Aは、本発明の第1の実施形態の装飾装置620を制御する装飾制御装置610のI<sup>2</sup>C I/Oエクスパンダ615周辺の回路図である。

【0198】

I<sup>2</sup>C I/Oエクスパンダ615は、入力端子としてNC端子、RESET端子、SC-L端子、SDA端子、Vcc端子、A0～A3端子、及びGND端子を備え、出力端子としてPORT0～PORT15を備える。

【0199】

RESET端子には、プルアップ抵抗Rを介してI<sup>2</sup>C I/Oエクスパンダ615に供給される電源が接続されている。このため、リセット端子に印加される電圧は常にHIGHに維持されている。

10

【0200】

SC-L端子は接続線SC-Lに接続され、SDA端子は接続線SDAに接続される。

【0201】

Vcc端子には、I<sup>2</sup>C I/Oエクスパンダ615に供給される電源が接続される。また、Vcc端子には、電源ノイズを除去するコンデンサCPが接続される。

【0202】

A0端子～A3端子は、I<sup>2</sup>C I/Oエクスパンダ615に固有のアドレスを設定するための端子である。なお、通常I<sup>2</sup>C I/Oエクスパンダ615のアドレスは、4ビットで表現され、この端子にI<sup>2</sup>C I/Oエクスパンダ615の電源が印加されている場合にはバスコントローラ634に「1」が設定され、この端子がグランドに接続されている場合にはバスコントローラ634に「0」が設定される。

20

【0203】

したがって、図8Aに示すI<sup>2</sup>C I/Oエクスパンダ615のアドレスは「0100」であり、図8Bに示すI<sup>2</sup>C I/Oエクスパンダ615のアドレスは「0110」である。GND端子は、電圧をグランドするための端子である。

【0204】

各PORT0端子～PORT15端子は、電流制限抵抗R0～R15を介して各LED0～LED15からなる装飾装置620に接続される。なお、PORT0のように、ポート1個に対して1個のLEDを接続してもよいが、PORT1～15のように、ポート1個に対して複数個のLEDを接続してもよい。

30

【0205】

全てのポートにLEDを1個ずつ設ける場合は、1個のI<sup>2</sup>C I/Oエクスパンダ615によって、最大で16個のLEDを制御できることになる。また、各ポートに接続されるLEDの個数が異なる場合は、1個のポートに直列に接続された全てのLEDを1種類のLEDということにすれば、1個のI<sup>2</sup>C I/Oエクスパンダ615によって、最大で16種類のLEDを制御できることになる。

【0206】

PORT0端子～PORT15端子に接続されるトランジスタ638A～638P(図7参照)のゲートに対してドライバ637から電圧が印加されると、電圧が印加されたトランジスタ638A～638Pのドレインからソースへ電流が流れることが可能になり、PORT0端子～PORT15端子に接続されるLED0～LED15に電流が流れ、各LED0～LED15は点灯する。

40

【0207】

一方、ドライバ637がトランジスタ638A～638Pのゲートに電圧を印加しなければ、各LED0～LED15に電流が流れない状態になり、各LED0～LED15は点灯しない。

【0208】

なお、I<sup>2</sup>C I/Oエクスパンダ615のPORT0端子～PORT15端子には、LEDの代わりに、モーターやソレノイドを接続することも可能であるので、I<sup>2</sup>C I/Oエクスパンダ615を用いて、モーターやソレノイドを駆動する場合について説明する。

50

## 【0209】

図8Bは、本発明の第1の実施形態の役物駆動MOT561及び役物駆動SOL560を制御する装飾制御装置610のI<sup>2</sup>C I/Oエクスパンダ615周辺の回路図である。

## 【0210】

役物駆動MOT561はステッピングモータにより構成され、ステッピングモータを駆動する各相の信号端子に、所定の電圧を順次印加することで回動する。本実施形態では、役物駆動MOT561の各相の信号端子が、PORT0端子～PORT3端子に接続される。

## 【0211】

役物駆動MOT561に接続されているPORT0端子～PORT3端子に接続されるトランジスタ638A～638Dのいずれかのゲートに対してドライバ637から電圧が印加されると、電圧が印加されたトランジスタ638A～638Dのドレインからソースへ電流が流れることが可能になり、PORT0端子～PORT3端子に接続される役物駆動MOT561に電流が流れ、役物駆動MOT561が駆動する。

10

## 【0212】

なお、各PORT0端子～PORT3端子と役物駆動MOT561とを接続する接続線は分岐し、分岐した一方の接続線は、役物駆動MOT561に供給される電源にダイオードD及びツェナダイオードZDを介して接続される。

## 【0213】

また、PORT端子15は、役物駆動SOL560に接続される。役物駆動SOL560に接続されているPORT15端子に接続されるトランジスタ638Pのゲートに対してドライバ637から電圧が印加されると、電圧が印加されたトランジスタ638Pのドレインからソースへ電流が流れることが可能になり、PORT15端子に接続される役物駆動SOL560に電流が流れ、役物駆動SOL560が駆動する。

20

## 【0214】

なお、図8Bでは、I<sup>2</sup>C I/Oエクスパンダ615に役物駆動MOT561及び役物駆動SOL560の双方が接続されているが、一つのI<sup>2</sup>C I/Oエクスパンダ615に対して、役物駆動MOT561及び役物駆動SOL560の少なくとも一方だけを接続した構成でもよい。

## 【0215】

30

例えば、ステッピングモーターだけを制御するグループとしてのI<sup>2</sup>C I/Oエクスパンダ615を専用に設けたり、ソレノイドだけを制御するグループとしてのI<sup>2</sup>C I/Oエクスパンダ615を専用に設けるようにしてもよい。このような構成により、同一グループに属する演出装置を同じタイミングで制御することが可能となるので、高速処理が必要な演出装置だけをグループ化して効率よく制御することも可能となる。

## 【0216】

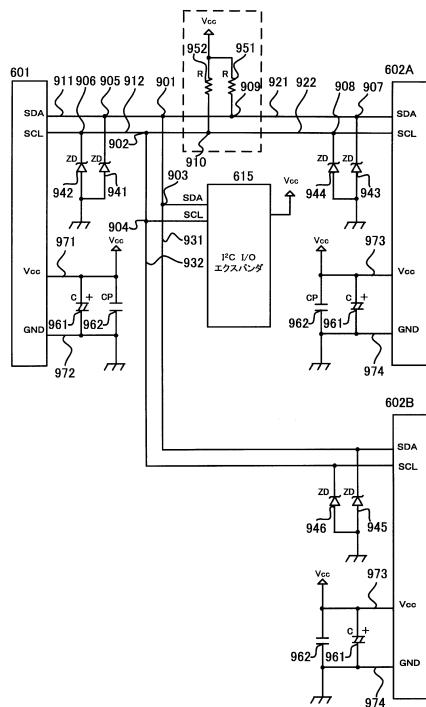

図9は、本発明の第1実施形態の中継基板600の入出力に関する接続線の回路図である。

## 【0217】

中継基板600は、上流コネクタ601、二つの下流コネクタ602A、602B、及びI<sup>2</sup>C I/Oエクスパンダ615を備える。

40

## 【0218】

上流コネクタ601は中継基板600よりも上流のマスタIC570に接続されるコネクタであり、コネクタ602A、602Bは、中継基板600よりも下流の装飾制御装置610に接続される。

## 【0219】

二つの下流コネクタ602A、602Bに接続線SDAを接続するために、上流コネクタ601から延びる内部接続線SDA911は分岐901で第1接続線SDA921と第2接続線SDA931とに分岐する。第1接続線SDA921は下流コネクタ602Aに接続され、第2接続線SDA931は下流コネクタ602Bに接続される。

50

## 【0220】

同じく、上流コネクタ601から延びる内部接続線SCL912は分岐902で第1接続線SCL922と第2接続線SCL932とに分岐する。第1接続線SCL922は下流コネクタ602Aに接続され、第2接続線SCL932は下流コネクタ602Bに接続される。

## 【0221】

接続線SDAをI<sup>2</sup>C I / Oエクスパンダ615に接続するために、第2接続線SDA931は分岐903で分岐し、分岐した第2接続線SDA931はI<sup>2</sup>C I / Oエクスパンダ615の図8A及び図8に示すSDA端子に接続される。また、接続線SCLをI<sup>2</sup>C I / Oエクスパンダ615に接続するために、第2接続線SCL932は分岐904で分岐し、分岐した第2接続線SCL932はI<sup>2</sup>C I / Oエクスパンダ615の図8A及び図8Bに示すSCL端子に接続される。 10

## 【0222】

なお、I<sup>2</sup>C I / Oエクスパンダ615には、I<sup>2</sup>C I / Oエクスパンダ615の電源電圧となる電圧Vccが供給されている。また、図9では図示されていないが、I<sup>2</sup>C I / Oエクスパンダ615からは、中継基板600に設けたLED（装飾装置200）を駆動する各ポート0～15の信号線（図8A参照）が出力されている。

## 【0223】

また、I<sup>2</sup>C I / Oエクスパンダ615は、第2接続線SDA931及び第2接続線SCL932が接続されるとしたが、第1接続線SDA921及び第1接続線SCL922に接続されてもよい。 20

## 【0224】

I<sup>2</sup>C I / Oエクスパンダ615が上流のマスタIC570に接続線SDAを介して出力する信号、及び上流のマスタIC570から中継基板600のI<sup>2</sup>C I / Oエクスパンダ615へ接続線SDAを介して入力される信号のノイズを除去するために、内部接続線SDA911にはツェナダイオードZD941が接続されている。

## 【0225】

具体的には、内部接続線SDA911は分岐905で分岐し、分岐した内部接続線SDA911はツェナダイオードZD941のカソード側に接続され、ツェナダイオードZD941のアノード側は接地されている。 30

## 【0226】

このため、内部接続線SDA911に印加された所定以上の電圧（例えば、パルス性のノイズ信号）は、ツェナダイオードZD941によって逃がされる。

## 【0227】

また、上流のマスタIC570から中継基板600のI<sup>2</sup>C I / Oエクスパンダ615へ接続線SCLを介して入力される信号のノイズを除去するために、内部接続線SCL912にはツェナダイオードZD942が接続されている。

## 【0228】

具体的には、内部接続線SCL912は分岐906で分岐し、分岐した内部接続線SCL912はツェナダイオードZD942のカソード側に接続され、ツェナダイオードZD942のアノード側は接地されている。 40

## 【0229】

このため、内部接続線SCL912に印加された所定以上の電圧（例えば、パルス性のノイズ信号）は、ツェナダイオードZD942によって逃がされる。

## 【0230】

中継基板600のI<sup>2</sup>C I / Oエクスパンダ615が下流コネクタ602Aに接続された装飾制御装置610に接続線SDAを介して出力する信号、及び下流コネクタ602Aに接続された装飾制御装置610から中継基板600のI<sup>2</sup>C I / Oエクスパンダ615へ接続線SDAを介して入力される信号のノイズを除去するために、第1接続線SDA921にはツェナダイオードZD943が接続されている。 50

## 【0231】

具体的には、第1接続線 SDA921は分岐907で分岐し、分岐した第1接続線 SDA921はツエナダイオードZD943のカソード側に接続され、ツエナダイオードZD943のアノード側は接地されている。

## 【0232】

このため、内部接続線 SDA921に印加された所定以上の電圧（例えば、パルス性のノイズ信号）は、ツエナダイオードZD943によって逃がされる。

## 【0233】

また、第1接続線 SDA921に接続されるツエナダイオードZD943と同じく、第2接続線 SDA931にもツエナダイオード945が接続される。

10

## 【0234】

また、中継基板600のI<sup>2</sup>CI/Oエクスパンダ615から下流コネクタ602Aに接続された装飾制御装置610へ接続線SCLを介して入力される信号のノイズを除去するため、第1接続線SCL922にはツエナダイオードZD944が接続されている。

## 【0235】

具体的には、第1接続線SCL922は分岐908で分岐し、分岐した第1接続線SCL922はツエナダイオードZD944のカソード側に接続され、ツエナダイオードZD944のアノード側は接地されている。

## 【0236】

このため、内部接続線SCL922に印加された所定以上の電圧（例えば、パルス性のノイズ信号）は、ツエナダイオードZD944によって逃がされる。

20

## 【0237】

また、第1接続線SCL922に接続されるツエナダイオードZD944と同じく、第2接続線SCL932にもツエナダイオードZD946が接続される。

## 【0238】

また、マスタI<sup>2</sup>C570に接続される上流側の接続線SDA、及び装飾制御装置610に接続される下流側の接続線SDAの電圧をプルアップするためのプルアップ抵抗R951が、第1接続線SDA921に接続される。同じく、マスタI<sup>2</sup>C570に接続される上流側の接続線SCL、及び装飾制御装置610に接続される下流側の接続線SCLの電圧をプルアップするためのプルアップ抵抗R952が、第1接続線SDA922に接続される。

30

## 【0239】

具体的には、第1接続線SDA921は分岐909で分岐し、分岐した第1接続線SDA921はプルアップ抵抗R951に接続される。同じく第1接続線SCL922は分岐910で分岐し、分岐した第1接続線SCL922はプルアップ抵抗R952に接続される。

## 【0240】

なお、接続線SDA及び接続線SCLの電圧をプルアップするプルアップ抵抗951、952は、中継基板600が備えなくてもよく、マスタI<sup>2</sup>C570が備えてもよいし、中継基板600以外の装飾制御装置610が備えてもよい。要するに、接続線SDA及び接続線SCLを駆動するトランジスタのドレインの端子に、電圧Vccを供給できる箇所であれば、どこでもよい。

40

## 【0241】

中継基板600のI<sup>2</sup>CI/Oエクスパンダ615に電源電圧を供給する接続線Vccに接続される上流コネクタ601のVcc端子から延びる内部接続線Vcc971と、上流コネクタ601のGND端子から延び、接地されている内部接続線GND972とは、平滑コンデンサC961及びバイパスコンデンサ962を介して接続されている。

## 【0242】

平滑コンデンサC961は、電源の電圧波形を滑らかにするためのコンデンサであり、バイパスコンデンサC962は、電源の電圧のノイズを除去するためのコンデンサであ

50

る。

【0243】

このため、中継基板600のI<sup>2</sup>C I/Oエクスパンダ615に供給される電源電圧は、平滑コンデンサC961により電圧が平滑化され、バイパスコンデンサ962によりノイズが除去されて、I<sup>2</sup>C I/Oエクスパンダ615に供給される。

【0244】

同じく、下流コネクタ602A、602BのVcc端子から延びる内部接続線Vcc973と、GND端子から延びる内部接続線GND974とは、平滑コンデンサC961及びバイパスコンデンサ962を介して接続されている。これによって、平滑化され、ノイズが除去された電圧が下流の装飾制御装置610に接続される接続線Vccに印加される。

10

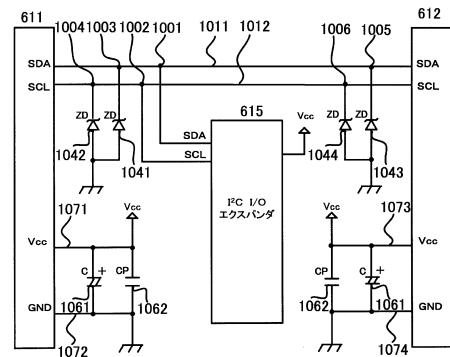

【0245】

図10は、本発明の第1実施形態の装飾制御装置610の入出力に関する接続線の回路図である。

【0246】

装飾制御装置610は、上流コネクタ611、I<sup>2</sup>C I/Oエクスパンダ615、及び下流コネクタ612を備える。

【0247】

上流コネクタ611には、中継基板600又は上流側の装飾制御装置610からバスが接続される。下流コネクタ612には、下流側の装飾制御装置610に接続するバスが接続される。

20

【0248】

上流コネクタ611のSDA端子と下流コネクタ612のSDA端子とは、内部接続線SDA1011によって接続されている。また、上流コネクタ611のSCL端子と下流コネクタ612のSCL端子とは、内部接続線SCL1012によって接続されている。

【0249】

接続線SDAをI<sup>2</sup>C I/Oエクスパンダ615に接続するために、内部接続線SDA1011は分岐1001で分岐し、分岐した内部接続線SDA1011はI<sup>2</sup>C I/Oエクスパンダ615の図8A及び図8に示すSDA端子に接続される。また、接続線SCLをI<sup>2</sup>C I/Oエクスパンダ615に接続するために、内部接続線SCL1012は分岐1002で分岐し、分岐した内部接続線SCL1012はI<sup>2</sup>C I/Oエクスパンダ615の図8A及び図8Bに示すSCL端子に接続される。

30

【0250】

なお、I<sup>2</sup>C I/Oエクスパンダ615には、I<sup>2</sup>C I/Oエクスパンダ615の電源電圧となる電圧Vccが供給されている。また、図10では図示されていないが、I<sup>2</sup>C I/Oエクスパンダ615からは、当該装飾制御装置610に係わるLED(装飾装置200)を駆動する各ポート0~15の信号線(図8A参照)が出力されている。

【0251】

図10に示す装飾制御装置610のI<sup>2</sup>C I/Oエクスパンダ615が上流コネクタ611に接続された上流の装飾制御装置610又は中継基板600に接続線SDAを介して出力する信号、及び上流コネクタ611に接続された上流の装飾制御装置610又は中継基板600から図10に示す装飾制御装置610のI<sup>2</sup>C I/Oエクスパンダ615へ接続線SDAを介して入力される信号のノイズを除去するために、内部接続線SDA1011にはツエナダイオードZD1041が接続されている。

40

【0252】

具体的には、内部接続線SDA1011は分岐1003で分岐し、分岐した内部接続線SDA1011はツエナダイオードZD1041のカソード側に接続され、ツエナダイオードZD1041のアノード側は接地されている。

【0253】

このため、内部接続線SDA1011に印加された所定以上の電圧(例えば、パルス性

50

のノイズ信号)は、ツェナダイオードZD1041によって逃がされる。

【0254】

また、上流コネクタ611に接続される上流の装飾制御装置610又は中継基板600から図10に示す装飾制御装置610のI<sup>2</sup>C I/Oエクスパンダ615へ接続線SCLを介して入力される信号のノイズを除去するために、内部接続線SCL1012にはツェナダイオードZD942が接続されている。

【0255】

具体的には、内部接続線SCL1012は分岐1004で分岐し、分岐した内部接続線SCL1012はツェナダイオードZD1042のカソード側に接続され、ツェナダイオードZD1042のアノード側は接地されている。

10

【0256】

このため、内部接続線SCL1012に印加された所定以上の電圧(例えば、パルス性のノイズ信号)は、ツェナダイオードZD1042によって逃がされる。

【0257】

図10に示す装飾制御装置610のI<sup>2</sup>C I/Oエクスパンダ615が下流コネクタ612に接続された下流の装飾制御装置610に接続線SDAを介して出力する信号、及び下流コネクタ612に接続された下流の装飾制御装置610から図10に示す装飾制御装置のI<sup>2</sup>C I/Oエクスパンダ615へ接続線SDAを介して入力される信号のノイズを除去するために、内部接続線SDA1011にはツェナダイオードZD1043が接続されている。

20

【0258】

具体的には、内部接続線SDA1011は分岐1005で分岐し、分岐した内部接続線SDA1011はツェナダイオードZD1043のカソード側に接続され、ツェナダイオードZD1043のアノード側は接地されている。

【0259】

このため、内部接続線SDA1011に印加された所定以上の電圧(例えば、パルス性のノイズ信号)は、ツェナダイオードZD1043によって逃がされる。

【0260】

また、図10に示す装飾制御装置610のI<sup>2</sup>C I/Oエクスパンダ615から下流コネクタ612に接続された下流の装飾制御装置610へ接続線SCLを介して入力される信号のノイズを除去するために、内部接続線SCL1012にはツェナダイオードZD1044が接続されている。

30

【0261】

具体的には、内部接続線SCL1012は分岐1006で分岐し、分岐した内部接続線SCL1012はツェナダイオードZD1044のカソード側に接続され、ツェナダイオードZD1044のアノード側は接地されている。

【0262】

このため、内部接続線SCL1012に印加された所定以上の電圧(例えば、パルス性のノイズ信号)は、ツェナダイオードZD1044によって逃がされる。

【0263】

装飾制御装置610のI<sup>2</sup>C I/Oエクスパンダ615に電源電圧を供給する接続線Vccに接続される上流コネクタ611のVcc端子から延びる内部接続線Vcc1071と、上流コネクタ611のGND端子から延び、接地されている内部接続線GND1072とは、平滑コンデンサC1061及びバイパスコンデンサ1062を介して接続されている。

40

【0264】

平滑コンデンサC1061は図9に示す平滑コンデンサC961と同じコンデンサであり、バイパスコンデンサC1062は図9に示すバイパスコンデンサ962と同じコンデンサである。

【0265】

50

また、下流コネクタ 612 の Vcc 端子から延びる内部接続線 Vcc1073 と、GND 端子から延びる内部接続線 GND1074 とは、平滑コンデンサ C1061 及びバイパスコンデンサ 1062 を介して接続されている。

【0266】

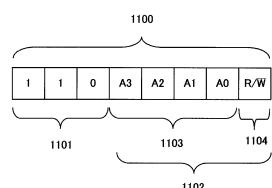

図 11 は、本発明の第 1 の実施形態の演出制御装置 550 から装飾制御装置 610 に出力されるデータに含まれるスレーブアドレス 1100 の説明図である。

【0267】

スレーブアドレス 1100 は、上位 3 ビットからなる固定アドレス部 1101 及び下位 5 ビットからなる可変アドレス部 1102 を含む。

【0268】

固定アドレス部 1101 は、「110」が予め設定されていて、I<sup>2</sup>C/I/O エクスパンダ 615 が変更できないアドレスである。

【0269】

可変アドレス部 1102 は、I<sup>2</sup>C/I/O エクスパンダ 615 に設定可能なアドレスであり、制御対象となる I<sup>2</sup>C/I/O エクスパンダ 615 の A0 ~ A3 の端子に設定されているパターンに対応した 4 ビットの I<sup>2</sup>C/I/O エクスパンダアドレス 1103 と、当該データが読み出し要求であるのか書き込み要求であるのかを示す 1 ビットの R/W 識別データ 1104 と、が含まれる。

【0270】

演出制御装置 550 から装飾制御装置 610 に出力される演出制御データは、書き込み要求であるので、R/W 識別データ 1104 には、通常「0」が登録される。

【0271】

図 12 は、本発明の第 1 の実施形態の I<sup>2</sup>C/I/O エクスパンダアドレステーブル 1200 の説明図である。

【0272】

I<sup>2</sup>C/I/O エクスパンダアドレステーブル 1200 は、マスタ I<sub>C</sub>570 によって管理されるテーブルである。I<sup>2</sup>C/I/O エクスパンダアドレステーブル 1200 は、スレーブアドレス 1201 と I<sup>2</sup>C/I/O エクスパンダアドレス 1202 との対応関係を示している。

【0273】

スレーブアドレス 1201 には、演出制御装置 550 により送受信の対象として指定される装飾制御装置 610 のスレーブアドレスが格納されている。スレーブアドレスは、図 13 で前述したように、上位 3 ビットからなる固定アドレス部と、4 ビットの I<sup>2</sup>C/I/O エクスパンダアドレスと、1 ビットの R/W 識別データとを組み合わせて構成される。

【0274】

I<sup>2</sup>C/I/O エクスパンダアドレス 1202 には、図 8A や図 8B で前述したように、各スレーブアドレスに対応する 4 ビットの I<sup>2</sup>C/I/O エクスパンダアドレスが登録される。

【0275】

ただし、I<sup>2</sup>C/I/O エクスパンダアドレスのうち、アドレス「1000」及びアドレス「1011」は、各 I<sup>2</sup>C/I/O エクスパンダ 615 を相互に識別するための固有のアドレスとしては使用できない。

【0276】

「1000」は、すべての装飾制御装置 610 に対する指令を出力する場合に指定されるアドレス（オールコールアドレス）の電源投入時のデフォルト値として用いられる。「1011」はソフトウェアによって、マスタ I<sub>C</sub>570 に接続されている全ての装飾制御装置 610 を無条件にリセットする場合に用いられる共通アドレスである。

【0277】

このように、装飾制御装置 610 の I<sup>2</sup>C/I/O エクスパンダ 615 に設定可能な固有アドレスは 14 個であるために、演出制御装置 550 は、14 個の I<sup>2</sup>C/I/O エクスパ

10

20

30

40

50

ンダ 615 を制御できる。また、一つの装飾制御装置 610 は、PORT0～PORT15 を備えるので、16 個（言い換えれば 16 種類）の LED を制御できる。よって、演出制御装置 550 は、224 個（言い換えれば 224 種類）の LED を制御できる。

#### 【0278】

図 13 は、本発明の第 1 の実施形態の I<sup>2</sup>C I/O エクスパンダ 615 に備わる出力設定レジスタ 635（図 7 参照）に割り当てられたワークレジスタを説明するための図である。

#### 【0279】

I<sup>2</sup>C I/O エクスパンダ 615 の出力設定レジスタ 635 には、ワークレジスタ（デバイスレジスタ）と、コントロールレジスタ（制御レジスタ）とが割り当てられている。ワークレジスタは、I<sup>2</sup>C I/O エクスパンダ 615 に対して予め定義されている設定を行うための情報や、I<sup>2</sup>C I/O エクスパンダ 615 に接続されている演出装置（例えば、LED）の出力態様を特定するための情報を記憶するものである。また、コントロールレジスタは、ワークレジスタへのデータ書き込み手順を規定する情報を記憶するものである。

#### 【0280】

なお、図 13 に示すように、ワークレジスタは、複数の情報を異なる記憶領域に分散して記憶する構成となっており、各記憶領域毎に異なるレジスタ番号が付与されている。

#### 【0281】

レジスタ番号が「00h」となる記憶領域には、「MODE1」というレジスタ名が付与されており、また、レジスタ番号が「01h」となる記憶領域には、「MODE2」というレジスタ名が付与されている。レジスタ番号「00h」及び「01h」の記憶領域に値が書き込まれると、書き込まれた値に基づいて、I<sup>2</sup>C I/O エクスパンダ 615 の初期設定が行われる。

#### 【0282】

レジスタ番号が「02h」～「11h」となる記憶領域には、「PWM0」～「PWM15」というレジスタ名が付与されている。レジスタ番号「02h」～「11h」の記憶領域のいずれかに値が書き込まれると、I<sup>2</sup>C I/O エクスパンダ 615 に接続される発光装置を構成する 16 個の LED のうち、値が書き込まれたレジスタ番号に対応する LED の輝度が、書き込まれた値に基づいて調整される。例えば、レジスタ番号「02h」の記憶領域に値が書き込まれた場合には、図 8A に示すポート 0 に接続された LED0 の輝度が調整される。

#### 【0283】

なお、I<sup>2</sup>C I/O エクスパンダ 615 に役物駆動 SOL560 が接続される場合には、役物駆動 SOL560 が接続されるポートに対応するレジスタ番号の記憶領域には、役物駆動 SOL560 を通電して作動するか、通電せずに未作動状態にするかを示す値が書き込まれる。

#### 【0284】

また、I<sup>2</sup>C I/O エクスパンダ 615 に役物駆動 MOT561 が接続される場合には、役物駆動 MOT561 が接続されるポートに対応するレジスタ番号の記憶領域には、役物駆動 MOT561 の目標回転位置を示す値が書き込まれる。

#### 【0285】

レジスタ番号が「12h」となる記憶領域には、「GRPPWM」というレジスタ名が付与され、レジスタ番号が「13h」となる記憶領域には、「GRPFREQ」というレジスタ名が付与されている。レジスタ番号「12h」及び「13h」の記憶領域に値が書き込まれると、書き込まれた値に基づいて、全体の LED（16 個の LED）の点滅パターンが設定される。

#### 【0286】

具体的には、レジスタ番号「12h」の記憶領域に値が書き込まれた場合には、全体の LED のオン・オフ比率であるデューティサイクルが設定され、レジスタ番号「13h」

10

20

30

40

50

の記憶領域に値が書き込まれた場合には、全体の LED の点滅周期が設定される。

【 0 2 8 7 】

レジスタ番号が「 1 4 h 」となる記憶領域には、「 LEDOUT0 」というレジスタ名が付与されている。レジスタ番号「 1 4 h 」の記憶領域に値が書き込まれると、書き込まれた値に基づいて、 LED0 ~ LED3 の出力状態が設定される。

【 0 2 8 8 】

レジスタ番号が「 1 5 h 」となる記憶領域には、「 LEDOUT1 」というレジスタ名が付与されている。レジスタ番号「 1 5 h 」の記憶領域に値が書き込まれると、書き込まれた値に基づいて、 LED4 ~ LED7 の出力状態が設定される。

【 0 2 8 9 】

レジスタ番号が「 1 6 h 」となる記憶領域には、「 LEDOUT2 」というレジスタ名が付与されている。レジスタ番号「 1 6 h 」の記憶領域に値が書き込まれると、書き込まれた値に基づいて、 LED8 ~ LED11 の出力状態が設定される。

10

【 0 2 9 0 】

レジスタ番号が「 1 7 h 」となる記憶領域には、「 LEDOUT3 」というレジスタ名が付与されている。レジスタ番号「 1 7 h 」の記憶領域に値が書き込まれると、書き込まれた値に基づいて、 LED12 ~ LED15 の出力状態が設定される。

【 0 2 9 1 】

レジスタ番号が「 1 8 h 」 ~ 「 1 A h 」となる記憶領域には、「 SUBADR1 」 ~ 「 SUBADR3 」というレジスタ名が付与されている。レジスタ番号「 1 8 h 」 ~ 「 1 A h 」の記憶領域に値が書き込まれると、書き込まれた値に基づいて、第 1 サブアドレス ~ 第 3 サブアドレスが設定される。

20

【 0 2 9 2 】

レジスタ番号が「 1 B h 」となる記憶領域には、「 ALLCALLADR 」というレジスタ名が付与されている。レジスタ番号「 1 B h 」の記憶領域に値が書き込まれると、書き込まれた値に基づいて、オールコールアドレスが設定される。

【 0 2 9 3 】

図 14 は、本発明の第 1 の実施形態のマスタ I C 570 が接続線 SDA 及び接続線 SCL を介して出力するデータのスタート条件及びストップ条件の説明図である。

【 0 2 9 4 】

30

接続線 SCL は、データの非送信時に信号レベルが HIGH になっており、マスタ I C 570 は、装飾制御装置 610 にデータを出力する際に、接続線 SCL の信号レベルを LOW から HIGH に変化させ、装飾制御装置 610 が接続線 SDA のデータを取り込むためのストローブ信号として作用させる。

【 0 2 9 5 】

接続線 SDA は、データの非送信時に信号レベルが HIGH になっており、接続線 SCL のクロック信号に合わせて接続線 SDA からデータが出力される。

【 0 2 9 6 】

マスタ I C 570 は、接続線 SCL の信号レベルを HIGH に維持したまま、接続線 SDA の信号レベルを HIGH から LOW に変化させることで、データの出力が開始することを示すスタート条件となる信号を出力する。

40

【 0 2 9 7 】

装飾制御装置 610 の I<sup>2</sup>C I / O エクスパンダ 615 は、接続線 SDA 及び接続線 SCL からスタート条件となる信号が入力されると、データの出力が開始することを把握する。

【 0 2 9 8 】

マスタ I C 570 は、接続線 SCL の信号レベルを HIGH に維持したまま、接続線 SDA の信号レベルを LOW から HIGH に変化させることで、データの出力が終了することを示すストップ条件を示す信号を出力する。

【 0 2 9 9 】

50

装飾制御装置 610 の I<sup>2</sup>C I / O エクスパンダ 615 は、ストップ条件が入力されると、データの出力が終了することを把握する。

【0300】

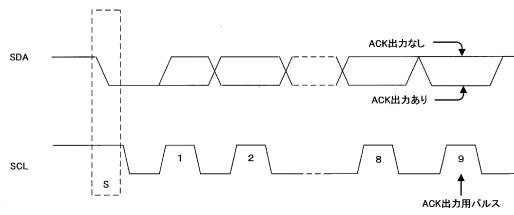

図 15 は、本発明の第 1 の実施形態のマスタ I C 570 から出力されたデータが入力された装飾制御装置 610 が返答信号を出力するタイミングチャートである。

【0301】

装飾制御装置 610 は、スタート条件が成立してから接続線 SCL の信号レベルの変化回数を計数し、接続線 SCL のクロック信号に合わせて接続線 SDA から入力されるデータを取り込む。

【0302】

そして、装飾制御装置 610 は、スタート条件が成立してから接続線 SCL の信号レベルの変化回数が 9 回に達する直前に、返答信号をマスタ I C 570 に接続線 SDA を介して出力する。換言すると、装飾制御装置 610 は、接続線 SDA から 8 ビット目のデータを取り込んだ後に、接続線 SCL の信号レベルが HIGH から LOW に変化することを契機に、返答信号を当該接続線 SDA を介して出力する。

【0303】

なお、図に示すように、データの受信に成功したことを示す返答信号 (ACK の返答信号) は LOW レベルによって示され、データの受信に失敗したことを示す返答信号 (NACK の返答信号、図では ACK 出力なしに相当) は HIGH レベルによって示される。

【0304】

また、マスタ I C 570 は、スタート条件が成立してから接続線 SCL の信号レベルが 8 回変化すると、接続線 SDA を解放することによって、装飾制御装置 610 から返答信号の入力を待機する。そして、マスタ I C 570 は、接続線 SDA を解放したまま、接続線 SCL の信号レベルを変化させて、装飾制御装置 610 からの返答信号を取り込む。

【0305】

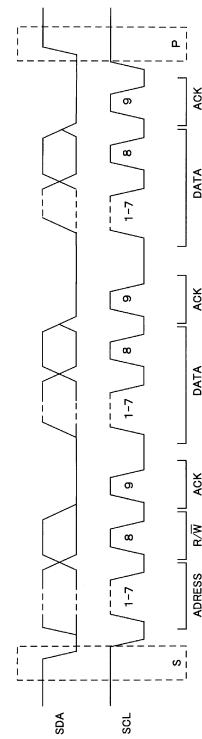

図 16 は、本発明の第 1 の実施形態のマスタ I C 570 が演出制御データを出力する場合の接続線 SDA 及び接続線 SCL の信号レベルのタイミングチャートである。

【0306】

まず、マスタ I C 570 は、データの出力を開始する場合には、接続線 SCL の信号レベルを HIGH に維持したまま、接続線 SDA の信号レベルを HIGH から LOW に変化させることによって、スタート条件を示す信号を出力し、これからデータを出力することを装飾制御装置 610 に通知する。

【0307】

次に、マスタ I C 570 は、合計 7 ビットからなる制御対象となる装飾制御装置 610 のスレーブアドレスを出力する。次に、マスタ I C 570 は、読み出し要求である書き込み要求であるかを示すデータを 8 ビット目に出力する。

【0308】

そして、マスタ I C 570 は、接続線 SCL の信号レベルが 9 回目に HIGH になると、装飾制御装置 610 から返答信号が入力されるので、ACK の返答信号であれば接続線 SDA の信号レベルが LOW に変化し、NACK の返答信号であれば接続線 SDA の信号レベルが HIGH に変化する。

【0309】

次に、マスタ I C 570 は、アドレスデータの出力後、データを、8 の倍数となるビット数で出力する。マスタ I C 570 は、データの 8 ビット目を出力した後、ACK の返答信号が入力されるのを待ってデータの 9 ビット目を出力する。以降、8 の倍数番目に相当するビットのデータを出力すると、ACK の返答信号が入力されるのを確認してから、(8 の倍数 + 1) 番目のビットを出力し、全データが出力されるまで繰り返す。

【0310】

なお、マスタ I C 570 は、データの 8 の倍数番目となるビットを出力した後、所定時間経過しても ACK の返答信号が入力されない場合には、データの送信に失敗したものと

10

20

30

40

50

みなして、再度スタート条件を送信する。次いで、接続線 S D A を介して、再度アドレスデータを出力し、ACK の返答信号を確認しながら、もう一度、データを 1 ビット目から出力する。

【 0 3 1 1 】

また、マスタ I C 5 7 0 は、データの最後のビットのデータを出力した後、ACK の返答信号が入力されるのを待って、ストップ条件を示す信号を出力する。

【 0 3 1 2 】

なお、図 1 6 では、スタート条件を示す信号を出力してからストップ条件を示す信号を出力するまでの間に、合計 24 ビット（スレーブアドレス 8 ビット、データ 16 ビット）のデータを出力しているが、24 ビット以上であってもよいし、24 ビット以下であってもよい。

10

【 0 3 1 3 】

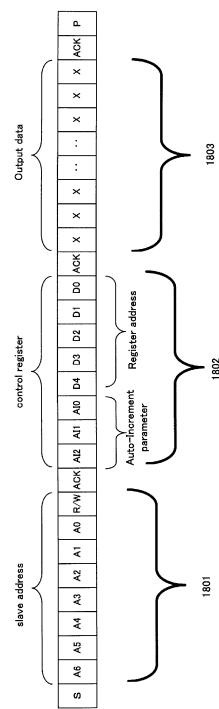

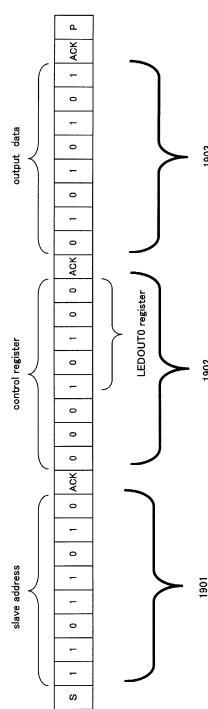

図 1 7 は、本発明の第 1 の実施形態のマスタ I C 5 7 0 が、スレーブの個別アドレスを指定して装飾制御装置 6 1 0 に演出制御データを設定する場合において、マスタ I C 5 7 0 と I<sup>2</sup> C I / O エクスパンダ 6 1 5 との間で授受されるデータのフォーマットを説明する図である。

【 0 3 1 4 】

はじめに出力される 8 ビットのデータ 1 8 0 1 には、データ送信の対象となる装飾制御装置 6 1 0 のアドレス「A 0 ~ A 6」と、当該データが読み出し要求であるのか書き込み要求であるのかを示す 1 ビットの R / W 識別データとが含まれる。このアドレス「A 0 ~ A 6」のうち、「A 4 ~ A 6」は値「1 1 0」となる固定アドレス部であり、「A 0 ~ A 3」は I<sup>2</sup> C I / O エクスパンダ 6 1 5 の A 0 ~ A 3 の端子に設定されているアドレスに相当する（図 8 参照）。なお、このデータ 1 8 0 1 は、図 1 6 における「A D R E S S」及び「R / W」に対応するものである。

20

【 0 3 1 5 】

次に、出力される 8 ビットのデータ 1 8 0 2 には、I<sup>2</sup> C I / O エクスパンダ 6 1 5 の出力設定レジスタ 6 3 5（図 7 参照）に割り当てられているコントロールレジスタへの設定データが含まれる。このデータ 1 8 0 2 は、図 1 6 において 1 番目に送信される「D A T A」に対応するものである。

【 0 3 1 6 】

30

ここで、コントロールレジスタについて説明する。コントロールレジスタは 8 ビットからなり、上位 3 ビット「A I 0 ~ A I 2」が出力設定レジスタ 6 3 5 のワークレジスタへの書き込み又は読み出し方法を指定する自動書き込みパラメータであり、下位 5 ビット「D 0 ~ D 4」がワークレジスタにおけるアクセス開始位置（書き込みを開始する先頭位置、又は読み出しを開始する先頭位置）を指定するレジスタアドレスである。

【 0 3 1 7 】

自動書き込みパラメータは、マスタ I C 5 7 0 によって、レジスタアドレスが指定するアクセス開始位置の領域のみをアクセス（オートインクリメントを禁止）するのか、指定するアクセス開始位置の領域に隣接する領域も含んでアクセス（オートインクリメントを許可）するのかを指定するパラメータであり、具体的には「0 0 0」、「1 0 0」、「1 0 1」、「1 1 0」、「1 1 1」の何れかの値を設定することができる。

40

【 0 3 1 8 】

自動書き込みパラメータに「0 0 0」の値を設定すると、オートインクリメントが禁止され、レジスタアドレスが指定するアクセス開始位置の領域のみにアクセスし、開始位置以外の領域にはアクセスしない。例えば、レジスタアドレスが「1 0 1 0 0」であれば、レジスタ番号が「1 4 h」となる記憶領域のみにアクセスし、他の記憶領域にはアクセスしない。

【 0 3 1 9 】

自動書き込みパラメータに「1 0 0」の値を設定すると、オートインクリメントが許可され、レジスタアドレスが指定するアクセス開始位置の領域にアクセスした後は、レジスタ番

50

号が増加する方向に領域を移動しながら順にアクセスを繰り返す。そして、レジスタ番号が最終の「1Bh」となる記憶領域にアクセスした後は、レジスタ番号が「00h」となる記憶領域にアクセスし、再度、レジスタ番号が増加する方向に領域を移動しながら順にアクセスを繰り返す。例えば、レジスタアドレスが「10100」であれば、レジスタ番号が「14h」となる記憶領域にアクセスした後は、レジスタ番号が「15h」「16h」…「1Bh」「00h」「01h」…となる領域（即ち、全ての領域）に、繰り返しアクセスする。

#### 【0320】

自動書込パラメータに「101」の値を設定すると、自動書込パラメータに「100」の値を設定した場合と同様に、レジスタアドレスが指定するアクセス開始位置の領域にアクセスした後は、レジスタ番号が増加する方向に領域を移動しながら順にアクセスを繰り返す。但し、一旦、レジスタ番号が「11h」となる記憶領域にアクセスした後は、レジスタ番号が「02h」となる記憶領域にアクセスし、以降、レジスタ番号が「02h」～「11h」となる区間の記録領域（LEDの輝度調整に関する領域）に繰り返しアクセスする。例えば、レジスタアドレスが「10100」であれば、レジスタ番号が「14h」となる記憶領域にアクセスした後は、レジスタ番号が「15h」「16h」…「1Bh」「00h」「01h」…となる領域に、順にアクセスする。そして、レジスタ番号が「11h」となる記憶領域にアクセスした後は、レジスタ番号が「02h」「03h」…「11h」「02h」「03h」…となる領域に、繰り返しアクセスする。

10

#### 【0321】

自動書込パラメータに「110」の値を設定すると、自動書込パラメータに「100」の値を設定した場合と同様に、レジスタアドレスが指定するアクセス開始位置の領域にアクセスした後は、レジスタ番号が増加する方向に領域を移動しながら順にアクセスを繰り返す。但し、一旦、レジスタ番号が「13h」となる記憶領域にアクセスした後は、レジスタ番号が「12h」となる記憶領域にアクセスし、以降、レジスタ番号が「12h」～「13h」となる区間の記録領域（LEDの点滅周期に関する領域）を繰り返しアクセスする。例えば、レジスタアドレスが「10100」であれば、レジスタ番号が「14h」となる記憶領域にアクセスした後は、レジスタ番号が「15h」「16h」…「1Bh」「00h」「01h」…となる領域に、順にアクセスする。そして、レジスタ番号が「13h」となる記憶領域にアクセスした後は、レジスタ番号が「12h」「13h」「12h」「13h」…となる領域に、繰り返しアクセスする。

20

#### 【0322】

自動書込パラメータに「111」の値を設定すると、自動書込パラメータに「100」の値を設定した場合と同様に、レジスタアドレスが指定するアクセス開始位置の領域にアクセスした後は、レジスタ番号が増加する方向に領域を移動しながら順にアクセスを繰り返す。但し、一旦、レジスタ番号が「13h」となる記憶領域にアクセスした後は、レジスタ番号が「02h」となる記憶領域にアクセスし、以降、レジスタ番号が「02h」～「13h」となる区間の記録領域（LEDの輝度及び点滅周期に関する領域）に繰り返しアクセスする。例えば、レジスタアドレスが「10100」であれば、レジスタ番号が「14h」となる記憶領域にアクセスした後は、レジスタ番号が「15h」「16h」…「1Bh」「00h」「01h」…となる領域に、順にアクセスする。そして、レジスタ番号が「13h」となる記憶領域にアクセスした後は、レジスタ番号が「02h」「03h」…「13h」「02h」「03h」…となる領域に、繰り返しアクセスする。

30

#### 【0323】

図17に戻り、コントロールレジスタへの設定データ1802に続いて、ワークレジスタへの設定データ1803が出力される。この設定データ1803は、図16において2番目以降に送信される「DATA」に対応するものである。

40

#### 【0324】

50

自動書込パラメータを「000」とした場合には、この設定データ1803は、レジスタアドレスが指定する1箇所の記憶領域を更新するために必要な8ビットのデータとなる。自動書込パラメータを「000」以外の値とした場合には、この設定データ1803は、レジスタアドレスが指定する記憶領域を先頭に、複数の領域を繰り返し更新するために必要な8の倍数となるビットのデータとなる。

【0325】

図18は、本発明の第1の実施形態のマスタIC570が、スレーブの個別アドレスを指定して装飾制御装置610に演出制御データを設定する場合において、マスタIC570とI<sup>2</sup>CI/Oエクスパンダ615との間で授受される演出制御データに具体的な数値を適用したものである。本図では、オートインクリメントを禁止して、ワークレジスタの1箇所の記憶領域だけを更新する演出制御データを例示しており、I<sup>2</sup>CI/Oエクスパンダ615のPORT0端子～PORT3端子に接続されるLEDの発光状態を更新する場合を想定している。

【0326】

まず、はじめに出力される8ビットのデータ1901には、送信先の装飾制御装置610のI<sup>2</sup>CI/Oエクスパンダ615のスレーブアドレスを示す「1101100」が割り当てられている。

【0327】

次に出力される8ビットのデータ1902には、自動書込パラメータ、及びLEDの出力データを設定するために割り当てられているI<sup>2</sup>CI/Oエクスパンダ615の出力設定レジスタ635のコントロールレジスタに設定される値が含まれる。

【0328】

ここでは、I<sup>2</sup>CI/Oエクスパンダ615のPORT0端子～PORT3端子に接続されるLEDの発光状態を設定するので、レジスタアドレスにはLEDOUT0（アドレス=10100）を指定することにする。

【0329】

なお、自動書込パラメータには、オートインクリメントを禁止するために「000」が指定されている。

【0330】

次に、出力される8ビットのデータ1903には、送信先の装飾制御装置610によって制御される装飾装置620の発光様式を設定するデータが含まれる。具体的には、LEDOUT0レジスタに設定されるデータが割り当てられている。これにより、I<sup>2</sup>CI/Oエクスパンダ615のPORT0端子～PORT3端子に接続されるLEDの発光状態（点灯、消灯、点滅など）が指定され、指定された状態でLEDが発光する。

【0331】

このようにして、I<sup>2</sup>CI/Oエクスパンダ615のPORT0端子～PORT3端子のLEDの発光状態が制御されるが、I<sup>2</sup>CI/Oエクスパンダ615の他のPORT端子（PORT4～PORT15）も、コントロールレジスタに書き込むデータ1902の値を指定して、出力データ1903を設定することで制御可能である。PORT端子に、モーター ソレノイドが接続されていても、同様に制御される。

【0332】

図19は、本発明の第1の実施形態の演出制御データの別の形態を説明する図である。本図では、オートインクリメントを許可して、ワークレジスタの全ての記憶領域を更新する場合を想定しており、演出制御データに含まれる各データの送信順序を規定している。

【0333】

まず、マスタIC570は、制御対象となる装飾制御装置610の個別アドレスを特定可能な8ビットのデータ（図18のデータ1901と同一フォーマットのデータ）を送信する。

【0334】

次に、マスタIC570は、制御対象のI<sup>2</sup>CI/Oエクスパンダ615の出力設定レ

10

20

30

40

50

ジスタ 635 のコントロールレジスタに設定されるデータ（図 18 のデータ 1902 と同一フォーマットのデータ）を送信する。本図においては、オートインクリメントを許可してワークレジスタの全ての記憶領域を更新するため、自動書込パラメータには「100」が指定され、書き込み先又は読み出しの開始位置を指定するレジスタアドレスには、ワークレジスタの先頭領域となる「00h」が指定される。

【0335】

このため、コントロールレジスタ設定値を受信した後の制御対象となる装飾制御装置 610 の I<sup>2</sup>C I / O エクスパンダ 615 においては、レジスタ番号が「00h」の記憶領域（MODE 1 レジスタ）が最初に更新されることになる。

【0336】

次いで、マスタ I C 570 は、コントロールレジスタ設定値の送信後、MODE 1 レジスタに書き込む値（合計 8 ビット）を送信する。I<sup>2</sup>C I / O エクスパンダ 615 は、当該書き込み値を受信すると MODE 1 レジスタの値を更新し、レジスタ番号をインクリメントして次の「01h」の記憶領域（MODE 2 レジスタ）を更新するための準備をする。

【0337】

次いで、マスタ I C 570 は、MODE 2 レジスタに書き込む値（合計 8 ビット）を送信し、以降、レジスタ番号が「02h」～「1Bh」となる残りの記憶領域のレジスタに対して、順に設定値を送信する。I<sup>2</sup>C I / O エクスパンダ 615 は、当該書き込み値を受信する毎に対応するレジスタの値を更新し、レジスタ番号をインクリメントして次の記憶領域を更新するための準備を繰り返すことで、ワークレジスタに割り当てられた「00h」～「1Bh」の全てのレジスタの値が更新される。

【0338】

なお、I<sup>2</sup>C I / O エクスパンダ 615 は、ワークレジスタの最終となる「1Bh」の記憶領域を更新すると、レジスタ番号は「00h」に変更して、MODE 1 レジスタの更新を待つ状態となる。

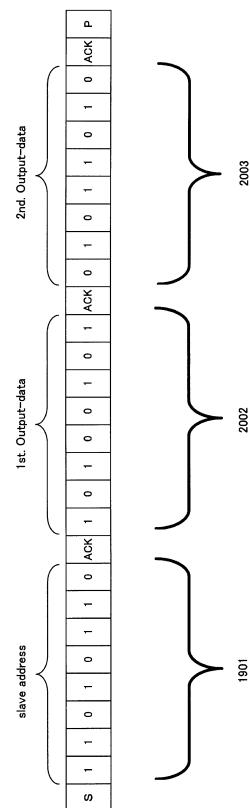

【0339】

図 20 は、本発明の第 1 の実施形態のマスタ I C 570 が I<sup>2</sup>C I / O エクスパンダ 615 を初期化するときに、マスタ I C 570 から I<sup>2</sup>C I / O エクスパンダ 615 へ送信される初期化指示データのデータフォーマットを説明する図である。

【0340】

演出制御装置 550 の C P U 551 がマスタ I C 570 に対して装飾制御装置 610 の初期化を行うように指示すると、マスタ I C 570 は、配下に接続している全ての装飾制御装置 610 に初期化指示データを送信する。

【0341】

はじめに出力される 8 ビットのデータ 2001 には、図 18 に示す固定アドレス「110」と、共通アドレスであるリセットアドレス「1011」（図 12 参照）とが含まれる。なお、このデータ 2001 は、図 16 における「A D R E S S」に対応するものであり、「R / W」のビットには、書き込みを示す「0」が設定される。

【0342】

次に出力される 8 ビットのデータ 2002 では、第 1 所定値「10100101」が出力さて、次に出力される 8 ビットのデータ 2003 では、第 2 所定値「01011010」が出力される。なお、このデータ 2002 は、図 16 において 1 番目に送信される「D A T A」に対応し、データ 2003 は、図 16 において 2 番目に送信される「D A T A」に対応する。

【0343】

マスタ I C 570 に接続されるすべての I<sup>2</sup>C I / O エクスパンダ 615 は、リセットアドレス、第 1 所定値、及び第 2 所定値から構成される初期化指示データを受信すると、自身の初期化を行う。

【0344】

10

20

30

40

50

リセットアドレスの出力後に、第1所定値及び第2所定値を出力するようにしたのは、マスタI C 5 7 0 がリセットアドレス「1 0 1 1」を送信していないにもかかわらず、ノイズなどの影響で、I<sup>2</sup>C I / Oエクスパンダ6 1 5 が誤ってリセットアドレス「1 0 1 1」を取り込んでしまい、誤ったタイミングで初期化が行われることを防止するためである。

【0 3 4 5】

また、リセットアドレスは、個別アドレスとは異なって、全て（換言すれば複数）のI<sup>2</sup>C I / Oエクスパンダ6 1 5 に共通なアドレスである。そのため、リセットアドレスを含んだ初期化指示データを1回送信するだけで、全て（複数）のI<sup>2</sup>C I / Oエクスパンダ6 1 5 を選択して初期化することになるので、I<sup>2</sup>C I / Oエクスパンダ6 1 5 を個別に選択して初期化を指示する方法と比較すると、高速に初期化を指示することが可能となる。

【0 3 4 6】

なお、図2 0 では、第1所定値と第2所定値とを異なる値としたが、同じ値であってもよい。また、第1所定値及び第2所定値のいずれかが1回送信されるようにしてもよい。

【0 3 4 7】

図2 1 は、本発明の第1の実施形態の異常判定テーブル2 1 0 0 を説明する図である。

【0 3 4 8】

異常判定テーブル2 1 0 0 は、演出制御装置5 5 0 のR A M 5 5 3 に格納される。異常判定テーブル2 1 0 0 は、演出制御装置5 5 0 のマスタI C 5 7 0 と当該マスタI C 5 7 0 に接続されるI<sup>2</sup>C I / Oエクスパンダ6 1 5 との接続状態を監視するものであり、接続状態の確認結果に対応して、該当するI<sup>2</sup>C I / Oエクスパンダ6 1 5 に対応した後述のエラーフラグ2 1 0 5 が設定される。

【0 3 4 9】

異常判定テーブル2 1 0 0 は、I / Oエクスパンダアドレス2 1 0 1 、スレーブアドレス2 1 0 2 、エラーカウンタ2 1 0 3 、比較値2 1 0 4 、及びエラーフラグ2 1 0 5 を含む。

【0 3 5 0】

I / Oエクスパンダアドレス2 1 0 1 は、マスタI C 5 7 0 に接続されるI<sup>2</sup>C I / Oエクスパンダ6 1 5 のA 0 ~ A 3 の端子に設定されているアドレス（図8 参照）に対応している。

【0 3 5 1】

スレーブアドレス2 1 0 2 には、図1 2 に示すI<sup>2</sup>C I / Oエクスパンダアドレステーブル1 2 0 0 に登録されているスレーブアドレスが登録される。

【0 3 5 2】

エラーカウンタ2 1 0 3 は、マスタI C 5 7 0 からI<sup>2</sup>C I / Oエクスパンダ6 1 5 への演出制御データの送信に対して、I<sup>2</sup>C I / Oエクスパンダ6 1 5 からのA C K が受信できたか否かを監視した際に、このA C K の受信に2回連続して失敗するとインクリメントされるものである。

【0 3 5 3】

比較値2 1 0 4 には所定値が登録される。エラーフラグ2 1 0 5 には、当該エントリのI<sup>2</sup>C I / Oエクスパンダ6 1 5 との接続状態に異常が発生したか否かを示すエラーフラグが登録される。

【0 3 5 4】

具体的には、インクリメントされたエラーカウンタ2 1 0 3 の値が、比較値2 1 0 4 に登録された所定値に達した場合に、エラーフラグ2 1 0 5 にONが設定されて当該エントリのI<sup>2</sup>C I / Oエクスパンダ6 1 5 に異常が発生したことが登録される。

【0 3 5 5】

なお、I / Oエクスパンダアドレス2 1 0 1 に登録された「0 1 1 0」のI<sup>2</sup>C I / Oエクスパンダ6 1 5 は、図8 B に示すように、役物駆動S O L 5 6 0 や役物駆動M O T 5

10

20

30

40

50

61といった可動装置を制御している。そこで、このI<sup>2</sup>C I/Oエクスパンダ615を備える装飾制御装置610を、可動制御装置（可動グループ単位制御手段）ということにする。

【0356】

一方、I/Oエクスパンダアドレス2101に登録された「0110」以外のI<sup>2</sup>C I/Oエクスパンダ615は、図8Aに示すように、LED等の発光装置を制御している。そのため、このI<sup>2</sup>C I/Oエクスパンダ615を備える装飾制御装置610を、前述の可動制御装置と区別するために、発光制御装置（発光グループ単位制御手段）ということにする。

【0357】

図21では、可動制御装置（I/Oエクスパンダアドレス2101に登録された値が「0110」）のエントリが存在せず、発光制御装置のエントリのみが登録されている。

【0358】

可動制御装置に異常が発生している場合には、役物駆動MOT561が回転しすぎて、可動役物60が動作可能な範囲を超えて可動してしまい、可動役物60及び可動役物付近の部材を破損してしまうことを防止するため、発光制御装置よりも短時間で異常判定する必要がある。そのため、可動制御装置の接続監視タイミングと発光制御装置の接続監視タイミングとが異なるので、換言すると、可動制御装置の接続監視の構成と発光制御装置の接続監視の構成とが異なるので、異常判定テーブル2100から可動制御装置のエントリが除外されているのである。

【0359】

具体的には、本実施形態では、後述するように、発光制御装置のデータ出力処理（図22参照）は、VDP割込（約33.3ms周期）に同期して実行されるようし、可動制御装置のデータ出力処理をタイマ割込（2ms周期）に同期して実行されるようにしている。

【0360】

前述したように、マスタI<sup>2</sup>C570から、発光制御装置に備えられるI<sup>2</sup>C I/Oエクスパンダ615への2回目の演出制御データの送信に対して、当該I<sup>2</sup>C I/Oエクスパンダ615からのACKが受信できなければ、エラーカウンタ2103がインクリメントされる。

【0361】

したがって、発光制御装置に異常が発生している場合には、データ出力処理の実行周期が33msで、比較値2104が「300」であるので、33.3ms × 300 = 10sで発光制御装置に異常が発生したことを検出する。

【0362】

なお、可動制御装置に異常が発生している場合には、データ出力処理の実行周期が2msであり、後述するように、次の実行周期を待つことなく、異常が発生したことを検出するので、極めて短時間（2ms程度の時間）で可動制御装置に異常が発生したことを検出できる。

【0363】

このため、可動制御装置のエラー判定が発光制御装置のエラー判定よりも頻繁に行われ、可動制御装置に異常が発生したことを発光制御装置に異常が発生したことよりも早く検出することができるので、可動役物60が動作可能な範囲を超えて可動してしまい、可動役物60及び可動役物付近の部材を破損してしまうことを防止できる。

【0364】

これに対して、LED等の発光装置は、誤動作によって破損する恐れが少ないため、発光制御装置に関する異常判定に時間を要しても問題が生じることはない。

【0365】

従って、異常判定を短時間で行う必要がある装飾制御装置610に限定して判定の周期を短縮し、他の装飾制御装置610の異常判定を余裕のある周期で行うので、処理負担の

10

20

30

40

50

バランスを考慮した異常判定処理を実行することが可能となる。

【0366】

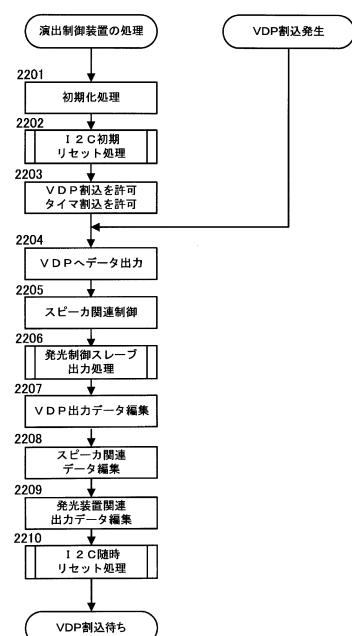

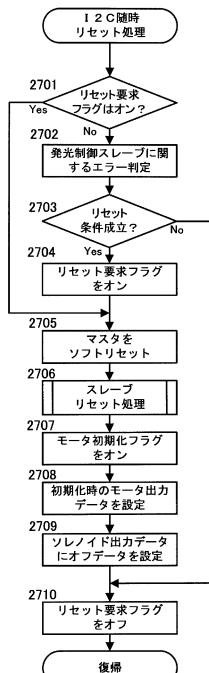

図22は、本発明の第1実施形態の演出制御装置550による処理のフローチャートである。

【0367】

図22に示す演出制御装置550の処理は、演出制御装置550のCPU551によって実行される。

【0368】

演出制御装置550は、演出制御装置550に電源が投入されると、まずステップ2201～2210の処理を実行した後、VDP556から画像更新周期と同期する同期信号(例えば、33ms秒周期の同期信号)がCPU551に入力されるまで待機する。そして、以降は、VDP556から画像更新周期と同期する同期信号がCPU551に入力される毎に、ステップ2204～2210の処理を繰り返し実行する。

10

【0369】

まず、演出制御装置550は、演出制御装置550のRAM553を初期化する(2201)。このとき、当該演出制御装置550への電源投入時を基点として、CPU551からVDP556や音LSI557に出力される、初回の制御データも生成される。

【0370】

次に、演出制御装置550は、マスタIC570、及びマスタIC570に接続された装飾制御装置610、を初期化するI<sup>2</sup>C初期リセット処理を実行する(2202)。

20 I<sup>2</sup>C初期リセット処理は、図23で詳細を説明する。このI<sup>2</sup>C初期リセット処理が実行されると、役物駆動MOT561、及び役物駆動SOL560の初期化動作も開始される。

【0371】

そして、演出制御装置550は、VDP556から画像更新周期と同期する同期信号(VDP割込)、及びタイマ割込の受け入れを許可する(2203)。

【0372】

そして、演出制御装置550は、表示装置53に画像を表示するために、VDP556に画像を表示させる指令となるデータを出力し(2204)、スピーカ30から音を遊技状態に応じて出力させるために、音制御データを音LSI557に出力し、音LSI557に音制御データに基づいてスピーカ30から音を出力させる(2205)。

30

【0373】

次に、演出制御装置550は、発光制御装置に演出制御データをマスタIC570から出力する発光制御スレーブ出力処理を実行する(2206)。発光制御スレーブ出力処理は、図25で詳細を説明する。

【0374】

そして、演出制御装置550は、VDP556に次に出力されるデータを編集し(2207)、音LSI557に次に出力される音制御データを編集し(2208)、各グループの発光制御装置に次に出力される演出制御データを編集する(2209)。

【0375】

次に、演出制御装置550は、異常判定テーブル2100を参照して、すべての発光制御装置のエラーフラグ2105がONになっている場合にリセット条件が成立したとみなし、マスタIC570、役物駆動MOT561、マスタIC570に接続されたすべてのI<sup>2</sup>C I/Oエクスパンダ615、及び役物駆動SOL560の初期化を指示するI<sup>2</sup>C随時リセット処理を実行し(2210)、その後、VDP556から同期信号がCPU551に入力されるまで待機する。

40 I<sup>2</sup>C随時リセット処理は、図27で詳細を説明する。

【0376】

図22による処理では、表示装置53の画像を更新する周期と同期して、演出制御装置550のマスタIC570から装飾制御装置610のI<sup>2</sup>C I/Oエクスパンダ615へ演出制御データを送信し、I<sup>2</sup>C I/Oエクスパンダ615は受信した演出制御データに基づいて装飾装置620を制御するので、表示装置53における演出と装飾装置620に

50

おける演出とが調和し、遊技者に違和感を与えるので、興趣を高めることができる。

【0377】

また、表示装置53の画像を更新する周期と同期してマスタIC570から送信された演出制御データが装飾制御装置610で受信されると、その都度、I<sup>2</sup>CI/Oエクスパンダ615によってワークレジスタの値が更新される。そのため、毎回ワークレジスタの値が最新の状態に更新されるので、ノイズ等でワークレジスタの値が破壊されても、正常な値に復帰することが可能である。

【0378】

また、表示装置53の画像を更新する周期と同期して、ステップ2211の処理で実行されるエラー判定処理を実行するので、エラー判定の実行頻度を適切にできる、つまり、エラー判定処理の実行頻度が多すぎると、演出制御装置550のCPU551の処理負荷が増大してしまい、逆に、エラー判定処理の実行頻度が少なすぎると、異常が発生したことを適切に検出できなくなってしまうことになるので、適度な頻度でエラー判定を行うことにより処理の不具合を防止することができる。

10

【0379】

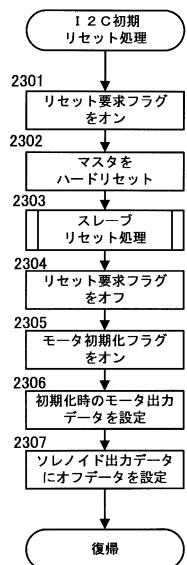

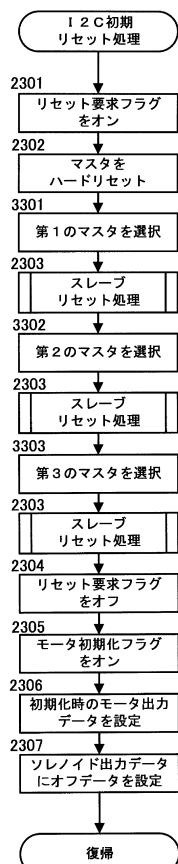

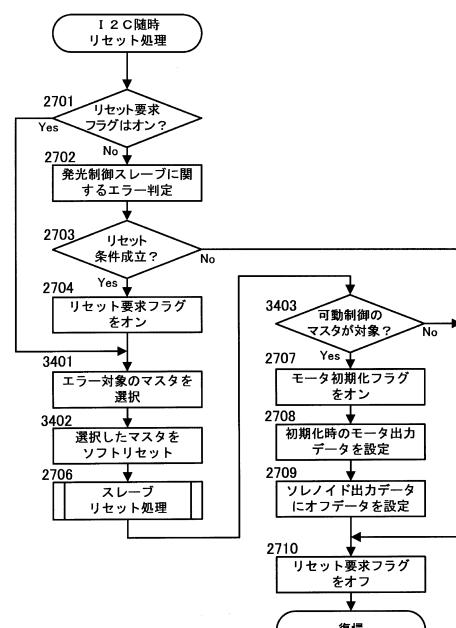

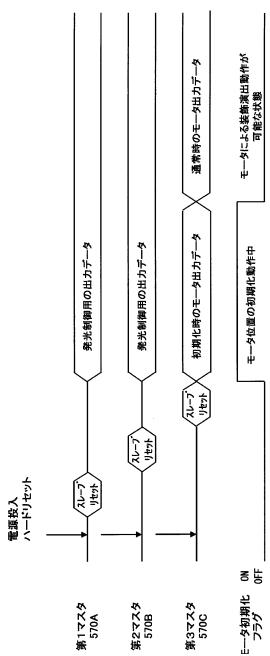

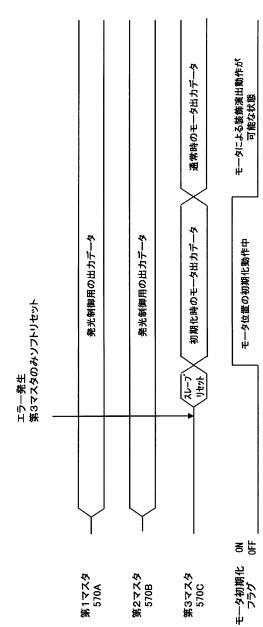

図23は、本発明の第1実施形態のI<sup>2</sup>C初期リセット処理のフローチャートである。

【0380】

I<sup>2</sup>C初期リセット処理は、演出制御装置550への電源投入の直後に、マスタIC570、マスタIC570に接続されたすべてのI<sup>2</sup>CI/Oエクスパンダ615の初期化を指示する処理であり、図22に示すステップ2202の処理で実行される。なお、当該処理中にて、役物駆動MOT561、及び役物駆動SOL560の初期化動作の開始が指示される

20

まず、演出制御装置550のCPU551は、初期化中であることを示すリセット要求フラグを設定し(2301)、入出力I/F558とNORゲート回路590とを介してリセットパルスをマスタIC570へ入力し、マスタIC570をハード的に初期化(ハードリセット)する(2302)。

【0381】

ハードリセットとは、マスタIC570の図示しないリセット回路にマスタIC570のRESET端子が接続されており、RESET端子に印加される電圧が所定時間ローレベルに保持されることによって、マスタIC570のリセット回路がマスタIC570自身をリセットすることをいう。なお、このRESET端子は、本実施形態における初期化信号入力指示端子として機能している。

30

【0382】

本実施形態では、このRESET端子に印加されるリセット信号が、前述したように、演出制御装置550に備わっている他の回路にも接続されている。この他の回路とは、例えば、VDP556や音LSI557などであり、演出制御装置550に電源が投入されて起動したときに、CPU551により初期化されるものである。従って、電源投入時には、ハードリセットによって、マスタIC570とともに、これらの回路もあわせて初期化できるため、処理の高速化が期待できる。

40

【0383】

次に、演出制御装置550は、マスタIC570に接続されたすべての装飾制御装置610のI<sup>2</sup>CI/Oエクスパンダ615を初期化するために、マスタIC570から初期化指示データを出力するスレーブリセット処理を実行する(2303)。スレーブリセット処理は、図24で詳細を説明する。

【0384】

次に、演出制御装置550は、ステップ2302の処理、及びステップ2303の処理でマスタIC570及びI<sup>2</sup>CI/Oエクスパンダ615の初期化が完了したので、リセット要求フラグを解除する(2304)。そして、演出制御装置550は、役物駆動MOT561が初期化中であることを示すモータ初期化フラグを設定する(2305)。なお、役物駆動MOT561の初期化とは、役物駆動MOT561の回転軸を初期位置に戻す

50

処理であり、図28に示すタイマ割込処理で行われる。

【0385】

次に、演出制御装置550は、役物駆動MOT561を初期化する場合に役物駆動MOT561に出力されるモータ出力データをRAM553に設定する(2306)。そして、演出制御装置550は、役物駆動SOL560を初期化するために、役物駆動SOL560の通電状態を非通電状態にするオフデータを役物駆動SOL560に出力し(2307)、図22に示すステップ2203の処理に進む。なお、役物駆動SOL560の初期化とは、役物駆動SOL560の通電状態を非通電状態にすることである。

【0386】

なお、CPU551は、入出力I/F558とNORゲート回路590とを介してリセットパルスをマスタIIC570へ入力し、マスタIIC570をハード的にリセットするとしたが、CPU551から、バス563を介してリセットレジスタ573に情報を書き込むことにより、マスタIIC570をソフト的にリセットしてもよい。

【0387】

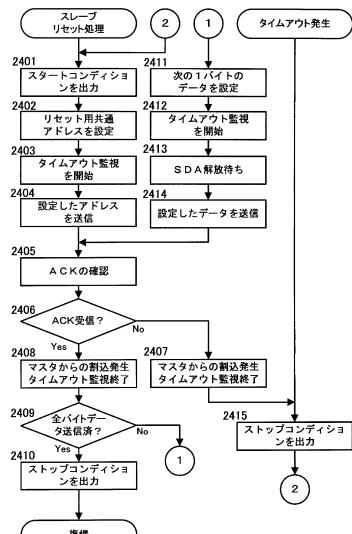

図24は、本発明の第1実施形態のスレーブリセット処理のフローチャートである。

【0388】

スレーブリセット処理は、I<sup>2</sup>C I / Oエクスパンダ615を初期化するための初期化指示データをI<sup>2</sup>C I / Oエクスパンダ615に送信する処理であり、図23に示すステップ2303の処理、及び図27に示すステップ2706の処理で実行される。

【0389】

初期化指示データは、マスタIIC570からバイトモードで送信される。バイトモードでは、マスタIIC570は、I<sup>2</sup>C I / Oエクスパンダ615へデータを1バイト送信する毎に、I<sup>2</sup>C I / Oエクスパンダ615からACK又はNACKを受信し、ACK及びNACKの何れを受信した場合でも、割込信号をCPU551に出力する。つまり、マスタIIC570からI<sup>2</sup>C I / Oエクスパンダ615へ1バイトのデータを送信することが完了すれば、ACK / NACKの受信に拘らず、必ず、マスタIIC570からCPU551へ割込信号が出力される。

【0390】

まず、マスタIIC570は、接続線SDA及び接続線SCLの信号レベルを、スタート条件を示す信号レベルに変化させる(2401)。

【0391】

次に、CPU551は、リセットアドレス(図20参照)を示す1バイト分のデータを出力用BUF572に設定する(2402)。

【0392】

そして、CPU551は、マスタIIC570へデータ送信の開始を指示した時点から、マスタIIC570がCPU551へ割込信号を伝達させるまでの時間を監視するために、バイトモード用の監視タイマの起動を開始する(2403)。以降、この監視時間をバイトモード監視時間ということにする。

【0393】

CPU551は、バイトモード時間の監視を開始してから所定時間経過しても、マスタIIC570から割込信号を受け付けていない場合には、タイムアウトが発生したとして、データ送信を中断するために、マスタIIC570にストップ条件を出力させ(2415)、その後、ステップ2401の処理に戻り、再度マスタIIC570にスタート条件を出力させてから、初期化指示データを初めのデータから送信する。

【0394】

次に、マスタIIC570は、ステップ2402の処理で出力用バッファ572に設定されたリセットアドレスをI<sup>2</sup>C I / Oエクスパンダ615に出力する(2404)。マスタIIC570は、このリセットアドレスを出力する際に、一旦、ドライバ576Aをオフさせて接続線SDAを解放する(ハイレベルに変化させる)動作を行う。そして、接続線SDAが解放されていない場合(ドライバ576Aをオフしても、接続線SDAがハイレ

10

20

30

40

50

ベルにならずロウレベルのままで維持されているとき)には、このリセットアドレスの出力は、接続線 SDA が開放される(接続線 SDA がハイレベルになる)まで待機する。

#### 【0395】

次に、マスタ I C 570 は、1 バイト分のデータ出力完了から、所定時間(前述したバイトモード監視時間よりも短い監視時間となっている)以内に ACK の返答信号がマスタ I C 570 に入力されたか否かを確認する(2405)。

#### 【0396】

そして、マスタ I C 570 は、ステップ 2405 の処理の確認結果に基づいて、データが出力されてから所定時間以内に ACK の返答信号が入力されているか否かを判定する(2406)。

10

#### 【0397】

ステップ 2406 の処理で、データが出力されてから所定時間以内に ACK の返答信号が入力されていないと判定された場合、マスタ I C 570 は、ステータス REG579 に返答信号が NACK であった旨の情報を設定したうえで、割込信号を発生させる。これにより、I<sup>2</sup>C I / O エクスパンダ 615 から NACK の返答信号を受信したことが、CPU 551 に通知される。このとき、CPU 551 はバイトモードの時間監視を終了する(2407)。

#### 【0398】

次いで、CPU は、データ送信を中断するために、マスタ I C 570 にストップ条件を出力させ(2415)、その後、ステップ 2401 の処理に戻り、再度マスタ I C 570 にスタート条件を出力させてから、初期化指示データを再度出力する。

20

#### 【0399】

ステップ 2406 の処理で、データが出力されてから所定時間以内に ACK の返答信号が入力されたと判定された場合、マスタ I C 570 は、ステータス REG579 に返答信号が ACK であった旨の情報を設定したうえで、割込信号を発生させる。これにより、I<sup>2</sup>C I / O エクスパンダ 615 から ACK の返答信号を受信したことが、CPU 551 に通知される。このとき、CPU 551 はバイトモードの時間監視を終了する(2408)。

#### 【0400】

そして、CPU 551 は、初期化指示データを構成する 3 種類のデータ(図 20 に示す、リセットアドレスを含むデータ 2001、第 1 所定値のデータ 2002、及び第 2 所定値のデータ 2003)をすべて出力したか否かを判定する(2409)。なお、これらのデータは出力順序が予め定められているので、ステップ 2409 の処理では、第 2 所定値のデータ 2003 が直後に出力されたか否かを判定すればよい。

30

#### 【0401】

ステップ 2409 の処理で、初期化指示データを構成するすべてのデータを出力したと判定された場合、つまり、図 20 に示す第 2 所定値を示すデータを出力した場合には、マスタ I C 570 は、接続線 SDA 及び接続線 SCL の信号レベルを、ストップ条件を示す信号レベルに変化させ(2410)、スレーブリセット処理を終了する。

#### 【0402】

40

ステップ 2409 の処理で、初期化指示データ構成するすべてのデータ出力していないと判定された場合には、CPU 551 は、次に送信される 1 バイトのデータを出力用 BUF572 に設定する(2411)。リセットアドレスを出力した直後に実行されるステップ 2411 の処理では、出力用 BUF572 には、図 20 に示す第 1 所定値のデータ 2002 が設定され、第 1 所定値のデータを出力した直後に実行されるステップ 2411 の処理では、出力用 BUF572 には、図 20 に示す第 2 所定値のデータ 2002 が設定される。

#### 【0403】

そして、CPU 551 は、マスタ I C 570 へデータ送信の開始を指示した時点から、マスタ I C 570 が CPU 551 へ割込信号を伝達させるまでの時間を監視するために、

50

バイトモード用の監視タイマの起動を開始する(2412)。

【0404】

次に、マスタIC570は、接続線SDAの電圧レベルを監視し、接続線SDAが解放されていることを確認してから(2413)、出力用BUF572に設定された1バイトのデータを出力し(2414)、ステップ2405の処理に進む。ステップ2413の処理は、グループ単位制御手段からの返答信号の出力が終了するまでは、接続線SDAが返答信号により占有されているので、マスタIC570は、グループ単位制御手段からの返答信号の出力が終了し、接続線SDAが解放されるまで待機する処理である。

【0405】

以上より、初期化指示データは、1バイトのデータを出力するごとに(つまり、3バイトの初期化指示データを送信する途中で)、出力した1バイトのデータに対する返答信号が否かを示す割込信号が出力されるか否かを監視するバイトモードで送信される。

【0406】

なお、ステップ2403の処理、及びステップ2412の処理において、1バイトのデータを送信してからマスタIC570から割込信号が出力されるまでの時間の監視は、CPU551が行ったが、マスタIC570自身が、1バイトのデータを送信してからマスタIC570から割込信号を出力するまでの時間を監視してもよい。

【0407】

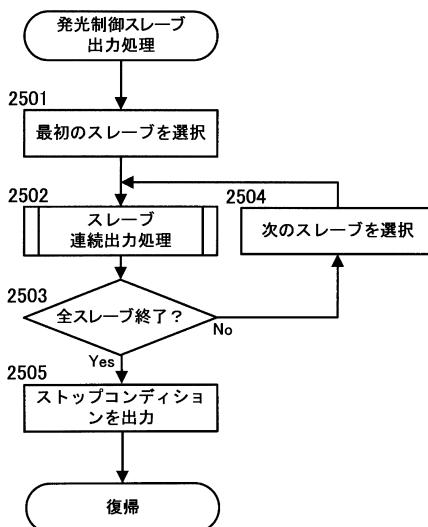

図25は、本発明の第1実施形態の発光制御スレーブ出力処理のフローチャートである。

20

【0408】

発光制御スレーブ出力処理は、発光装置に接続されるI<sup>2</sup>CI/Oエクスパンダ615(発光制御装置)に発行制御データを送信する処理であり、図22に示すステップ2206の処理で実行される。

【0409】

演出制御装置550は、複数の発光制御装置から、一つの発光制御装置を選択し(2501)、ステップ2501の処理で選択された発光制御装置にマスタIC570からデータを出力するスレーブ連続処理を実行する(2502)。スレーブ連続処理は、図26で詳細を説明する。

【0410】

そして、演出制御装置550は、すべての発光制御装置にデータを出力したか否かを判定する(2503)。

30

【0411】

ステップ2503の処理で、すべての発光制御装置にデータを出力していないと判定された場合、次の発光装飾制御装置を選択し(2504)、ステップ2504の処理で選択された発光制御装置にマスタIC570からデータを出力するスレーブ連続処理を実行する(2502)。

【0412】

一方、ステップ2503の処理で、すべての発光制御装置にデータを出力したと判定された場合、CPU551は、マスタIC570にストップ条件を出力させて発光制御スレーブ出力処理を終了し(2505)、図22に示すステップ2207の処理に進む。

40

【0413】

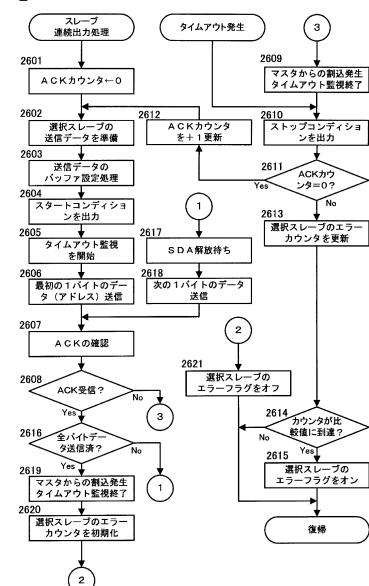

図26は、本発明の第1実施形態のスレーブ連続処理のフローチャートである。

【0414】

スレーブ連続処理は、発光装置に接続されるI<sup>2</sup>CI/Oエクスパンダ615に、演出制御データである発光制御データを送信する処理であり、図25に示すステップ2502の処理で実行される。

【0415】

発光制御データは、マスタIC570からバッファモードで送信される。バッファモードでは、マスタIC570は、出力用BUF572に格納された複数バイトのデータを、

50

I<sup>2</sup>C I / O エクスパンダ 615 へ 1 バイト毎送信し、その送信の都度、I<sup>2</sup>C I / O エクスパンダ 615 から ACK 又は NACK を受信する。そして、NACK を受信した場合には、その時点で、割込信号を CPU551 に出力する。

【0416】

ただし、ACK を受信した場合には、出力用 BUF572 に格納されたすべてのデータが送信完了となった場合にのみ、割込信号を CPU551 に出力する。マスタ I C 570 は、出力用 BUF572 に未送信のデータが残っている状態で I<sup>2</sup>C I / O エクスパンダ 615 から ACK を受信したときには、割込信号を CPU551 に出力せずに、出力用 BUF572 から次の送信すべきデータを取り出して、I<sup>2</sup>C I / O エクスパンダ 615 へ出力する。

10

【0417】

つまり、バッファモードの場合には、マスタ I C 570 は、出力用 BUF572 に格納されたデータが I<sup>2</sup>C I / O エクスパンダ 615 にすべて送信されるまでの間は、I<sup>2</sup>C I / O エクスパンダ 615 から ACK を受信し続けている限り、CPU551 に処理を引き渡すことなく、処理を継続することとなる。

【0418】

まず、CPU551 は、ACK の返答信号の受信に失敗したことを計数する ACK カウンタに 0 を設定する (2601)。

【0419】

次に、CPU551 は、選択されている装飾制御装置 610 に出力するデータを生成する (2602)。

20

【0420】

そして、CPU551 は、ステップ 2602 の処理で生成されたデータを出力用 BUF572 に設定するバッファ設定処理を実行する (2603)。設定されるデータは、図 19 に示す演出制御データのフォーマットとなっており、図 19 に示す送信順序に従って、1 バイト毎に区切られながら、I<sup>2</sup>C I / O エクスパンダ 615 へ送信される。

【0421】

そして、マスタ I C 570 は、接続線 SDA 及び接続線 SCL の信号レベルを、スタート条件を示す信号レベルに変化させる (2604)。

【0422】

具体的には、マスタ I C 570 は、接続線 SCL の信号レベルを HIGH に維持したまま、接続線 SDA の信号レベルを HIGH から LOW に変化させることによってスタート条件を示す信号を出力する。

30

【0423】

なお、マスタ I C 570 は、スタート条件を示す信号を出力後、制御対象となる装飾制御装置 610 へデータを送るために、接続線 SCL のレベルを LOW に変更する。

【0424】

次に、CPU551 は、マスタ I C 570 へデータ送信の開始を指示した時点から、マスタ I C 570 が CPU551 へ割込信号を伝達させるまでの時間を監視するために、バッファモード用の監視タイマの起動を開始する (2605)。以降、この監視時間をバッファモード監視時間ということにする。

40

【0425】

そして、マスタ I C 570 は、出力用 BUF572 に設定されているデータの先頭から、制御対象となる装飾制御装置 610 のスレーブアドレスに相当する 8 ビット分のデータを取得し、このアドレスの値を接続線 SCL の信号レベルを変化させながら、接続線 SDA を介して出力する (2606)。

【0426】

ステップ 2606 の処理で出力されるアドレスデータは 8 ビットのデータ列であるため、1 回の出力処理 (接続線 SCL が 8 回 HIGH に変化する間の出力) でアドレスデータが出力される。

50

## 【0427】

なお、マスタ I C 5 7 0 は、このスレーブアドレスを出力する際に、一旦、ドライバ 5 7 6 A をオフさせて接続線 S D A を解放する（ハイレベルに変化させる）動作を行う。そして、接続線 S D A が解放されていない場合には、このスレーブアドレスの出力は、接続線 S D A が開放されるまで待機する。

## 【0428】

ステップ 2 6 0 6 の処理で出力されたアドレスデータが I<sup>2</sup> C I / O エクスパンダ 6 1 5 に入力された場合、I<sup>2</sup> C I / O エクスパンダ 6 1 5 は、入力されたアドレスデータと自身に設定されているアドレスとが一致するか否かを判定する。

## 【0429】

10

入力されたアドレスデータと一致するアドレスが設定されている I<sup>2</sup> C I / O エクスパンダ 6 1 5 は、接続線 S C L の L O W から H I G H への変更回数が 8 回目になった直後であって、その H I G H レベルとなっている接続線 S C L が L O W レベルへと変化することを契機として、返答信号を接続線 S D A からマスタ I C 5 7 0 に出力する。

## 【0430】

次に、マスタ I C 5 7 0 は、ステップ 2 6 0 5 の処理でアドレスデータが出力されてから所定時間以内に A C K の返答信号がマスタ I C 5 7 0 に入力されたか否かを確認する（2 6 0 7）。

## 【0431】

次に、マスタ I C 5 7 0 は、ステップ 2 6 0 6 の処理の確認結果に基づいて、ステップ 2 6 0 2 の処理でアドレスデータが出力されてから所定時間以内に A C K の返答信号が入力されているか否かを判定する（2 6 0 8）。

## 【0432】

ステップ 2 6 0 5 の処理でアドレスデータが出力されてから所定時間以内に A C K の返答信号が入力されていないと、ステップ 2 6 0 8 の処理で判定された場合には、マスタ I C 5 7 0 は、ステータス R E G 5 7 9 に返答信号が N A C K であった旨の情報を設定したうえで、割込信号を発生させる。これにより、I<sup>2</sup> C I / O エクスパンダ 6 1 5 から N A C K の返答信号を受信したことが、C P U 5 5 1 に通知される。このとき、C P U 5 5 1 は、バイトモードの時間監視を終了する（2 6 0 9）。

## 【0433】

30

C P U 5 5 1 は、ステップ 2 6 0 9 で割込信号を受けつけると、マスタ I C 5 7 0 に対して、ストップ条件を発行するように指示する。ストップ条件の発行を指示されたマスタ I C 5 7 0 は、接続線 S D A 及び接続線 S C L の信号レベルを制御して、ストップ条件を発行する（2 6 1 0）。その後、A C K カウンタが 0 であるか否かを判定する（2 6 1 1）。

## 【0434】

ステップ 2 6 1 1 の処理で、A C K カウンタが 0 であると判定された場合、A C K の返答信号の受信に失敗したことを計数するために A C K カウンタを + 1 更新し（2 6 1 2）、再度同じデータを当該装飾制御装置 6 1 0 に送信するために、ステップ 2 6 0 2 の処理に戻る。

## 【0435】

一方、ステップ 2 6 1 1 の処理で、A C K カウンタが 0 でないと判定された場合、C P U 5 5 1 は、異常判定テーブル 2 1 0 0 に登録されたエントリのうち、I / O エクスパンダアドレス 2 1 0 1 が選択された装飾制御装置 6 1 0 の I<sup>2</sup> C I / O エクスパンダ 6 1 5 のアドレスと一致するエントリを選択し、選択されたエントリのエラーカウンタ 2 1 0 3 をインクリメントする（2 6 1 3）。

## 【0436】

そして、C P U 5 5 1 は、ステップ 2 6 1 3 の処理でインクリメントされたエラーカウンタ 2 1 0 3 の値が比較値 2 1 0 4 に達しているか否かを判定する（2 6 1 4）。

## 【0437】

10

20

30

40

50

ステップ2613の処理でインクリメントされたエラーカウンタ2103の値が比較値2104に達していると、ステップ2614の処理で判定された場合、CPU551は、異常判定テーブル2100に登録されたエントリのうち、選択された装飾制御装置610のエントリのエラーフラグをONに設定し(2615)、スレーブ連続出力処理を終了する。

【0438】