(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2005-506711

(P2005-506711A)

(43) 公表日 平成17年3月3日(2005.3.3)

(51) Int.Cl.<sup>7</sup>

H01L 29/786

C23C 16/42

G02F 1/1368

H01L 21/316

H01L 21/336

F 1

H01L 29/78 619A

C23C 16/42

G02F 1/1368

H01L 21/316 X

H01L 29/78 618E

テーマコード(参考)

2H092

4KO30

5FO58

5F110

審査請求 有 予備審査請求 未請求 (全 170 頁) 最終頁に続く

(21) 出願番号 特願2003-538811 (P2003-538811)

(86) (22) 出願日 平成13年11月7日 (2001.11.7)

(85) 翻訳文提出日 平成16年3月29日 (2004.3.29)

(86) 國際出願番号 PCT/KR2001/001896

(87) 國際公開番号 WO2003/036376

(87) 國際公開日 平成15年5月1日 (2003.5.1)

(31) 優先権主張番号 2001/60442

(32) 優先日 平成13年9月28日 (2001.9.28)

(33) 優先権主張国 韓国 (KR)

(71) 出願人 591028452

サムスン エレクトロニクス カンパニー

リミテッド

SAMSUNG ELECTRONICS

COMPANY, LIMITED

大韓民国 ギヨンギード スウォンーシ

ョントンギ メタニードン 416

(74) 代理人 100094145

弁理士 小野 由己男

100106367

弁理士 稲積 朋子

(72) 発明者 ホン, ワンーシック

大韓民国, ソウル 137-061, ソチ

ヨーグ, バンベードン, 104-402

ダイウーヒヨウリヨン アパート

最終頁に続く

(54) 【発明の名称】低誘電率絶縁膜を使用する薄膜トランジスタ基板及びその製造方法

## (57) 【要約】

薄膜トランジスター陣列基板は、絶縁基板、前記基板に形成されたゲート線集合、及び前記ゲート線集合の上を横切ると共に前記ゲート線集合から絶縁されているデータ線集合を備える。薄膜トランジスタは、ゲート線集合及びデータ線集合に接続される。保護膜が a-Si:C:O 又は a-Si:O:F で、前記薄膜トランジスタの上に形成される。画素電極が前記保護膜上に形成されると共に前記薄膜トランジスタ群に接続される。この構造において、寄生容量の問題が解決されつつ、開口比を向上させ、加工時間を低減させる。

**【特許請求の範囲】****【請求項 1】**

絶縁基板、

前記絶縁基板の上に形成されている第1信号線、

前記第1信号線上に形成されている第1絶縁膜、

前記第1絶縁膜の上に形成されていて、前記第1信号線と交差している第2信号線、

前記第1信号線及び前記第2信号線と連結されている薄膜トランジスタ、

誘電率が4.0以下のCVD膜であり、前記薄膜トランジスタ上に形成されており、前記薄膜トランジスタの所定電極を露出させる第1接触孔を有する第2絶縁膜、

前記第2絶縁膜の上に形成されていて、前記第1接触孔を通じて前記薄膜トランジスタの所定電極と連結されている第1画素電極 10

を含むことを特徴とする薄膜トランジスタ基板。

**【請求項 2】**

前記第1絶縁膜は低誘電率CVD膜である下部膜と窒化シリコン膜である上部膜からなることを特徴とする、請求項1に記載の薄膜トランジスタ基板。

**【請求項 3】**

前記第1画素電極は光を反射させる不透明な導電物質から構成されていることを特徴とする、請求項1に記載の薄膜トランジスタ基板。

**【請求項 4】**

前記第2絶縁膜は表面に凹凸パターンを有することを特徴とする、請求項3に記載の薄膜トランジスタ基板。 20

**【請求項 5】**

低誘電率CVD膜であり、前記第1画素電極上に形成されており、前記第1画素電極の所定部分を露出させる第2接触孔を有する第3絶縁膜、及び

前記第3絶縁膜の上に形成されていて、前記第2接触孔を通じて前記第1画素電極と連結されており、光を反射させる不透明な導電物質から構成されている第2画素電極をさらに含み、

前記第1画素電極は透明な導電物質から構成されており、前記第2画素電極は前記第1画素電極を透過した光が通過できる所定の開口部を有することを特徴とする、請求項1に記載の薄膜トランジスタ基板。 30

**【請求項 6】**

前記低誘電率CVD膜はa-Si:C:Oで構成されることを特徴とする、請求項1に記載の薄膜トランジスタ基板。

**【請求項 7】**

前記低誘電率CVD膜はa-Si:O:Fで構成されることを特徴とする、請求項1に記載の薄膜トランジスタ基板。

**【請求項 8】**

前記低誘電率CVD膜の誘電率は2ないし4の間の値を有することを特徴とする、請求項1に記載の薄膜トランジスタ基板。

**【請求項 9】**

絶縁基板の上に形成されているデータ線を含むデータ配線、 40

前記絶縁基板の上に形成されている赤、緑、青色フィルター、

低誘電率CVD膜であり、前記データ配線及び前記色フィルター上に形成されていて前記データ配線の所定部分を露出させる第1接触孔を有するバッファー層、

前記バッファー層上に形成されており、前記データ線と交差して画素を定義するゲート線及び前記ゲート線と連結されているゲート電極を含むゲート配線、

前記ゲート配線上に形成されていて、前記第1接触孔の少なくとも一部分を露出させる第2接触孔を有するゲート絶縁膜、

前記ゲート電極上部の前記ゲート絶縁膜の上に形成されている半導体層、

前記第1接触孔及び前記第2接触孔を通じて前記データ線と連結されていて少なくとも一 50

部分が前記半導体層と接しているソース用電極、前記半導体層上で前記ソース用電極と対向しているドレーン用電極及び前記ドレーン用電極と連結されている画素電極を含む画素配線

を含むことを特徴とする薄膜トランジスタ基板。

【請求項 10】

前記半導体層パターンは第1非晶質シリコン膜と、前記第1非晶質シリコン膜よりバンドギャップが低い第2非晶質シリコン膜の二重層構造になっていることを特徴とする、請求項9に記載の薄膜トランジスタ基板。

【請求項 11】

前記データ線と同一層、同一物質で形成されており、前記半導体層パターンに対応する部分に位置する光遮断部をさらに含むことを特徴とする、請求項10に記載の薄膜トランジスタ基板。

【請求項 12】

前記光遮断部は前記ゲート線方向に伸びていることを特徴とする、請求項11に記載の薄膜トランジスタ基板。

【請求項 13】

前記バッファー層の誘電率は2ないし4の間の値を有することを特徴とする、請求項1に記載の薄膜トランジスタ基板。

【請求項 14】

絶縁基板、

前記基板の上に形成されていてゲート線、ゲート電極及びゲートパッドを含むゲート配線、

前記ゲート配線上に形成されていて少なくとも前記ゲートパッドを露出させる接触孔を有するゲート絶縁膜、

前記ゲート絶縁膜の上に形成されている半導体層パターン、

前記半導体層パターンの上に形成されている接触層パターン、

前記接触層パターンの上に形成されていて、前記接触層パターンと実質的に同じ形態を有し、ソース電極、ドレーン電極、データ線及びデータパッドを含むデータ配線、

前記データ配線上に形成されていて、前記ゲートパッド、前記データパッド及び前記ドレーン電極を露出させる接触孔を有し、低誘電率CVD膜からなる保護膜パターン、

露出されている前記ゲートパッド、データパッド及びドレーン電極と各々電気的に連結される透明電極層パターン

を含むことを特徴とする液晶表示装置用薄膜トランジスタ基板。

【請求項 15】

前記絶縁基板上の前記ゲート配線と同一層に形成されている維持容量線、

前記維持容量と重なっていて前記半導体パターンと同一層に形成されている維持蓄電器用半導体パターン、

前記維持蓄電器用半導体パターンの上に形成されていて、前記維持蓄電器用半導体パターンと同じ平面的模様を有する維持蓄電器用接触層パターン及び

前記維持蓄電器用接触層パターンの上に形成されていて、前記維持蓄電器用半導体パターンと同じ平面的模様を有する維持蓄電器用導電体パターンをさらに含み、

前記維持蓄電器用導電体パターンは前記透明電極パターンの一部と連結されていることを特徴とする、請求項14に記載の薄膜トランジスタ基板。

【請求項 16】

前記低誘電率CVD膜の誘電率は2ないし4の間の値を有することを特徴とする、請求項14に記載の薄膜トランジスタ基板。

【請求項 17】

絶縁基板の上にゲート線、前記ゲート線と連結されているゲート電極及び前記ゲート線と連結されているゲートパッドを含むゲート配線を形成する段階、

ゲート絶縁膜を形成する段階、

10

20

30

40

50

半導体層を形成する段階、

導電物質を積層しパターニングして前記ゲート線と交差するデータ線、前記データ線と連結されているデータパッド、前記データ線と連結されていて前記ゲート電極に隣接するソース電極及び前記ゲート電極に対して前記ソース電極の対向側に位置するドレーン電極を含むデータ配線を形成する段階、

低誘電率CVD膜を蒸着して保護膜を形成する段階、

前記ゲート絶縁膜と共に前記保護膜をパターニングして前記ゲートパッド、前記データパッド及び前記ドレーン電極を各々露出する接触孔を形成する段階、

透明導電膜を積層しパターニングして前記接触孔を通じて前記ゲートパッド、前記データパッド及び前記ドレーン電極と各々連結される補助ゲートパッド、補助データパッド及び画素電極を形成する段階

を含むことを特徴とする薄膜トランジスタ基板の製造方法。

【請求項18】

前記保護膜を形成する段階は

気体状態のSiH<sub>3</sub>、SiO<sub>2</sub>、(SiH)<sub>4</sub>O<sub>4</sub>のうちの少なくともいずれか一つを基本ソースとして使用し、N<sub>2</sub>OまたはO<sub>2</sub>を酸化剤として使用してPECVD法によって蒸着する段階であることを特徴とする、請求項17に記載の薄膜トランジスタ基板の製造方法。

【請求項19】

前記保護膜を形成する段階は

気体状態のSiH<sub>4</sub>、SiF<sub>4</sub>のうちの少なくともいずれか一つとCF<sub>4</sub>及びO<sub>2</sub>を添加した気体を使用してPECVD法によって蒸着する段階であることを特徴とする、請求項17に記載の薄膜トランジスタ基板の製造方法。

【請求項20】

前記データ配線及び前記半導体層は所定の厚さの第1部分、前記第1部分より厚さが厚い第2部分、前記第1厚さより厚さが薄い第3部分を有する感光膜パターンを利用する写真蝕刻工程で共に形成することを特徴とする、請求項17に記載の薄膜トランジスタ基板の製造方法。

【請求項21】

前記写真蝕刻工程において、前記第1部分は前記ソース電極と前記ドレーン電極の間に位置するように形成し、前記第2部分は前記データ配線に位置するように形成することを特徴とする、請求項20に記載の薄膜トランジスタ基板の製造方法。

【請求項22】

前記ゲート絶縁膜を形成する段階は

低誘電率CVD膜を蒸着する第1段階及び窒化シリコン膜を蒸着する第2段階からなり、前記第1段階と前記第2段階は真空が維持される状態で進められることを特徴とする、請求項17に記載の薄膜トランジスタ基板の製造方法。

【請求項23】

絶縁基板の上にデータ線を含むデータ配線を形成する第1段階、

前記基板上部に赤、緑、青色フィルターを形成する第2段階、

低誘電率CVD膜を蒸着して前記データ配線及び前記色フィルターを覆うバッファー層を形成する第3段階、

前記絶縁膜上部にゲート線及びゲート電極を含むゲート配線を形成する第4段階、

前記ゲート配線を覆うゲート絶縁膜を形成する第5段階、

前記ゲート絶縁膜の上に島模様の抵抗性接触層と半導体層パターンを形成すると同時に、前記ゲート絶縁膜と前記バッファー層に前記データ線の一部を露出する第1接触孔を形成する第6段階、

前記島模様の抵抗性接触層パターンの上に互いに分離されて形成されていて同一層で作られたソース用電極及びドレーン用電極と、前記ドレーン用電極と連結された画素電極を含む画素配線を形成する第7段階、

10

20

30

40

50

前記ソース用電極と前記ドレーン用電極の間に位置する前記抵抗性接觸層パターンの露出部分を除去して前記抵抗性接觸層パターンを両側に分離する第8段階、

を含むことを特徴とする薄膜トランジスタ基板の製造方法。

【請求項24】

前記第6段階は、

前記ゲート絶縁膜の上に非晶質シリコン膜、不純物がドーピングされた非晶質シリコン膜を順次に蒸着する段階、

前記ゲート電極上の所定面積を覆っている第1部分、前記第1接觸孔が形成される部分を除いた残りの部分を覆っていて、前記第1部分より薄い第2部分からなる感光膜パターンを形成する段階、

前記感光膜の第1部分及び第2部分をマスクとしてその下部の前記不純物がドーピングされた非晶質シリコン膜、前記非晶質シリコン膜、前記ゲート絶縁膜及び前記バッファー層を蝕刻して前記第1接觸孔を形成する段階、

前記感光膜パターンの第2部分を除去する段階、

前記感光膜パターンの第1部分をマスクとしてその下部の前記不純物がドーピングされた非晶質シリコン膜及び前記非晶質シリコン膜を蝕刻して前記島模様の半導体層パターンと前記抵抗性接觸層パターンを形成する段階、

前記感光膜パターンの第1部分を除去する段階

を含むことを特徴とする、請求項23に記載の薄膜トランジスタ基板の製造方法。

【請求項25】

前記低誘電率CVD膜の誘電率は2ないし4の間の値を有することを特徴とする、請求項17に記載の薄膜トランジスタ基板の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、低誘電率絶縁層を有する薄膜トランジスタ基板及びその製造方法に関するものである。

【背景技術】

【0002】

薄膜トランジスタ基板は液晶表示装置や有機EL (electro luminescence) 表示装置などで各画素を独立的に駆動するための回路基板として用いられる。薄膜トランジスタ基板は走査信号を伝達する走査信号配線またはゲート配線と、画像信号を伝達する画像信号線またはデータ配線とが形成されており、ゲート配線及びデータ配線と連結されている薄膜トランジスタ、薄膜トランジスタと連結されている画素電極、ゲート配線を覆って絶縁するゲート絶縁膜及び薄膜トランジスタとデータ配線を覆って絶縁する保護膜などから構成されている。薄膜トランジスタはゲート配線に接続されたゲート電極とチャンネルを形成する半導体層、データ配線の一部であるソース電極とドレーン電極及びゲート絶縁膜と保護膜などからなる。薄膜トランジスタはゲート配線を通じて伝達される走査信号により、データ配線を通じて伝達される画像信号を画素電極に伝達または遮断するスイッチング素子である。

【0003】

大型で高精細の液晶表示装置が求められていることに伴い、各種寄生容量の増加による信号歪曲問題が至急解決しなければならない問題として浮上している。また、ノートブックコンピュータでの消費電力減少とテレビ用液晶表示装置での可視聴距離を増加させるための輝度向上が必要となって、開口率の増大要求が大きくなっている。ところが、開口率を増大させるためには画素電極をデータ配線上にまで重なるように形成する必要があるが、このようにすると画素電極とデータ線の間の寄生容量が増加してしまう。寄生容量増加による問題を解決するためには画素電極とデータ線間の垂直離隔を十分に確保しなければならず、垂直離隔確保のために従来は主に有機絶縁膜で保護膜を形成していた。しかし、有機絶縁膜を利用する工程は次のような短所を持つ。まず、材料費が高い。特に、スピンドル

10

20

30

40

50

ーティングの際に失われる量が多いため材料費の増加をもたらす。次に、有機絶縁膜は耐熱性が不足していて後続工程が多くの制約を受ける。また、材料が固まりなどによって不純物粒子が発生する頻度が高い。近接する層との接着力が脆弱である。保護膜上に形成される画素電極の形成時の蝕刻誤差が非常に大きい。

【発明の開示】

【発明が解決しようとする課題】

【0004】

本発明が解決しようとする技術的課題は、高開口率を有して寄生容量問題がない薄膜トランジスタ基板を提供することにある。

【課題を解決するための手段】

【0005】

このような課題を解決するために本発明では低誘電率CVD膜を利用する。

具体的には、絶縁基板、前記絶縁基板上に形成されている第1信号線、

前記第1信号線上に形成されている第1絶縁膜、前記第1絶縁膜上に形成されており、前記第1信号線と交差している第2信号線、前記第1信号線及び前記第2信号線と連結されている薄膜トランジスタ、低誘電率CVD膜であって前記薄膜トランジスタ上に形成されており、前記薄膜トランジスタの所定電極を露出させる第1接触孔を有する第2絶縁膜、前記第2絶縁膜上に形成されており、前記第1接触孔を通じて前記薄膜トランジスタの所定電極と連結されている第1画素電極を含む薄膜トランジスタ基板を備える。

【0006】

この時、前記第1絶縁膜は低誘電率CVD膜である下部膜と窒化シリコン膜である上部膜とで構成でき、前記第1画素電極は光を反射させる不透明な導電物質で構成でき、前記第2絶縁膜は表面に凹凸パターンが有ってもよい。また、低誘電率CVD膜であって前記第1画素電極上に形成されており、前記第1画素電極の所定部分を露出させる第2接触孔を有する第3絶縁膜、及び前記第3絶縁膜の上に形成されており、前記第2接触孔を通じて前記第1画素電極と連結されており、光を反射させる不透明な導電物質から構成されている第2画素電極を更に含み、前記第1画素電極は透明な導電物質から構成されており、前記第2画素電極は前記第1画素電極を透過した光が通過できる所定の開口部を有することができる。前記低誘電率CVD膜はa-Si:C:Oまたはa-Si:O:Fで構成できる。また、前記低誘電率CVD膜の誘電率は2から4の間の値を有するのが好ましい。

【0007】

一方、絶縁基板上に形成されているデータ線を含むデータ配線、前記絶縁基板上に形成されている赤、緑、青の色フィルター、低誘電率CVD膜であって前記データ配線及び前記色フィルターの上に形成されており、前記データ配線の所定部分を露出させる第1接触孔を有するバッファー層、前記バッファー層上に形成されており、前記データ線と交差して画素を定義するゲート線及び前記ゲート線と連結されているゲート電極を含むゲート配線、前記ゲート配線上に形成されており、前記第1接触孔の少なくとも一部分を露出させる第2接触孔を有するゲート絶縁膜、前記ゲート電極上部の前記ゲート絶縁膜上に形成されている半導体層、前記第1接触孔及び前記第2接触孔を通じて前記データ線と連結されており、少なくとも一部分が前記半導体層と接しているソース用電極、前記半導体層上で前記ソース用電極と対向しているドレーン用電極、及び前記ドレーン用電極と連結されている画素電極を含む画素配線を含む薄膜トランジスタ基板を用意し、色フィルターを薄膜トランジスタアレイの下に形成することもできる。

【0008】

ここで、前記半導体層パターンは第1非晶質シリコン膜と、前記第1非晶質シリコン膜よりバンドギャップの低い第2非晶質シリコン膜の二重層構造として構成でき、前記データ線と同じ層及び同じ物質で形成されており、前記半導体層パターンに対応する部分に位置する光遮断部をさらに含むことができる。

このような薄膜トランジスタ基板は、絶縁基板上にデータ線を含むデータ配線を形成する第1段階、前記基板上部に赤、緑、青の色フィルターを形成する第2段階、低誘電率CVD

10

20

30

40

50

D膜を蒸着して、前記データ配線及び前記色フィルターを覆うバッファー層を形成する第3段階、前記絶縁膜上部にゲート線及びゲート電極を含むゲート配線を形成する第4段階、前記ゲート配線を覆うゲート絶縁膜を形成する第5段階、前記ゲート絶縁膜上に島模様の抵抗性接触層と半導体層パターンを形成する同時に、前記ゲート絶縁膜と前記バッファー層に前記データ線一部を露出する第1接触孔を形成する第6段階、前記島模様の抵抗性接触層パターンの上に互いに分離して形成されており、同じ層で作られたソース用電極及びドレーン用電極と、前記ドレーン用電極と連結された画素電極を含む画素配線を形成する第7段階、前記ソース用電極と前記ドレーン用電極の間に位置する前記抵抗性接触層パターンの露出部分を除去して、前記抵抗性接触層パターンを両側に分離する第8段階を含む方法で製造する。

10

## 【0009】

ここで、第6段階は、前記ゲート絶縁膜上に非晶質シリコン膜、不純物がドーピングされた非晶質シリコン膜を順次に蒸着する段階、前記ゲート電極上の所定面積を覆っている所定の厚さの第1部分、前記第1接触孔が形成される部分を除いた残り部分を覆っており、前記第1部分より薄い第2部分からなる感光膜パターンを形成する段階、前記感光膜の第1部分及び第2部分をマスクとしてその下部の前記不純物がドーピングされた非晶質シリコン膜、前記非晶質シリコン膜、前記ゲート絶縁膜及び前記バッファー層を蝕刻して前記第1接触孔を形成する段階、前記感光膜パターンの第2部分を除去する段階、前記感光膜パターンの第1部分をマスクとしてその下部の前記不純物がドーピングされた非晶質シリコン膜及び前記非晶質シリコン膜を蝕刻して、前記島模様の半導体層パターンと前記抵抗性接触層パターンを形成する段階、前記感光膜パターンの第1部分を除去する段階を含む段階であることができる。

20

## 【0010】

また、絶縁基板、前記基板上に形成されており、ゲート線、ゲート電極及びゲートパッドを含むゲート配線、前記ゲート配線上に形成されており、少なくとも前記ゲートパッドを露出させる接触孔を有するゲート絶縁膜、前記ゲート絶縁膜上に形成されている半導体層パターン、前記半導体層パターン上に形成されている接触層パターン、前記接触層パターン上に形成されており、前記接触層パターンと実質的に同じ形態を有し、ソース電極、ドレーン電極、データ線及びデータパッドを含むデータ配線、前記データ配線上に形成されており、前記ゲートパッド、前記データパッド及び前記ドレーン電極を露出させる接触孔を有し、低誘電率CVD膜からなる保護膜パターン、前記ゲートパッド、データパッド及びドレーン電極と各々電気的に連結される透明電極層パターンを含む液晶表示装置用薄膜トランジスタ基板を用意する。

30

## 【0011】

この時、前記絶縁基板上の前記ゲート配線と同一層に形成されている維持容量線、前記維持容量と重なっており、前記半導体パターンと同一層に形成されている維持蓄電器用半導体パターン、前記維持蓄電器用半導体パターン上に形成されており、前記維持蓄電器用半導体パターンと同じ平面的模様を有する維持蓄電器用接触層パターン及び前記維持蓄電器用接触層パターン上に形成されており、前記維持蓄電器用半導体パターンと同じ平面的模様を有する維持蓄電器用導電体パターンをさらに含み、前記維持蓄電器用導電体パターンは前記透明電極パターンの一部と連結されていてもよい。

40

## 【0012】

このような薄膜トランジスタ基板は、絶縁基板上にゲート線、前記ゲート線と連結されているゲート電極及び前記ゲート線と連結されているゲートパッドを含むゲート配線を形成する段階、ゲート絶縁膜を形成する段階、半導体層を形成する段階、導電物質を積層しパターン化して、前記ゲート線と交差するデータ線、前記データ線と連結されているデータパッド、前記データ線と連結されており、前記ゲート電極に隣接するソース電極、及び前記ゲート電極に対して前記ソース電極の対向側に位置するドレーン電極を含むデータ配線を形成する段階、低誘電率CVD膜を蒸着して保護膜を形成する段階、前記ゲート絶縁膜と共に前記保護膜をパターン化して、前記ゲートパッド、前記データパッド及び前記ドレ

50

ーン電極を各々露出する接触孔を形成する段階、透明導電膜を積層しパターン化して、前記接触孔を通じて前記ゲートパッド、前記データパッド及び前記ドレーン電極と各々連結される補助ゲートパッド、補助データパッド及び画素電極を形成する段階を含む方法で製造する。

【0013】

この時、前記保護膜を形成する段階は、気体状態の  $\text{SiH}(\text{CH}_3)_3$ 、 $\text{SiO}_2(\text{CH}_3)_4$ 、 $(\text{SiH})_4\text{O}_4(\text{CH}_3)_4$ 、 $\text{Si}(\text{C}_2\text{H}_5\text{O})_4$  のうちの少なくともいずれか一つを基本ソースとして使用し、 $\text{N}_2\text{O}$  または  $\text{O}_2$  を酸化剤として使用して PECVD 法により蒸着したり、気体状態の  $\text{SiH}_4$ 、 $\text{SiF}_4$  のうちの少なくともいずれか一つと  $\text{CF}_4$  と  $\text{O}_2$  を添加した気体とを使用し、PECVD 法により蒸着する段階であり得る。 10

【0014】

また、前記データ配線及び前記半導体層は、第 1 部分、前記第 1 部分より厚さが厚い第 2 部分、前記第 1 厚さより厚さが薄い第 3 部分を有する感光膜パターンを利用する写真蝕刻工程で一緒に形成でき、前記写真蝕刻工程で、前記第 1 部分は前記ソース電極と前記ドレーン電極の間に位置するように形成し、前記第 2 部分は前記データ配線上部に位置するように形成するのが好ましい。また、前記ゲート絶縁膜を形成する段階は、低誘電率 CVD 膜を蒸着する第 1 段階及び窒化シリコン膜を蒸着する第 2 段階からなり、前記第 1 段階と前記第 2 段階は真空の維持される状態で行う段階であり得る。以上において、前記低誘電率 CVD 膜の誘電率は 2 から 4 までの間の値を有する。 20

【発明の効果】

【0015】

本発明では低誘電率 CVD 膜を使用して保護膜を形成するので寄生容量問題を解消して高開口率構造を実現でき、工程時間を短縮できて、有機絶縁膜を使用する時に発生する材料費の上昇、耐熱性不足、隣接膜との接着力不足などの問題を解決できる。

【発明を実施するための最良の形態】

【0016】

以下、添付した図面を参照して本発明の実施例について説明する。

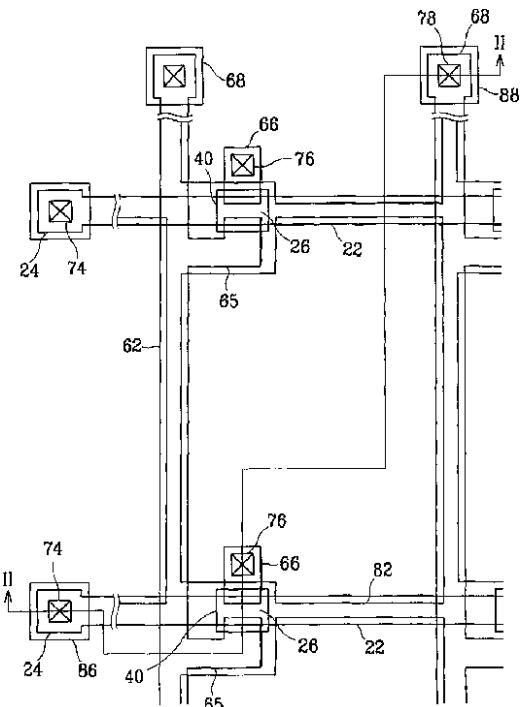

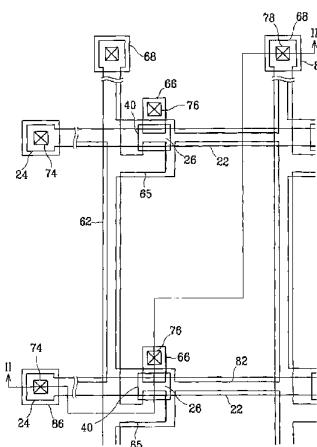

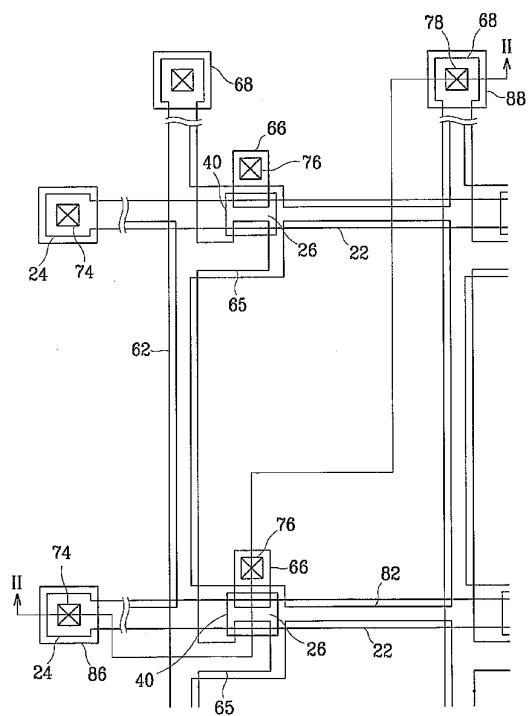

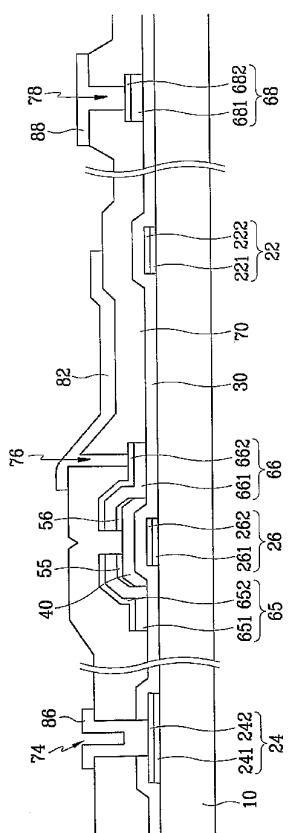

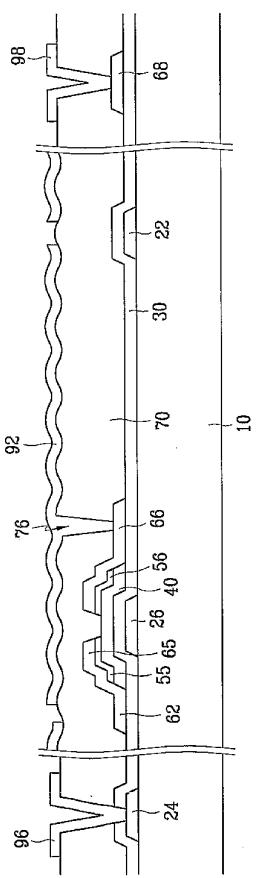

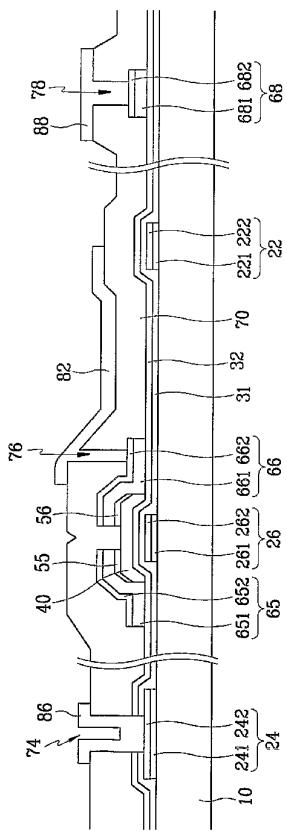

図 1 は本発明の第 1 実施例による液晶表示装置用薄膜トランジスタ基板であり、図 2 は図 1 に示した薄膜トランジスタ基板の II - II 線に対する断面図である。

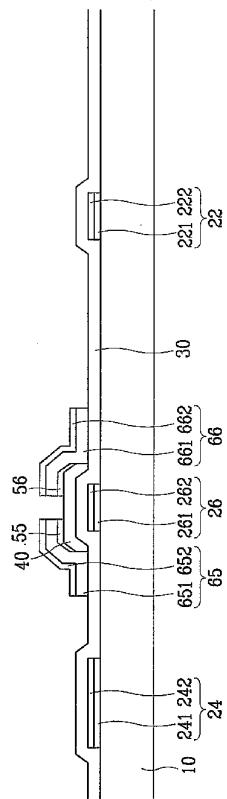

絶縁基板 10 の上にクロム (Cr) またはモリブデン (Mo) 合金などで構成された第 1 ゲート配線層 221、241、261 と、アルミニウム (Al) または銀 (Ag) 合金などで構成された第 2 ゲート配線層 222、242、262 の二重層として構成されるゲート配線が形成されている。ゲート配線は横方向に伸びているゲート線 22、ゲート線 22 の端に連結されていて外部からのゲート信号の印加を受けてゲート線に伝達するゲートパッド 24、及びゲート線 22 に連結されている薄膜トランジスタのゲート電極 26 を含む。 30

【0017】

基板 10 の上には窒化シリコン ( $\text{SiN}_x$ ) などからなるゲート絶縁膜 30 がゲート配線 22、24、26 を覆っている。

ゲート電極 24 のゲート絶縁膜 30 の上部には非晶質シリコンなどの半導体からなる半導体層 40 が島模様に形成されており、半導体層 40 の上部にはシリサイドまたは n 形不純物が高濃度でドーピング (活性剤として添加) されている n+ 水素化非晶質シリコンなどの物質で作られた抵抗性接触層 54、56 が各々形成されている。 40

【0018】

抵抗性接触層 54、56 及びゲート絶縁膜 30 の上にはデータ線アセンブリが 2 重層構造で形成されている。データ戦アセンブリは、Cr 合金や Mo 合金などからなる第 1 データ配線層 621、651、661、681 と、Al または Ag 合金などからなる第 2 データ配線層 622、652、662、682 の二重層になっている。データ配線 62、65、66、68 は縦方向に形成され、ゲート線 22 と交差して画素を定義するデータ線 62、データ線 62 の分枝であり、抵抗性接触層 54 の上部まで伸びているソース電極 65、データ線 62 の一端に連結されており、外部からの画像信号の印加を受けるデータパッド 6 50

8、ソース電極 6 5 と分離されており、ゲート電極 2 6 に対してソース電極 6 5 の反対側抵抗性接触層 5 6 の上部に形成されているドレーン電極 6 6 を含む。

【0019】

データ配線 6 2、6 5、6 6、6 8 及びこれらが遮ることのない半導体層 4 0 の上部には、PECVD (プラズマ強化CVD) 法によって蒸着された a - Si : C : O 膜または a - Si : O : F 膜 (低誘電率CVD膜) からなる保護膜 7 0 が形成されている。PECVD 法によって蒸着された a - Si : C : O 膜と a - Si : O : F 膜 (低誘電率CVD膜) は誘電定数が 4 以下 (誘電定数は 2 ないし 4 の間の値を有する) であって誘電率が非常に低い。従って、厚さが薄くても寄生容量問題が発生しない。さらに、他の膜との接着性及び段差被覆性 (step coverage) が優れている。また、無機質CVD膜であるので耐熱性が有機絶縁膜に比べて優れている。同時に、PECVD 法によって蒸着された a - Si : C : O 膜と a - Si : O : F 膜 (低誘電率CVD膜) は蒸着速度や蝕刻速度が窒化シリコン膜に比べて 4 ~ 10 倍速いので、工程時間面からも非常に有利である。

【0020】

保護膜 7 0 にはドレーン電極 6 6 及びデータパッド 6 8 を各々露出する接触孔 7 6、7 8 が形成されており、ゲート絶縁膜 3 0 と共にゲートパッド 2 4 を露出する接触孔 7 4 が形成されている。この時、パッド 2 4、6 8 を露出する接触孔 7 4、7 8 は角を有したり円形の多様な模様で形成でき、面積は  $2 \text{ mm} \times 60 \mu\text{m}$  を超えず、 $0.5 \text{ mm} \times 15 \mu\text{m}$  以上であるのが好ましい。

【0021】

保護膜 7 0 の上には接触孔 7 6 を通じてドレーン電極 6 6 と電気的に連結されており、画素に位置する画素電極 8 2 が形成されている。また、保護膜 7 0 の上には接触孔 7 4、7 8 を通じて各々ゲートパッド 2 4 及びデータパッド 6 8 と連結されている補助ゲートパッド 8 6 及び補助データパッド 8 8 が形成されている。ここで、画素電極 8 2 と補助ゲート及びデータパッド 8 6、8 8 はITO (インジウム錫酸化物) またはIZO (インジウム亜鉛酸化物) から構成されている。

【0022】

ここで、画素電極 8 2 は図 1 及び図 2 のように、ゲート線 2 2 と重なって維持蓄電器をなし、維持容量が足りない場合には、ゲート配線 2 2、2 4、2 6 と同一層に維持容量用配線を追加することもできる。

また、画素電極 8 2 はデータ線 6 2 とも重なるように形成して開口率を極大化している。このように開口率を極大化するために画素電極 8 2 をデータ線 6 2 と重ねて形成しても、保護膜 7 0 の誘電率が低いためこれらの間で形成される寄生容量は問題にならない程度に小さい。

【0023】

以下、このような本発明の第 1 実施例による薄膜トランジスタ基板の製造法について、図 3 a 乃至図 7 b を参照して詳細に説明する。

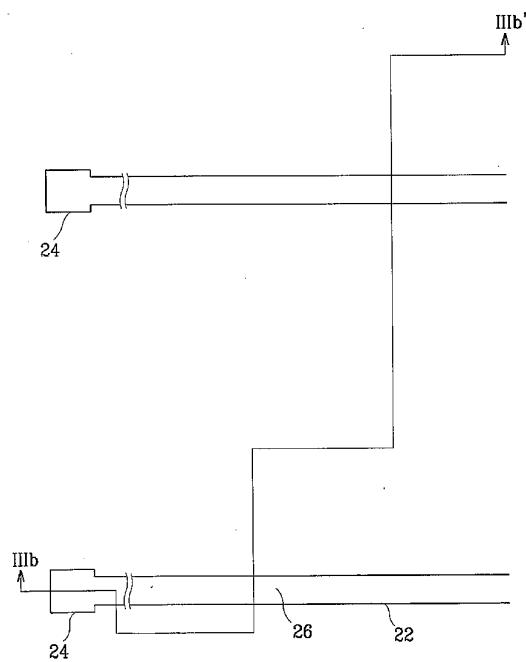

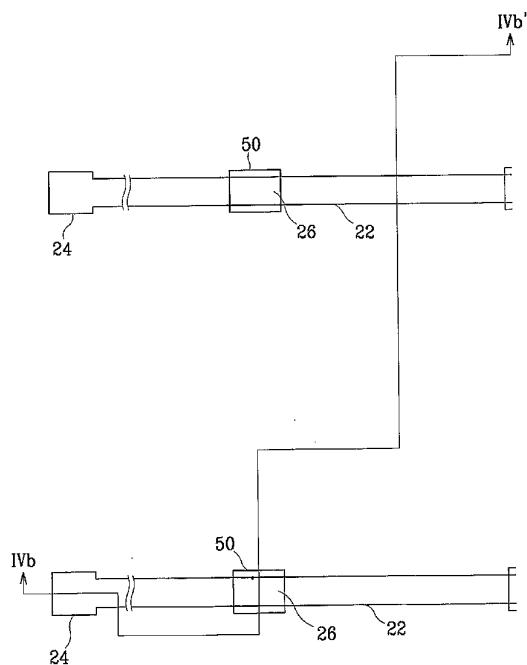

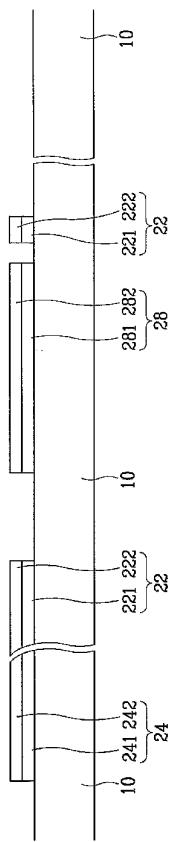

まず、図 3 a 及び 3 b に示したように、基板 1 0 の上に Cr または Mo 合金などを蒸着して第 1 ゲート配線層 2 2 1、2 4 1、2 6 1 を積層し、Al または Ag 合金などを蒸着して第 2 ゲート配線層 2 2 2、2 4 2、2 6 2 を積層した後にパターニングして、ゲート線 2 2、ゲート電極 2 6 及びゲートパッド 2 4 を含む横方向に伸びているゲート配線を形成する。

【0024】

この時、第 1 ゲート配線層 2 2 1、2 4 1、2 6 1 を Mo 合金で形成し、第 2 ゲート配線層 2 2 2、2 4 2、2 6 2 を Ag 合金で形成した場合には、これら二つの層が全て Ag 合金蝕刻剤であるリン酸、硝酸、酢酸及び超純水 (deionized water) を混合した物質によって蝕刻される。従って、一回の蝕刻工程により二重層のゲート配線 2 2、2 4、2 6 を形成できる。また、リン酸、硝酸、酢酸及び超純水混合物による Ag 合金と Mo 合金に対する蝕刻比は Ag 合金に対する蝕刻比がより大きいので、ゲート配線に必要な  $30^\circ$  程度の細り (taper) 角が得られる。

10

20

30

40

50

## 【0025】

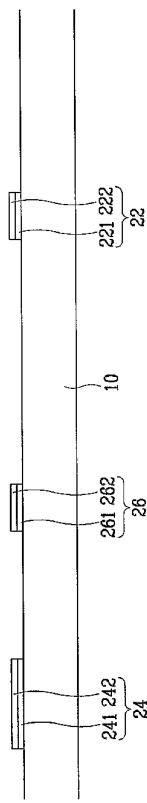

次に、図4a及び図4bに示したように、窒化シリコンからなるゲート絶縁膜30、非晶質シリコンからなる半導体層40、ドーピングされた非晶質シリコン層50の3層膜を連続して積層し、半導体層40とドーピングされた非晶質シリコン層50を写真蝕刻して、ゲート電極24上部のゲート絶縁膜30の上に島模様の半導体層40と抵抗性接触層50を形成する。

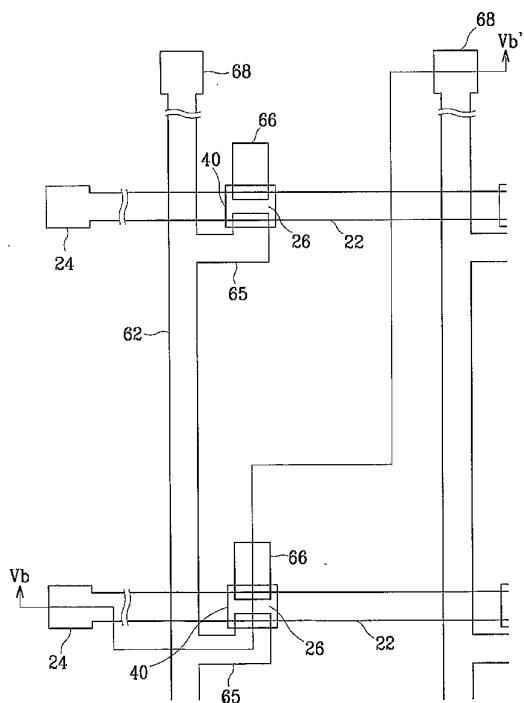

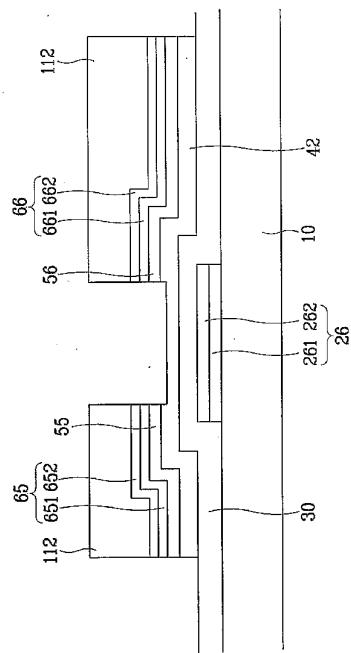

## 【0026】

次に、図5a乃至図5bに示したように、CrまたはMo合金などを基板10に蒸着して第1データ配線層651、661、681を積層し、AlまたはAg合金などを蒸着して第2データ配線層652、662、682を積層した後に写真蝕刻して、ゲート線22と交差するデータ線62、データ線62と連結されてゲート電極26の上部まで延びているソース電極65、外部から画像信号を受信するデータ線62の一端に連結されているデータパッド68、及びソース電極64と分離されており、ゲート電極26を中心にソース電極65と対向するドレーン電極66を含むデータ配線を形成する。

## 【0027】

次に、データ配線62、65、66、68で遮らないドーピングされた非晶質シリコン層50を蝕刻してゲート電極26を中心に両側に分離させる一方、両側のドーピングされた非晶質シリコン層55、56の間の半導体層40を露出させる。次に、露出された半導体層40の表面を安定化するために酸素プラズマを実施するのが好ましい。

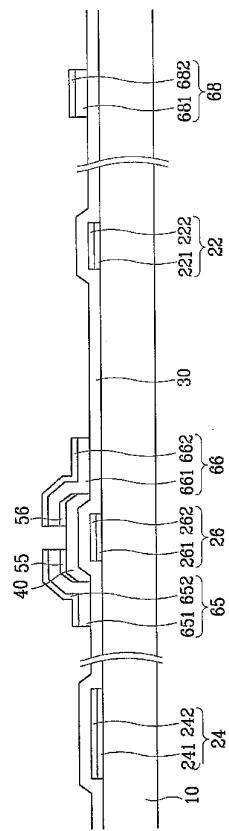

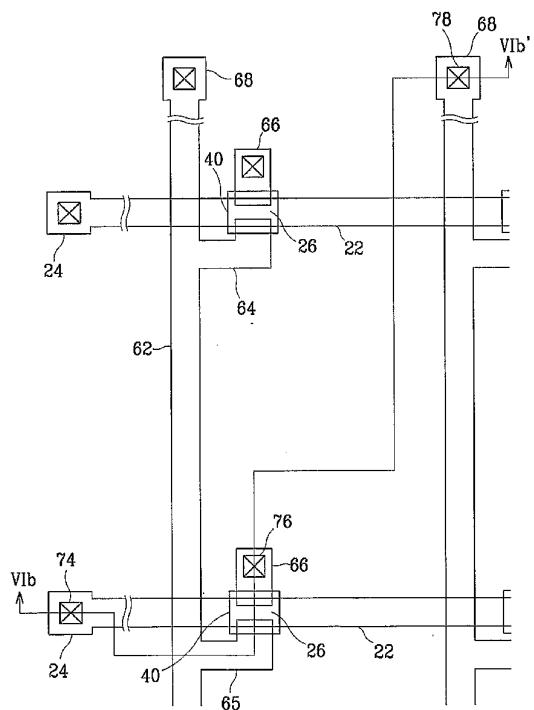

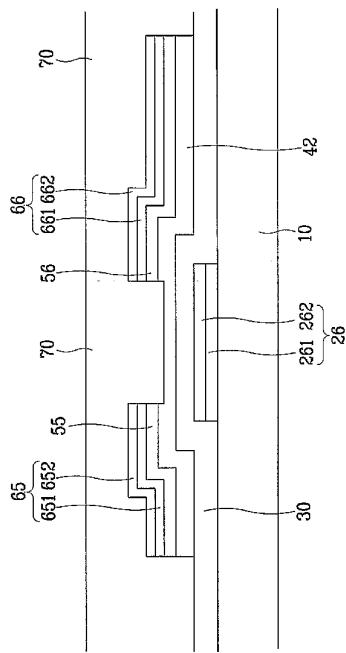

次に、図6a及び6bのように、a-Si:C:O膜またはa-Si:O:F膜を化学気相蒸着(CVD)法によって成長させて保護膜70を形成する。この時、a-Si:C:O膜の場合には気体状態のSiH(CH3)3、SiO2(CH3)4、(SiH)4O4(CH3)4、Si(C2H5O)4などを基本ソースとして使用し、N2OまたはO2などの酸化剤とArまたはHeなどを混合した気体を落としながら蒸着する。また、a-Si:O:F膜の場合にはSiH4、SiF4等にO2を添加した気体を落としながら蒸着する。この時、フッ素の補助ソースとしてCF4を添加することもできる。

## 【0028】

次に、ゲート絶縁膜30と共に保護膜70をパターニングして、ゲートパッド24、ドレーン電極66及びデータパッド68を露出する接触孔74、76、78を形成する。ここで、接触孔74、76、78は角を有する模様または円形の模様に形成でき、パッド24、68を露出する接触孔74、78の面積は2mm×60μmを超えず、0.5mm×15μm以上であるのが好ましい。

## 【0029】

次に、最後に図1及び2に示したように、ITOまたはIZO膜を蒸着し写真蝕刻して、第1接触孔76を通じてドレーン電極66と連結される画素電極82と第2及び第3接触孔74、78を通じてゲートパッド24及びデータパッド68と各々連結される補助ゲートパッド86、及び補助データパッド88を形成する。ITOやIZOを積層する前の予熱(pre-heating)工程で使用する気体は窒素を利用するのが好ましい。これは接触孔74、76、78を通じて露出している金属膜24、66、68の上部に金属酸化膜が形成されることを防止するためである。

## 【0030】

以上のように、PECVDで形成したa-Si:C:Oまたはa-Si:O:Fなどの低誘電率絶縁膜(低誘電率CVD膜)を保護膜70として使用することにより寄生容量問題を解決でき、従って、開口率を極大化できる。それだけでなく、蒸着及び蝕刻速度が速くなるので工程時間を縮小できる。

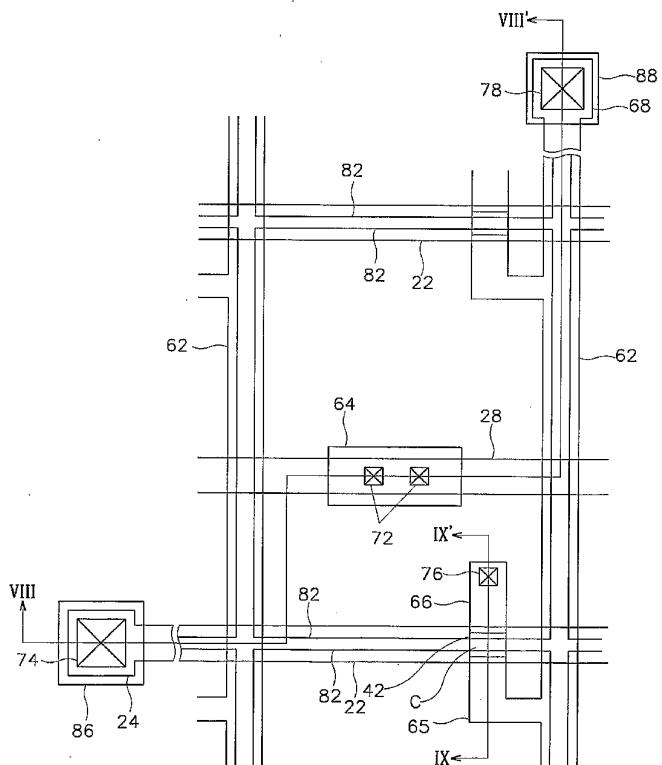

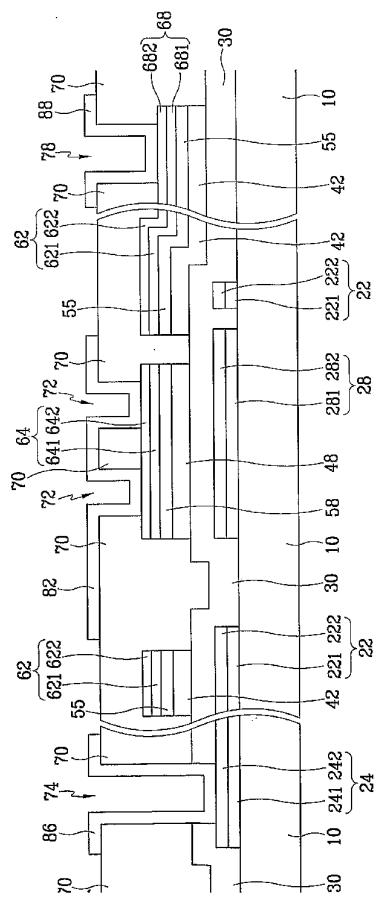

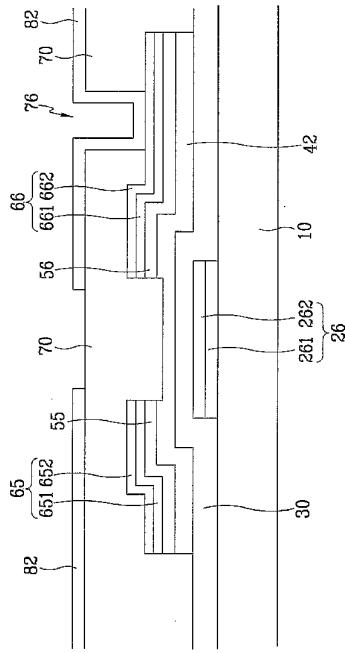

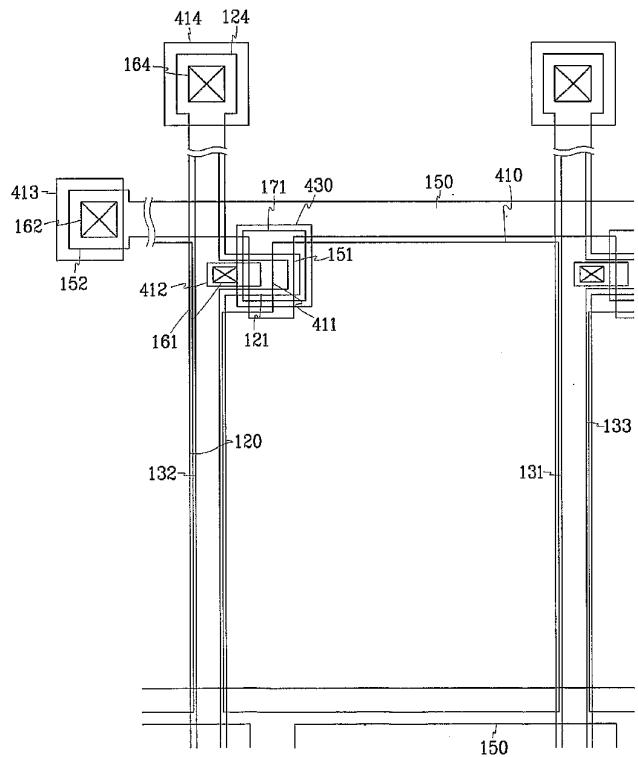

図7は本発明の第2実施例による液晶表示装置用薄膜トランジスタ基板の配置図であり、図8及び図9は各々図7に示した薄膜トランジスタ基板をVIII-VIII'線及びIX-IX'線による断面図である。

## 【0031】

まず、絶縁基板10の上に、第1実施例と同一にCrまたはMo合金などからなる第1ゲ

10

20

30

40

50

ート配線層 221、241、261 または Al または Ag 合金などからなる第 2 ゲート配線層 222、242、262 の二重層からなるゲート配線が形成されている。ゲート配線はゲート線 22、ゲートパッド 24 及びゲート電極 26 を含む。

基板 10 の上にはゲート線 22 と平行に維持電極線 28 が形成されている。維持電極線 28 もまた第 1 ゲート配線層 281 と第 2 ゲート配線層 282 の二重層になっている。維持電極線 28 は後述する画素電極 82 と連結された維持蓄電器用導電体パターン 64 と重なって画素の電荷保存能力を向上させる維持蓄電器をなし、後述する画素電極 82 とゲート線 22 の重なりで発生する維持容量が十分である場合には形成しないこともある。維持電極線 28 には通常、上部基板の共通電極と同じ電圧が印加される。

#### 【0032】

ゲート配線 22、24、26 及び維持電極線 28 の上には窒化シリコン (SiNx) などからなるゲート絶縁膜 30 が形成されてゲート配線 22、24、26、28 を覆っている。

ゲート絶縁膜 30 の上には水素化非晶質シリコン (hydrogenated amorphous silicon) などの半導体からなる半導体パターン 42、48 が形成されており、半導体パターン 42、48 の上にはリン (P) などの n 形不純物が高濃度でドーピングされている非晶質シリコンなどからなる第 1 から第 3 の抵抗性接触層 (ohmic contact layer) パターン 55、56、58 が形成されている。

#### 【0033】

抵抗性接触層パターン 55、56、58 の上には Cr または Mo 合金などからなる第 1 データ配線層 621、641、651、661、681 と、Al または Ag 合金などからなる第 2 データ配線層 622、642、652、662、682 の二重層からなるデータ配線 62、64、65、66、68 が形成されている。データ配線は縦方向に形成されているデータ線 62、データ線 62 の一端に連結されて外部からの画像信号の印加を受けるデータパッド 68、及びデータ線 62 の分枝である薄膜トランジスタのソース電極 65 からなるデータ線部 62、68、65 を含み、また、データ線部 62、68、65 と分離されており、ゲート電極 26 または薄膜トランジスタのチャンネル部 C に対してソース電極 65 の反対側に位置する薄膜トランジスタのドレーン電極 66 と、維持電極線 28 上に位置している維持蓄電器用導電体パターン 64 も含む。維持電極線 28 を形成しない場合には維持蓄電器用導電体パターン 64 も形成しない。

#### 【0034】

データ配線 62、64、65、66、68 は Al または Ag の単一層で形成することもできる。

第 1 から第 3 の接触層パターン 55、56、58 はその下部の半導体パターン 42、48 とその上部のデータ配線 62、64、65、66、68 の接触抵抗を低くする役割を果たし、データ配線 62、64、65、66、68 と完全に同じ形態を有する。つまり、データ線部中間層パターン 55 はデータ線部 62、68、65 と同一で、ドレーン電極用中間層パターン 56 はドレーン電極 66 と同一で、維持蓄電器用中間層パターン 58 は維持蓄電器用導電体パターン 64 と同一である。

#### 【0035】

一方、半導体パターン 42、48 は薄膜トランジスタのチャンネル部 C を除いてはデータ配線 62、64、65、66、68 及び抵抗性接触層パターン 55、56、58 と同じ形態を有している。具体的には、維持蓄電器用半導体パターン 48 と維持蓄電器用導電体パターン 64 及び維持蓄電器用接触層パターン 58 は同じ形態であるが、薄膜トランジスタ用半導体パターン 42 はデータ配線及び接触層パターンの残りの部分と多少異なる。つまり、チャンネル部 C でデータ線部 62、68、65、特にソース電極 65 とドレーン電極 66 が分離されており、第 1 及び第 2 の抵抗接触層 55、56 も分離されているが、薄膜トランジスタ用半導体パターン 42 はこのところで切れずに連結されて薄膜トランジスタのチャンネルを生成する。

#### 【0036】

データ配線 62、64、65、66、68 上にはPECVD 法によって蒸着された a-S

10

20

30

40

50

i : C : O 膜または a - Si : O : F 膜 ( 低誘電率 CVD 膜 ) からなる保護膜 70 が形成されている。PECVD 法によって蒸着された a - Si : C : O 膜と a - Si : O : F 膜 ( 低誘電率 CVD 膜 ) は誘電定数が 4 以下であって誘電率が非常に低い。従って、厚さが薄くても寄生容量問題が発生しない。また、他の膜との接着性及び段差被覆性が優れている。さらに、無機質 CVD 膜であるので耐熱性が有機絶縁膜に比べて優れている。同時に、PECVD 法によって蒸着された a - Si : C : O 膜と a - Si : O : F 膜 ( 低誘電率 CVD 膜 ) は蒸着速度や蝕刻速度が窒化シリコン膜に比べて 4 ~ 10 倍速いので、工程時間面でも非常に有利である。

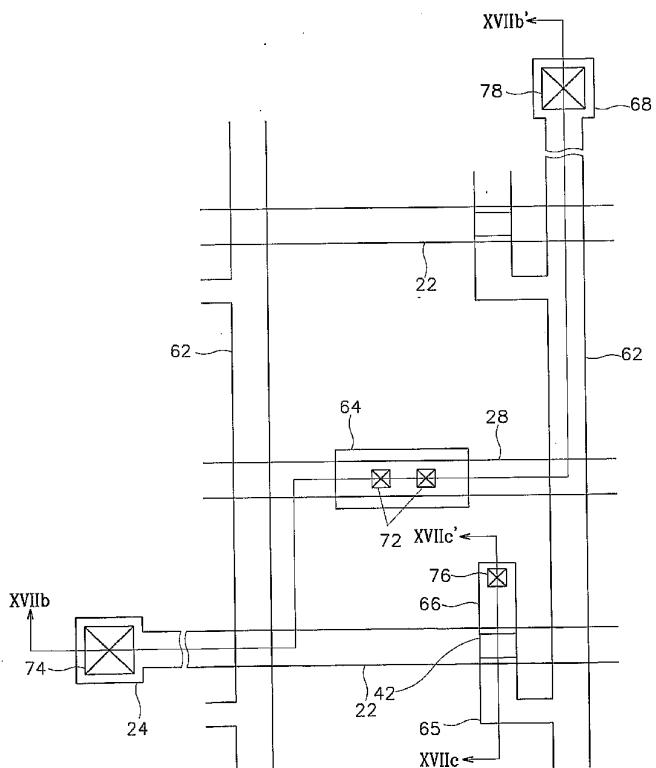

### 【 0037 】

保護膜 70 はドレーン電極 66 、データパッド 68 及び維持蓄電器用導電体パターン 64 を露出させる接触孔 76 、 78 、 72 を有しており、また、ゲート絶縁膜 30 と共にゲートパッド 24 を露出させる接触孔 74 を有している。

保護膜 70 上には薄膜トランジスタから画像信号を受けてカラーフィルター基板の共通電極と共に電場を生成する画素電極 82 が形成されている。画素電極 82 は ITO または IZO などの透明な導電物質で形成され、ドレーン電極 66 と物理的、電気的に連結されて画像信号の伝達を受ける。また、画素電極 82 は隣接するゲート線 22 及びデータ線 62 と重なって開口率を高めているが、重ならないこともある。また、画素電極 82 は接触孔 72 を通じて維持蓄電器用導電体パターン 64 とも連結されて導電体パターン 64 に画像信号を伝達する。一方、ゲートパッド 24 及びデータパッド 68 上には接触孔 74 、 78 を通じて各々これらと連結される補助ゲートパッド 86 及び補助データパッド 88 が形成されており、これらはパッド 24 、 68 と外部回路装置との接着性を補完しパッドを保護する役割を果たすもので必須なものではなく、これらの適用如何は選択的である。

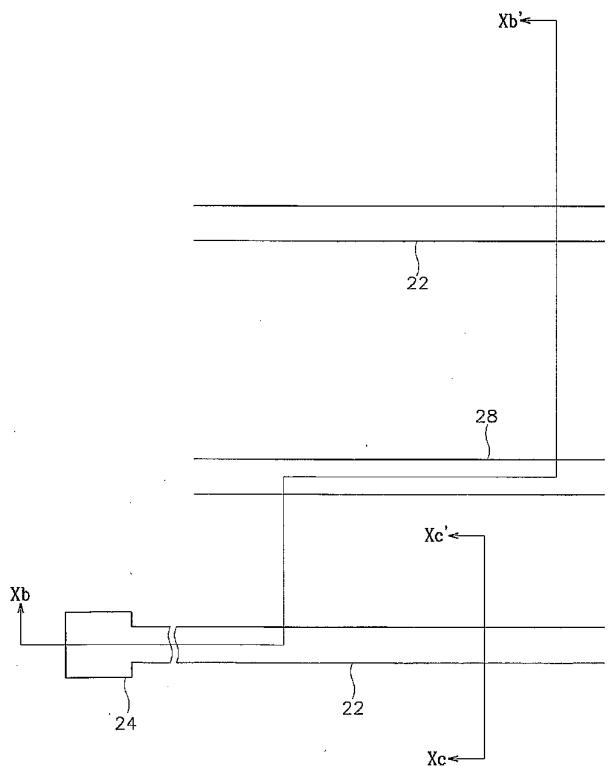

### 【 0038 】

以下、薄膜トランジスタ基板を 4 枚のマスクを用いて製造する方法について、詳細に図 10a 乃至図 17c を参照して説明する。

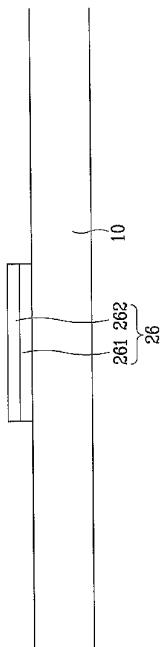

まず、図 10a 乃至 10c に示したように、Cr または Mo 合金などを基板 10 に蒸着して第 1 ゲート配線層 221 、 241 、 261 、 281 を積層し、Al または Ag 合金などを蒸着して第 2 ゲート配線層 222 、 242 、 262 、 282 を積層した後、写真蝕刻してゲート線 22 、ゲートパッド 24 、ゲート電極 26 を含むゲート配線と維持電極線 28 を形成する。

### 【 0039 】

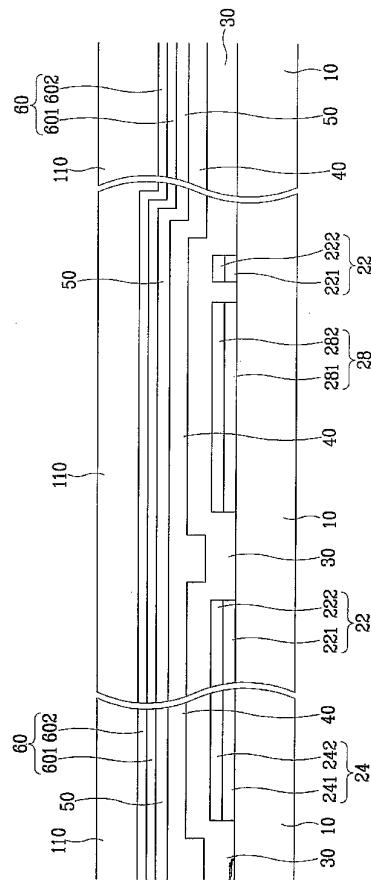

その後、図 11a 及び 11b に示したように、ゲート絶縁膜 30 、半導体層 40 、中間層 50 を化学気相蒸着法を用いて各々 1,500 乃至 5,000 、 500 乃至 2,000 、 300 乃至 600 の厚さで連続蒸着し、次いで、Cr または Mo 合金などからなる第 1 導電膜 601 と Al または Ag 合金からなる第 2 導電膜 602 をスパッタリングなどの方法で抵抗接觸層 50 に蒸着して導電体層 60 を形成した後、その上に感光膜 110 を 1 乃至 2  $\mu\text{m}$  の厚さで塗布する。

### 【 0040 】

その後、マスクを通して感光膜 110 に光を照射した後、現像して、図 12b 及び 12c に示したように、感光膜パターン 112 、 114 を形成する。この時、感光膜パターン 112 、 114 の中にチャンネル部 C 、即ち、ソース電極 65 とドレーン電極 66 の間に位置した第 1 部分 114 は第 2 部分 112 より厚さを薄くするようにし、その他の部分 B の感光膜は全て除去する。この時、チャンネル部 C に残っている感光膜 114 の厚さとデータ配線部 A に残っている感光膜 112 の厚さの比は後述する蝕刻工程での工程条件によって異なるようにしなければならず、第 1 部分 114 の厚さを第 2 部分 112 の厚さの 1/2 以下とするのが好ましく、例えば、4,000 以下であるのがよい。

### 【 0041 】

このように、位置によって感光膜の厚さを異にする方法としては多様なものが有り得、a 領域の光透過量を調節するために主にスリット (slit) または格子形態のパターンを形成したり半透明膜を使用する。

10

20

30

40

50

この時、スリットの幅は露光時に使用する露光器の分解能より小さいのが好ましく、半透明膜を利用する場合にはマスクを製作する時に透過率を調節するために異なる透過率を有する薄膜を利用したり厚さの異なる薄膜を利用できる。

【0042】

このようなマスクを通して感光膜に光を照射すると光に直接露出される部分では高分子が完全に分解され、スリットパターンまたは半透明膜が形成されている部分では光の照射量が少ないので高分子は完全分解されていない状態であり、遮光幕で遮った部分では高分子が殆ど分解されない。次いで、感光膜を現像すると、高分子の分子が分解されない部分のみが残り、光が少なく照射された中央部分には光に全く照射されない部分より厚さの薄い感光膜を残せる。この時、露光時間を長くすると全ての分子が分解されるので、そうならないようにしなければならない。

【0043】

このような、厚さの薄い感光膜114は、リフローの可能な物質で作られた感光膜を利用し、光が完全に透過できる部分と光が完全に透過できない部分とに分けられた通常のマスクで露光した後に現像し、リフローさせて、感光膜が残留しない部分に感光膜の一部を流れ落ちるようにすることによって、形成することもできる。

次いで、感光膜パターン114及びその下部の膜、即ち、導電体層60、中間層50及び半導体層40に対する蝕刻を進める。この時、データ配線部Aにはデータ配線及びその下部の膜がそのまま残っており、チャンネル部Cには半導体層のみが残っていなければならず、残りの部分Bには上の3個の層60、50、40が全て除去されてゲート絶縁膜30が露出されなければならない。

【0044】

まず、図13a及び13bに示したように、その他の部分Bの露出されている導電体層60を除去してその下部の中間層50を露出させる。この過程では乾式蝕刻または湿式蝕刻法の両方を使用でき、この時、導電体層60は蝕刻され感光膜パターン112、114は殆ど蝕刻されない条件下で行うのが好ましい。しかし、乾式蝕刻の場合、導電体層60のみを蝕刻し感光膜パターン112、114は蝕刻されない条件を探すことが難しく、感光膜パターン112、114も共に蝕刻される条件下で行える。この場合には湿式蝕刻の場合より第1部分114の厚さを厚くしてこの過程で第1部分114が除去されて下部の導電体層60が露出されることが発生しないようとする。

【0045】

このようにすると、図13a及び図13bに示したように、チャンネル部C及びデータ配線部Bの導電体層、即ち、ソース/ドレーン用導電体パターン67と維持蓄電器用導電体パターン68のみが残り、他の部分Bの導電体層60は全て除去されてその下部の中間層50が露出される。この時に残った導電体パターン67、64はソース及びドレーン電極65、66が分離されずに連結されている点を除いてはデータ配線62、64、65、66、68の形態と同一である。また、乾式蝕刻を使用した場合、感光膜パターン112、114もある程度の厚さで蝕刻される。

【0046】

次いで、図14a及び14bに示したように、他の部分Bの露出された中間層50及びその下部の半導体層40を感光膜の第1部分114と共に乾式蝕刻法で同時に除去する。この時の蝕刻は感光膜パターン112、114と中間層50及び半導体層40が同時に蝕刻されゲート絶縁膜30は蝕刻されない条件下で行わなければならず、特に感光膜パターン112、114と半導体層40に対する蝕刻比が殆ど同じ条件で蝕刻するのが好ましい。例えば、SF6とHCLの混合気体、またはSF6とO2の混合気体を用いると殆ど同じ厚さで二つの膜を蝕刻できる。感光膜パターン112、114と半導体層40に対する蝕刻比が同じ場合、第1部分114の厚さは半導体層40と中間層50の厚さを合わせたものと同じか、それより小さくなければならない。

【0047】

このようにすると、図14a及び14bに示したように、チャンネル部Cの第1部分11

10

20

30

40

50

4 が除去されてソース / ドレーン用導電体パターン 6 7 が露出され、その他の部分 B の中間層 5 0 及び半導体層 4 0 が除去されてその下部のゲート絶縁膜 3 0 が露出される。一方、データ配線部 A の第 2 部分 1 1 2 も蝕刻されるので厚さが薄くなる。また、この段階で半導体パターン 4 2 、 4 8 が完成する。図面符号 5 7 と 5 8 は各々ソース / ドレーン用導電体パターン 6 7 下部の中間層パターンと維持蓄電器用導電体パターン 6 4 下部の中間層パターンを指す。

#### 【 0 0 4 8 】

次いで、灰化処理 (ashing) を通じてソース / ドレーン用導電体パターン 6 7 の表面に残っている感光膜クズを除去する。

その次、図 1 5 a 及び 1 5 b に示したように、チャンネル部 C のソース / ドレーン用導電体パターン 6 7 及びその下部の中間層パターン 5 7 を蝕刻して除去する。この時、蝕刻はソース / ドレーン用導電体パターン 6 7 と中間層パターン 5 7 の両方に対して乾式蝕刻のみで行え、ソース / ドレーン用導電体パターン 6 7 に対しては湿式蝕刻で、中間層パターン 5 7 に対しては乾式蝕刻で行うこともできる。前者の場合、ソース / ドレーン用導電体パターン 6 7 と中間層パターン 5 7 の蝕刻選択比が大きい条件下で蝕刻を行うのが好ましく、これは蝕刻選択比が大きくない場合には蝕刻終点を探すことが難しいのでチャンネル部 C に残る半導体パターン 4 2 の厚さを調節することが容易ではないためである。湿式蝕刻と乾式蝕刻を交互にする後者の場合には湿式蝕刻されるソース / ドレーン用導電体パターン 6 7 の側面は蝕刻されるが、乾式蝕刻される中間層パターン 5 7 は殆ど蝕刻されないので階段形態に形成される。蝕刻気体の例としては C F 4 と H C L の混合気体または C F 4 と O 2 の混合気体があり、C F 4 と O 2 を使用すると均一な厚さで半導体パターン 4 2 を残せる。この時、図 1 5 b に示したように、半導体パターン 4 2 の一部が除去されて厚さを薄くでき、感光膜パターンの第 2 部分 1 1 2 もこの時ある程度の厚さで蝕刻される。この時の蝕刻はゲート絶縁膜 3 0 が蝕刻されない条件で行わなければならず、第 2 部分 1 1 2 が蝕刻されてその下部のデータ配線 6 2 、 6 4 、 6 5 、 6 6 、 6 8 が露出されることがないように厚い感光膜パターンが好ましいことは当然である。

#### 【 0 0 4 9 】

このようにすると、ソース電極 6 5 とドレーン電極 6 6 が分離されデータ配線 6 2 、 6 4 、 6 5 、 6 6 、 6 8 とその下部の接触層パターン 5 5 、 5 6 、 5 8 が完成する。

最後にデータ配線部 A に残っている感光膜第 2 部分 1 1 2 を除去する。しかし、第 2 部分 1 1 2 の除去はチャンネル部 C ソース / ドレーン用導電体パターン 6 7 を除去した後、その下の中間層パターン 5 7 を除去する前に行われることもできる。

#### 【 0 0 5 0 】

前述のように、ドライエッティングのみの場合には一つの種類の蝕刻のみを使用するので工程が比較的に簡便であるが、適当な蝕刻条件を探すことが難しい。反面、前者の場合には蝕刻条件を探すことが比較的に容易であるが、工程が後者に比べて面倒な点がある。

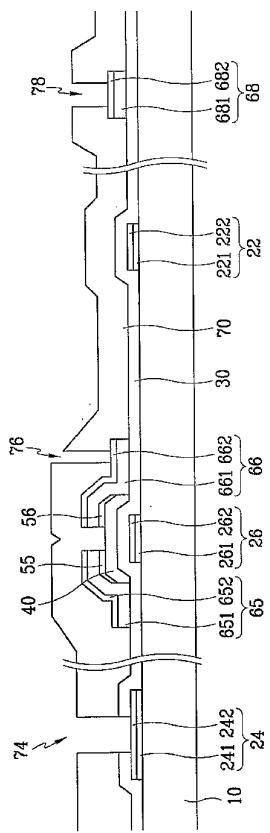

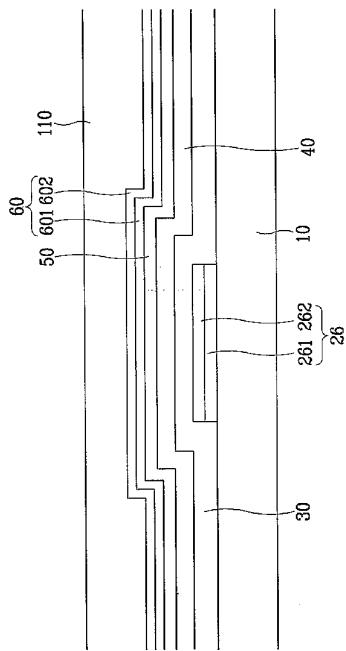

その次、図 1 6 a 及び図 1 6 b に示したように、a - S i : C : O 膜または a - S i : O : F 膜を化学気相蒸着 ( C V D ) 法によって成長させて保護膜 7 0 を形成する。この時、a - S i : C : O 膜の場合は気体状態の S i H ( C H 3 ) 3 、 S i O 2 ( C H 3 ) 4 、 ( S i H ) 4 O 4 ( C H 3 ) 4 、 S i ( C 2 H 5 O ) 4 などを基本ソースとして使用し、N 2 O または O 2 などの酸化剤と A r または H e などを混合した気体を流しながら蒸着する。また、a - S i : O : F 膜の場合は S i H 4 、 S i F 4 等に O 2 を添加した気体を流しながら蒸着する。この時、フッ素の補助ソースとして C F 4 を添加することもできる。

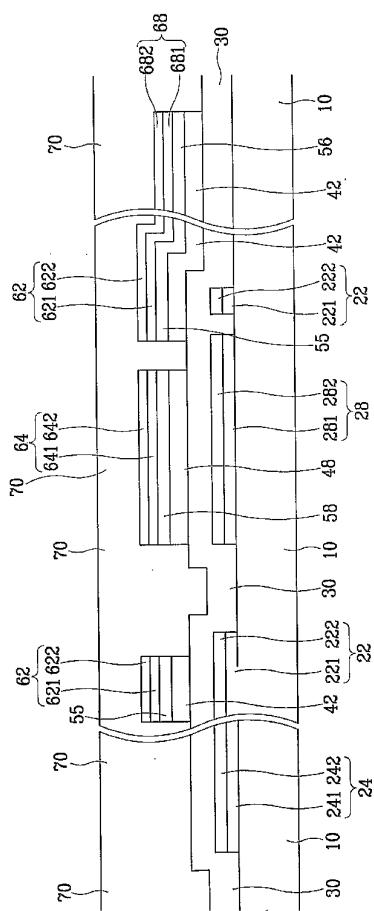

#### 【 0 0 5 1 】

次いで、図 1 7 a 乃至図 1 7 c に示したように、保護膜 7 0 をゲート絶縁膜 3 0 と共に写真蝕刻してドレーン電極 6 6 、ゲートパッド 2 4 、データパッド 6 8 及び維持蓄電器用導電体パターン 6 4 を各々露出する接触孔 7 6 、 7 4 、 7 8 、 7 2 を形成する。この時、パッド 2 4 、 6 8 を露出する接触孔 7 4 、 7 8 の面積は 2 m m × 6 0 μ m を超えず、0 . 5 m m × 1 5 μ m 以上であるのが好ましい。

#### 【 0 0 5 2 】

10

20

30

40

50

最後に、図8乃至10に示したように、400乃至500の厚さのITO層またはIZO層を蒸着し写真蝕刻してドレーン電極66及び維持蓄電器用導電体パターン64に連結された画素電極82、ゲートパッド24に連結された補助ゲートパッド86、及びデータパッド68に連結された補助データパッド88を形成する。

この時、画素電極82、補助ゲートパッド86及び補助データパッド88をIZOで形成する場合には蝕刻液としてクロム蝕刻液を使用できるので、これらを形成するための蝕刻過程で接触孔を通じて露出されたデータ配線やゲート配線金属が腐食されることを防止できる。このようなクロム蝕刻液としては(HNO<sub>3</sub> / (NH<sub>4</sub>)<sub>2</sub>CrO<sub>4</sub> / H<sub>2</sub>O)などがある。また、接触部の接触抵抗を最少化するためにはIZOを常温から200以下の範囲で積層するのが好ましく、IZO薄膜を形成するために使用するターゲットはIn<sub>2</sub>O<sub>3</sub>及びZnOを含むのが好ましく、ZnOの含有量は15~20%範囲であるのが好ましい。10

#### 【0053】

一方、ITOまたはIZOを積層する前の予熱工程で使用する気体としては窒素を使用するのが好ましく、これは接触孔72、74、76、78を通じて露出された金属膜24、64、66、68の上部に金属酸化膜が形成されることを防止するためである。

このような本発明の第2実施例では第1実施例による効果だけでなくデータ配線62、64、65、66、68とその下部の接触層パターン55、56、58及び半導体パターン42、48を一つのマスクを用いて形成し、この過程でソース電極65とドレーン電極66を分離することによって製造工程を単純化できる。20

#### 【0054】

本発明によるCVDで形成したa-Si:C:O膜またはa-Si:O:F膜(低誘電率CVD膜)は色フィルター上に薄膜トランジスタアレイを形成するAOC(array on color filter)構造で色フィルターと薄膜トランジスタを分離するバッファー層として使用しても有用である。

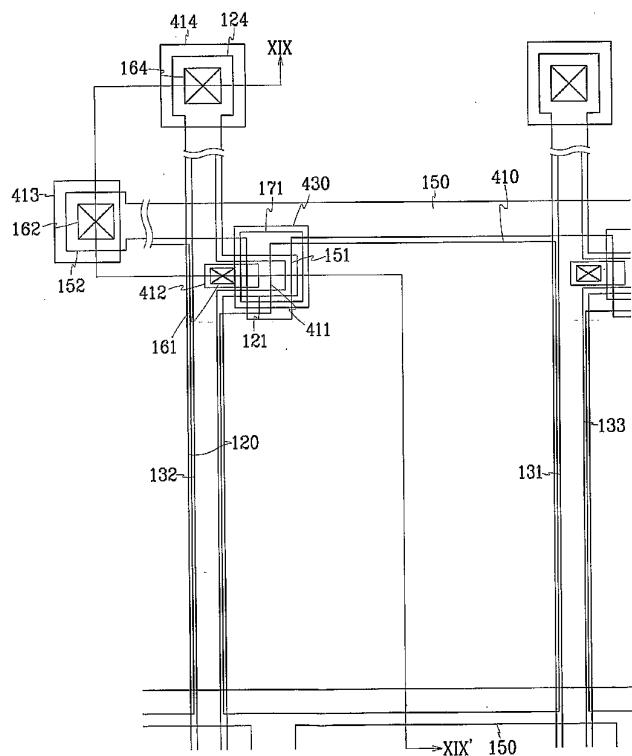

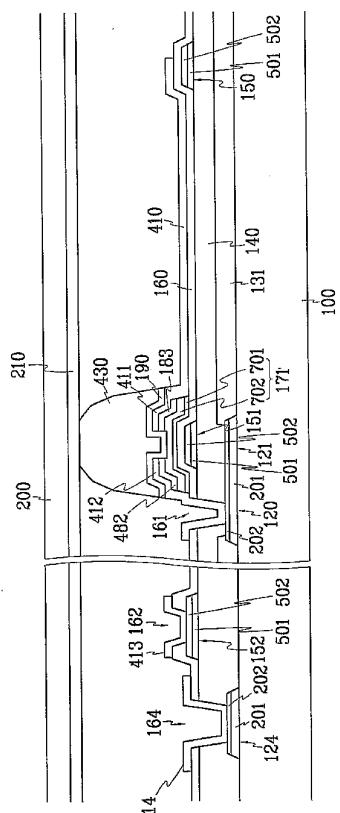

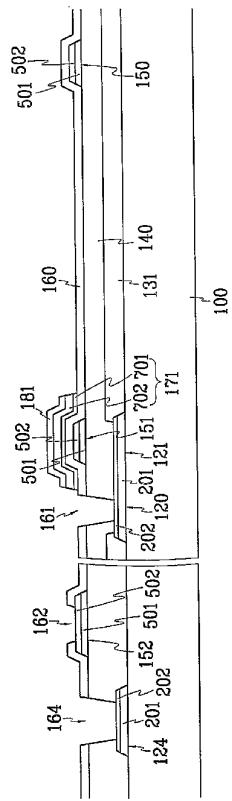

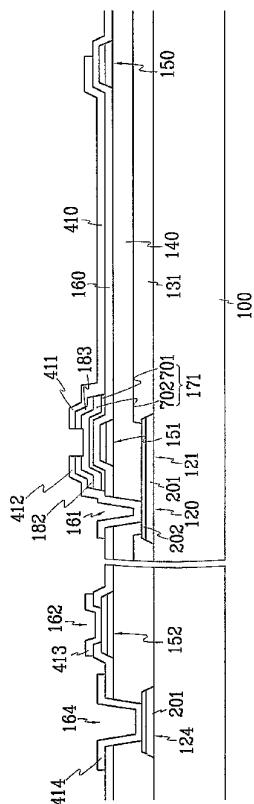

図18は本発明の第3実施例による薄膜トランジスタ基板の配置図であり、図19は、図18に示した薄膜トランジスタ基板を、切断線XIX-XIXに沿って示した断面図である。図19には薄膜トランジスタ基板である下部基板とこれと対向する上部基板を共に示した。

#### 【0055】

まず、下部基板には、絶縁基板100の上部に銅、銅合金、銀、銀合金、アルミニウム及びアルミニウム合金などの物質のうちのいずれかの一つからなる下層201とクロム、モリブデン、モリブデン合金、窒化クロム及び窒化モリブデンなどの物質のうちのいずれかの一つからなる上層201を含むデータ配線120、121、124が形成されている。30

#### 【0056】

データ配線120、121、124は縦方向に伸びているデータ線120、データ線120の端に連結されていて外部から画像信号の伝達を受けてデータ線120に伝達するデータパッド124、及びデータ線120の分枝であって基板100の下部から薄膜トランジスタの半導体層170に入射する光を遮断する光遮断部121を含む。ここで、光遮断部121は漏洩する光を遮断するブラックマトリックスの機能も共に有し、データ線120から分離して断絶された配線として形成できる。40

#### 【0057】

データ配線120、121、124は二重膜で形成されているが、銅または銅合金またはアルミニウム(AI)またはアルミニウム合金(AI alloy)、モリブデン(Mo)またはモリブデン-タンゲステン(MoW)合金、クロム(Cr)、タンタル(Ta)などの導電物質からなる単一膜で形成することもできる。

ここでは、データ配線120、121、124は、この後に形成される画素配線410、411、412及び補助パッド413、414がITOであることを考慮して、下層201を抵抗の小さい物質で形成し、上層202は異なる物質、特にITOとの接触特性が良い物質で形成した場合を例示した。具体的な例として、下層201をAI-Ndで形成し、上層202をCrNxで形成できる。50

## 【0058】

画素配線 410、411、412 及び補助パッド 413、414 が IZO である場合にはデータ配線 120、121、124 をアルミニウムまたはアルミニウム合金の単一膜で形成するのが好ましく、銅が IZO 及び ITO との接触特性に優れているので銅の単一膜で形成することもできる。

下部絶縁基板 100 の上には端部がデータ配線 120、121 の端部と重なる赤 (R)、緑 (G)、青 (b) の色フィルター 131、132、133 が各々形成されている。ここで、色フィルター 131、132、133 はデータ線 120 を全て覆うように形成できる。

## 【0059】

データ配線 120、121、124 及び色フィルター 131、132、133 上には PE CVD 法によって蒸着された a-Si:C:O 膜または a-Si:O:F 膜 (低誘電率 CVD 膜) からなるバッファー層 140 が形成されている。ここで、バッファー層 140 は色フィルター 131、132、133 からのガス放出を防止して色フィルター自体が後続工程での熱及びプラズマエネルギーによって損傷することを防止するための層である。また、バッファー層 140 は最下部のデータ配線 120、121、124 と薄膜トランジスタアレイを分離しているので誘電率が低く厚さが厚いほど有利である。このような点を考慮すると、PECVD 法によって蒸着された a-Si:C:O 膜または a-Si:O:F 膜 (低誘電率 CVD 膜) はバッファー層 140 として使用するのに適格である。つまり、誘電率が低く、蒸着速度が非常に速く、BCB (bisbenzocyclobutene) または PFCB (perfluorocyclobutene) などの有機絶縁物質に比べて価格が安い。また、a-Si:O:C 薄膜は常温から 400 に至る広い温度範囲で優れた絶縁特性を有する。

## 【0060】

バッファー層 140 上には上部に銅、銅合金、銀、銀合金、アルミニウム及びアルミニウム合金などの物質のうちのいずれかの一つからなる下層 501 とクロム、モリブデン、モリブデン合金、窒化クロム、窒化モリブデンなどの物質のうちのいずれかの一つからなる上層 502 を含む二重層構造のゲート配線が形成されている。

ゲート配線は横方向に伸びてデータ線 120 と交差して単位画素を定義するゲート線 150、ゲート線 150 の端に連結されており、外部からの走査信号の印加を受けてゲート線 150 に伝達するゲートパッド 152、及びゲート線 150 の一部である薄膜トランジスタのゲート電極 151 を含む。

## 【0061】

ここで、ゲート線 150 は後述する画素電極 410 と重なって画素の電荷保存能力を向上させる維持蓄電器を構成し、後述する画素電極 410 とゲート線 150 の重なりで発生する維持容量が十分でない場合には維持容量用共通電極を形成することもできる。

このように、ゲート配線を二重層以上に形成する場合には一層は抵抗が小さい物質で形成し、他の層は異なる物質との接触特性の良い物質で形成することが好ましく、Al (または Al 合金) \ Cr の二重層または Cu \ Cr の二重層がその例である。また、接触特性を改善するために窒化クロム膜または窒化モリブデン膜などを追加することもできる。

## 【0062】

ゲート配線 150、151、152 は低抵抗を有する銅またはアルミニウムまたはアルミニウム合金などの単一膜で形成することもできる。

ゲート配線 150、151、152 及びバッファー層 140 上には低温蒸着ゲート絶縁膜 160 が形成されている。この時、低温蒸着ゲート絶縁膜 160 は有機絶縁膜、低温非晶質酸化シリコン膜、低温非晶質窒化シリコン膜等で形成できる。本発明による薄膜トランジスタ構造では色フィルターが下部基板に形成されるので、ゲート絶縁膜は、高温蒸着される通常の絶縁膜とは異なる低温蒸着可能な、例えば、250 以下の低温条件で蒸着が可能な低温蒸着絶縁膜を使用する。

## 【0063】

そして、ゲート電極 151 のゲート絶縁膜 160 上には二重層構造の半導体層 171 が島

10

20

30

40

50

模様に形成されている。二重層構造の半導体層 171において、下層半導体層 701はバンドギャップが高い非晶質シリコンからなり、上層半導体層 702は下層半導体 701に比べてバンドギャップの低い通常の非晶質シリコンからなる。例えば、下層半導体層 701のバンドギャップを 1.9~2.1 eV に、上層半導体層 702のバンドギャップを 1.7~1.8 eV にして形成できる。ここで、下層半導体層 701は 50~200 の厚さで形成し、上層半導体層 702は 1000~2000 の厚さで形成する。

#### 【0064】

このように、バンドギャップが互いに異なる上層半導体層 702と下層半導体層 701の間には両層のバンドギャップの差に相当するだけのバンドオフセットが形成される。この時、TFTがオン(ON)状態になると、二つの半導体層 701、702の間に位置するバンドオフセット領域にチャンネルが形成される。このバンドオフセット領域は基本的に同じ原子構造を有していて、欠陥が少ないので良好な TFT の特性を期待できる。

#### 【0065】

半導体層 171は単一層で形成することもできる。

半導体層 171上にはリン(P)などのn形不純物が高濃度でドーピングされている非晶質シリコンまたは微細結晶化されたシリコンまたは金属シリサイドなどを含む抵抗性接触層 182、183が互いに分離されて形成されている。

抵抗性接触層 182、183上にはITOからなるソース用及びドレーン用電極 412、411及び画素電極 410を含む画素配線 410、411、412が形成されている。ソース用電極 412はゲート絶縁膜 160及びバッファー層 140に形成されている接触孔 161を通じてデータ線 120と連結されている。ドレーン用電極 411は画素電極 410と連結されており、薄膜トランジスタから画像信号を受けて画素電極 410に伝達する。画素配線 410、411、412はITOまたはIZOなどの透明な導電物質で形成される。

#### 【0066】

また、画素配線 410、411、412と同一層には接触孔 162、164を通じてゲートパッド 152及びデータパッド 124と各々連結されている補助ゲートパッド 413及び補助データパッド 414が形成されている。ここで、補助ゲートパッド 413はゲートパッド 152の上部膜 502であるクロム膜と直接接触しており、補助データパッド 414もデータパッド 124の上部膜 202であるクロム膜と直接接触している。この時、ゲートパッド 152及びデータパッド 124が窒化クロム膜または窒化モリブデン膜を含む場合には補助ゲートパッド 413及び補助データパッド 414は窒化クロム膜または窒化モリブデン膜と接触するのが好ましい。これらはパッド 152、124と外部回路装置との接着性を補完してパッドを保護する役割を果たすものであって、必須なものではなく、これらの適用如何は選択的である。また、画素電極 410は隣接するゲート線 150及びデータ線 120と重なって開口率を高めているが、重ならないこともある。

#### 【0067】

ここで、抵抗性接触層 182、183はITOのソース用及びドレーン用電極 412、411と半導体層 171の間の接触抵抗を減らす機能を有し、微細結晶化されたシリコン層またはモリブデン、ニッケル、クロムなどの金属シリサイドが含まれることができ、シリサイド用金属膜が残留することもできる。

ソース用及びドレーン用電極 412、411の上部には薄膜トランジスタを保護するための保護膜 190が形成されており、その上部には光吸収が優れた濃厚な色を有する感光性有色有機膜 430が形成されている。この時、有色有機膜 430は薄膜トランジスタの半導体層 171に入射する光を遮断する役割を果たし、有色有機膜 430の高さを調節して下部絶縁基板 100とこれと対向する上部絶縁基板 200の間の間隔を維持するスペーサとして用いられる。ここで、保護膜 190と有機膜 430はゲート線 150とデータ線 120に沿って形成でき、有機膜 430はゲート配線とデータ配線の周囲から漏洩する光を遮断する役割を果たせる。

#### 【0068】

10

20

30

40

50

この時、有機膜 430 が、画素電極及び各金属層との隙間を全て覆うように設計される場合には上部基板に光遮断のための別途のブラックマトリックスを設計する必要がないという長所がある。

一方、上部基板 200 には ITO または IZO からなり、画素電極 410 と共に電場を生成する共通電極 210 が全面的に形成されている。

#### 【0069】

以下、薄膜トランジスタ基板の製造法について図 20a 乃至 28b を参照して詳細に説明する。

まず、図 20a と 20b に示したように、アルミニウムまたはアルミニウム合金または銅または銅合金などのように低抵抗を有する導電物質とクロムまたはモリブデンまたはチタニウムまたは窒化クロムまたは窒化モリブデンなどのような ITO との接触特性が優れた導電物質を順次にスパッタリングなどの方法で蒸着し、マスクを用いた写真蝕刻工程で乾式または湿式蝕刻して、下部絶縁基板 100 上に下層 201 と上層 202 の二重層構造になっているデータ線 120、データパッド 124 及び光遮断部 121 を含むデータ配線 120、121、124 を形成する。

#### 【0070】

前述のように、この後に形成される画素配線 410、411、412 及び補助パッド 413、414 が ITO であることを考慮して、アルミニウムまたはアルミニウム合金または銅または銅合金の下層 201 とクロムまたはモリブデンまたはチタニウムの上層 202 とからなるデータ配線を形成したが、画素配線 410、411、412 及び補助パッド 413、414 が IZO である場合にはアルミニウムまたはアルミニウム合金の単一膜で形成できる。

#### 【0071】

次に、図 21a 及び図 21b に示したように、赤 (R)、緑 (G)、青 (B) の顔料を含む感光性物質を順次に塗布し、写真工程でパターニングして、赤 (R)、緑 (G)、青 (B) の色フィルター 131、132、133 を順次に形成する。この時、赤 (R)、緑 (G)、青 (B) の色フィルター 131、132、133 は三枚のマスクを用いて形成するが、一つのマスクを移動しながら形成することもできる。また、レーザー転写法またはプリント法を利用するとマスクを使用せずに形成することもできる。この時、赤 (R)、緑 (G)、青 (B) の色フィルター 131、132、133 の端部はデータ線 120 と重なるように形成するのが好ましい。

#### 【0072】

次に、図 22a 及び図 22b のように、絶縁基板 100 上部に a-Si:C:O 膜または a-Si:O:F 膜を化学気相蒸着 (CVD) 法によって成長させてバッファー層 140 を形成する。この時、a-Si:C:O 膜の場合には気体状態の SiH (CH<sub>3</sub>)<sub>3</sub>、SiO<sub>2</sub> (CH<sub>3</sub>)<sub>4</sub>、(SiH)<sub>4</sub>O<sub>4</sub> (CH<sub>3</sub>)<sub>4</sub>、Si (C<sub>2</sub>H<sub>5</sub>O)<sub>4</sub>などを基本ソースとして使用し、N<sub>2</sub>O または O<sub>2</sub> などの酸化剤と Ar または He などを混合した気体を流しながら蒸着する。また、a-Si:O:F 膜の場合には SiH<sub>4</sub>、SiF<sub>4</sub> 等に O<sub>2</sub> を添加した気体を流しながら蒸着する。この時、フッ素の補助ソースとして CF<sub>4</sub> を添加することもできる。

#### 【0073】

次に、クロムまたはモリブデンまたはチタニウムまたは窒化クロムまたは窒化モリブデンなどの物理化学的に安定した物質とアルミニウムまたはアルミニウム合金または銅または銅合金などのように低抵抗を有する導電物質をスパッタリングなどの方法で連続蒸着しマスクを用いた写真蝕刻工程でパターニングして、バッファー層 140 上にゲート線 150、ゲート電極 151 及びゲートパッド 152 を含むゲート配線 150、151、152 を形成する。

#### 【0074】

この時、ゲート配線 150、151、152 は単一層構造で形成できる。

次に、図 23 に示したように、ゲート配線 150、151、152 及び有機絶縁膜 140

10

20

30

40

50

上に低温蒸着ゲート絶縁膜160、第1非晶質シリコン膜701、第2非晶質シリコン膜702及び不純物がドーピングされた非晶質シリコン膜180を順次に蒸着する。

低温蒸着ゲート絶縁膜160は250以下 の蒸着温度でも蒸着できる有機絶縁膜、低温非晶質酸化シリコン膜、低温非晶質窒化シリコン膜などを使用して形成できる。

#### 【0075】

第1非晶質シリコン膜701はバンドギャップが高い、例えば1.9~2.1eVのバンドギャップを有する非晶質シリコン膜で形成し、第2非晶質シリコン膜702はバンドギャップが第1非晶質シリコン膜701よりは低い、例えば1.7~1.8eVのバンドギャップを有する通常の非晶質シリコン膜で形成する。この時、第1非晶質シリコン膜701は非晶質シリコン膜の原料ガスであるSiH4にCH4、C2H2、または、C2H6等を適切な量で添加してCVD法によって蒸着できる。例えば、CVD装置にSiH4:CH4を1:9の割合で投入し、蒸着工程を進めると、Cが50%程度含まれ、2.0~2.3eVのバンドギャップを有する非晶質シリコン膜を蒸着できる。このように、非晶質シリコン層のバンドギャップは蒸着工程条件から影響を受けるが、炭素化合物の添加量によって大体1.7~2.5eV範囲でバンドギャップを容易に調節できる。

この時、低温蒸着ゲート絶縁膜160、第1非晶質シリコン膜701及び第2非晶質シリコン膜702、不純物がドーピングされた非晶質シリコン膜180は同じCVD装置で真空を維持したまま連続的に蒸着できる。

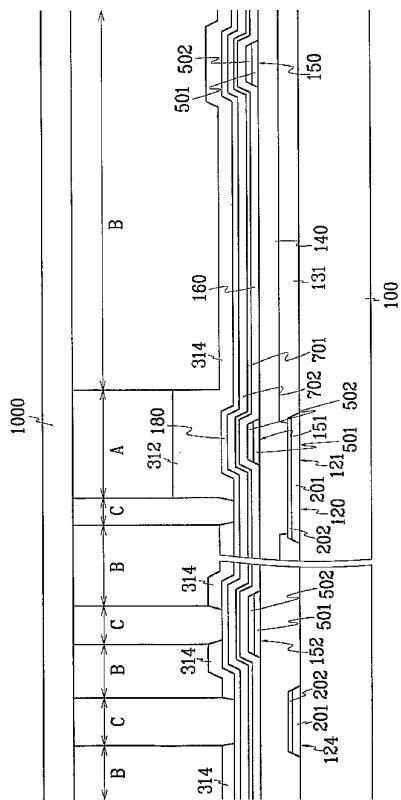

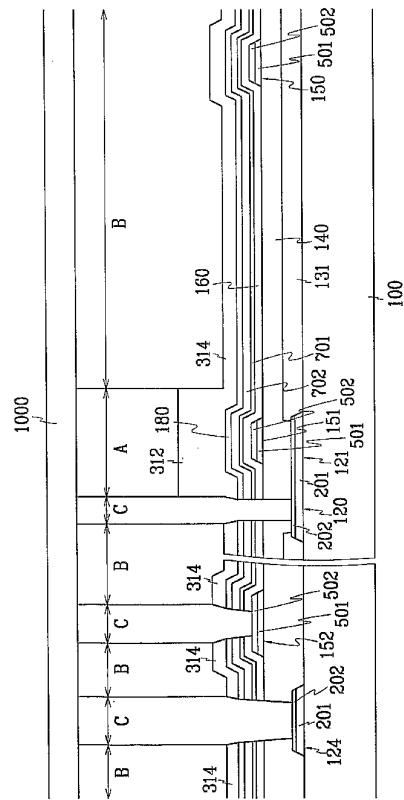

次に、図24a及び24bに示したように、第1非晶質シリコン膜701、第2非晶質シリコン膜702及び不純物がドーピングされた非晶質シリコン膜180を写真蝕刻工程で20パターニングして島模様の半導体層171及び抵抗性接触層181を形成し、同時に、低温蒸着ゲート絶縁膜160と有機絶縁膜140にデータ線120、ゲートパッド152及びデータパッド124を各々露出させる接触孔161、162、164を形成する。

この時、ゲート電極151の上部を除いた部分では第1、第2非晶質シリコン膜701、702及び不純物がドーピングされた非晶質シリコン膜180を全て除去しなければならず、ゲートパッド152上部では第1及び、第2非晶質シリコン膜701、702及び不純物がドーピングされた非晶質シリコン膜180と共にゲート絶縁膜160も除去しなければならず、データ線120及びデータパッド124上部では第1及び第2非晶質シリコン膜701、702、不純物がドーピングされた非晶質シリコン膜180及び低温蒸着ゲート絶縁膜160と共に有機絶縁膜140も除去しなければならない。

#### 【0076】

これを一つのマスクを利用した写真蝕刻工程で形成するためには、部分的に異なる厚さを有する感光膜パターンを蝕刻マスクとして用いなければならない。これについて図25と図26を参照して説明する。

まず、図25に示したように、不純物がドーピングされた非晶質シリコン膜180の上部に感光膜を1乃至2μmの厚さで塗布した後、マスクを利用した感光膜に光を照射して現像し、感光膜パターン312、314を形成する。

#### 【0077】

この時、感光膜パターン312、314の中でゲート電極151の上部に位置した第1部分312は他の第2部分314より厚さが厚くなるように形成し、データ線120、データパッド124及びゲートパッド152の一部の上には感光膜が存在しないようにする。第2部分314の厚さを第1部分312の厚さの1/2以下にすることが好ましく、例えば、4,000以下であるのがよい。

#### 【0078】

このように、位置によって感光膜の厚さを異なるようにする方法は多様にあるが、ここではポジ型感光膜を使用する場合について説明する。

露光器の分解能より小さいパターン、例えば、B領域にスリットや格子形態のパターンを形成したり半透明膜を形成しておくことによって光の照射量が調節できるマスク1000を通じて感光膜に光を照射すると、照射される光の量または強さによって高分子が分解される程度が異なるようになる。この時、光に完全に露出されるC領域の高分子が完全に分

10

20

30

40

50

解される時期に合せて露光を中断すれば、光に完全に露出される部分に比べてスリットや半透明膜が形成されているB領域を通過する光の照射量が少ないので、B領域の感光膜は一部だけが分解されて、残りは分解されない状態で残る。露光時間を長くすると全ての分子が分解される。

【0079】

このような感光膜を現像すると、分子が分解されていない第1部分312は殆どそのまま残り、光照射が少ない第2部分314は第1部分312より薄い厚さで一部だけ残り、光に完全に露光されたC領域に対応する部分では感光膜が殆ど除去される。

このような方法を通じて位置により厚さが互いに異なる感光膜パターンが作られる。

次に、図26に示したように、このような感光膜パターン312、314を蝕刻マスクとして用い、不純物がドーピングされた非晶質シリコン膜180、第2非晶質シリコン膜702、第1非晶質シリコン膜701及び低温蒸着ゲート絶縁膜160を乾式蝕刻してゲートパッド152を露出する接触孔162を完成し、C領域のバッファー層140を露出する。引続き、感光膜パターン312、314を蝕刻マスクとして用いてC領域のバッファー層140を乾式蝕刻してデータ線120及びデータパッド124を露出する接触孔161、164を完成する。

【0080】

次に、感光膜の第2部分314を完全に除去する作業を行う。ここで、第2部分314の感光膜クズを完全に除去するために酸素を利用した灰化処理工程を追加することも可能である。

このようにすると、感光膜パターンの第2部分314は除去され、不純物がドーピングされた非晶質シリコン膜180が露出されるようになり、感光膜パターンの第1部分312は感光膜パターンの第2部分312の厚さと同じ程減少した状態で残る。

【0081】

次に、残っている感光膜パターンの第1部分312を蝕刻マスクとして用いて不純物がドーピングされた非晶質シリコン膜180及びその下部の第1及び第2非晶質シリコン膜701、702を蝕刻して除去することによりゲート電極151上部の低温蒸着ゲート絶縁膜160上に島模様の半導体層171と抵抗性接触層181を残す。

最後に、残っている感光膜の第1部分312を除去する。ここで、第1部分312の感光膜クズを完全に除去するために酸素を利用した灰化処理工程を追加することもできる。

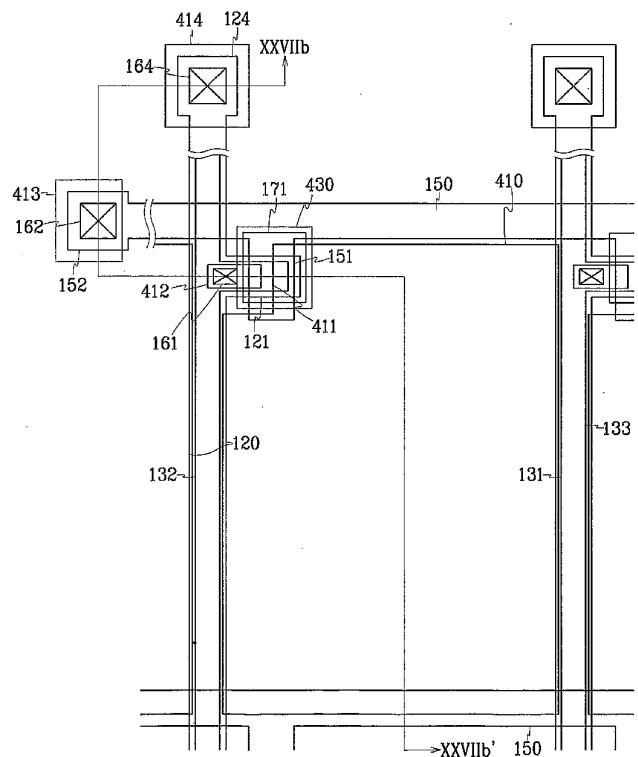

【0082】

次に、図27a及び図27bに示すように、ITO層を蒸着して写真蝕刻工程でパターニングし画素電極410、ソース用電極412、ドレーン用電極411、補助ゲートパッド413及び補助データパッド414を形成する。この時、ITOの代わりにIZOを使用することもできる。

次に、ソース用電極412とドレーン用電極411を蝕刻マスクとして用いてこれらの間の抵抗性接触層181を蝕刻して二つの部分182、183に分離された抵抗性接触層パターンを形成して、ソース用電極412とドレーン用電極411の間に半導体層171を露出させる。

【0083】

最後に、図18及び図19のように、下部絶縁基板100の上部に窒化シリコンや酸化シリコンなどの絶縁物質と黒色顔料を含む感光性有機物質などの絶縁物質を順次に積層しマスクを利用した写真工程で露光現像して有色有機膜430を形成し、これを蝕刻マスクとして用いてその下部の絶縁物質を蝕刻して保護膜190を形成する。この時、有色有機膜430は薄膜トランジスタに入射する光を遮断し、ゲート配線またはデータ配線の上部に形成して配線の周囲から漏洩する光を遮断する機能を付与することもできる。また、本発明の実施例のように有機膜430の高さを調節して間隔維持材として用いることも可能である。

【0084】

一方、上部絶縁基板200の上にはITOまたはIZOの透明な導電物質を積層して共通

10

20

20

30

40

50

電極 210 を形成する。

この時、有色有機膜 430 が画素電極 410 及び各金属層との隙間を全て覆えるように設計する場合には、上部基板に光遮断のための別途のブラックマトリックスを設計する必要はない。

【 0085 】

図 28 は本発明の第 4 実施例による薄膜トランジスタ基板の配置図を示したものである。本発明の第 3 実施例による薄膜トランジスタ基板と比較して、データ配線 120、121、124 及び有色有機膜 130 のパターンが異なるだけである。

ゲート線 150 と画素電極 410 が所定の間隔をおくように設計する場合には、画素電極 410 とゲート線 150 の間で光がもれる部分を覆う必要がある。このために、色フィルター 131、132、133 の下部に形成されたデータ線 120 の一部をゲート線 150 10 方向に突出するように延長してゲート線 150 と画素電極 410 の間の隙間を覆うように形成する。この時、データ線 120 で覆えない部分、つまり、互いに隣接する二つのデータ線 120 の間の領域には有色有機膜 430 が覆うように形成できる。

【 0086 】

一方、図面には示していないが、ゲート配線 150、151、152 と同一層にはゲート配線 150、151、152 形成用物質で画面表示部の周縁から漏洩する光を遮断するためのブラックマトリックスの縦部が形成され、データ配線 120、121、124 と同一層にはデータ配線 120、121、124 形成用金属物質で画面表示部の周縁から漏洩する光を遮断するためのブラックマトリックスの横部が形成できる。

【 0087 】

このように、ゲート配線 150、151、152 及びデータ配線 120、121、124 を形成する物質で画面表示部の周縁から漏洩する光を遮断するためのブラックマトリックスの横部及び縦部を形成し、データ配線 120、121、124 でゲート線 150 と画素電極 410 の間の光がもれる領域を覆い、有色有機膜 430 で隣接する二つのデータ配線 120 の間の光がもれる領域を覆う場合に、データ配線、ゲート配線及び間隔維持材が薄膜トランジスタ基板で光が漏洩される全ての領域を覆えて、上部基板に別途のブラックマトリックスを形成する必要がない。従って、上部基板と下部基板の整列誤差を考慮しなくてもいいので開口率を向上させることができる。また、データ線 120 と画素電極 410 の間にはゲート絶縁膜 160 と低い誘電率を有するバッファー層 140 が形成されていて、これらの間で発生する寄生容量を最小化できて表示装置の特性を向上させることができると同時に、これらの間に間隔をおく必要がないので開口率を最大限確保できる。

【 0088 】

このように、低温工程条件下で、TFT を製作する。つまり、高温工程による色フィルターの損傷を防止するためにゲート絶縁膜を低温蒸着絶縁膜で形成し、低温蒸着ゲート絶縁膜と接触することによって引き起こされるチャンネルの特性悪化を防止するために、チャンネルを低温蒸着ゲート絶縁膜と半導体層の界面に形成せず、半導体層のバルク側に形成する。

【 0089 】

本発明は提示された実施例だけではなく。様々な方式で適用可能である。例えば、重量減少及び耐衝撃性向上のために浮上したプラスチック液晶表示装置のように、低温工程条件が必要なディスプレイの場合本発明は役立つように適用できる。

本発明による CVD で形成した a-Si:C:O 膜または a-Si:O:F 膜（低誘電率 CVD 膜）は反射形や半透過形液晶表示装置に用いられる薄膜トランジスタ基板で反射光の干渉を防止するために形成するエンボシング絶縁層、つまり、表面に凹凸が形成されている絶縁層として使用しても有用である。

【 0090 】

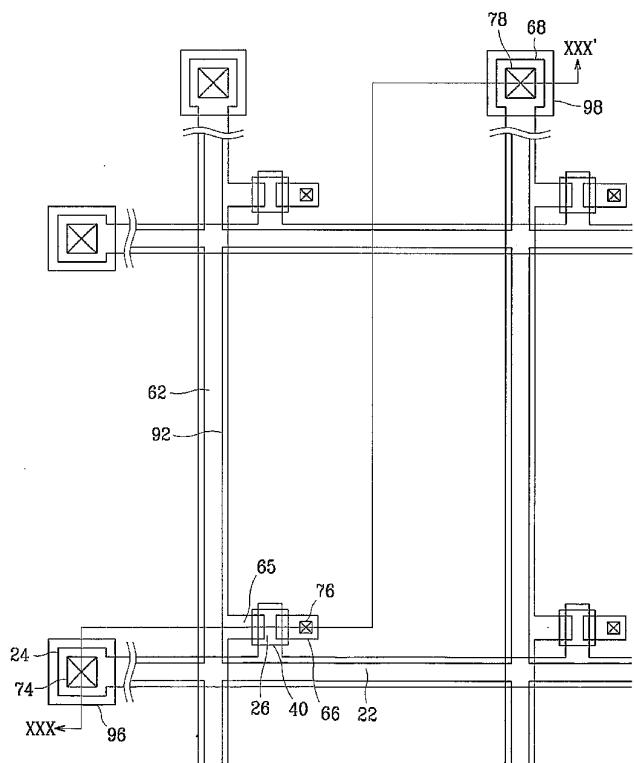

図 29 は本発明の第 5 実施例による反射形液晶表示装置用薄膜トランジスタ基板の配置図であり、図 30 は図 29 に示した薄膜トランジスタ基板を XXX-XXX' 線に沿って切断して示した断面図である。

10

20

30

40

50

絶縁基板 10 上に低抵抗を有する銀または銀合金またはアルミニウムまたはアルミニウム合金からなる単一膜またはこれを含む多層膜になっているゲート配線が形成されている。ゲート配線は横方向に伸びているゲート線 22、ゲート線 22 の端に連結されていて外部からのゲート信号の印加を受けてゲート線に伝達するゲートパッド 24 及びゲート線 22 に連結されている薄膜トランジスタのゲート電極 26 を含む。

【 0 0 9 1 】

この時、基板 10 上には上板の共通電極に入力される共通電極電圧などの電圧の印加を外部から受ける維持電極が形成でき、このような維持電極は後述する反射膜 92 と重なって画素の電荷保存能力を向上させる維持蓄電器を構成する。

ゲート配線 22、24、26 上には窒化シリコン (SiNx) などからなるゲート絶縁膜 30 がゲート配線 22、24、26 を覆っている。 10

【 0 0 9 2 】

ゲート電極 26 上部のゲート絶縁膜 30 上には非晶質シリコンなどの半導体からなる半導体層 40 が形成されており、半導体層 40 上にはシリサイドまたは n 形不純物が高濃度でドーピングされている n+ 水素化非晶質シリコンなどの物質で作られた抵抗性接触層 55、56 が各々形成されている。

抵抗性接触層 55、56 及びゲート絶縁膜 30 上にはアルミニウムまたは銀のような低抵抗の導電物質からなる導電膜を含むデータ配線が形成されている。データ配線は縦方向に形成されてゲート線 22 と交差し画素領域を定義するデータ線 62、データ線 62 に連結されて抵抗性接触層 55 の上部まで伸びているソース電極 65、データ線 62 の一端に連結されていて外部からの画像信号の印加を受けるデータパッド 68、ソース電極 65 と分離されていてゲート電極 26 を中心にしてソース電極 65 と対向しているドレーン電極 66 を含む。ドレーン電極 66 は抵抗性接触層 56 上に形成されており、画素領域内部に伸びている。 20

【 0 0 9 3 】

データ配線 62、64、65、66、68 及びこれらが覆わない半導体層 40 上部には PECVD 法によって蒸着された a-Si:C:O 膜または a-Si:O:F 膜 (低誘電率 CVD 膜) からなる保護膜 70 が形成されている。この時、保護膜 70 の表面は以降に形成される反射膜 92 の反射効率を極大化するために凹凸パターンを有する。

保護膜 70 にはドレーン電極 66 及びデータパッド 68 を各々露出する接触孔 76、78 が形成されており、ゲート絶縁膜 30 と共にゲートパッド 24 を露出する接触孔 74 が形成されている。 30

【 0 0 9 4 】

保護膜 70 上には接触孔 76 を通じてドレーン電極 66 と電気的に連結されていて画素領域に位置する反射膜 92 が形成されている。また、保護膜 70 上には接触孔 74、78 を通じて各々ゲートパッド 24 及びデータパッド 68 と連結されている補助ゲートパッド 96 及び補助データパッド 98 が形成されている。ここで、補助ゲート及びデータパッド 96、98 はゲート及びデータパッド 24、68 を保護するためのものであり、必須ではない。

【 0 0 9 5 】

一方、図 31a 乃至図 34b 及び図 29 及び図 30 を参照して本発明の実施例による薄膜トランジスタ基板の製造方法について具体的に説明する。 40

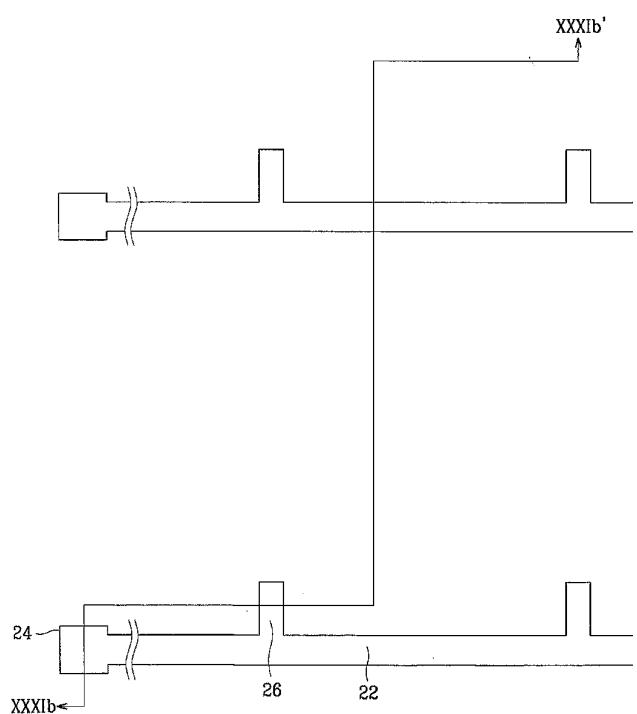

まず、図 31a 及び図 31b に示したように、ガラス基板 10 上部に低抵抗の導電物質を積層し、写真蝕刻工程でパターニングしてゲート線 22、ゲート電極 26 及びゲートパッド 24 を含む横方向のゲート配線を形成する。

【 0 0 9 6 】

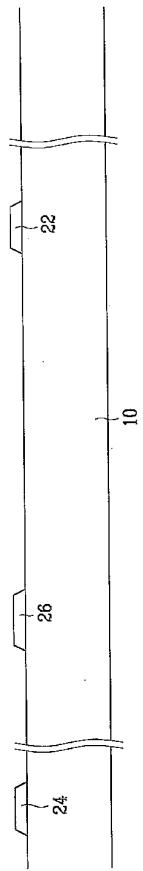

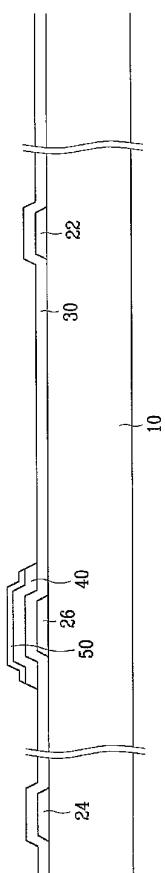

次に、図 32a 及び図 32b に示したように、窒化シリコンからなるゲート絶縁膜 30、非晶質シリコンからなる半導体層 40、ドーピングされた非晶質シリコン層 50 の三層膜を連続して基板 10 に積層して写真蝕刻し、半導体層 40 とドーピングされた非晶質シリコン層 50 をパターニングしてゲート電極 24 上部のゲート絶縁膜 30 上に半導体層 40 50

と抵抗性接触層 50 を形成する。

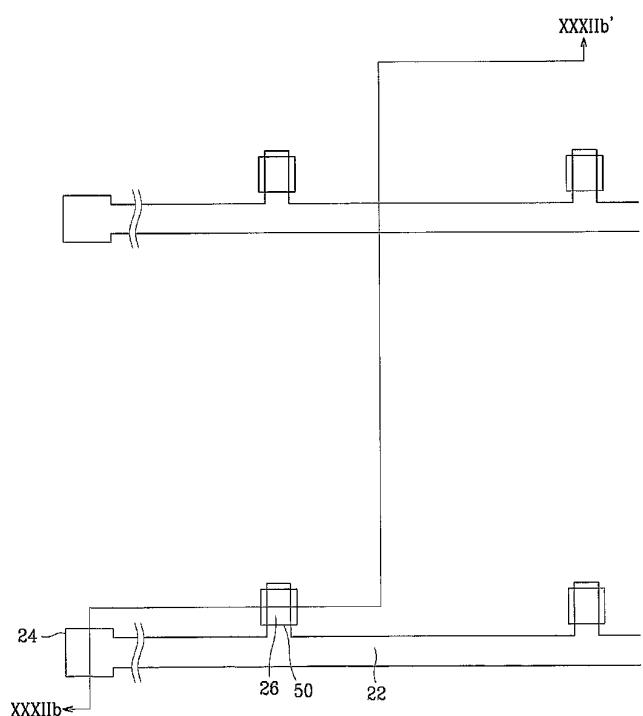

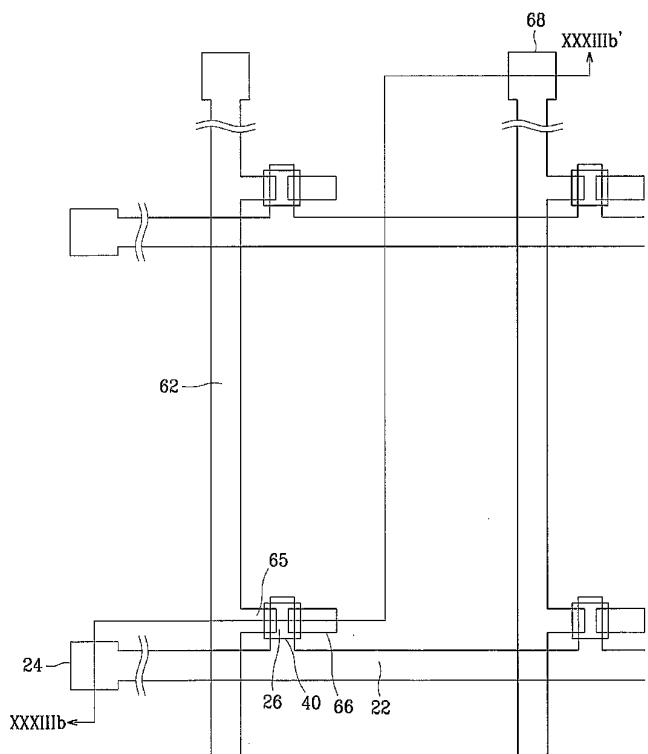

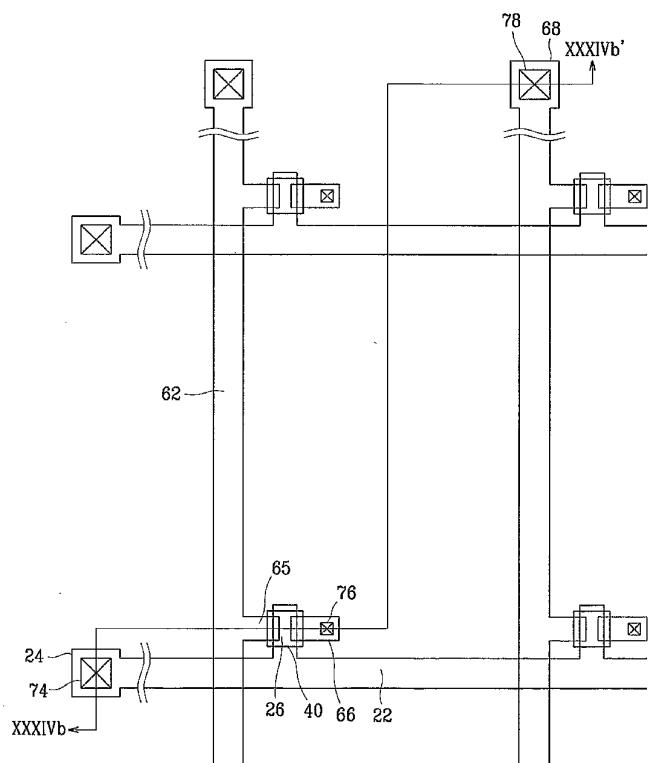

【0097】

次に、図33a乃至図33bに示したように、導電膜を基板10に積層した後、写真工程してゲート線22と交差するデータ線62、データ線62と連結されてゲート電極26上部まで延びているソース電極65、データ線62の一端に連結されているデータパッド68及びソース電極65と分離されていてゲート電極26を中心にしてソース電極65と対向するドレーン電極66を含むデータ配線を形成する。

【0098】

次に、データ配線62、65、66、68で覆わない非晶質シリコン層パターン50を蝕刻してゲート電極26を中心に両側に分離させる。また、露出された半導体層40の表面を安定化するために酸素プラズマを実施することが好ましい。

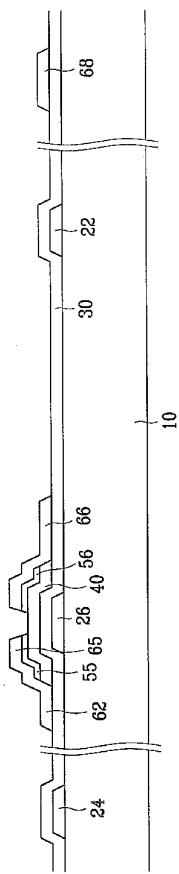

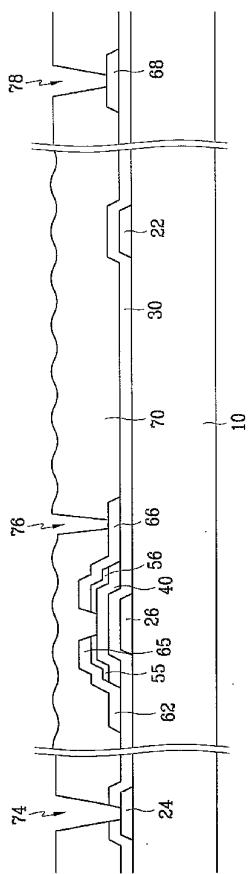

次に、図34a及び34bのように、a-Si:C:O膜またはa-Si:O:F膜を化学気相蒸着(CVD)法によって成長させて保護膜70を形成する。この時、a-Si:C:O膜の場合には気体状態のSiH(CH3)3、SiO2(CH3)4、(SiH)4O4(CH3)4、Si(C2H5O)4などを基本ソースとして用い、N2OまたはO2などの酸化剤とArまたはHeなどを混合した気体を流しながら蒸着する。また、a-Si:O:F膜の場合にはSiH4、SiF4等にO2を添加した気体を流しながら蒸着する。この時、フッ素の補助ソースとしてCF4を添加することもできる。引き続き、マスクを利用した写真工程でゲート絶縁膜30と共にパターニングして、ゲートパッド24、ドレーン電極66及びデータパッド68を露出する接触孔74、76、78を形成する同時に、保護膜70の上部に凹凸パターンを形成する。

【0099】

接触孔74、76、78と凹凸を共に形成するために第2実施例で使用したハーフトーン露光法を使用する。つまり、スリットパターンや格子パターンまたは半透過膜を有するマスクを利用して感光膜を露光した後、現像することによって接触孔74、76、78が形成される部分の上では感光膜が全て除去されて保護膜70が露出されるようにし、凸部になる部分では感光膜が薄く残るようにして、凹部になる部分では感光膜が厚く残るようにする。

【0100】

次に、感光膜を蝕刻マスクとして保護膜70とゲート絶縁膜30を蝕刻することによって接触孔74、76、78を形成し、感光膜を灰化処理して厚さの薄い感光膜が除去されるようにする。この時、感光膜の厚い部分も共に灰化処理して、その厚さを薄くする。

次に、保護膜70を所定の蝕刻時間だけ継続して蝕刻し、凸部を形成する。この時、蝕刻時間は保護膜70の蝕刻率と凸部の深さを考慮して決める。

【0101】

図29及び図30に示すように、光を反射させる特性に優れた、またはアルミニウムを含む導電物質を基板10積層して写真蝕刻工程でパターニングして接触孔76を通じてドレーン電極66と連結される反射膜92と接触孔74、78を通じてゲートパッド24及びデータパッド68と各々連結される補助ゲートパッド96及び補助データパッド98を各々形成する。

【0102】

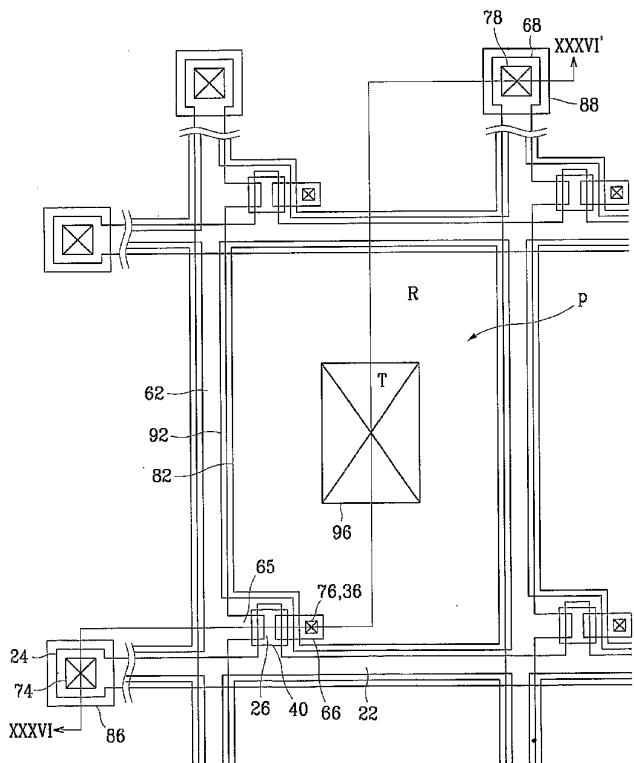

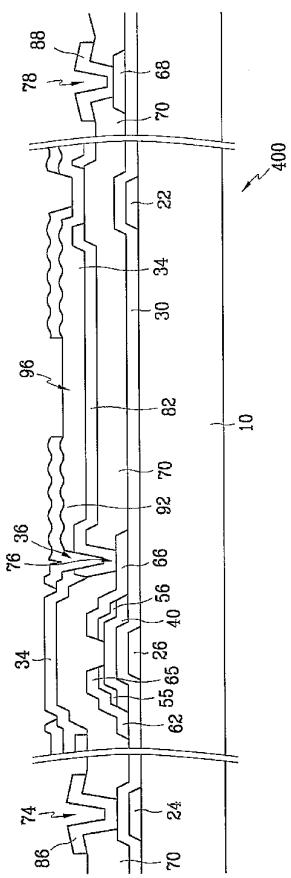

図35は本発明の第6実施例による半透過形液晶表示装置用薄膜トランジスタ基板の配置図であり、図36は図35に示した薄膜トランジスタ基板をXXXVI-XXXVI'線に沿って切断して示した断面図である。

絶縁基板10上に低抵抗を有する銀または銀合金またはアルミニウムまたはアルミニウム合金からなる単一膜またはこれを含む多層膜になっているゲート配線が形成されている。ゲート配線は横方向にのびているゲート線22、ゲート線22の端に連結されていて外部からゲート信号の印加を受けてゲート線に伝達するゲートパッド24及びゲート線22に連結されている薄膜トランジスタのゲート電極26を含む。ここで、ゲート配線22、24、26が多層膜である場合には他の物質と接触特性に優れているパッド用物質を含むこ

10

20

30

40

50

とが好ましい。

【0103】

基板10上には窒化シリコン(SiNx)などからなるゲート絶縁膜30がゲート配線22、24、26を覆っている。

ゲート電極26のゲート絶縁膜30上部には非晶質シリコンなどの半導体からなる半導体層40が形成されており、半導体層40の上部にはシリサイドまたはn形不純物が高濃度でドーピングされているn+水素化非晶質シリコンなどの物質で作られた抵抗接觸層55、56が各々形成されている。

【0104】

抵抗性接觸層55、56及びゲート絶縁膜30上にはアルミニウムまたは銀のような低抵抗の導電物質からなる導電膜を含むデータ配線62、65、66、68が形成されている。データ配線は形成されてゲート線22と交差して画素を定義するデータ線62、データ線62に連結されて抵抗性接觸層55の上部まで延びているソース電極65、データ線62の一端に連結されていて外部から画像信号の印加を受けるデータパッド68、ソース電極65と分離されていてゲート電極26に対してソース電極65に対向して形成されているドレーン電極66を含む。

【0105】

データ配線62、64、65、66、68及びこれらが覆わない半導体層40上部にはPECVD法によって蒸着されたa-Si:C:O膜またはa-Si:O:F膜(低誘電率CVD膜)からなる保護膜70が形成されている。PECVD法によって蒸着されたa-Si:C:O膜とa-Si:O:F膜は誘電定数が4以下である。従って、厚さが薄くても寄生容量問題が発生しない。他の膜との接着性及び段差被覆性が優れている。また、無機質CVD膜であるので耐熱性が有機絶縁膜に比べて優れている。同時に、PECVD法によって蒸着されたa-Si:C:O膜とa-Si:O:F膜(低誘電率CVD膜)は蒸着速度や蝕刻速度が窒化シリコン膜に比べて4~10倍速いので工程時間の面でも非常に有利である。

【0106】

保護膜70にはドレーン電極66及びデータパッド68を各々露出する接觸孔76、78が形成されており、ゲート絶縁膜30と共にゲートパッド24を露出する接觸孔74が形成されている。

保護膜70上部には接觸孔76を通じてドレーン電極66と電気的に連結されていて画素に位置する透明電極82が形成されている。また、保護膜70上には接觸孔74、78を通じて各々ゲートパッド24及びデータパッド68と連結されている補助ゲートパッド86及び補助データパッド88が形成されている。ここで、透明電極82と補助ゲート及びデータパッド86、88は透明な導電物質であるITOまたはIZO等で作られている。

【0107】

透明電極82の上部には透明電極82の一部を露出する接觸孔36を有し、PECVD法によって蒸着されたa-Si:C:O膜またはa-Si:O:F膜(低誘電率CVD膜)からなる層間絶縁膜34が形成されている。ここで、層間絶縁膜34は、この後の反射膜92の反射効率を極大化するために凹凸パターンを有するのが好ましい。

層間絶縁膜34の上部には接觸孔36を通じて透明電極82と電気的に連結されており、透過モード領域(T)に透過窓96を有する反射膜92が形成されている。反射膜92はアルミニウムまたはアルミニウム合金、銀または銀合金、モリブデンまたはモリブデン合金などに高い反射率を有する導電膜からなり、透明電極82と共に画素電極になる。この時、反射膜92の透過窓96は様々な模様に形成でき、一つの画素領域に多数形成できる。前記で、層間絶縁膜34に凹凸パターンが形成されている場合でも透過窓96部分には凹凸パターンを形成しないのが好ましい。

【0108】

ここで、画素電極82、92は前段のゲート線22と重なって維持蓄電器を構成する。場合によっては維持容量を形成するためにゲート配線22、24、26と同一層に維持容量用配線を形成することもできる。

10

20

30

40

50

以下、このような本発明の液晶表示装置用薄膜トランジスタ基板の製造方法について説明する。

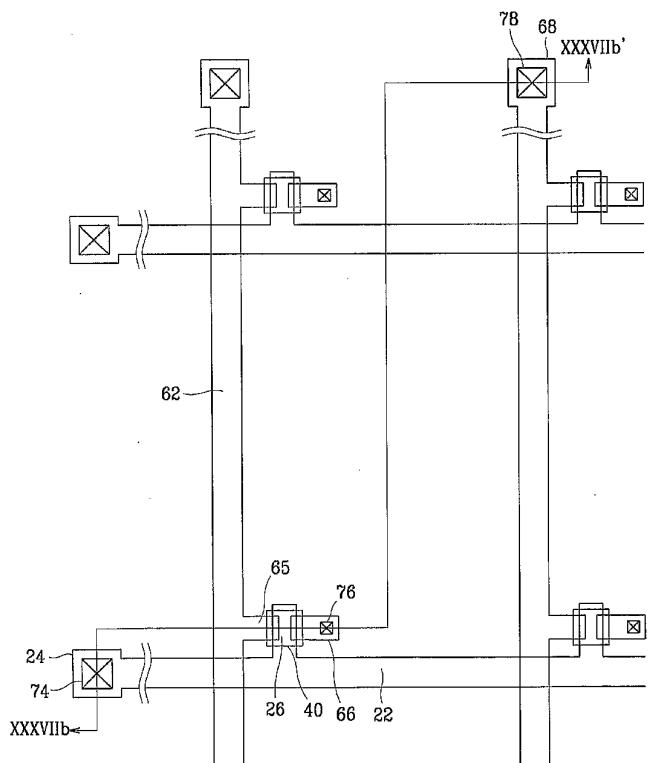

【0109】

まず、データ配線 62、65、66、68を形成する段階までは本発明の第5実施例による薄膜トランジスタ基板の製造法と同一である。つまり、図31a乃至図33bに示した工程に従う。

データ配線 62、65、66、68を形成した後には、図37a及び37bのように、データ配線 62、65、66、68上にa-Si:C:O膜またはa-Si:O:F膜を化学気相蒸着(CVD)法によって成長させて保護膜70を形成する。次に、感光膜パターンを利用した写真蝕刻工程でゲート絶縁膜30と共にパターニングして、ゲートパッド24、ドレーン電極66及びデータパッド68を露出する接触孔74、76、78を形成する。この時、蝕刻は乾式蝕刻による。

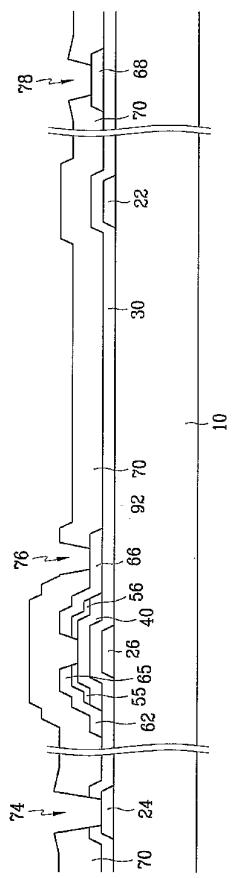

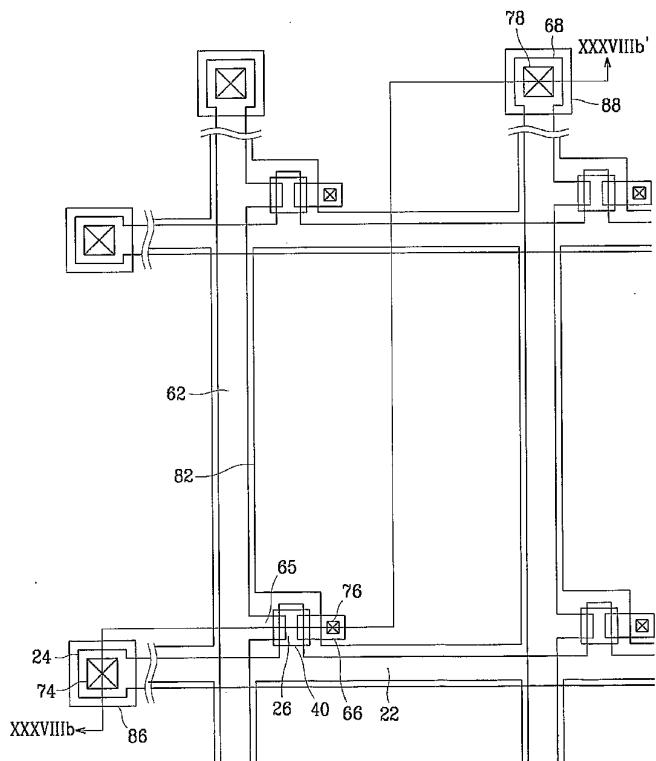

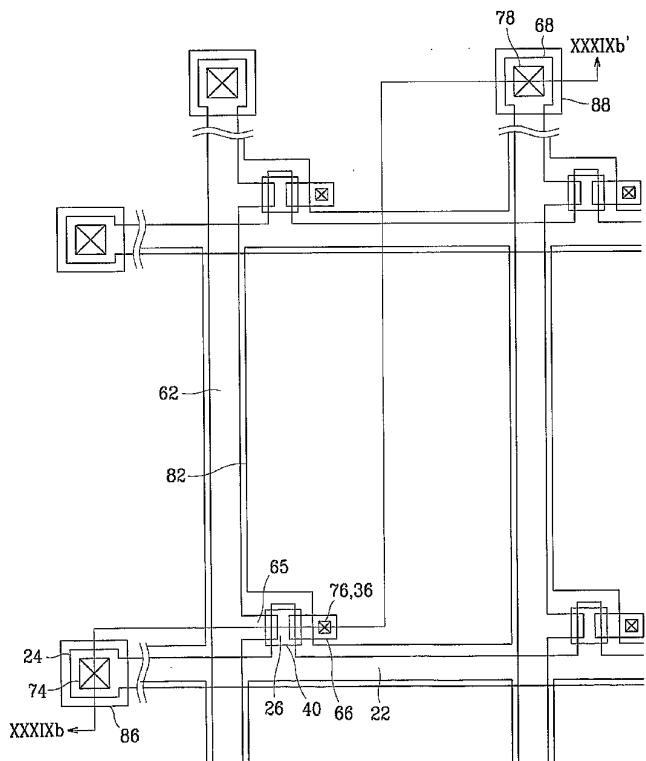

【0110】

次に、図38a及び図38bのように、ITOまたはIZO膜を基板10に積層して写真蝕刻し、接触孔76を通じてドレーン電極66と連結される透明電極82と、接触孔74、78を通じてゲートパッド24及びデータパッド68と各々連結される補助ゲートパッド86及び補助データパッド88と、を各々形成する。

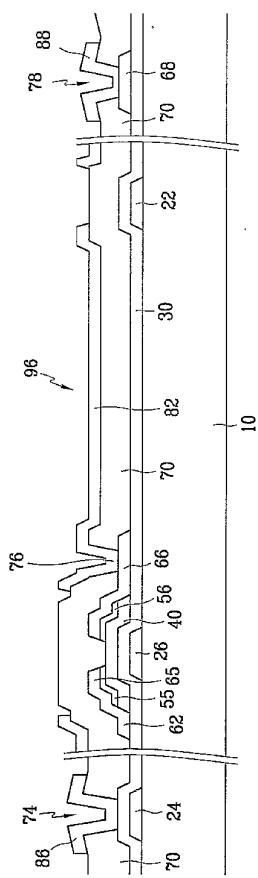

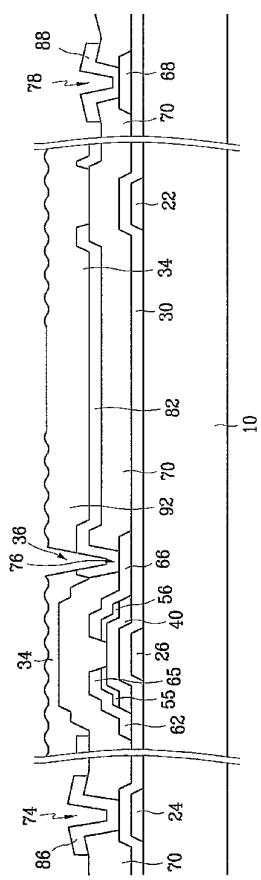

また、図39a及び図39bに示したように、a-Si:C:O膜またはa-Si:O:F膜を化学気相蒸着(CVD)法によって成長させ、写真蝕刻工程でパターニングして透明電極82を露出する接触孔36を有する層間絶縁膜34を形成する。この時、層間絶縁膜34に凹凸パターンを形成できる。凹凸パターンを形成する場合には第5実施例による薄膜トランジスタ基板の製造法のうち保護膜をパターニングする工程でのようにハーフトーン露光法を使用する。

【0111】

次に、最後として図35及び図36のように、高い反射率を有するアルミニウムまたは銀またはモリブデンを含む導電膜を積層してパターニングし透過窓96を有する反射膜92を形成する。

a-Si:C:O膜またはa-Si:O:F膜(低誘電率CVD膜)はゲート絶縁膜にも適用できる。

【0112】

図40は本発明の第7実施例による薄膜トランジスタ基板の断面図である。

第7実施例による薄膜トランジスタ基板は第1実施例による薄膜トランジスタ基板とゲート絶縁膜を除いては同じ構造を有する。第7実施例ではゲート絶縁膜が二重層になっている。つまり、PECVDにより形成したa-Si:C:O膜またはa-Si:O:F膜(低誘電率CVD膜)である第1層31と窒化シリコン膜である第2層32から構成されている。

【0113】

ゲート絶縁膜は非晶質シリコンからなる半導体層40との界面特性を考慮して緻密な膜質を維持しなければならない。ところが、膜質が緻密であれば緻密であるほど蒸着速度が遅いので工程時間が長くなる短所がある。一方、半導体層40と接する面から約500程度の厚さまで緻密な膜質が維持されると薄膜トランジスタが動作するのに無理が無いことが知られている。従って、ゲート絶縁膜の上部は蒸着速度が速いa-Si:C:O膜またはa-Si:O:F膜で形成し、ゲート絶縁膜の下部は膜質が緻密な窒化シリコン膜で形成すれば、薄膜トランジスタの性能を低下させずに工程時間を短縮できる。a-Si:C:O膜は窒化シリコン膜に比べて4倍から10倍程度蒸着速度が速い。この時、a-Si:C:O膜は真空が維持される状態で連続して蒸着する。

【0114】

このような低誘電率CVD膜と窒化シリコン膜の二重層になっているゲート絶縁膜は第2乃至第6実施例による薄膜トランジスタ基板にも適用できる。

【図面の簡単な説明】

10

20

30

40

50

## 【0115】

【図1】本発明の第1実施例による液晶表示装置用薄膜トランジスタ基板である。

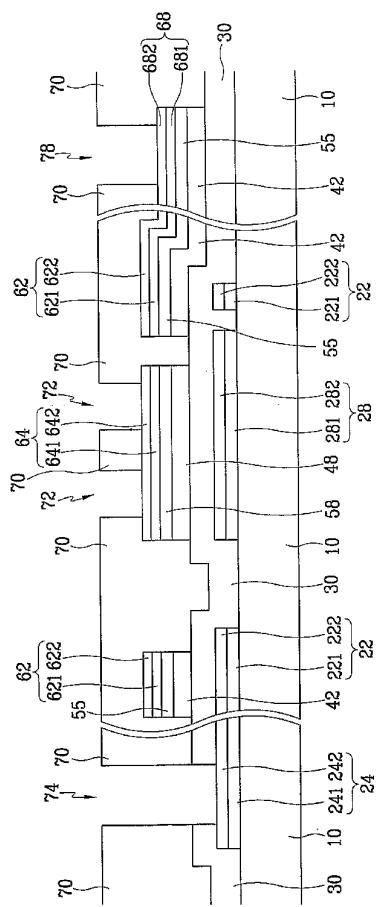

【図2】図1のII-II線による断面図である。

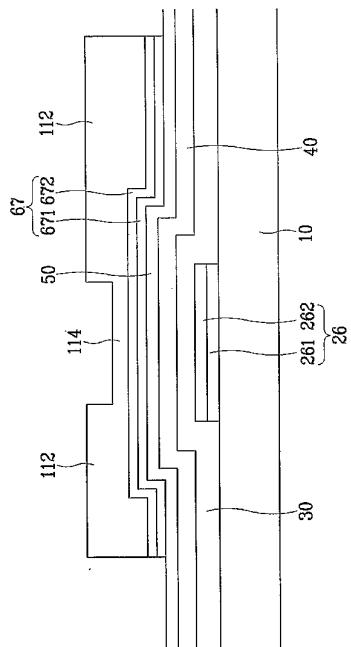

【図3a】本発明の第1実施例による液晶表示装置用薄膜トランジスタ基板を製造する過程をその工程順序に従って示した薄膜トランジスタ基板の配置図である。

【図3b】図3aでのIIIb-IIIb'線に対する断面図である。

【図4a】本発明の第1実施例による液晶表示装置用薄膜トランジスタ基板を製造する過程をその工程順序に従って示した薄膜トランジスタ基板の配置図である。

【図4b】図4aでのIVb-IVb'線に対する断面図である。

【図5a】本発明の第1実施例による液晶表示装置用薄膜トランジスタ基板を製造する過程をその工程順序に従って示した薄膜トランジスタ基板の配置図である。 10

【図5b】図5aでのVb-Vb'線に対する断面図。

【図6a】本発明の第1実施例による液晶表示装置用薄膜トランジスタ基板を製造する過程をその工程順序に従って示した薄膜トランジスタ基板の配置図である。

【図6b】図6aでのVIb-VIb'線に対する断面図。

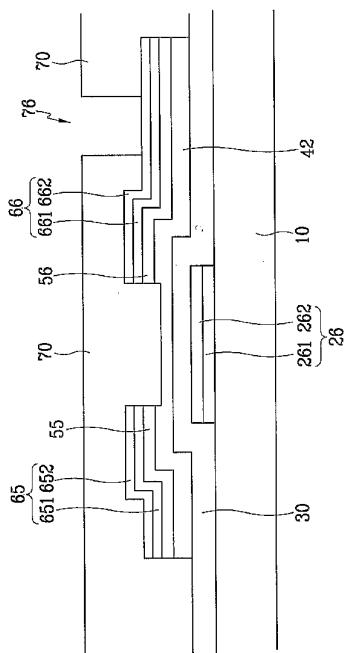

【図7】本発明の第2実施例による液晶表示装置用薄膜トランジスタ基板の配置図である。

。

【図8】各々図7のVIII-VIII'線に対する断面図である。

【図9】各々図7のIX-IX'線に対する断面図である。

【図10a】図7に示す薄膜トランジスタ基板を製造する第1段階を示す図である。 20

【図10b】各々図10aでのXb-Xb'線及びXc-Xc'線に対する断面図である。

【図10c】各々図10aでのXb-Xb'線及びXc-Xc'線に対する断面図である。

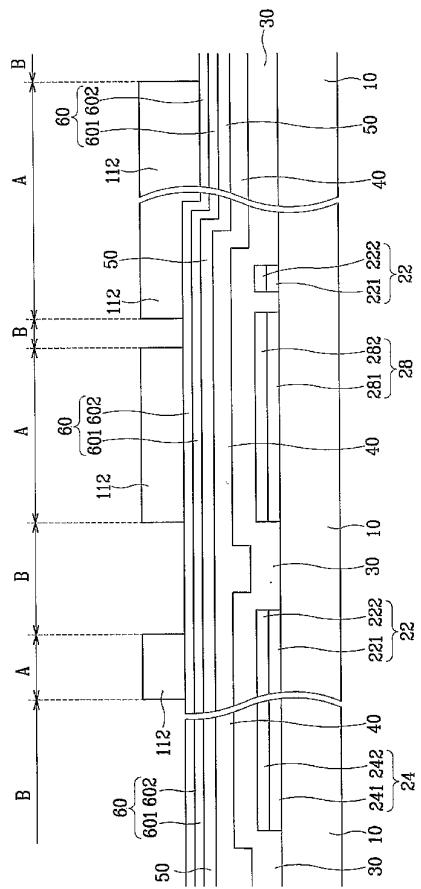

【図11a】図10b及び図10cの次の段階での製造工程を示す図である。

【図11b】図10b及び図10cの次の段階での製造工程を示す図である。

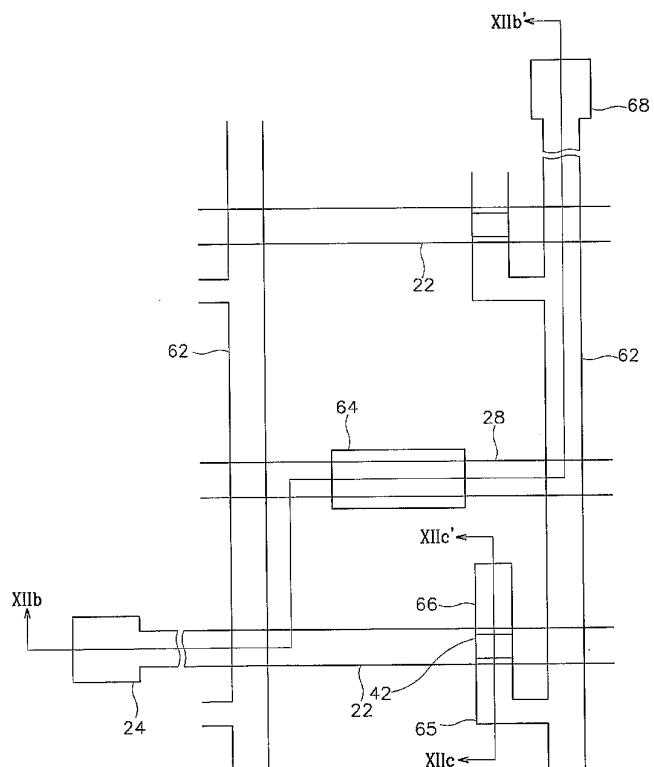

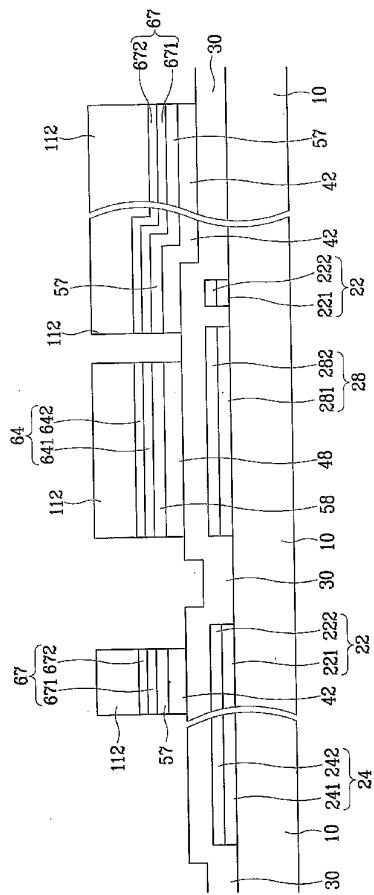

【図12a】図10aの次の段階での薄膜トランジスタ基板の工程である。

【図12b】図12aでのXIb-XIb'線に対する断面図である。

【図12c】図12aでの及びXIc-XIc'線に対する断面図である。

【図13a】図12aに示すステップに続く工程図。

【図13b】図12aに示すステップに続く工程図。

【図14a】図12aに示すステップに続く工程図。 30

【図14b】図12aに示すステップに続く工程図。

【図15a】図12aに示すステップに続く工程図。

【図15b】図12aに示すステップに続く工程図。

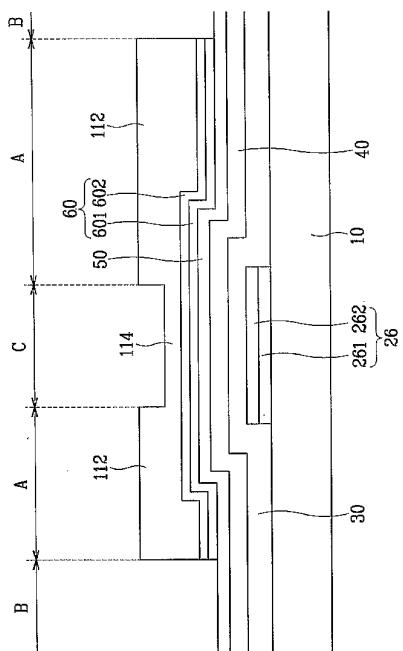

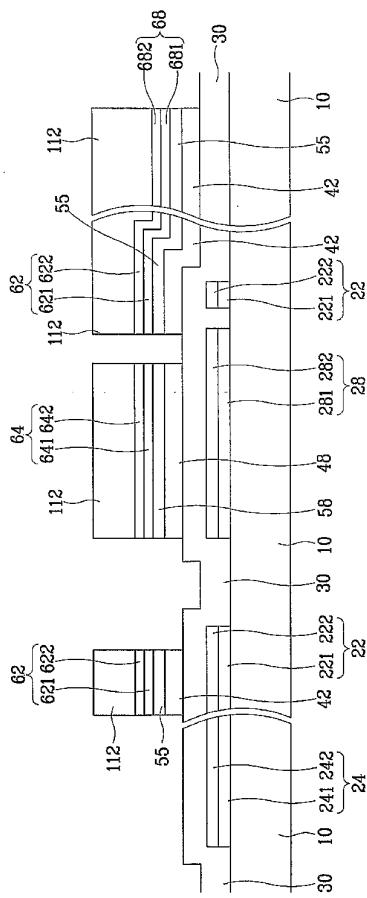

【図16a】図15aの次の段階での薄膜トランジスタ基板の断面図である。

【図16b】図15bの次の段階での薄膜トランジスタ基板の断面図である。

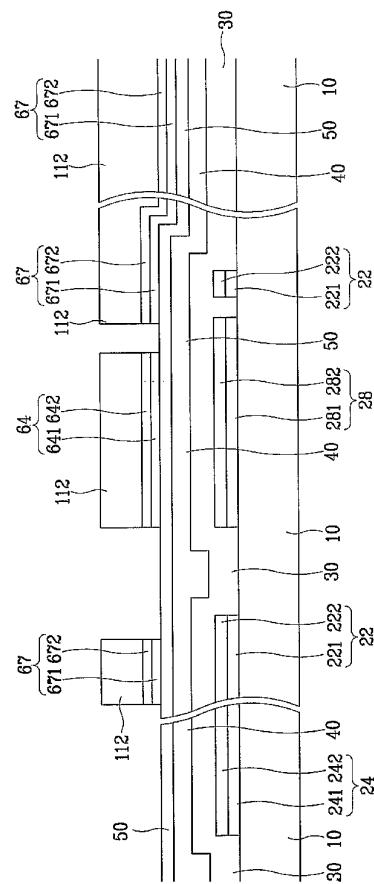

【図17a】図16a及び図16bの次の段階での薄膜トランジスタ基板の配置図である。

。

【図17b】各々図17aでのXVIIb-XVIIb'線及びXVIIc-XVIIc'線に対する断面図である。

【図17c】各々図17aでのXVIIb-XVIIb'線及びXVIIc-XVIIc'線に対する断面図である。 40

【図18】本発明の第3実施例による薄膜トランジスタ基板の配置図である。

【図19】図18に示した薄膜トランジスタ基板を切断線XIX-XIX'に沿って示した断面図である。

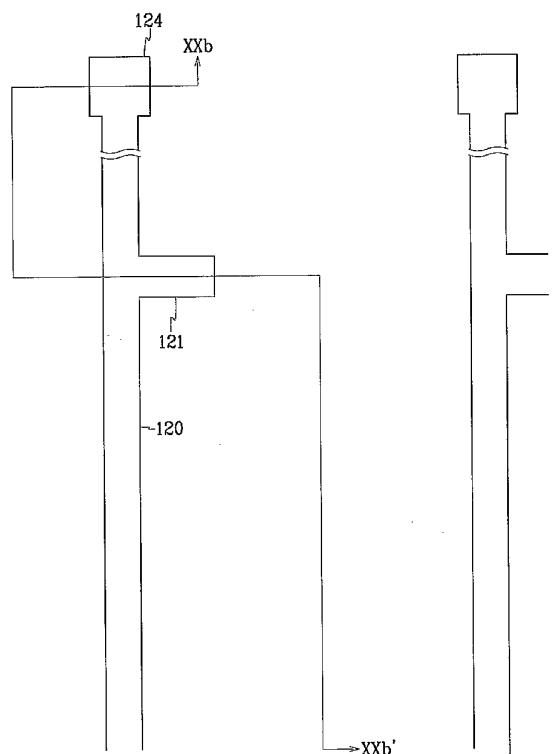

【図20a】図18に示す薄膜トランジスタ基板の第1の製造段階である。

【図20b】図20aに示した切断線XXb-XXb'に沿って示した断面図である。

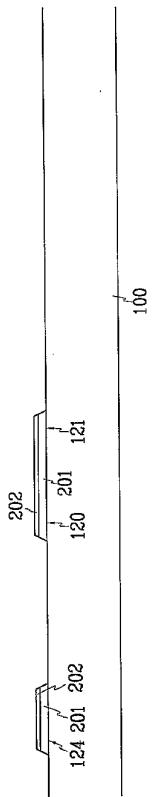

【図21a】図20aの次の段階での基板の配置図である。

【図21b】図21aに示した切断線XXIb-XXIb'に沿って示した断面図である。

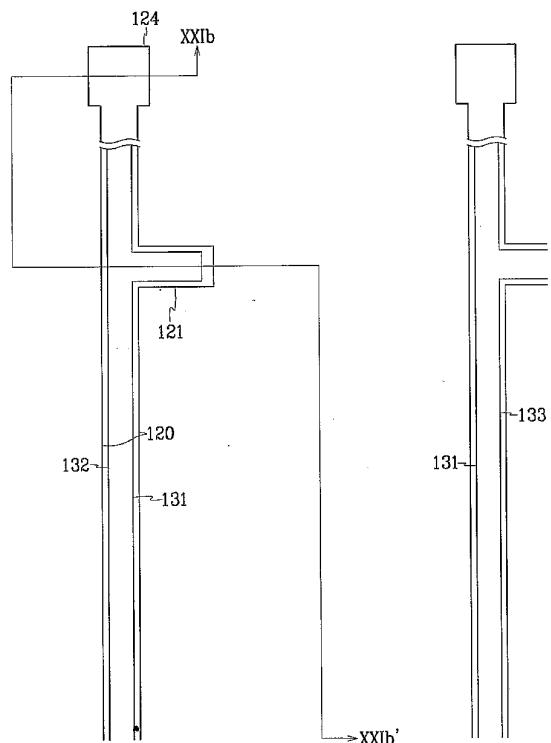

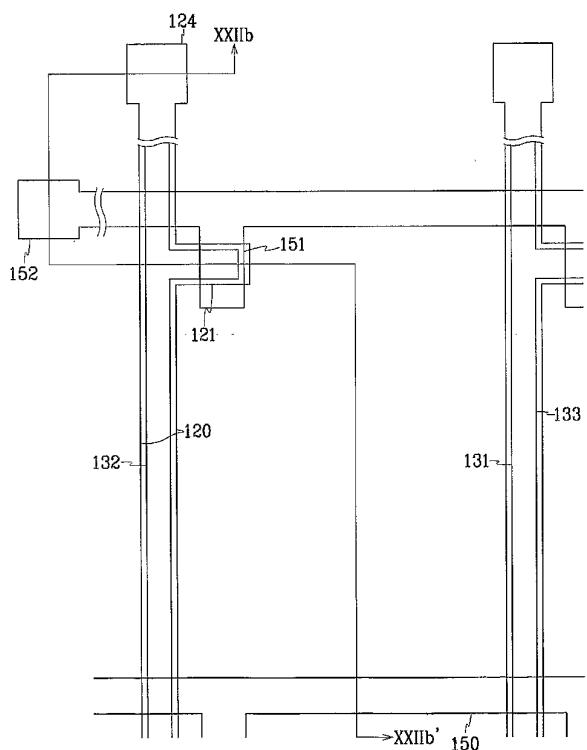

【図22a】図22aの次の段階での基板の配置図である。

【図22b】図22aに示した切断線XXIIb-XXIIb'に沿って示した断面図である。 50

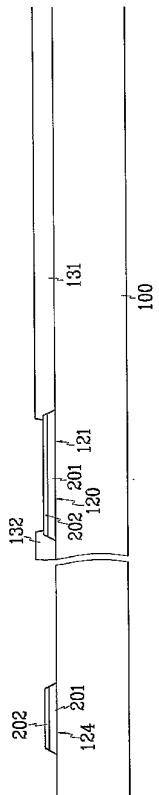

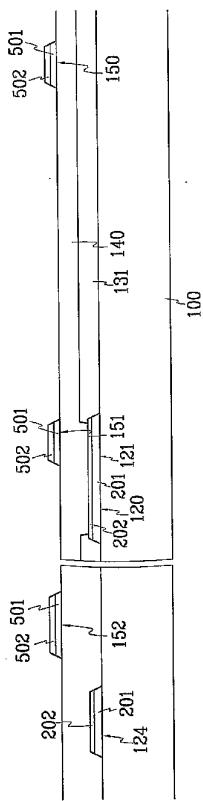

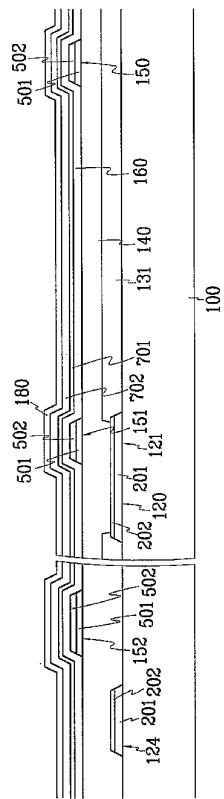

- 【図23】図22の次の段階での基板の製造工程である。

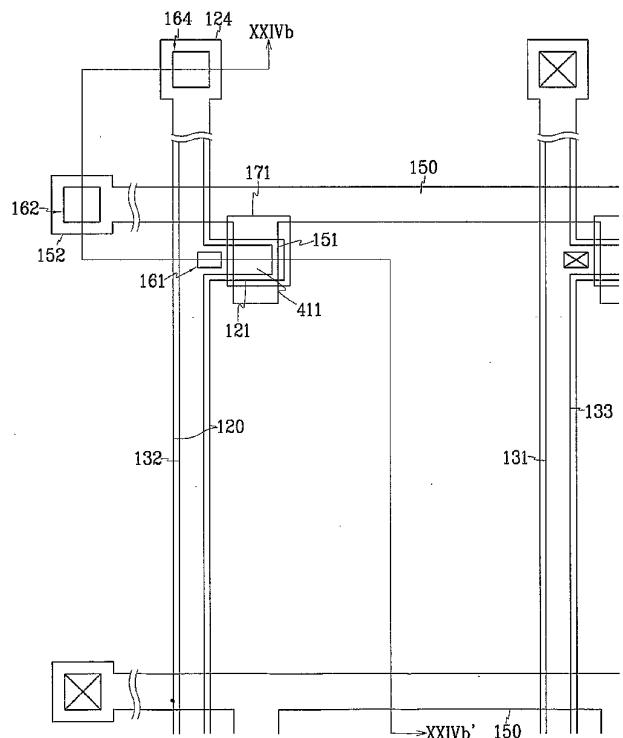

- 【図24a】図23の次の段階での基板の配置図である。

- 【図24b】図24aに示した切断線XXIVb - XXIVb'に沿って示した断面図である。

- 【図25】図23と図24bの間に実施される製造工程を示したものである。

- 【図26】図23と図24bの間に実施される製造工程を示したものである。

- 【図27a】図24aの次の段階での基板の配置図である。

- 【図27b】図27aに示した切断線XXVIIb - XXVIIb'に沿って示した断面図である。

- 【図28】本発明の第4実施例による薄膜トランジスタ基板の配置図である。

- 【図29】本発明の第5実施例による反射形液晶表示装置用薄膜トランジスタ基板の構造を示した配置図である。 10

- 【図30】図29でのXXX' - XXX'線に沿って切断して示した断面図である。

- 【図31a】図29に示す薄膜トランジスタ基板の製造工程を示す図。

- 【図31b】図31aでのXXXIb - XXXIb'線に沿って切断した断面図である。

- 【図32a】図29に示す薄膜トランジスタ基板の製造工程を示す図。

- 【図32b】図32aでのXXXIb - XXXIb'線に沿って切断して示した図面である。

- 【図33a】図29に示す薄膜トランジスタ基板の製造工程を示す図。

- 【図33b】図33aでのXXXIIb - XXXIIb'線に沿って切断して示した図面である。

- 【図34a】図29に示す薄膜トランジスタ基板の製造工程を示す図。

- 【図34b】図34aでのXXXIVb - XXXIVb'線に沿って切断して示した図面である。

- 【図35】本発明の第6実施例による半透過形液晶表示装置での薄膜トランジスタ基板の構造を示した配置図である。 20

- 【図36】図35でのXXXVI - XXXVI'線に沿って切断して示した薄膜トランジスタ基板の断面図である。

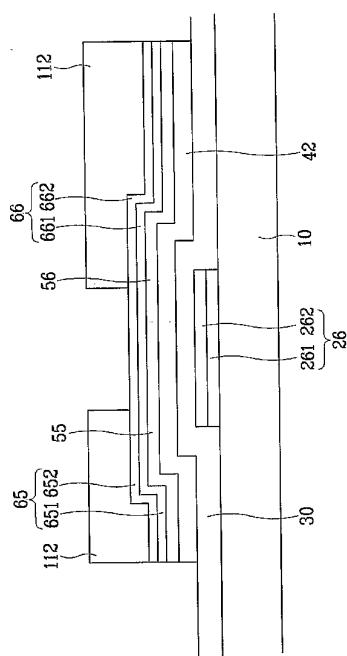

- 【図37a】図35に示される薄膜トランジスタ基板の製造工程を示す図面である。

- 【図37b】図35に示す薄膜トランジスタの製造工程を示す図。

- 【図38a】図35に示される薄膜トランジスタ基板の製造工程を示す図面である。

- 【図38b】図38aでのXXXVIIb - XXXVIIb'線に沿って切断して示した図面である。 30

- 【図39a】図39aでのXXXIXb - XXXIXb'線に沿って切断して示した図面である。

- 【図40】本発明の第7実施例による薄膜トランジスタ基板の断面図である。

- 【符号の説明】

- 【0116】

- 10 絶縁基板

- 22、24、26 ゲート配線

- 28 維持電極線

- 30 ゲート絶縁膜

- 31 第1層

- 32 第2層

- 36 接触孔

- 40 半導体層

- 42、48 半導体パターン

- 50 中間層

- 54 抵抗性接触層

- 55、56、58 抵抗性接触層パターン

- 57 ソース/ドレーン用中間層パターン

- 62、65、66、68 データ配線

- 64 維持蓄電器用導電体パターン

- 67 ソース/ドレーン用導電体パターン

- 70、190 保護膜

- 72、74、76、78 接触孔

8 2 透明電極

8 6 補助ゲートパッド

8 8 補助データパッド

9 2 反射膜

9 6 補助ゲートパット

9 8 補助データパッド

1 0 0 絶縁基板

1 1 0 感光膜

1 1 2 、 1 1 4 感光膜パターン

1 2 0 、 1 2 1 、 1 2 4 データ配線 10

1 3 0 有色有機膜

1 3 1 、 1 3 2 、 1 3 3 色フィルター

1 4 0 バッファ層

1 5 0 、 1 5 1 、 1 5 2 ゲート配線

1 6 0 ゲート絶縁膜

2 0 1 下層

2 0 2 上層

2 2 1 、 2 4 1 、 2 6 1 、 2 8 1 第1ゲート配線層

2 2 2 、 2 4 2 、 2 6 2 、 2 8 2 第2ゲート配線層

4 1 0 、 4 1 1 、 4 1 2 画素配線 20

4 1 3 、 4 1 4 補助パッド

4 3 0 有機膜

6 2 1 、 6 5 1 、 6 6 1 、 6 8 1 第1データ配線層

6 2 2 、 6 5 2 、 6 6 2 、 6 8 2 第2データ配線層

7 0 1 下層半導体層

7 0 2 上層半導体層

## 【国際公開パンフレット】

(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau(43) International Publication Date

1 May 2003 (01.05.2003)

PCT

(10) International Publication Number

WO 03/036376 A1

(51) International Patent Classification: G02F 1/136

[KR/KR]; Daewoo-Hyoryeong Apt. 104-402, Bangbae-dong, Seocho-ku, 137-061 Seoul (KR).

(21) International Application Number: PCT/KR01/01896

CHOI, Joon-Hoo [KR/KR]; Samho Apt. 108-303, Youngcheon-dong 100, Seocho-ku, 120-070 Seoul (KR).

(22) International Filing Date: 7 November 2001 (07.11.2001)

KIM, Sang-Cab [KR/KR]; Samik Apt. 205-913, Myungil-dong 309-1, Kangdong-ku, 134-830 Seoul (KR).

(25) Filing Language: Korean

JUNG, Kwan-Woo [KR/KR]; Byeokjeokgol-Jeokkong

(26) Publication Language: English

Apt. 911-1502, Youngtong-dong, Paldal-ku, 442-470 Su-

(30) Priority Data: 2001/60482 28 September 2001 (28.09.2001) KR

won-city, Kyungki-do (KR); CHUNG, Kyu-Ha [KR/KR]; Samsung Apt. 110-1401, Daechi 1-dong, Gangnam-ku, 135-968 Seoul (KR).

(71) Applicant (for all designated States except US): SAM-SUNG ELECTRONICS CO., LTD. [KR/KR]; 416, Maeun-dong, Paldal-ku, 442-370 Suwon-city, Kyungki-do (KR).

(74) Agent: YOU ME PATENT &amp; LAW FIRM; Teheran Bldg., 825-33, Yoksam-dong, Gangnam-ku, 135-080 Seoul (KR).

(72) Inventors; and

(81) Designated States (national): AB, AG, AL, AM, AT, AU,

(75) Inventors/Applicants (for US only): HONG, Wan-Shick

AZ, BA, BB, BG, BR, BY, BZ, CA, CL, CN, CO, CR, CU,

CZ, DE, DK, DM, DZ, EC, EE, ES, FI, GB, GD, GE, GI,

GM, HR, HU, ID, IL, IN, IS, JP, KU, KG, KP, KZ, LC, LK,

LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW, MX,

[Continued on next page]

(54) Title: A THIN FILM TRANSISTOR SUBSTRATE OF USING INSULATING LAYERS HAVING LOW DIELECTRIC CONSTANT AND A METHOD OF MANUFACTURING THE SAME

(57) Abstract: A thin film transistor array substrate includes an insulating substrate, a gate line assembly formed on the substrate, and a data line assembly crossing over the gate line assembly while being insulated from the gate line assembly. Thin film transistors are connected to the gate line assembly, and the data line assembly. A passivation layer is formed on the thin film transistors with a-SiCO or a-SiOF. The a-SiCO or a-SiOF-based layer is deposited through PECVD. Pixel electrodes are formed on the passivation layer while being connected to the thin film transistors. In this structure, the problem of parasitic capacitance is solved while enhancing the opening ratio, and reducing the processing time.

WO 03/036376 A1

## WO 03/036376 A1

MZ, NO, NZ, PH, PL, PT, RO, RU, SD, SE, SG, SI, SK, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, SI, TJ, TM, TR, TT, TZ, UA, UG, US, UZ, VN, YU, ZA, TG, ZW.

- (84) Designated States (regional):** ARIPO patent (GH, GM, KU, LX, MW, MZ, SD, SI, SZ, TZ, UG, ZW), Eurasian patent (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European patent (AT, BE, CH, CY, DE, DK, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE, TR), OAPI patent (BF, BJ, CF, TG).

**Published:**

with international search report

*For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.*

WO 03/036376

PCT/KR01/01896

**A THIN FILM TRANSISTOR SUBSTRATE OF USING INSULATING LAYERS HAVING LOW DIELECTRIC CONSTANT AND A METHOD OF MANUFACTURING THE SAME**

5

**BACKGROUND OF THE INVENTION**

**(a) Field of the Invention**

The present invention relates to a thin film transistor array substrate with a low dielectric insulating layer, and a method of fabricating the same.

**(b) Description of the Related Art**

10 Generally, a thin film transistor array substrate is used as a circuit substrate for independently driving the respective pixels in a liquid crystal display or an organic electroluminescence display. The thin film transistor array substrate has gate lines for carrying scanning signals, data lines for carrying picture signals, thin film transistors connected to the gate and the 15 data lines, pixel electrodes connected to the thin film transistors, a gate insulating layer covering the gate lines, and a passivation layer covering the thin film transistors and the data lines. Each thin film transistor is formed with a gate electrode connected to the gate line, a channel-forming semiconductor layer, a source electrode connected to the data line, a drain 20 electrode, a gate insulating layer, and a passivation layer. The thin film transistor functions as a switching circuit where the picture signal from the data line is transmitted to the pixel electrode in accordance with the scanning signal from the gate line.

Meanwhile, as large-sized high definition liquid crystal displays have

WO 03/036376

PCT/KR01/01896

been the choice of electronic consumers, there exists a problem of solving signal deformation due to the increase of various kinds of parasitic capacity. Furthermore, as the liquid crystal displays for notebook computers have involved the decrease in the consumption power and those for TVs have 5 involved improvement in the brightness for increasing the space of visibility, it is required to increase the opening ratio of the liquid crystal displays. In order to increase the opening ratio, it is required to extend the pixel electrodes over the data line assembly such that they are overlapped with the data line assembly. In this case, the parasitic capacity between the pixel 10 electrodes and the data lines is increased. In order to solve the problem of increase in the parasitic capacitance, the vertical spacing between the pixel electrodes and the data lines should be made in a sufficient manner. For this purpose, a passivation layer is usually formed with an organic insulating film. However, the formation of the passivation layer using the organic 15 insulating film involves the following shortcomings. First, the material cost is high particularly in that the amount of material loss is large at the spin coating process. Second, the organic insulating film involves limited thermostability while making the post-processing steps to be restricted by various conditions. Third, the layer formation process based on the organic insulating film 20 involves high frequency of occurrence of impure particles due to the material conglomeration. Fourth, the organic insulating film-based layer involves weak adhesive strength with respect to the neighboring layers. Fifth, when pixel electrodes are formed on the passivation layer, the possibility of etching

WO 03/036376

PCT/KR01/01896

error is significantly high.

**SUMMARY OF THE INVENTION**

It is an object of the present invention to provide a thin film transistor array substrate which bears a high opening ratio while not involving the 5 problem of parasitic capacitance.

This and other objects may be achieved through using a CVD layer having dielectric constant 4.0 or less.

According to one aspect of the present invention, the thin film transistor array substrate includes an insulating substrate, a first signal line 10 formed on the insulating substrate, a first insulating layer formed on the first signal line, and a second signal line formed on the first insulating layer while crossing over the first signal line. A thin film transistor is connected to the first and the second signal lines. A second insulating layer is formed on the thin film transistor with a CVD layer having dielectric constant 4.0 or less. 15 The second insulating layer has a first contact hole exposing a predetermined electrode of the thin film transistor. A first pixel electrode is formed on the second insulating layer while being connected to the predetermined electrode of the thin film transistor through the first contact hole.

20 The first insulating layer has a bottom layer portion based on a CVD layer having dielectric constant 4.0 or less, and a top layer portion based on a silicon nitride layer. The first pixel electrode is formed with an opaque conductive material of light reflection. The second insulating layer has a

WO 03/036376

PCT/KR01/01896

pattern of prominence and depression. The thin film transistor array substrate may further include a third insulating layer formed on the first pixel electrode with a CVD layer having dielectric constant 4.0 or less. The third insulating layer has a second contact hole exposing a predetermined portion 5 of the first pixel electrode. A second pixel electrode is formed on the third insulating layer with an opaque conductive material of light reflection while being connected to the predetermined portion of the first pixel electrode through the second contact hole. The first pixel electrode is formed with a transparent conductive material, and the second pixel electrode has a 10 predetermined opening portion capable of passing the light transmitted through the first pixel electrode. The CVD layer having dielectric constant 4.0 or less is formed with a-Si:C:O, or a-Si:C:O. The CVD layer has a dielectric constant of 2-4.

According to another aspect of the present invention, the thin film 15 transistor array substrate includes a data line assembly formed on an insulating substrate, the data line assembly including data lines, color filters of red, green and blue formed on the insulating substrate, and a buffer layer formed on the data line assembly and the color filters with a CVD layer having dielectric constant 4.0 or less. The buffer layer has a first contact 20 hole exposing a predetermined portion of the data line assembly. A gate line assembly is formed on the buffer layer. The gate line assembly includes gate lines crossing over the data lines while defining pixel regions, and gate electrodes connected to the gate lines. A gate insulating layer is

WO 03/036376

PCT/KR01/01896

formed on the gate line assembly with a second contact hole partially exposing the first contact hole. A semiconductor pattern is formed on the gate insulating layer over the gate electrodes. A pixel line assembly is further provided at the substrate. The pixel line assembly includes source 5 electrodes connected to the data lines through the first and the second contact holes while partially contacting the semiconductor pattern, drain electrodes facing the source electrodes over the semiconductor pattern, and pixel electrodes connected to the drain electrodes.

The semiconductor pattern has a first amorphous silicon layer with a 10 predetermined band gap, and a second amorphous silicon layer with a band gap lower than the band gap of the first amorphous silicon layer. The thin film transistor array substrate may further include light interception members formed at the same plane as the data lines with the same material as the data lines while being placed corresponding to the semiconductor pattern.

15 In a method of fabricating the thin film transistor array substrate, a data line assembly including data lines is first formed on an insulating substrate. In the second step, color filters of red, green and blue are formed at the substrate. In the third step, a buffer layer is formed through depositing a CVD layer having dielectric constant 4.0 or less such that the 20 buffer layer covers the data line assembly and the color filters. In the fourth step, a gate line assembly is formed on the insulating layer. The gate line assembly includes gate lines, and gate electrodes. In the fifth step, a gate insulating layer is formed such that the gate insulating layer covers the gate

WO 03/036376

PCT/KR01/01896

line assembly. In the sixth step, an island-shaped ohmic contact pattern and an island-shaped semiconductor pattern are formed on the gate insulating layer while forming first contact holes at the gate insulating layer and the buffer layer such that the contact holes partially expose the data lines.

5 In the seventh step, a pixel line assembly is formed such that it includes source and drain electrodes formed on the island-shaped ohmic contact pattern at the same plane while being separated from each other, and pixel electrodes connected to the drain electrodes. In the eighth step, the ohmic contact pattern is divided into two pattern parts through removing the portions

10 of the ohmic contact pattern exposed between the source and the drain electrodes.

In the sixth step, an amorphous silicon layer and an impurities-doped amorphous silicon layer are sequentially deposited onto the gate insulating layer. A photoresist pattern is formed such that the photoresist pattern has

15 a first portion covering a predetermined area of the gate electrode with a predetermined thickness, and a second portion covering the remaining area except for the regions of first contact holes to be formed later with a thickness smaller than the thickness of the first portion. The impurities-doped amorphous silicon layer, the amorphous silicon layer, the gate insulating

20 layer and the buffer layer are etched using the first and second portions of the photoresist pattern as a mask to thereby form the first contact holes. The second portion of the photoresist pattern is then removed. The impurities-doped amorphous silicon layer and the amorphous silicon layer

WO 03/036376

PCT/KR01/01896

are etched using the first portion of the photoresist pattern as a mask to thereby form the island-shaped semiconductor pattern and the island-shaped ohmic contact pattern. The first portion of the photoresist pattern is then removed.

5 According to still another aspect of the present invention, the thin film transistor array substrate for a liquid crystal display includes an insulating substrate, and a gate line assembly formed on the substrate. The gate line assembly has gate lines, gate electrodes, and gate pads. A gate insulating layer is formed on the gate line assembly. The gate insulating layer has 10 contact holes exposing the gate pads. A semiconductor pattern is formed on the gate insulating layer. An ohmic contact pattern is formed on the semiconductor pattern. A data line assembly is formed on the ohmic contact pattern while bearing substantially the same shape as the ohmic contact pattern. The data line assembly has source electrodes, drain 15 electrodes, data lines, and data pads. A passivation pattern is formed on the data line assembly with a CVD layer having dielectric constant 4.0 or less. The passivation pattern has contact holes exposing the gate pads, the data pads, and the drain electrodes. A transparent electrode pattern is 20 electrically connected to the gate pads, the data pads, and the drain electrodes.

The thin film transistor array substrate may further include storage capacitor lines formed at the same plane as the gate line assembly, a storage capacitor semiconductor pattern overlapped with the storage

WO 03/036376

PCT/KR01/01896

capacitor lines while being placed at the same plane as the semiconductor pattern, a storage capacitor ohmic contact pattern formed on the storage capacitor semiconductor pattern while bearing the same outline as the storage capacitor semiconductor pattern, and a storage capacitor conductive pattern formed on the storage capacitor ohmic contact pattern while bearing the same outline as the storage capacitor semiconductor pattern. The storage capacitor conductive pattern is partially connected to the transparent electrode pattern.

In a method of fabricating the thin film transistor array substrate, a gate line assembly is first formed with gate lines, gate electrodes connected to the gate lines, and gate pads connected to the gate lines. A gate insulating layer is then formed on the gate line assembly, and a semiconductor layer is formed on the gate insulating layer. A data line assembly is then formed through depositing and patterning a conductive layer. The data line assembly includes data lines crossing over the gate lines, data pads connected to the data lines, source electrodes connected to the data lines while being placed close to the gate electrodes, and drain electrodes facing the source electrodes around the gate electrodes. A passivation layer is formed through depositing a low dielectric CVD. The gate insulating layer is patterned together with the passivation layer to thereby form contact holes exposing the gate pads, the data pads, and the drain electrodes. A transparent conductive layer is deposited, and patterned to thereby form subsidiary gate pads connected to the gate pads, subsidiary

WO 03/036376

PCT/KR01/01896

data pads connected to the data pads, and pixel electrodes connected to the drain electrodes.

The formation of the passivation layer is made through PECVD using a gaseous material selected from the group consisting of  $\text{SiH}(\text{CH}_3)_3$ ,  $5 \text{ SiO}_2(\text{CH}_3)_4$  and  $(\text{SiH})_4\text{O}_4(\text{CH}_3)_4$  as a basic source while introducing an oxide agent of  $\text{N}_2\text{O}$  or  $\text{O}_2$ . Alternatively, the formation of the passivation layer may be made through PECVD using a gaseous material selected from the group consisting of  $\text{SiH}_4$  and  $\text{SiF}_4$  as a basic source while adding  $\text{CF}_4$  and  $\text{O}_2$  thereto.

10 The data line assembly and the semiconductor layer are formed through photolithography using a photoresist pattern with a first portion bearing a predetermined thickness, a second portion bearing a thickness larger than the thickness of the first portion, and a third portion bearing a thickness smaller than the thickness of the first portion. The first photoresist 15 pattern portion is placed between the source and the drain electrodes, and the second photoresist pattern portion is placed over the data line assembly. The gate insulating layer may be formed through depositing a CVD layer having dielectric constant 4.0 or less in a vacuum state, and depositing a silicon nitride layer also in a vacuum state. The CVD layer has a dielectric 20 constant of 2-4.

#### BRIEF DESCRIPTION OF THE DRAWINGS

A more complete appreciation of the invention, and many of the attendant advantages thereof, will be readily apparent as the same becomes

WO 03/036376

PCT/KR01/01896

better understood by reference to the following detailed description when considered in conjunction with the accompanying drawings in which like reference symbols indicate the same or the similar components, wherein:

Fig. 1 is a plan view of a thin film transistor array substrate for a liquid crystal display according to a first preferred embodiment of the present invention;

Fig. 2 is a cross sectional view of the thin film transistor array substrate taken along the II-II' line of Fig. 1;

Figs. 3A, 4A, 5A and 6A sequentially illustrate the steps of fabricating the thin film transistor array substrate shown in Fig. 1;

Fig. 3B is a cross sectional view of the thin film transistor array substrate taken along the IIIb-IIIb' line of Fig. 3A;

Fig. 4B is a cross sectional view of the thin film transistor array substrate taken along the IVb-IVb' line of Fig. 4A;

Fig. 5B is a cross sectional view of the thin film transistor array substrate taken along the Vb-Vb' line of Fig. 5A;

Fig. 6B is a cross sectional view of the thin film transistor array substrate taken along the VIb-VIb' line of Fig. 6A;

Fig. 7 is a plan view of a thin film transistor array substrate for a liquid crystal display according to a second preferred embodiment of the present invention;

Figs. 8 and 9 are cross sectional view of the thin film transistor array substrate taken along the VIII-VIII' line and the IX-IX' line of Fig. 7,

WO 03/036376

PCT/KR01/01896

respectively;

Fig. 10A illustrates the first step of fabricating the thin film transistor array substrate shown in Fig. 7;

Figs. 10B and 10C are cross sectional views of the thin film transistor array substrate taken along the Xb-Xb' line and the Xc-Xc' line of Fig. 10A, respectively;

Figs. 11A and 11B illustrate the step of fabricating the thin film transistor array substrate following the step illustrated in Figs. 10B and 10C;

Fig. 12A illustrates the step of fabricating the thin film transistor array substrate following the step illustrated in Fig. 10A;

Figs. 12B and 12C are cross sectional views of the thin film transistor array substrate taken along the XIb-XIb' line and the XIc-XIc' line of Fig. 12A, respectively;

Figs. 13A to 15B illustrate the steps of fabricating the thin film transistor array substrate following the step illustrated in Fig. 12A;

Figs. 16A and 16B illustrate the step of fabricating the thin film transistor array substrate following the step illustrated in Figs. 15A and 15B;

Fig. 17A illustrate the step of fabricating the thin film transistor array substrate following the step illustrated in Figs. 16A and 16B;

20 Figs. 17B and 17C are cross sectional views of the thin film transistor array substrate taken along the XVIIb-XVIIb' line and the XVIIc-XVIIc' line of Fig. 17A, respectively;

Fig. 18 is a plan view of a thin film transistor array substrate

WO 03/036376

PCT/KR01/01896

according to a third preferred embodiment of the present invention;

Fig. 19 is a cross sectional view of a thin film transistor array substrate taken along the XIX-XIX' line of Fig. 18;

Fig. 20A illustrates the first step of fabricating the thin film transistor array substrate shown in Fig. 18;

Fig. 20B is a cross sectional view of the thin film transistor array substrate taken along the XXb-XXb' line of Fig. 20A;

Fig. 21A illustrates the step of fabricating the thin film transistor array substrate following the step illustrated in Fig. 20A;

Fig. 21B is a cross sectional view of the thin film transistor array substrate taken along the XXIb-XXIb' line of Fig. 21A;

Fig. 22A illustrates the step of fabricating the thin film transistor array substrate following the step illustrated in Fig. 21A;

Fig. 22B is a cross sectional view of the thin film transistor array substrate taken along the XXIb-XXIb' line of Fig. 22A;

Fig. 23 illustrates the step of fabricating the thin film transistor array substrate following the step illustrated in Fig. 22A;

Fig. 24A illustrates the step of fabricating the thin film transistor array substrate following the step illustrated in Fig. 23;

Fig. 24B is a cross sectional view of the thin film transistor array substrate taken along the XXIVb-XXIVb' line of Fig. 24A;

Figs. 25 and 26 illustrate the sub-steps of fabricating the thin film transistor array substrate during the steps illustrated in Figs. 23 and 24A;

Fig. 27A illustrates the step of fabricating the thin film transistor array substrate following the step illustrated in Fig. 24A;

Fig. 27B is a cross sectional view of the thin film transistor array substrate taken along the XXVIIb-XXVIIb' line of Fig. 27A;

5 Fig. 28 is a plan view of a thin film transistor array substrate according to a fourth preferred embodiment of the present invention;

Fig. 29 is a plan view of a thin film transistor array substrate for a reflection type liquid crystal display according to a fifth preferred embodiment of the present invention;

10 Fig. 30 is a cross sectional view of the thin film transistor array substrate taken along the XXX-XXX' line of Fig. 29;

Figs. 31A, 32A, 33A and 34A sequentially illustrate the steps of fabricating the thin film transistor array substrate shown in Fig. 29;

15 Fig. 31B is a cross sectional view of the thin film transistor array substrate taken along the XXXIb-XXXIb' line of Fig. 31A;

Fig. 32B is a cross sectional view of the thin film transistor array substrate taken along the XXXIIb-XXXIIb' line of Fig. 32A;

Fig. 33B is a cross sectional view of the thin film transistor array substrate taken along the XXXIIIb-XXXIIIb' line of Fig. 33A;

20 Fig. 34B is a cross sectional view of the thin film transistor array substrate taken along the XXXIVb-XXXIVb' line of Fig. 34A;

Fig. 35 is a plan view of a thin film transistor array substrate for a semi-transparent liquid crystal display according to a sixth preferred

WO 03/036376

PCT/KR01/01896

embodiment of the present invention;

Fig. 36 is a cross sectional view of the thin film transistor array substrate taken along the XXXVI-XXXVI' line of Fig. 35;

Figs. 37A, 38A and 39A sequentially illustrate the steps of fabricating 5 the thin film transistor array substrate shown in Fig. 35;

Fig. 37B is a cross sectional view of the thin film transistor array substrate taken along the XXXVIIb-XXXVIIb' line of Fig. 37A;

Fig. 38B is a cross sectional view of the thin film transistor array substrate taken along the XXXVIIIb-XXXVIIIb' line of Fig. 38A;

10 Fig. 39B is a cross sectional view of the thin film transistor array substrate taken along the XXXIXb-XXXIXb' line of Fig. 39A; and

Fig. 40 is a cross sectional view of a thin film transistor array substrate according to a seventh preferred embodiment of the present invention.

15 **DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS**

Preferred embodiments of this invention will be explained with reference to the accompanying drawings.

Fig. 1 is a plan view of a thin film transistor array substrate for a liquid crystal display according to a first preferred embodiment of the present 20 invention, and Fig. 2 is a cross sectional view of the thin film transistor array substrate taken along the II-II line of Fig. 1.

A gate line assembly is formed on an insulating substrate 10 with a double-layered structure. The gate line assembly has a first layer 221, 241

WO 03/036376

PCT/KR01/01896

and 261 formed with chrome Cr alloy or molybdenum Mo alloy, and a second layer 222, 242 and 262 formed with aluminum Al or silver Ag alloy. The gate line assembly includes gate lines 22 proceeding in the horizontal direction, gate pads 24 connected to the gate lines 22 to receive gate signals 5 from the outside and transmit them to the gate lines 22, and gate electrodes 26 connected to the gate lines 22 to function as parts of thin film transistors.

A gate insulating layer 30 is formed on the substrate 10 with silicon nitride SiNx such that it covers the gate line assembly.

A semiconductor layer 40 is formed on the gate insulating layer 30 10 over the gate electrodes 24 with amorphous silicon while bearing the shape of island. An ohmic contact layer 54 and 56 is formed on the semiconductor layer 40 with silicide, or n<sup>+</sup> hydrogenated amorphous silicon where n-type impurities are doped at high concentration.

A data line assembly is formed on the ohmic contact layer 54 and 56 15 and the gate insulating layer 30 with a double-layered structure. The data line assembly has a first layer 621, 651, 661 and 681 formed with Cr alloy or Mo alloy, and a second layer 622, 652, 662 and 682 formed with Al alloy or Ag alloy. The data line assembly includes data lines 62 proceeding in the vertical direction, source electrodes branched from the data lines 62 while 20 being extended over the one-sided portion 54 of the ohmic contact layer, data pads 68 connected to the one-sided ends of the data lines 62 to receive picture signals from the outside, and drain electrodes 66 separated from the source electrodes 65 around the gate electrodes 26 while being placed on

WO 03/036376

PCT/KR01/01896

the other-sided portion 56 of the ohmic contact layer. The data lines 62 cross over the gate lines 22 while defining pixel regions.

A passivation layer 70 is formed on the data line assembly and the semiconductor layer 40 through depositing a layer of a-Si:C:O or a-Si:O:F (a 5 low dielectric CVD film) by way of plasma enhanced chemical vapor deposition (PECVD). The a-Si:C:O or a-Si:O:F-based layer bears a dielectric constant of 4 or less (the dielectric constant being ranged from 2 to 4). Therefore, the passivation layer 70 does not involve the problem of parasitic capacitance even if it bears a thin thickness. Furthermore, the 10 passivation layer 70 involves good adhesion characteristic and step coverage characteristic in relation to other layers. As the passivation layer 70 is based on a low dielectric CVD film, it bears excellent thermostability compared to that based on an organic insulating film. In addition, the a-Si:C:O or a-Si:O:F-based layer deposited through PECVD exhibits an 15 advantage in the processing time as the deposition speed or etching speed related thereto is rapid by four to ten times compared to that related to a silicon nitride-based layer.