(12) 发明专利

(10) 授权公告号 CN 108122937 B

(45) 授权公告日 2022.02.11

(21) 申请号 201711200024.1

(51) Int.CI.

(22) 申请日 2017.11.27

H01L 27/146 (2006.01)

(65) 同一申请的已公布的文献号

申请公布号 CN 108122937 A

(43) 申请公布日 2018.06.05

(56) 对比文件

CN 104917980 A, 2015.09.16

(30) 优先权数据

CN 104917980 A, 2015.09.16

2016-232726 2016.11.30 JP

CN 102202189 A, 2011.09.28

(73) 专利权人 佳能株式会社

JP 2012124611 A, 2012.06.28

地址 日本东京

CN 105934826 A, 2016.09.07

(72) 发明人 关根宽 大贯裕介 小林昌弘

CN 102017149 A, 2011.04.13

(74) 专利代理机构 中国贸促会专利商标事务所

有限公司 11038

JP WO2007119626 A1, 2009.08.27

代理人 杨小明

US 2012193692 A1, 2012.08.02

CN 104469200 A, 2015.03.25

审查员 杨娇

(54) 发明名称

权利要求书2页 说明书10页 附图12页

成像器件

(57) 摘要

提供一种成像器件，该成像器件包括：基板；在基板上以二维方式布置像素的像素阵列，各像素包括蓄积从入射光产生的电荷的光电转换单元、保持从光电转换单元传送的电荷的电荷保持单元和接收从电荷保持单元传送的电荷的放大单元；和被布置为至少覆盖电荷保持单元的遮光部分。在与基板正交的俯视图中，各像素的光电转换单元和电荷保持单元沿第一方向对准。在俯视图中，相邻像素的电荷保持单元沿与第一方向相交的第二方向对准。遮光部分沿第二方向且在电荷保持单元之上延伸，并且覆盖电荷保持单元之间的区域。

1. 一种成像器件,其特征在于,包括:

基板;

像素阵列,在像素阵列中,多个像素以二维方式布置在基板上,其中,所述像素中的每一个包括被配置为蓄积从入射光产生的电荷的光电转换单元、被配置为保持从光电转换单元传送的电荷的电荷保持单元和具有接收从电荷保持单元传送的电荷的输入节点的放大单元;和

遮光部分,被布置为至少覆盖电荷保持单元,

其中,在与基板正交的方向的俯视图中,包含于所述像素中的一个中的光电转换单元和电荷保持单元沿第一方向对准,

其中,在俯视图中,所述像素中的相互邻近的多个的多个电荷保持单元沿与第一方向相交的第二方向对准,

其中,遮光部分沿第二方向且在多个电荷保持单元之上延伸,并且覆盖多个电荷保持单元之间的区域,

其中,所述像素中的每一个还包含多个触点,所述多个触点连接对基板设置的电极和在基板之上形成的布线层,以及

其中,在俯视图中,所述多个触点形成在沿第一方向对准的多个电荷保持单元之间的区域中,以及

其中,遮光部分包括沿第一方向延伸并且被设置在光电转换单元和所述多个触点之间的部分。

2. 根据权利要求1所述的成像器件,其中,布线层被布置为覆盖电荷保持单元。

3. 根据权利要求1所述的成像器件,其中,在俯视图中,遮光部分具有均在形成光电转换单元的区域中形成的第一开口和均在形成多个触点的区域中形成的第二开口。

4. 根据权利要求3所述的成像器件,其中,包含于所述像素中的一个中的多个触点聚集在第二开口中的相应一个下面。

5. 根据权利要求1所述的成像器件,

其中,使光电转换单元与电荷保持单元相互电气隔离的元件隔离区域被布置在像素阵列中,以及

其中,元件隔离区域由限制光入射到电荷保持单元的材料形成。

6. 根据权利要求5所述的成像器件,其中,元件隔离区域是形成PN结隔离的杂质扩散区域。

7. 根据权利要求1所述的成像器件,

其中,像素阵列被成形为具有长边和短边的矩形,以及

其中,第二方向与所述长边平行。

8. 根据权利要求1所述的成像器件,

其中,所述像素中的每一个包含多个电荷保持单元,以及

其中,在俯视图中,所述多个电荷保持单元被布置为沿第二方向对准。

9. 根据权利要求1所述的成像器件,

其中,所述像素中的每一个包含多个电荷保持单元,以及

其中,在俯视图中,所述多个电荷保持单元被布置为夹着光电转换单元沿第一方向对

准。

10. 根据权利要求1所述的成像器件,其中,在俯视图中,被配置为读出在光电转换单元中产生的电荷作为电信号的读出电路单元被布置于沿第二方向对准的多个电荷保持单元之间的区域中。

11. 根据权利要求1所述的成像器件,其中,遮光部分从像素阵列的一端到像素阵列的另一端是连续的,从而覆盖沿第二方向形成列的多个电荷保持单元。

12. 根据权利要求1所述的成像器件,

其中,所述像素中的每一个还包含晶体管,所述晶体管包含栅电极并且将电荷从光电转换单元传送到电荷保持单元,以及

其中,在俯视图中,多个电荷保持单元中的相互邻近的两个电荷保持单元的间隔小于晶体管的栅电极的宽度。

13. 一种成像系统,其特征在于包括:

根据权利要求1~12中的任一项所述的成像器件;和

被配置为处理从成像器件的像素输出的信号的信号处理单元。

14. 一种移动装置,其特征在于包括:

根据权利要求1~12中的任一项所述的成像器件;

距离信息获取单元,被配置为从基于来自成像器件的信号的视差图像获取到物体的距离的距离信息;和

移动装置控制单元,被配置为基于距离信息控制移动装置。

## 成像器件

### 技术领域

[0001] 本发明涉及成像器件。

### 背景技术

[0002] 近年,允许低功耗和快速读出的CMOS图像传感器被广泛用作用于诸如数字静态照相机或数字视频摄像机等的成像系统的成像器件。作为成像器件中的读出方法,已提出所有像素具有共同的电荷蓄积开始时间和结束时间的全局电子快门。

[0003] 在日本专利申请公开No.2009-272374所公开的成像器件的各像素内,除了执行光电转换的光电转换单元以外,为了实现全局电子快门的功能,还设置将由光电转换单元产生的电荷保持预定时段的电荷保持单元。当光入射到电荷保持单元时,由电荷保持单元光电转换的电荷形成错误信号,这会导致图像质量的劣化。因此,覆盖电荷保持单元的遮光部分被设置在日本专利申请公开No.2009-272374的成像器件中。

[0004] 在日本专利申请公开No.2009-272374的技术中,遮光部分的开口的多个边缘在俯视图中被布置为接近电荷保持单元的端部,这会导致遮光不足。因此,入射到电荷保持单元的光会导致错误信号,该错误信号导致图像质量的劣化。

### 发明内容

[0005] 本发明意欲提供减少由于错误信号导致的图像质量劣化的成像器件。

[0006] 根据本发明的一个实施例,提供一种成像器件,该成像器件包括:基板;像素阵列,在像素阵列中,多个像素以二维方式布置在基板上,其中,所述像素中的每一个包括被配置为蓄积从入射光产生的电荷的光电转换单元、被配置为保持从光电转换单元传送的电荷的电荷保持单元和具有接收从电荷保持单元传送的电荷的输入节点的放大单元;以及,遮光部分,被布置为至少覆盖电荷保持单元。在与基板正交的方向的俯视图中,包含于所述像素中的一个中的光电转换单元和电荷保持单元沿第一方向对准。在俯视图中,所述像素中的相互邻近的多个的多个电荷保持单元沿与第一方向相交的第二方向对准。遮光部分沿第二方向且在多个电荷保持单元之上延伸,并且覆盖多个电荷保持单元之间的区域。

[0007] 根据本发明,可以提供减少由于错误信号导致的图像质量劣化的成像器件。

[0008] 从参照附图对示例性实施例的以下描述,本发明的其它特征将变得清晰。

### 附图说明

[0009] 图1是根据本发明的第一实施例的成像器件的框图。

[0010] 图2是根据本发明的第一实施例的成像器件中的像素的等价电路图。

[0011] 图3A和图3B是根据本发明的第一实施例的成像器件中的像素的平面图。

[0012] 图4是根据本发明的第一实施例的成像器件中的像素的平面图。

[0013] 图5是根据本发明的第一实施例的成像器件中的像素的截面图。

[0014] 图6A和图6B是根据本发明的第二实施例的成像器件中的像素的平面图。

- [0015] 图7A和图7B是根据本发明的第三实施例的成像器件中的像素的平面图。

- [0016] 图8A和图8B是根据本发明的第四实施例的成像器件中的像素的平面图。

- [0017] 图9是根据本发明的第五实施例的成像系统的框图。

- [0018] 图10A和图10B是根据本发明的第六实施例的成像系统和移动装置的框图。

## 具体实施方式

[0019] 现在将根据附图详细描述本发明的优选实施例。在多个附图中始终具有相同功能的部件由相同的附图标记表示，并且，其描述可能被省略或简化。

### [0020] 第一实施例

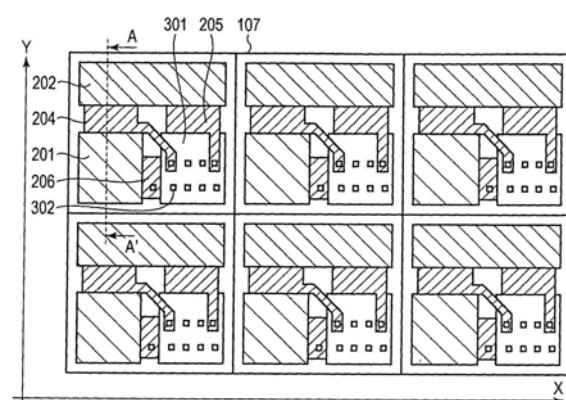

[0021] 图1是示出根据本实施例的成像器件100的总体构造的框图。成像器件100具有像素阵列101、垂直扫描电路102、列放大电路103、水平扫描电路104、输出电路105和控制电路106。成像器件100是在诸如硅基板的半导体基板上形成的半导体器件，并且在本实施例中是CMOS图像传感器。像素阵列101具有在半导体基板上以包含多个行和多个列的二维方式布置的多个像素107。垂直扫描电路102供给用于控制包含于像素107中的多个晶体管以接通(导通状态)或关断(非导通状态)的多个控制信号。列信号线108被设置在像素107的各列上，并且，来自像素107的信号以列为基础上被读出到列信号线108。列放大电路103放大被输出到列信号线108的像素信号，并且基于像素107的复位时的信号和光电转换时的信号对其进行执行诸如相关双重采样等的处理。水平扫描电路104具有连接到列放大电路103的放大器的开关，并且供给控制信号以将开关控制为开或关。控制电路106控制垂直扫描电路102、列放大电路103和水平扫描电路104。输出电路105包含缓冲放大器或差动放大器等，并且将来自列放大电路103的像素信号输出到成像器件100外面的信号处理单元。并且，可以对成像器件100设置模拟数字(AD)转换单元，并且，成像器件100可由此被配置为输出数字像素信号。

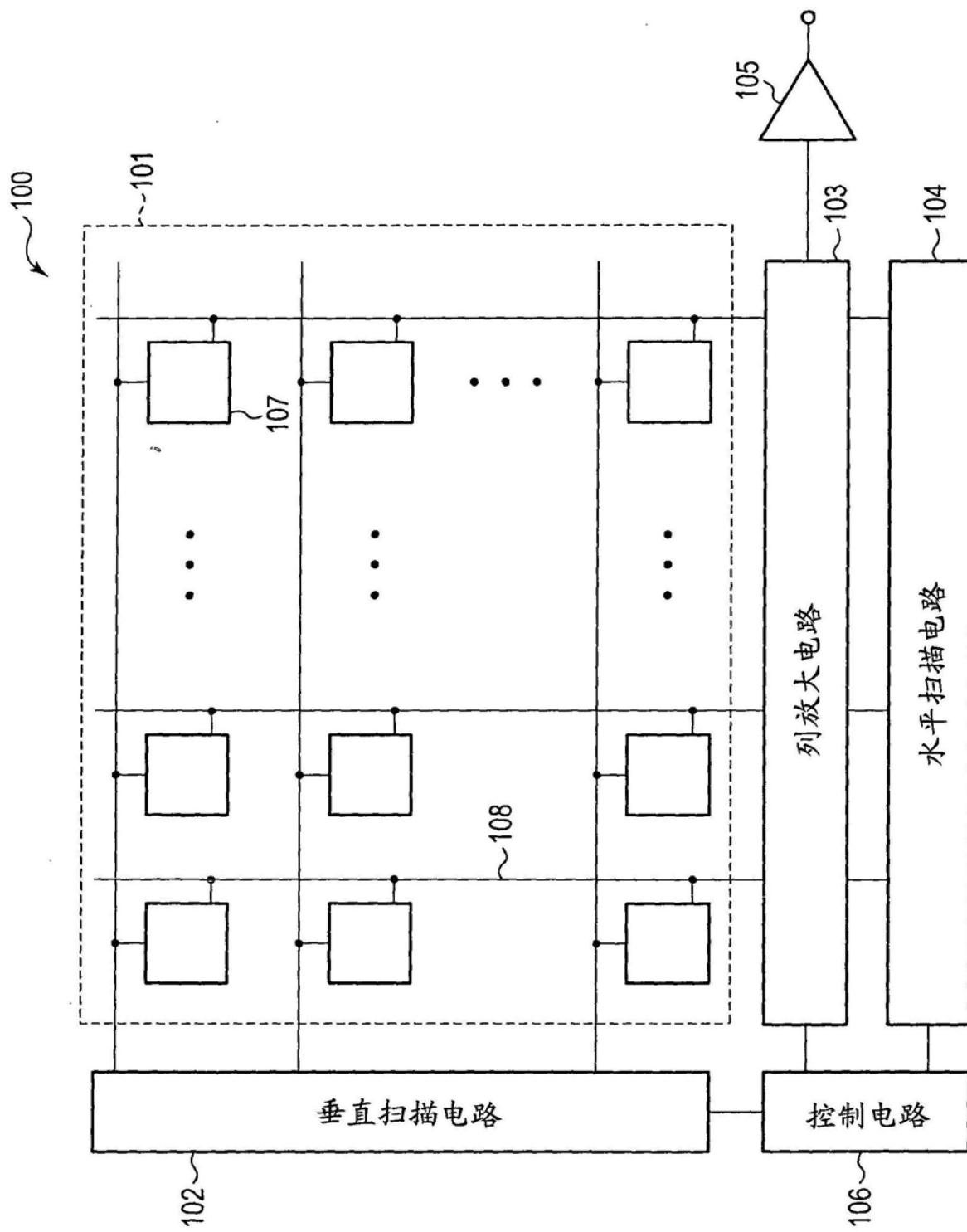

[0022] 图2是示出根据本实施例的成像器件100的像素107的等价电路的示图。图2示出沿行方向和列方向二维布置的多个像素107中的3行×3列的9个像素107。但是，这仅是示出多个像素107的一部分的例子，并且成像器件100可以具有更多的像素。各像素107包含光电转换单元201、电荷保持单元202、第一传送晶体管204、第二传送晶体管205和溢流晶体管206。并且，各像素107包含复位晶体管209、放大晶体管210和选择晶体管207。第一传送晶体管204、第二传送晶体管205、溢流晶体管206、选择晶体管207、复位晶体管209和放大晶体管210中的每一个可由MOS晶体管形成。控制这些晶体管中的每一个的各控制信号经由控制线从垂直扫描电路102被输入到各晶体管的栅极。虽然描述将集中于第(m+1)行和第(p+1)列处的像素107中的一个，但是其它的像素107可以具有相同的构造。

[0023] 光电转换单元201光电转换入射光并且蓄积由光电转换产生的信号电荷。第一传送晶体管204由输入到其栅极的控制信号pTX1(m+1)控制，并且，当接通时，将光电转换单元201的电荷传送到电荷保持单元202。电荷保持单元202保持从光电转换单元201传送的电荷。第二传送晶体管205由输入到其栅极的控制信号pTX2(m+1)控制，并且，当接通时，将电荷保持单元202的电荷传送到作为放大晶体管210的输入节点的浮置扩散部分203。即，用作放大单元的放大晶体管210包含用作接收从电荷保持单元202传送的电荷的输入节点的浮置扩散部分203。

[0024] 放大晶体管210的漏极连接到电源电压线212，并且放大晶体管210的源极连接到

选择晶体管207的漏极。选择晶体管207的源极连接到列信号线108。列信号线108与恒流源(未示出)连接。选择晶体管207由输入到其栅极的控制信号pSEL (m+1)控制,并且当接通时,使得放大晶体管210的源极连接到列信号线108以用作源极跟随器。此时,基于浮置扩散部分203的电压的输出信号Vout (p+1)经由各列上的列信号线108被输出到列放大电路103。

[0025] 复位晶体管209由输入到其栅极的控制信号pRES (m+1)控制,并且,当接通时,复位浮置扩散部分203的电压。溢流晶体管206的源极连接到光电转换单元201。溢流晶体管206的漏极连接到具有电源电压的诸如溢流漏极的节点,并且在图2中被描述为以等价的方式连接到电源电压线212。溢流晶体管206由输入到其栅极的控制信号pOFG (m+1)控制,并且,当被接通时,使得蓄积于光电转换单元201中的电荷排出到电源电压线212等。

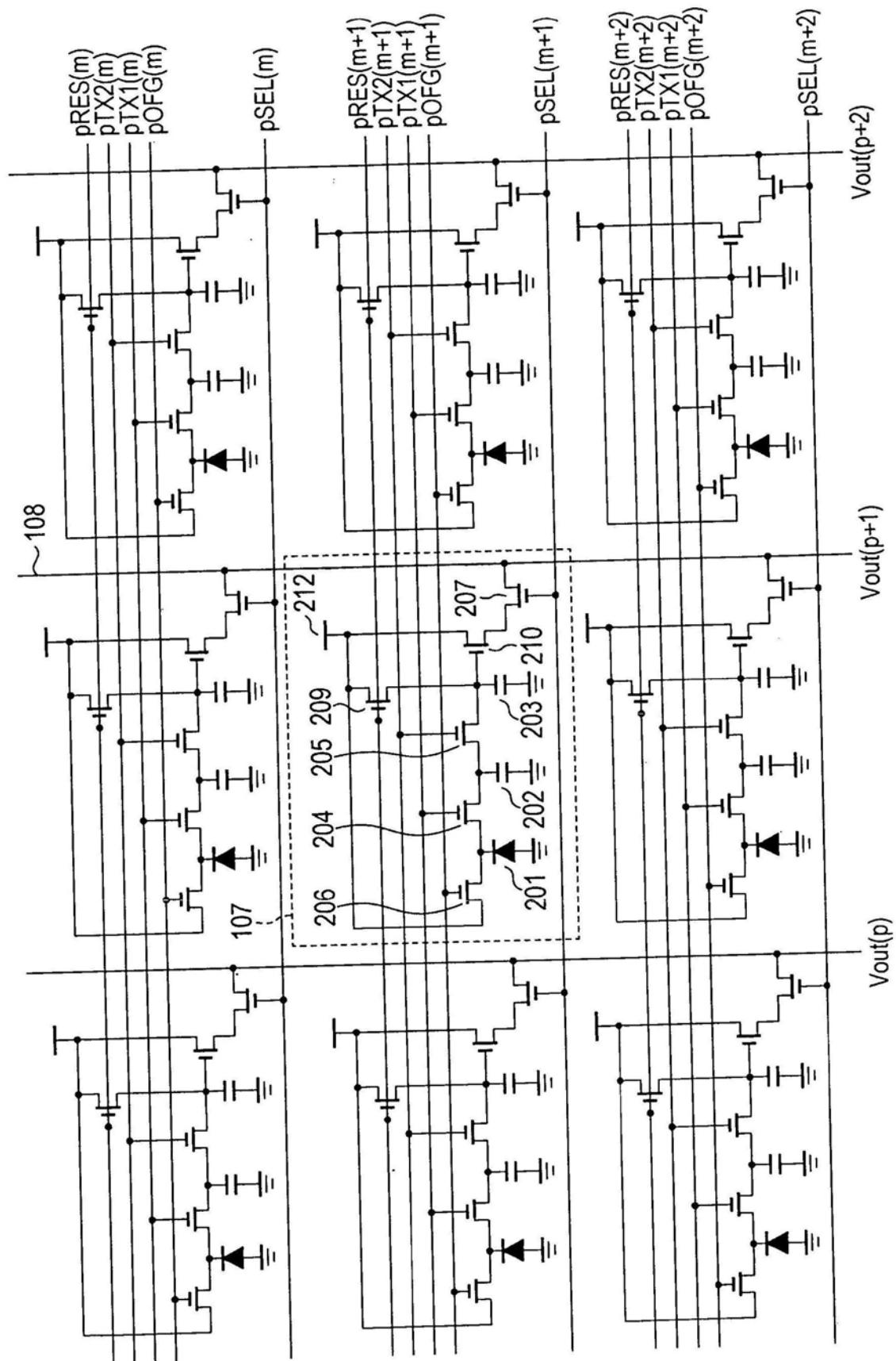

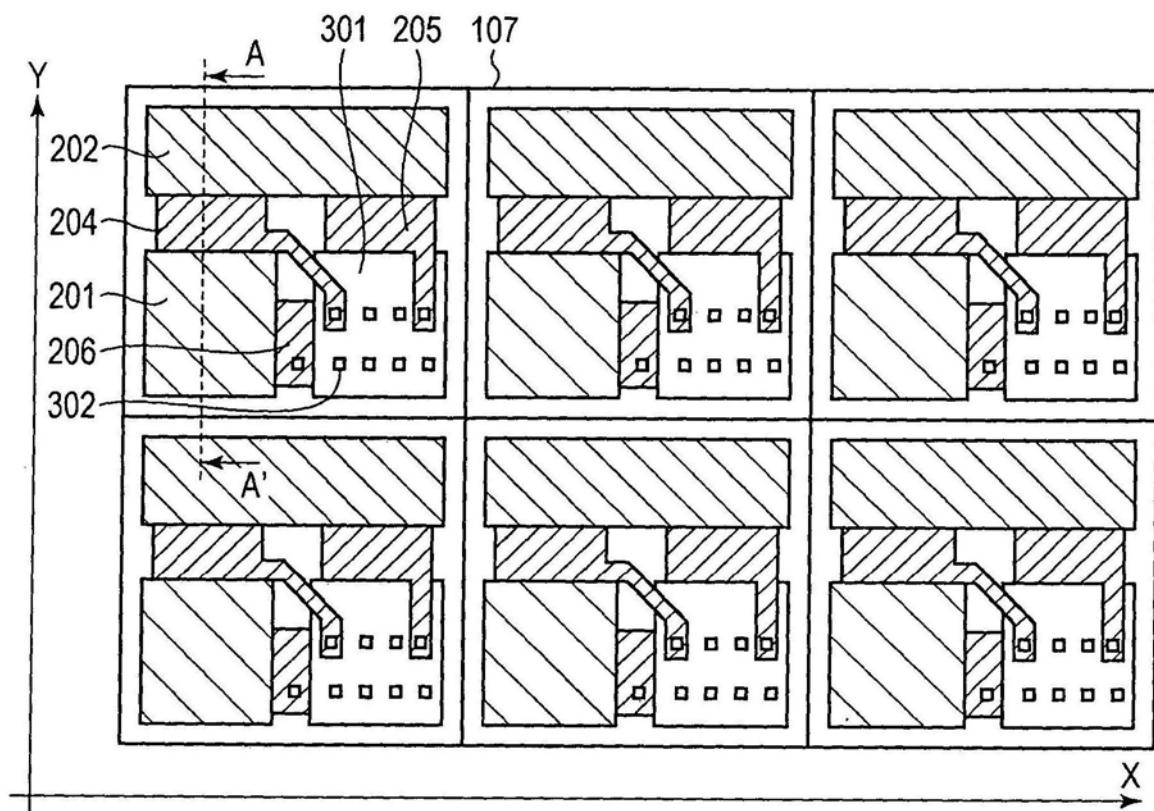

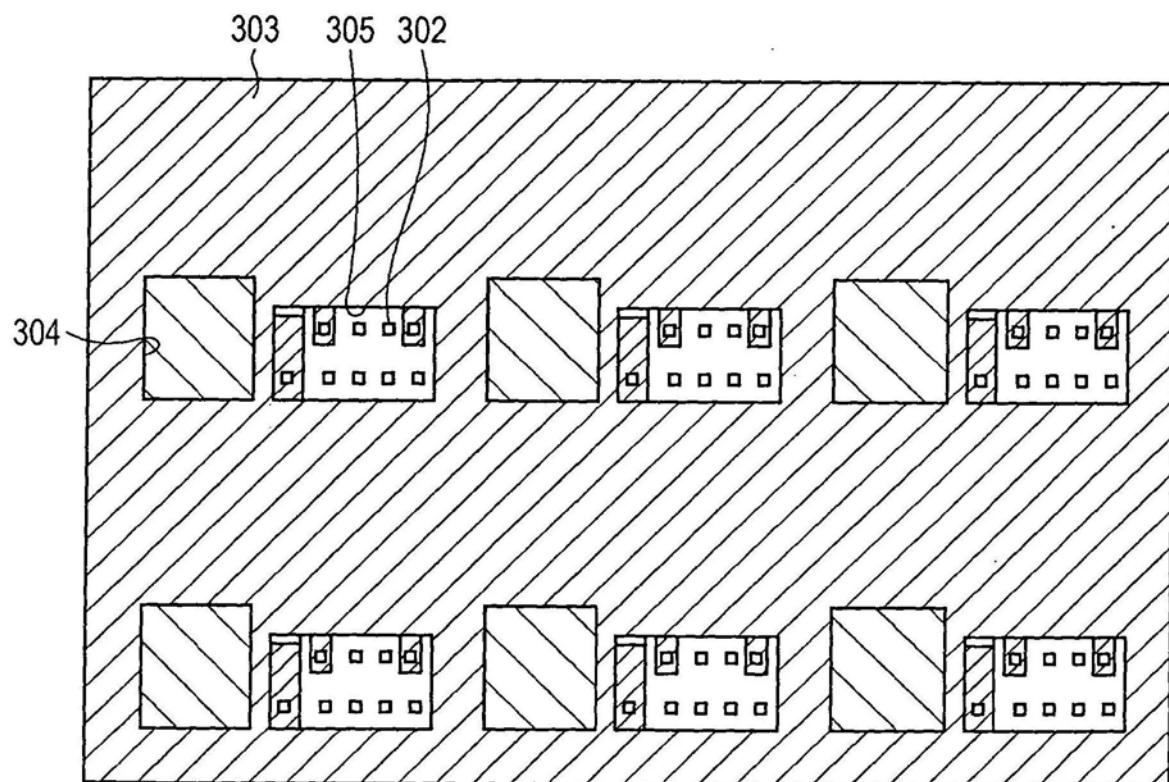

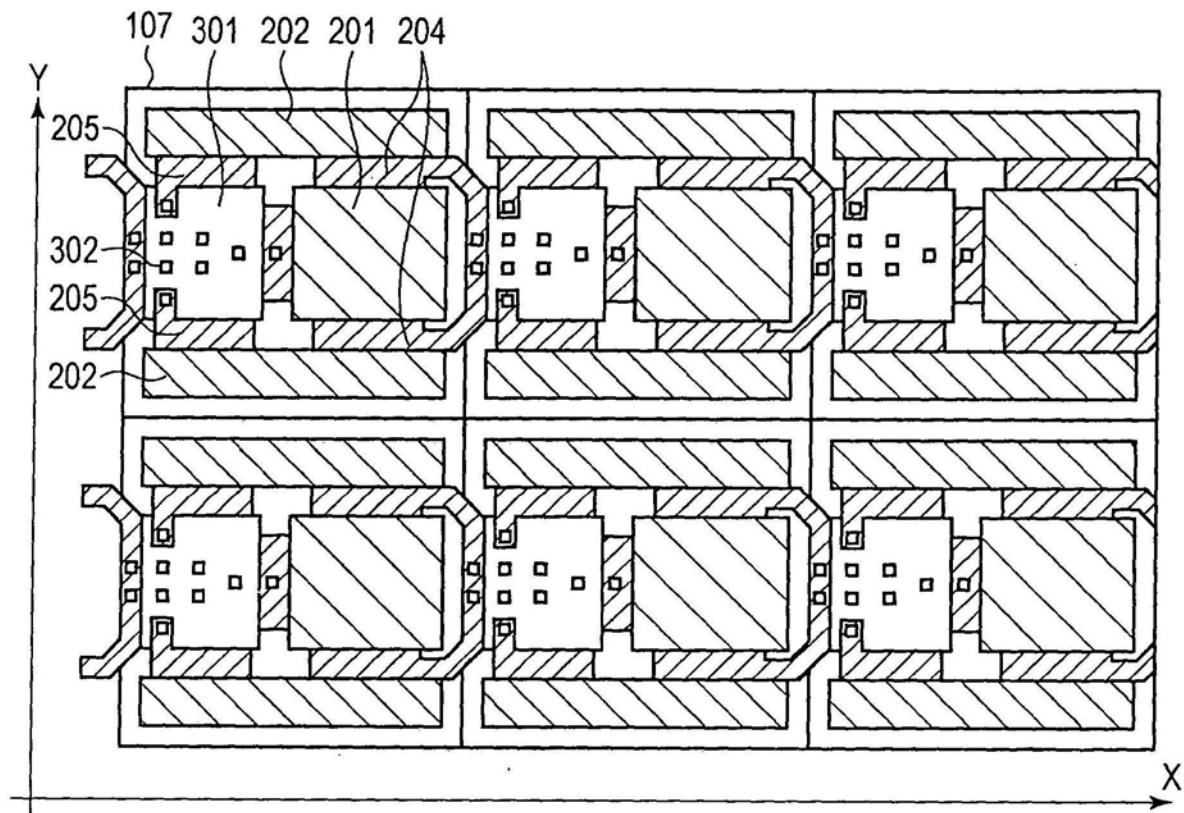

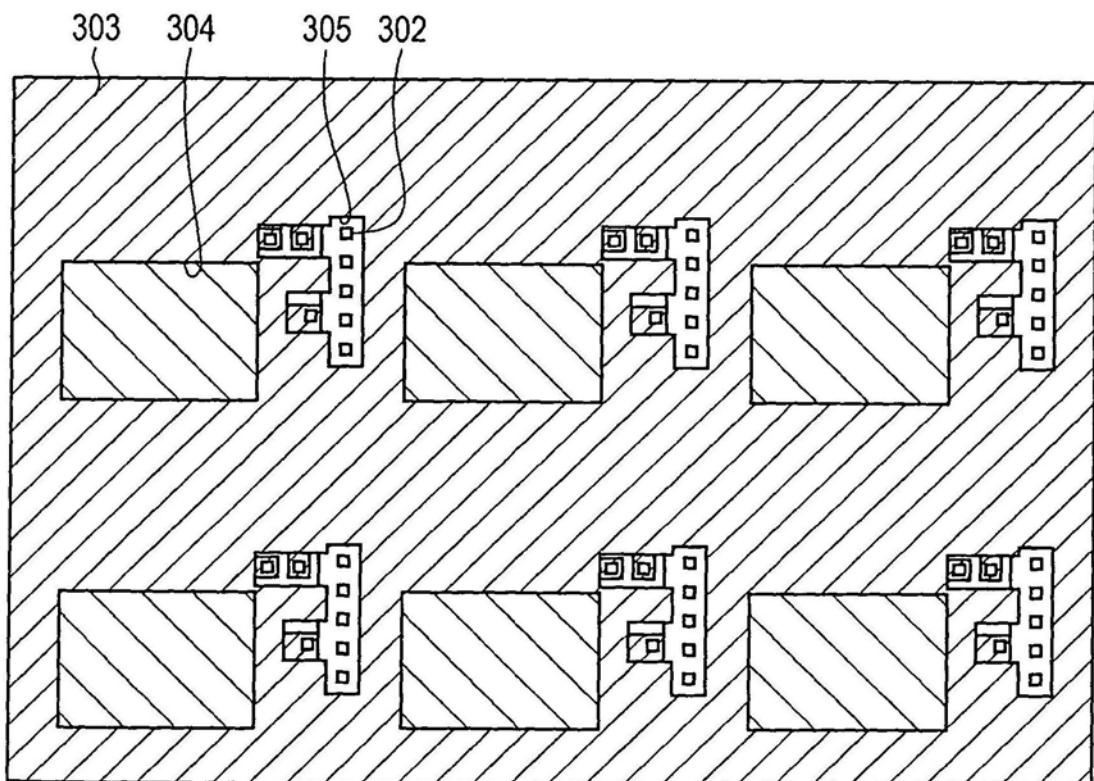

[0026] 图3A和图3B是根据本实施例的成像器件100的像素107的平面图。图3A是在与半导体基板正交的方向的俯视图中示意性地示出半导体基板表面周围的图案的平面图,图3B是主要示意性地示出在半导体基板之上形成的遮光部分303的图案的平面图。在图3A中,具有与图1和图2相同的功能的部分由相同的附图标记表示,并且,其功能的描述将被省略。图3A中的读出电路单元301被示为包含选择晶体管207、复位晶体管209和放大晶体管210的一个块。即,读出电路单元301是用于读出由光电转换单元201产生的电荷作为电信号的一组电路。并且,读出电路单元301包含形成溢流漏极的半导体区域和形成浮置扩散部分203的半导体区域。形成溢流漏极的半导体区域被布置为与溢流晶体管206的栅电极相邻。形成浮置扩散部分203的半导体区域被布置为与第二传送晶体管205的栅电极相邻。并且,像素107具有将设置在半导体基板上的杂质扩散层或诸如栅电极的电极等连接到在半导体基板之上形成的布线层的多个触点302。

[0027] 在图3A所示的各像素107中,光电转换单元201和读出电路单元301被布置为夹着溢流晶体管206的栅电极沿X方向(第二方向)对准。并且,光电转换单元201和电荷保持单元202被布置为夹着第一传送晶体管204的栅电极沿与X方向相交的Y方向(第一方向)对准。在本实施例中,X方向和Y方向相互正交。并且,电荷保持单元202和读出电路单元301被布置为夹着第二传送晶体管205的栅电极沿Y方向对准。在相邻的像素107中提供相同的布置,并且,相邻的像素107的电荷保持单元202被布置为沿X方向对准。多个触点302被布置在布置读出电路单元301的区域中或附近。更具体而言,多个触点302在除沿X方向对准的多个电荷保持单元202之间的区域以外的区域中形成。并且,多个电荷保持单元202中的相互邻近的两个电荷保持单元202的间隙小于第一传送晶体管204的栅电极的宽度。这里,栅电极的宽度对应于第一传送晶体管204的沟道方向上的长度。

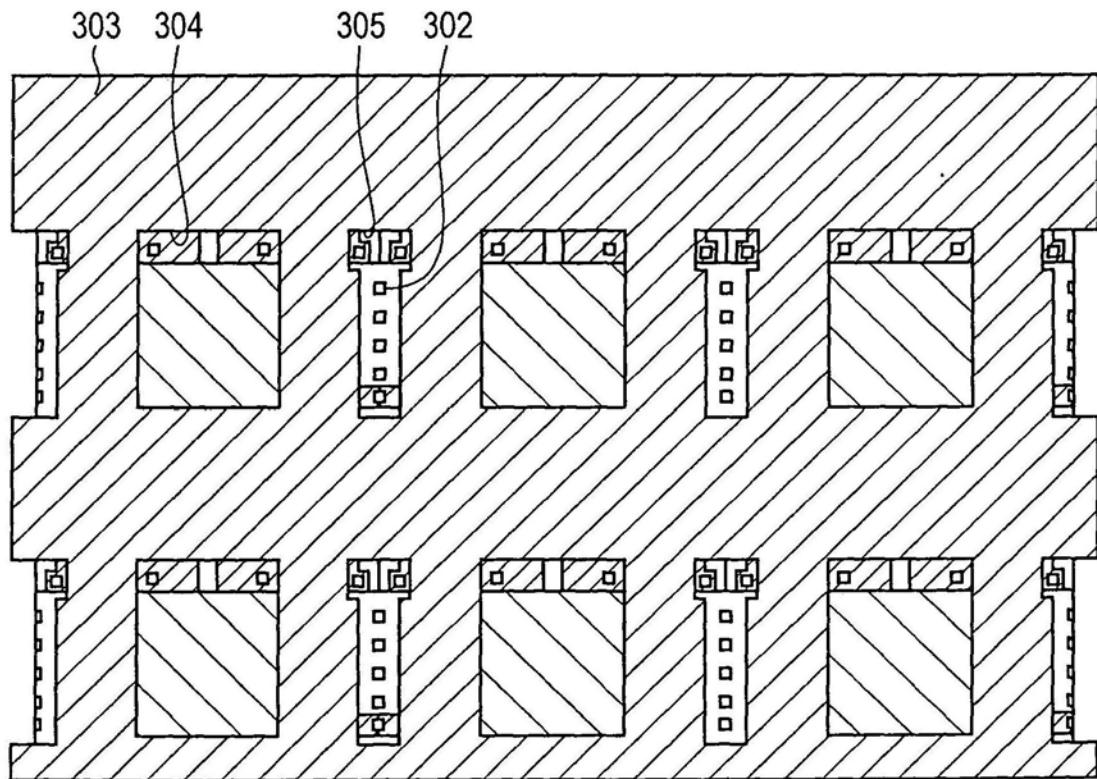

[0028] 图3B示出被布置为至少覆盖电荷保持单元202的遮光部分303的图案。在俯视图中,遮光部分303具有在形成光电转换单元201的区域中形成的开口304(第一开口)。并且,遮光部分303具有在多个相邻像素107的光电转换单元201之间的并且在其中形成读出电路单元301的区域中形成的开口305(第二开口)。即,在本实施例中,遮光部分303被布置为覆盖除开口304和开口305以外的像素107的整个表面。图3B示出在2行×3列的矩阵中布置的6个像素。优选在整个像素阵列上重复相同的对准。在这种情况下,优选从像素阵列的一端到另一端,所述对准是连续的,以覆盖沿X方向形成一个行的多个电荷保持单元202。遮光部分303是经由绝缘层(未示出)在半导体基板之上形成的层,并且由不太可能透光的材料制成。钨用于遮光部分303。此外,诸如铝或铜等的金属可用于遮光部分303。

[0029] 在读出电路单元301之上设置开口305的原因是为了避免触点302与遮光部分303之间的导通。因此,开口305的形状可以是任何形状,只要它不与触点302导通即可,并且,相对于读出电路单元301的位置关系是不受限的。例如,在俯视图中,开口305可被布置为覆盖读出电路单元301的没设置触点302的至少一部分。并且,开口305可被布置为使包含读出电路单元301周围的部分的区域开放。

[0030] 在读出电路单元301的光电转换单元201之上设置开口304的原因是为了允许光入射到光电转换单元201。注意,为了减少错误信号的出现,在电荷保持单元202之上设置遮光部分303,并且,电荷保持单元202由此被遮光。为了减少当斜入射光等泄漏到电荷保持单元202时可能出现的错误信号的影响,希望尽可能多地将电荷保持单元202周围的部分之上的区域遮光。因此,希望遮光部分303的开口304的端部被布置为尽可能地远离电荷保持单元202。

[0031] 如上所述,在本实施例中,光电转换单元201和读出电路单元301被布置在电荷保持单元202与Y方向平行地移动的位置中。但是,在电荷保持单元202与X方向平行地移动的位置中,布置相邻像素的电荷保持单元202,并且,不布置光电转换单元201、读出电路单元301和触点302中的任一个。因此,虽然遮光部分303的多个开口304和305被布置在电荷保持单元202与Y方向平行地移动的位置中,但是不在电荷保持单元202与X方向平行地移动的位置中布置遮光部分303的多个开口304和305中的任一个。换句话说,在俯视图中,遮光部分303沿X方向跨着多个电荷保持单元202延伸以覆盖沿X方向对准的多个电荷保持单元202之间的区域。

[0032] 在日本专利申请公开No.2009-272374中,在俯视图中,遮光部分的开口边缘被布置在电荷保持单元的端部附近。在该结构中,当存在来自斜方向等的入射光时,光可以从开口的端部泄漏到电荷保持单元,这会导致遮光不足。相反,在本实施例中,沿X方向对准的多个电荷保持单元202之间的区域被遮光部分303覆盖,并且遮光部分303的多个开口304和305被布置在电荷保持单元202与Y方向平行地移动的位置中。从而,由于遮光部分303的开口304和305的各端部可被定位于较远离电荷保持单元202的各端部的位置中,因此电荷保持单元202的遮光性能可得到提高。因此,可以提供进一步减少由入射到电荷保持单元202的光导致的错误信号所引起的图像质量的劣化的成像器件100。

[0033] 注意,在本实施例中,包含于像素107中的一个中的多个触点302聚集在开口305中的相应的一个中。如图3B所示,希望像素107内的多个触点302在触点302之间具有可能的最小的间隙,并且在俯视图中被布置在开口305中的一个内。这是由于,如果多个触点302以分散的方式布置于像素107内,那么这会导致开口的数量或面积的增加。通过在俯视图中在形成多个触点302的区域中形成开口305中的每一个,开口的数量或面积可最小化以提高电荷保持单元202的遮光性能。由此,可以提供进一步减少由于错误信号导致的图像质量劣化的成像器件100。

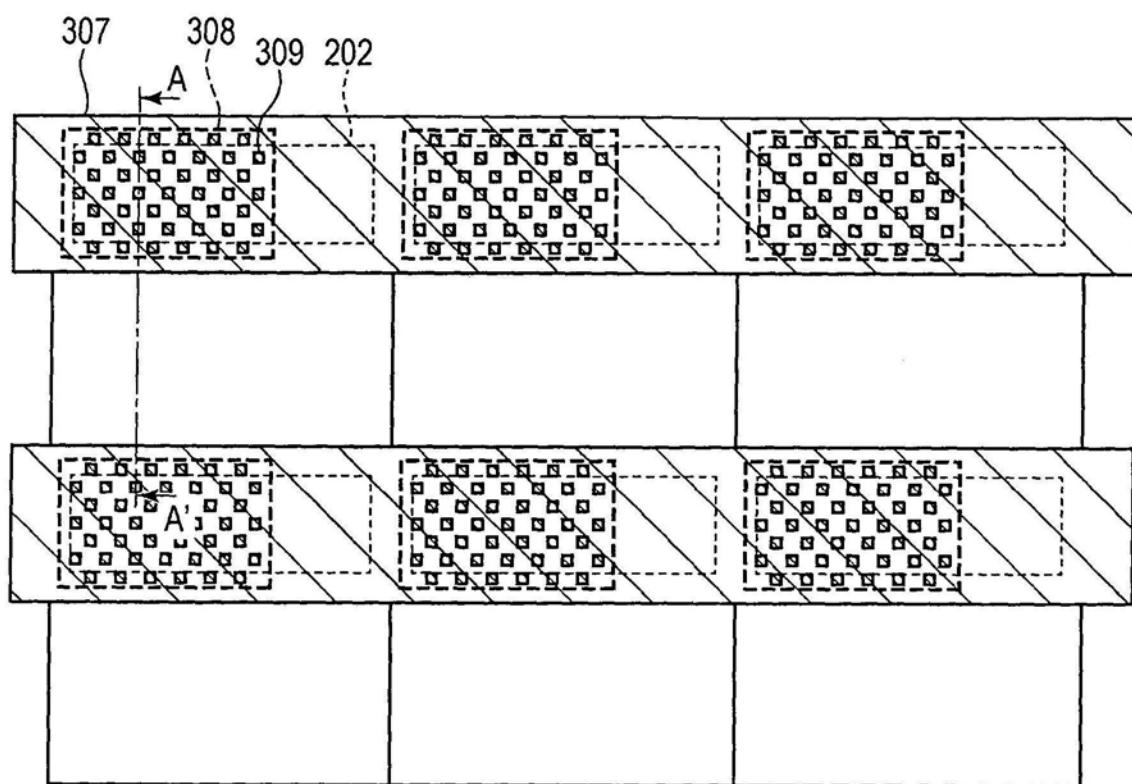

[0034] 图4是主要示意性地示出在半导体基板之上形成的第一布线层307、第二布线层308和通孔309的图案的平面图。第一布线层307经由层间绝缘层(未示出)被布置于电荷保持单元202之上。并且,第二布线层308经由层间绝缘层(未示出)被布置于第一布线层307之上。在第一布线层307与第二布线层308之间,以方格图案布置电连接这些层的多个通孔309。第一布线层307、第二布线层308和通孔309均具有导电性,并且可以由不太可能透光的

诸如金属的构件形成。

[0035] 图5是示意性地示出沿图3A和图4所示的线A-A'切取的截面的结构的示图。在图5所示的半导体基板中,示出形成光电转换单元201的半导体区域、形成电荷保持单元202的半导体区域、电气隔离光电转换单元201与电荷保持单元202的元件隔离区域213。并且,在半导体基板上或之上,图5示出形成第一传送晶体管204的栅电极、遮光部分303、第一布线层307、第二布线层308和通孔309。以这种方式,第一布线层307、第二布线层308和通孔309可被布置在电荷保持单元202之上以覆盖电荷保持单元202。在这种情况下,第一布线层307、第二布线层308和通孔309阻挡光,并且,向电荷保持单元202的光入射可进一步减少。因此,可以提供进一步减少由于错误信号导致的图像质量劣化的成像器件100。

[0036] 对于布置于电荷保持单元202周围的元件隔离区域213的特定结构,可以使用通过浅沟槽隔离(STI)或PN结隔离等的隔离。这里希望用于元件隔离区域213的材料为限制光入射到电荷保持单元202的材料。特别地,希望用于元件隔离区域213的材料是对可见光具有低的透过率的材料。由于诸如硅的半导体对可见光具有低的透过率,因此,例如,希望在元件隔离区域213中布置形成PN结隔离的杂质扩散区域,即,诸如硅的半导体。在这种情况下,入射到元件隔离区域213的光在到达电荷保持单元202之前衰减,因此,入射到电荷保持单元202的光的量减少。因此,由于入射到电荷保持单元202的光的量与使用利用对可见光透明的诸如氧化硅的材料的元件隔离结构诸如通过STI的隔离的情况相比减少,因此可以提供进一步减少由于错误信号导致的图像质量劣化的成像器件100。

[0037] 并且,像素阵列101的形状可以是具有短边和长边的矩形。例如,当包含于像素阵列101中的像素107的行数N和列数M相互不同时,像素阵列101的形状可以是矩形。并且,当像素107是矩形时,像素阵列101的形状可以是矩形。在这种情况下,希望图3A所示的多个电荷保持单元202对准的X方向与像素阵列101的长边方向平行。从被照体发出的入射光经由包含于诸如照相机的成像系统的光学系统中的透镜入射到成像器件100的像素阵列101。在这种情况下,由于像素阵列101的长边的端部处于最远离透镜的中心轴的位置,因此在长边端部处对于像素阵列101的入射光的入射角最大。当光斜入射遮光部分303的开口304和305并且电荷保持单元202被布置在入射光通过的部分附近时,可能出现由于错误信号导致的图像质量的劣化。入射角越大,则越可能出现这种情况。因此,在入射光最大的长边的端部周围,优选电荷保持单元202不被布置在来自遮光部分303的开口304和305的斜入射光的延伸线上。为了实现这种布置,电荷保持单元202对准的X方向和像素阵列101的长边方向优选平行。由于以上的原因,随着像素阵列101的长边方向平行于多个电荷保持单元202对准的X方向,可以减少入射到像素阵列101的端部附近的电荷保持单元202的光。因此,可以提供进一步减少由于错误信号导致的图像质量劣化的成像器件100。

#### [0038] 第二实施例

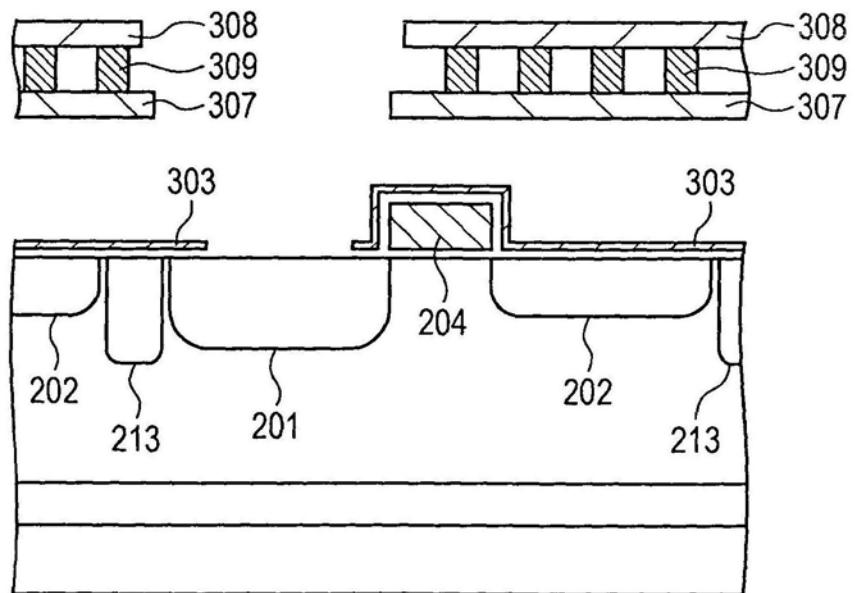

[0039] 图6A和图6B是根据第二实施例的成像器件100的像素107的平面图。图6A是在与半导体基板正交的方向的俯视图中示意性地示出半导体基板的表面附近的图案的平面图,图6B是主要示意性地示出在半导体基板之上形成的遮光部分303的图案的平面图。在本实施例的描述中,对于与第一实施例共同的特征省略详细的描述。并且,在图6A和图6B中,具有与图3A和图3B等中的功能相同的功能的特征由相同的附图标记表示,并且,其功能的描述可能被省略。

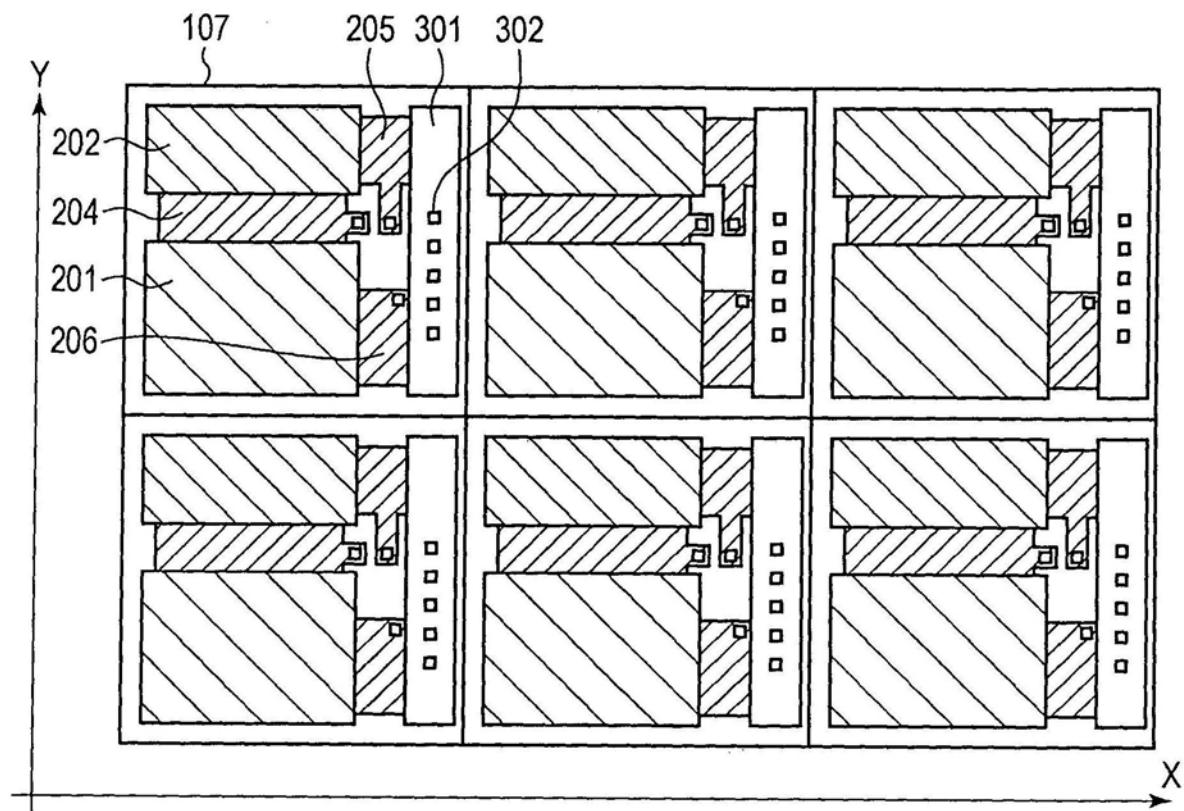

[0040] 如图6A所示,本实施例与第一实施例的不同在于,两个第一传送晶体管204、两个第二传送晶体管205和两个电荷保持单元202被设置在像素107内。光电转换单元201和读出电路单元301被布置为夹着溢流晶体管206的栅电极沿X方向对准。并且,光电转换单元201和两个电荷保持单元202被布置为夹着两个不同的第一传送晶体管204的栅电极沿与X方向相交的Y方向对准。并且,两个电荷保持单元202被布置为夹着光电转换单元201或读出电路单元301等沿Y方向对准。并且,两个电荷保持单元202被布置为沿X方向对准。由于其它的相邻像素107中的每一个具有相同的布置,因此,包含相邻像素107的多个电荷保持单元202被布置为沿X方向对准。并且,两个电荷保持单元202经由两个不同的第二传送晶体管205连接到不同的读出电路单元301。读出电路单元301被布置在两个像素107的边界附近并且被两个像素107共享。多个触点302被布置在其中布置读出电路单元301的区域中或附近。更具体而言,在除沿X方向对准的多个电荷保持单元202之间的区域以外的区域中形成多个触点302。

[0041] 在图6B中,遮光部分303被布置为覆盖除设置在光电转换单元201之上的开口304和设置在读出电路单元301之上的开口305以外的像素107的整个表面。因此,在本实施例中,同样,虽然遮光部分303的多个开口304和305被布置在电荷保持单元202与Y方向平行地移动的位置中,但是,遮光部分303的多个开口304和305均不被布置在电荷保持单元202与X方向平行地移动的位置中。换句话说,沿X方向对准的电荷保持单元202之间的区域在俯视图中被遮光部分303覆盖。

[0042] 如上所述,在本实施例中,对第一实施例进行变更,以增加包含于像素107中的诸如电荷保持单元202的元件的数量。并且,在这种构造中,遮光部分303的开口304和305的端部可被定位于较远离电荷保持单元202的各端部的位置中,这可进一步提高电荷保持单元202的遮光性能。因此,与第一实施例类似,在本实施例中,也可提供进一步减少由入射到电荷保持单元202的光导致的错误信号所引起的图像质量劣化的成像器件100。

### [0043] 第三实施例

[0044] 图7A和图7B是根据第三实施例的成像器件100的像素107的平面图。图7A是在与半导体基板正交的方向的俯视图中示意性地示出半导体基板的表面附近的图案的平面图,图7B是主要示意性地示出在半导体基板之上形成的遮光部分303的图案的平面图。在本实施例的描述中,对于与第一实施例或第二实施例共同的特征省略详细的描述。并且,在图7A和图7B中,具有与图3A和图3B等中的功能相同的功能的特征由相同的附图标记表示,并且,其功能的描述可能被省略。

[0045] 如图7A所示,在本实施例中,与第二实施例类似,两个第一传送晶体管204、两个第二传送晶体管205和两个电荷保持单元202被设置在像素107内。但是,本实施例与第二实施例的不同在于,两个电荷保持单元202被布置为夹着光电转换单元201和读出电路单元301沿Y方向对准。并且,本实施例与第二实施例的不同在于,两个电荷保持单元202经由两个不同的第二传送晶体管205连接到同一读出电路单元301。

[0046] 光电转换单元201和读出电路单元301被布置为夹着溢流晶体管206的栅电极沿X方向对准。并且,光电转换单元201和两个电荷保持单元202被布置为夹着不同的两个第一传送晶体管204的栅电极沿与X方向相交的Y方向对准。在图7A中,两个第一传送晶体管204的栅电极形成为相互连续。但是,两个第一传送晶体管204的栅电极可形成为相互电气隔

离。并且,两个电荷保持单元202被布置为夹着光电转换单元201和读出电路单元301沿Y方向对准。并且,两个电荷保持单元202经由两个不同的第二传送晶体管205连接到同一读出电路单元301。多个触点302被布置在其中布置读出电路单元301的区域中或附近。更具体而言,多个触点302形成在除沿X方向对准的电荷保持单元202之间的区域以外的区域中。

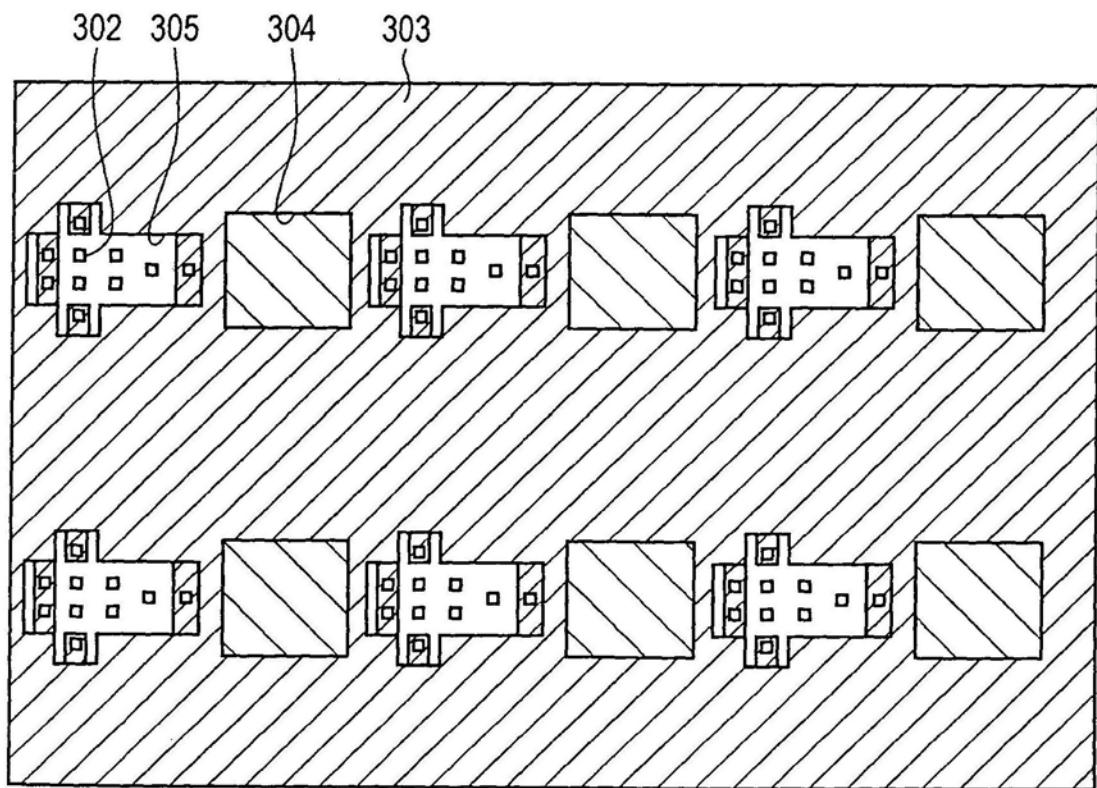

[0047] 在图7B中,遮光部分303被布置为覆盖除设置在光电转换单元201之上的开口304和设置在读出电路单元301之上的开口305以外的像素107的整个表面。因此,在本实施例中,同样,虽然遮光部分303的多个开口304和305被布置在电荷保持单元202与Y方向平行地移动的位置中,但是,遮光部分303的多个开口304和305均不被布置在电荷保持单元202与X方向平行地移动的位置中。换句话说,在俯视图中,遮光部分303被布置在沿X方向对准的多个电荷保持单元202之中的相应两个之间。

[0048] 如上所述,在本实施例中,对第一实施例进行变更,以通过使用与第二实施例不同的方案增加包含于像素107中的诸如电荷保持单元202等的元件的数量。并且,在这种构造中,遮光部分303的开口304和305的端部可被定位于较远离电荷保持单元202的各端部的位置中,这可进一步提高电荷保持单元202的遮光性能。因此,与第一实施例和第二实施例类似,在本实施例中,也可提供进一步减少由入射到电荷保持单元202的光导致的错误信号所引起的图像质量劣化的成像器件100。

#### [0049] 第四实施例

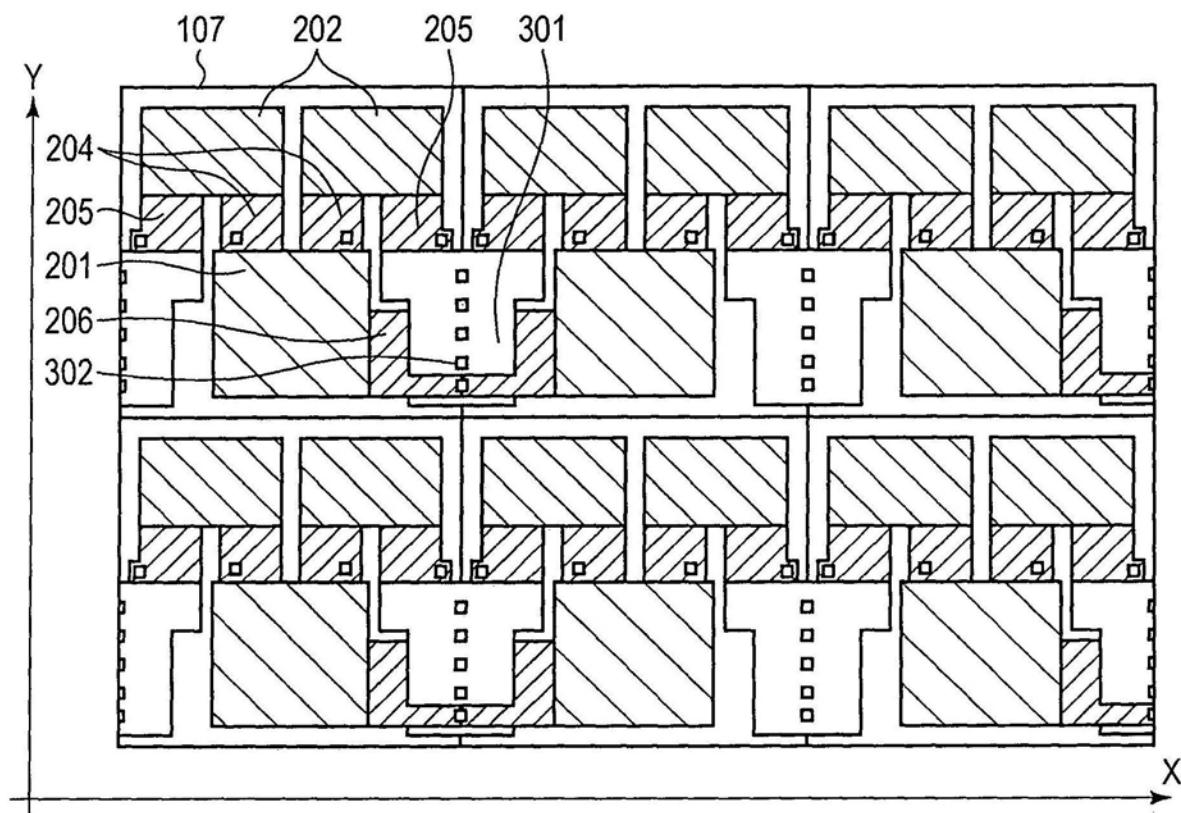

[0050] 图8A和图8B是根据第四实施例的成像器件100的像素107的平面图。图8A是在与半导体基板正交的方向的俯视图中示意性地示出半导体基板的表面附近的图案的平面图,图8B是主要示意性地示出在半导体基板之上形成的遮光部分303的图案的平面图。在本实施例的描述中,对于与第一到第三实施例共同的特征省略详细的描述。并且,在图8A和图8B中,具有与图3A和图3B等中的功能相同的功能的特征由相同的附图标记表示,并且,其功能的描述可能被省略。

[0051] 如图8A所示,本实施例与第一实施例的不同在于电荷保持单元202、第二传送晶体管205和读出电路单元301等的布置。光电转换单元201和读出电路单元301被布置为夹着溢流晶体管206的栅电极沿X方向对准。并且,光电转换单元201和电荷保持单元202被布置为夹着第一传送晶体管204的栅电极沿Y方向对准。并且,电荷保持单元202和读出电路单元301被布置为夹着第二传送晶体管205的栅电极沿X方向对准。多个触点302被布置在其中布置读出电路单元301的区域中或附近。更具体而言,多个触点302形成在除沿X方向对准的多个电荷保持单元202之间的区域以外的区域中。

[0052] 在图8B中,遮光部分303被布置为覆盖除设置在光电转换单元201之上的开口304和设置在读出电路单元301之上的开口305以外的像素107的整个表面。因此,在本实施例中,同样,虽然遮光部分303的多个开口304和305被布置在电荷保持单元202与Y方向平行地移动的位置中,但是,遮光部分303的多个开口304和305均不被布置在电荷保持单元202与X方向平行地移动的位置中。换句话说,在俯视图中,遮光部分303被布置在沿X方向对准的多个电荷保持单元202之中的相应两个之间。

[0053] 如上所述,在本实施例中,对第一实施例进行变更,以改变电荷保持单元202、第二传送晶体管205和读出电路单元301等的布置。具体而言,第二传送晶体管205的栅电极和读出电路单元301被布置在沿X方向对准的相邻像素的电荷保持单元202之间的区域中。但是,

由于开口304和305不被设置在电荷保持单元202之间,因此出于与第一实施例相同的原因,可以提高电荷保持单元202的遮光性能。因此,与第一实施例类似,在本实施例中,也可提供进一步减少由入射到电荷保持单元202的光导致的错误信号所引起的图像质量劣化的成像器件100。

#### [0054] 第五实施例

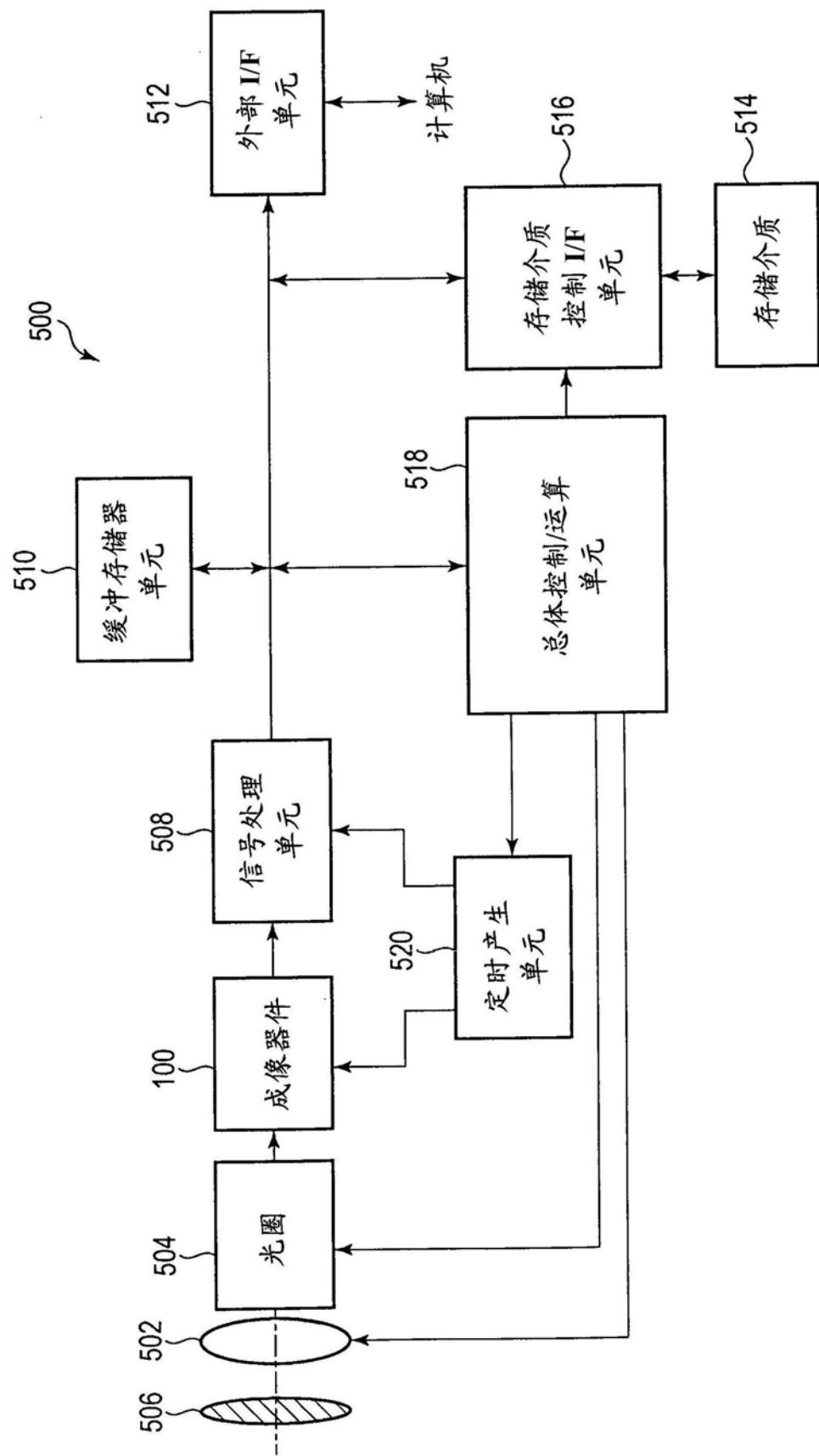

[0055] 图9是示出根据本实施例的成像系统500的构造的框图。在以上的第一到第四实施例中描述的成像器件100可被应用于成像系统500。例如,可应用成像器件100的成像系统500可包括数字静态照相机、数字摄像机或监视照相机等。图9示出应用在以上的实施例中描述的成像器件100的数字静态照相机的示例性构造。

[0056] 作为例子在图9中示出的成像系统500具有成像器件100、将被照体的光学图像捕获到成像器件100上的透镜502、用于改变通过透镜502的光量的光圈504和用于保护透镜502的挡板506。透镜502和光圈504形成将光会聚到成像器件100上的光学系统。成像器件100是在第一到第四实施例中描述的成像器件100中的任一个。

[0057] 成像系统500还具有处理从成像器件100输出的输出信号的信号处理单元508。信号处理单元508执行在必要的情况下对输入的信号执行各种校正或压缩并且输出信号的信号处理的操作。信号处理单元508可具有用于对从成像器件100输出的输出信号执行AD转换处理的功能。在这种情况下,成像器件100不必需要在其中具有AD转换电路。

[0058] 成像系统500还具有用于在其中暂时存储图像数据的缓冲存储器单元510和用于与外部计算机等通信的外部接口单元(外部I/F单元)512。成像系统500还具有用于执行图像拾取数据的存储或读出的诸如半导体存储器的存储介质514以及用于对存储介质514执行存储或读出的存储介质控制接口单元(存储介质控制I/F单元)516。注意,存储介质514可被嵌入成像系统500中或者可被去除。

[0059] 成像系统500还具有执行各种计算并且控制整个数字静态照相机的总体控制/运算单元518和向成像器件100和数字处理单元508输出各种定时信号的定时产生单元520。这里,定时信号等可从外面被输入,并且,成像系统500可至少具有成像器件100和处理从成像器件100输出的输出信号的数字处理单元508。总体控制/运算单元518和定时产生单元520可被配置为实现成像器件100的控制电路106等的功能的一部分或全部。

[0060] 成像器件100将图像形成信号输出到信号处理单元508。信号处理单元508对从成像器件100输出的图像形成信号执行预定的信号处理并且输出图像数据。并且,信号处理单元508使用图像形成信号以生成图像。

[0061] 第一到第四实施例中的任一个的成像器件100被用于形成成像系统,并由此可实现能够获取更高质量图像的成像系统。

#### [0062] 第六实施例

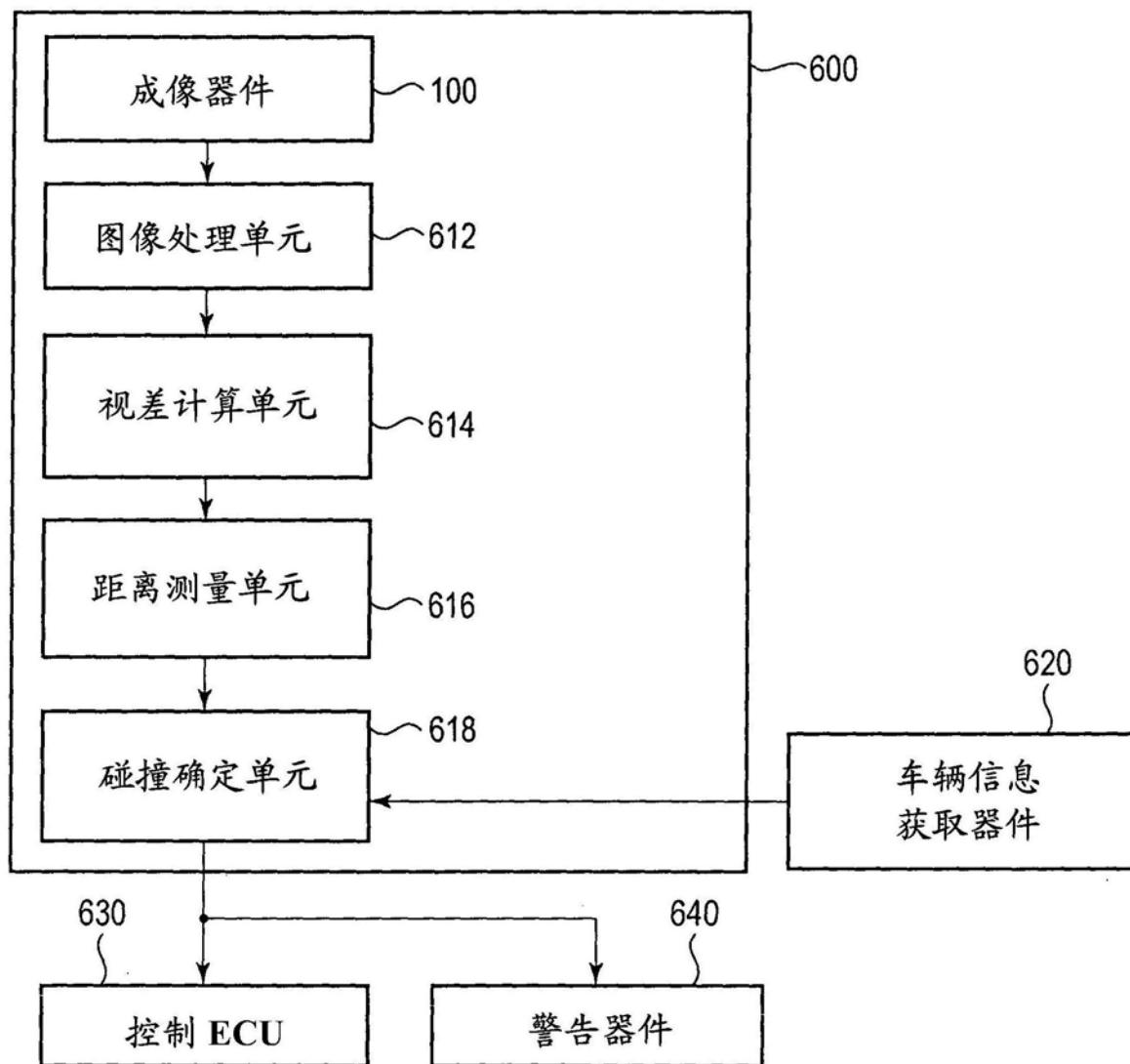

[0063] 图10A和图10B是根据本实施例的成像系统600和移动装置的构造的示图。图10A示出与车载照相机有关的成像系统600的例子。成像系统600具有成像器件100。成像器件100是在以上的第一到第四实施例中描述的成像器件100中的任一个。成像系统600具有对通过成像器件100获取的多个图像数据执行图像处理的图像处理单元612和从由成像系统600获取的多个图像数据计算视差(视差图像的相位差)的视差计算单元614。并且,成像系统600具有基于计算的视差计算到物体的距离的距离测量单元616和基于计算的距离确定是否存

在碰撞可能性的碰撞确定单元618。这里,视差计算单元614和距离测量单元616是获取到物体的距离信息的距离信息获取单元的例子。即,距离信息是关于视差、散焦量或到物体的距离等的信息。碰撞确定单元618可使用距离信息中的任一种以确定碰撞可能性。距离信息获取单元可由专门设计的硬件实现,或者可由软件模块实现。并且,距离信息获取单元可由场可编程门阵列(FPGA)或应用特定集成电路(ASIC)等实现,或者可由其组合实现。

[0064] 成像系统600连接到车辆信息获取器件620,并且可获取诸如车辆速度、偏航率或转向角等的车辆信息。并且,成像系统600与控制ECU 630连接,该控制ECU 630是输出用于基于碰撞确定单元618的确定结果使车辆产生制动力的控制信号的控制器件。即,控制ECU 630是基于距离信息控制移动装置的移动装置控制单元的例子。并且,成像系统600与基于碰撞确定单元618的确定结果向驾驶员发出警告的警告器件640连接。例如,当作为碰撞确定单元618的确定结果碰撞可能性高时,控制ECU 630执行车辆控制以通过施加制动、加速器减速或抑制发动机功率等避免碰撞或来减少损坏。警告器件640通过发出诸如声音的警告、在汽车导航系统等的显示器上显示警告信息或向座椅安全带或方向盘等提供振动等,警告用户。

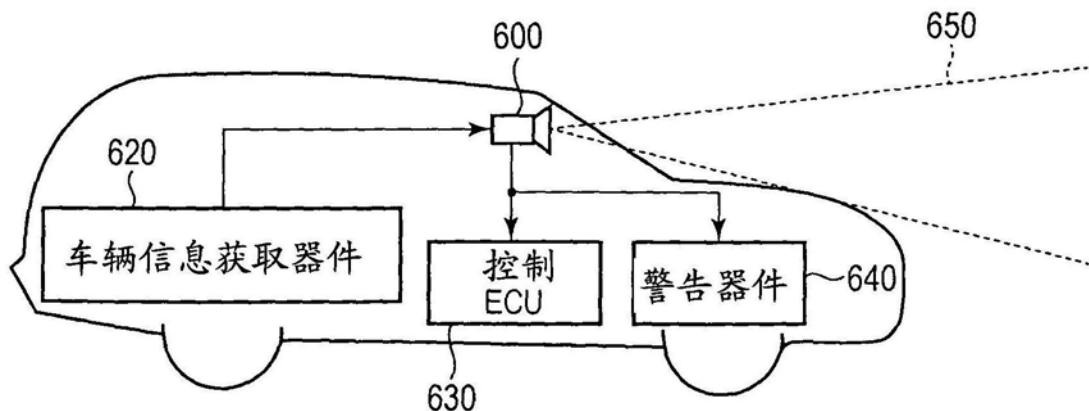

[0065] 在本实施例中,成像系统600捕获例如车辆的诸如前方区域或后方区域的周围区域的图像。图10B示出捕获车辆的前方区域(捕获区域650)的情况下成像系统600。车辆信息获取器件620传送指令以使成像系统600动作并执行捕获。根据第一到第四实施例中的任一个的成像器件100的使用允许本实施例的成像系统600进一步提高测距精度。

[0066] 尽管在上面的描述中示出了用于避免与另一车辆的碰撞的控制的例子,但是实施例适用于用来跟随另一车辆的自动驾驶控制或不从车道出去的自动驾驶控制等。并且,成像系统不限于诸如本车辆的车辆,并且可以被应用于例如诸如船舶、飞机或工业机器人的移动装置(运动装置)。另外,成像系统可以广泛地应用于诸如智能交通系统(ITS)的利用物体识别的器件,而不限于移动装置。

#### [0067] 其他实施例

[0068] 注意,上述实施例中的任一个已经被提供以仅示出实现本发明的实施例的例子,并且本发明的技术范围不应通过这些实施例以限制性的意义被解释。即,能够以各种形式实现本发明而不背离本发明的技术概念或其主要特征。例如,应该理解,实施例中的任一个的构造的一部分被添加到另一实施例或者由另一实施例的构造的一部分替代的实施例应被视为可应用本发明的实施例。

[0069] 也可通过读出并执行记录于存储介质(也可被更完整地称为“非暂时性计算机可读存储介质”)上的计算机可执行指令(例如,一个或更多个程序)以执行上述实施例中的一个或更多个的功能并且/或者包含用于执行上述实施例中的一个或更多个的功能的一个或更多个电路(例如,应用特定集成电路(ASIC))的系统或装置的计算机,以及,通过由系统或装置的计算机通过例如读出并执行来自存储介质的计算机可执行指令以执行上述实施例中的一个或更多个的功能并且/或者控制一个或更多个电路以执行上述实施例中的一个或更多个的功能执行的方法,实现本发明的实施例。计算机可包括一个或更多个处理器(例如,中央处理单元(CPU)、微处理单元(MPU)),并且可包含单独的计算机或单独的处理器的网络,以读出并执行计算机可执行指令。计算机可执行指令可例如从网络或存储介质被提供给计算机。存储介质可包含例如硬盘、随机存取存储器(RAM)、只读存储器(ROM)、分布式

计算系统的存储器、光盘(诸如紧致盘(CD)、数字万用盘(DVD)或蓝光盘(BD)<sup>TM</sup>)、快擦写存储器设备和记忆卡等中的一个或更多个。

[0070] 本发明的实施例还可以通过如下的方法来实现,即,通过网络或者各种存储介质将执行上述实施例的功能的软件(程序)提供给系统或装置,该系统或装置的计算机或是中央处理单元(CPU)、微处理单元(MPU)读出并执行程序的方法。

[0071] 虽然已参照示例性实施例说明了本发明,但应理解,本发明不限于公开的示例性实施例。所附权利要求的范围应被赋予最宽的解释以包含所有这样的变更方式以及等同的结构和功能。

图1

图2

图3A

图3B

图4

图5

图6A

图6B

图7A

图7B

图8A

图8B

图9

图10A

图10B