(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7580552号**

**(P7580552)**

(45)発行日 令和6年11月11日(2024.11.11)

(24)登録日 令和6年10月31日(2024.10.31)

(51)国際特許分類

|         |                 |     |         |      |         |

|---------|-----------------|-----|---------|------|---------|

| G 0 9 G | 3/20 (2006.01)  | F I | G 0 9 G | 3/20 | 6 2 2 E |

| G 0 9 G | 3/36 (2006.01)  |     | G 0 9 G | 3/36 |         |

| G 0 9 F | 9/30 (2006.01)  |     | G 0 9 G | 3/20 | 6 2 1 F |

| G 1 1 C | 19/28 (2006.01) |     | G 0 9 G | 3/20 | 6 1 1 J |

|         |                 |     | G 0 9 G | 3/20 | 6 7 0 J |

請求項の数 2 (全39頁) 最終頁に続く

|                   |                                    |

|-------------------|------------------------------------|

| (21)出願番号          | 特願2023-175809(P2023-175809)        |

| (22)出願日           | 令和5年10月11日(2023.10.11)             |

| (62)分割の表示         | 特願2022-111220(P2022-111220)<br>の分割 |

| 原出願日              | 平成25年9月6日(2013.9.6)                |

| (65)公開番号          | 特開2023-182758(P2023-182758)<br>A)  |

| (43)公開日           | 令和5年12月26日(2023.12.26)             |

| 審査請求日             | 令和5年10月23日(2023.10.23)             |

| (31)優先権主張番号       | 特願2012-197224(P2012-197224)        |

| (32)優先日           | 平成24年9月7日(2012.9.7)                |

| (33)優先権主張国・地域又は機関 | 日本国(JP)                            |

|          |                                                |

|----------|------------------------------------------------|

| (73)特許権者 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (72)発明者  | 梅崎 敦司<br>神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内       |

| 審査官      | 中村 直行                                          |

最終頁に続く

(54)【発明の名称】 半導体装置

**(57)【特許請求の範囲】****【請求項 1】**

走査線駆動回路と、画素と、を有し、

前記走査線駆動回路は、第1乃至第11のトランジスタを有し、

前記画素は、第12のトランジスタを有し、

前記第1のトランジスタのソース及びドレインの一方は、走査線と常に導通し、

前記第1のトランジスタのソース及びドレインの他方は、電源線と常に導通し、

前記第2のトランジスタのソース及びドレインの一方は、前記走査線と常に導通し、

前記第2のトランジスタのソース及びドレインの他方は、前記電源線と常に導通し、

前記第1のトランジスタのゲートは、前記第3のトランジスタのソース及びドレインの一方と常に導通し、

前記第2のトランジスタのゲートは、前記第4のトランジスタのソース及びドレインの一方と常に導通し、

前記第3のトランジスタのソース及びドレインの他方は、前記第4のトランジスタのソース及びドレインの他方と常に導通し、

前記第3のトランジスタのゲートは、第1の信号線と常に導通し、

前記第4のトランジスタのゲートは、第2の信号線と常に導通し、

前記第5のトランジスタのソース及びドレインの一方は、前記第1のトランジスタのゲートと常に導通し、

前記第5のトランジスタのソース及びドレインの他方は、第3の信号線と常に導通し、

10

20

前記第5のトランジスタのゲートは、前記第2の信号線と常に導通し、

前記第6のトランジスタのソース及びドレインの一方は、前記第2のトランジスタのゲートと常に導通し、

前記第6のトランジスタのソース及びドレインの他方は、前記第3の信号線と常に導通し、

前記第6のトランジスタのゲートは、前記第1の信号線と常に導通し、

前記第7のトランジスタのソース及びドレインの一方は、前記走査線と常に導通し、

前記第7のトランジスタのソース及びドレインの他方は、クロック信号線と常に導通し、

前記第8のトランジスタのソース及びドレインの一方は、前記第7のトランジスタのゲートと常に導通し、

前記第8のトランジスタのソース及びドレインの他方は、第4の信号線と常に導通し、

前記第8のトランジスタのゲートは、前記第4の信号線と常に導通し、

前記第9のトランジスタのソース及びドレインの一方は、前記第7のトランジスタのゲートと常に導通し、

前記第9のトランジスタのソース及びドレインの他方は、前記電源線と常に導通し、

前記第9のトランジスタのゲートは、前記第3の信号線と常に導通し、

前記第10のトランジスタのソース及びドレインの一方は、前記第3のトランジスタのソース及びドレインの他方と常に導通し、

前記第10のトランジスタのゲートは、前記第10のトランジスタのソース及びドレインの他方と常に導通し、

前記第11のトランジスタのソース及びドレイン一方は、前記第3のトランジスタのソース及びドレインの他方と常に導通し、

前記第11のトランジスタのソース及びドレインの他方は、前記電源線と常に導通し、

前記第11のトランジスタのゲートは、前記第7のトランジスタのゲートと常に導通し、

前記第12のトランジスタのソース及びドレインの一方は、画素電極と常に導通し、

前記第12のトランジスタのソース及びドレインの他方は、第5の信号線と常に導通し、

前記第12のトランジスタのゲートは、前記走査線と常に導通し、

前記第10のトランジスタのソース又はドレインの他方が少なくとも前記第10のトランジスタのチャネル形成領域及び前記第3のトランジスタのチャネル形成領域を介して前記第1のトランジスタのゲートと導通状態であるとき、前記第1のトランジスタがオンする電位が少なくとも前記第10のトランジスタのチャネル形成領域及び前記第3のトランジスタのチャネル形成領域を介して前記第1のトランジスタのゲートに入力され、

前記第10のトランジスタのソース又はドレインの他方が少なくとも前記第10のトランジスタのチャネル形成領域及び前記第4のトランジスタのチャネル形成領域を介して前記第2のトランジスタのゲートと導通状態であるとき、前記第2のトランジスタがオンする電位が少なくとも前記第10のトランジスタのチャネル形成領域及び前記第4のトランジスタのチャネル形成領域を介して前記第2のトランジスタのゲートに入力される半導体装置。

## 【請求項2】

走査線駆動回路と、画素と、を有し、

前記走査線駆動回路は、第1乃至第11のトランジスタを有し、

前記画素は、第12のトランジスタを有し、

前記第1のトランジスタのソース及びドレインの一方は、走査線と常に導通し、

前記第1のトランジスタのソース及びドレインの他方は、電源線と常に導通し、

前記第2のトランジスタのソース及びドレインの一方は、前記走査線と常に導通し、

前記第2のトランジスタのソース及びドレインの他方は、前記電源線と常に導通し、

前記第1のトランジスタのゲートは、前記第3のトランジスタのソース及びドレインの一方と常に導通し、

前記第2のトランジスタのゲートは、前記第4のトランジスタのソース及びドレインの一方と常に導通し、

前記第3のトランジスタのソース及びドレインの他方は、前記第4のトランジスタのソ

10

20

30

40

50

ース及びドレインの他方と常に導通し、

前記第3のトランジスタのゲートは、第1の信号線と常に導通し、

前記第4のトランジスタのゲートは、第2の信号線と常に導通し、

前記第5のトランジスタのソース及びドレインの一方は、前記第1のトランジスタのゲートと常に導通し、

前記第5のトランジスタのソース及びドレインの他方は、第3の信号線と常に導通し、

前記第5のトランジスタのゲートは、前記第2の信号線と常に導通し、

前記第6のトランジスタのソース及びドレインの一方は、前記第2のトランジスタのゲートと常に導通し、

前記第6のトランジスタのソース及びドレインの他方は、前記第3の信号線と常に導通し、 10

前記第6のトランジスタのゲートは、前記第1の信号線と常に導通し、

前記第7のトランジスタのソース及びドレインの一方は、前記走査線と常に導通し、

前記第7のトランジスタのソース及びドレインの他方は、クロック信号線と常に導通し、

前記第8のトランジスタのソース及びドレインの一方は、前記第7のトランジスタのゲートと常に導通し、

前記第8のトランジスタのソース及びドレインの他方は、第4の信号線と常に導通し、

前記第8のトランジスタのゲートは、前記第4の信号線と常に導通し、

前記第9のトランジスタのソース及びドレインの一方は、前記第7のトランジスタのゲートと常に導通し、

前記第9のトランジスタのソース及びドレインの他方は、前記電源線と常に導通し、

前記第9のトランジスタのゲートは、前記第3の信号線と常に導通し、 20

前記第10のトランジスタのソース及びドレインの一方は、前記第3のトランジスタのソース及びドレインの他方と常に導通し、

前記第10のトランジスタのゲートは、前記第10のトランジスタのソース及びドレインの他方と常に導通し、

前記第11のトランジスタのソース及びドレイン一方は、前記第3のトランジスタのソース及びドレインの他方と常に導通し、

前記第11のトランジスタのソース及びドレインの他方は、前記電源線と常に導通し、

前記第12のトランジスタのソース及びドレインの一方は、前記第7のトランジスタのゲートと常に導通し、

前記第12のトランジスタのソース及びドレインの他方は、第5の信号線と常に導通し、 30

前記第12のトランジスタのゲートは、前記走査線と常に導通し、

前記第10のトランジスタのソース又はドレインの他方が少なくとも前記第10のトランジスタのチャネル形成領域及び前記第3のトランジスタのチャネル形成領域を介して前記第1のトランジスタのゲートと導通状態であるとき、前記第1のトランジスタがオンする電位が少なくとも前記第10のトランジスタのチャネル形成領域及び前記第3のトランジスタのチャネル形成領域を介して前記第1のトランジスタのゲートに入力され、

前記第10のトランジスタのソース又はドレインの他方が少なくとも前記第10のトランジスタのチャネル形成領域及び前記第4のトランジスタのチャネル形成領域を介して前記第2のトランジスタのゲートと導通状態であるとき、前記第2のトランジスタがオンする電位が少なくとも前記第10のトランジスタのチャネル形成領域及び前記第4のトランジスタのチャネル形成領域を介して前記第2のトランジスタのゲートに入力され、

前記第3のトランジスタがオン状態であり、前記第6のトランジスタがオン状態であり、前記第4のトランジスタがオフ状態であり、前記第5のトランジスタがオフ状態である第1の期間と、

前記第3のトランジスタがオフ状態であり、前記第6のトランジスタがオフ状態であり、前記第4のトランジスタがオン状態であり、前記第5のトランジスタがオン状態である第2の期間と、を有し、

前記クロック信号線の信号の周期は、前記第1の期間と前記第2の期間とを切り替える信号の周期よりも短い半導体装置。 50

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明の一態様は、半導体装置、及び該半導体装置を有する表示装置に関する。特に、順序回路、及び該順序回路を有するシフトレジスタ等の半導体装置に関する。

**【背景技術】****【0002】**

近年、同じ極性のトランジスタで構成される順序回路の開発が活発に進められている。特に、特許文献1には、トランジスタの特性変化を抑制することができる順序回路が開示されている。

10

**【0003】**

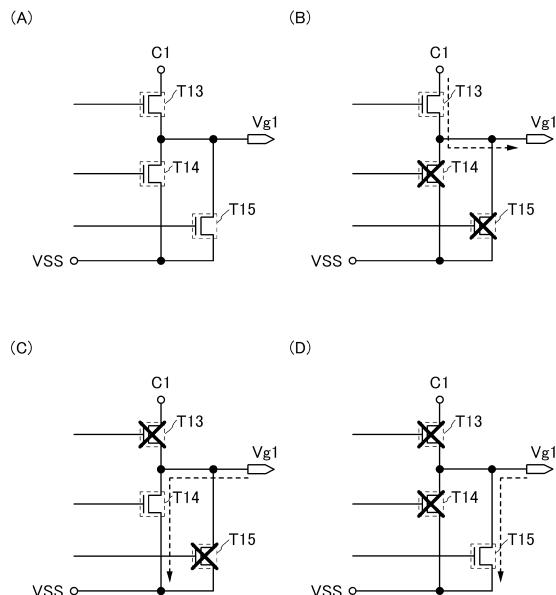

図17(A)は、従来の順序回路の構成を示す。従来の順序回路は、トランジスタT13と、並列に接続されたトランジスタT14及びトランジスタT15と、を有する。従来の順序回路では、トランジスタT13がオンになり、トランジスタT14及びトランジスタT15がオフになることで、第1クロック信号C1を出力している。第1クロック信号C1がハイレベルであれば、第1スキャン信号Vg1がハイレベルになる(図17(B)参照)。そして、奇数フレームでは、トランジスタT13がオフになり、トランジスタT14がオンになり、トランジスタT15がオフになることで、第1供給電圧VSSを出力している(図17(C)参照)。また、偶数フレームでは、トランジスタT13がオフになり、トランジスタT14がオフになり、トランジスタT15がオンになることで、第1供給電圧VSSを出力している(図17(D)参照)。このように、奇数フレームではトランジスタT15をオフにし、偶数フレームではトランジスタT14をオフにすることで、トランジスタT14及びトランジスタT15の特性変化が抑制される。

20

**【先行技術文献】****【特許文献】****【0004】****【文献】特開2007-004167号公報****【発明の概要】****【発明が解決しようとする課題】****【0005】**

しかしながら、従来の順序回路では、並列に接続された二つのトランジスタの一方をオフにし、他方のトランジスタのみを駆動させるため、並列に接続された二つのトランジスタのそれぞれに十分な駆動能力が求められる。よって、トランジスタのW(Wはチャネル幅)/L(Lはチャネル長)が大きくなるといった問題があった。また、トランジスタのW/Lが十分に大きくなれば、出力信号の変化がゆるやかになり、出力信号に遅延やなまりが生じるといった問題があった。

30

**【0006】**

そこで、本発明の一態様は、トランジスタの特性変化を抑制するとともに、トランジスタのW/Lを大きくすることなく、出力信号を急峻に変化させることができる半導体装置を提供することを課題の一とする。また、本発明の一態様は、新規の回路構成を含む半導体装置を提供することを課題の一とする。なお、これらの課題の記載は、他の課題の存在を妨げるものではない。なお、本発明の一態様は、これらの課題の全てを解決する必要はないものとする。なお、これら以外の課題は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の課題を抽出することが可能である。

40

**【課題を解決するための手段】****【0007】**

本発明の一態様は、ソース又はドレインの一方に第1の信号が入力された第1のトランジスタと、ソース又はドレインの一方に第1の電位が入力され、ソース又はドレインの他方が第1のトランジスタのソース又はドレインの他方と電気的に接続された第2のトランジ

50

10

スタと、ソース又はドレインの一方が第2のトランジスタのソース又はドレインの一方と電気的に接続され、ソース又はドレインの他方が第1のトランジスタのソース又はドレインの他方と電気的に接続された第3のトランジスタと、第1のトランジスタ、第2のトランジスタ及び第3のトランジスタのオン又はオフを制御する手段と、を有する半導体装置の駆動方法である。そして、当該半導体装置は、第1の信号を第1のトランジスタを介して出力する第1のステップと、第1の電位を第2のトランジスタ及び第3のトランジスタを介して出力する第2のステップと、第1の電位を第2のトランジスタを介して出力する第3のステップと、を有する第1の期間と、第1の信号を第1のトランジスタを介して出力する第4のステップと、第1の電位を第2のトランジスタ及び第3のトランジスタを介して出力する第5のステップと、第1の電位を第3のトランジスタを介して出力する第6のステップと、を有する第2の期間と、を順に繰り返す。

#### 【0008】

上記本発明の一態様は、第1の期間において、第1のステップ、第2のステップ及び第3のステップのそれぞれを2回以上行い、第2の期間において、第4のステップ、第5のステップ及び第6のステップのそれぞれを2回以上行ってもよい。また、上記本発明の一態様は、第2のトランジスタのチャネル幅は、第3のトランジスタのチャネル幅の90%以上、110%以下であってもよい。また、上記本発明の一態様において、第1のトランジスタのチャネル幅は、第2のトランジスタのチャネル幅よりも大きく、且つ第3のトランジスタのチャネル幅よりも大きくてもよい。

#### 【0009】

20

本発明の一態様は、ソース又はドレインの一方が第1の配線と電気的に接続され、ソース又はドレインの他方が第2の配線と電気的に接続された第1のトランジスタと、ソース又はドレインの一方が第1の配線と電気的に接続され、ソース又はドレインの他方が第2の配線と電気的に接続された第2のトランジスタと、第1の端子が第1のトランジスタのゲートと電気的に接続された第1のスイッチと、第1の端子が第2のトランジスタのゲートと電気的に接続され、第2の端子が第1のスイッチの第2の端子と電気的に接続された第2のスイッチと、第1の端子が第3の配線と電気的に接続され、第2の端子が第1のトランジスタのゲートと電気的に接続された第3のスイッチと、第1の端子が第3の配線と電気的に接続され、第2の端子が第2のトランジスタのゲートと電気的に接続された第4のスイッチと、を有することを特徴とする半導体装置である。

#### 【0010】

30

上記本発明の一態様は、ソース又はドレインの一方が第4の配線と接続され、ソース又はドレインの他方が第1のスイッチの第2の端子と接続され、ゲートが第4の配線と接続された第3のトランジスタと、ソース又はドレインの一方が第2の配線と接続され、ソース又はドレインの他方が第1のスイッチの第2の端子と接続された第4のトランジスタと、を有していてもよい。また、上記本発明の一態様は、第1のスイッチ及び第4のスイッチがオンであり、第2のスイッチ及び第3のスイッチがオフである第1の期間と、第1のスイッチ及び第4のスイッチがオフであり、第2のスイッチ及び第3のスイッチがオンである第2の期間と、を有していてもよい。

#### 【発明の効果】

#### 【0011】

40

本発明の一態様は、トランジスタの特性変化を抑制することができるとともに、トランジスタのW/Lを大きくすることなく、出力信号の変化を急峻にすることができる半導体装置を提供することができる。また、本発明の一態様は、新規の回路構成を含む半導体装置を提供することができる。

#### 【図面の簡単な説明】

#### 【0012】

【図1】順序回路の構成を示す図。

【図2】順序回路のタイミングチャート。

【図3】順序回路のタイミングチャート。

【図 4】順序回路の動作を示す図。

【図 5】順序回路の動作を示す図。

【図 6】順序回路の動作を示す図。

【図 7】順序回路の動作を示す図。

【図 8】順序回路の構成を示す図。

【図 9】順序回路の構成を示す図。

【図 10】順序回路の構成を示す図。

【図 11】シフトレジスタの構成を示す図。

【図 12】パネルの構成を示す図。

【図 13】トランジスタの断面構造を示す図。

【図 14】液晶表示装置の上面図と断面図。

【図 15】電子機器を示す図。

【図 16】順序回路の構成を示す図。

【図 17】従来の順序回路の構成及び動作を示す図。

10

## 【発明を実施するための形態】

## 【0013】

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは、当業者であれば容易に理解される。したがって、本発明は、以下に示す実施の形態の記載内容に限定して解釈されるものではない。

20

## 【0014】

なお、本発明は、集積回路、RFタグ、表示装置など、トランジスタを用いたあらゆる半導体装置を、その範疇に含む。なお、集積回路には、マイクロプロセッサ、画像処理回路、DSP(Digital Signal Processor)、マイクロコントローラを含むLSI(Large Scale Integrated Circuit)、FPGA(Field Programmable Gate Array)やCPLD(Complex PLD)などのプログラマブル論理回路(PLD:Programmable Logic Device)が、その範疇に含まれる。また、表示装置には、液晶表示装置、有機発光素子(OLED)に代表される発光素子を各画素に備えた発光装置、電子ペーパー、DMD(Digital Micromirror Device)、PDP(Plasma Display Panel)、FED(Field Emission Display)などが、その範疇に含まれる。

30

## 【0015】

なお、本明細書において表示装置とは、液晶素子や発光素子などの表示素子が各画素に形成されたパネルと、該パネルにコントローラを含むIC等を実装した状態にあるモジュールとを、その範疇に含む。

## 【0016】

なお、本明細書において接続とは電気的な接続を意味しており、電流、電圧または電位が、供給可能、或いは伝送可能な状態に相当する。従って、接続している状態とは、直接接続している状態を必ずしも指すわけではなく、電流、電圧または電位が、供給可能、或いは伝送可能であるように、配線、抵抗、ダイオード、トランジスタなどの回路素子を介して間接的に接続している状態も、その範疇に含む。また、回路図上は独立している構成要素どうしが接続されている場合であっても、実際には、例えば配線の一部が電極として機能する場合など、一の導電膜が、複数の構成要素の機能を併せ持っている場合もある。本明細書において接続とは、このような、一の導電膜が、複数の構成要素の機能を併せ持っている場合も、その範疇に含める。

40

## 【0017】

なお、トランジスタのソースとは、活性層として機能する半導体膜の一部であるソース領域、或いは上記半導体膜に接続されたソース電極を意味する。同様に、トランジスタのドレンとは、上記半導体膜の一部であるドレン領域、或いは上記半導体膜に接続された

50

ドレイン電極を意味する。また、ゲートはゲート電極を意味する。

#### 【0018】

なお、トランジスタが有するソースとドレインは、トランジスタの極性及び各端子に与えられる電位の高低によって、その呼び方が入れ替わる。一般的に、nチャネル型トランジスタでは、低い電位が与えられる端子がソースと呼ばれ、高い電位が与えられる端子がドレインと呼ばれる。また、pチャネル型トランジスタでは、低い電位が与えられる端子がドレインと呼ばれ、高い電位が与えられる端子がソースと呼ばれる。本明細書では、便宜上、ソースとドレインとが固定されているものと仮定して、トランジスタの接続関係を説明する場合があるが、実際には上記電位の関係に従ってソースとドレインの呼び方が入れ替わる。

10

#### 【0019】

##### (実施の形態1)

本実施の形態では、本発明の一態様に係る順序回路（半導体装置ともいう）について説明する。

#### 【0020】

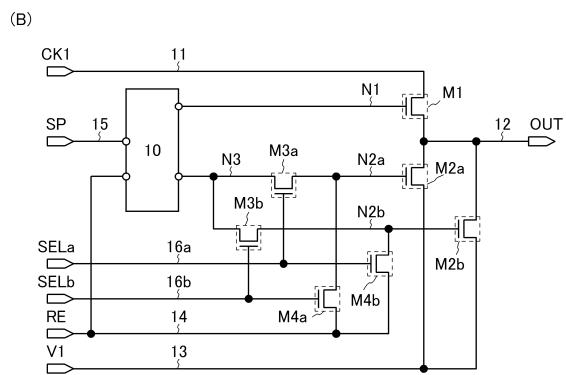

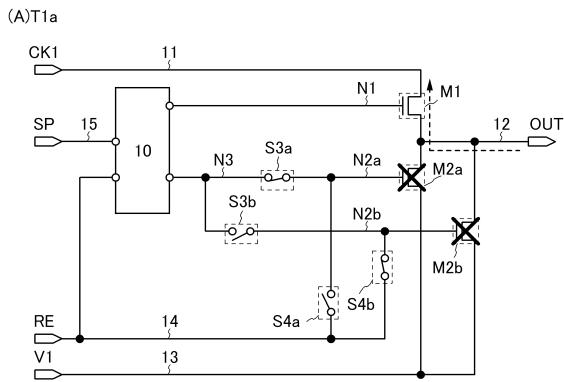

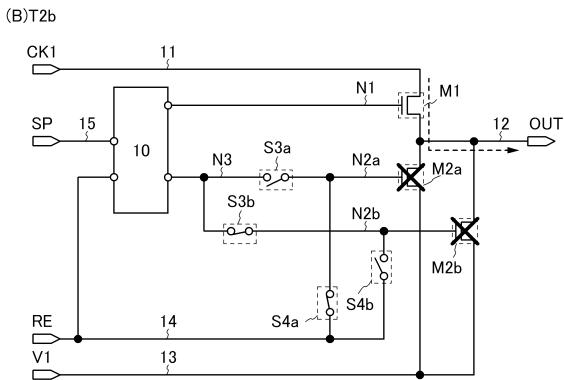

図1(A)は、本実施の形態の順序回路を示す。図1(A)の順序回路は、トランジスタM1、トランジスタM2a、トランジスタM2b、スイッチS3a、スイッチS3b、スイッチS4a、スイッチS4b、及び回路10を有する。

20

#### 【0021】

トランジスタM1は、第1の端子（ソース又はドレインの一方ともいう）が配線11と接続され、第2の端子（ソース又はドレインの他方ともいう）が配線12と接続され、ゲートがノードN1と接続される。トランジスタM2aは、第1の端子が配線13と接続され、第2の端子が配線12と接続され、ゲートがノードN2aと接続される。トランジスタM2bは、第1の端子が配線13と接続され、第2の端子が配線12と接続され、ゲートがノードN2bと接続される。スイッチS3aは、第1の端子がノードN3と接続され、第2の端子がノードN2aと接続される。スイッチS3bは、第1の端子がノードN3と接続され、第2の端子がノードN2bと接続される。スイッチS4aは、第1の端子が配線14と接続され、第2の端子がノードN2aと接続される。スイッチS4bは、第1の端子が配線14と接続され、第2の端子がノードN2bと接続される。回路10は、第1の端子が配線15と接続され、第2の端子が配線14と接続され、第3の端子がノードN1と接続され、第4の端子がノードN3と接続される。

30

#### 【0022】

回路10は、ノードN1にトランジスタM1のオン又はオフを制御するための電位を供給する機能を有する。具体的には、回路10は、ノードN1にトランジスタM1がオンになる電位を供給した後、ノードN1を浮遊状態とする機能を有する。また、回路10は、ノードN1にトランジスタM1がオフになる電位を供給する機能を有する。さらに、回路10は、ノードN3にトランジスタM2a又はトランジスタM2bのオン又はオフを制御するための電位を供給する機能を有する。具体的には、回路10は、ノードN3にトランジスタM2a又はトランジスタM2bがオンになる電位を供給する機能を有する。また、回路10は、ノードN3にトランジスタM2a又はトランジスタM2bがオフになる電位を供給する機能を有する。なお、回路10がノードN3に供給する電位は、スイッチS3aがオンであればノードN2aに供給され、スイッチS3bがオンであればノードN2bに供給される。また、回路10の接続関係は、回路10の構成により適宜変更することができる。

40

#### 【0023】

なお、順序回路が有するトランジスタは同じ極性とする。トランジスタの極性としては、Nチャネル型又はPチャネル型がある。本実施の形態では、便宜上、トランジスタM1、トランジスタM2a及びトランジスタM2bをNチャネル型とする。

#### 【0024】

なお、トランジスタは、第1の端子の接続先と第2の端子の接続先との導通又は非導通を

50

制御する機能を有する。例えば、トランジスタM 1は、配線1 1と配線1 2との導通又は非導通を制御する機能を有する。トランジスタM 2 aは、配線1 3と配線1 2との導通又は非導通を制御する機能を有する。トランジスタM 2 bは、配線1 3と配線1 2との導通又は非導通を制御する機能を有する。

#### 【0025】

なお、トランジスタは、ゲートの接続先と第1の端子又は第2の端子の接続先との間の電位差を保持する機能を有する。例えば、トランジスタM 1は、配線1 2とノードN 1との間の電位差を保持する機能を有する。

#### 【0026】

なお、トランジスタをスイッチに置き換えてよい。トランジスタの第1の端子がスイッチの第1の端子に対応し、トランジスタの第2の端子がスイッチの第2の端子に対応する。例えば、トランジスタM 2 aを第1の端子が配線1 3と接続され、第2の端子が配線1 2と接続されたスイッチに置き換えてよい。トランジスタM 2 bを第1の端子が配線1 3と接続され、第2の端子が配線1 2と接続されたスイッチに置き換えてよい。

10

#### 【0027】

なお、配線には信号又は電位等が入力され、配線は入力された信号又は電位等を伝達する機能を有する。例えば、配線1 1の信号又は電位は、配線1 2の電位を上昇させる機能を有することが好ましい。配線1 3の信号又は電位は、配線1 2の電位を下降させる機能を有することが好ましい。配線1 4は、トランジスタM 2 aのオン若しくはオフを制御する機能、トランジスタM 2 bのオン若しくはオフを制御する機能、又は回路1 0を制御する機能を有することが好ましい。配線1 5の信号又は電位は、回路1 0を制御する機能を有することが好ましい。

20

#### 【0028】

本実施の形態では、便宜上、配線1 1には信号CK 1（クロック信号ともいう）が入力され、配線1 2からは信号OUT（出力信号ともいう）が出力され、配線1 3には電位V 1（第1の電位ともいう）が供給され、配線1 4には信号RE（リセット信号ともいう）が入力され、配線1 5には信号SP（スタート信号ともいう）が入力されるものとする。また、便宜上、信号CK 1、信号SP及び信号REは、ハイレベル及びロウレベルを有するものとする。そして、ロウレベルの電位が電位V 1であり、ハイレベルの電位が電位V 2（第2の電位ともいう）であるものとする。電位V 2は電位V 1よりも高い電位である。

30

#### 【0029】

次に、図1(A)の順序回路の動作について説明する。

#### 【0030】

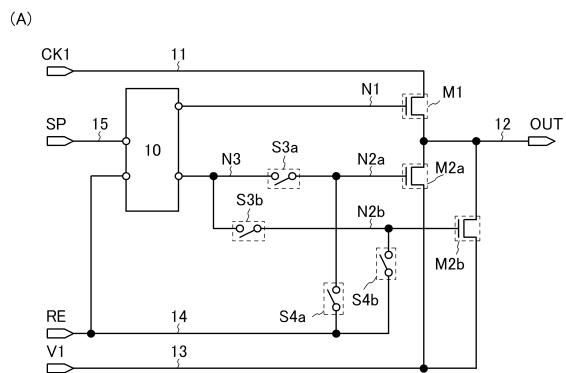

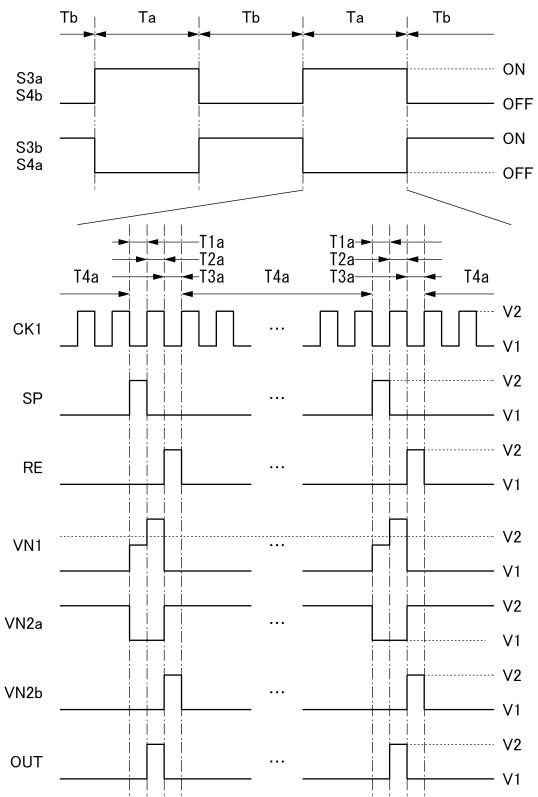

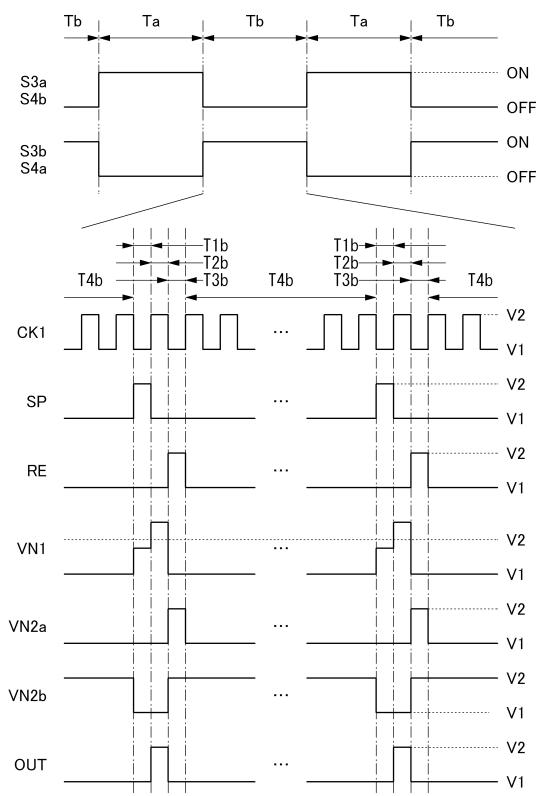

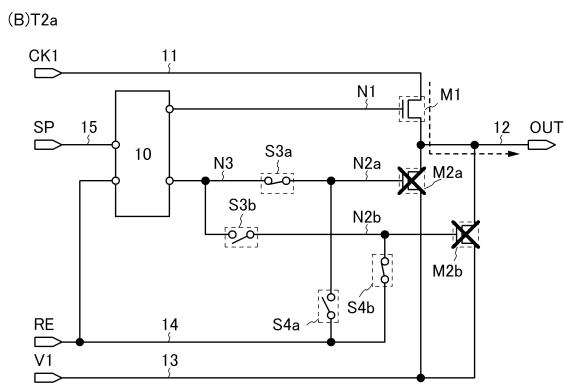

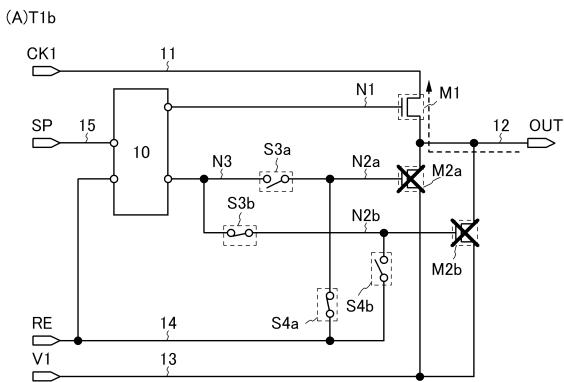

図2及び図3は、図1(A)の順序回路の動作を説明するためのタイミングチャートの一例を示す。図2及び図3のタイミングチャートは、期間Ta及び期間Tbを有する。そして、図2は、期間T1 a乃至期間T4 aを有する期間Taのタイミングチャートを示し、図3は、期間T1 b乃至期間T4 bを有する期間Tbのタイミングチャートを示す。また、図2及び図3は、スイッチS3 a及びスイッチS4 bのオン又はオフの関係、スイッチS3 b及びスイッチS4 aのオン又はオフの関係、信号CK 1、信号SP、信号RE、ノードN 1の電位VN 1、ノードN 2 aの電位VN 2 a、ノードN 2 bの電位VN 2 b、並びに信号OUTを示す。

40

#### 【0031】

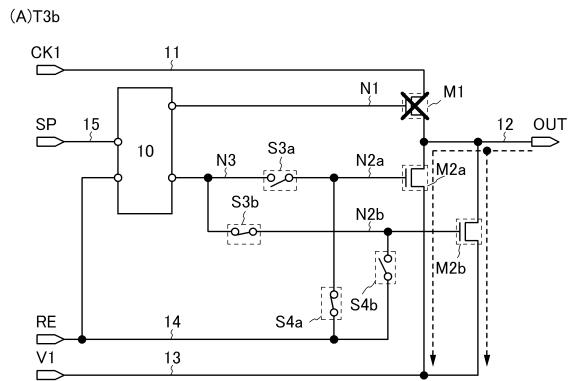

図4乃至図7は、各期間（各ステップともいう）における図1(A)の順序回路の動作の模式図を示す。図4(A)は期間T1 a、図4(B)は期間T2 a、図5(A)は期間T3 a、図5(B)は期間T4 a、図6(A)は期間T1 b、図6(B)は期間T2 b、図7(A)は期間T3 b、図7(B)は期間T4 bにおける図1(A)の順序回路の動作の模式図を示す。

#### 【0032】

まず、期間Taにおける動作について説明する。期間Taでは、スイッチS3 a及びスイッチS4 bがオンであり、スイッチS3 b及びスイッチS4 aがオフである。

50

**【 0 0 3 3 】**

期間 T 1 a では、信号 C K 1 がロウレベルになり、信号 S P がハイレベルになり、信号 R E がロウレベルになる。ノード N 1 にはトランジスタ M 1 がオンになる電位が回路 1 0 から供給されるため、トランジスタ M 1 がオンになる。その後、ノード N 1 への回路 1 0 からの電位の供給が止まるため、ノード N 1 が浮遊状態になる。ノード N 1 の電位はトランジスタ M 1 がオンになる電位に維持されるため、トランジスタ M 1 がオンのままになる。また、ノード N 2 a にはトランジスタ M 2 a がオフになる電位が回路 1 0 からスイッチ S 3 a を介して供給される。よって、トランジスタ M 2 a がオフになる。また、ノード N 2 b には信号 R E がスイッチ S 4 b を介して供給される。信号 R E はロウレベルであるため、トランジスタ M 2 b がオフになる。また、配線 1 2 には信号 C K 1 がトランジスタ M 1 を介して供給される。信号 C K 1 はロウレベルであるため、配線 1 2 の電位が電位 V 1 になる。つまり、信号 O U T がロウレベルになる。10

**【 0 0 3 4 】**

期間 T 2 a では、信号 C K 1 がハイレベルになり、信号 S P がロウレベルになり、信号 R E がロウレベルのままである。ノード N 1 への回路 1 0 からの電位の供給が止まったままなので、ノード N 1 が浮遊状態のままであり、トランジスタ M 1 がオンのままである。また、ノード N 2 a にはトランジスタ M 2 a がオフになる電位が回路 1 0 からスイッチ S 3 a を介して供給されたままであるため、トランジスタ M 2 a がオフのままである。また、ノード N 2 b には信号 R E がスイッチ S 4 b を介して供給されたままである。信号 R E はロウレベルのままであるため、トランジスタ M 2 b がオフのままである。また、配線 1 2 には信号 C K 1 がトランジスタ M 1 を介して供給されたままである。信号 C K 1 はハイレベルであるため、配線 1 2 の電位が電位 V 2 になる。つまり、信号 O U T がハイレベルになる。20

**【 0 0 3 5 】**

なお、ノード N 1 が浮遊状態であり、且つトランジスタ M 1 が配線 1 2 とノード N 1 との間の電位差を保持しているため、配線 1 2 の電位の上昇に伴ってノード N 1 の電位も上昇する。いわゆるブートストラップ動作である。これにより、ノード N 1 の電位をトランジスタ M 1 の第 1 の端子の電位（例えば電位 V 2 ）とトランジスタ M 1 のしきい値電圧との和を超えた値とすることができますため、配線 1 2 の電位を電位 V 2 まで上昇させることができる。30

**【 0 0 3 6 】**

期間 T 3 a では、信号 C K 1 がロウレベルになり、信号 S P がロウレベルのままであり、信号 R E がハイレベルになる。ノード N 1 にはトランジスタ M 1 がオフになる電位が回路 1 0 から供給されるため、トランジスタ M 1 がオフになる。また、ノード N 2 a にはトランジスタ M 2 a がオンになる電位が回路 1 0 からスイッチ S 3 a を介して供給されるため、トランジスタ M 2 a がオンになる。また、ノード N 2 b には信号 R E がスイッチ S 4 b を介して供給されたままである。信号 R E はハイレベルであるため、トランジスタ M 2 b がオンになる。すなわち、トランジスタ M 2 a 及びトランジスタ M 2 b の双方がオンになる。また、配線 1 2 には電位 V 1 がトランジスタ M 2 a 及びトランジスタ M 2 b の双方を介して供給される。よって、配線 1 2 の電位が電位 V 1 になる。つまり、信号 O U T がロウレベルになる。40

**【 0 0 3 7 】**

なお、配線 1 2 には電位 V 1 がトランジスタ M 2 a 及びトランジスタ M 2 b の双方を介して供給されるため、トランジスタ M 2 a 及びトランジスタ M 2 b の W / L を大きくすることなく、信号 O U T の立ち下がり時間を短くすることができる。

**【 0 0 3 8 】**

期間 T 4 a では、信号 C K 1 がハイレベルとロウレベルとを繰り返し、信号 S P がロウレベルのままであり、信号 R E がロウレベルになる。ノード N 1 にはトランジスタ M 1 がオフになる電位が回路 1 0 から供給されたままであるため、トランジスタ M 1 がオフのままである。また、ノード N 2 a にはトランジスタ M 2 a がオンになる電位が回路 1 0 からス50

イッチ S 3 a を介して供給されたままであるため、トランジスタ M 2 a がオンのままである。また、ノード N 2 b には信号 R E がスイッチ S 4 b を介して供給されたままである。信号 R E はロウレベルであるため、トランジスタ M 2 b がオフになる。また、配線 1 2 には電位 V 1 がトランジスタ M 2 a を介して供給される。よって、配線 1 2 の電位が電位 V 1 のままである。つまり、信号 O U T がロウレベルのままである。

#### 【 0 0 3 9 】

なお、期間 T 4 a は期間 T 1 a 乃至期間 T 3 a よりも長く、動作期間の大部分を占めている。そして、トランジスタ M 2 b は期間 T 4 a においてオフである。よって、トランジスタ M 2 b がオンである時間を短くすることができ、トランジスタ M 2 b の特性変化を抑制することができる。

10

#### 【 0 0 4 0 】

次に、期間 T b における動作について説明する。期間 T b では、スイッチ S 3 a 及びスイッチ S 4 b がオフであり、スイッチ S 3 b 及びスイッチ S 4 a がオンである。

#### 【 0 0 4 1 】

期間 T 1 b では、信号 C K 1 がロウレベルになり、信号 S P がハイレベルになり、信号 R E がロウレベルになる。ノード N 1 にはトランジスタ M 1 がオンになる電位が回路 1 0 から供給されるため、トランジスタ M 1 がオンになる。その後、ノード N 1 への回路 1 0 からの電位の供給が止まるため、ノード N 1 が浮遊状態になる。ノード N 1 の電位はトランジスタ M 1 がオンになる電位に維持されるため、トランジスタ M 1 がオンのままになる。また、ノード N 2 b にはトランジスタ M 2 b がオフになる電位が回路 1 0 からスイッチ S 3 b を介して供給される。よって、トランジスタ M 2 b がオフになる。また、ノード N 2 a には信号 R E がスイッチ S 4 a を介して供給される。信号 R E はロウレベルであるため、トランジスタ M 2 a がオフになる。また、配線 1 2 には信号 C K 1 がトランジスタ M 1 を介して供給される。信号 C K 1 はロウレベルであるため、配線 1 2 の電位が電位 V 1 になる。つまり、信号 O U T がロウレベルになる。

20

#### 【 0 0 4 2 】

期間 T 2 b では、信号 C K 1 がハイレベルになり、信号 S P がロウレベルになり、信号 R E がロウレベルのままである。ノード N 1 への回路 1 0 からの電位の供給が止まったままなので、ノード N 1 が浮遊状態のままであり、トランジスタ M 1 がオンのままである。また、ノード N 2 b にはトランジスタ M 2 b がオフになる電位が回路 1 0 からスイッチ S 3 b を介して供給されたままであるため、トランジスタ M 2 b がオフのままである。また、ノード N 2 a には信号 R E がスイッチ S 4 a を介して供給されたままである。信号 R E はロウレベルのままであるため、トランジスタ M 2 a がオフのままである。また、配線 1 2 には信号 C K 1 がトランジスタ M 1 を介して供給されたままである。信号 C K 1 はハイレベルであるため、配線 1 2 の電位が電位 V 2 になる。つまり、信号 O U T がハイレベルになる。

30

#### 【 0 0 4 3 】

なお、ノード N 1 が浮遊状態であり、且つトランジスタ M 1 が配線 1 2 とノード N 1との間の電位差を保持しているため、配線 1 2 の電位の上昇に伴ってノード N 1 の電位も上昇する。いわゆるブートストラップ動作である。これにより、ノード N 1 の電位をトランジスタ M 1 の第 1 の端子の電位（例えば電位 V 2 ）とトランジスタ M 1 のしきい値電圧との和を超えた値とすることができますため、配線 1 2 の電位を電位 V 2 まで上昇させることができます。

40

#### 【 0 0 4 4 】

期間 T 3 b では、信号 C K 1 がロウレベルになり、信号 S P がロウレベルのままであり、信号 R E がハイレベルになる。ノード N 1 にはトランジスタ M 1 がオフになる電位が回路 1 0 から供給されるため、トランジスタ M 1 がオフになる。また、ノード N 2 b にはトランジスタ M 2 b がオンになる電位が回路 1 0 からスイッチ S 3 b を介して供給されるため、トランジスタ M 2 b がオンになる。また、ノード N 2 a には信号 R E がスイッチ S 4 a を介して供給されたままである。信号 R E はハイレベルであるため、トランジスタ M 2 a

50

がオンになる。すなわち、トランジスタM 2 a 及びトランジスタM 2 b の双方がオンになる。また、配線1 2 には電位V 1 がトランジスタM 2 a 及びトランジスタM 2 b の双方を介して供給される。よって、配線1 2 の電位が電位V 1 になる。つまり、信号O U T がロウレベルになる。

#### 【 0 0 4 5 】

なお、配線1 2 には電位V 1 がトランジスタM 2 a 及びトランジスタM 2 b の双方を介して供給されるため、トランジスタM 2 a 及びトランジスタM 2 b のW / L を大きくすることなく、信号O U T の立ち下がり時間を短くすることができる。

#### 【 0 0 4 6 】

期間T 4 b では、信号C K 1 がハイレベルとロウレベルとを繰り返し、信号S P がロウレベルのままであり、信号R E がロウレベルになる。ノードN 1 にはトランジスタM 1 がオフになる電位が回路1 0 から供給されたままであるため、トランジスタM 1 がオフのままである。また、ノードN 2 b にはトランジスタM 2 b がオンになる電位が回路1 0 からスイッチS 3 b を介して供給されたままであるため、トランジスタM 2 b がオンのままである。また、ノードN 2 a には信号R E がスイッチS 4 a を介して供給されたままである。信号R E はロウレベルであるため、トランジスタM 2 a がオフになる。また、配線1 2 には電位V 1 がトランジスタM 2 b を介して供給される。よって、配線1 2 の電位が電位V 1 のままである。つまり、信号O U T がロウレベルのままである。

#### 【 0 0 4 7 】

なお、期間T 4 b は期間T 1 b 乃至期間T 3 b よりも長く、動作期間の大部分を占めている。そして、トランジスタM 2 a は期間T 4 b においてオフである。よって、トランジスタM 2 a がオンである時間を短くすることができ、トランジスタM 2 a の特性変化を抑制することができる。

#### 【 0 0 4 8 】

以上のとおり、図1 ( A ) の順序回路は、トランジスタの特性変化を抑制することができるとともに、トランジスタのW / L を大きくすることなく出力信号の立ち下がり時間を短くすることができる。

#### 【 0 0 4 9 】

なお、トランジスタM 1 がオンになる電位とは、トランジスタM 1 の第1の端子又は第2の端子の電位（例えば電位V 1 ）とトランジスタM 1 のしきい値電圧との和を超えた値である。また、トランジスタM 1 がオフになる電位とは、トランジスタM 1 の第1の端子又は第2の端子の電位（例えば電位V 1 ）とトランジスタM 1 のしきい値電圧との和未満の値である。例えば、トランジスタM 1 がオフになる電位としては、電位V 1 がある。また、トランジスタM 2 a 又はトランジスタM 2 b がオンになる電位とは、トランジスタM 2 a 又はトランジスタM 2 b の第1の端子の電位（例えば電位V 1 ）とトランジスタM 2 a 又はトランジスタM 2 b のしきい値電圧との和を超えた値である。例えば、トランジスタM 2 a 又はトランジスタM 2 b がオフになる電位としては、電位V 2 がある。また、トランジスタM 2 a 又はトランジスタM 2 b がオフになる電位とは、トランジスタM 2 a 又はトランジスタM 2 b の第1の端子の電位（例えば電位V 1 ）とトランジスタM 2 a 又はトランジスタM 2 b のしきい値電圧との和未満の値である。例えば、トランジスタM 2 a 又はトランジスタM 2 b がオフになる電位としては、電位V 1 がある。なお、トランジスタM 1 がオフになる電位は、トランジスタM 2 a 又はトランジスタM 2 b がオフになる電位と等しくてもよいし、異なっていてもよい。また、トランジスタM 2 a がオンになる電位は、トランジスタM 2 b がオンになる電位と等しくてもよいし、異なっていてもよい。また、トランジスタM 2 a がオフになる電位は、トランジスタM 2 b がオフになる電位と等しくてもよいし、異なっていてもよい。

#### 【 0 0 5 0 】

なお、上述した動作の説明は一例であり、これに限定されない。例えば、回路1 0 は、期間T 1 a においてトランジスタM 2 a がオンになる電位をノードN 2 a に供給し、期間T 1 b においてトランジスタM 2 b がオンになる電位をノードN 2 b に供給してもよい。こ

10

20

30

40

50

の場合、期間 T 1 a において、トランジスタ M 2 a がオンになり、電位 V 1 がトランジスタ M 2 a を介して配線 1 2 に供給される。また、期間 T 1 b において、トランジスタ M 2 b がオンになり、電位 V 1 がトランジスタ M 2 b を介して配線 1 2 に供給される。

#### 【 0 0 5 1 】

また、回路 1 0 は、期間 T 4 a 及び期間 T 4 b においてノード N 1 への電位の供給を止めてもよい。この場合、期間 T 4 a 及び期間 T 4 b において、ノード N 1 が浮遊状態になる。ノード N 1 の電位は期間 T 3 a 又は期間 T 3 b における電位（トランジスタ M 1 がオフになる電位）に維持されるため、トランジスタ M 1 がオフのままとなる。

#### 【 0 0 5 2 】

また、回路 1 0 は、期間 T 4 a 及び期間 T 4 b においてノード N 3 への電位の供給を止めてもよい。この場合、期間 T 4 a において、ノード N 3 及びノード N 2 a が浮遊状態になる。ノード N 2 a の電位はトランジスタ M 2 a がオンになる電位に維持されるため、トランジスタ M 2 a がオンのままとなる。また、期間 T 4 b において、ノード N 3 及びノード N 2 b が浮遊状態になる。ノード N 2 b の電位はトランジスタ M 2 b がオンになる電位に維持されるため、トランジスタ M 2 b がオンのままとなる。

10

#### 【 0 0 5 3 】

なお、トランジスタ M 1 の W ( W はチャネル幅 ) / L ( L はチャネル長 ) は、図 1 ( A ) の順序回路が有するトランジスタの中で一番大きいことが好ましい。例えば、トランジスタ M 1 の W / L は、トランジスタ M 2 a 及びトランジスタ M 2 b の W / L よりも大きいことが好ましい。また、回路 1 0 がトランジスタを有する場合、トランジスタ M 1 の W / L は、回路 1 0 が有するトランジスタの W / L よりも大きいことが好ましい。

20

#### 【 0 0 5 4 】

また、トランジスタ M 2 a の W / L は、トランジスタ M 2 b の W / L と概ね等しいことが好ましい。例えば、トランジスタ M 2 a の W / L は、トランジスタ M 2 b の W / L の ± 1 0 [ % ] 以内であることが好ましい。より好ましくは ± 5 [ % ] 以内である。

#### 【 0 0 5 5 】

なお、本明細書等において、W / L を W と置き換えてよい。なぜなら、トランジスタのチャネル長は等しい又は概略等しいことが多いからである。

#### 【 0 0 5 6 】

なお、期間 T a 及び期間 T b の切り替わりは期間 T 4 a 又は期間 T 4 b において行われることが好ましい。具体的には、期間 T 4 a において、スイッチ S 3 a 及びスイッチ S 4 b がオンからオフになり、スイッチ S 3 b 及びスイッチ S 4 a がオフからオンになることが好ましい。また、期間 T 4 b において、スイッチ S 3 b 及びスイッチ S 4 a がオフからオンになり、スイッチ S 3 a 及びスイッチ S 4 b がオンからオフになることが好ましい。こうすれば、期間 T a 及び期間 T b の切り替わりによる誤動作を防止することができる。

30

#### 【 0 0 5 7 】

また、スイッチ S 3 a 及びスイッチ S 4 b がオンからオフになった後に、スイッチ S 3 b 及びスイッチ S 4 a がオフからオンになってよい。同様に、スイッチ S 3 b 及びスイッチ S 4 a がオンからオフになった後に、スイッチ S 3 a 及びスイッチ S 4 b がオフからオンになってよい。すなわち、スイッチ S 3 a 、スイッチ S 3 b 、スイッチ S 4 a 及びスイッチ S 4 b がオフである期間を有していてよい。こうすれば、回路 1 0 の第 4 の端子と配線 1 4 とが導通してしまうことを防止することができる。

40

#### 【 0 0 5 8 】

また、期間 T 1 a 乃至期間 T 4 a を複数回（例えば 1 0 0 回以上、より好ましくは 2 0 0 回以上、さらに好ましくは 3 0 0 回以上）繰り返した後に、期間 T a から期間 T b に切り替わることが好ましい。また、期間 T 1 b 乃至期間 T 4 b を複数回（1 0 0 回以上、より好ましくは 2 0 0 回以上、さらに好ましくは 3 0 0 回以上）繰り返した後に、期間 T b から期間 T a に切り替わることが好ましい。すなわち、期間 T a は、期間 T 1 a 乃至期間 T 4 a のいずれかを複数個（例えば 1 0 0 個以上、より好ましくは 2 0 0 個以上、さらに好ましくは 3 0 0 個以上）有することが好ましい。また、期間 T b は、期間 T 1 b 乃至期間

50

T<sub>4</sub> b のいずれかを複数個（100個以上、より好ましくは200個以上、さらに好ましくは300個以上）有することが好ましい。こうすれば、期間T<sub>a</sub>及び期間T<sub>b</sub>の切り替わりに伴う消費電力の増加を抑制することができる。ただし、繰り返す回数が多すぎると、トランジスタM<sub>2</sub> a 及びトランジスタM<sub>2</sub> b の特性にばらつきを生じる恐れがある。そのため、期間T<sub>1</sub> a 乃至期間T<sub>4</sub> a を繰り返す回数、又は期間T<sub>1</sub> b 乃至期間T<sub>4</sub> b を繰り返す回数は、1000回未満、より好ましくは700回未満、さらに好ましくは500回未満であるとよい。

#### 【0059】

なお、スイッチとしてはトランジスタを適用することができる。図1(B)は、図1(A)において、スイッチS<sub>3</sub> a、スイッチS<sub>3</sub> b、スイッチS<sub>4</sub> a 及びスイッチS<sub>4</sub> b としてトランジスタM<sub>3</sub> a、トランジスタM<sub>3</sub> b、トランジスタM<sub>4</sub> a 及びトランジスタM<sub>4</sub> b をそれぞれ適用した順序回路を示す。トランジスタM<sub>3</sub> a、トランジスタM<sub>3</sub> b、トランジスタM<sub>4</sub> a 及びトランジスタM<sub>4</sub> b は、トランジスタM<sub>1</sub>と同じ極性である。トランジスタM<sub>3</sub> a は、第1の端子がノードN<sub>3</sub>と接続され、第2の端子がノードN<sub>2</sub> a と接続され、ゲートが配線16 aと接続される。トランジスタM<sub>3</sub> b は、第1の端子がノードN<sub>3</sub>と接続され、第2の端子がノードN<sub>2</sub> b と接続され、ゲートが配線16 bと接続される。トランジスタM<sub>4</sub> a は、第1の端子が配線14と接続され、第2の端子がノードN<sub>2</sub> a と接続され、ゲートが配線16 bと接続される。トランジスタM<sub>4</sub> b は、第1の端子が配線14と接続され、第2の端子がノードN<sub>2</sub> b と接続され、ゲートが配線16 aと接続される。配線16 aの信号又は電位は、トランジスタM<sub>3</sub> aのオン若しくはオフを制御する機能、又はトランジスタM<sub>4</sub> bのオン若しくはオフを制御する機能を有することが好ましい。また、配線16 bの信号又は電位は、トランジスタM<sub>3</sub> bのオン若しくはオフを制御する機能、又はトランジスタM<sub>4</sub> aのオン若しくはオフを制御する機能を有することが好ましい。本実施の形態では、便宜上、配線16 aには信号SEL aが入力され、配線16 bには信号SEL bが入力されるものとする。

#### 【0060】

期間T<sub>a</sub>では、信号SEL aがハイレベルであり、信号SEL bがロウレベルである。よって、トランジスタM<sub>3</sub> a 及びトランジスタM<sub>4</sub> b がオンであり、トランジスタM<sub>3</sub> b 及びトランジスタM<sub>4</sub> a がオフである。期間T<sub>b</sub>では、信号SEL aがロウレベルであり、信号SEL bがハイレベルである。よって、トランジスタM<sub>3</sub> a 及びトランジスタM<sub>4</sub> b がオフであり、トランジスタM<sub>3</sub> b 及びトランジスタM<sub>4</sub> a がオンである。すなわち、トランジスタM<sub>3</sub> a、トランジスタM<sub>3</sub> b、トランジスタM<sub>4</sub> a 及びトランジスタM<sub>4</sub> b は、スイッチS<sub>3</sub> a、スイッチS<sub>3</sub> b、スイッチS<sub>4</sub> a 及びスイッチS<sub>4</sub> b とそれ同様のタイミングでオン又はオフが制御される。よって、図1(B)の順序回路は、図1(A)の順序回路と同様の動作を行うことができるため、図1(A)の順序回路と同様の効果を奏する。

#### 【0061】

なお、信号SEL a 及び信号SEL b のロウレベルの電位を電位V<sub>1</sub>としてもよい。ただし、これに限定されず、信号SEL a 及び信号SEL b のロウレベルの電位を電位V<sub>1</sub>未満の値としてもよい。こうすれば、トランジスタのゲートとソースとの間の電位差を0[V]未満にすることができるため、トランジスタの特性変化を抑制することができる。

#### 【0062】

また、信号SEL a 及び信号SEL b のハイレベルの電位を電位V<sub>2</sub>としてもよい。ただし、これに限定されず、信号SEL a 及び信号SEL b のハイレベルの電位を電位V<sub>2</sub>よりも高い値としてもよい。こうすれば、ノードN<sub>2</sub> a 及びノードN<sub>2</sub> b の電位を高くすることができる。

#### 【0063】

なお、信号SEL aがハイレベルからロウレベルとなった後に、信号SEL bがロウレベルからハイレベルとなってもよい。また、信号SEL bがハイレベルからロウレベルとなった後に、信号SEL aがロウレベルからハイレベルとなってもよい。すなわち、信号S

10

20

30

40

50

E L a 及び信号 S E L b がロウレベルである期間を有していてもよい。こうすれば、回路 10 の第 4 の端子と配線 14 とが導通してしまうことを防止することができる。

#### 【 0 0 6 4 】

なお、トランジスタ M 3 a の W / L は、トランジスタ M 3 b の W / L と概ね等しいことが好ましい。例えば、トランジスタ M 3 a の W / L は、トランジスタ M 3 b の W / L の ± 10 [ % ] 以内であることが好ましい。より好ましくは ± 5 [ % ] 以内である。また、トランジスタ M 4 a の W / L は、トランジスタ M 4 b の W / L と概ね等しいことが好ましい。例えば、トランジスタ M 4 a の W / L は、トランジスタ M 4 b の W / L の ± 10 [ % ] 以内であることが好ましい。より好ましくは ± 5 [ % ] 以内である。また、トランジスタ M 1 の W / L は、トランジスタ M 3 a、トランジスタ M 3 b、トランジスタ M 4 a 及びトランジスタ M 4 b の W / L よりも大きいことが好ましい。また、トランジスタ M 2 a 及びトランジスタ M 2 b の W / L は、トランジスタ M 3 a、トランジスタ M 3 b、トランジスタ M 4 a 及びトランジスタ M 4 b の W / L よりも大きいことが好ましい。また、トランジスタ M 4 a 及びトランジスタ M 4 b の W / L は、トランジスタ M 3 a 及びトランジスタ M 3 b の W / L よりも大きいことが好ましい。

10

#### 【 0 0 6 5 】

本実施の形態は、他の実施の形態等に記載した構成と適宜組み合わせて実施することができる。

#### 【 0 0 6 6 】

##### ( 実施の形態 2 )

20

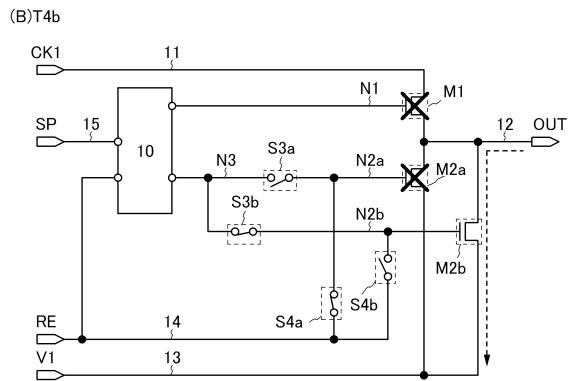

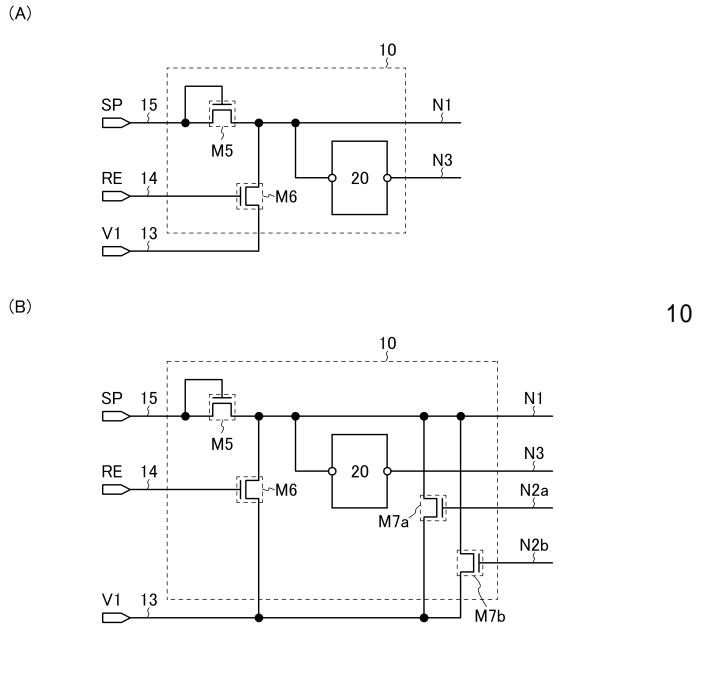

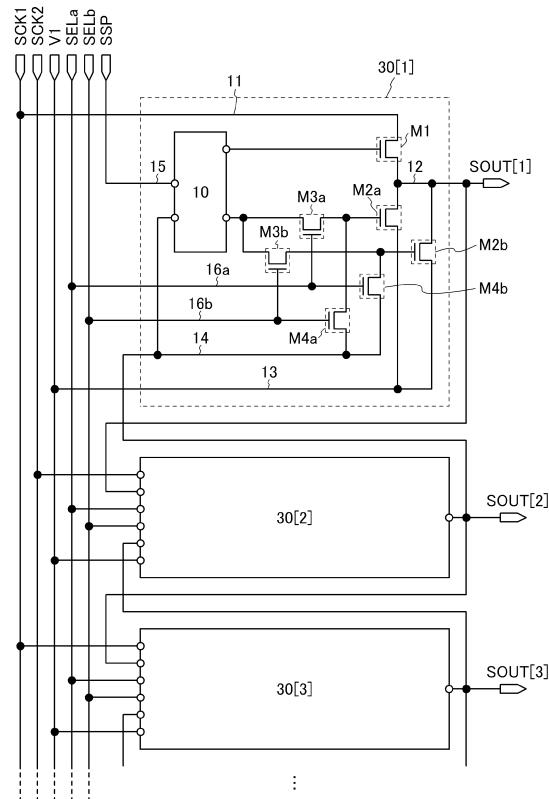

本実施の形態では、実施の形態 1 の順序回路の回路 10 に適用することができる回路について説明する。

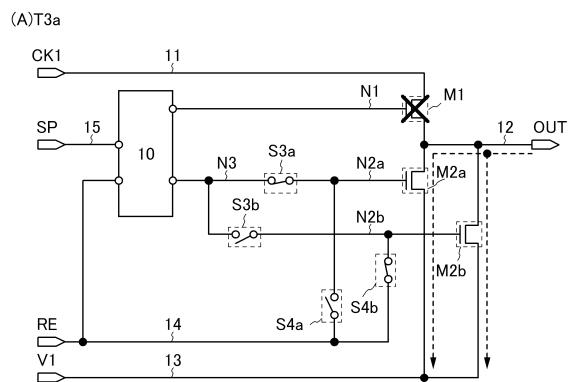

#### 【 0 0 6 7 】

図 8 ( A ) の回路 10 は、トランジスタ M 5、トランジスタ M 6 及び回路 20 を有する。トランジスタ M 5 及びトランジスタ M 6 は、トランジスタ M 1 と同じ極性である。トランジスタ M 5 は、第 1 の端子が配線 15 と接続され、第 2 の端子がノード N 1 と接続され、ゲートが配線 15 と接続される。トランジスタ M 6 は、第 1 の端子が配線 13 と接続され、第 2 の端子がノード N 1 と接続され、ゲートが配線 14 と接続される。回路 20 は、第 1 の端子がノード N 1 と接続され、第 2 の端子がノード N 3 と接続される。

30

#### 【 0 0 6 8 】

回路 20 は、ノード N 1 の電位に応じて、ノード N 3 にトランジスタ M 2 a 又はトランジスタ M 2 b のオン又はオフを制御するための電位を供給する機能を有する。具体的には、回路 20 は、ノード N 1 の電位が低いとき（例えば期間 T 3 a、期間 T 3 b、期間 T 4 a 又は期間 T 4 b 等）において、ノード N 3 にトランジスタ M 2 a 又はトランジスタ M 2 b がオンになる電位を供給する機能を有する。また、回路 20 は、ノード N 1 の電位が高いとき（例えば期間 T 1 a、期間 T 1 b、期間 T 2 a 又は期間 T 2 b 等）において、ノード N 3 にトランジスタ M 2 a 又はトランジスタ M 2 b がオフになる電位を供給する機能を有する。また、回路 20 を入力端子がノード N 1 と接続され、出力端子がノード N 3 と接続されたインバータ回路に置き換えるてもよい。

30

#### 【 0 0 6 9 】

期間 T 1 a 及び期間 T 1 b において、トランジスタ M 5 がオンになり、トランジスタ M 6 がオフになる。ノード N 1 には信号 S P がトランジスタ M 5 を介して供給される。信号 S P はハイレベルであるため、ノード N 1 の電位が上昇する。ノード N 1 の電位がトランジスタ M 5 のゲートの電位（例えば電位 V 2 ）からトランジスタ M 5 のしきい値電圧を引いた値になると、トランジスタ M 5 がオフになる。よって、ノード N 1 は浮遊状態になる。また、回路 20 は、トランジスタ M 2 a 又はトランジスタ M 2 b がオフになる電位をノード N 3 に供給する。

40

#### 【 0 0 7 0 】

期間 T 2 a 及び期間 T 2 b において、トランジスタ M 5 がオフのままであり、トランジスタ M 6 がオフのままである。また、回路 20 は、トランジスタ M 2 a 又はトランジスタ M

50

2 b がオフになる電位をノード N 3 に供給したままである。

#### 【 0 0 7 1 】

期間 T 3 a 及び期間 T 3 b において、トランジスタ M 5 がオフのままであり、トランジスタ M 6 がオンになる。ノード N 1 には電位 V 1 がトランジスタ M 6 を介して供給されるため、ノード N 1 の電位が電位 V 1 になる。また、回路 2 0 は、トランジスタ M 2 a 又はトランジスタ M 2 b がオンになる電位をノード N 3 に供給する。

#### 【 0 0 7 2 】

期間 T 4 a 及び期間 T 4 b において、トランジスタ M 5 がオフのままであり、トランジスタ M 6 がオフになる。また、回路 2 0 はトランジスタ M 2 a 又はトランジスタ M 2 b がオンになる電位をノード N 3 に供給したままである。

10

#### 【 0 0 7 3 】

図 8 ( B ) の回路 1 0 は、図 8 ( A ) と比較して、トランジスタ M 7 a 及びトランジスタ M 7 b を有するところが異なる。トランジスタ M 7 a 及びトランジスタ M 7 b は、トランジスタ M 1 と同じ極性である。トランジスタ M 7 a は、第 1 の端子が配線 1 3 と接続され、第 2 の端子がノード N 1 と接続され、ゲートがノード N 2 a と接続される。トランジスタ M 7 b は、第 1 の端子が配線 1 3 と接続され、第 2 の端子がノード N 1 と接続され、ゲートがノード N 2 b と接続される。

#### 【 0 0 7 4 】

期間 T 1 a 、期間 T 2 a 、期間 T 1 b 及び期間 T 2 b において、トランジスタ M 7 a 及びトランジスタ M 7 b がオフである。また、期間 T 3 a 及び期間 T 3 b において、トランジスタ M 7 a 及びトランジスタ M 7 b がオンである。また、期間 T 4 a において、トランジスタ M 7 a がオンであり、トランジスタ M 7 b がオフである。また、期間 T 4 b において、トランジスタ M 7 a がオフであり、トランジスタ M 7 b がオンである。図 8 ( B ) の回路 1 0 では、期間 T 3 a 、期間 T 4 a 、期間 T 3 b 及び期間 T 4 b において、電位 V 1 がノード N 1 に供給される。よって、ノード N 1 の電位を電位 V 1 に維持しやすくなる。

20

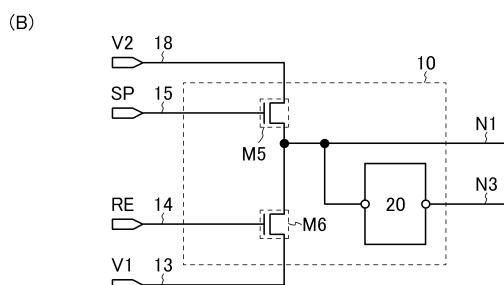

#### 【 0 0 7 5 】

図 9 ( A ) の回路 1 0 は、図 8 ( A ) と比較して、トランジスタ M 5 のゲートが配線 1 7 と接続されるところが異なる。配線 1 7 の信号又は電位は、トランジスタ M 5 のオン又はオフを制御する機能を有することが好ましい。本実施の形態では、便宜上、配線 1 7 には信号 C K 2 が入力されるものとする。信号 C K 2 としては、信号 C K 1 が反転した信号、信号 C K 1 と位相が異なる信号等がある。例えば、信号 C K 2 は、期間 T 1 a 及び期間 T 1 b ではハイレベルであり、期間 T 2 a 及び期間 T 2 b ではロウレベルであり、期間 T 3 a 及び期間 T 3 b ではハイレベル又はロウレベルであり、期間 T 4 a 及び期間 T 4 b ではハイレベルとロウレベルとを繰り返す。

30

#### 【 0 0 7 6 】

期間 T 1 a 及び期間 T 1 b において、トランジスタ M 5 がオンになる。よって、信号 S P がトランジスタ M 5 を介してノード N 1 に供給される。信号 S P はハイレベルであるため、ノード N 1 の電位が上昇する。ただし、ノード N 1 の電位がトランジスタ M 5 のゲートの電位（例えば電位 V 2 ）からトランジスタ M 5 のしきい値電圧を引いた値になると、トランジスタ M 5 がオフになる。また、期間 T 2 a 及び期間 T 2 b において、トランジスタ M 5 がオフである。また、期間 T 3 a 及び期間 T 3 b において、信号 C K 2 がハイレベルであれば、トランジスタ M 5 がオンである。よって、信号 S P がトランジスタ M 5 を介してノード N 1 に供給される。一方、信号 C K 2 がロウレベルであれば、トランジスタ M 5 がオフである。また、期間 T 4 a 及び期間 T 4 b において、トランジスタ M 5 はオンとオフとを繰り返す。トランジスタ M 5 がオンであれば、信号 S P がトランジスタ M 5 を介してノード N 1 に供給される。図 9 ( A ) の回路 1 0 では、期間 T 4 a 及び期間 T 4 b において、信号 S P がノード N 1 に供給される。信号 S P はロウレベルであるため、ノード N 1 の電位を電位 V 1 に維持しやすくなる。

40

#### 【 0 0 7 7 】

図 9 ( B ) の回路 1 0 は、図 8 ( A ) と比較して、トランジスタ M 5 の第 1 の端子が配線

50

18と接続されるところが異なる。配線18の信号又は電位は、トランジスタM1をオンにする機能を有する。本実施の形態では、便宜上、配線18には電位V2が供給されるものとする。

#### 【0078】

期間T1a及び期間T1bにおいて、トランジスタM5がオンである。よって、電位V2がトランジスタM5を介してノードN1に供給されるため、ノードN1の電位が上昇する。ただし、ノードN1の電位がトランジスタM5のゲートの電位（例えば電位V2）からトランジスタM5のしきい値電圧を引いた値になると、トランジスタM5がオフになる。また、期間T2a乃至期間T4a、及び期間T2b乃至期間T4bにおいて、トランジスタM5がオフである。図9(B)の回路10では、期間T1a及び期間T1bにおいて、電位V2がノードN1に供給される。よって、配線15に流れる電流を小さくすることができる。

10

#### 【0079】

なお、図8(B)において、図9(A)と同様にトランジスタM5のゲートを配線17と接続してもよいし、図9(B)と同様にトランジスタM5の第1の端子を配線18と接続してもよい。特に、図8(B)において、トランジスタM5のゲートを配線17と接続すると、期間T4a及び期間T4bにおいて、ノードN1にトランジスタM7a又はトランジスタM7bを介して供給された電位V1が、トランジスタM5を介して配線15に供給される。よって、配線15の電位を電位V1に維持しやすくなる。

20

#### 【0080】

なお、図8(A)、図8(B)及び図9(B)において、トランジスタM5の第1の端子を配線17と接続してもよい。こうすれば、例えば期間T1a、期間T4aの一部、期間T1b、又は期間T4bの一部等において、トランジスタM5の第1の端子の電位が低くなるため、トランジスタM5の特性変化を抑制することができる。

20

#### 【0081】

なお、図8(A)、図8(B)及び図9(B)において、第1の端子が配線15と接続され、第2の端子がノードN1と接続され、ゲートが配線17と接続されたトランジスタを新たに設けてもよい。こうすれば、図9(A)の回路10と同様の効果を奏すことができる。

30

#### 【0082】

なお、図8(A)、図8(B)及び図9(A)において、第1の端子が配線18又は配線17と接続され、第2の端子がノードN1と接続され、ゲートが配線15と接続されたトランジスタを新たに設けてもよい。こうすれば、図9(B)の回路10と同様の効果を奏すことができる。

30

#### 【0083】

なお、図9(A)のように回路10が第1の端子が配線15と接続され、第2の端子がノードN1と接続され、ゲートが配線17と接続されるトランジスタを有する場合、トランジスタM6を省略してもよい。

40

#### 【0084】

なお、上述した回路10において、トランジスタM6の第1の端子を配線11と接続してもよい。

#### 【0085】

なお、上述した回路10において、回路20の第1の端子を配線12と接続してもよい。

#### 【0086】

なお、上述した回路10において、トランジスタM6の第1の端子を配線18又は配線17と接続し、トランジスタM6の第2の端子をノードN3と接続してもよい。または、第1の端子が配線18又は配線17と接続され、第2の端子がノードN3と接続され、ゲートが配線14と接続されたトランジスタを新たに設けてもよい。または、第1の端子が配線18又は配線17と接続され、第2の端子がノードN2aと接続され、ゲートが配線14と接続されたトランジスタと、第1の端子が配線18又は配線17と接続され、第2の

50

端子がノードN 2 bと接続され、ゲートが配線1 4と接続されたトランジスタと、を新たに設けてよい。

**【0087】**

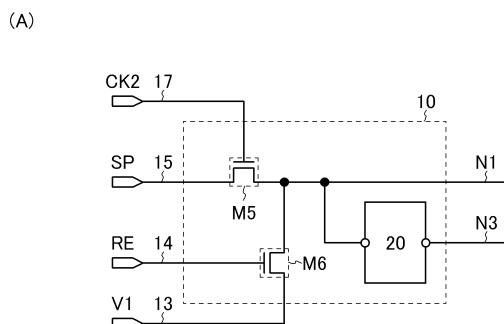

次に、回路2 0に適用することができる回路について説明する。

**【0088】**

図10(A)の回路2 0は、トランジスタM 8、及びトランジスタM 9を有する。トランジスタM 8及びトランジスタM 9はトランジスタM 1と同じ極性である。トランジスタM 8は、第1の端子が配線1 8と接続され、第2の端子が回路2 0の第2の端子と接続され、ゲートが配線1 8と接続される。トランジスタM 9は、第1の端子が配線1 3と接続され、第2の端子が回路2 0の第2の端子と接続され、ゲートが回路2 0の第1の端子と接続される。期間T 1 a、期間T 2 a、期間T 1 b及び期間T 2 bにおいて、トランジスタM 8がオンであり、トランジスタM 9がオフである。また、期間T 3 a、期間T 4 a、期間T 3 b及び期間T 4 bにおいて、トランジスタM 8がオフになり、トランジスタM 9がオンである。

10

**【0089】**

なお、トランジスタM 8の第1の端子を配線1 1又は配線1 7と接続してもよい。また、トランジスタM 8のゲートを配線1 1又は配線1 7と接続してもよい。また、トランジスタM 8の第1の端子及びゲートの双方を配線1 1又は配線1 7と接続してもよい。

**【0090】**

図10(B)の回路2 0は、トランジスタM 1 0乃至トランジスタM 1 3を有する。トランジスタM 1 0乃至トランジスタM 1 3は、トランジスタM 1と同じ極性である。トランジスタM 1 0は、第1の端子が配線1 8と接続され、第2の端子が回路2 0の第2の端子と接続される。トランジスタM 1 1は、第1の端子が配線1 3と接続され、第2の端子が回路2 0の第2の端子と接続され、ゲートが回路2 0の第1の端子と接続される。トランジスタM 1 2は、第1の端子が配線1 8と接続され、第2の端子がトランジスタM 1 0のゲートと接続され、ゲートが配線1 8と接続される。トランジスタM 1 3は、第1の端子が配線1 3と接続され、第2の端子がトランジスタM 1 0のゲートと接続され、ゲートが回路2 0の第1の端子と接続される。期間T 1 a、期間T 2 a、期間T 1 b及び期間T 2 bにおいて、トランジスタM 1 0がオフであり、トランジスタM 1 1がオンであり、トランジスタM 1 2がオフであり、トランジスタM 1 3がオフである。期間T 3 a、期間T 4 a、期間T 3 b及び期間T 4 bにおいて、トランジスタM 1 0がオンであり、トランジスタM 1 1がオフであり、トランジスタM 1 2がオンであり、トランジスタM 1 3がオフである。

20

30

**【0091】**

なお、トランジスタM 1 0の第1の端子、トランジスタM 1 2の第1の端子、及びトランジスタM 1 2のゲートを配線1 1又は配線1 7と接続してもよい。こうすれば、期間T 4 a及び期間T 4 bにおいて、回路2 0からハイレベルヒロウレベルとを繰り返す信号を出力することができる。よって、トランジスタM 2 a及びトランジスタM 2 bの特性変化を抑制することができる。

**【0092】**

図10(C)の回路2 0は、トランジスタM 1 4乃至トランジスタM 1 8、及び容量素子Cを有する。トランジスタM 1 4乃至トランジスタM 1 8は、トランジスタM 1と同じ極性である。トランジスタM 1 4は、第1の端子が配線1 8と接続され、第2の端子が回路2 0の第2の端子と接続される。トランジスタM 1 5は、第1の端子が配線1 3と接続され、第2の端子が回路2 0の第2の端子と接続され、ゲートが回路2 0の第1の端子と接続される。トランジスタM 1 6は、第1の端子が配線1 8と接続され、ゲートがトランジスタM 1 4のゲートと接続される。トランジスタM 1 7は、第1の端子が配線1 3と接続され、第2の端子がトランジスタM 1 6の第2の端子と接続され、ゲートが回路2 0の第1の端子と接続される。トランジスタM 1 8は、第1の端子が配線1 3と接続され、第2の端子がトランジスタM 1 4のゲートと接続され、ゲートが回路2 0の第1の端子と接続

40

50

される。容量素子Cは、第1の電極が回路20の第1の端子と接続され、第2の電極がトランジスタM16の第2の端子と接続される。期間T1a、期間T2a、期間T1b及び期間T2bにおいて、トランジスタM14がオフであり、トランジスタM15がオンであり、トランジスタM16がオフであり、トランジスタM17がオンであり、トランジスタM18がオンである。期間T3a、期間T4a、期間T3b及び期間T4bにおいて、トランジスタM14がオンであり、トランジスタM15がオフであり、トランジスタM16がオンであり、トランジスタM17がオフであり、トランジスタM18がオフである。図10(C)の回路20は、期間T3a及び期間T3bにおいて、容量素子Cの容量結合を用いてトランジスタM14及びトランジスタM16をオンにするため、回路20の第2の端子の電位の立ち上がり時間を短くすることができる。よって、トランジスタM2a又はトランジスタM2bがオンになるタイミングを早くすることができるため、信号OUTの立ち下がり時間をより短くすることができる。

#### 【0093】

本実施の形態は、他の実施の形態等に記載した構成と適宜組み合わせて実施することができる。

#### 【0094】

##### (実施の形態3)

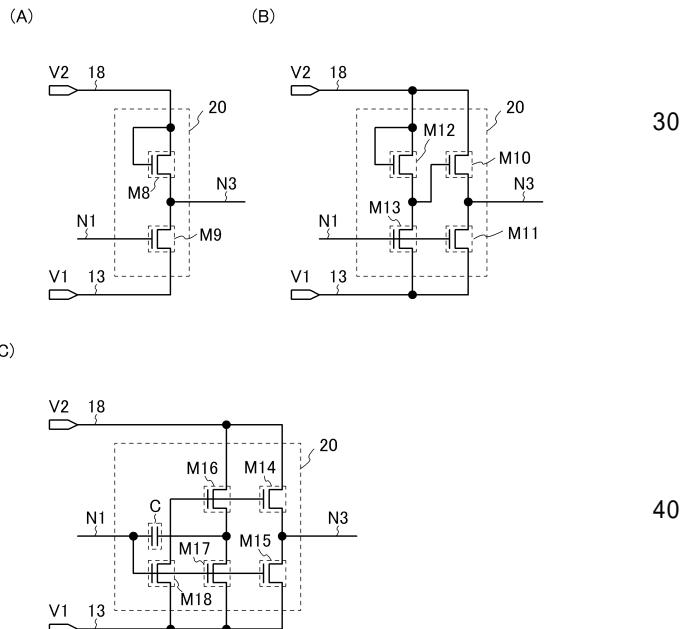

本実施の形態では、本発明の一態様に係る順序回路を適用したシフトレジスタ回路について説明する。

#### 【0095】

図11は、本実施の形態のシフトレジスタ回路を示す。図11のシフトレジスタ回路は、N(Nは3以上の自然数)個の順序回路30を有する。ただし、図11には、順序回路30[1]乃至順序回路30[3]のみを示す。

#### 【0096】

図11のシフトレジスタ回路は、順序回路30として図1(B)の順序回路が適用される。順序回路30[i](iは2以上N-1以下)において、配線15には信号SOUT[i-1]が入力され、配線16aには信号SELaが入力され、配線16bには信号SELbが入力され、配線14には信号SOUT[i+1]が入力され、配線13には電位V1が入力され、配線12からは信号SOUT[i]が出力される。また、奇数段の順序回路30において、配線11には信号SCK1が入力され、偶数段の順序回路30において、配線11には信号SCK2が入力される。また、順序回路30[1]は、順序回路30[i]と比較して、配線11に信号SSPが入力されるところが異なる。また、順序回路30[N]は、順序回路30[i]と比較して、配線14にリセット信号又は信号SSPが入力されるところが異なる。

#### 【0097】

信号SCK1は信号CK1と同様の信号であり、信号SCK2は信号CK2と同様の信号である。また、信号SSPはシフトレジスタ回路のスタートパルスであり、信号SPと同様の信号である。また、信号SOUTは信号OUTと同様の信号である。

#### 【0098】

なお、回路10として、図9(A)のように配線17と接続された構成を適用する場合、奇数段の順序回路30において、配線17に信号SCK2を入力し、偶数段の順序回路30において、配線17に信号SCK1を入力すればよい。

#### 【0099】

なお、回路10として、図9(B)のように配線18が接続された構成を適用する場合、各段の順序回路30において、配線18に電位V2を供給すればよい。

#### 【0100】

本実施の形態は、他の実施の形態等に記載した構成と適宜組み合わせて実施することができる。

#### 【0101】

##### (実施の形態4)

10

20

30

40

50

本実施の形態では、表示素子として液晶素子を用いたパネルの構成を一例として示す。

#### 【0102】

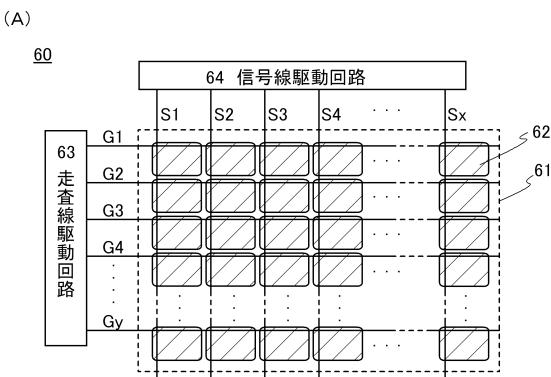

図12(A)に示すパネル60は、画素部61と、走査線駆動回路63と、信号線駆動回路64と、を有する。また、画素部61は、複数の画素62と、画素62を行毎に選択するための複数の走査線Gと、選択された画素62に画像信号を供給するための複数の信号線Sとを有する。各画素62は、走査線Gの少なくとも一つと、信号線Sの少なくとも一つとに、それぞれ接続されている。また、走査線駆動回路63は、走査線Gへ信号を出力する。信号線駆動回路64は、信号線Sへ画像信号を出力する。

#### 【0103】

走査線駆動回路63は、シフトレジスタ回路を有する。シフトレジスタ回路の出力信号は、走査線Gに順次入力される。この走査線駆動回路63のシフトレジスタ回路に、本発明の一態様に係る順序回路を適用することができる。

10

#### 【0104】

なお、画素部61に設けられる配線の種類及びその数は、画素62の構成、数及び配置によって決めることができる。具体的に、図12(A)に示す画素部61の場合、 $x$ 列 $\times$  $y$ 行の画素62がマトリクス状に配置されており、信号線S1乃至信号線Sx、走査線G1乃至走査線Gyが、画素部61内に配置されている場合を例示している。

#### 【0105】

図12(B)は、画素62の構成の一例を示す。画素62は、液晶素子65と、トランジスタ66と、容量素子67と、を有する。液晶素子65は、第1電極(画素電極ともいう)と、第2電極(対向電極ともいう)と、第1電極と第2電極の間の電圧が印加される液晶材料を含んだ液晶層とを有する。トランジスタ66は、ソース又はドレインの一方が信号線S1乃至信号線Sxのいずれか一つと接続され、ソース又はドレインの他方が液晶素子65の第1の電極と接続され、ゲートが走査線G1乃至Gyのいずれか一つと接続される。トランジスタ66は、信号線Sと液晶素子65の第1の電極との導通又は非導通を制御する機能を有する。容量素子67は、第1の電極が液晶素子65の第1の電極と接続され、第2の電極が図示しない容量線と接続される。容量素子67は、液晶素子65の第1の電極と容量線との電位差を保持する機能を有する。

20

#### 【0106】

なお、各画素62において、液晶素子65の第2の電極を共通にしてもよい。また、各画素62において、容量素子67の第2の電極を同一の容量配線と接続してもよい。また、容量線には、液晶素子65の第2の電極と同じコモン電位を供給してもよい。

30

#### 【0107】

なお、画素62は、トランジスタ、ダイオード、抵抗素子、容量素子、インダクタなどのその他の素子を、さらに有していても良い。

#### 【0108】

なお、本発明の一態様では、画素62において、液晶素子65及び容量素子67に蓄積された電荷を保持するためのスイッチとして、オフ電流の小さいトランジスタを用いることが望ましい。具体的に、図12(B)に示す画素62の場合、トランジスタ66のオフ電流が小さいと、トランジスタ66を介して電荷がリークするのを防ぐことができる。よって、液晶素子65及び容量素子67に与えられた画像信号に応じた電位をより確実に保持することができるので、1フレーム期間内において電荷のリークにより液晶素子65の透過率が変化するのを防ぎ、それにより、表示する画像の質を向上させることができる。また、トランジスタ66のオフ電流が小さい場合、トランジスタ66を介して電荷がリークするのを防ぐことができるため、容量素子67の面積を小さく抑えることができる。よって、パネル60の透過率を高め、それにより、バックライトやフロントライトなどの光供給部から供給される光の、パネル60の内部における損失を低減し、液晶表示装置の消費電力を低減させることができる。

40

#### 【0109】

なお、本実施の形態では、表示素子として液晶素子を用いたパネルについて説明したが、

50

表示素子として発光素子を用いてもよい。発光素子は、LED (Light Emitting Diode) やOLED (Organic Light Emitting Diode) などの、電流または電圧によって輝度が制御される素子をその範疇に含んでいる。例えば、OLEDは、EL層と、アノードと、カソードとを少なくとも有している。EL層はアノードとカソードの間に設けられた単層または複数の層で構成されており、これらの層の中に、発光性の物質を含む発光層を少なくとも含んでいる。EL層は、カソードとアノード間の電位差が、発光素子の閾値電圧  $V_{th}$  以上になったときに供給される電流により、エレクトロルミネッセンスが得られる。エレクトロルミネッセンスには、一重項励起状態から基底状態に戻る際の発光（蛍光）と三重項励起状態から基底状態に戻る際の発光（リン光）とが含まれる。

10

#### 【0110】

走査線駆動回路63に本発明の一態様に係る順序回路を適用することにより、走査線Gの信号の立ち下がり時間を短くすることができる。よって、別の行に対応する画像信号が画素62に入力されることを防止することができるため、より正確な画像信号を保持することができ、表示品位の向上を図ることができる。

#### 【0111】

なお、走査線駆動回路63に本発明の一態様に係る順序回路を適用する場合、画素62が有するトランジスタ66はトランジスタM1と同じ極性であることが好ましい。また、走査線駆動回路63と同じ基板に設けられるトランジスタはトランジスタM1と同じ極性であることが好ましい。

20

#### 【0112】

本実施の形態は、他の実施の形態等に記載した構成と適宜組み合わせて実施することができる。

#### 【0113】

##### （実施の形態5）

本発明の一態様に係る半導体装置では、非晶質、微結晶、多結晶又は単結晶である、シリコン又はゲルマニウムなどの半導体膜にチャネル形成領域を有するトランジスタが用いられていても良いし、シリコンよりもバンドギャップが広く、真性キャリア密度がシリコンよりも低い半導体膜にチャネル形成領域を有するトランジスタが用いられていても良い。

30

#### 【0114】

シリコンとしては、プラズマCVD法などの気相成長法若しくはスパッタリング法で作製された非晶質シリコン、非晶質シリコンをレーザーアニールなどの処理により結晶化させた多結晶シリコン、単結晶シリコンウェハに水素イオン等を注入して表層部を剥離した単結晶シリコンなどを用いることができる。

#### 【0115】

電子供与体（ドナー）となる水分または水素などの不純物が低減され、なおかつ酸素欠損が低減されることにより高純度化された酸化物半導体（purified OS）は、i型（真性半導体）又はi型に限りなく近い。そのため、高純度化された酸化物半導体膜にチャネル形成領域を有するトランジスタは、オフ電流が著しく小さく、信頼性が高い。

40

#### 【0116】

具体的に、高純度化された酸化物半導体膜にチャネル形成領域を有するトランジスタのオフ電流が小さいことは、いろいろな実験により証明できる。例えば、チャネル幅が $1 \times 10^6 \mu m$ でチャネル長が $10 \mu m$ の素子であっても、ソース電極とドレイン電極間の電圧（ドレイン電圧）が $1V$ から $10V$ の範囲において、オフ電流が、半導体パラメータアナライザの測定限界以下、すなわち $1 \times 10^{-13} A$ 以下という特性を得ることができる。この場合、オフ電流をトランジスタのチャネル幅で規格化したオフ電流は、 $100 zA / \mu m$ 以下であることが分かる。また、容量素子とトランジスタとを接続して、容量素子に流入または容量素子から流出する電荷を当該トランジスタで制御する回路を用いて、オフ電流の測定を行った。当該測定では、上記トランジスタに高純度化された酸化物半導体膜をチャネル形成領域に用い、容量素子の単位時間あたりの電荷量の推移から当該トランジ

50

スタのオフ電流を測定した。その結果、トランジスタのソース電極とドレイン電極間の電圧が3Vの場合に、数十 $\mu$ A /  $\mu$ mという、さらに小さいオフ電流が得られることが分かった。従って、高純度化された酸化物半導体膜をチャネル形成領域に用いたトランジスタは、オフ電流が、結晶性を有するシリコンを用いたトランジスタに比べて著しく小さい。

#### 【0117】

なお、特に断りがない限り、本明細書でオフ電流とは、nチャネル型トランジスタにおいては、ドレインをソースとゲートよりも高い電位とした状態において、ソースの電位を基準としたときのゲートの電位が0以下であるときに、ソースとドレインの間に流れる電流のことを意味する。或いは、本明細書でオフ電流とは、pチャネル型トランジスタにおいては、ドレインをソースとゲートよりも低い電位とした状態において、ソースの電位を基準としたときのゲートの電位が0以上であるときに、ソースとドレインの間に流れる電流のことを意味する。

10

#### 【0118】

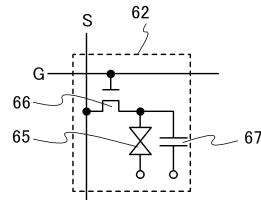

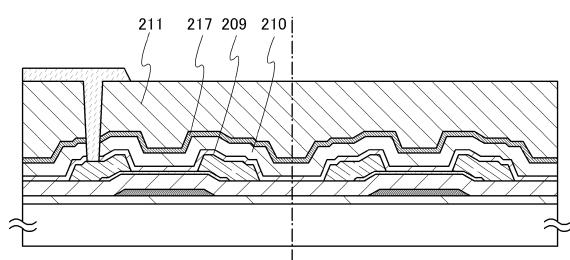

次いで、酸化物半導体膜にチャネル形成領域を有するトランジスタの一例について、図面を参照して説明する。

#### 【0119】

図13(A)に、画素に設けられたトランジスタ201と、駆動回路に設けられたトランジスタ202の断面構造を、一例として示す。

#### 【0120】

図13(A)に示すトランジスタ201は、絶縁表面上に設けられた、ゲートとして機能する導電膜204と、導電膜204上の絶縁膜205と、絶縁膜205上において導電膜204と重なる位置に設けられた半導体膜206と、半導体膜206上においてソースまたはドレインとして機能する導電膜207及び導電膜208と、を有する。また、図13(A)では、半導体膜206、導電膜207及び導電膜208上に、絶縁膜209及び絶縁膜210が、順に積層するように設けられている。トランジスタ201は、絶縁膜209及び絶縁膜210をその構成要素に含んでいても良い。また、絶縁膜209及び絶縁膜210上には、絶縁膜211が設けられている。そして、絶縁膜209、絶縁膜210、及び絶縁膜211には開口部が設けられており、絶縁膜211上には、当該開口部において導電膜207に接続された導電膜203が設けられている。

20

#### 【0121】

なお、導電膜203は、表示素子の第1電極として機能する。例えば、液晶素子は第1電極及び第2電極と、第1電極及び第2電極により電界が加えられる液晶層とを有する。よって、液晶素子をトランジスタ201上に形成する場合、導電膜203に加え、第2電極として機能する導電膜と、液晶層とを、絶縁膜211上に設ければよい。また、表示素子がOLEDである場合、アノードまたはカソードの一方として機能する導電膜203に加え、アノードまたはカソードの他方として機能する導電膜と、EL層とを、絶縁膜211上に設ければよい。

30

#### 【0122】

なお、絶縁膜211に樹脂を用いることで、導電膜203の被形成表面に凹凸が生じることを防ぐことができる。すなわち、導電膜203の被形成表面の平坦性を高めることができる。具体的に、絶縁膜211として、アクリル樹脂、エポキシ樹脂、ベンゾシクロブテン系樹脂、ポリイミド、ポリアミド等の有機材料を用いることができる。また上記有機材料の他に、シリコーン樹脂等を用いることができる。なお、これらの材料で形成される絶縁膜を複数積層することで、より平坦性の高い絶縁膜211を形成することができる。

40

#### 【0123】

なお、導電膜203として、酸化インジウム、酸化インジウム-酸化スズ(ITO: Indium Tin Oxide)、珪素若しくは酸化珪素を含有した酸化インジウム-酸化スズ、酸化インジウム-酸化亜鉛(Indium Zinc Oxide)、酸化タンゲステン及び酸化亜鉛を含有した酸化インジウム、窒素を含ませたAl-Zn系酸化物半導体、窒素を含ませたZn系酸化物半導体、窒素を含ませたSn-Zn系酸化物半導体、

50

金( A u )、白金( P t )、ニッケル( N i )、タングステン( W )、クロム( C r )、モリブデン( M o )、鉄( F e )、コバルト( C o )、銅( C u )、パラジウム( P d )、チタン( T i )の他、元素周期表の第1族または第2族に属する元素、すなわちリチウム( L i )やセシウム( C s )等のアルカリ金属、およびマグネシウム( M g )、カルシウム( C a )、ストロンチウム( S r )等のアルカリ土類金属、およびこれらを含む合金( M g A g 、 A l L i )、ユウロピウム( E u )、イッテルビウム( Y b )等の希土類金属およびこれらを含む合金などを用いることができる。なお、導電膜 2 0 3 は、例えばスパッタリング法や蒸着法等により上記材料を用いて導電膜を形成した後、フォトリソグラフィ法を用いたエッチングにより当該導電膜を所望の形状に加工することで、形成することができる。

10

#### 【 0 1 2 4 】

図 1 3 ( A ) に示すトランジスタ 2 0 2 は、絶縁表面上に設けられた、ゲートとして機能する導電膜 2 1 2 と、導電膜 2 1 2 上の絶縁膜 2 0 5 と、絶縁膜 2 0 5 上において導電膜 2 1 2 と重なる位置に設けられた半導体膜 2 1 3 と、半導体膜 2 1 3 上においてソースまたはドレインとして機能する導電膜 2 1 4 及び導電膜 2 1 5 と、を有する。また、図 1 3 ( A ) では、半導体膜 2 1 3 、導電膜 2 1 4 及び導電膜 2 1 5 上に、絶縁膜 2 0 9 及び絶縁膜 2 1 0 が順に積層するように設けられている。また、絶縁膜 2 0 9 及び絶縁膜 2 1 0 上には、樹脂を用いた絶縁膜 2 1 1 が設けられている。

20

#### 【 0 1 2 5 】

なお、図 1 3 ( A ) では、駆動回路が有するトランジスタ 2 0 2 のバックゲートとして機能する導電膜を、画素において液晶素子の電極として機能する導電膜 2 0 3 と共に、絶縁膜 2 1 1 上に形成しても良い。上記構成により、一の導電膜をエッチング等により所望の形状に加工することにより、導電膜 2 0 3 と、バックゲートとして機能する導電膜とを形成することができる。よって、半導体装置の作製工程を増やすことなく、バックゲートとして機能する導電膜を設けることができる。バックゲートはフローティングの状態であっても良いし、電位が他から与えられる状態であっても良い。後者の場合、通常のゲート( フロントゲート ) 及びバックゲートに同じ高さの電位が与えられても良いし、バックゲートにのみ接地電位などの固定の電位が与えられていても良い。バックゲートに与える電位を制御することで、トランジスタ 2 0 2 の閾値電圧を制御することができる。また、バックゲートを設けることで、チャネル形成領域が増え、ドレイン電流の増加を実現することができる。また、バックゲートを設けることで、半導体膜に空乏層ができやすくなるため、S 値の改善を図ることができる。

30

#### 【 0 1 2 6 】

なお、図 1 3 ( A ) では、半導体膜 2 0 6 及び半導体膜 2 1 3 と絶縁膜 2 1 1 の間に、絶縁膜 2 0 9 及び絶縁膜 2 1 0 が設けられている場合を例示しているが、半導体膜 2 0 6 及び半導体膜 2 1 3 と絶縁膜 2 1 1 の間に設けられる絶縁膜は、一層であっても良いし、3 以上の複数層であっても良い。

#### 【 0 1 2 7 】

なお、絶縁膜 2 1 0 は、化学量論的組成以上の酸素が含まれており、加熱により上記酸素の一部を半導体膜 2 0 6 に供給する機能を有する絶縁膜であることが望ましい。また、絶縁膜 2 1 0 は、欠陥が少ないことが好ましく、代表的には、E S R 測定により、シリコンのダングリングボンドに由来する  $g = 2.001$  に現れる信号のスピノ密度が  $1 \times 10^{18} \text{ spins/cm}^3$  以下であることが好ましい。ただし、絶縁膜 2 1 0 を半導体膜 2 0 6 及び半導体膜 2 1 3 上に直接設けると、絶縁膜 2 1 0 の形成時に半導体膜 2 0 6 にダメージが与えられる場合、図 1 3 ( A ) に示すように、絶縁膜 2 0 9 を半導体膜 2 0 6 及び半導体膜 2 1 3 と絶縁膜 2 1 0 の間に設けると良い。絶縁膜 2 0 9 は、その形成時に半導体膜 2 0 6 に与えるダメージが絶縁膜 2 1 0 の場合よりも小さく、なおかつ、酸素を透過する機能を有する絶縁膜であることが望ましい。ただし、半導体膜 2 0 6 及び半導体膜 2 1 3 に与えられるダメージを小さく抑えつつ、半導体膜 2 0 6 及び半導体膜 2 1 3 上に直接絶縁膜 2 1 0 を形成することができるのであれば、絶縁膜 2 0 9 は必ずしも設けなくと

40

50

も良い。

#### 【0128】

なお、絶縁膜209は、欠陥が少ないことが好ましく、代表的には、E S R測定により、シリコンのダングリングボンドに由来する $g = 2.001$ に現れる信号のスピンドル密度が $3 \times 10^{17} \text{ spins/cm}^3$ 以下であることが好ましい。これは、絶縁膜209に含まれる欠陥密度が多いと、当該欠陥に酸素が結合してしまい、絶縁膜209における酸素の透過量が減少してしまうためである。

#### 【0129】

なお、絶縁膜209と半導体膜206及び半導体膜213との界面に欠陥が少ないことが好ましく、代表的には、磁場の向きを膜面に対して平行に印加したE S R測定により、半導体膜206及び半導体膜213に用いられる酸化物半導体中の酸素欠損に由来する $g = 1.93$ に現れる信号のスピンドル密度が $1 \times 10^{17} \text{ spins/cm}^3$ 以下、更には検出下限以下であることが好ましい。

10

#### 【0130】

具体的に、絶縁膜209または絶縁膜210として、酸化シリコン膜または酸化窒化シリコン膜を用いることができる。

#### 【0131】

次いで、図13(B)に、図13(A)に示した断面構造に、さらに絶縁膜210と絶縁膜211の間に絶縁膜217を設けた場合の、トランジスタ201と、トランジスタ201に接続された導電膜203と、トランジスタ202の断面構造を、一例として示す。絶縁膜217は、酸素、水素、水の拡散を防ぐブロッキング効果を有することが、望ましい。或いは、絶縁膜217は、水素、水の拡散を防ぐブロッキング効果を有することが、望ましい。

20

#### 【0132】

絶縁膜は、密度が高くて緻密である程、また未結合手が少なく化学的に安定である程、より高いブロッキング効果を示す。酸素、水素、水のブロッキング効果を示す絶縁膜は、例えば、酸化アルミニウム、酸化窒化アルミニウム、酸化ガリウム、酸化窒化ガリウム、酸化イットリウム、酸化窒化イットリウム、酸化ハフニウム、酸化窒化ハフニウム等を用いて、形成することができる。水素、水のブロッキング効果を示す絶縁膜は、例えば、窒化シリコン、窒化酸化シリコン等を用いることができる。

30

#### 【0133】

絶縁膜217が水、水素などのブロッキング効果を有する場合、樹脂を用いた絶縁膜211や、パネルの外部に存在する水、水素などの不純物が、半導体膜206または半導体膜213に侵入するのを防ぐことができる。半導体膜206または半導体膜213に酸化物半導体を用いる場合、酸化物半導体に侵入した水または水素の一部は電子供与体(ドナー)となるため、上記ブロッキング効果を有する絶縁膜217を用いることで、トランジスタ201及びトランジスタ202の閾値電圧がドナーの生成によりシフトするのを防ぐことができる。

#### 【0134】

半導体膜206または半導体膜213に酸化物半導体を用いる場合、絶縁膜217が酸素のブロッキング効果を有することで、酸化物半導体からの酸素が外部に拡散するのを防ぐことができる。よって、酸化物半導体中において、ドナーとなる酸素欠損が低減されるので、トランジスタ201及びトランジスタ202の閾値電圧がドナーの生成によりシフトするのを防ぐことができる。

40

#### 【0135】

絶縁膜217と絶縁膜211の密着性が、絶縁膜210と絶縁膜211の密着性よりも高い場合、絶縁膜217を用いることで、絶縁膜211の剥離を防ぐことができる。

#### 【0136】

なお、半導体膜206及び半導体膜213として酸化物半導体膜を用いる場合、酸化物半導体としては、少なくともインジウム(I n)あるいは亜鉛(Z n)を含むことが好まし

50

い。また、該酸化物半導体を用いたトランジスタの電気的特性のばらつきを減らすためのスタビライザーとして、それらに加えてガリウム( Ga )を有することが好ましい。また、スタビライザーとしてスズ( Sn )を有することが好ましい。また、スタビライザーとしてハフニウム( Hf )を有することが好ましい。また、スタビライザーとしてアルミニウム( Al )を有することが好ましい。また、スタビライザーとしてジルコニウム( Zr )を含むことが好ましい。

#### 【 0 1 3 7 】

酸化物半導体の中でも In - Ga - Zn 系酸化物、In - Sn - Zn 系酸化物などは、炭化シリコン、窒化ガリウム、または酸化ガリウムとは異なり、スペッタリング法や湿式法により電気的特性の優れたトランジスタを作製することが可能であり、量産性に優れるといった利点がある。また、炭化シリコン、窒化ガリウム、または酸化ガリウムとは異なり、上記 In - Ga - Zn 系酸化物は、ガラス基板上に、電気的特性の優れたトランジスタを作製することが可能である。また、基板の大型化にも対応が可能である。

10

#### 【 0 1 3 8 】

また、他のスタビライザーとして、ランタノイドである、ランタン( La )、セリウム( Ce )、プラセオジム( Pr )、ネオジム( Nd )、サマリウム( Sm )、ユウロピウム( Eu )、ガドリニウム( Gd )、テルビウム( Tb )、ジスプロシウム( Dy )、ホルミウム( Ho )、エルビウム( Er )、ツリウム( Tm )、イッテルビウム( Yb )、ルテチウム( Lu )のいずれか一種または複数種を含んでいてもよい。

20

#### 【 0 1 3 9 】

例えば、酸化物半導体として、酸化インジウム、酸化ガリウム、酸化スズ、酸化亜鉛、In - Zn 系酸化物、Sn - Zn 系酸化物、Al - Zn 系酸化物、Zn - Mg 系酸化物、Sn - Mg 系酸化物、In - Mg 系酸化物、In - Ga 系酸化物、In - Ga - Zn 系酸化物( IGZO とも表記する)、In - Al - Zn 系酸化物、In - Sn - Zn 系酸化物、Sn - Ga - Zn 系酸化物、Al - Ga - Zn 系酸化物、Sn - Al - Zn 系酸化物、In - Hf - Zn 系酸化物、In - La - Zn 系酸化物、In - Pr - Zn 系酸化物、In - Nd - Zn 系酸化物、In - Sm - Zn 系酸化物、In - Eu - Zn 系酸化物、In - Gd - Zn 系酸化物、In - Tb - Zn 系酸化物、In - Dy - Zn 系酸化物、In - Ho - Zn 系酸化物、In - Er - Zn 系酸化物、In - Tm - Zn 系酸化物、In - Yb - Zn 系酸化物、In - Lu - Zn 系酸化物、In - Sn - Ga - Zn 系酸化物、In - Hf - Ga - Zn 系酸化物、In - Al - Ga - Zn 系酸化物、In - Sn - Al - Zn 系酸化物、In - Sn - Hf - Zn 系酸化物、In - Hf - Al - Zn 系酸化物を用いることができる。

30

#### 【 0 1 4 0 】

なお、例えば、In - Ga - Zn 系酸化物とは、In と Ga と Zn を含む酸化物という意味であり、In と Ga と Zn の比率は問わない。また、In と Ga と Zn 以外の金属元素を含んでいてもよい。In - Ga - Zn 系酸化物は、無電界時の抵抗が十分に高くオフ電流を十分に小さくすることが可能であり、また、移動度も高い。

#### 【 0 1 4 1 】

例えば、 $In : Ga : Zn = 1 : 1 : 1 (= 1 / 3 : 1 / 3 : 1 / 3)$  あるいは  $In : Ga : Zn = 2 : 2 : 1 (= 2 / 5 : 2 / 5 : 1 / 5)$  の原子比の In - Ga - Zn 系酸化物やその組成の近傍の酸化物を用いることができる。あるいは、 $In : Sn : Zn = 1 : 1 : 1 (= 1 / 3 : 1 / 3 : 1 / 3)$ 、 $In : Sn : Zn = 2 : 1 : 3 (= 1 / 3 : 1 / 6 : 1 / 2)$  あるいは  $In : Sn : Zn = 2 : 1 : 5 (= 1 / 4 : 1 / 8 : 5 / 8)$  の原子比の In - Sn - Zn 系酸化物やその組成の近傍の酸化物を用いるとよい。

40

#### 【 0 1 4 2 】

例えば、In - Sn - Zn 系酸化物では比較的容易に高い移動度が得られる。しかしながら、In - Ga - Zn 系酸化物でも、バルク内欠陥密度を低減することにより移動度を上げることができる。

#### 【 0 1 4 3 】

50

なお、本発明の一態様では、単結晶、多結晶（ポリクリスタルともいう。）または非晶質などの状態を有する酸化物半導体膜を、トランジスタに用いることができる。好ましくは、酸化物半導体膜は、CAAC-O<sub>S</sub>（C Axis Aligned Crystal line Oxide Semiconductor）膜とする。

#### 【0144】

CAAC-O<sub>S</sub>膜は、完全な単結晶ではなく、完全な非晶質でもない。なお、CAAC-O<sub>S</sub>膜に含まれる結晶部は、一辺が100nm未満の立方体内に収まる大きさであることが多い。また、透過型電子顕微鏡（TEM：Transmission Electron Microscope）による観察像では、CAAC-O<sub>S</sub>膜に含まれる非晶質部と結晶部との境界は明確ではない。また、TEMによってCAAC-O<sub>S</sub>膜には粒界（グレインバウンダリーともいう。）は確認できない。そのため、CAAC-O<sub>S</sub>膜は、粒界に起因する電子移動度の低下が抑制される。

10

#### 【0145】

CAAC-O<sub>S</sub>膜に含まれる結晶部は、c軸がCAAC-O<sub>S</sub>膜の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向に揃い、かつa b面に垂直な方向から見て三角形状または六角形状の原子配列を有し、c軸に垂直な方向から見て金属原子が層状または金属原子と酸素原子とが層状に配列している。なお、異なる結晶部間で、それぞれa軸およびb軸の向きが異なっていてもよい。本明細書において、単に垂直と記載する場合、85°以上95°以下の範囲も含まれることとする。また、単に平行と記載する場合、-5°以上5°以下の範囲も含まれることとする。

20

#### 【0146】

なお、CAAC-O<sub>S</sub>膜において、結晶部の分布が一様でなくてもよい。例えば、CAAC-O<sub>S</sub>膜の形成過程において、酸化物半導体膜の表面側から結晶成長させる場合、被形成面の近傍に対し表面の近傍では結晶部の占める割合が高くなることがある。また、CAAC-O<sub>S</sub>膜へ不純物を添加することにより、当該不純物添加領域において結晶部が非晶質化することもある。

#### 【0147】

CAAC-O<sub>S</sub>膜に含まれる結晶部のc軸は、CAAC-O<sub>S</sub>膜の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向に揃うため、CAAC-O<sub>S</sub>膜の形状（被形成面の断面形状または表面の断面形状）によっては互いに異なる方向を向くことがある。なお、結晶部のc軸の方向は、CAAC-O<sub>S</sub>膜が形成されたときの被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向となる。結晶部は、成膜することにより、または成膜後に加熱処理などの結晶化処理を行うことにより形成される。

30

#### 【0148】

CAAC-O<sub>S</sub>膜を用いたトランジスタは、可視光や紫外光の照射による電気的特性の変動を低減することが可能である。よって、当該トランジスタは、信頼性が高い。

#### 【0149】

CAAC-O<sub>S</sub>膜は、例えば、多結晶である酸化物半導体スパッタリング用ターゲットを用い、スパッタリング法によって成膜する。当該スパッタリング用ターゲットにイオンが衝突すると、スパッタリング用ターゲットに含まれる結晶領域がa - b面から劈開し、a - b面に平行な面を有する平板状またはペレット状のスパッタリング粒子として剥離することがある。この場合、当該平板状のスパッタリング粒子が、結晶状態を維持したまま基板に到達することで、CAAC-O<sub>S</sub>膜を成膜することができる。

40

#### 【0150】

また、CAAC-O<sub>S</sub>膜を成膜するために、以下の条件を適用することが好ましい。

#### 【0151】

成膜時の不純物混入を低減することで、不純物によって結晶状態が崩れることを抑制できる。例えば、成膜室内に存在する不純物濃度（水素、水、二酸化炭素および窒素など）を低減すればよい。また、成膜ガス中の不純物濃度を低減すればよい。具体的には、露点が-80以下、好ましくは-100以下である成膜ガスを用いる。

50

**【 0 1 5 2 】**

また、成膜時の基板加熱温度を高めることで、基板到達後にスパッタリング粒子のマイグレーションが起こる。具体的には、基板加熱温度を 100 以上 740 以下、好ましくは 200 以上 500 以下として成膜する。成膜時の基板加熱温度を高めることで、平板状のスパッタリング粒子が基板に到達した場合、基板上でマイグレーションが起り、スパッタリング粒子の平らな面が基板に付着する。

**【 0 1 5 3 】**

また、成膜ガス中の酸素割合を高め、電力を最適化することで成膜時のプラズマダメージを軽減すると好ましい。成膜ガス中の酸素割合は、30 体積%以上、好ましくは 100 体積%とする。

10

**【 0 1 5 4 】**

スパッタリング用ターゲットの一例として、In - Ga - Zn 系酸化物ターゲットについて以下に示す。

**【 0 1 5 5 】**

In<sub>x</sub>O<sub>y</sub> 粉末、Ga<sub>y</sub>O<sub>z</sub> 粉末およびZnO<sub>z</sub> 粉末を所定の mol 数比で混合し、加圧処理後、1000 以上 1500 以下の温度で加熱処理することで多結晶である In - Ga - Zn 系酸化物ターゲットとする。なお、X、Y および Z は任意の正数である。ここで、所定の mol 数比は、例えば、In<sub>x</sub>O<sub>y</sub> 粉末、Ga<sub>y</sub>O<sub>z</sub> 粉末およびZnO<sub>z</sub> 粉末が、2 : 2 : 1、8 : 4 : 3、3 : 1 : 1、1 : 1 : 1、4 : 2 : 3 または 3 : 1 : 2 である。なお、粉末の種類、およびその混合する mol 数比は、作製するスパッタリング用ターゲットによって適宜変更すればよい。

20

**【 0 1 5 6 】**

また、半導体膜 206 及び半導体膜 213 は、金属の原子数比が互いに異なる金属酸化物のターゲットを用いて形成された複数の酸化物半導体膜が、積層された構造を有していても良い。例えば、ターゲットの原子数比は、1 層目の酸化物半導体膜が In : Ga : Zn = 1 : 1 : 1、2 層目の酸化物半導体膜が In : Ga : Zn = 3 : 1 : 2 となるように、形成しても良い。また、ターゲットの原子数比は、1 層目の酸化物半導体膜が In : Ga : Zn = 1 : 3 : 2、2 層目の酸化物半導体膜が In : Ga : Zn = 3 : 1 : 2、3 層目の酸化物半導体膜が In : Ga : Zn = 1 : 1 : 1 となるように、形成しても良い。

**【 0 1 5 7 】**

30

或いは、半導体膜 206 及び半導体膜 213 は、異なる金属を含む金属酸化物のターゲットを用いて形成された複数の酸化物半導体膜が、積層された構造を有していても良い。

**【 0 1 5 8 】**

本実施の形態は、他の実施の形態等に記載した構成と適宜組み合わせて実施することができる。

**【 0 1 5 9 】****( 実施の形態 6 )**

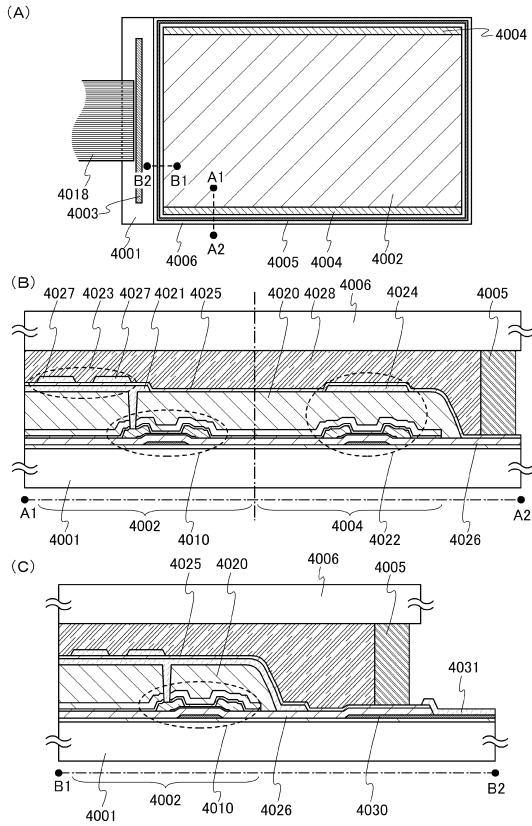

液晶表示装置を例に挙げて、本発明の一態様に係る半導体装置の外観について、図 14 を用いて説明する。図 14 (A) は、基板 4001 と基板 4006 とを封止材 4005 によって接着させた液晶表示装置の上面図である。また、図 14 (B) は、図 14 (A) の破線 A1 - A2 における断面図に相当し、図 14 (C) は、図 14 (A) の破線 B1 - B2 における断面図に相当する。なお、図 14 では、FFS (Fringe Field Switching) モードの液晶表示装置を例示している。

40

**【 0 1 6 0 】**

基板 4001 上に設けられた画素部 4002 と、一対の走査線駆動回路 4004 とを囲むように、封止材 4005 が設けられている。また、画素部 4002、走査線駆動回路 4004 の上に基板 4006 が設けられている。よって、画素部 4002 と、走査線駆動回路 4004 とは、基板 4001 と封止材 4005 と基板 4006 とによって封止されている。また、基板 4001 上の封止材 4005 によって囲まれている領域とは異なる領域に、信号線駆動回路 4003 が実装されている。

50

**【 0 1 6 1 】**

なお、走査線駆動回路 4 0 0 4 に本発明の一態様に係る順序回路を適用することができる。これにより、トランジスタの W / L を小さくすることができるため、額縁を小さくできる。

**【 0 1 6 2 】**

基板 4 0 0 1 上に設けられた画素部 4 0 0 2 、走査線駆動回路 4 0 0 4 は、トランジスタを複数有している。図 14 ( B ) では、画素部 4 0 0 2 に含まれるトランジスタ 4 0 1 0 と、走査線駆動回路 4 0 0 4 に含まれるトランジスタ 4 0 2 2 とを例示している。また、図 14 ( C ) では、画素部 4 0 0 2 に含まれるトランジスタ 4 0 1 0 を例示している。

**【 0 1 6 3 】**

画素部 4 0 0 2 及び走査線駆動回路 4 0 0 4 において、トランジスタ 4 0 1 0 及びトランジスタ 4 0 2 2 上には、樹脂を用いた絶縁膜 4 0 2 0 が設けられている。そして、絶縁膜 4 0 2 0 上には、液晶素子 4 0 2 3 の第 1 電極 4 0 2 1 と、導電膜 4 0 2 4 とが設けられている。導電膜 4 0 2 4 は、絶縁膜 4 0 2 0 に蓄積された電荷の放電経路として機能させることができる。或いは、導電膜 4 0 2 4 及び絶縁膜 4 0 2 0 をトランジスタ 4 0 2 2 の構成要素とし、導電膜 4 0 2 4 をバックゲートとして機能させることもできる。

**【 0 1 6 4 】**

絶縁膜 4 0 2 0 、第 1 電極 4 0 2 1 、及び導電膜 4 0 2 4 上には、絶縁膜 4 0 2 5 が設けられている。絶縁膜 4 0 2 5 は、水、水素などのブロッキング効果が高いことが望ましい。絶縁膜 4 0 2 5 として、窒化シリコン膜、窒化酸化シリコン膜などを用いることができる。

**【 0 1 6 5 】**

図 14 ( B ) 及び図 14 ( C ) に示すように、本発明の一態様では、絶縁膜 4 0 2 0 は、パネルの端部において除去されている。そして、絶縁膜 4 0 2 0 上の絶縁膜 4 0 2 5 は、封止材 4 0 0 5 と基板 4 0 0 1 の間において、トランジスタ 4 0 1 0 及びトランジスタ 4 0 2 2 のゲート絶縁膜として機能する絶縁膜 4 0 2 6 と接している。

**【 0 1 6 6 】**

絶縁膜 4 0 2 5 及び絶縁膜 4 0 2 6 の、水、水素などのブロッキング効果が高い場合、パネルの端部において絶縁膜 4 0 2 5 と絶縁膜 4 0 2 6 とが接することで、パネルの外部から、または封止材 4 0 0 5 から、水、水素などがトランジスタ 4 0 1 0 及びトランジスタ 4 0 2 2 がそれぞれ有する半導体膜に侵入するのを、防ぐことができる。

**【 0 1 6 7 】**

絶縁膜 4 0 2 5 上には、液晶素子 4 0 2 3 の第 2 電極 4 0 2 7 が設けられている。そして、第 2 電極 4 0 2 7 及び絶縁膜 4 0 2 5 と、基板 4 0 0 6 との間には、液晶層 4 0 2 8 が設けられている。液晶素子 4 0 2 3 は、第 1 電極 4 0 2 1 、第 2 電極 4 0 2 7 、及び液晶層 4 0 2 8 を有する。

**【 0 1 6 8 】**

液晶素子 4 0 2 3 では、第 1 電極 4 0 2 1 と第 2 電極 4 0 2 7 の間に与えられる電圧の値に従って、液晶層 4 0 2 8 に含まれる液晶分子の配向が変化し、透過率が変化する。よって、液晶素子 4 0 2 3 は、第 1 電極 4 0 2 1 に与えられる画像信号の電位によって、その透過率が制御されることで、階調を表示することができる。

**【 0 1 6 9 】**

なお、本発明の一態様では、液晶表示装置の液晶層に、例えば、サーモトロピック液晶またはリオトロピック液晶に分類される液晶材料を用いることができる。或いは、液晶層には、例えば、ネマチック液晶、スマクチック液晶、コレステリック液晶、または、ディスコチック液晶に分類される液晶材料を用いることができる。或いは、液晶層には、例えば、強誘電性液晶、または反強誘電性液晶に分類される液晶材料を用いることができる。或いは、液晶層には、例えば、主鎖型高分子液晶、側鎖型高分子液晶、或いは、複合型高分子液晶などの高分子液晶、または低分子液晶に分類される液晶材料を用いることができる。或いは、液晶層には、例えば、高分子分散型液晶 ( P D L C ) に分類される液晶材料を

10

20

30

40

50

用いることができる。

【0170】

なお、配向膜を用いないブルー相を示す液晶を液晶層に用いてもよい。ブルー相は液晶相の一つであり、コレステリック液晶を昇温していくと、コレステリック相から等方相へ転移する直前に発現する相である。ブルー相は狭い温度範囲でしか発現しないため、カイラル剤や紫外線硬化樹脂を添加して温度範囲を改善する。ブルー相を示す液晶とカイラル剤とを含む液晶組成物は、応答速度が1msec以下と短く、光学的等方性であるため配向処理が不要であり、視野角依存性が小さいため好ましい。

【0171】

なお、本発明の一態様では、液晶表示装置において、カラーフィルタを用いることでカラーの画像を表示しても良いし、異なる色相の光を発する複数の光源を順次点灯させることで、カラーの画像を表示しても良い。

10

【0172】

なお、信号線駆動回路4003からの画像信号や、FPC4018からの各種制御信号及び電源電位は、引き回し配線4030及び4031を介して、走査線駆動回路4004または画素部4002に与えられる。

【0173】

なお、本実施の形態では、液晶の駆動方法としてFFS(Fringe Field S switching)モードを用いる場合を例示したが、液晶の駆動方法としては、TN(Twisted Nematic)モード、STN(Super Twisted Nematic)モード、VA(Vertical Alignment)モード、MVA(Multi-domain Vertical Alignment)モード、IPS(In-Plane Switching)モード、OCB(Optically Compensated Birefringence)モード、ブルー相モード、TBA(Transverse Bend Alignment)モード、VA-IPSモード、ECB(Electrically Controlled Birefringence)モード、FLC(Ferroelectric Liquid Crystal)モード、AFLC(AntiFerroelectric Liquid Crystal)モード、PDLC(Polymer Dispersed Liquid Crystal)モード、PNLC(Polymer Network Liquid Crystal)モード、ゲストホストモード、ASV(Advanced Super View)モードなどを適用することも可能である。

20

30

【0174】

本実施の形態は、他の実施の形態等に記載した構成と適宜組み合わせて実施することができる。

【0175】

(実施の形態7)

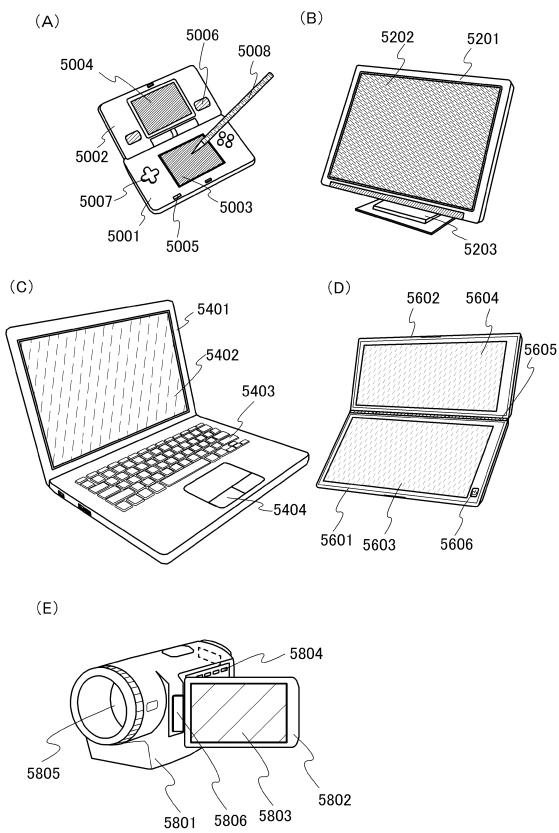

本発明の一態様に係る半導体装置は、表示機器、パーソナルコンピュータ、記録媒体を備えた画像再生装置(代表的にはDVD:Digital Versatile Disc等の記録媒体を再生し、その画像を表示しうるディスプレイを有する装置)に用いることができる。その他に、本発明の一態様に係る半導体装置を用いることができる電子機器として、携帯電話、携帯型を含むゲーム機、携帯情報端末、電子書籍、ビデオカメラ、デジタルスチルカメラ、ゴーグル型ディスプレイ(ヘッドマウントディスプレイ)、ナビゲーションシステム、音響再生装置(カーオーディオ、デジタルオーディオプレイヤー等)、複写機、ファクシミリ、プリンター、プリンター複合機、現金自動預け入れ払い機(ATM)、自動販売機などが挙げられる。これら電子機器の具体例を図15に示す。

40

【0176】

図15(A)は携帯型ゲーム機であり、筐体5001、筐体5002、表示部5003、表示部5004、マイクロホン5005、スピーカー5006、操作キー5007、スタイルス5008等を有する。表示部5003または表示部5004に、或いはその他の回

50

路に、本発明の一態様に係る半導体装置を用いることができる。なお、図15(A)に示した携帯型ゲーム機は、2つの表示部5003と表示部5004とを有しているが、携帯型ゲーム機が有する表示部の数は、これに限定されない。

#### 【0177】

図15(B)は表示機器であり、筐体5201、表示部5202、支持台5203等を有する。表示部5202に、或いはその他の回路に、本発明の一態様に係る半導体装置を用いることができる。なお、表示機器には、パーソナルコンピュータ用、TV放送受信用、広告表示用などの全ての情報表示用表示機器が含まれる。

#### 【0178】

図15(C)はノート型パーソナルコンピュータであり、筐体5401、表示部5402、キーボード5403、ポインティングデバイス5404等を有する。表示部5402に、或いはその他の回路に、本発明の一態様に係る半導体装置を用いることができる。

#### 【0179】

図15(D)は携帯情報端末であり、第1筐体5601、第2筐体5602、第1表示部5603、第2表示部5604、接続部5605、操作キー5606等を有する。第1表示部5603は第1筐体5601に設けられており、第2表示部5604は第2筐体5602に設けられている。そして、第1筐体5601と第2筐体5602とは、接続部5605により接続されており、第1筐体5601と第2筐体5602との間の角度は、接続部5605により可動となっている。第1表示部5603における映像の切り替えを、接続部5605における第1筐体5601と第2筐体5602との間の角度に従って、切り替える構成としても良い。第1表示部5603または第2表示部5604に、或いはその他の回路に、本発明の一態様に係る半導体装置を用いることができる。なお、第1表示部5603及び第2表示部5604の少なくとも一方に、位置入力装置としての機能が付加された半導体装置を用いるようにしても良い。なお、位置入力装置としての機能は、半導体装置にタッチパネルを設けることで付加することができる。或いは、位置入力装置としての機能は、フォトセンサとも呼ばれる光電変換素子を半導体装置の画素部に設けることでも、付加することができる。

#### 【0180】

図15(E)はビデオカメラであり、第1筐体5801、第2筐体5802、表示部5803、操作キー5804、レンズ5805、接続部5806等を有する。操作キー5804及びレンズ5805は第1筐体5801に設けられており、表示部5803は第2筐体5802に設けられている。そして、第1筐体5801と第2筐体5802とは、接続部5806により接続されており、第1筐体5801と第2筐体5802との間の角度は、接続部5806により可動となっている。表示部5803における映像の切り替えを、接続部5806における第1筐体5801と第2筐体5802との間の角度に従って行う構成としても良い。表示部5803に、或いはその他の回路に、本発明の一態様に係る半導体装置を用いることができる。

#### 【0181】

ここで、本発明の一態様は、以下に示す半導体装置をその範疇に含む。

#### 【0182】

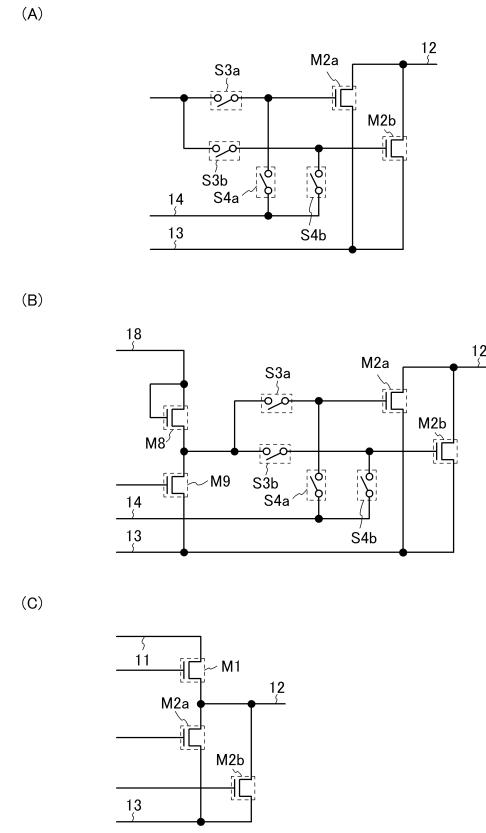

本発明の一態様は、トランジスタM2a、トランジスタM2b、スイッチS3a、スイッチS3b、スイッチS4a及びスイッチS4bを有する半導体装置である。トランジスタM2aは、第1の端子が配線13と接続され、第2の端子が配線12と接続される。トランジスタM2bは、第1の端子が配線13と接続され、第2の端子が配線12と接続される。スイッチS3aは、第2の端子がトランジスタM2aのゲートと接続される。スイッチS3bは、第1の端子がスイッチS3aの第1の端子と接続され、第2の端子がトランジスタM2bのゲートと接続される。スイッチS4aは、第1の端子が配線14と接続され、第2の端子がトランジスタM2aのゲートと接続される。スイッチS4bは、第1の端子が配線14と接続され、第2の端子がトランジスタM2bのゲートと接続される(図16(A)参照)。

10

20

30

40

50

**【 0 1 8 3 】**

なお、上記半導体装置は、スイッチ S 3 a 及びスイッチ S 4 b がオンであり、スイッチ S 3 b 及びスイッチ S 4 a がオフである期間 T a と、スイッチ S 3 a 及びスイッチ S 4 b がオフであり、スイッチ S 3 b 及びスイッチ S 4 a がオンである期間 T b と、を有していてもよい。また、スイッチ S 3 a、スイッチ S 3 b、スイッチ S 4 a 及びスイッチ S 4 b がオフである期間を有していてもよい。

**【 0 1 8 4 】**

なお、上記半導体装置において、期間 T a は、スイッチ S 3 a の第 1 の端子の電位がトランジスタ M 2 a がオンになる値であり、配線 1 4 の電位がトランジスタ M 2 b がオンになる値である期間 T 3 a と、スイッチ S 3 a の第 1 の端子の電位がトランジスタ M 2 a がオンになる値であり、配線 1 4 の電位がトランジスタ M 2 b がオフになる値である期間 T 4 a と、を有していてもよい。また、期間 T b は、スイッチ S 3 b の第 1 の端子の電位がトランジスタ M 2 b がオンになる値であり、配線 1 4 の電位がトランジスタ M 2 a がオンになる値である期間 T 3 b と、スイッチ S 3 b の第 1 の端子の電位がトランジスタ M 2 b がオンになる値であり、配線 1 4 の電位がトランジスタ M 2 a がオフになる値である期間 T 4 b と、を有していてもよい。

10

**【 0 1 8 5 】**

なお、上記半導体装置は、トランジスタ M 8、及びトランジスタ M 9 を有していてもよい。トランジスタ M 8 は、第 1 の端子が配線 1 8 と接続され、第 2 の端子がスイッチ S 3 a の第 1 の端子と接続され、ゲートが配線 1 8 と接続される。トランジスタ M 9 は、第 1 の端子が配線 1 3 と接続され、第 2 の端子がスイッチ S 3 a の第 1 の端子と接続される（図 1 6 ( B ) 参照）。

20

**【 0 1 8 6 】**

また、本発明の一態様は、トランジスタ M 1、トランジスタ M 2 a 及びトランジスタ M 2 b を有する半導体装置である。トランジスタ M 1 は、第 1 の端子が配線 1 1 と接続され、第 2 の端子が配線 1 2 と接続される。トランジスタ M 2 a は、第 1 の端子が配線 1 3 と接続され、第 2 の端子が配線 1 2 と接続される。トランジスタ M 2 b は、第 1 の端子が配線 1 3 と接続され、第 2 の端子が配線 1 2 と接続される（図 1 6 ( C ) 参照）。そして、上記半導体装置は、トランジスタ M 1 がオンであり、トランジスタ M 2 a 及びトランジスタ M 2 b がオフである期間（期間 T 1 a、期間 T 2 a、期間 T 1 b 又は期間 T 2 b ）と、トランジスタ M 1 がオフであり、トランジスタ M 2 a 及びトランジスタ M 2 b がオンである期間（例えば期間 T 3 a 又は期間 T 3 b ）と、トランジスタ M 1 及びトランジスタ M 2 b がオフであり、トランジスタ M 2 a がオンである期間（例えば期間 T 4 a ）と、トランジスタ M 1 及びトランジスタ M 2 a がオフであり、トランジスタ M 2 b がオンである期間（例えば期間 T 4 b ）と、を有する。

30

**【 0 1 8 7 】**

本実施の形態は、他の実施の形態等に記載した構成と適宜組み合わせて実施することができる。

**【 符号の説明 】****【 0 1 8 8 】**

40

C 1 クロック信号

C 容量素子

C K 1 信号

C K 2 信号

G 走査線

G 1 走査線

G y 走査線

M 1 トランジスタ

M 2 a トランジスタ

M 2 b トランジスタ

50

|         |        |    |

|---------|--------|----|

| M 3 a   | トランジスタ |    |

| M 3 b   | トランジスタ |    |

| M 4 a   | トランジスタ |    |

| M 4 b   | トランジスタ |    |

| M 5     | トランジスタ |    |

| M 6     | トランジスタ |    |

| M 7 a   | トランジスタ |    |

| M 7 b   | トランジスタ |    |

| M 8     | トランジスタ |    |

| M 9     | トランジスタ | 10 |

| M 1 0   | トランジスタ |    |

| M 1 1   | トランジスタ |    |

| M 1 2   | トランジスタ |    |

| M 1 3   | トランジスタ |    |

| M 1 4   | トランジスタ |    |

| M 1 5   | トランジスタ |    |

| M 1 6   | トランジスタ |    |

| M 1 7   | トランジスタ |    |

| M 1 8   | トランジスタ |    |

| N 1     | ノード    | 20 |

| N 2 a   | ノード    |    |

| N 2 b   | ノード    |    |

| N 3     | ノード    |    |

| S       | 信号線    |    |

| S x     | 信号線    |    |

| S 1     | 信号線    |    |

| S 3 a   | スイッチ   |    |

| S 3 b   | スイッチ   |    |

| S 4 a   | スイッチ   |    |

| S 4 b   | スイッチ   | 30 |

| S C K 1 | 信号     |    |

| S C K 2 | 信号     |    |

| T a     | 期間     |    |

| T b     | 期間     |    |

| T 1 a   | 期間     |    |

| T 1 b   | 期間     |    |

| T 2 a   | 期間     |    |

| T 2 b   | 期間     |    |

| T 3 a   | 期間     |    |

| T 3 b   | 期間     | 40 |

| T 4 a   | 期間     |    |

| T 4 b   | 期間     |    |

| T 1 3   | トランジスタ |    |

| T 1 4   | トランジスタ |    |

| T 1 5   | トランジスタ |    |

| V 1     | 電位     |    |

| V 2     | 電位     |    |

| V g 1   | スキャン信号 |    |

| V N 1   | 電位     |    |

| V N 2 a | 電位     | 50 |

|         |         |    |

|---------|---------|----|

| V N 2 b | 電位      |    |

| S P     | 信号      |    |

| R E     | 信号      |    |

| O U T   | 信号      |    |

| S E L a | 信号      |    |

| S E L b | 信号      |    |

| S S P   | 信号      |    |

| S O U T | 信号      |    |

| 1 0     | 回路      |    |

| 1 1     | 配線      | 10 |

| 1 2     | 配線      |    |

| 1 3     | 配線      |    |

| 1 4     | 配線      |    |

| 1 5     | 配線      |    |

| 1 6 a   | 配線      |    |

| 1 6 b   | 配線      |    |

| 1 7     | 配線      |    |

| 1 8     | 配線      |    |

| 2 0     | 回路      |    |

| 3 0     | 順序回路    | 20 |

| 6 0     | パネル     |    |

| 6 1     | 画素部     |    |

| 6 2     | 画素      |    |

| 6 3     | 走査線駆動回路 |    |

| 6 4     | 信号線駆動回路 |    |

| 6 5     | 液晶素子    |    |

| 6 6     | トランジスタ  |    |

| 6 7     | 容量素子    |    |

| 2 0 1   | トランジスタ  |    |

| 2 0 2   | トランジスタ  | 30 |

| 2 0 3   | 導電膜     |    |

| 2 0 4   | 導電膜     |    |

| 2 0 5   | 絶縁膜     |    |

| 2 0 6   | 半導体膜    |    |

| 2 0 7   | 導電膜     |    |

| 2 0 8   | 導電膜     |    |

| 2 0 9   | 絶縁膜     |    |

| 2 1 0   | 絶縁膜     |    |

| 2 1 1   | 絶縁膜     |    |

| 2 1 2   | 導電膜     | 40 |

| 2 1 3   | 半導体膜    |    |

| 2 1 4   | 導電膜     |    |

| 2 1 5   | 導電膜     |    |

| 2 1 7   | 絶縁膜     |    |

| 4 0 0 1 | 基板      |    |

| 4 0 0 2 | 画素部     |    |

| 4 0 0 3 | 信号線駆動回路 |    |

| 4 0 0 4 | 走査線駆動回路 |    |

| 4 0 0 5 | 封止材     |    |

| 4 0 0 6 | 基板      | 50 |

|         |             |    |

|---------|-------------|----|

| 4 0 1 0 | トランジスタ      |    |

| 4 0 1 8 | F P C       |    |

| 4 0 2 0 | 絶縁膜         |    |

| 4 0 2 1 | 電極          |    |

| 4 0 2 2 | トランジスタ      | 10 |

| 4 0 2 3 | 液晶素子        |    |

| 4 0 2 4 | 導電膜         |    |

| 4 0 2 5 | 絶縁膜         |    |

| 4 0 2 6 | 絶縁膜         |    |

| 4 0 2 7 | 電極          |    |

| 4 0 2 8 | 液晶層         |    |

| 4 0 3 0 | 配線          |    |

| 5 0 0 1 | 筐体          |    |

| 5 0 0 2 | 筐体          |    |

| 5 0 0 3 | 表示部         |    |

| 5 0 0 4 | 表示部         |    |

| 5 0 0 5 | マイクロホン      |    |

| 5 0 0 6 | スピーカー       |    |

| 5 0 0 7 | 操作キー        |    |

| 5 0 0 8 | スタイルス       | 20 |

| 5 2 0 1 | 筐体          |    |

| 5 2 0 2 | 表示部         |    |

| 5 2 0 3 | 支持台         |    |

| 5 4 0 1 | 筐体          |    |

| 5 4 0 2 | 表示部         |    |

| 5 4 0 3 | キーボード       |    |

| 5 4 0 4 | ポインティングデバイス |    |

| 5 6 0 1 | 筐体          |    |

| 5 6 0 2 | 筐体          |    |

| 5 6 0 3 | 表示部         | 30 |

| 5 6 0 4 | 表示部         |    |

| 5 6 0 5 | 接続部         |    |

| 5 6 0 6 | 操作キー        |    |

| 5 8 0 1 | 筐体          |    |

| 5 8 0 2 | 筐体          |    |

| 5 8 0 3 | 表示部         |    |

| 5 8 0 4 | 操作キー        |    |

| 5 8 0 5 | レンズ         |    |

| 5 8 0 6 | 接続部         |    |

|         |             | 40 |

## 【図面】

## 【図1】

## 【図2】

10

20

30

40

50

【図3】

【図4】

10

20

【図5】

30

【図6】

40

50

【図 7】

【図 8】

【図 9】

【図 10】

【図 1 1】

【図 1 2】

10

(B)

20

【図 1 3】

(B)

【図 1 4】

30

40

50

【図15】

【図16】

10

20

30

40

【図17】

50

---

フロントページの続き

(51)国際特許分類

F I

|         |       |       |

|---------|-------|-------|

| G 0 9 F | 9/30  | 3 3 8 |

| G 1 1 C | 19/28 | 2 3 0 |

(56)参考文献

特開2011-133826 (JP, A)

特開2011-004393 (JP, A)

米国特許第07633477 (US, B2)

(58)調査した分野 (Int.Cl., DB名)

G 0 9 G 3 / 0 0 - 5 / 4 2

G 0 9 F 9 / 0 0 - 9 / 4 6

G 1 1 C 1 9 / 2 8