(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4287039号

(P4287039)

(45) 発行日 平成21年7月1日(2009.7.1)

(24) 登録日 平成21年4月3日(2009.4.3)

|                      |            |

|----------------------|------------|

| (51) Int.Cl.         | F 1        |

| HO4L 27/36 (2006.01) | HO4L 27/00 |

| HO3C 3/04 (2006.01)  | HO3C 3/04  |

| HO3G 3/20 (2006.01)  | HO3G 3/20  |

| HO4L 27/20 (2006.01) | HO4L 27/20 |

請求項の数 5 (全 11 頁)

(21) 出願番号 特願2000-385375 (P2000-385375)

(22) 出願日 平成12年12月19日 (2000.12.19)

(65) 公開番号 特開2002-185547 (P2002-185547A)

(43) 公開日 平成14年6月28日 (2002.6.28)

審査請求日 平成18年8月18日 (2006.8.18)

(73) 特許権者 308014341

富士通マイクロエレクトロニクス株式会社

東京都新宿区西新宿二丁目7番1号

(74) 代理人 100068755

弁理士 恩田 博宣

(74) 代理人 100105957

弁理士 恩田 誠

(72) 発明者 森邊 剛

愛知県春日井市高蔵寺町二丁目1844番

2 富士通ヴィエルエスアイ株式会社内

(72) 発明者 有村 一義

愛知県春日井市高蔵寺町二丁目1844番

2 富士通ヴィエルエスアイ株式会社内

最終頁に続く

(54) 【発明の名称】半導体集積回路装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1変調信号を生成する直交変調器と、

前記第1変調信号を増幅した第2変調信号を生成するAGC部と

を備えた半導体集積回路装置において、

前記直交変調器を構成する位相シフタ回路の利得を制御信号に従って調整する利得調整

回路を備え、

前記利得調整回路は、前記AGC部の第2変調信号のレベルの減衰にともなって前記位

相シフタ回路の利得を減衰させる

ことを特徴とする半導体集積回路装置。

10

## 【請求項 2】

前記利得調整回路は、前記制御信号に基づいて、前記位相シフタ回路の利得を調整する

利得制御信号を該位相シフタ回路に出力することを特徴とする請求項1記載の半導体集積

回路装置。

## 【請求項 3】

前記位相シフタ回路は、利得の異なる複数の位相シフタ回路のうちの一つであり、前記

第2変調信号のレベルの減衰にともなって利得の低い位相シフタ回路を選択して動作させ

ることを特徴とする請求項1又は2に記載の半導体集積回路装置。

## 【請求項 4】

前記位相シフタ回路は、利得の調整可能な振幅可変型位相シフタ回路と、固定利得の位

20

相シフタ回路とを含む複数の位相シフタ回路のうちの一つであり、前記第2変調信号のレベルの減衰にともなって前記振幅可変型位相シフタ回路を活性化し、該振幅可変型位相シフタ回路は前記制御信号に従って自己の利得を低下させることを特徴とする請求項1又は2に記載の半導体集積回路装置。

【請求項5】

前記直交変調器は、前記制御信号をA/D変換して前記位相シフタ回路に供給する信号を生成するA/D変換器を備えたことを特徴とする請求項3または4記載の半導体集積回路装置。

【発明の詳細な説明】

【0001】

10

【発明の属する技術分野】

この発明は、利得可変増幅器（AGC回路）を備えた直交変調器に関するものである。

【0002】

近年、携帯電話等の移動体通信機器では、低消費電力化及び通話品質の向上が急務となっている。そこで、移動体通信機器の送信部に用いられる直交変調器の特性を向上させる必要がある。

【0003】

【従来の技術】

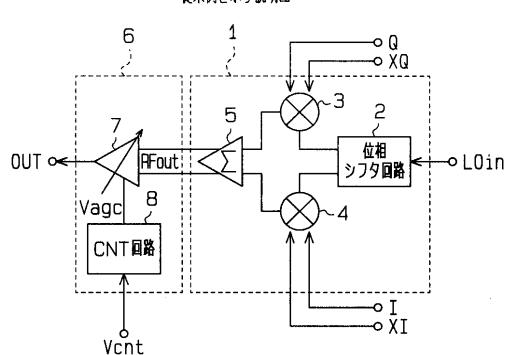

図10は、AGC回路を備えた直交変調器の従来例を示す。直交変調器1は、位相シフタ回路2と、変調用ミキサ回路3, 4と、加算器5とで構成される。

20

【0004】

この位相シフタ回路2には、所定周波数の相補入力信号LOinが入力される。そして、位相シフタ回路2は入力信号LOinに基づいて、位相を90度ずつシフトさせたキャリア信号を生成する。

【0005】

変調用ミキサ回路3, 4には、前記位相シフタ回路2から出力されるキャリア信号のうち、180度位相がずれた信号がそれぞれ入力されるとともに、ベースバンド信号Q, XQと、同I, XIがそれぞれ入力される。

【0006】

そして、変調用ミキサ回路3はキャリア信号とベースバンド信号Q, XQを掛け合わせた変調信号を加算器5に出力し、変調用ミキサ回路4はキャリア信号とベースバンド信号I, XIを掛け合わせた変調信号を加算器5に出力する。

30

【0007】

加算器5は、変調用ミキサ回路3, 4から出力される変調信号を加算して、出力信号RFoutをAGC部6に出力する。

AGC部6は、AGC回路7と、CNT回路8とで構成され、変調用ミキサ回路3, 4の出力信号RFoutはAGC回路7に入力される。

【0008】

CNT回路8には制御信号Vcntが入力され、CNT回路8はその制御信号Vcntに基づいて利得制御信号Vagcを生成してAGC回路7に出力する。

40

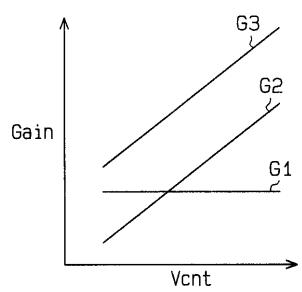

図12に示すように、位相シフタ回路2の利得G1は一定であり、AGC回路7の利得G2は利得制御信号Vagcに基づいて変化する。そして、直交変調器1とAGC部6との総合利得G3は、制御信号Vcntに基づいてAGC部6の利得G2と同じ傾きで変化する。

【0009】

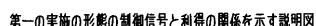

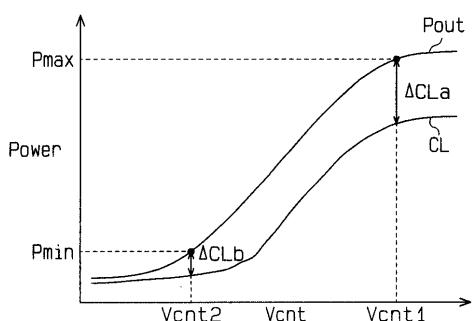

従って、AGC回路7から出力される出力信号OUTの出力レベルPoutは、図11に示すように、制御信号VcntをVcnt1からVcnt2まで変化させることにより、最大値Pmaxから最小値Pminまでの範囲で調整可能となっている。

【0010】

【発明が解決しようとする課題】

上記のように構成された直交変調器1及びAGC部6では、位相シフタ回路2の出力周波

50

数成分がキャリアリークとして常に出力信号 OUT に含まれている。

【0011】

図11に示すように、キャリアリーク CL は、AGC回路7の利得の減少にともなって、出力信号 Poutとともに減衰するが、出力信号 Poutが最小値 Pminに近づくにつれて、その減衰幅は出力信号 Poutより小さくなる。

【0012】

すると、出力信号 Poutが最大値 Pmaxとなるときにおける出力信号 Poutとキャリアリーク CLとのレベル差 CLa に比して、出力信号 Poutが最小値 Pminとなるときにおける出力信号 Poutとキャリアリーク CLとのレベル差 CLb が小さくなる。これは、位相シフタ回路2からキャリアリーク成分として出力される出力周波数成分が一定レベルで出力されているからである。 10

【0013】

従って、制御信号 Vcntにより出力信号 Poutを最小値 Pmin近傍まで減衰させると、キャリアリーク特性が劣化するという問題点がある。

この発明の目的は、出力信号レベルを減衰させた場合にも、キャリアリーク特性が劣化しない直交変調器を提供することにある。

【0014】

【課題を解決するための手段】

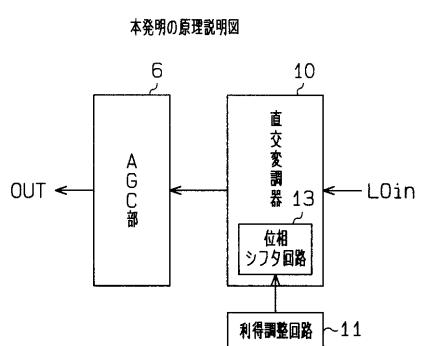

図1は、本発明の原理説明図である。すなわち、第1変調信号を生成する直交変調器10と、前記第1変調信号を増幅した第2変調信号を生成するAGC部6とを備えた半導体集積回路装置には、前記直交変調器10を構成する位相シフタ回路13の利得を制御信号に従って調整する利得調整回路11が備えられる。利得調整回路11により位相シフタ回路13の利得が制御信号に従って調整されて直交変調器10の利得が調整され、その直交変調器10の出力信号がAGC回路に入力される。 20

【0015】

そして、利得調整回路は、前記AGC部の第2変調信号のレベルの減衰にともなって前記位相シフタ回路の利得を減衰させる。利得調整回路の動作により、AGC部の第2変調信号のレベルが減衰するとき、位相シフタ回路の利得が減衰する。

【0016】

本発明の別の態様では、前記利得調整回路は、前記制御信号に基づいて、前記位相シフタ回路の利得を調整する利得制御信号を該位相シフタ回路に出力する。AGC部に入力される制御信号で、AGC回路の利得が調整されるとき、位相シフタ回路に利得制御信号が入力されて、位相シフタ回路の利得が調整される。 30

【0017】

本発明の別の態様では、前記位相シフタ回路は、利得の異なる複数の位相シフタ回路のうちの一つであり、前記第2変調信号のレベルの減衰にともなって利得の低い位相シフタ回路を選択して動作させる。AGC部の利得が減衰するとき、利得の異なる複数の位相シフタ回路の中から、利得の低い位相シフタ回路が選択されて動作する。

【0018】

本発明の別の態様では、前記位相シフタ回路は、利得の調整可能な振幅可変型位相シフタ回路と、固定利得の位相シフタ回路とを含む複数の位相シフタ回路のうちの一つであり、前記第2変調信号のレベルの減衰にともなって前記振幅可変型シフタ回路を活性化し、該振幅可変型シフタ回路は前記制御信号に従って自己の利得を低下させる。AGC部の利得が減衰するとき、振幅可変型位相シフタ回路が選択されて動作し、その振幅可変型位相シフタ回路はAGC部の出力信号レベルの減衰にともなって利得が低下する。 40

【0019】

本発明の別の態様では、前記直交変調器は、前記制御信号をA/D変換して前記位相シフタ回路に供給する信号を生成するA/D変換器を備えた。AGC部の利得を調整する制御信号がA/D変換され、その変換後の信号で位相シフタ回路が選択される。

【0020】

## 【発明の実施の形態】

## (第一の実施の形態)

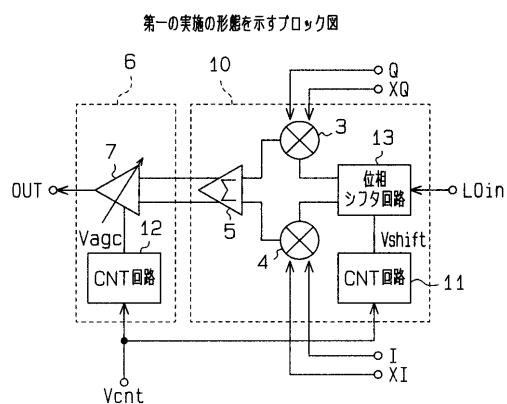

図2は、この発明を具体化した第一の実施の形態を示す。この実施の形態は、直交変調器10を構成する位相シフタ回路13の出力振幅を第一のCNT回路11で制御し、前述した従来例と同様なAGC回路7の利得を第二のCNT回路12で制御するように構成したものであり、その他の構成は前記従来例と同様である。

## 【0021】

第一及び第二のCNT回路11, 12には、制御信号Vcntが入力され、第一のCNT回路11は制御信号Vcntの入力に基づいて位相シフタ回路13の利得を制御する利得制御信号Vshiftを生成して、同位相シフタ回路13に出力する。

10

## 【0022】

第二のCNT回路12は、制御信号Vcntの入力に基づいてAGC回路7の利得を制御する利得制御信号Vagcを同AGC回路7に出力する。

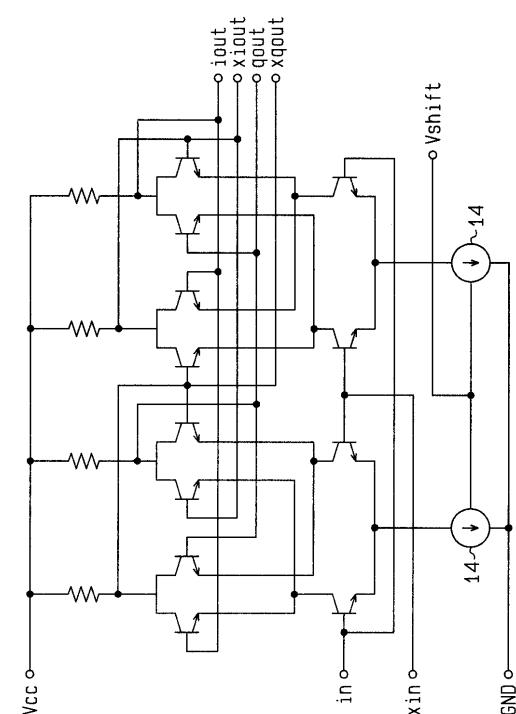

位相シフタ回路13の具体的構成を図3に従って説明する。同図に示すように、位相シフタ回路13はマスター段のラッチ回路と、スレーブ段のラッチ回路とからフリップフロップ回路が構成され、各ラッチ回路は、電流源回路14を介してグランドGNDに接続されている。

## 【0023】

電流源回路14には利得制御信号Vshiftが入力され、その利得制御信号Vshiftに基づいて電流源回路14の出力電流を制御することにより、位相シフタ回路13の出力信号iout, xiout, qout, xqoutの出力振幅を制御可能となっている。

20

## 【0024】

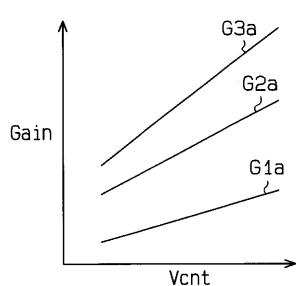

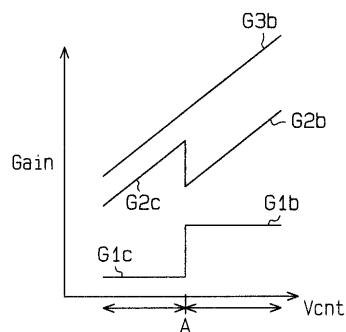

上記のように構成された直交変調器10では、図4に示すように、制御信号Vcntに基づいて位相シフタ回路13の利得G1aが制御される。また、AGC部6では、制御信号Vcntに基づいて、AGC回路7の利得G2aが制御される。

## 【0025】

そして、出力信号OUTの総合利得G3aは、利得G1a, G2aを合算したものとなり、前記従来例の総合利得G3と同様に設定されている。

上記のように構成された直交変調器10及びAGC部6では、次に示す作用効果を得ることができる。

30

(1) 制御信号Vcntに基づいて、AGC部6から出力される出力信号OUTの出力レベルPoutを調整するとき、AGC回路7の利得G2aとともに位相シフタ回路13の利得G1aを調整することができる。

(2) 出力信号OUTの出力レベルPoutを減衰させると、AGC回路7の利得G2aとともに位相シフタ回路13の利得G1aも減衰させることができる。従って、図5に示すように、出力信号OUTの出力レベルPoutを最小値Pmin近傍まで減衰させたとき、キャリアリークCLの出力レベルも減衰するため、出力信号PoutとキャリアリークCLとのレベル差CLが小さくなることはない。

(3) 出力信号OUTの出力レベルPoutを減衰させても、出力信号PoutとキャリアリークCLとのレベル差CLが小さくなることはないので、キャリアリーク特性を向上させることができる。

40

## (第二の実施の形態)

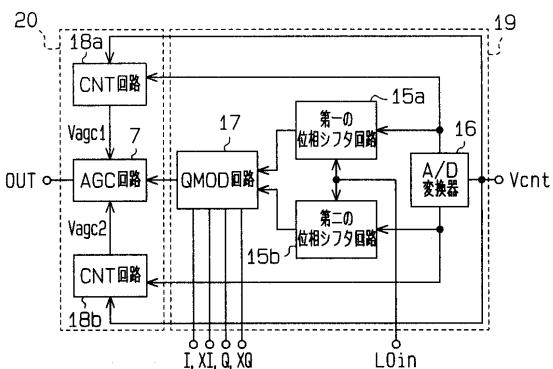

図6は、第二の実施の形態の直交変調器19及びAGC部20を示す。この実施の形態は、入力信号LOinが第一及び第二の位相シフタ回路15a, 15bに入力される。前記第一及び第二の位相シフタ回路15a, 15bは、それぞれ一定の利得で動作し、第一の位相シフタ回路15aの利得は、第二の位相シフタ回路15bの利得より小さく設定されている。

## 【0026】

制御信号Vcntは、A/D変換器16に入力される。前記A/D変換器16は、例えば前記制御信号Vcntが図7に示すあらかじめ設定された所定値A以下であれば、Lレベルの

50

信号を前記第一及び第二の位相シフタ回路 15a, 15b に出力するとともに、制御信号 Vcnt が前記所定値 A を越えると、H レベルの信号を第一及び第二の位相シフタ回路 15a, 15b に出力する。

【0027】

そして、A/D 変換器 16 の出力信号が L レベルであれば、第一の位相シフタ回路 15a が活性化されて、その出力信号が QM0D 回路 17 に出力される。

また、A/D 変換器 16 の出力信号が H レベルであると、第二の位相シフタ回路 15b が活性化されて、その出力信号が QM0D 回路 17 に出力される。

【0028】

QM0D 回路 17 は、前記第一の実施の形態の変調用ミキサ回路 3, 4 及び加算器 5 に相 10

当するものである。

QM0D 回路 17 の出力信号は、AGC 回路 7 に入力される。前記 AGC 回路 7 には第三

及び第四のCNT 回路 18a, 18b から利得制御信号 Vagc1, Vagc2 が入力される。

【0029】

第三及び第四のCNT 回路 18a, 18b には、前記制御信号 Vcnt 及び前記 A/D 変換

器 16 の出力信号が入力される。

A/D 変換器 16 の出力信号が L レベルであれば、第三のCNT 回路 18a が活性化され

、利得制御信号 Vagc1 が AGC 回路 7 に出力される。また、A/D 変換器 16 の出力信号

が H レベルであれば、第四のCNT 回路 18b が活性化され、利得制御信号 Vagc2 が AG

C 回路 7 に出力される。 20

【0030】

そして、AGC 回路 7 は利得制御信号 Vagc1, Vagc2 に基づいて異なる利得で動作する

とともに、利得制御信号 Vagc1 の方が高利得で動作し、その利得差は、前記第一及び第二の

位相シフタ回路 15a, 15b の利得差と等しくなるように設定されている。

【0031】

上記のように構成された直交変調器 19 及び AGC 部 20 の動作を図 7 に従って説明する

。

制御信号 Vcnt が所定値 A を越えている場合には、A/D 変換器 16 の出力信号に基づいて

第二の位相シフタ回路 15b が活性化されて、利得 G1b で動作し、その出力信号が QM0D

回路 17 に出力される。 30

【0032】

また、第四のCNT 回路 18b が活性化されて、利得制御信号 Vagc2 が AGC 回路 7 に入

力され、AGC 回路 7 は利得 G2b で動作する。そして、AGC 回路 7 から第二の位相シ

フタ回路 15b 及び AGC 回路 7 の利得 G1b, G2b に基づく出力信号 OUT が利得 G

3b で出力される。

【0033】

一方、制御信号 Vcnt が所定値 A 以下となる場合には、A/D 変換器 16 の出力信号に基づ

いて第一の位相シフタ回路 15a が活性化されて、利得 G1c で動作し、その出力信号

が QM0D 回路 17 に出力される。

【0034】

また、第三のCNT 回路 18a が活性化されて、利得制御信号 Vagc2 が AGC 回路 7 に入

力され、AGC 回路 7 は利得 G2c で動作する。そして、AGC 回路 7 から第一の位相シ

フタ回路 15a 及び AGC 回路 7 の利得 G1c, G2c に基づく出力信号 OUT が利得 G

3b で出力される。 40

【0035】

上記のように構成された直交変調器 19 及び AGC 部 20 では、次に示す作用効果を得る

ことができる。

(1) 制御信号 Vcnt に基づいて、AGC 部 20 から出力される出力信号 OUT の出力レ

ベルを調整するとき、制御信号 Vcnt が所定値 A を越えて、出力信号 OUT の出力レベル

が高いとき、高い利得 G1b で動作する第二の位相シフタ回路 15b と、低い利得 G2b 50

で動作する第四のC N T回路18bとが動作して、出力信号O U Tが出力される。

【0036】

また、制御信号V cntが所定値A以下となって、出力信号O U Tの出力レベルが低いとき、低い利得G 1 cで動作する第一の位相シフタ回路15aと、高い利得G 2 cで動作する第三のC N T回路18aとが動作して、出力信号O U Tが出力される。

【0037】

従って、出力信号O U Tの出力レベルが低いとき、低い利得G 1 cで動作する第一の位相シフタ回路15aの利得を補うように第三のC N T回路18aを動作させることができること。

(2) 出力信号O U Tの出力レベルを減衰させると、第一の位相シフタ回路15aを選択して動作させて、位相シフタ回路部分の利得を小さくすることができる。従って、図5に示すように、出力信号O U Tの出力レベルP outを最小値P min近傍まで減衰させたとき、キャリアリークC Lの出力レベルも減衰するため、出力信号P outとキャリアリークC Lとのレベル差C Lが小さくなることはない。

(3) 出力信号O U Tの出力レベルP outを減衰させても、出力信号P outとキャリアリークC Lとのレベル差C Lが小さくなることはないので、キャリアリーク特性を向上させることができる。

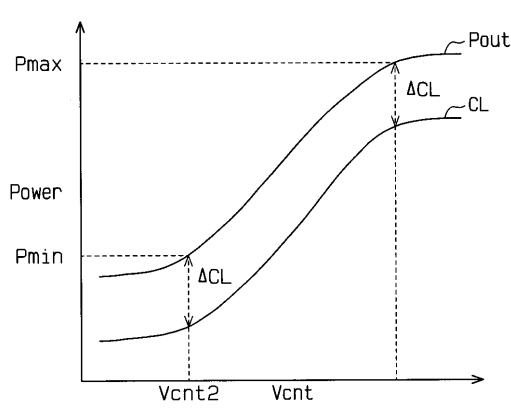

(第三の実施の形態)

図8は、第三の実施の形態の直交変調器21及びAGC部22を示す。この実施の形態は、入力信号L O inが利得を調整可能とした振幅可変型位相シフタ回路23aと、利得を固定した位相シフタ回路23bとに入力される。

【0038】

制御信号V cntは、前記第二の従来例と同様なA / D変換器16に入力される。前記A / D変換器16は、制御信号V cntが図9に示すあらかじめ設定された所定値A以下であれば、Lレベルの信号を前記位相シフタ回路23a, 23bに出力するとともに、制御信号V cntが前記所定値Aを越えると、Hレベルの信号を位相シフタ回路23a, 23bに出力する。

【0039】

そして、A / D変換器16の出力信号がLレベルであれば、振幅可変型シフタ回路23aが活性化されて、その出力信号がQ M O D回路17に出力される。

また、A / D変換器16の出力信号がHレベルであると、位相シフタ回路23bが活性化されて、その出力信号がQ M O D回路17に出力される。

【0040】

Q M O D回路17は、前記第一の実施の形態の変調用ミキサ回路3, 4及び加算器5に相当するものである。

Q M O D回路17の出力信号は、AGC回路7に入力される。このAGC回路7には第五及び第六のC N T回路24a, 24bから利得制御信号V agc3, V agc4が入力される。

【0041】

第五及び第六のC N T回路24a, 24bには、制御信号V cnt及びA / D変換器16の出力信号が入力される。

A / D変換器16の出力信号がLレベルであれば、第五のC N T回路24aが活性化され、利得制御信号V agc3がAGC回路7及び振幅可変型位相シフタ回路23aに出力される。

【0042】

また、A / D変換器16の出力信号がHレベルであれば、第六のC N T回路24bが活性化され、利得制御信号V agc4がAGC回路7に出力される。

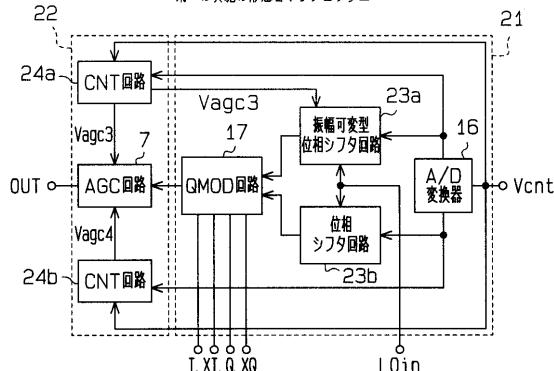

そして、図9に示すように、AGC回路7の利得G 2 d, G 2 eは利得制御信号V agc3, V agc4に基づいて異なる傾きで変化し、利得制御信号V agc4に基づく利得G 2 eの方が大きな傾きで動作する。

【0043】

10

20

30

40

50

また、利得制御信号  $V_{agc3}$  に基づく A G C 回路 7 の利得  $G_{2d}$  の傾きと、前記振幅可変型位相シフタ回路 2 3 a の利得  $G_{1d}$  の傾きの和は、利得制御信号  $V_{agc4}$  に基づく A G C 回路 7 の利得  $G_{2e}$  の傾きと等しくなるように設定されている。

【 0 0 4 4 】

上記のように構成された直交変調器 2 1 及び A G C 部 2 2 の動作を図 9 に従って説明する。

制御信号  $V_{cnt}$  が所定値 A を越えている場合には、A / D 変換器 1 6 の出力信号に基づいて位相シフタ回路 2 3 b が活性化されて、固定利得  $G_{1e}$  で動作し、その出力信号が Q M O D 回路 1 7 に出力される。

【 0 0 4 5 】

また、第六の C N T 回路 2 4 b が活性化されて、利得制御信号  $V_{agc4}$  が A G C 回路 7 に入力され、A G C 回路 7 は利得  $G_{2e}$  で動作する。そして、A G C 回路 7 から位相シフタ回路 2 3 b の利得  $G_{1e}$  及び A G C 回路 7 の利得  $G_{2e}$  に基づく出力信号 O U T が利得  $G_{3c}$  で出力される。

【 0 0 4 6 】

一方、制御信号  $V_{cnt}$  が所定値 A 以下となる場合には、A / D 変換器 1 6 の出力信号に基づいて振幅可変型位相シフタ回路 2 3 a が活性化されて、利得  $G_{1d}$  で動作し、その出力信号が Q M O D 回路 1 7 に出力される。

【 0 0 4 7 】

また、第五の C N T 回路 1 8 a が活性化されて、利得制御信号  $V_{agc3}$  が A G C 回路 7 に入力され、A G C 回路 7 は利得  $G_{2d}$  で動作する。そして、A G C 回路 7 から振幅可変型位相シフタ回路 2 3 a 及び A G C 回路 7 の利得  $G_{1d}$  ,  $G_{2d}$  に基づく出力信号 O U T が利得  $G_{3c}$  で出力される。

【 0 0 4 8 】

上記のように構成された直交変調器 1 9 及び A G C 部 2 0 では、次に示す作用効果を得ることができる。

( 1 ) 制御信号  $V_{cnt}$  に基づいて、A G C 部 2 2 から出力される出力信号 O U T の出力レベルを調整するとき、制御信号  $V_{cnt}$  が所定値 A を越えて、出力信号 O U T の出力レベルが高いとき、固定利得  $G_{1e}$  で動作する位相シフタ回路 2 3 b と、第六の C N T 回路 2 4 b とが動作して、出力信号 O U T が出力される。

【 0 0 4 9 】

また、制御信号  $V_{cnt}$  が所定値 A 以下となって、出力信号 O U T の出力レベルが低いとき、振幅可変型位相シフタ回路 2 3 a と、第五の C N T 回路 2 4 a とが動作して、出力信号 O U T が出力される。

【 0 0 5 0 】

従って、出力信号 O U T の出力レベルが低いとき、低い利得  $G_{1d}$  で動作する振幅可変型位相シフタ回路 1 5 a の利得を補うように第五の C N T 回路 2 4 a を動作させることができる。

( 2 ) 出力信号 O U T の出力レベル  $P_{out}$  を減衰させると、振幅可変型位相シフタ回路 2 3 a を選択して動作させて、位相シフタ回路部分の利得を小さくすることができる。従って、図 5 に示すように、出力信号 O U T の出力レベル  $P_{out}$  を最小値  $P_{min}$  近傍まで減衰させたとき、キャリアリーク C L の出力レベルも減衰するため、出力信号  $P_{out}$  とキャリアリーク C L とのレベル差 C L が小さくなることはない。

( 3 ) 出力信号 O U T の出力レベル  $P_{out}$  を減衰させても、出力信号  $P_{out}$  とキャリアリーク C L とのレベル差 C L が小さくなることはないので、キャリアリーク特性を向上させることができる。

【 0 0 5 1 】

前記実施の形態は、次に示すように変更することもできる。

・ 第二の実施の形態では、二つの位相シフタ回路 1 5 a , 1 5 b からいずれかを選択する構成としたが、それぞれ利得の異なる 3 つ以上の位相シフト回路からいずれかを選択する

10

20

30

40

50

構成としてもよい。

・複数の位相シフタ回路からいずれかを選択する構成に代えて、振幅可変型位相シフタ回路で利得を調整する構成としてもよい。

【0052】

【発明の効果】

以上詳述したように、この発明は出力信号レベルを減衰させた場合にも、キャリアアリーク特性が劣化しない直交変調器を提供することができる。

【図面の簡単な説明】

【図1】 本発明の原理説明図である。

【図2】 第一の実施の形態を示すブロック図である。

10

【図3】 位相シフタ回路を示す回路図である。

【図4】 第一の実施の形態の制御信号と利得の関係を示す説明図である。

【図5】 キャリアアリークと出力信号レベルの減衰特性を示す説明図である。

【図6】 第二の実施の形態を示すブロック図である。

【図7】 第二の実施の形態の制御信号と利得の関係を示す説明図である。

【図8】 第三の実施の形態を示すブロック図である。

【図9】 第三の実施の形態の制御信号と利得の関係を示す説明図である。

【図10】 従来例を示す説明図である。

【図11】 従来例のキャリアアリークと出力信号レベルの減衰特性を示す説明図である。

【図12】 従来例の制御信号と利得の関係を示す説明図である。

20

【符号の説明】

|    |         |

|----|---------|

| 6  | A G C 部 |

| 10 | 直交変調器   |

| 11 | 利得調整回路  |

| 13 | 位相シフタ回路 |

【図1】

【図3】

【図2】

【図4】

【 义 5 】

キャリアリークと出力信号レベルとの差を示す説明図

( 8 )

### 第三の実施の形態を示すブロック図

( 9 )

### 第三の実施の形態の制御信号と利得の関係を示す説明図

【 图 6 】

## 第二の実施の形態を示すブロック図

〔 义 7 〕

## 第二の実施の形態の制御信号と利得の関係を示す説明図

( 8 )

〔 四 10 〕

### 従来例を示す説明図

( 111 )

従来例のキャリアリークと出力信号レベルとの差を示す説明図

## 【図 1 2】

従来例の制御信号と利得の関係を示す説明図

---

フロントページの続き

(72)発明者 加藤 進

愛知県春日井市高蔵寺町二丁目1844番2 富士通ヴィエルエスアイ株式会社内

審査官 彦田 克文

(56)参考文献 特開2000-013186 (JP, A)

特開平11-355205 (JP, A)

特開昭60-134514 (JP, A)

特開平11-317777 (JP, A)

特開2000-004173 (JP, A)

特開2001-358560 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H04L 27/36

H04L 27/20

H03C 3/04

H03G 3/20