(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5589891号

(P5589891)

(45) 発行日 平成26年9月17日(2014.9.17)

(24) 登録日 平成26年8月8日(2014.8.8)

(51) Int.Cl.

F 1

|        |       |           |

|--------|-------|-----------|

| HO 1 G | 4/252 | (2006.01) |

| HO 1 G | 4/228 | (2006.01) |

| HO 1 G | 4/232 | (2006.01) |

| HO 1 G | 4/12  | (2006.01) |

| HO 1 G | 4/30  | (2006.01) |

|        |      |     |

|--------|------|-----|

| HO 1 G | 1/14 | V   |

| HO 1 G | 1/14 | F   |

| HO 1 G | 4/12 | 361 |

| HO 1 G | 4/12 | 352 |

| HO 1 G | 4/12 | 364 |

請求項の数 10 (全 16 頁) 最終頁に続く

|              |                              |

|--------------|------------------------------|

| (21) 出願番号    | 特願2011-36860 (P2011-36860)   |

| (22) 出願日     | 平成23年2月23日 (2011.2.23)       |

| (65) 公開番号    | 特開2012-9813 (P2012-9813A)    |

| (43) 公開日     | 平成24年1月12日 (2012.1.12)       |

| 審査請求日        | 平成24年10月24日 (2012.10.24)     |

| (31) 優先権主張番号 | 特願2010-121867 (P2010-121867) |

| (32) 優先日     | 平成22年5月27日 (2010.5.27)       |

| (33) 優先権主張国  | 日本国 (JP)                     |

|           |                                              |

|-----------|----------------------------------------------|

| (73) 特許権者 | 000006231<br>株式会社村田製作所<br>京都府長岡京市東神足1丁目10番1号 |

| (74) 代理人  | 110001232<br>特許業務法人 宮▲崎▼・目次特許事務所             |

| (72) 発明者  | 西坂 康弘<br>京都府長岡京市東神足1丁目10番1号<br>株式会社村田製作所内    |

| (72) 発明者  | 眞田 幸雄<br>京都府長岡京市東神足1丁目10番1号<br>株式会社村田製作所内    |

| (72) 発明者  | 佐藤 浩司<br>京都府長岡京市東神足1丁目10番1号<br>株式会社村田製作所内    |

最終頁に続く

(54) 【発明の名称】セラミック電子部品及びその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

セラミック素体と、前記セラミック素体の上に形成されている外部電極とを備えるセラミック電子部品であって、

前記外部電極は、前記セラミック素体の上に形成されている下地電極層と、前記下地電極層の上に形成されている第1のCuめっき膜とを有し、

前記下地電極層は、Cuに拡散し得る金属と、セラミック結合材とを含み、

前記第1のCuめっき膜の少なくとも前記下地電極層側の表層には、前記Cuに拡散し得る金属が拡散している、セラミック電子部品。

## 【請求項 2】

前記下地電極層は、前記セラミック素体の上に導電性ペーストを塗布し、焼成することにより形成されている、請求項1に記載のセラミック電子部品。

## 【請求項 3】

前記第1のCuめっき膜には、粒界が存在しており、前記Cuに拡散し得る金属は、前記第1のCuめっき膜の粒界に沿って拡散している、請求項1または2に記載のセラミック電子部品。

## 【請求項 4】

前記Cuに拡散し得る金属は、前記第1のCuめっき膜の前記下地電極層とは反対側の表面にまで拡散している、請求項1～3のいずれか一項に記載のセラミック電子部品。

## 【請求項 5】

10

20

前記 Cu に拡散し得る金属は、 Ni , Ag , Pd 及び Au からなる群から選ばれた一種以上の金属である、請求項 1 ~ 4 のいずれか一項に記載のセラミック電子部品。

**【請求項 6】**

前記外部電極は、前記第 1 の Cu めっき膜の上に形成されている第 2 の Cu めっき膜をさらに有し、前記第 2 の Cu めっき膜には、前記 Cu に拡散し得る金属は拡散していない、請求項 1 ~ 5 のいずれか一項に記載のセラミック電子部品。

**【請求項 7】**

前記下地電極層には、前記第 1 の Cu めっき膜から Cu が拡散している、請求項 1 ~ 6 のいずれか一項に記載のセラミック電子部品。

**【請求項 8】**

セラミック素体と、前記セラミック素体の上に形成されている外部電極とを備えるセラミック電子部品の製造方法であって、

セラミック素体の上に、Cu に拡散し得る金属と、セラミック結合材とを含む下地電極層を形成し、さらに前記下地電極層の上に第 1 の Cu めっき膜を形成した後に、前記下地電極層と前記第 1 の Cu めっき膜とを加熱することにより、前記第 1 の Cu めっき膜の少なくとも前記下地電極層側の表層に前記 Cu に拡散し得る金属を拡散させることにより前記外部電極を形成する、セラミック電子部品の製造方法。

**【請求項 9】**

前記下地電極層と前記第 1 の Cu めっき層とを加熱することにより、前記第 1 の Cu めっき膜の少なくとも前記下地電極層側の表層に前記 Cu に拡散し得る金属を拡散させた後に、前記第 1 の Cu めっき膜の上に、第 2 の Cu めっき膜をさらに形成することにより前記外部電極を形成する、請求項 8 に記載のセラミック電子部品の製造方法。

**【請求項 10】**

前記下地電極層と前記第 1 の Cu めっき膜とを、 350 ~ 800 まで加熱することにより、前記第 1 の Cu めっき膜の少なくとも前記下地電極層側の表層に前記 Cu に拡散し得る金属を拡散させることにより前記外部電極を形成する、請求項 8 または 9 に記載のセラミック電子部品の製造方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、セラミック電子部品及びその製造方法に関する。特に、本発明は、配線基板に埋め込まれて使用される埋め込み型セラミック電子部品として好適に使用できるセラミック電子部品及びその製造方法に関する。

**【背景技術】**

**【0002】**

近年、携帯電話機や携帯音楽プレイヤーなどの電子機器の小型化や薄型化に伴い、電子機器に搭載される配線基板の小型化が進んでいる。

**【0003】**

配線基板を小型化する方法としては、例えば、下記の特許文献 1 において、セラミック電子部品を配線基板の内部に埋め込み、かつ、セラミック電子部品の上に形成されたビアホール導体により、セラミック電子部品への配線を構成する方法が提案されている。この方法によれば、配線基板の表面にセラミック電子部品を配置する領域を確保する必要がないばかりか、セラミック電子部品への配線を設ける領域を、セラミック電子部品が設けられる領域とは別個に確保する必要がない。従って、部品内蔵配線基板を小型化することができる。

**【0004】**

セラミック電子部品接続用のビアホールは、例えば、CO<sub>2</sub> レーザーなどのレーザーを用いて形成される。レーザーを用いてビアホールを形成する場合、レーザーがセラミック電子部品の外部電極に直接照射されることとなる。このため、外部電極は、レーザーを高い反射率で反射する Cu めっき膜を有するものであることが好ましい。外部電極のレーザー

10

20

30

40

50

ーに対する反射率が低いと、レーザーがセラミック電子部品の内部にまで至り、セラミック電子部品が損傷してしまう場合があるためである。

**【先行技術文献】**

**【特許文献】**

**【0005】**

【特許文献1】特開2002-100875号公報

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0006】**

ところで、配線基板の内部に埋め込まれるセラミック電子部品に対しては、配線基板の厚みを薄くする観点から、低背化が強く求められている。 10

**【0007】**

セラミック電子部品を低背化する方法としては、外部電極のうち、セラミック素体の直上に位置する下地電極層を、内部電極を含むセラミック素体と同時焼成する、すなわちコファイアにより形成することが好ましい。このようにすることにより、例えば、ディップにより塗布した導電性ペーストを焼き付けることによって下地電極層を形成した場合よりも、下地電極層の最大厚みを小さくできるためである。

**【0008】**

しかしながら、下地電極層をコファイアにより形成する場合、セラミック素体と下地電極層との高い密着性を確保するために、セラミック材料などのセラミック接合材の下地電極層における含有量を多くする必要がある。ところが、下地電極層におけるセラミック接合材の含有量を多くすると、下地電極層における金属成分の含有量が少なくなる。このため、下地電極層と、下地電極層の上に形成されためっき層との密着性が低下してしまう。従って、電子部品の信頼性が低下してしまうという問題がある。 20

**【0009】**

本発明は、かかる点に鑑みてなされたものであり、その目的は、セラミック素体の上に形成された下地電極層と、下地電極層の上に形成されたCuめっき膜とを有する外部電極を備えるセラミック電子部品であって、高い信頼性を有するセラミック電子部品を提供することにある。

**【課題を解決するための手段】**

**【0010】**

本発明に係るセラミック電子部品は、セラミック素体と、外部電極とを備えている。外部電極は、セラミック素体の上に形成されている。外部電極は、下地電極層と、第1のCuめっき膜とを有する。下地電極層は、セラミック素体の上に形成されている。第1のCuめっき膜は、下地電極層の上に形成されている。下地電極層は、Cuに拡散し得る金属と、セラミック結合材とを含む。第1のCuめっき膜の少なくとも下地電極層側の表層には、Cuに拡散し得る金属が拡散している。 30

**【0011】**

本発明に係るセラミック電子部品のある特定の局面では、前記下地電極層は、前記セラミック素体の上に導電性ペーストを塗布し、焼成することにより形成されている。 40

また、本発明に係るセラミック電子部品の他の特定の局面では、第1のCuめっき膜には、粒界が存在している。Cuに拡散し得る金属は、第1のCuめっき膜の粒界に沿って拡散している。

**【0012】**

本発明に係るセラミック電子部品の他の特定の局面では、Cuに拡散し得る金属は、第1のCuめっき膜の下地電極層とは反対側の表面にまで拡散している。この構成によれば、第1のCuめっき膜と下地電極層との密着性をより高めることができる。

**【0013】**

本発明に係るセラミック電子部品の別の特定の局面では、Cuに拡散し得る金属は、Ni, Ag, Pd及びAuからなる群から選ばれた一種以上の金属である。 50

**【0014】**

本発明に係るセラミック電子部品のさらに別の特定の局面では、外部電極は、第1のCuめっき膜の上に形成されている第2のCuめっき膜をさらに有し、第2のCuめっき膜には、Cuに拡散し得る金属は拡散していない。この構成では、Cuに拡散し得る金属が拡散していない第2のCuめっき膜が設けられているため、外部電極に入射するレーザー光の外部電極における反射率をより高くすることができる。このため、レーザー光を外部電極に照射した場合であっても、セラミック素体が損傷しにくい。従って、埋め込み型セラミック電子部品として好適に使用することができる。

**【0015】**

本発明に係るセラミック電子部品のまた他の特定の局面では、下地電極層には、第1のCuめっき膜からCuが拡散している。この場合、下地電極層と第1のCuめっき膜との密着性をより高めることができる。

10

**【0016】**

本発明に係るセラミック電子部品の製造方法は、セラミック素体と、セラミック素体の上に形成されている外部電極とを備えるセラミック電子部品の製造方法に関する。本発明に係るセラミック電子部品の製造方法では、セラミック素体の上に、Cuに拡散し得る金属と、セラミック結合材とを含む下地電極層を形成し、さらに下地電極層の上に第1のCuめっき膜を形成する。その後に、下地電極層と第1のCuめっき膜とを加熱することにより、第1のCuめっき膜の少なくとも下地電極層側の表層にCuに拡散し得る金属を拡散させることにより外部電極を形成する。

20

**【0017】**

本発明に係るセラミック電子部品の製造方法のある特定の局面では、下地電極層と第1のCuめっき層とを加熱することにより、第1のCuめっき膜の少なくとも下地電極層側の表層にCuに拡散し得る金属を拡散させた後に、第1のCuめっき膜の上に、第2のCuめっき膜をさらに形成することにより外部電極を形成する。この場合、Cuに拡散し得る金属が拡散していない第2のCuめっき膜が設けられているため、外部電極に入射するレーザー光の外部電極における反射率がより高く、埋め込み型セラミック電子部品として好適に使用することができるセラミック電子部品を製造することができる。

**【0018】**

本発明に係るセラミック電子部品の製造方法の他の特定の局面では、下地電極層と第1のCuめっき膜とを、350～800まで加熱することにより、第1のCuめっき膜の少なくとも下地電極層側の表層にCuに拡散し得る金属を拡散させることにより外部電極を形成する。この場合、Cuに拡散し得る金属がより好適に拡散する。

30

**【発明の効果】****【0019】**

本発明では、第1のCuめっき膜の少なくとも下地電極層側の表層には、下地電極層に含まれているCuに拡散し得る金属が拡散している。このため、下地電極層と第1のCuめっき膜との密着性を高めることができる。従って、セラミック電子部品の信頼性を高めることができる。

**【図面の簡単な説明】**

40

**【0020】**

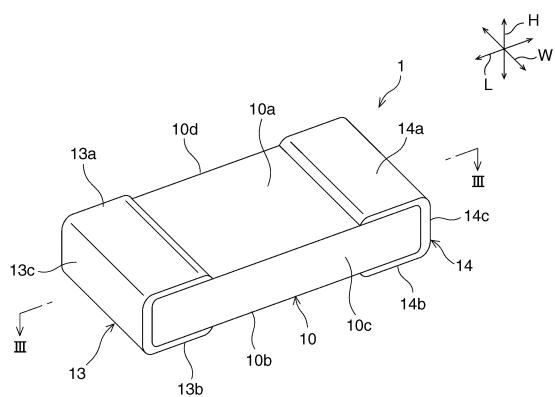

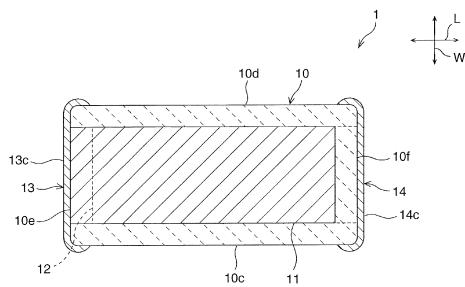

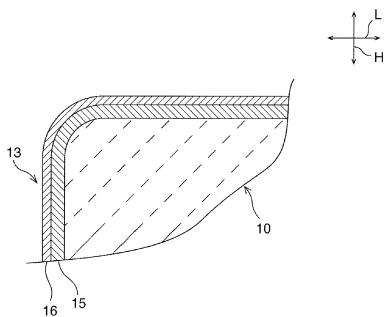

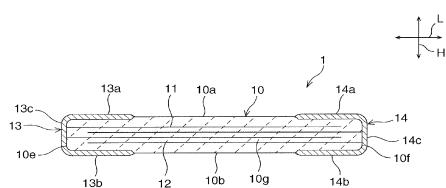

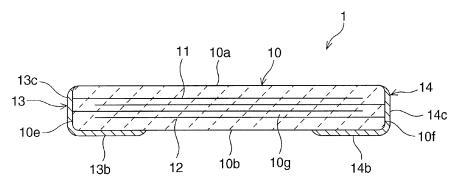

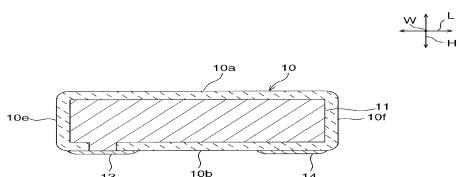

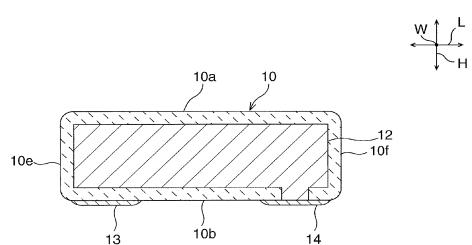

【図1】第1の実施形態に係るセラミック電子部品の略図的斜視図である。

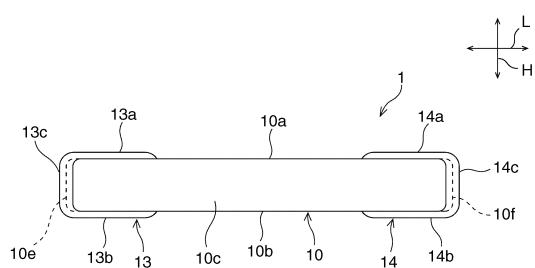

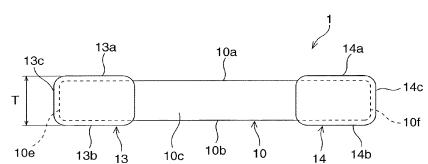

【図2】第1の実施形態に係るセラミック電子部品の略図的側面図である。

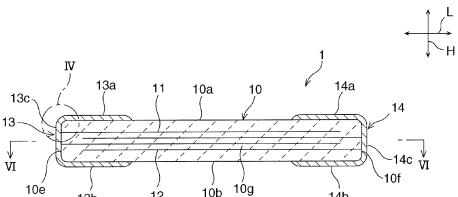

【図3】図1の線I—I—I—Iにおける略図的断面図である。

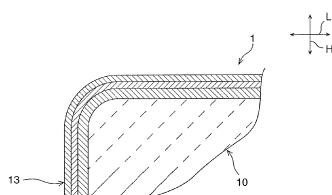

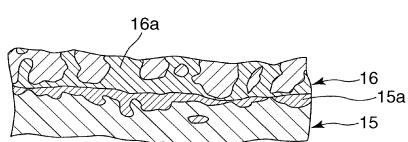

【図4】図3の線IVで囲まれた部分を拡大した略図的断面図である。

【図5】第1の外部電極の一部分を拡大した模式的断面図である。

【図6】図3の線VI-VIにおける略図的断面図である。

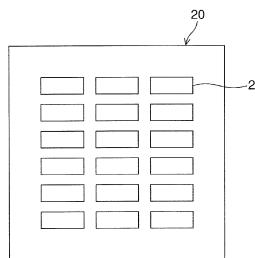

【図7】導電パターンが形成されたセラミックグリーンシートの略図的平面図である。

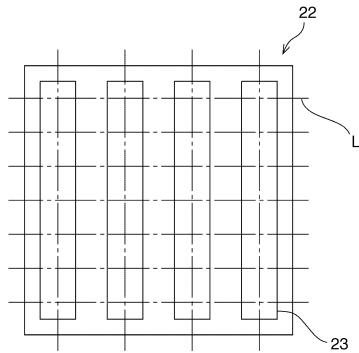

【図8】マザーリードの積層体の略図的平面図である。

【図9】第2の実施形態に係るセラミック電子部品の一部を拡大した略図的断面図である

50

。

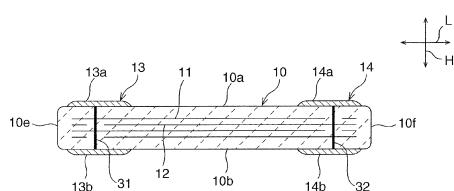

【図10】第3の実施形態に係るセラミック電子部品の略図的断面図である。

【図11】第4の実施形態に係るセラミック電子部品の略図的断面図である。

【図12】第5の実施形態に係るセラミック電子部品の略図的側面図である。

【図13】第6の実施形態に係るセラミック電子部品の略図的断面図である。

【図14】第7の実施形態に係るセラミック電子部品の高さ方向H及び長さ方向Lに沿った略図的断面図である。

【図15】第7の実施形態に係るセラミック電子部品の高さ方向H及び長さ方向Lに沿った略図的断面図である。

【図16】変形例における第1の外部電極の一部分を拡大した模式的断面図である。

10

【発明を実施するための形態】

【0021】

(第1の実施形態)

以下、本発明の好ましい実施形態について、図1に示すセラミック電子部品1を例に挙げて説明する。但し、セラミック電子部品1は、単なる例示である。本発明は、以下に示すセラミック電子部品1及びその製造方法に何ら限定されない。

【0022】

図1は、第1の実施形態に係るセラミック電子部品の略図的斜視図である。図2は、第1の実施形態に係るセラミック電子部品の略図的側面図である。図3は、図1の線I—I—I—Iにおける略図的断面図である。図4は、図3の線IVで囲まれた部分を拡大した略図的断面図である。図5は、第1の外部電極の一部分を拡大した模式的断面図である。図6は、図3の線VI—VIにおける略図的断面図である。

20

【0023】

まず、図1～図6を参照しながら、セラミック電子部品1の構成について説明する。

【0024】

図1～図3及び図6に示すように、セラミック電子部品1は、セラミック素体10を備えている。セラミック素体10は、セラミック電子部品1の機能に応じた適宜のセラミック材料からなる。具体的には、セラミック電子部品1がコンデンサである場合は、セラミック素体10を誘電体セラミック材料により形成することができる。誘電体セラミック材料の具体例としては、例えば、BaTiO<sub>3</sub>、CaTiO<sub>3</sub>、SrTiO<sub>3</sub>、CaZrO<sub>3</sub>などが挙げられる。なお、セラミック素体10には、所望するセラミック電子部品1の特性に応じて、上記セラミック材料を主成分として、例えば、Mn化合物、Mg化合物、Si化合物、Fe化合物、Cr化合物、Co化合物、Ni化合物、希土類化合物などの副成分を適宜添加してもよい。

30

【0025】

セラミック電子部品1がセラミック圧電素子である場合は、セラミック素体10を圧電セラミック材料により形成することができる。圧電セラミック材料の具体例としては、例えば、PZT(チタン酸ジルコン酸鉛)系セラミック材料などが挙げられる。

【0026】

セラミック電子部品1がサーミスタ素子である場合は、セラミック素体10を半導体セラミック材料により形成することができる。半導体セラミック材料の具体例としては、例えば、スピネル系セラミック材料などが挙げられる。

40

【0027】

セラミック電子部品1が、インダクタ素子である場合は、セラミック素体10を磁性体セラミック材料により形成することができる。磁性体セラミック材料の具体例としては、例えば、フェライトセラミック材料などが挙げられる。

【0028】

セラミック素体10の形状は特に限定されない。本実施形態では、セラミック素体10は、直方体状に形成されている。図1～図3に示すように、セラミック素体10は、長さ方向L及び幅方向Wに沿って延びる第1及び第2の主面10a、10bを有する。セラミ

50

ツク素体10は、図1、図2及び図6に示すように、高さ方向H及び長さ方向Lに沿って延びる第1及び第2の側面10c、10dを有する。また、図2、図3及び図6に示すように、高さ方向H及び幅方向Wに沿って延びる第1及び第2の端面10e、10fを備えている。

#### 【0029】

なお、本明細書において、「直方体状」には、角部や稜線部が面取り状またはR面取り状である直方体が含まれるものとする。すなわち、「直方体状」の部材とは、第1及び第2の正面、第1及び第2の側面並びに第1及び第2の端面とを有する部材全般を意味する。また、正面、側面、端面の一部または全部に凹凸などが形成されていてもよい。

#### 【0030】

セラミック素体10の寸法は、特に限定されないが、セラミック素体10は、セラミック素体10の厚み寸法をT、長さ寸法をL、幅寸法をWとしたときに、 $T \leq W < L$ 、 $(1/5)W \leq T \leq (1/2)W$ 、 $T \geq 0.3\text{ mm}$ が満たされるような薄型のものであることが好ましい。具体的には、 $0.1\text{ mm} \leq T \leq 0.3\text{ mm}$ 、 $0.4\text{ mm} \leq L \leq 1\text{ mm}$ 、 $0.2\text{ mm} \leq W \leq 0.5\text{ mm}$ であることが好ましい。

#### 【0031】

図3及び図6に示すように、セラミック素体10の内部には、略矩形状の複数の第1及び第2の内部電極11、12が高さ方向Hに沿って等間隔に交互に配置されている。第1及び第2の内部電極11、12のそれぞれは、第1及び第2の正面10a、10bと平行である。第1及び第2の内部電極11、12は、高さ方向Hにおいて、セラミック層10gを介して、互いに対向している。

#### 【0032】

なお、セラミック層10gの厚さは、特に限定されない。セラミック層10gの厚さは、例えば、 $0.5\text{ }\mu\text{m} \sim 10\text{ }\mu\text{m}$ 程度とすることができます。第1及び第2の内部電極11、12のそれぞれの厚さも、特に限定されない。第1及び第2の内部電極11、12のそれぞれの厚さは、例えば、 $0.2\text{ }\mu\text{m} \sim 2\text{ }\mu\text{m}$ 程度とすることができます。

#### 【0033】

第1及び第2の内部電極11、12は、適宜の導電材料により形成することができる。第1及び第2の内部電極11、12は、例えば、Ni、Cu、Ag、Pd、Auなどの金属や、Ag-Pd合金などの、これらの金属の一種以上を含む合金により形成することができる。

#### 【0034】

図1～図3に示すように、セラミック素体10の表面の上には、第1及び第2の外部電極13、14が形成されている。第1の外部電極13は、第1の内部電極11に電気的に接続されている。第1の外部電極13は、第1の正面10aの上に形成されている第1の部分13aと、第2の正面10bの上に形成されている第2の部分13bと、第1の端面10eの上に形成されている第3の部分13cとを備えている。本実施形態では、第1の外部電極13は、第1及び第2の側面10c、10dの上には実質的に形成されていない。

#### 【0035】

一方、第2の外部電極14は、第2の内部電極12に電気的に接続されている。第2の外部電極14は、第1の正面10aの上に形成されている第1の部分14aと、第2の正面10bの上に形成されている第2の部分14bと、第2の端面10fの上に形成されている第3の部分14cとを備えている。本実施形態では、第2の外部電極14は、第1及び第2の側面10c、10dの上には実質的に形成されていない。

#### 【0036】

次に、第1及び第2の外部電極13、14の構成について説明する。なお、本実施形態では、第1及び第2の外部電極13、14は、実質的に同じ膜構成を有する。このため、ここでは、第1及び第2の外部電極13、14の構成について、第1の外部電極13の一部分が描画されている図4を主として参照しながら説明する。

10

20

30

40

50

## 【0037】

図4に示すように、第1及び第2の外部電極13,14のそれぞれは、下地電極層15と、第1及び第2のCuめっき膜16,17との積層体により構成されている。下地電極層15は、セラミック素体10の上に形成されている。第1のCuめっき膜16は、下地電極層15の上に形成されている。第2のCuめっき膜17は、第1のCuめっき膜16の上に形成されている。

## 【0038】

下地電極層15は、第1及び第2の外部電極13,14と、セラミック素体10との密着強度を高めるための層である。このため、下地電極層15は、下地電極層15とセラミック素体10との密着強度が高くなると共に、下地電極層15と第1のCuめっき膜16との密着性も高くなるような組成を有する。具体的には、下地電極層15は、Cuに拡散し得る金属と、セラミック結合材とを含んでいる。10

## 【0039】

下地電極層15における、Cuに拡散し得る金属の含有量は、例えば、50体積%~70体積%の範囲内であることが好ましい。下地電極層15におけるセラミック結合材の含有量は、例えば、30体積%~50体積%の範囲内であることが好ましい。

## 【0040】

セラミック結合材は、セラミック素体10に対する密着強度を高めるための成分である。セラミック結合材は、例えば、セラミック素体が下地電極層と同時に焼成される際に、セラミック素体の収縮の挙動と下地電極層の収縮の挙動を近づけるようにして、その種類が選択される。セラミック結合材は、セラミック素体10に含まれるセラミック材料の主成分を構成する元素を含むことが好ましく、中でも、セラミック素体10に含まれるセラミック材料と主成分が同じセラミック材料であることが望ましい。20

## 【0041】

一方、Cuに拡散し得る金属（以下、「拡散可能金属」とすることがある。）は、第1のCuめっき膜16に対する密着強度を向上するための成分である。本実施形態では、この拡散可能金属が第1のCuめっき膜16の少なくとも下地電極層15側の表層に拡散している。また、下地電極層15には、第1のCuめっき膜16からCuが拡散している。本実施形態では、この相互拡散により、下地電極層15と第1のCuめっき膜16との高い密着性が実現されている。30

## 【0042】

より具体的には、本実施形態では、第1のCuめっき膜16には、粒界が存在しており、この粒界に沿って拡散可能金属が拡散している。そして、図5に示すように、第1のCuめっき膜16のうち、拡散可能金属が拡散している拡散部分16aは、第1のCuめっき膜16の下地電極層15とは反対側の表面にまで至っている。一方、下地電極層15の第1のCuめっき膜16側の表層には、Cuが拡散している拡散部分15aが存在している。

## 【0043】

なお、拡散可能金属が拡散していることは、セラミック電子部品1の側面をW方向の中心付近まで研磨し、反対側の側面と平行な断面を露出させ、その断面を集束イオンビーム（FIB）を用いて処理し、WDX（波長分散型）の元素マッピングすることにより検出することができる。40

## 【0044】

拡散可能金属の種類は特に限定されない。拡散可能金属は、例えば、Ni, Ag, Auからなる群から選ばれた一種以上の金属により構成することができる。なかでも、拡散可能金属としては、Niを用いることが好ましい。

## 【0045】

但し、本実施形態では、第2のCuめっき膜17には、拡散可能金属は拡散していない。このため、第2のCuめっき膜17は、Cuにより実質的に形成されている。

## 【0046】

50

20

30

40

50

なお、下地電極層15の最大厚みは、例えば、1μm～20μm程度とすることができる。第1のCuめっき膜16の最大厚みは、例えば、2μm～6μm程度であることが好ましい。第2のCuめっき膜17の最大厚みは、例えば、3μm～6μm程度であることが好ましい。

#### 【0047】

次に、本実施形態のセラミック電子部品1の製造方法の一例について説明する。

#### 【0048】

まず、セラミック素体10を構成するためのセラミック材料を含むセラミックグリーンシート20(図7を参照)を用意する。次に、図7に示すように、そのセラミックグリーンシート20の上に、導電性ペーストを塗布することにより、導電パターン21を形成する。なお、導電パターンの塗布は、例えば、スクリーン印刷法などの各種印刷法により行うことができる。導電性ペーストは、導電性微粒子の他に、公知のバインダーや溶剤を含んでいてもよい。

10

#### 【0049】

次に、導電パターン21が形成されていない複数枚のセラミックグリーンシート20、第1または第2の内部電極11、12に対応した形状の導電パターン21が形成されているセラミックグリーンシート20、及び導電パターン21が形成されていない複数枚のセラミックグリーンシート20をこの順番で積層し、積層方向に静水圧プレスすることにより、図8に示すマザー積層体22を作製する。

#### 【0050】

20

次に、マザー積層体22の上に、第1及び第2の外部電極13、14の下地電極層15の第1及び第2の部分13a、13bを構成している部分に対応した形状の導電パターン23を、スクリーン印刷法などの適宜の印刷法により形成する。なお、この導電パターン23の形成に用いる導電性ペーストは、拡散可能金属と、セラミック結合材とを含んでいる。

#### 【0051】

次に、仮想のカットラインLに沿ってマザー積層体22をカッティングすることにより、マザー積層体22から複数の生のセラミック積層体を作製する。なお、マザー積層体22のカッティングは、ダイシングや押切により行うことができる。

#### 【0052】

30

生のセラミック積層体作成後、バレル研磨などにより、生のセラミック積層体の稜線部及び稜線部の面取りまたはR面取り及び表層の研磨を行うようにしてもよい。

#### 【0053】

次に、生のセラミック積層体の両端面に導電性ペーストを塗布することにより第1及び第2の外部電極13、14の下地電極層15の第3の部分13cを構成している部分に対応した形状の導電パターンを形成する。この導電性ペーストの塗布は、例えば、ディップやスクリーン印刷などにより行うことができる。なお、この導電パターンの形成に用いる導電性ペーストは、拡散可能金属と、セラミック結合材とを含んでいる。

#### 【0054】

40

次に、生のセラミック積層体の焼成を行う。この焼成工程において、下地電極層15並びに第1及び第2の内部電極11、12が同時焼成される(コファイア)。焼成温度は、使用するセラミック材料や導電性ペーストの種類により適宜設定することができる。焼成温度は、例えば、900～1300程度とすることができます。

#### 【0055】

次に、下地電極層15の上にCuめっきを施すことにより、第1のCuめっき膜16を形成する。本実施形態では、その後、セラミック積層体に熱処理を施すことにより、第1のCuめっき膜16と下地電極層15とを加熱する。この加熱工程により、第1のCuめっき膜16の少なくとも下地電極層15側の表層に、下地電極層15に含まれていた拡散可能金属が拡散する。それと共に、第1のCuめっき膜16のCuが下地電極層15の少なくとも第1のCuめっき膜16側の表層に拡散する。すなわち、下地電極層15と第1

50

のCuめっき膜16との間で、相互拡散が進行する。

#### 【0056】

第1のCuめっき膜16と下地電極層15との熱処理工程において、第1のCuめっき膜16と下地電極層15とを350～800まで加熱することが好ましく、550～650まで加熱することがより好ましい。第1のCuめっき膜16と下地電極層15との加熱温度が低すぎると、十分に拡散が進行しない場合がある。一方、第1のCuめっき膜16と下地電極層15との加熱温度が高すぎると、第1のCuめっき膜16に含まれるCuが融解してしまう場合がある。

#### 【0057】

上記熱処理工程は、窒素やアルゴンなどの不活性ガス雰囲気中で行うことが好ましい。10

これにより、第1のCuめっき膜16等の酸化を抑制することができる。

#### 【0058】

その後、第1のCuめっき膜16の上に、Cuめっきにより、第2のCuめっき膜17を形成することにより、図1に示すセラミック電子部品1を完成させる。このように、本実施形態では、第1のCuめっき膜16及び下地電極層15の熱処理後に第2のCuめっき膜17を形成する。このため、第1のCuめっき膜16には拡散可能金属が拡散するものの、第2のCuめっき膜17には拡散可能金属が実質的に拡散しない。従って、第2のCuめっき膜17は、実質的にCuからなるものとなる。

#### 【0059】

以上説明したように、本実施形態では、コファイアにより下地電極層15を形成する。20

このため、第1及び第2の外部電極13, 14の第1及び第2の部分13a, 14a, 13b, 14bを薄く形成することができる。従って、セラミック電子部品1の厚みを薄くすることができる。

#### 【0060】

また、下地電極層15は、セラミック結合材を含んでいる。このため、下地電極層15をコファイアにより形成した場合であっても、下地電極層15とセラミック素体10との密着性を高めることができる。

#### 【0061】

さらに、下地電極層15は、Cuに拡散し得る金属を含んでおり、そのCuに拡散し得る金属が、第1のCuめっき膜16の少なくとも下地電極層15側の表層に拡散している。30

このため、下地電極層15と第1のCuめっき膜16との密着性を高めることができる。特に、Cuに拡散し得る金属が、第1のCuめっき膜16の下地電極層15とは反対側の表面にまで拡散している場合は、下地電極層15と第1のCuめっき膜16との密着性をさらに高めることができる。

#### 【0062】

また、本実施形態では、第1のCuめっき膜16の上に、実質的にCuからなる第2のCuめっき膜17が形成されている。このため、第1及び第2の外部電極13, 14にレーザー光を照射した場合であっても、レーザー光が高い反射率で第1及び第2の外部電極13, 14において反射される。従って、第1及び第2の外部電極13, 14にレーザー光を照射した場合であっても、セラミック素体10が損傷しにくい。すなわち、本実施形態のセラミック電子部品1は、レーザー光に対する耐性が高い。40

#### 【0063】

このように、本実施形態では、セラミック電子部品1の厚みを薄くでき、セラミック素体10、下地電極層15及び第1のCuめっき膜16間の密着性を高めることができ、かつ、第1及び第2の外部電極13, 14におけるレーザー光の反射率を高くすることができます。従って、本実施形態の高い信頼性を有するセラミック電子部品1は、埋め込み型のセラミック電子部品として好適に使用される。本実施形態のセラミック電子部品1を埋め込み型のセラミック電子部品として用いた場合、レーザー光を用いて、セラミック電子部品1の第1及び第2の外部電極13, 14の上部にピアホールを、セラミック電子部品1を損傷させることなく、好適に形成することができる。50

## 【0064】

また、本実施形態では、セラミック電子部品が、少なくとも一対の内部電極と、第1及び第2の外部電極を備えている例について説明した。但し、本発明は、この構成に限定されない。本発明において、セラミック電子部品は、少なくとも一つの外部電極を有していればよく、例えば、内部電極を有していないなくてもよい。

## 【0065】

以下、本発明の好ましい実施形態の他の例について説明する。但し、以下の説明において、上記第1の実施形態と実質的に共通の機能を有する部材を共通の機能で参照し、説明を省略する。

## 【0066】

10

## (第2の実施形態)

図9は、第2の実施形態に係るセラミック電子部品の一部を拡大した略図的断面図である。

## 【0067】

上記第1の実施形態では、第1及び第2の外部電極13, 14が、下地電極層15並びに第1及び第2のCuめっき膜16, 17の積層体により形成されている例について説明した。但し、本発明は、この構成に限定されない。外部電極は、下地電極層と、下地電極層の上に積層された少なくとも一つのCuめっき膜を有する限りにおいて特に限定されない。

## 【0068】

20

例えば、図9に示すように、第1及び第2の外部電極13, 14のそれぞれは、下地電極層15と、下地電極層15の上に形成されている第1のCuめっき膜16との積層体により形成されていてもよい。この場合、下地電極層15に含まれている拡散可能金属は、第1のCuめっき膜16の下地電極層15とは反対側の表面にまで拡散していないことが好ましい。すなわち、第1のCuめっき膜16の下地電極層15とは反対側の表層は、Cuからなることが好ましい。

## 【0069】

但し、第1のCuめっき膜16の下地電極層15とは反対側の表面にまで拡散可能金属が拡散しないように制御するのは困難である。このため、第1及び第2の外部電極13, 14のセラミック素体10とは反対側の表層を、確実にCuからなるものとするためには、第2のCuめっき膜16を形成することが好ましい。

30

## 【0070】

## (第3の実施形態)

図10は、第3の実施形態に係るセラミック電子部品の略図的断面図である。

## 【0071】

上記第1の実施形態では、第1及び第2の主面10a, 10bのうち、第1または第2の外部電極13, 14が形成されている部分と、第1または第2の外部電極13, 14が形成されていない部分とが面一に形成されている例について説明した。但し、本発明はこの構成に限定されない。第1及び第2の主面10a, 10bのうち、第1または第2の外部電極13, 14が形成されている部分と、第1または第2の外部電極13, 14が形成されていない部分とは、面一でなくてもよい。

40

## 【0072】

例えば、図10に示すように、第1及び第2の主面10a, 10bのうち、第1または第2の外部電極13, 14が形成されている部分は、第1または第2の外部電極13, 14が形成されていない部分よりも高さ方向Hにおける内側に位置していてもよい。この場合は、セラミック電子部品1をより低背化することができる。

## 【0073】

## (第4の実施形態)

図11は、第4の実施形態に係るセラミック電子部品の略図的断面図である。

## 【0074】

50

上記第1の実施形態では、第1及び第2の外部電極13, 14のそれぞれが、第1及び第2の主面10a、10bの両方の上に形成されている例について説明した。但し、本発明は、この構成に限定されない。第1及び第2の外部電極13, 14のそれぞれは、セラミック素体10の表面のいずれかの部分の上に形成されればよい。

#### 【0075】

例えば、図11に示すように、第1及び第2の外部電極13, 14のそれぞれを、第1及び第2の主面10a、10bのうちの第2の主面10bの上にのみ形成してもよい。このように、第1及び第2の外部電極13, 14のそれを、第1及び第2の主面10a、10bのうちの少なくとも一方の上に形成することにより、セラミック電子部品1の実装容易性を高めることができる。

10

#### 【0076】

##### (第5の実施形態)

図12は、第5の実施形態に係るセラミック電子部品の略図的側面図である。

#### 【0077】

上記第1の実施形態では、第1及び第2の側面10c、10d上には、第1及び第2の外部電極13, 14が実質的に形成されない例について説明した。但し、図12に示すように、第1及び第2の外部電極13, 14を、第1及び第2の側面10c、10d上にも形成してもよい。

#### 【0078】

##### (第6の実施形態)

20

図13は、第6の実施形態に係るセラミック電子部品の略図的断面図である。

#### 【0079】

上記第1の実施形態では、第1及び第2の内部電極11, 12を第1または第2の端面10e、10fに引き出すと共に、第1及び第2の端面10e、10fの上に、第1または第2の外部電極13, 14を形成することにより、第1及び第2の内部電極11, 12を第1または第2の外部電極13, 14と電気的に接続する例について説明した。但し、本発明は、この構成に限定されない。

#### 【0080】

例えば、図13に示すように、ピアホール電極31, 32を形成し、第1及び第2の内部電極11, 12を第1及び第2の主面10a、10bに引き出し、第1及び第2の主面10a、10bにおいて、第1及び第2の外部電極13, 14と電気的に接続させてもよい。この場合は、第1及び第2の外部電極13, 14は、第1及び第2の主面10a、10bの少なくとも一方に形成されればよく、第1及び第2の側面10c、10dや第1及び第2の端面10e、10fの上には、第1及び第2の外部電極13, 14は、必ずしも形成されなくてよい。

30

#### 【0081】

##### (第7の実施形態)

図14及び図15は、第7の実施形態に係るセラミック電子部品の高さ方向H及び長さ方向Lに沿った略図的断面図である。

#### 【0082】

40

上記第1の実施形態では、第1及び第2の内部電極11, 12が、第1及び第2の主面10a、10bと平行に形成されており、かつ、第1または第2の端面10e、10fに引き出されている例について説明した。但し、本発明は、この構成に限定されない。

#### 【0083】

例えば、図14及び図15に示すように、第1及び第2の内部電極11, 12を高さ方向H及び長さ方向Lに沿って平行に形成し、第1及び第2の内部電極11, 12を幅方向Wに沿って積層するようにしてもよい。この場合は、第1及び第2の内部電極11, 12を第1及び第2の主面10a、10bの少なくとも一方に直接引き出して、第1及び第2の主面10a、10bの少なくとも一方の上に形成されている第1または第2の外部電極13, 14に直接接続するようにしてもよい。

50

## 【0084】

(変形例)

図16は、変形例における第1の外部電極の一部分を拡大した模式的断面図である。

## 【0085】

上記第1の実施形態では、図5に示すように、拡散部分16aが第1のCuめっき膜16の下地電極層15とは反対側の表面にまで至っている例について説明した。但し、本発明は、この構成に限定されない。例えば、図16に示すように、拡散部分16aが第1のCuめっき膜16の下地電極層15とは反対側の表面にまで至っていなくてもよい。

## 【0086】

(実施例1)

10

本実施例では、上記第1の実施形態に係るセラミック電子部品1と同様の構成を有する、セラミックコンデンサとしてのセラミック電子部品を、上記第1の実施形態で説明した製造方法で、以下の条件に基づいて作製した。

## 【0087】

セラミック電子部品の寸法：1.0mm×0.5mm×0.15mm

セラミック電子部品の容量：10nF

セラミック電子部品の定格電圧：6.3V

セラミック素体を構成するセラミック材料の主成分：BaTiO<sub>3</sub>

下地電極層：Cuに拡散し得る金属として、Niを50体積%含む。また、セラミック結合材を50体積%含む。

20

## 【0088】

下地電極層の形成条件：1200で2時間焼成

下地電極層の厚み：5μm

第1のCuめっき膜の厚み：4μm

第2のCuめっき膜の厚み：4μm

第1のCuめっき膜にNiを拡散させる熱処理の条件：600（最高温度）で10分保持、総熱処理時間：1時間、雰囲気は、酸素濃度10ppm以下の不活性ガス雰囲気

## 【0089】

上記作製のセラミック電子部品の側面をW方向の中心付近まで研磨し、反対側の側面と平行な断面を露出させ、その断面を収束イオンビーム(FIB)を用いて処理し、WDX(波長分散型)の元素マッピングを行うことにより、第1のCuめっき膜にNiが拡散していることを確認した。

30

## 【0090】

(比較例1)

第1のCuめっき膜にNiを拡散させる熱処理を行わなかったこと以外は、上記実施例1と同様にしてセラミック電子部品を作製した。

## 【0091】

上記作製のセラミック電子部品を切断することにより、外部電極の断面を露出させ、電子顕微鏡を用いて観察した結果、第1のCuめっき膜にNiが拡散していないことを確認した。

40

## 【0092】

(テープ剥離試験)

上記実施例1及び比較例1のそれぞれで作製したセラミック電子部品の第2の正面側を導電性接着剤を用いてガラスエポキシ基板に接着した。その後、セラミック電子部品の第1の正面側に粘着テープ(積水化学社製セロテープ(登録商標)No.252)を貼り付け、セラミック電子部品の長さ方向に沿って、一定の張力で引っ張ることにより剥離させた(180°剥離試験)。その後、電子顕微鏡を用いてめっき膜に剥がれが生じているか否かを観察した。この試験を、実施例1及び比較例1につき、各100サンプルを行い、めっき膜に剥離が観察されたサンプルの割合を測定した。その結果、実施例1では、いずれのサンプルにおいても剥離は観察されなかった。それに対して、比較例1では、75%の

50

サンプルで剥離が観察された。

**【0093】**

この結果から、第1のCuめっき膜に下地電極層に含まれていた金属を拡散させることにより、第1のCuめっき膜の密着強度を高めることができることが分かる。

**【0094】**

(剪断試験)

上記実施例1及び比較例1のそれぞれで作製したセラミック電子部品の第2の主面側を導電性接着剤を用いてガラスエポキシ基板に接着した。その後、荷重治具を用いてセラミック電子部品の長さ方向両側から0.5mm/秒で外部電極が剥離するまで荷重を加えた。

10

**【0095】**

その結果、比較例1では、Cuめっき膜の剥離が観察されたが、実施例1では、セラミック素体が破壊されるまで試験を継続してもCuめっき膜の剥離は観察されなかった。

**【0096】**

この結果からも、第1のCuめっき膜に下地電極層に含まれていた金属を拡散させることにより、第1のCuめっき膜の密着強度を高めることができることが分かる。

**【0097】**

(耐湿負荷試験)

実施例1及び比較例1のそれぞれにおいて作製したセラミック電子部品のサンプル各2個を、共晶半田を用いてガラスエポキシ基板に実装した。その後、サンプルを、85、相対湿度83%RHの高温高湿槽内にて、6.3Vの電圧を1000時間印加した。この耐湿負荷試験後のサンプルの絶縁抵抗値が、10G以下となったものを不良としてカウントした。その結果、実施例1では、72個のサンプルのうち、不良と判定されたサンプルは、0個であった。一方、比較例1では、72個のサンプルのうち、30個のサンプルが不良と判定された。

20

**【0098】**

この結果から、第1のCuめっき膜に下地電極層に含まれていた金属を拡散させることにより、セラミック電子部品の耐湿性を改善できることは分かる。

**【符号の説明】**

**【0099】**

30

1 ... セラミック電子部品

1 0 ... セラミック素体

1 0 a ... セラミック素体の第1の主面

1 0 b ... セラミック素体の第2の主面

1 0 c ... セラミック素体の第1の側面

1 0 d ... セラミック素体の第2の側面

1 0 e ... セラミック素体の第1の端面

1 0 f ... セラミック素体の第2の端面

1 0 g ... セラミック層

1 1 ... 第1の内部電極

40

1 2 ... 第2の内部電極

1 3 ... 第1の外部電極

1 3 a ... 第1の外部電極の第1の部分

1 3 b ... 第1の外部電極の第2の部分

1 3 c ... 第1の外部電極の第3の部分

1 4 ... 第2の外部電極

1 4 a ... 第2の外部電極の第1の部分

1 4 b ... 第2の外部電極の第2の部分

1 4 c ... 第2の外部電極の第3の部分

1 5 ... 下地電極層

50

- 1 5 a ... 粒界

1 6 ... 第 1 の Cu めっき膜

1 7 ... 第 2 の Cu めっき膜

2 0 ... セラミックグリーンシート

2 1 ... 導電パターン

2 2 ... マザー積層体

2 3 ... 導電パターン

3 1 , 3 2 ... ピアホール電極

【図 1】

【図 2】

【図 3】

【図 4】

【図 5】

【図 6】

【図 7】

【図 8】

【図 9】

【図 10】

【図 13】

【図 11】

【図 14】

【図 12】

【図 15】

【図 16】

---

フロントページの続き

(51)Int.Cl.

F I

H 01G 4/30 301B

H 01G 4/30 311E

(72)発明者 松本 誠一

京都府長岡市東神足1丁目10番1号 株式会社村田製作所内

審査官 田中 晃洋

(56)参考文献 特開2010-034225 (JP, A)

特開2009-295687 (JP, A)

特開2008-072072 (JP, A)

特開平08-264371 (JP, A)

特開平08-264372 (JP, A)

特開平07-057959 (JP, A)

特開2002-231569 (JP, A)

特開2010-034503 (JP, A)

特開2010-016306 (JP, A)

特開平11-087167 (JP, A)

特開2002-008938 (JP, A)

特開2007-043144 (JP, A)

特開2009-212298 (JP, A)

特開2005-109125 (JP, A)

特開2002-203734 (JP, A)

国際公開第2008/059666 (WO, A1)

特開2000-100647 (JP, A)

特公昭55-035845 (JP, B1)

特開2010-267687 (JP, A)

特開2008-227515 (JP, A)

特開平5-343259 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01C 7/02 - 7/22

H 01F 17/00 - 21/12

H 01F 27/00

H 01F 27/02

H 01F 27/06

H 01F 27/08

H 01F 27/23

H 01F 27/29

H 01F 27/36

H 01F 27/42

H 01F 30/00

H 01F 38/42

H 01G 4/00 - 4/22

H 01G 4/228 - 4/40

H 01G 13/00 - 17/00