(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7149275号**

**(P7149275)**

(45)発行日 令和4年10月6日(2022.10.6)

(24)登録日 令和4年9月28日(2022.9.28)

(51)国際特許分類

|         |                 |     |         |              |

|---------|-----------------|-----|---------|--------------|

| H 0 4 N | 5/3745(2011.01) | F I | H 0 4 N | 5/3745 2 0 0 |

| H 0 1 L | 31/10 (2006.01) |     | H 0 1 L | 31/10 G      |

| H 0 4 N | 5/372(2011.01)  |     | H 0 1 L | 31/10 A      |

| G 0 1 J | 1/02 (2006.01)  |     | H 0 4 N | 5/372        |

| H 0 1 L | 27/146(2006.01) |     | G 0 1 J | 1/02 B       |

請求項の数 37 (全44頁) 最終頁に続く

(21)出願番号 特願2019-534096(P2019-534096)

(86)(22)出願日 平成29年12月22日(2017.12.22)

(65)公表番号 特表2020-504507(P2020-504507)

A)

(43)公表日 令和2年2月6日(2020.2.6)

(86)国際出願番号 PCT/US2017/068089

(87)国際公開番号 WO2018/119347

(87)国際公開日 平成30年6月28日(2018.6.28)

審査請求日 令和2年12月21日(2020.12.21)

(31)優先権主張番号 62/438,051

(32)優先日 平成28年12月22日(2016.12.22)

(33)優先権主張国・地域又は機関

米国(US)

(73)特許権者 516144164

クアンタム - エスアイ インコーポレイ

テッド

QUANTUM - S I INCORPO

RATED

アメリカ合衆国 06437 コネチカッ

ト州 ギルフォード オールド ウィット

フィールド ストリート 530

(74)代理人 100105957

弁理士 恩田 誠

(74)代理人 100068755

弁理士 恩田 博宣

(74)代理人 100142907

弁理士 本田 淳

(72)発明者 ロスバーグ、ジョナサン エム.

最終頁に続く

(54)【発明の名称】 直接ビニングピクセルを備える集積光検出器

**(57)【特許請求の範囲】****【請求項1】**

入射光子を受け取るように構成された光検出領域であって、前記入射光子に応答して複数の電荷キャリアを生成するように構成された光検出領域と、

少なくとも1つの電荷キャリア貯蔵領域と、

前記複数の電荷キャリアのうちの電荷キャリアを、前記電荷キャリアが生成された時間に基づいて、前記少なくとも1つの電荷キャリア貯蔵領域内へ直接方向付けするべく、選択的に方向付けするように、また複数の励起光パルスに応答して生成された電荷キャリアを前記少なくとも1つの電荷キャリア貯蔵領域に集約するように構成された電荷キャリア分離構造と、を備える集積回路。

**【請求項2】**

直接ビニングピクセルを備える集積回路であって、前記直接ビニングピクセルは、

入射光子を受け取るように構成された光検出領域であって、前記入射光子に応答して複数の電荷キャリアを生成するように構成された光検出領域と、

少なくとも1つの電荷キャリア貯蔵領域と、

前記複数の電荷キャリアのうちの電荷キャリアを、前記電荷キャリアが生成された時間に基づいて、前記少なくとも1つの電荷キャリア貯蔵領域内へ選択的に方向付けするように、また複数の励起光パルスに応答して生成された電荷キャリアを前記少なくとも1つの電荷キャリア貯蔵領域に集約するように構成された電荷キャリア分離構造と、を備える、集積回路。

**【請求項 3】**

複数のピクセルを備える集積回路であって、前記複数のピクセルのうちの第1のピクセルは、

入射光子を受け取るように構成された光検出領域であって、前記入射光子に応答して複数の電荷キャリアを生成するように構成された光検出領域と、

複数の電荷キャリア貯蔵領域と、

前記複数の電荷キャリアのうちの電荷キャリアを、前記電荷キャリアが生成された時間に基づいて、前記複数の電荷キャリア貯蔵領域のそれぞれの電荷キャリア貯蔵領域内へ直接方向付けするべく、選択的に方向付けするように、また複数の励起光パルスに応答して生成された電荷キャリアを前記複数の電荷キャリア貯蔵領域に集約するように構成された電荷キャリア分離構造と、二を備える直接ビニングピクセルである集積回路。

10

**【請求項 4】**

前記電荷キャリア分離構造は、前記光検出領域と前記少なくとも1つの電荷キャリア貯蔵領域のうちの第1の電荷キャリア貯蔵領域との間の境界に少なくとも1つの電極を備える、請求項1～3のいずれか一項に記載の集積回路。

**【請求項 5】**

前記電荷キャリア分離構造は、前記光検出領域と前記第1の電荷キャリア貯蔵領域との間の前記境界に单一の電極を備える、請求項4に記載の集積回路。

**【請求項 6】**

電荷キャリア捕獲領域が前記直接ビニングピクセルに存在しないか、電荷キャリア捕獲領域が前記光検出領域と電荷キャリア貯蔵領域との間に存在しないか、またはその両方である、請求項2または3に記載の集積回路。

20

**【請求項 7】**

前記光検出領域と前記少なくとも1つの電荷キャリア貯蔵領域との間ににおいて前記キャリアを捕獲することなく、電荷キャリアが前記少なくとも1つの電荷キャリア貯蔵領域に対し移送される、請求項1～6のいずれか一項に記載の集積回路。

**【請求項 8】**

電荷キャリア除去領域が、除去期間中に前記光検出領域において生成された電荷キャリアを廃棄する、請求項1～7のいずれか一項に記載の集積回路。

**【請求項 9】**

廃棄された前記電荷キャリアは、キャリアが前記光検出領域から電荷キャリア貯蔵領域に向かって方向付けされる方向とは異なる方向において前記光検出領域から取り除かれる、請求項8に記載の集積回路。

30

**【請求項 10】**

電荷キャリア除去領域が、前記光検出領域と前記電荷キャリア除去領域との間の境界における電極の電圧を変化させることによって、除去期間中に前記光検出領域において生成された電荷キャリアを廃棄する、請求項8に記載の集積回路。

**【請求項 11】**

単一光子が、前記少なくとも1つの電荷キャリア貯蔵領域に対し移送され、前記少なくとも1つの電荷キャリア貯蔵領域に集約される、請求項1～10のいずれか一項に記載の集積回路。

40

**【請求項 12】**

半導体基板の表面の下において1マイクロメートルよりも深い位置にある電荷キャリアは除去される、請求項1～11のいずれか一項に記載の集積回路。

**【請求項 13】**

前記半導体基板の表面の下において1マイクロメートルよりも深い位置にある電荷キャリアは、前記光検出領域のフォトダイオードの下のインプラントによって少なくとも部分的に除去される、請求項12に記載の集積回路。

**【請求項 14】**

前記インプラントは深部遮蔽体または深部ドレインを提供する、請求項13に記載の集

50

積回路。

**【請求項 15】**

前記インプラントはN型またはP+型である、請求項14に記載の集積回路。

**【請求項 16】**

前記半導体基板の表面の下において1マイクロメートルよりも深い位置にある電荷キャリアは、前記半導体基板の前記表面の下のドリフトの場によって除去される、請求項12または13に記載の集積回路。

**【請求項 17】**

前記光検出領域は、2マイクロメートル未満の深さであるエピタキシャル領域に形成されている、請求項1～3のいずれか一項に記載の集積回路。

10

**【請求項 18】**

前記光検出領域は、フォトダイオードを含むエピタキシャル領域である、請求項1～17のいずれか一項に記載の集積回路。

**【請求項 19】**

前記フォトダイオードにおける電荷キャリアは除去期間中に除去領域に対して移送され、次いで第1の電荷キャリア貯蔵領域に対する第1の電位障壁が低下され、次いで第2の電荷キャリア貯蔵領域に対する第2の電位障壁が低下される、請求項13または18に記載の集積回路。

**【請求項 20】**

前記第1の電位障壁は第1の電極によって制御され、前記第2の電位障壁は第2の電極によって制御される、請求項19に記載の集積回路。

20

**【請求項 21】**

前記少なくとも1つの電荷キャリア貯蔵領域は、複数の電荷キャリア貯蔵領域を含む、請求項1～20のいずれか一項に記載の集積回路。

**【請求項 22】**

(A) 直接ビニングピクセルの光検出領域において入射光子を受け取る工程と、

(B) 前記入射光子に応答して生成された複数の電荷キャリアのうちの電荷キャリアを、前記電荷キャリアが生成された時間に基づいて、前記光検出領域から直接、前記直接ビニングピクセルの少なくとも1つの電荷キャリア貯蔵領域内へ選択的に方向付けし、複数の励起光パルスに応答して生成された電荷キャリアを前記少なくとも1つの電荷キャリア貯蔵領域に集約する工程と、を備える光検出方法。

30

**【請求項 23】**

電荷キャリア捕獲領域が前記直接ビニングピクセルに存在しないか、電荷キャリア捕獲領域が前記光検出領域と電荷キャリア貯蔵領域との間に存在しないか、またはその両方である、請求項22に記載の光検出方法。

**【請求項 24】**

前記光検出領域と前記少なくとも1つの電荷キャリア貯蔵領域との間ににおいて前記キャリアを捕獲することなく、電荷キャリアが前記少なくとも1つの電荷キャリア貯蔵領域に対し移送される、請求項22または23に記載の光検出方法。

40

**【請求項 25】**

電荷キャリア除去領域が、除去期間中に前記光検出領域において生成された電荷キャリアを廃棄する、請求項22～24のいずれか一項に記載の光検出方法。

**【請求項 26】**

廃棄された前記電荷キャリアは、キャリアが前記光検出領域から電荷キャリア貯蔵領域に向かって方向付けされる方向とは異なる方向において前記光検出領域から取り除かれる、請求項25に記載の光検出方法。

**【請求項 27】**

電荷キャリア除去領域が、前記光検出領域と前記電荷キャリア除去領域との間の境界における電極の電圧を変化させることによって、除去期間中に前記光検出領域において生成された電荷キャリアを廃棄する、請求項25に記載の光検出方法。

50

**【請求項 2 8】**

単一光子が、前記少なくとも 1 つの電荷キャリア貯蔵領域に対し移送され、前記少なくとも 1 つの電荷キャリア貯蔵領域に集約される、請求項 2 2 ~ 2 7 のいずれか一項に記載の光検出方法。

**【請求項 2 9】**

半導体基板の表面の下において 1 マイクロメートルよりも深い位置にある電荷キャリアは除去される、請求項 2 2 ~ 2 8 のいずれか一項に記載の光検出方法。

**【請求項 3 0】**

前記半導体基板の表面の下において 1 マイクロメートルよりも深い位置にある電荷キャリアは、前記光検出領域のフォトダイオードの下のインプラントによって少なくとも部分的に除去される、請求項 2 9 に記載の光検出方法。 10

**【請求項 3 1】**

前記インプラントは深部遮蔽体または深部ドレインを提供する、請求項 3 0 に記載の光検出方法。

**【請求項 3 2】**

前記インプラントは N 型または P + 型である、請求項 3 1 に記載の光検出方法。

**【請求項 3 3】**

前記半導体基板の表面の下において 1 マイクロメートルよりも深い位置にある電荷キャリアは、前記半導体基板の前記表面の下のドリフトの場によって除去される、請求項 2 9 または 3 0 に記載の光検出方法。 20

**【請求項 3 4】**

前記光検出領域は、フォトダイオードを含むエピタキシャル領域である、請求項 2 2 ~ 3 3 のいずれか一項に記載の光検出方法。

**【請求項 3 5】**

前記フォトダイオードにおける電荷キャリアは除去期間中に除去領域に対して移送され、次いで第 1 の電荷キャリア貯蔵領域に対する第 1 の電位障壁が低下され、次いで第 2 の電荷キャリア貯蔵領域に対する第 2 の電位障壁が低下される、請求項 3 0 または 3 4 に記載の光検出方法。

**【請求項 3 6】**

前記第 1 の電位障壁は第 1 の電極によって制御され、前記第 2 の電位障壁は第 2 の電極によって制御される、請求項 3 5 に記載の光検出方法。 30

**【請求項 3 7】**

前記少なくとも 1 つの電荷キャリア貯蔵領域は、複数の電荷キャリア貯蔵領域を含む、請求項 2 2 ~ 3 6 のいずれか一項に記載の光検出方法。

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

本開示は、直接ビニングピクセルを備える集積光検出器に関する。

**【背景技術】****【0 0 0 2】**

光検出器は、様々な用途において光を検出するために使用されている。入射光の強度を示す電気信号を生成する集積光検出器が開発されている。イメージング用途の集積光検出器は、シーン全体から受け取られた光の強度を検出するためのピクセルのアレイを含む。集積光検出器の例は、電荷結合素子 ( C C D ) および相補型金属酸化膜半導体 ( C M O S ) 画像センサを含む。 40

**【図面の簡単な説明】****【0 0 0 3】**

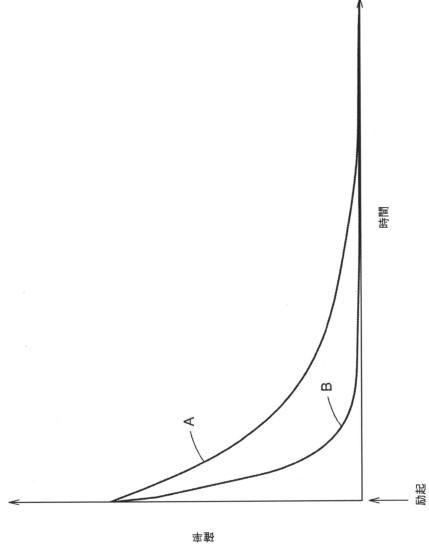

【図 1 A】異なる寿命を有する 2 つのマーカについて時間の関数として光子の放出される確率をプロットする図。

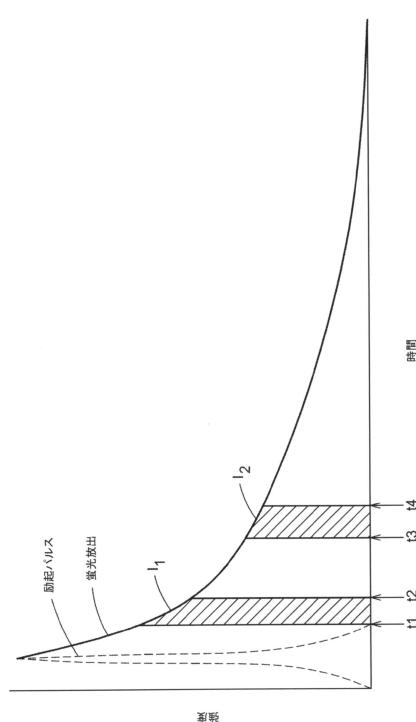

【図 1 B】例示的な励起パルス（点線）および例示的な蛍光放出（実線）の例示的な強度

10

20

30

40

50

プロファイルを経時的に示す図。

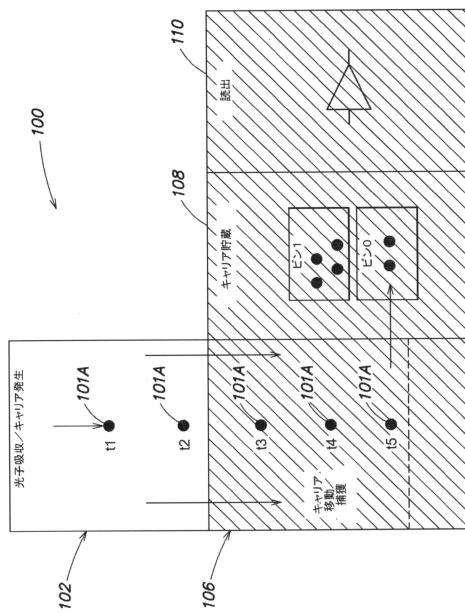

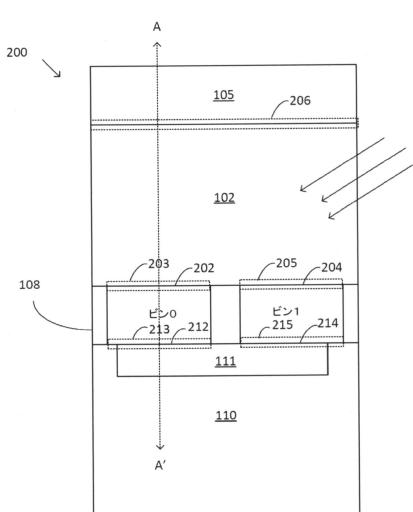

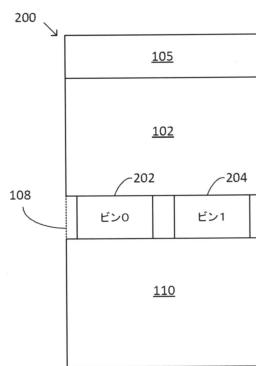

【図 2 A】集積光検出器のピクセルの図。

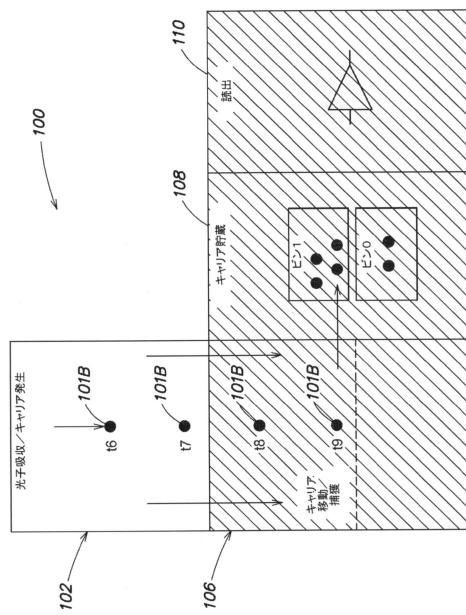

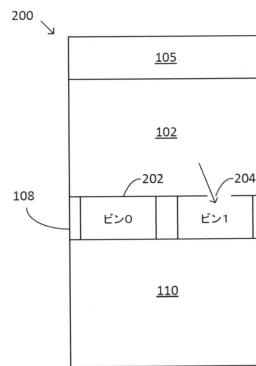

【図 2 B】図 2 A と異なる時点および空間で電荷キャリアを捕獲することを示す図。

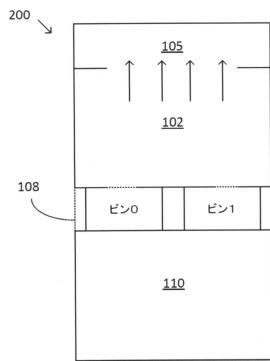

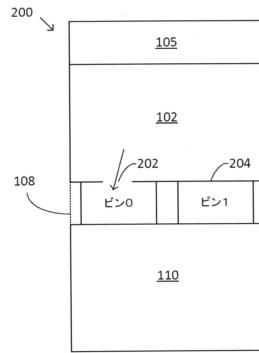

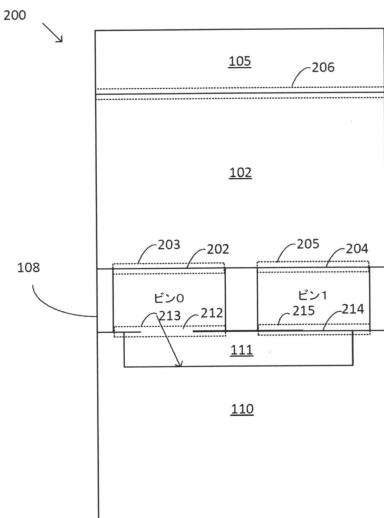

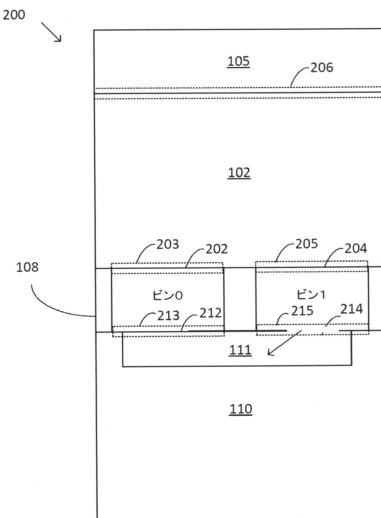

【図 3】直接ビニングピクセルの例を示す図。

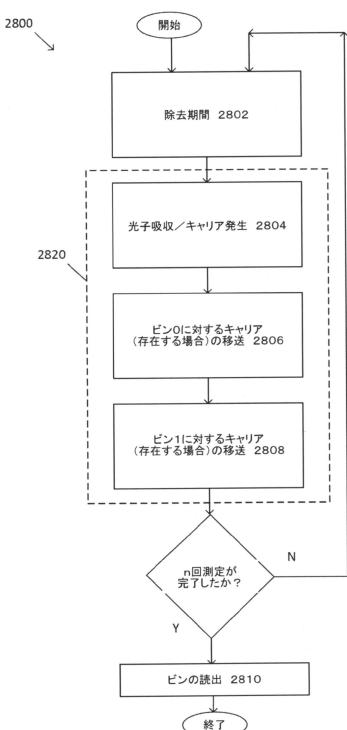

【図 4】直接ビニングピクセルを動作させる方法のフローチャート。

【図 5 A】図 4 の方法の様々なステージにおける直接ビニングを示す図。

【図 5 B】図 4 の方法の様々なステージにおける直接ビニングを示す図。

【図 5 C】図 4 の方法の様々なステージにおける直接ビニングを示す図。

【図 5 D】図 4 の方法の様々なステージにおける直接ビニングを示す図。

【図 5 E】図 4 の方法の様々なステージにおける直接ビニングを示す図。

【図 5 F】図 4 の方法の様々なステージにおける直接ビニングを示す図。

【図 6】直接ビニングピクセルの断面図。

【図 7】 $p+$ 領域および $n+$ 領域を有する分割ドーピングされた電極 (split-doped electrode) を示す図。

【図 8】直接ビニングピクセルの一例の平面図。

【図 9】直接ビニングピクセルの別の例の平面図。

【図 10】除去期間中の直接ビニングピクセルにおける電位を示す図。

【図 11】除去領域およびビンに対する電位障壁が上昇した期間中の直接ビニングピクセルにおける電位を示す図。

【図 12】電荷がビンに対して移送され得る期間における直接ビニングピクセルにおける電位を示す図。

【図 13】移送ゲートによって生成される電位障壁を低下させることによる、ビンに貯蔵されている電荷の浮遊拡散部 FD に対する移送を示す図。

【図 14】浮遊拡散部 FD のリセットを示す図。

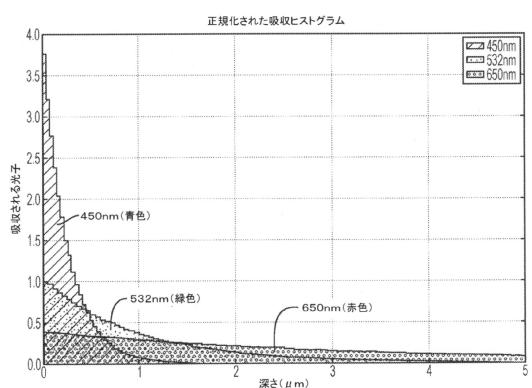

【図 15】波長の関数として吸収深さのプロットを示す図。

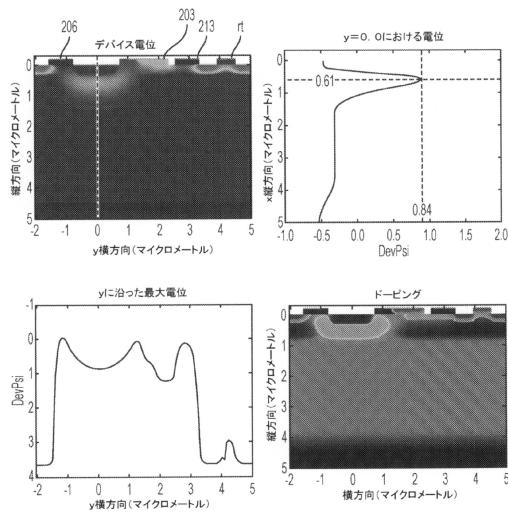

【図 16】フォトダイオードの一例についてのドーピング・プロファイルと電位とを示す図。

【図 17】深部生成キャリアが表面に到達するのを防止し得る深部ドーピング領域を示す図。

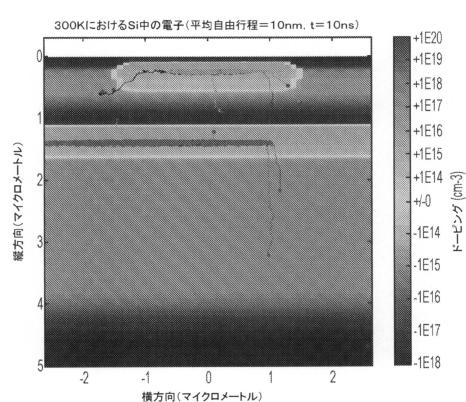

【図 18】示すキャリアが深部 n 井戸領域へと引き込まれる、10 ns 間の電子運動のシミュレーションを示す図。

【図 19】高電位にてバイアスがかけられている N 型埋設層（深部ドレイン）を示す図。

【図 20】基板と接触する P+ 型埋設層（深部遮蔽体）を示す図。

【図 21】集積回路が作製される材料の例を示す図。

【図 22】いくつかの実施形態による、直接ビニングピクセルのためのドーピング・プロファイルの例を示す図。

【図 23】図 22 に示されるドーピング・プロファイルを有する直接ビニングピクセルを形成するための例示的な処理シーケンスを示す図。

【図 24】図 22 の線  $y = 0$  に沿ったヒ素、ホウ素、リンおよび窒素についての例示的なドーピング・プロファイルのプロットを示す図。

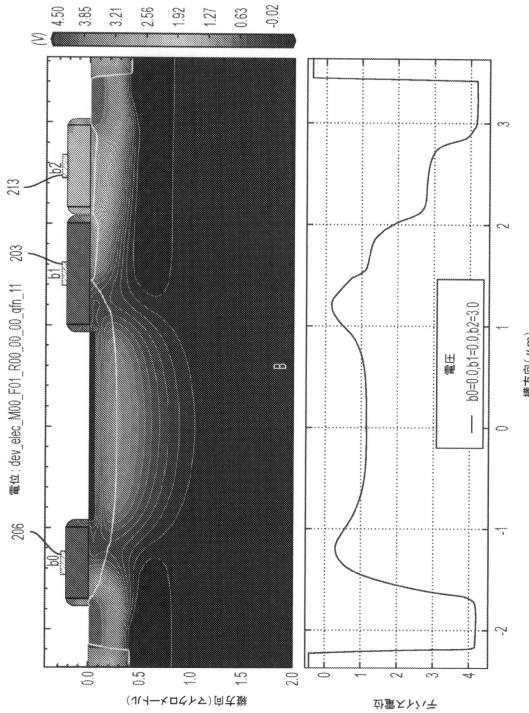

【図 25】すべての電極の電圧を 0 V に設定することによってすべての障壁が閉じられるときの、図 23 のピクセルにおける電位のプロットを示す図。

【図 26】電極 213 の電圧が 3 V に設定されるときの、図 23 のピクセルにおける電位のプロットを示す図。

【図 27】電極の電圧が変化したときの基板内の電位の曲線を示す図。

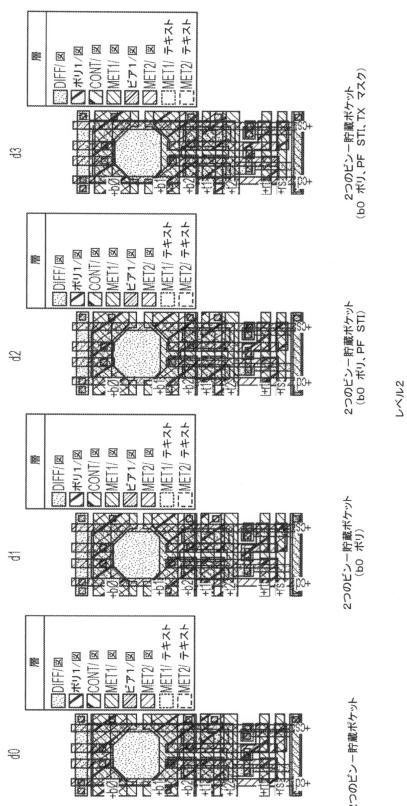

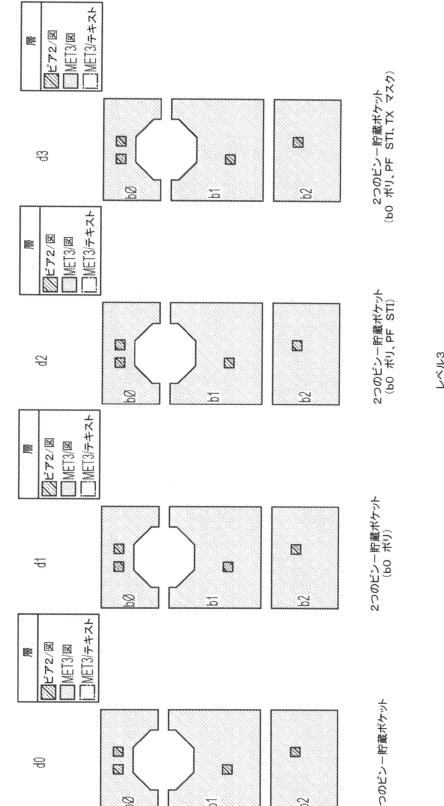

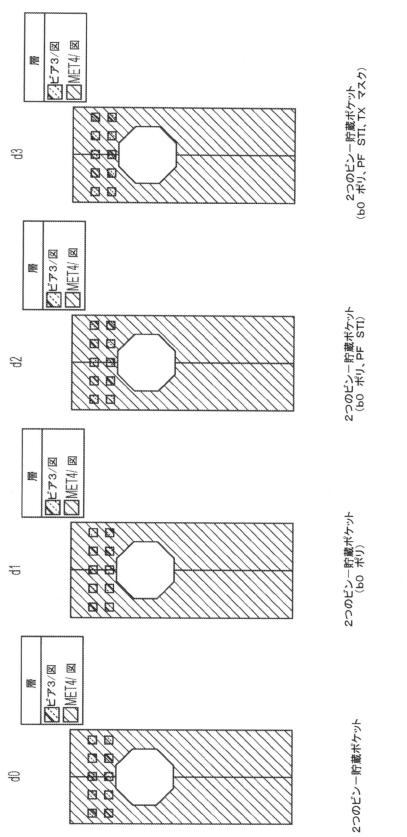

【図 28】光検出器を形成する例示的なプロセスと、4 つの異なるピクセル設計 d0 ~ d3 を示し、第 1 レベルを示す図。

【図 29】光検出器を形成する例示的なプロセスと、4 つの異なるピクセル設計 d0 ~ d3 を示し、第 2 レベルを示す図。

【図 30】光検出器を形成する例示的なプロセスと、4 つの異なるピクセル設計 d0 ~ d3 を示す図。

10

20

30

40

50

3を示し、第3レベルを示す図。

【図31】光検出器を形成する例示的なプロセスと、4つの異なるピクセル設計d0～d3を示し、第4レベルを示す図。

【図32】光検出器を形成する例示的なプロセスと、4つの異なるピクセル設計d0～d3を示し、第5レベルを示す図。

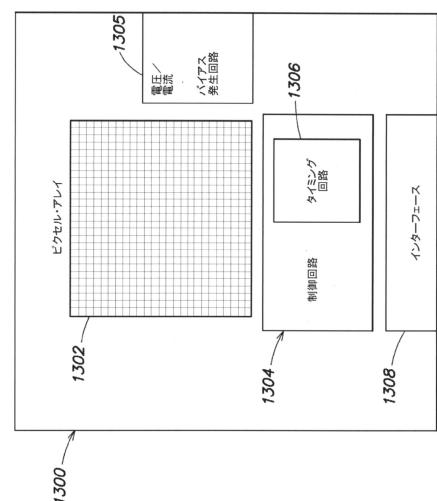

【図33】チップ・アーキテクチャの図。

【図34】例示的コンピューティング・デバイスのブロック図。

【発明を実施するための形態】

#### 【0004】

いくつかの実施形態は、入射光子を受け取るように構成された光検出領域であって、入射光子に応答して複数の電荷キャリアを生成するように構成された光検出領域と、少なくとも1つの電荷キャリア貯蔵領域と、複数の電荷キャリアのうちの電荷キャリアを、電荷キャリアが生成された時間に基づいて、少なくとも1つの電荷キャリア貯蔵領域内へ直接方向付けするべく、選択的に方向付けするように構成された電荷キャリア分離構造とを備える集積回路に関する。 10

#### 【0005】

いくつかの実施形態は、入射光子を受け取るように構成された光検出領域であって、入射光子に応答して複数の電荷キャリアを生成するように構成された光検出領域と、少なくとも1つの電荷キャリア貯蔵領域と、複数の電荷キャリアのうちの電荷キャリアを、電荷キャリアが生成された時間に基づいて、少なくとも1つの電荷キャリア貯蔵領域内へ選択的に方向付けするように構成された電荷キャリア分離構造とを備える直接ビニングピクセルを備える集積回路に関する。 20

#### 【0006】

いくつかの実施形態は、複数のピクセルを備える集積回路であって、複数のピクセルのうちの第1のピクセルは、入射光子を受け取るように構成された光検出領域であって、入射光子に応答して複数の電荷キャリアを生成するように構成された光検出領域と、複数の電荷キャリア貯蔵領域と、複数の電荷キャリアのうちの電荷キャリアを、電荷キャリアが生成された時間に基づいて、複数の電荷キャリア貯蔵領域のそれぞれの電荷キャリア貯蔵領域内へ直接方向付けするべく、選択的に方向付けするように、また複数の測定期間に生成された電荷キャリアを複数の電荷キャリア貯蔵領域において集約するように構成された電荷キャリア分離構造とを備える直接ビニングピクセルである、集積回路に関する。 30

#### 【0007】

いくつかの実施形態は、光検出方法に関し、光検出方法は、(A)光検出領域において入射光子を受け取る工程と、(B)入射光子に応答して生成された複数の電荷キャリアのうちの電荷キャリアを、電荷キャリアが生成された時間に基づいて、光検出領域から直接少なくとも1つの電荷キャリア貯蔵領域内へ選択的に方向付けする工程とを備える。

#### 【0008】

電荷キャリア分離構造は、光検出領域と少なくとも1つの電荷キャリア貯蔵領域のうちの第1の電荷キャリア貯蔵領域との間の境界に少なくとも1つの電極を備えてよい。

電荷キャリア分離構造は、光検出領域と第1の電荷キャリア貯蔵領域との間の境界に单一の電極を備えてよい。 40

#### 【0009】

いくつかの実施形態では、電荷キャリア捕獲領域が直接ビニングピクセルに存在しないか、電荷キャリア捕獲領域が光検出領域と電荷キャリア貯蔵領域との間に存在しないか、またはその両方である。

#### 【0010】

光検出領域と少なくとも1つの電荷キャリア貯蔵領域との間においてキャリアを捕獲することなく、電荷キャリアが少なくとも1つの電荷キャリア貯蔵領域に対し移送されてよい。

#### 【0011】

10

20

30

40

50

電荷キャリア除去領域は、除去期間中に光検出領域において生成された電荷キャリアを廃棄してよい。

廃棄された電荷キャリアは、キャリアが光検出領域から電荷キャリア貯蔵領域に向かって方向付けされる方向とは異なる方向において光検出領域から取り除かれてよい。

#### 【0012】

電荷キャリア除去領域は、光検出領域と電荷キャリア除去領域との間の境界における電極の電圧を変化させることによって、除去期間中に光検出領域において生成された電荷キャリアを廃棄してよい。

#### 【0013】

単一光子が、少なくとも1つの電荷キャリア貯蔵領域に対し移送され、少なくとも1つの電荷キャリア貯蔵領域に集約されてよい。 10

半導体基板の表面の下において1マイクロメートルよりも深い位置にある電荷キャリアは除去されてよい。

#### 【0014】

半導体基板の表面の下において1マイクロメートルよりも深い位置にある電荷キャリアは、光検出領域のフォトダイオードの下のインプラントによって少なくとも部分的に除去されてよい。

#### 【0015】

インプラントは深部遮蔽体または深部ドレインを提供してよい。

インプラントはN型またはP+型であってよい。 20

半導体基板の表面の下において1マイクロメートルよりも深い位置にある電荷キャリアは、半導体基板の表面の下のドリフトの場によって除去されてよい。

#### 【0016】

光検出領域は、2マイクロメートル未満の深さであるエピタキシャル領域に形成されてよい。

光検出領域は、フォトダイオードを含むエピタキシャル領域であってよい。

#### 【0017】

フォトダイオードにおける電荷キャリアは除去期間中に除去領域に対して移送されてよく、次いで第1の電荷キャリア貯蔵領域に対する第1の電位障壁が低下されてよく、次いで第2の電荷キャリア貯蔵領域に対する第2の電位障壁が低下されてよい。 30

#### 【0018】

第1の電位障壁は第1の電極によって制御されてよく、第2の電位障壁は第2の電極によって制御されてよい。

少なくとも1つの電荷キャリア貯蔵領域は、複数の電荷キャリア貯蔵領域を含んでよい。

#### 【0019】

上記の概要は例示のために提供され、限定することは意図されていない。

図面では、様々な図に示される同一またはほぼ同一の各構成要素は、同様の参照符号によって表される。明確にするため、すべての構成要素がすべての図で標識付けされるわけではない。図面は必ずしも原寸に比例して描かれるのではなく、本明細書で説明される技法およびデバイスの様々な態様を例示することに重点が置かれる。 40

#### 【0020】

本明細書では、入射光子の到着のタイミングを正確に測定または「時間ビニング」することができる集積光検出器が説明される。いくつかの実施形態では、集積光検出器は、ナノ秒またはピコ秒の分解能で光子の到着を測定することができる。そのような光検出器は、核酸のシークエンシング（たとえばDNAシークエンシング）に適用され得る分子検出／定量化を含む様々な用途において用途を見出すことができる。そのような光検出器は、ヌクレオチドを標識するために使用される発光分子からの入射光子の到着の時間領域解析を容易にし、それにより、輝度寿命に基づくヌクレオチドの識別およびシークエンシングを可能にすることができます。集積光検出器の用途の他の例は、以下でさらに論じられるように蛍光寿命イメージングおよび飛行時間型イメージングを含む。

## 分子検出 / 定量化のための時間領域測定の考察

生物学的サンプルの検出および定量化が、生物学的アッセイ（「バイオアッセイ」）を使用して行われ得る。バイオアッセイは従来、大型で高価な実験機器を必要とし、機器を操作しバイオアッセイを行うために訓練された研究科学者を要する。バイオアッセイは従来、まとめて行われ、大量の特定のタイプのサンプルが検出および定量化のために必要となっている。いくつかのバイオアッセイは、特定の波長の光を放出する発光性マーカーを用いてサンプルにタグ付けすることによって行われる。サンプルは光源によって照射されて発光を生じ、発光性の光が光検出器によって検出され、マーカにより放出される光の量が定量化される。発光性タグおよび / またはレポータを使用するバイオアッセイは従来、サンプルを照射するための高価なレーザ光源、ならびに照射されたサンプルから光を収集するための複雑な発光性検出オプティクスおよび電子部品を必要とする。

10

### 【0021】

いくつかの実施形態では、本明細書に説明されるような集積光検出器は、励起に応答して生物学的および / または化学的サンプルの輝度特性を検出することができる。より具体的には、そのような集積光検出器は、サンプルから受け取られた光の時間的特性を検出することができる。そのような集積光検出器は、励起に応答して発光分子によって放出される光の輝度寿命、たとえば蛍光寿命を検出および / または弁別することを可能にすることができる。いくつかの実施形態では、輝度寿命の検出および / または弁別に基づいて、サンプルの識別および / または定量的測定が行われ得る。たとえば、いくつかの実施形態では、核酸（たとえば、DNA、RNA）のシークエンシングは、それぞれのヌクレオチドに付着された発光分子の輝度寿命を検出および / または弁別することによって行われ得る。各発光分子は、対応するヌクレオチドに対して直接的に付着（たとえば結合）されてもよく、または対応するヌクレオチドに対して、ヌクレオチドおよび発光分子に結合されたリンカーモル子を介して間接的に付着されてもよい。

20

### 【0022】

いくつかの実施形態では、「ピクセル」と称されるいくつかの光検出構造および関連付けられた電子部品を有する集積光検出器は、並列で複数のサンプル（たとえば、数百、数千、または数百万以上）の測定および分析を可能にすることができる、それにより、複雑な測定を行うコストを低減し、発見率を急速に高めることができる。いくつかの実施形態では、光検出器の各ピクセルは、単一分子または複数の分子であり得るサンプルからの光を検出することができる。いくつかの実施形態では、そのような集積光検出器は、核酸（たとえば、DNA、RNA）シークエンシングなどの動的なリアルタイム用途に使用されることが可能である。

30

### 【0023】

#### 輝度寿命を使用する分子の検出 / 定量化

本出願の態様による集積光検出器を有する集積回路は、様々な検出およびイメージング用途に適切な機能を用いて設計され得る。以下でさらに詳細に説明されるように、そのような集積光検出器は、1つまたは複数の時間間隔または「時間ビン」内で光を検出する能力を有することができる。光の到着の時間に関する情報を収集するために、入射光子に応答して電荷キャリアが生成され、到着の時間に基づいてそれぞれの時間ビン内へ分離され得る。

40

### 【0024】

本出願のいくつかの態様による集積光検出器は、フルオロフォアなどの発光分子を含む光放出源を区別するために使用されてよい。発光分子は、それらが放出する光の波長、それらが放出する光の時間的特性（たとえば、それらの放出減衰期間）、および励起エネルギーに対するそれらの応答について異なる。したがって、発光分子は、これらの属性の検出に基づいて、他の発光分子から識別または弁別されてよい。そのような識別または弁別の技法は、単独または任意の適切な組合せで使用されてよい。

### 【0025】

いくつかの実施形態では、本出願に説明されるような集積光検出器は、蛍光寿命などの

50

輝度寿命を測定または弁別することができる。蛍光寿命測定は、1つまたは複数の蛍光性分子を励起し、放出された発光の時間変化を測定することに基づく。蛍光性分子が励起状態に到達した後に蛍光性分子が光子を放出する確率は、経時に指数関数的に減少する。確率が減少する率は、蛍光性分子の特性を示すものであってもよく、また異なる蛍光性分子に対して異なっていてもよい。蛍光性分子によって放出される光の時間的特性を検出することにより、蛍光性分子の識別、および／または蛍光性分子の互いに対する弁別を可能にすることができます。発光分子は、本明細書では発光性マーカまたは単に「マーカ」とも呼ばれる。

#### 【0026】

励起された状態に到達した後、マーカは、所与の時間に、ある確率で光子を放出することができる。励起されたマーカから光子が放出される確率は、マーカの励起後に経時に減少し得る。経的な光子が放出される確率の減少は、指数関数的な減衰関数  $p(t) = e^{-t/\tau}$  によって表されてよく、ここで、 $\tau$  は時間  $t$  における光子放出の確率であり、 $\tau$  はマーカの時間的パラメータである。時間的パラメータ  $\tau$  は、マーカが光子を放出する確率がある値であるときの励起後の時間を示す。時間的パラメータ  $\tau$  は、その吸収および発光スペクトル属性とは異なり得るマーカの属性である。そのような時間的パラメータ  $\tau$  は、輝度寿命、蛍光寿命、または単純にマーカの「寿命」と呼ばれる。

10

#### 【0027】

図1Aは、異なる寿命を有する2つのマーカについて時間の関数として光子の放出される確率をプロットしている。確率曲線Bによって表されるマーカは、確率曲線Aによって表されるマーカの放出の確率よりも速く減衰する放出の確率を有する。確率曲線Bによって表されるマーカは、確率曲線Aによって表されるマーカよりも短い時間パラメータ または寿命を有する。いくつかの実施形態では、マーカは0.1～20nsの範囲の蛍光寿命を有してよい。しかしながら、本明細書に説明される技法は、使用されるマーカの寿命に関して限定されない。

20

#### 【0028】

マーカの寿命は、2つ以上のマーカを区別するために使用されてよく、かつ／またはマーカを識別するために使用されてもよい。いくつかの実施形態では、異なる寿命を有する複数のマーカが励起起源によって励起される蛍光寿命測定が行われてよい。一例として、それぞれ0.5、1、2、および3ナノ秒の寿命を有する4つのマーカが、選択された波長（たとえば635nm）を有する光を放出する光源によって励起されてよい。マーカは、マーカによって放出された光の寿命の測定に基づいて、互いに識別または区別されてよい。

30

#### 【0029】

蛍光寿命測定では、絶対強度値とは対照的に、経時にどのように強度が変化するかを比較することによって相対強度測定を使用することができる。結果として、蛍光寿命測定は、絶対強度測定の難点のいくつかを回避することができる。絶対強度測定は、存在するフルオロフォアの濃度に応じて異なることがあり、フルオロフォア濃度を変えるために較正工程が必要とされ得る。対照的に、蛍光寿命測定は、フルオロフォア濃度に影響されないことが可能である。

#### 【0030】

40

発光マーカは外因性または内因性であり得る。外因性マーカは、発光性標識化のためのレポータおよび／またはタグとして使用される外部発光性マーカであってよい。外因性マーカの例は、蛍光性分子、フルオロフォア、蛍光色素、蛍光染色剤、有機色素、蛍光タンパク質、酵素、および／または量子ドットを含み得る。そのような外因性マーカは、特定の標的または成分に特異的に結合するプローブまたは官能基（たとえば、分子、イオン、および／またはリガンド）にコンジュゲートされ得る。外因性のタグまたはレポータをプローブに付着することは、外因性のタグまたはレポータの存在の検出を通して標的の識別を可能にする。プローブの例は、タンパク質、DNA分子またはRNA分子などの核酸、脂質、および抗体プローブを含み得る。外因性のマーカと官能基の組合せは、検出のために使用される任意の適切なプローブ、タグ、および／または標識を形成してよく、それら

50

には、分子プローブ、標識プローブ、ハイブリダイゼーション・プローブ、抗体プローブ、タンパク質プローブ（たとえば、ビオチン結合プローブ）、酵素標識、蛍光性プローブ、蛍光性タグ、および／または酵素レポータが含まれる。

#### 【0031】

外因性マーカはサンプルまたは領域に対して追加され得るが、内因性マーカはすでにサンプルまたは領域の一部であり得る。内因性マーカは、励起エネルギーの存在下で発光または「自己蛍光」することができる、存在する任意の発光性マーカを含み得る。内因性フルオロフォアの自己蛍光は、外因性フルオロフォアの導入を必要とすることなく、無標識で非侵襲的な標識化を提供することができる。そのような内因性フルオロフォアの例は、限定ではなく例として、ヘモグロビン、酸素ヘモグロビン、脂質、コラーゲンおよびエラスチン・クロスリンク、還元型ニコチンアミド・アデニン・ジヌクレオチド（NADH）、酸化フラビン（FADおよびFMN）、リポフュチン、ケラチン、ならびに／またはポルフィリン（porphyrin）を含み得る。

10

#### 【0032】

寿命測定によってマーカを区別することによって、マーカが発光スペクトルの測定によって区別されるときよりも少ない波長の励起光が使用されることを可能にすることができる。いくつかの実施形態では、より少ない波長の励起光および／または発光性の光を使用するとき、センサ、フィルタ、および／または回折オプティクスが減少されるまたは除去されることが可能である。いくつかの実施形態では、異なる寿命を有するマーカを用いて標識化が行われてよく、マーカは、同じ励起波長またはスペクトルを有する光によって励起されてよい。いくつかの実施形態では、単一の波長またはスペクトルの光を放出する励起光源が使用されてよく、それによりコストを低減することができる。しかしながら、本明細書に説明されている技法は、これに関して限定されず、任意の数の励起光波長またはスペクトルが使用されてよい。いくつかの実施形態では、受け取られた光に関するスペクトル情報および時間情報の両方を決定するために、集積光検出器が使用されてよい。いくつかの実施形態では、存在する分子の種類の定量的分析は、マーカから放出された発光の時間的パラメータ、スペクトル・パラメータ、または時間的パラメータとスペクトル・パラメータとの組合せを決定することによって行われてよい。

20

#### 【0033】

入射光子の到着時間を検出する集積光検出器により、追加の光学フィルタリング（たとえば光学スペクトル・フィルタリング）要件を低減し得る。以下に説明されるように、本出願による集積光検出器は、光生成されたキャリアを特定の時間に除去するためのドレンを含むことができる。光生成されたキャリアをこのように除去することによって、励起光パルスに応答して生成された望ましくない電荷キャリアが、光学フィルタリングを必要とせずに廃棄されて、励起パルスからの光の受光を防止することができる。そのような光検出器により、全体的な設計統合の複雑性、光学的および／またはフィルタリング構成要素、および／またはコストを低減することができる。

30

#### 【0034】

いくつかの実施形態では、時間の関数として輝度強度値を検出するために、集積光検出器の1つまたは複数の時間ビンにおいて収集された電荷キャリアを集約することによって、放出された発光の時間プロファイルを測定することによって、蛍光寿命が決定され得る。いくつかの実施形態では、マーカが励起状態になるよう励起され次いで光子が放出される時間が測定される、複数回の測定を行うことによって、マーカの寿命が決定され得る。測定ごとに、励起源が、マーカに向けられた励起光のパルスを生成することができ、励起パルスとマーカからのその後の光子イベントとの間の時間が決定され得る。これに加えてまたはこれに代えて、励起パルスが繰り返し周期的に発生する場合、光子放出イベントが発生した時とその後の励起パルスとの間の時間が測定されることが可能であり、測定された時間が、励起パルス間の時間間隔（すなわち、励起パルス波形の周期）から差し引かれて、光子吸収イベントの時間を決定することができる。

40

#### 【0035】

50

複数の励起パルスを用いてそのような実験を繰り返すことによって、励起後のある時間間隔内に光子がマーカから放出される場合の数が決定されることが可能であり、それは、励起後のそのような時間間隔内に光子が放出される確率を示す。収集される光子放出イベントの数は、マーカに対して放出される励起パルスの数に基づくことができる。測定期間にわたる光子放出イベントの数は、50 ~ 10,000,000またはそれより多い範囲になり得るが、いくつかの実施形態では、本明細書に説明されている技法はこれに関して限定されない。励起後のある時間間隔内に光子がマーカから放出される場合の数は、一連の離散時間間隔または時間ビン内で発生する光子放出イベントの数を表すヒストグラムに投入されることがある。時間ビンの数および/または各ビンの時間間隔は、特定の寿命および/または特定のマーカを識別するように設定および/または調整されてよい。時間ビンの数および/または各ビンの時間間隔は、放出された光子を検出するために使用されるセンサに応じて異なり得る。時間ビンの数は、1、2、3、4、5、6、7、または8以上、たとえば16,32,64、または16、32、または64以上であってよい。曲線当てはめアルゴリズムが、記録されたヒストグラムに曲線をフィットさせるために使用されてよく、その結果、所与の時間におけるマーカの励起後に光子が放出される確率を表す関数が得られる。 $p(t) = e^{-t/\tau}$  のような指数関数的減衰関数が、ヒストグラムデータにほぼフィットするように使用されてよい。そのような曲線当てはめから、時間的パラメータまたは寿命が決定され得る。決定された寿命は、存在するマーカのタイプを識別するために、マーカの既知の寿命と比較され得る。

#### 【0036】

寿命は、2つの時間間隔における強度値から計算され得る。図1Bは、例示的な励起パルス（点線）および例示的な蛍光発光（実線）の例示的な強度プロファイルを経時的に示す。図1Bに示される例では、光検出器は、少なくとも2つの時間ビンにわたって強度を測定する。時間  $t_1$  と時間  $t_2$  の間で発光エネルギーを放出する光子は、光検出器によって、強度  $I_1$  として測定され、時間  $t_3$  と時間  $t_4$  の間で放出される発光エネルギーは  $I_2$  として測定される。任意の適切な数の強度値が得られてよいが、図1Bでは2つのみが示されている。次いで、そのような強度測定は、寿命を計算するために使用され得る。一度に1つのフルオロフォアが存在する場合、時間ビニングされた発光シグナルは単一の指数関数的減衰にフィットし得る。いくつかの実施形態では、フルオロフォアの寿命を正確に識別するために、2つの時間ビンしか必要とされなくてよい。2つ以上のフルオロフォアが存在する場合、発光信号を二重または三重指数関数のような複数の指数関数的減衰にフィットさせることによって、組み合わせた発光信号から個々の寿命が識別され得る。いくつかの実施形態では、そのような発光信号から複数の蛍光寿命を正確に識別するために、2つ以上の時間ビンが必要とされることがある。しかしながら、複数のフルオロフォアを用いるいくつかの例では、単一の指数関数的減衰を発光信号にフィットさせることによって、平均蛍光寿命が決定され得る。

#### 【0037】

いくつかの例では、光子放出イベントの確率、ひいてはマーカの寿命は、マーカの環境および/または条件に基づいて変化し得る。たとえば、励起光の波長よりも小さい直径を有するボリュームに閉じ込められたマーカの寿命は、マーカがそのボリュームにないときよりも小さくなり得る。マーカが標識化に使用されるときと同様の条件で、既知のマーカを用いた寿命測定が行われ得る。既知のマーカを用いたそのような測定から決定された寿命が、マーカを特定するときに使用され得る。

#### 【0038】

##### 輝度寿命測定を使用するシークエンシング

集積光検出器の個々のピクセルは、分子または分子上の特定の位置のような1つまたは複数の標的を標識する蛍光タグおよび/またはレポータを識別するために使用される、蛍光寿命測定が可能であり得る。対象の任意の1つまたは複数の分子は、フルオロフォアによって標識されてよく、タンパク質、アミノ酸、酵素、脂質、ヌクレオチド、DNA、およびRNAが含まれる。放出された光のスペクトルの検出または他の標識技法と組み合わ

10

20

30

40

50

せると、蛍光寿命は、使用され得る蛍光タグおよび／またはレポータの総数を増加させることができ。寿命に基づく識別は、複雑な混合物における分子相互作用の特性に関する情報を提供するために、単一分子分析法に使用されてよく、この場合、そのような情報は、アンサンブル平均化において失われ、タンパク質間相互作用、酵素活性、分子動力学、および／または膜上の拡散を含み得る。加えて、異なる蛍光寿命を有するフルオロフォアは、標識成分の存在に基づく様々なアッセイ方法において標的成分にタグ付けするために使用され得る。いくつかの実施形態では、フルオロフォアの特定の寿命を検出することに基づいて、マイクロ流体システムを使用することなどによって、成分が分離され得る。

#### 【0039】

蛍光寿命の測定は、他の分析方法と組み合わせて使用されてもよい。たとえば、蛍光寿命は、1つまたは複数の分子に配置されたドナーおよびアクセプター・フルオロフォアの状態および／または環境を弁別するために、蛍光共鳴エネルギー移動(FRET)技法と組み合わせて使用されてもよい。そのような測定は、供与体と受容体の間の距離を決定するために使用され得る。いくつかの例では、供与体から受容体へのエネルギー移動は、供与体の寿命を減少させることがある。別の例では、蛍光寿命測定は、DNAシークエンシング技法と組み合わせて使用されてよく、ここでは、異なる寿命を有する4つのフルオロフォアが、ヌクレオチドの未知の配列を有するDNA分子における4つの異なるヌクレオチド(A、T、G、C)を標識するために使用され得る。フルオロフォアの発光スペクトルの代わりに蛍光寿命が、ヌクレオチドの配列を識別するために使用されてもよい。いくつかの技法で発光スペクトルの代わりに蛍光寿命を使用することにより、絶対強度測定のためアーチファクトが減少されるので、精度および測定分解能を増大することができる。加えて、寿命測定では、必要とされる励起エネルギー波長がより少なく、かつ／または検出される必要がある発光エネルギー波長がより少ないため、システムの複雑性および／または費用を低減することができる。

#### 【0040】

本明細書に説明されている方法は、DNAシークエンシングまたはRNAシークエンシングのような核酸のシークエンシングに使用されることが可能である。DNAシークエンシングは、標的核酸分子におけるヌクレオチドの順序および位置の決定を可能にする。DNAシークエンシングに使用される技術は、核酸配列を決定するために使用される方法において、また、シークエンシング・プロセス中のレート、リード長、およびエラーの発生において大きく異なり得る。いくつかのDNAシークエンシング方法は、合成によるシークエンシングに基づいており、このシークエンシングでは、標的核酸分子に相補的な核酸の新しく合成された鎖にヌクレオチドが組み込まれるときに、ヌクレオチドのアイデンティティが決定される。合成方法による多くのシークエンシングは、標的核酸分子の集団の存在(たとえば、標的核酸のコピー)、または標的核酸の集団を実現するための標的核酸の增幅の工程を必要とする。単一の核酸分子の配列を決定するための改善された方法が所望されている。

#### 【0041】

高精度かつ長いリード長で単一の核酸分子をシークエンシングすることに関して近年進歩している。単一分子シークエンシング技術、たとえば、パシフィック・バイオサイエンス(Pacific Biosciences)によって開発されたSMRT技術で使用される標的核酸は、サンプル・ウェルの底などの固体支持体に固定または添加されたシークエンシング反応の少なくとも1つの成分(たとえばDNAポリメラーゼ)を含むサンプル・ウェルに添加される一本鎖DNA鑄型である。サンプル・ウェルはまた、フルオロフォアなどの検出標識にコンジュゲートされたアデニン、シトシン、グアニン、およびチミンdNTPを含む「dNTP」とも呼ばれるデオキシリボヌクレオシド三リン酸を含む。好ましくは、dNTPの各クラス(たとえば、アデニンdNTP、シトシンdNTP、グアニンdNTPおよびチミンdNTP)は、信号の検出が新たに合成された核酸に組み込まれたdNTPのアイデンティティを示すように、異なる検出標識にコンジュゲートされる。検出標識は、検出標識の存在が、新たに合成された核酸鎖へのdNTPの組み込みま

10

20

30

40

50

たはポリメラーゼの活性を阻害しないように、任意の位置で d N T P にコンジュゲートされ得る。いくつかの実施形態では、いくつかの実施形態では、検出標識は、d N T P の末端リン酸塩（ リン酸塩 ）にコンジュゲートされる。

#### 【 0 0 4 2 】

標的核酸に相補的な核酸を合成することができる単一分子 D N A シークエンシングのために、任意のポリメラーゼが使用され得る。ポリメラーゼの例は、大腸菌 ( E . c o l i ) D N A ポリメラーゼ I 、 T 7 D N A ポリメラーゼ、バクテリオファージ T 4 D N A ポリメラーゼ 2 9 ( プサイ 2 9 ) D N A ポリメラーゼ、およびその変異体を含む。いくつかの実施形態では、ポリメラーゼは、単一のサブユニット・ポリメラーゼである。標的核酸の核酸塩基と相補的な d N T P との塩基対合のときに、ポリメラーゼは、新しく合成された鎖の 3' ヒドロキシル端部と d N T P の リン酸塩との間にリン酸ジエステル結合を形成することによって、新しく合成された核酸鎖に d N T P を組み込む。d N T P にコンジュゲートされた検出タグがフルオロフォアである例では、その存在が励起によって信号伝達され、組み込みの工程中に放出パルスが検出される。d N T P の末端（ ）リン酸塩にコンジュゲートされた検出標識に関して、新たに合成された鎖への d N T P の組み込みの結果、および リン酸塩の解放をもたらし、サンプル・ウェル中に自由に拡散する検出標識が、フルオロフォアから検出される放出の減少をもたらす。

10

#### 【 0 0 4 3 】

本明細書に説明されている技法は、分子もしくは他のサンプルの検出もしくは定量化、または配列決定を行うことに関する限り限定されない。いくつかの実施形態では、集積光検出器は、領域、物体、またはシーンに関する空間情報と、領域、物体、またはシーンを使用する入射光子の到着に関する時間的情報とを得るためにイメージングを行うことができる。いくつかの実施形態では、集積光検出器は、蛍光寿命イメージングのような、領域、物体、またはサンプルの発光寿命イメージングを行うことができる。

20

#### 他の用途

本明細書に説明されている集積光検出器は、上述されたように、複数の生物学的および / または化学的サンプルの分析に適用され得るが、集積光検出器は、たとえば、イメージング用途などの他の用途に適用されてもよい。いくつかの実施形態では、集積光検出器は、領域、物体、またはシーンのイメージングを行うピクセル・アレイを含むことができ、領域、物体、またはシーンの異なる領域から個々のピクセルで受け取られる光の時間的特性を検出することができる。たとえば、いくつかの実施形態では、集積光検出器は、組織から受け取られた光の時間的特性に基づいて組織のイメージングを行うことができ、これにより、医師が処置（たとえば手術）を行って組織の異常または病変領域（たとえば、癌または前癌部）を識別することを可能にすることができる。いくつかの実施形態では、集積光検出器は、外科用イメージング・ツールのような医療デバイスに組み込まれ得る。いくつかの実施形態では、光励起パルスに応答して組織によって放出された光に関する時間領域情報が、組織のイメージングおよび / またはキャラクタリゼーションを行うために取得され得る。たとえば、蛍光寿命イメージングを使用して、組織または他の物体のイメージングおよび / またはキャラクタリゼーションが行われてよい。

30

#### 【 0 0 4 4 】

上述されたように、集積光検出器は、生物学的および / もしくは化学的サンプルのイメージングもしくは分析、または組織のイメージングを行うことなどによって、科学的または診断的コンテキストで適用され得るが、そのような集積光検出器は、他の任意の適切なコンテキストで使用されてもよい。たとえば、いくつかの実施形態では、そのような集積光検出器は、個々のピクセルで検出された光の時間的特性を使用してシーンのイメージングを行うことができる。シーンのイメージングを行う用途の例は、光検出器に光が到達するのにかかる時間の量が分析されて、光検出器まで光が移動された距離を決定する、レンジ・イメージングまたは飛行時間型イメージングである。そのような技法は、シーンの 3 次元イメージングを行うために使用され得る。たとえば、集積光検出器に対して既知の位置から放射された光パルス、および光検出器によって検出された反射光によって、シーン

40

50

が照射され得る。アレイのそれぞれのピクセルで光が集積光検出器に到達するのにかかる時間の量が測定されて、シーンのそれぞれの部分から光検出器のそれぞれのピクセルに対して移動されて到達する光の距離が決定される。いくつかの実施形態では、集積光検出器は、たとえば、カメラ、携帯電話、またはタブレットコンピュータなどの家庭用電子デバイスに組み込まれてよく、取得された範囲情報に基づいて、そのようなデバイスが画像またはビデオを捕獲し処理することを可能にする。

#### 【0045】

いくつかの実施形態では、本出願に説明されている集積光検出器は、低い光強度を測定するためには使用されてよい。そのような光検出器は、たとえば、単一光子計数技法を現在使用し得る用途など、高感度の光検出器を必要とする用途に適することがある。しかしながら、本明細書に説明されている技法はこれに関して限定されず、本出願に説明されている集積光検出器は、任意の適切な光強度を測定してよい。

10

#### 【0046】

##### 他の発光寿命用途

###### 寿命を使用するイメージングおよびキャラクタリゼーション

前述されたように、本明細書に説明されている技法は、外因性フルオロフォアを使用する標識化、検出、および定量化に限定されない。いくつかの実施形態では、領域、物体、またはサンプルは、集積光検出器の使用を通して、蛍光寿命イメージング技法を用いてイメージングおよび／またはキャラクタリゼーションが行われてよい。そのような技法では、領域、物体、またはサンプル自体の蛍光特性が、イメージングおよび／またはキャラクタリゼーションのために使用されてよい。外因性マーカまたは内因性マーカのいずれかが、寿命イメージングおよび／またはキャラクタリゼーションによって検出され得る。特定の標的成分の存在および／または位置を検出するために、プローブに付着された外因性マーカが領域、物体、またはサンプルに提供され得る。外因性マーカは、標識プローブのための標的を含む領域、物体、またはサンプルの部分を検出するために、標識プローブの一部としてのタグおよび／またはレポータの役割をすることができる。内因性マーカの自己蛍光は、内因性マーカの導入を必要とせずにイメージングに容易に利用され得る空間分解能のための無標識で非侵襲的なコントラストを提供することができる。たとえば、生物学的組織からの自己蛍光信号は、組織の生化学的および構造的組成に依存し、それを示すことができる。

20

#### 【0047】

蛍光寿命測定は、フルオロフォアの周囲の条件の定量的尺度を提供することができる。条件の定量的尺度が検出またはコントラストに追加されてもよい。フルオロフォアの蛍光寿命は、pHまたは温度などのフルオロフォアの周囲環境に応じて異なることがあり、蛍光寿命の値の変化は、フルオロフォアの周囲の環境の変化を示し得る。一例として、蛍光寿命イメージングは、生物学的組織（たとえば、組織切片または外科的切除）などにおけるサンプルの局所環境内の変化をマッピングすることができる。内因性フルオロフォアの自己蛍光の蛍光寿命測定が、組織における物理的および代謝的变化を検出するために使用され得る。例として、サンプルからの自己蛍光を測定し、測定された自己蛍光から寿命を決定することによって、組織構造、形態、酸素化、pH、血管分布、細胞構造、および／または細胞代謝状態の変化が検出され得る。そのような方法は、スクリーニング、画像誘導生検もしくは手術、および／または内視鏡検査などの臨床用途に使用され得る。いくつかの実施形態では、本出願の集積光検出器は、たとえば蛍光寿命イメージングを行うために、手術器具などの臨床ツールに組み込まれてもよい。測定された自己蛍光に基づいて蛍光寿命を決定することは、臨床医が迅速に組織をスクリーニングし、裸眼には見えない小さな癌および／または前癌病変を検出することを可能にする無標識イメージング方法としての臨床的価値を提供する。蛍光寿命イメージングは、健常組織よりも長い蛍光寿命を有する発光を放出する腫瘍または癌細胞などの悪性細胞または組織の検出および線引きのために使用され得る。たとえば、蛍光寿命イメージングは、手術中に露出される消化管、膀胱、皮膚、または組織表面などの光学的にアクセス可能な組織における癌を検出するため

30

40

50

に使用され得る。

**【 0 0 4 8 】**

いくつかの実施形態では、蛍光寿命は、異なるタイプまたは状態のサンプル間のコントラストを提供するために顕微鏡技術で使用され得る。蛍光寿命イメージング顕微鏡法（FLIM）が、サンプルを光パルスで励起し、寿命を決定するために減衰するときに蛍光信号を検出し、得られた画像において減衰時間をマッピングすることによって実施され得る。そのような顕微鏡画像では、画像におけるピクセル値は、視野を収集する光検出器における各ピクセルについて決定された蛍光寿命に基づいてよい。

**【 0 0 4 9 】**

時間的情報を使用するシーンまたは物体のイメージング

10

上述されたように、本出願に説明されているような集積光検出器は、科学的および臨床的コンテキストで使用されてよく、そのようなコンテキストで、放出された光のタイミングが、領域、物体またはサンプルの検出、定量化、および／またはイメージングを行うために使用され得る。しかしながら、本明細書に説明されている技法は、科学的および臨床的用途に限定されず、入射光子の到着の時間に関する時間的情報が利用され得る任意のイメージング用途において集積光検出器が使用されてよい。用途の一例は飛行時間型イメージングである。

**【 0 0 5 0 】**

飛行時間型用途

いくつかの実施形態では、飛行時間測定を含む散乱光または反射光の時間プロファイルを測定することに基づいて、イメージング技法において集積光検出器が使用され得る。そのような飛行時間型測定では、光パルスが領域またはサンプル内に放出され、散乱光が集積光検出器によって検出され得る。散乱光または反射光は、領域またはサンプルの特性を示し得る別個の時間プロファイルを有することができる。サンプルによる後方散乱光は、サンプルにおけるそれらの飛行時間によって検出および解像され得る。そのような時間プロファイルは、時間点広がり関数（TPSF）であってよい。時間プロファイルは、光パルスが放出された後の複数の時間ビンにわたる積分強度を測定することによって取得され得る。光パルスの繰り返しあおよび散乱光の蓄積が、すべての以前のTPSFが後続の光パルスを生成する前に完全に消滅されることを確実にするために、特定の速度で実行されてよい。時間分解拡散光学イメージング方法は、サンプルにおいてさらなる深さでイメージングを行うために、光パルスが赤外光であり得る分光拡散光トモグラフィを含むことができる。そのような時間分解拡散光学イメージング方法は、生体内または人間の頭などの生体の一部において腫瘍を検出するために使用され得る。

20

30

**【 0 0 5 1 】**

これに加えてまたはこれに代えて、飛行時間型測定は、放出された光パルスと物体から反射された光の検出との間の光の速度および時間に基づいて、距離または距離範囲を測定するために使用され得る。そのような飛行時間型技法は、カメラ、自動車内の近接検出センサ、ヒューマン・マシン・インターフェース、ロボット工学、およびそのような技法によって収集された3次元情報を使用できる他の用途を含む、様々な用途で使用されてよい。光生成電荷キャリアを時間ビニングするための集積光検出器

40

いくつかの実施形態は、入射光子に応答して電荷キャリアを生成する光検出器を有する集積回路に関し、集積回路は、基準時間（たとえばトリガ・イベント）に対する電荷キャリアが入射光子の到着によって生成されるタイミングを弁別することができる。いくつかの実施形態では、電荷キャリア分離構造は、異なる時間に生成された電荷キャリアを分離し、異なる期間内に生成された電荷キャリアを集約する1つまたは複数の（「ビン」と称される）電荷キャリア貯蔵領域内へ電荷キャリアを方向付けする。各ビンは、選択された時間間隔内に生成された電荷キャリアを貯蔵する。各ビンに貯蔵された電荷を読み出すことにより、各時間間隔内に到着された光子の数に関する情報を提供することができる。そのような集積回路は、本明細書に説明されているような任意の様々な用途で使用され得る。

**【 0 0 5 2 】**

50

光検出領域および電荷キャリア分離構造を有する集積回路の例が説明される。いくつかの実施形態では、集積回路は、ピクセルのアレイを含むことができ、各ピクセルは、以下に論じられるように、1つまたは複数の光検出領域および1つまたは複数の電荷キャリア分離構造を含むことができる。

#### 【0053】

##### ピクセルの構造および動作の概要

図2Aは、いくつかの実施形態によるピクセル100の図を示す。ピクセル100は、(光検出領域とも呼ばれる)光子吸収/キャリア発生領域102と、キャリア移動/捕獲領域106と、本明細書で「電荷キャリア貯蔵ピン」または単に「ピン」とも呼ばれる1つまたは複数の電荷キャリア貯蔵領域を有するキャリア貯蔵領域108と、電荷キャリア貯蔵ピンから信号を読み出すための読出回路構成110とを含む。10

#### 【0054】

光子吸収/キャリア発生領域102は、入射光子を光生成電荷キャリアに変換できる半導体材料(たとえばシリコン)の領域であってよい。光子吸収/キャリア発生領域102は、光に曝されてよく、入射光子を受け取ることができる。光子吸収/キャリア発生領域102によって光子が吸収されるとき、光子は電子/正孔対などの光生成電荷キャリアを生成することができる。光生成電荷キャリアは、本明細書では単に「電荷キャリア」と呼ばれることがある。

#### 【0055】

電場が光子吸収/キャリア発生領域102内に確立され得る。いくつかの実施形態では、電場は、キャリア移動/捕獲領域106内の変化する電場と区別されるように「静的」であり得る。光子吸収/キャリア発生領域102内の電場は、横方向成分、縦方向成分、または横方向成分と縦方向成分の両方を含むことができる。電場の横方向成分は、矢印で示されるように図2Aの下方向であってよく、これは、光生成電荷キャリアをキャリア移動/捕獲領域106に向けて駆動する光生成電荷キャリアに対する力を誘起する。電場は、様々な方法で形成され得る。20

#### 【0056】

いくつかの実施形態では、光子吸収/キャリア発生領域102上に1つまたは複数の電極が形成され得る。電極は、光子吸収/キャリア発生領域102に電場を確立するように印加された電圧を有することができる。そのような電極は、「フォトゲート(photo gate)」と称されることがある。いくつかの実施形態では、光子吸収/キャリア発生領域102は、電荷キャリアが完全に空乏化されたシリコンの領域であり得る。30

#### 【0057】

いくつかの実施形態では、光子吸収/キャリア発生領域102における電場は、P N接合などのジャンクションによって確立されてよい。光子吸収/キャリア発生領域102の半導体材料は、光生成電荷キャリアをキャリア誘導/捕獲領域106に向けて駆動する光生成電荷キャリアに対する力を誘起する電場を生成する配向および/または形状を有するP N接合を形成するようにドーピングされ得る。ジャンクションを使用して電場を生成することにより、光子吸収/キャリア発生領域102に入射光子の一部が到達するのを妨げ得る光子吸収/キャリア発生領域102の上に位置する電極の使用に関して量子効率を改善することができる。ジャンクションを使用することで、フォトゲートの使用に関して暗電流を低減することができる。暗電流は、キャリアを生成し得る半導体基板の表面における欠陥によって発生されると理解されている。いくつかの実施形態では、P N接合ダイオードのP端子は、その電圧を設定する端子に対して連結されてよい。そのようなダイオードは、「ピン止め(pinned)」フォトダイオードと呼ばれることがある。ピン止めフォトダイオードは、その電圧を設定しキャリアを引き付ける端子により、表面でキャリア再結合を促進することができ、それにより暗電流を低減することができる。捕獲されることが望ましい光生成電荷キャリアは、表面における再結合領域の下を通過してよい。いくつかの実施形態では、横方向電場は、半導体材料内の勾配ドーピング濃度を使用して確立され得る。40

**【 0 0 5 8 】**

いくつかの実施形態では、電場を生成するためにジャンクションを有する吸収 / キャリア発生領域 102 は、以下の特性の 1つまたは複数を有することができる：

- 1 ) 時間変動場から離れてテーパが付けられる空乏 n 型領域、

- 2 ) 電場を横方向に n 型領域へ遷移させるためのギャップを有する n 型領域を取り囲む p 型インプラント、および / または、

- 3 ) n 型領域を埋設し寄生電子の再結合領域として機能する、 p 型表面インプラント。

**【 0 0 5 9 】**

いくつかの実施形態では、ジャンクションと少なくとも 1つの電極との組合せによって、電場が光子吸収 / キャリア発生領域 102 に確立され得る。たとえば、ジャンクションと単一の電極、または 2つ以上の電極が使用されてよい。いくつかの実施形態では、ジャンクションから比較的遠くに配置され得るキャリア移動 / 捕獲領域 106 の近くに電位勾配を確立するために、1つまたは複数の電極がキャリア移動 / 捕獲領域 106 の近くに配置され得る。

10

**【 0 0 6 0 】**

図 2A に示されるように、時間 t1 で、光子が捕獲されて電荷キャリア 101A (たとえば電子) が生成され得る。いくつかの実施形態では、光子吸収 / キャリア発生領域 102、および (図 2A に示す矢印で示されるように) 図 2A の下方向に電荷キャリア 101A を移動させるキャリア移動 / 捕獲領域 106 に沿って、電位勾配が確立され得る。電位勾配に応答して、電荷キャリア 101A は、時間 t1 のその位置から、時間 t2 の第 2 の位置、時間 t3 の第 3 の位置、時間 t4 の第 4 の位置、および時間 t5 の第 5 の位置へ動くことができる。そのように、電荷キャリア 101A は、電位勾配に応答してキャリア移動 / 捕獲領域 106 内に移動する。

20

**【 0 0 6 1 】**

キャリア移動 / 捕獲領域 106 は半導体領域であり得る。いくつかの実施形態では、キャリア移動 / 捕獲領域 106 は、光子吸収 / キャリア発生領域 102 と同じ材料 (たとえばシリコン) の半導体領域であってもよいが、例外として、キャリア移動 / 捕獲領域 106 は、(たとえば、金属層のような上に位置する不透明材料によって) 入射光から遮蔽され得る。

30

**【 0 0 6 2 】**

いくつかの実施形態では、さらに以下に論じられるように、電位勾配が、光子吸収 / キャリア発生領域 102 およびキャリア移動 / 捕獲領域 106 内に、これらの領域の上に配置された電極によって確立され得る。しかしながら、本明細書に説明されている技法は、電位勾配を生成するために使用される電極の特定の位置に関して限定されない。また、本明細書に説明されている技法は、電極を使用して電位勾配を確立することに限定されない。いくつかの実施形態では、空間的に勾配したドーピング・プロファイルおよび / または P N 接合を使用して、電位勾配が確立され得る。電荷キャリアを光子吸収 / キャリア発生領域 102 およびキャリア移動 / 捕獲領域 106 に沿って移動させる電位勾配を確立するために、任意の適切な技法が使用され得る。

40

**【 0 0 6 3 】**

電荷キャリア分離構造は、異なる時間に生成された電荷キャリアを分離することを可能にするようにピクセル内に形成され得る。いくつかの実施形態では、電荷キャリア分離構造の少なくとも一部は、キャリア移動 / 捕獲領域 106 上に形成されてよい。電荷キャリア分離構造は、キャリア移動 / 捕獲領域 106 上に形成された 1つまたは複数の電極を含むことができ、その電圧は、制御回路構成によって、キャリア移動 / 捕獲領域 106 における電位を変更するように制御され得る。

**【 0 0 6 4 】**

キャリア移動 / 捕獲領域 106 における電位は、電荷キャリアを捕獲することを可能にするように変更され得る。電位勾配は、キャリア移動 / 捕獲領域 106 の上に位置する 1つまたは複数の電極の電圧を変更することによって変更されて、キャリアを所定の空間領

50

域内に閉じ込めることができが可能な電位障壁を生成することができる。たとえば、図 2 A のキャリア移動 / 捕獲領域 106 内の破線の上に位置する電極の電圧が、図 2 A のキャリア移動 / 捕獲領域 106 内の破線に沿った電位障壁を上昇させるために時間 t5 で変更され、それにより電荷キャリア 101A を捕獲することができる。図 2 A に示されるように、時間 t5 で捕獲されたキャリアは、キャリア貯蔵領域 108 の bin 「 bin 0 」に対して移送され得る。電荷キャリア貯蔵 bin に対するキャリアの移送は、キャリア移動 / 捕獲領域 106 および / またはキャリア貯蔵領域 108 における電位を変更することによって（たとえば、これらの領域の上に位置する電極の電圧を変更することによって）行われ、それによりキャリアを電荷キャリア貯蔵 bin 内へ移動させることができる。

#### 【 0065 】

キャリア移動 / 捕獲領域 106 の所定の空間領域内のある時点の電位を変更することにより、特定の時間間隔内に起きた光子吸収によって発生されたキャリアをトラップすることを可能にすることができる。異なる時間および / または位置で光生成電荷キャリアをトラップすることにより、光子吸収によって電荷キャリアが発生された時間が弁別され得る。この意味で、トリガ・イベントの発生後のある時点および / または空間において電荷キャリアをトラップすることによって、電荷キャリアが「時間ビニング」され得る。特定の bin 内への電荷キャリアの時間ビニングは、光生成電荷キャリアが入射光子の吸収によって発生された時間に関する情報を提供し、したがって同様に、トリガ・イベントに対して光生成電荷キャリアを生成した入射光子の到着を「時間ビニング」する。

#### 【 0066 】

図 2 B は、異なる時点および空間で電荷キャリアを捕獲することを示す。図 2 B に示されるように、キャリア移動 / 捕獲領域 106 内の破線の上に位置する電極の電圧が、図 2 B のキャリア移動 / 捕獲領域 106 内の破線に沿った電位障壁を上昇させるために時間 t9 で変更され、それによりキャリア 101B を捕獲することができる。図 2 B に示されるように、時間 t9 で捕獲されたキャリアは、キャリア貯蔵領域 108 の bin 「 bin 1 」に移送され得る。電荷キャリア 101B は時間 t9 でトラップされるので、それは、時間 t5 に捕獲されたキャリア 101A の光子吸収イベント（すなわち t1 ）とは異なる時間（すなわち時間 t6 ）に起きた光子吸収イベントを表す。

#### 【 0067 】

##### 直接ビニングピクセル

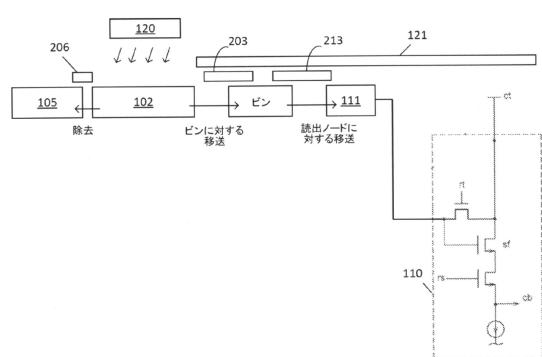

図 3 は、光子吸収 / キャリア発生領域 102 において発生する電荷キャリアが電荷キャリア貯蔵領域 108 における電荷貯蔵 bin に対し直接移送され得る、ピクセル 200 の一例を示す。そのようなピクセルは、「直接ビニングピクセル」と称される。図 3 に示されるように、ピクセル 200 はキャリア移動 / 捕獲領域 106 を含まない。キャリアをキャリア移動 / 捕獲領域 106 に捕獲するのではなく、電荷キャリアは光子吸収 / キャリア発生領域 102 から電荷キャリア貯蔵領域 108 の bin へと直接移送され得る。電荷キャリアが移送される bin は、電荷キャリアを生成する光子吸収 / キャリア発生領域 102 における光子の到着の時間に基づく。直接ビニングピクセルのエリアは、キャリア移動 / 捕獲領域 106 の省略のため少なくとも部分的に減少されてよい。有利には、いくつかの実施形態では、直接ビニングピクセルは半導体チップのより小さいエリアを占めてよく、その半導体チップは、数千、もしくは数百万のピクセル、またはそれを超えるピクセルなど、多くのピクセルをチップ上に形成することができる。多数のピクセルをチップ上に提供することによって、多数の測定を並列に行うこと、または高い空間分解能にてイメージングを行うことが可能となり得る。これに加えてまたはこれに代えて、直接ビニングピクセルは、電力消費を低減してよい。ピクセルの各電極を充電および放電することは電力を消費し得るので、ピクセル 200 はより少ない電極の存在のため電力消費を低減することができ、すなわち、キャリア移動 / 捕獲領域 106 において電荷キャリアを捕獲するための電極を省略することが可能である。

#### 【 0068 】

図 3 は電荷キャリア貯蔵領域 108 に 2 つの bin 、すなわち、 bin 0 および bin 1 を有

10

20

30

40

50

するピクセル 200 の一例を示す。上述されたように、ピン 0 はトリガ・イベントの後の一期間に受け取られる電荷キャリアを集約してよく、またピン 1 はトリガ・イベントに対して後の期間に受け取られる電荷キャリアを集約してよい。しかしながら、電荷貯蔵領域 108 は、1 つのピン、3 つのピン、4 つのピン、またはそれを超えるピンなどの任意の数のピンを有してよい。

#### 【0069】

光子吸収 / キャリア発生領域 102 は、たとえばシリコンなどの、任意の適切な半導体から形成され得る半導体領域を含んでよい。いくつかの実施形態では、光子吸収 / キャリア発生領域 102 は、ピン止めフォトダイオードなどのフォトダイオードを含んでよい。フォトダイオードは完全に空乏化されていてよい。いくつかの実施形態では、フォトダイオードは基本的に常に電子が空乏化されたままであってよい。いくつかの実施形態では、フォトダイオードは、単一光子を収集するように構成される。そのような実施形態では、単一光電子はフォトダイオードにおいて発生し閉じ込められてよい。CMOS 处理によって形成される場合、フォトダイオードは CMOS 处理によって生成されるデバイス内において得られる電位によって完全に空乏化されてよい。電極 203, 205 および 206 は、図 8 においてより詳細に示すように、ダイオードの周囲を少なくとも部分的に囲むダイオードに結合されてよい。しかしながら、図 8 に示されるこの実施形態は、電極 203, 205 および 206 に適した配置の单なる一例であることに留意されたい。電極 203 および 205 は、閉じ込められたキャリアの急速な電荷移送を可能とし得る。ピンに対する電荷キャリアの移送を論じる前に、望ましくないキャリアの除去領域 105 への移送による望ましくないキャリアの除去が説明される。

10

20

#### 【0070】

図 3 を再び参照すると、直接ビニングピクセル 200 は、光子吸収 / キャリア発生領域 102 において除去期間中に生成された電荷キャリアを排出または廃棄するための除去領域 105 を含んでよい。除去期間は励起光パルスなどのトリガ・イベント中に発生するようなくつつのタイミングを取りられてよい。励起光パルスが光子吸収 / キャリア発生領域 102 においていくつつの望ましくない電荷キャリアを生成し得るので、除去期間中にそのような電荷キャリアを除去領域 105 へと排出するようにピクセル 200 に電位勾配が確立されてよい。一例として、除去領域 105 は、電子が供給電圧へと排出される高い電位拡散エリアを含んでよい。除去領域 105 は、電荷が領域 102 を除去領域 105 に直接結合する電極 206 を含んでよい。いくつかの実施形態では、電極 206 は半導体領域の上に位置してよい。電極 206 の電圧は、光子吸収 / キャリア発生領域 102 に所望の電位勾配を確立するように変化してよい。除去期間中に、電極 206 の電圧は、キャリアを光子吸収 / キャリア発生領域 102 から電極 206 へと引き込むレベルに、および供給電圧の外に設定されてよい。たとえば、電極 206 の電圧は、電子が光子吸収 / キャリア発生領域 102 から離れて除去領域 105 へと引き込まれるように、電子を引き付ける正の電圧に設定されてよい。除去期間中に、電極 203 および 205 は、望ましくない電荷キャリアがピンに到達するのを防止するように、電位障壁 202 および 204 を形成する電位に設定されてよい。除去領域 105 によってキャリアを領域 102 からドレンへと横方向に移送させることができるので、除去領域 105 は「横方向除去領域」として考慮されてよい。いくつかの実施形態では、その除去は貯蔵ピンに対して光検出領域とは反対の方向にある。

30

40

#### 【0071】

除去期間の後、光子吸収 / キャリア発生領域 102 において生成される光生成電荷キャリアは時間ビニングされてよい。個々の電荷キャリアは、その到着の時間に基づいてピンへ方向付けされてよい。そうするために、光子吸収 / キャリア発生領域 102 と電荷キャリア貯蔵領域 108 との間の電位は、光生成電荷キャリアをそれぞれの時間ピンへと方向付ける電位勾配を確立するようにそれぞれの期間において変化してよい。たとえば、第 1 の期間中に電極 203 によって形成される電位障壁 202 は低下されてよく、この期間中に発生したキャリアがピン 0 に対して移送されるように、電位勾配は光子吸収 / キャリア

50

発生領域 102 からビン 0 へと確立されてよい。次いで、第 2 の期間中に、電極 205 によって形成される電位障壁 204 は低下されてよく、この後者の期間中に発生したキャリアがビン 1 に対して移送されるように、電位勾配は光子吸収 / キャリア発生領域 102 からビン 1 へと確立されてよい。

#### 【 0072 】

図 4 は、いくつかの実施形態による、複数の測定 2820 を行う工程を含む、ピクセル 200 を動作させる方法 2800 のフローチャートを示す。いくつかの実施形態では、「測定」は、光子を受け取ること、および特定の期間またはビンに対応する電荷貯蔵ノードに対して捕獲されたキャリアを移送することを含むことができる。光子が光検出器に到着する時間に関する統計情報を収集するために、測定が複数回繰り返されてよい。そのような方法は、本明細書に説明されているような集積デバイスによって少なくとも部分的に実施され得る。10

#### 【 0073 】

工程 2802 はトリガ・イベント中に発生するようにタイミングを取りられ得る。トリガ・イベントは、光子の到着を時間ビニングするための時間基準の役割をするイベントであり得る。トリガ・イベントは、たとえば、光パルスまたは電気パルスであってよく、特異的イベントまたは反復する周期的イベントであってよい。蛍光寿命検出のコンテキストでは、トリガ・イベントは、フルオロフォアを励起するための光励起パルスの発生であり得る。飛行時間型イメージングのコンテキストでは、トリガ・イベントは、集積光検出器を備えるイメージング・デバイスによって放出された（たとえば、フラッシュからの）光のパルスであり得る。トリガ・イベントは、光子またはキャリアの到着のタイミングを取るための基準として使用される任意のイベントであり得る。20

#### 【 0074 】

光励起パルスの発生はかなりの数の光子を生成することができ、その一部はピクセル 200 に到達し、光子吸収 / キャリア発生エリア 102 において電荷キャリアを生成することができる。光励起パルスからの光生成キャリアは、測定されることが望ましくないため、その光生成キャリアをドレインへ方向付けすることによって除去され得る。これは、不要な信号の量が減少させることができ、さもなければ、さらなる設計の複雑性および / またはコストを追加し得るシャッタまたはフィルタのような複雑な光学構成要素によって、不要な信号が到着するのを防止する必要があり得る。30

#### 【 0075 】

工程 2802 は除去期間に対応する。工程 2802 中のピクセル 200 の動作は、図 5 A に示される。工程 2802 では、ピクセル 200 は、領域 102 において生成される電荷キャリアを除去領域 105 に対して移送することによって、その電荷キャリアを除去するように動作する。たとえば、工程 2802 は、領域 102 において生成された電荷キャリアを除去領域 105 へと駆動する電位勾配を生成するように、電極 206 を制御する工程を含んでよい。図 5 A の上方向にキャリアを方向づけすることによって、キャリアは除去される。

#### 【 0076 】

工程 2804 では、光子吸収およびキャリア発生は、領域 102 において行われてよい。上述されたように、いくつかの用途では、トリガ・イベントに応答して光子を受け取ることとキャリアを発生させることとの確率は、低くてよい（たとえば、約 10000 回に 1 回）。したがって、工程 2804 は、トリガ・イベントに応答して光子が受け取られないことが多いので、各トリガ・イベントについて行われなくてよい。しかしながら、いくつかの実施形態では、受け取られる光子の量はより高くてよい。40

#### 【 0077 】

工程 2804 中、光生成電荷キャリアが除去されるのを防止するように、電位障壁が光検出領域 102 と除去領域 105 との間に存在する。工程 2804 中、ビン 0 に対する電位障壁 202 は、図 5 B に示されるように低下されてよく、または図 5 C に示されるように上昇されてよい。ビン 0 に対する電位障壁 202 が低下される場合、電荷キャリアは直

接ピン 0 へと通過してよい（工程 2806）。ピン 0 に対する電位障壁 202 が上昇される場合、電荷キャリアは工程 2806 まで領域 102 に閉じ込められてよい。

#### 【0078】

工程 2806 では、キャリアは（存在する場合）ピン 0 に対して移送される。ピン 0 に対する電位障壁 202 は、低下されるか低下されたままである。光生成電荷キャリアが工程 2802 の後の期間に生成されると、電位障壁 202 の低下によって電荷キャリアがピン 0 に対して移送される。電位障壁 202 は、領域 102 とピン 0 との間の境界における電極 203 の電圧を制御することによって上昇または低下され得る（図 3, 図 5B）。そのような電極は、半導体領域における電位を制御する半導体領域上に位置してよい。いくつかの実施形態では、ピン 0 に対する電荷キャリアの移送を可能とするか防止する電位障壁 202 を制御するように、単一の電極 203 のみが領域 102 とピン 0 との間の境界に配置されてよい。しかしながら、いくつかの実施形態では、電位障壁 202 は 2 つ以上の電極によって生成されてよい。図 2A の電荷キャリア捕獲領域 106 とは異なり、電位障壁 202 を生成する電極 206 は、ピンの外側の位置に電荷キャリアをトラップすることができない。むしろ、電極 206 は、電荷キャリアがピン 0 に入ることを可能とするか防止するように、電位障壁 202 を制御してよい。また、領域 102 とピンとの間にいくつかの電位障壁を生成する電荷キャリア捕獲領域 106 とは異なり、電位障壁 202 は領域 102 とピン 0 との間の単一の電位障壁であってよい。この段落において説明されるものと同一または同様の特性が、ピン 1、電位障壁 204、および電位障壁 204 を生成する電極 205 に存在してよい。

10

#### 【0079】

いくつかの実施形態では、除去期間後、電荷を一方向に、すなわち領域 102 から時間ピンに向かう方向に流れさせるだけの電位勾配が形成されてよい。電荷は、図 5A～図 5D の下方向におけるピンのうちの 1 つに流れる。発生したキャリアを電荷貯蔵領域 108 に向かって図の下方向に半導体領域を通って移動させるように、適切な電位勾配が半導体領域に確立されてよい。そのような電位勾配は、勾配ドーピング濃度、選択された電位における 1 または複数の電極、またはその両方を使用するなど、任意の適切な方法で確立されてよい。したがって、工程 2802 の後に領域 102 において生成される光生成電荷キャリアはピン 0 に対して移送され、したがってピン 0 において光生成電荷キャリアの到着を時間ビニングする。

20

#### 【0080】

工程 2806 の後、図 5C に示されるように、ピン 0 に対する電位障壁 202 は上昇される。任意選択で、ピン 0 に対する電位障壁 202 とピン 1 に対する電位障壁 204 との両方が、ある期間に上昇されてよい。障壁 202 と障壁 204 との両方が上昇される場合、工程 2806 の後に生成される電荷キャリアは、工程 2808 まで領域 102 に閉じ込められ得る。

30

#### 【0081】

工程 2808 では、図 5D に示されるように、電荷キャリア（存在する場合）はピン 1 に対して移送される。ピン 1 に対する電位障壁 204 は低下される。光生成電荷キャリアが工程 2806 の後の期間に生成される場合、電位障壁 204 の低下によって、電荷キャリアがピン 1 に対して移送される。電位障壁 204 は、領域 102 とピン 1 との間の境界における電極 205 の電圧を制御することによって、上昇または低下されてよい。そのような電極は、半導体領域上に位置してよい。したがって、工程 2806 の後に領域 102 において生成された光生成電荷キャリアはピン 1 に対して移送され、したがってピン 1 において光生成電荷キャリアの到着を時間ビニングする。工程 2808 の後、電位障壁 202 は上昇されてよい。

40

#### 【0082】

工程 2808 の後、測定 2820 は、トリガ・イベント後に光子が到着する傾向がある期間に関する情報（たとえば統計情報）を得るために、n - 1 回繰り返されてよい。測定 2820 が繰り返されるとき、時間ビニングされた電荷キャリアが対応する電荷貯蔵ピン

50

に集約され得る。測定 2820 を繰り返すことにより、統計的に有意な結果を提供するために充分な数の電荷キャリアを電荷キャリア貯蔵ビンに集約することを可能にすることができる。たとえば、蛍光寿命測定のコンテキストでは、フルオロフォアから受け取られた光子に応答する光子吸収イベントが比較的まれに発生することが予想され得る。たとえば、そのようなイベントは、約 1,000 回の測定において 1 回発生することが予想される。したがって、結果が統計的に有意であるか充分な信号対雑音比を有するかその両方であるように、充分な数の電荷キャリアを電荷キャリア貯蔵ビンに集約するために、多数の測定 2820 が行われる必要があり得る。いくつかの実施形態では、蛍光寿命測定のために行われ得るフルオロフォアの測定の数  $n$  は、充分な数（すなわち、いくつかの実施形態では数十または数百以上）の電荷キャリアを捕獲して各ビンにビニングすることを可能にするために、50,000 以上、100,000 以上、200,000 以上、300,000 以上、400,000 以上、500,000 以上、100 万以上、200 万以上、500 万以上であり得る。測定は、50 MHz と 100 MHz の間、25 MHz と 200 MHz の間、10 MHz と 500 MHz の間、または 1 MHz と 500 MHz の間などの MHz 範囲（すべての範囲は端点を含む）の周波数で、または別の周波数で繰り返されてよい。いくつかの実施形態では、測定が  $n - 1$  回繰り返された後、約 100 個のキャリア（たとえば、電子）が時間ビンに蓄積されてよい。しかしながら、当然のようにこれは受け取られた光子の数に依存する。いくつかの実施形態では、時間ビンに蓄積されるキャリアの数は、50 と 1,000 の間など、10 と 10,000 の間、または任意の他の適切な数であってよい。方法 2800 は、光子が捕獲されることが所望される任意の適切な期間にわたって行われてよい。蛍光寿命測定のコンテキストでは、方法 2800 を行う適切な期間は、たとえば、10 ミリ秒であり得る。いくつかの実施形態では、測定 2820 は、MHz 範囲である周波数で繰り返されてよい。いくつかの実施形態では、時間ビンは、ピコ秒またはナノ秒のスケールで分解能を有することができる。

#### 【0083】

割り当てられた数  $n$  の測定が行われると、方法は、時間ビンを読み出す工程 2810 に進む。工程 2810 では、電荷はビンから、浮遊拡散部を含み得る読出ノード 111 に対して移送される。電荷は、個々のビンから読出ノード 111 に対して順次移送されてよい。各ビンについて、電荷は読出ノード 111 に対して移送され、次いで、図 6 に一例が示される読出回路 110 を用いて電圧に変換されてよい。電荷を各ビンから移送するためには、電極 213 および / または 214（図 3）の電圧はビンと読出ノード 111 との間の電位障壁を低下させるように変化してよい。読出シーケンスの一例は、読出ノード 111 の電圧をリセットし、次いで、ビン 0 と読出ノード 111 との間の電位障壁 212 を低下させるように電極 213 の電圧を変化させることによって、電荷をビン 0 から読出ノード 111 に対して移送することである。電荷をビン 0 から読出ノード 111 へと流れさせる電位勾配が確立されてよい。これは図 5 E に示される。読出ノード 111 に対して移送される電荷は、次いで電圧に変換され、読み出されてよい。次いで、読出ノード 111 の電圧はリセットされてよい。次いで、ビン 1 と読出ノード 111 との間の電位障壁 214 を低下させるように電極 215 の電圧を変化させることによって、電荷がビン 1 から読出ノード 111 に対して移送される。電荷をビン 1 から読出ノード 111 へと流れさせる電位勾配が確立されてよい。これは図 5 F に示される。

#### 【0084】

図 6 は、図 3 における線 A - A' に沿ったピクセル 200 の一例の断面図を示す。示されるように、電極 206, 203 および 213 は半導体基板上に、または半導体基板の上方に形成されている。光は、光源 120 から光子吸収 / キャリア発生エリア 102 で受け取られる。光源 120 は、限定ではなく例として（たとえば、核酸に連結された）発光性サンプルまたはイメージングアプリケーションにおいてイメージングが行われる領域もしくはシーンを含む、任意のタイプの光源であり得る。光源 120 は、不要な励起レーザ光を含み得る。遮光体 121 は、たとえば、迷励起光（stray excitation light）または他の迷光によって電荷が貯蔵ビンまたは読出ノードに直接発生するのを

10

20

30

40

50

防止するように、光が基板の別の部分に到達するのを防止する。遮光体 121 は、限定ではなく例として集積回路の金属層のような、任意の適切な材料で形成され得る。図 6 は、除去中の電荷移送の反対方向（左方への）とビンへの移送（右方）とを示す。

#### 【0085】

##### 例示的な読出回路構成およびシーケンス

図 6 に示されるように、ピクセル 200 は、電荷キャリア貯蔵領域 108 の電荷貯蔵ビンに貯蔵された電荷を読み出すことを可能にする読出回路構成 110 を含むことができる。ピクセル 200 は、読出回路構成 110 が読出増幅器を含むようなアクティブ・ピクセル、または読出回路構成 110 が読出増幅器を含まないパッシブ・ピクセルであり得る。任意の適切なタイプのアクティブ・ピクセルまたはパッシブ・ピクセル読出回路構成が使用されてよい。読出回路構成 110 が読出増幅器を含む場合、読出増幅器は、電荷貯蔵ビン（たとえば、ビン 0, ビン 1）に蓄積された電荷を入力として取り込むことができ、電荷貯蔵ビン内の電荷を表す電圧を出力として生成することができる。

#### 【0086】

読出回路構成 110 が読出増幅器を含む場合、任意の適切なタイプの増幅器が使用されてよい。適切な増幅器の例は、共通ソース構成に基づく増幅器、およびソースフォロワ構成に基づく増幅器を含む。ソースフォロワ構成に基づく読出回路構成 110 の一例が図 6 に示されている。図 6 に示されるように、読出領域 110 は、ソースフォロワバッファトランジスタ  $s_f$ 、リセット・トランジスタ  $r_t$ 、および行選択トランジスタ  $r_s$  を備えてよい。しかしながら、本明細書に説明されている技法はいかなる特定の増幅器構成にも限定されない。いくつかの実施形態では、1 または複数の移送電極 213, 215 は読出回路構成 110 の一部であり得る。

#### 【0087】

ノイズ・リダクション技法を含む任意の適切な読出技法が使用されてもよい。いくつかの実施形態では、読出回路構成 110 は、相関二重サンプリングを使用して電荷キャリア貯蔵ビンを読み出すことができる。相関二重サンプリングは、未定の量のノイズを含むリセット電圧レベルのノードの第 1 のサンプルが取り出され、同じ未定のノイズを含むノードの信号レベルの第 2 のサンプルが取り出され得る、技法である。ノイズは、サンプリングされた信号レベルからサンプリングされたリセット・レベルを引くことによって差し引くことができる。

#### 【0088】

時間ビンを読み取ることは、上述したように、電荷貯蔵ビンのそれぞれに集約された電荷の量を対応する電圧に変換することを含んでよい。時間ビンからの読出は、50 Hz ~ 100 Hz, 10 Hz ~ 500 Hz、または別のレートなどの、任意の適切なレートで行われてよい。いくつかの実施形態では、ピクセルの電荷キャリア貯蔵ビンからの読出は、同一のピクセルの 1 または複数の電荷キャリア貯蔵ビンにおける電荷キャリアの収集と同時に行われてよい。移送電極 213 および 215 は、各ビンに別個に結合されている電荷であってよい。共通の読出ノード 111 は、すべての移送電極に結合されている電荷であってよい。図 6 に示されるように、読出ノード 111 はリセット・トランジスタ  $r_t$  のソースに接続されてよい。リセット・トランジスタ  $r_t$  および行選択トランジスタ  $r_s$  のドレインは、高電圧源に接続されてよい。リセット・トランジスタ  $r_t$  および行選択トランジスタ  $r_s$  のゲートは、行駆動回路によって制御されてよい。いくつかの実施形態では、トランジスタ  $s_f$  のソースは、行選択トランジスタ  $r_s$  のドレインに接続されてよい。トランジスタ  $s_f$  のゲートは、読出ノード 111 に接続されてよい。いくつかの実施形態では、ソースフォロワのソースは、列線読出部に接続されてよい。

#### 【0089】

##### 時間ビンの数およびタイミング

任意の適切な数の時間ビンが使用されてよい。図 3 には、2 つのビンを有するピクセルの例が示されている。しかしながら、任意の適切な数のビンを有するピクセルが、所望の時間分解能および他の因子に基づいて生成されてもよい。ビンの数の増加は、各ピクセル

10

20

30

40

50

によって占められるエリアを増大させる可能性があり、ピクセルの全体数を減らすことによって、またはより小さい特徴サイズを有する作製プロセスを使用することによって達成され得る。少数のピンを使用することにより、チップに取り付けられるピクセルの数の増加を可能にすることができる。いくつかの実施形態では、特定の期間内に到着する光子の数を決定するために、単一のピンが使用され得る。

#### 【 0 0 9 0 】

時間ピンのタイミングは、任意の適切な方法で選択されてよい。いくつかの実施形態では、時間ピンのタイミングは、各測定期間においてタイミングが同じになるように固定され得る。タイミングは、グローバル・タイミング信号に基づいて設定され得る。たとえば、タイミング信号は、測定期間の開始を確立することができ、時間ピンは、タイミング信号から経過した所定の量の時間に基づいて開始および終了するように制御され得る。蛍光寿命測定コンテキストでは、時間ピンのタイミングは、検出されると予想される蛍光寿命の可能な範囲に基づいて、励起パルスのタイミングに関して設定され得る。飛行時間型イメージングのコンテキストでは、時間ピンのタイミングは、イメージングの行われるシンの予想される距離範囲に基づいて設定され得る。しかしながら、いくつかの実施形態では、時間ピンのタイミングは、可変またはプログラム可能であり得る。

#### 【 0 0 9 1 】

いくつかの実施形態では、時間ピンのタイミングは、測定 2820 の測定期間を開始するトリガ・イベントのタイミングに基づいて設定され得る。蛍光寿命測定のコンテキストでは、時間ピンのタイミングは、フルオロフォアを励起する励起パルスのタイミングを検出することに応答して設定され得る。たとえば、光励起パルスがピクセル 200 に到達すると、キャリアのサージが光子吸収 / キャリア発生領域 102 からドレインに対して移動し得る。励起パルスに応答するドレインにおける光生成キャリアの蓄積が、ドレインの電圧の変化を引き起こし得る。したがって、いくつかの実施形態では、励起パルスは、ドレインの電圧を検出することによって検出され得る。たとえば、コンパレータは、ドレインの電圧を閾値と比較することができ、ドレインの電圧が閾値を超えたときにパルスを生成することができる。パルスのタイミングはトリガ・イベントのタイミングを示すことができ、このタイミングに基づいて時間ピンのタイミングが設定され得る。しかしながら、本明細書に説明されている技法はこれに関して限定されず、任意の適切な技法が測定の開始を検出するために使用されてよい。

#### 【 0 0 9 2 】

いくつかの実施形態では、集積デバイスは、時間ピンのタイミングを変更可能なようにプログラム可能であり得る。いくつかの実施形態では、時間ピンのタイミングは、実行される測定の特定のセットについてプログラムされ得る。たとえば、集積デバイスが、第 1 の範囲内の寿命を有する第 1 のセットのマーカを使用する第 1 のタイプの試験のために使用される場合、時間ピンは、その範囲内のマーカの寿命を弁別するために適切な値にプログラムされ得る。しかしながら、異なる寿命を有する異なるマーカを使用する別のタイプのテストのために集積デバイスが使用される場合、時間ピンは、第 2 のタイプの試験で使用されるマーカに適した異なる時間間隔に対応するように時間ピンをプログラミングすることによって変更され得る。いくつかの実施形態では、時間ピンのタイミングは、測定のセットの結果に基づいて測定間で適応的に制御されてよい。

#### 【 0 0 9 3 】

##### 例示的な貯蔵ピン

電荷貯蔵ピンを半導体領域内のポテンシャル井戸（ウェル）として実装するいくつかの手法がある。いくつかの実施形態では、ポテンシャル井戸は、部分的に電極 203 または 205 内にあってよい。電荷を井戸の中および井戸の外に移動するための 2 つのタイプの移送がある。蓄積の移送は電荷を井戸へと移動させる。読出部の移送は電荷を井戸の外に移動させる。

#### 【 0 0 9 4 】

以下はポテンシャル井戸の可能な特性である。すなわち、

10

20

30

40

50

- ・井戸は、少なくとも 100 個の電子の蓄積された電荷を 30 にて 10 ms 間に貯蔵するのに充分な深さであってよい。

- ・電極 203 または 205 は、領域 102 を井戸に対して電荷結合する。

- ・井戸は、少なくとも部分的に電極 203 または 205 内にあってよい。

- ・蓄積の移送中、井戸は領域 102 の完全な空乏電圧よりも高い電位にあってよい。

- ・井戸の完全な空乏電圧は、読出の移送中の浮遊拡散部リセット・レベルよりも低い電位にあってよい。

- ・井戸の電位は、蓄積の移送と読出の移送との両方の要求に適うように、動的に変調されてよい。

#### 【0095】

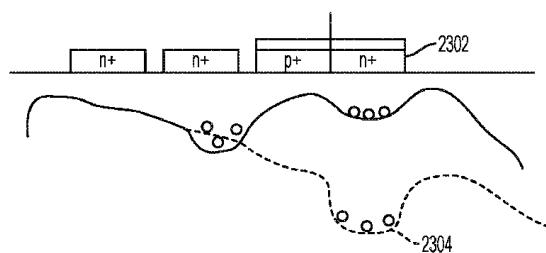

10 ピン 0 またはピン 1 などのピンについてのポテンシャル井戸を作り出すために、いくつかの技法が存在する。一例として、電極 203, 205, 213 および 215 のうちの 1 または複数が相補的ドーピング(分割ドーピング)されてよい。図 7 は、p+ 領域および n+ 領域を有する分割ドーピングされた電極 2302 を示す。図 7 に示されるように、分割ドーピングされた電極 2302 の n+ 領域は、電荷キャリア(たとえば電子)を閉じ込めることが可能なポテンシャル井戸を n+ 領域の下に生成してよい。図 7 は、分割ドーピングされた電極 2302 の電圧を高く保持することにより、電荷キャリア(たとえば電子)をポテンシャル井戸 2304 に閉じ込めることが可能な破線で示されるような電位勾配を生成できることを示す。分割ドーピングされた電極 2302 の下の電位を上昇させて、たとえば、ポテンシャル井戸 2304 内にトラップされた電荷を電荷貯蔵ピンに移送することを可能にすることができる。

#### 【0096】

電極 2302 には、領域 102 の側に P+ およびピン側に N+ にドーピングされてよい。仕事関数の差は、たとえば 1 ボルトなどの電圧勾配を生成し得る。第 2 の選択肢は、電極によって変調される井戸の位置に埋設されたチャネルの n 型インプラントを置くことである。電極が高い電位にあるとき、井戸の電位は収集領域を超えて上昇する。第 3 の選択肢は、領域 102 のダイオードと同一であるレプリカのダイオードを生成することである。そのダイオードは、領域 102 のダイオードと同様に、同一のインプラントを有する埋設ダイオードであってよい。そのダイオードは、障壁 202 または 204 と移送電極 213 との間に形成されてよい。空乏電圧は、読出移送ゲートにわたって延びている n 型インプラントにより調整されてよい。障壁 202 または 204 を形成する電極は、N+ にドーピングされてよく、一方で読出移送電極は P+ にドーピングされてよい。いくつかの実施形態では、ピンについてのポテンシャル井戸を形成するように上記の技法の組合せが用いられる。

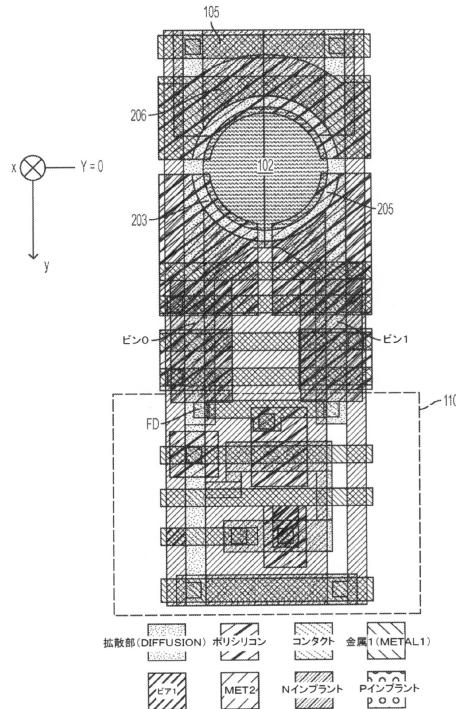

#### 【0097】

図 8 は、いくつかの実施形態による直接ビニングピクセル 200 の一例の平面図を示す。示されるように、領域 102 は円形を有するが、しかしながら本明細書に説明されている技法はこれに関して限定されない。

#### 【0098】

図 9 は、いくつかの実施形態による直接ビニングピクセル 200 の別の例の平面図を示す。図 9 は、下のポリシリコン電極の上に位置するとともにそのポリシリコン電極に電気的に接続されている金属端子を示す。金属領域 c d は除去領域 105 に接続されており、金属領域 b0 は電極 206 に接続されており、金属領域 b1 は電極 203 に接続されており、金属領域 b2 は電極 205 に接続されている。金属領域 t1 は、ピン 0 に対する移送ゲートとして機能するポリシリコン電極と接続し、読出用のピン 0 に貯蔵されている電荷を外に移送することができる。同様に、金属領域 t2 は、ピン 1 に対する移送ゲートとして機能する別のポリシリコン電極と接続し、読出用のピン 1 に貯蔵されている電荷を外に移送することができる。

#### 【0099】

10

20

30

40

50

ポケット・インプラントが、“TG”層により示される電極203および205の下部に位置する。拡散部とポケット・インプラントとの共通部分には、N=0のラベルが付される。側壁インプラントのため、黒いマーキングはポケット電位が生じるところである。この例では、ポケットは電極間に延びている。しかしながら、本明細書に説明されている技法およびデバイスはこれに関して限定されない。

#### 【0100】

ピンの位置は、電極の下、電極によって覆われない領域、または電極の下と電極によって覆われない領域との両方であってよい。たとえば、ピン0は、電極203の下、電極203とt1に接続されているポリシリコン移送電極との間であって電極203の下でない領域、または電極203の下と電極203の下でない領域との両方にあってよい。

10

#### 【0101】

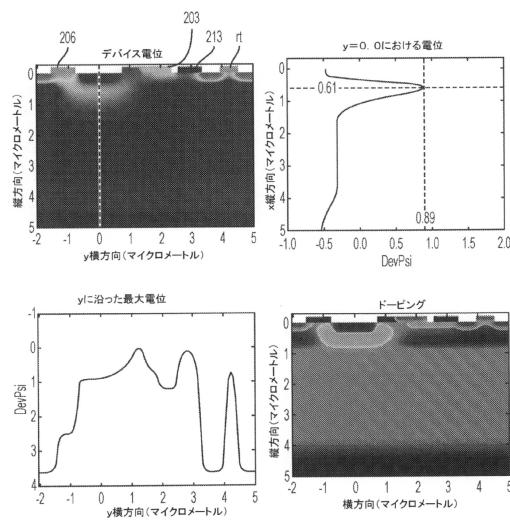

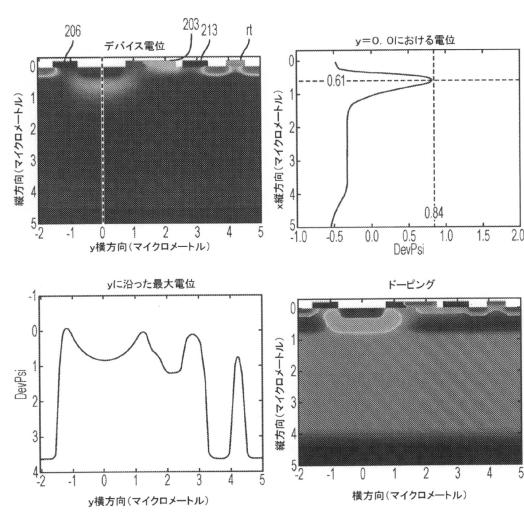

図10～図14は、ピクセル200の実施形態についての、半導体材料におけるドーピング濃度と方法2800の様々な工程におけるピクセル200の電位勾配とを示す。

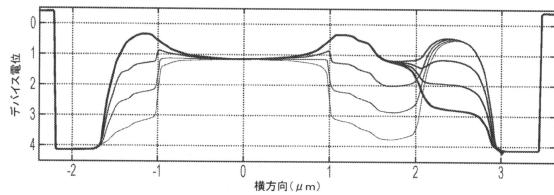

図10は、工程2802の除去期間中の電位を示し、また図5Aに対応する。左下のプロットは、図8のy次元に沿った電位を示す。光子吸収/キャリア発生領域102は、y=0に中心が置かれる。左下および左上のプロットに見られるように、y=0に関して左方への除去領域の電極が高くなるとき、電位はy=0の左方の除去領域に向かって降下する。したがって、キャリアは光子吸収/キャリア発生領域102から除去領域105に対して移送される。右下のプロットは、ドーピング濃度を示す。

20

#### 【0102】

図11は、除去領域およびピンに対する電位障壁が上昇されている(図5Cのように)期間中の電位を示す。この状態では、領域102において生成される任意の電荷キャリアが、y=0のまわりに生成されるボウル形ポテンシャル井戸のため、領域102に閉じ込められる。

#### 【0103】

図12は、電荷がピンに対して移送され得る工程2806および2808中の電位を示し、図5Bおよび図5Dに対応する。y次元の電位は、電荷がピン0およびピン1に対して移送される場合について同様である。これに関して、図12は、キャリアを一方のピン对他方のピンに向かって駆動する図8の横方向の次元に沿った勾配を示さない。図12に示されるように、電位は、ピンに向かって領域102の右方へと落下し、対応するピンの中に存在する任意のキャリアを駆動する。

30

#### 【0104】

図13および図14は、読出段階中のポテンシャルを示す。図13は、移送ゲートによって生成される電位障壁を低下させることによる、ピンに貯蔵されている電荷の浮遊拡散部FDへの移送を示す。図14は、浮遊拡散部FDのリセットを示す。

#### 縦方向除去

本発明者らは、半導体基板内の深くにおける電荷キャリアの光生成から問題が生じることを認識し理解している。基板内の深くにかなりの電位勾配がない場合があるので、この領域において生成されたキャリアは遅い移動であってよく、予測可能な経路を取らなくてよい。いくつかの場合では、深部で生成されたキャリアは、最終的に表面に移動してよく、領域102に閉じ込められてよい。そのようなキャリアは電流測定期間に到着した光子に対応しないので、そのキャリアを領域102に収集することは望ましくなく、したがって、除去される必要があるノイズである。本発明者らは、直接ビニングピクセルまたは別のタイプのピクセルに用いられ得る、深部生成キャリアを除去する構造および技法を開発した。そのような構造および技法を論じる前に、深部生成キャリアの発生および移動が論じられる。

40

#### 【0105】

図15に示されるように、吸収深さは、光が吸収される前に長波長ほど半導体の中深くに入り込むように、波長の関数である。吸収深さは、吸収係数の逆数、すなわち $1/a$ によって与えられる。吸収深さは、光が表面強度の約36%に低下する材料の中への距離、

50

$1/e$ 、すなわち 1 タウ( )であるように、強度は基板の中へと指數関数的に減衰する。短波長の光(青色)は、表面から短距離内において吸収されるように、より大きい吸収係数を有し、一方で長波長の光(赤色)はより低い割合にて吸収される。

#### 【0106】

エピウェーハは、高添加のハンドルを有する、3~5マイクロメートルの厚さの低添加(たとえば  $2 \times 10^{15} \text{ cm}^{-3}$ )エピタキシ領域を含む。アクティブエリアには電位勾配がないので、電場は最小である。キャリアは3つの原因

- 1) 热

- 2) ドリフト

- 3) 拡散

から移動を受ける。

10

#### 【0107】

電場またはドーピング勾配がないと、キャリアは半導体の振動原子と確率過程において衝突する。キャリアはドーパントおよび他のキャリアと静電的に相互作用する。 $300^\circ\text{K}$ における自由衝突時間の時間は、 $1 \text{ e}^{-7} \text{ cm/s}$ の熱運動速度で約  $1 \text{ e}^{-13} \text{ s}$ である。特有の平均自由行程は約  $10 \text{ nm}$ である。

#### 【0108】

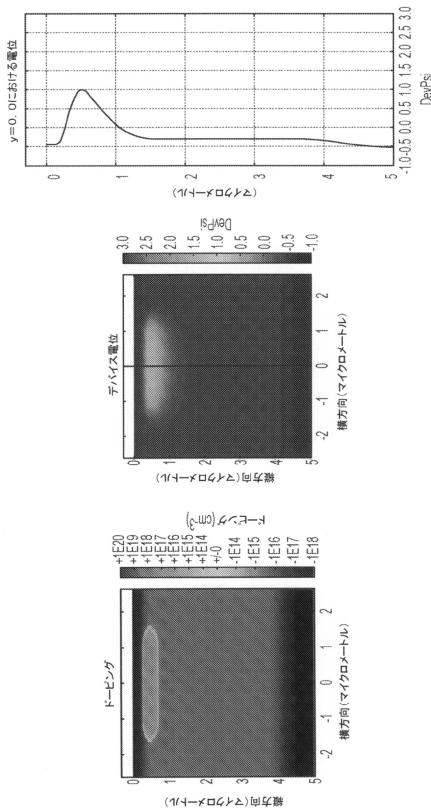

図16は、領域102のフォトダイオードについてのドーピング・プロファイルおよび電位を示す。完全に空乏化された低添加( $1 \times 10^{16} \text{ cm}^{-3}$ )埋設n型領域は、キャリアを電位が最も高い領域へと引き込む電場を生成する。空乏領域の下で発生したキャリアは、閉じ込められる前に電場へと拡散する。拡散過程は遅く、キャリアが発生した後にキャリアを井戸に到着させる。

20

#### 【0109】

埋設ダイオード領域の深さは、インプラントが(エネルギー <  $400 \text{ keV}$ )に実装されているステージにて、CMOS処理によって制限されてよい。アクティブ領域および電場の拡張部は、 $1.5 \mu\text{m}$ 未満の深さであってよく、約20%の光電子が平坦な電場を有する領域に入ることとなる。 $10 \text{ ns}$ のサイクルでは、100万個の光子をシミュレートした後、約40個に1個の光子が半サイクル、すなわち  $5 \text{ ns}$  後に、基板に依然として立ち遅れている。最初の  $100 \text{ ps}$  内では、約10個に1個の光子が依然として立ち遅れている。これは、 $100 \text{ ps}$  の除去レイテンシを用いた10対1の最良の場合の除去比を示す。

30

#### 【0110】

深部で生成されたキャリアを排出すること、および/またはそれらのキャリアが表面付近のフォトダイオード領域に到達するのを少なくとも防止することが所望される。発明者らは、そうするための構造および技法を開発した。いくつかの実施形態では、「深部生成キャリア」は、表面の下において1マイクロメートルを越えて生成されたキャリアを呼ぶ。しかしながら、キャリアが問題となる深さが様々な材料および処理技術について変化し得るので、本発明はこれに関して限定されない。

30

#### 【0111】

1つの技法は、深部生成キャリアがフォトダイオードに入るのを妨げるドレインまたは障壁をフォトダイオードの下に形成する。図17は、深部生成キャリアが表面に到達するのを防止することができる深部ドーピングされた領域を示す。深部ドーピングされた領域は、 $900 \text{ keV}$ のエネルギー、または任意の他の適切なエネルギーを用いた深部インプラントであってよい。いくつかの実施形態では、深部インプラントは、表面を基板の底部と同一の電位とするように、不連続(たとえば図20におけるものなど)であってよい。図18は、 $10 \text{ ns}$ 間の電子運動のシミュレーションを示し、示すキャリアは深部n井戸領域へと引き込まれる。

40

#### 【0112】

深部ドーピングされた領域がn型である場合、深部生成キャリアをドレインに収集および移送するように、除去領域に、したがって電源電圧に接続されてよい。深部ドーピング

50

領域が p 型である場合、深部ドーピングキャリアを妨げ、そのキャリアがフォトダイオードに到達するのを防止する障壁が形成されてよい。

#### 【 0 1 1 3 】

3 ~ 5  $\mu\text{m}$  の厚さ、または任意の他の適切な厚さのエピタキシ基板を用いるとき、深部キャリアは除去されてよい。表面から 1  $\mu\text{m}$  以内の光生成キャリアは、空乏化されたダイオード N 領域へと収集されてよい。

#### 【 0 1 1 4 】

2 つの別々の技法が深部キャリアを扱うように実装されてよい。

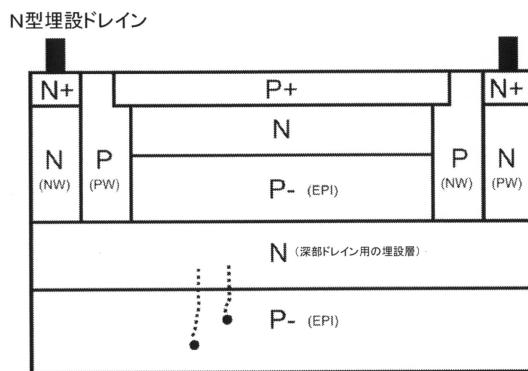

1 ) 1 つの技法は、埋設ドレインである。図 19 は、N 型の埋設層（深部ドレイン）が高い電位（たとえば 3 ボルト）でバイアスがかけられている一例を示す。深部の光電子は、N 型の埋設層へと引き込まれ、コンタクトにて排出される。

#### 【 0 1 1 5 】

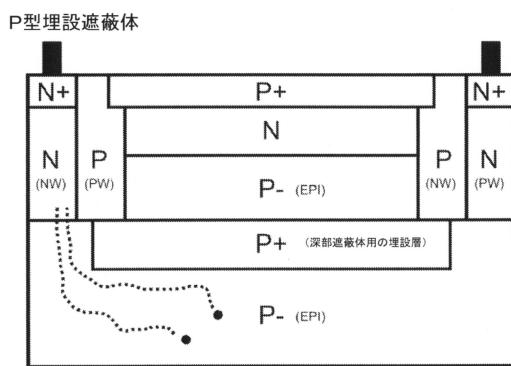

2 ) 別の技法は、埋設遮蔽体である。図 20 は、基板と接触する P + 型の埋設層（深部遮蔽体）を示す。深部の光電子は、P + 型の埋設層から反発され、N 型ピックアップへと拡散し、コンタクトにて排出される。P + 型の埋設層は、不連続であり、ダイオード構造を低電位の底面から基板の電位へとバイアスがかけられたままにする。ダイオードとインターフェースする電極の速い動的スイッチングでは、これはダイオードの空乏電圧が高周波数においてさえも固定されたままであるので、利点となり得る。

#### 【 0 1 1 6 】

埋設ダイオードの左側および右側の N および P 領域は、標準 N ウェル ( NW ) および P ウェル ( PW ) 処理を用いて実装されてよい。N ウェルに対する N + タップは、標準ソース・ドレイン高添加インプラントであってよい。深部の N 領域は、1 0 0 0 keV を超える高エネルギーのリンインプラントであってよい。深部の P + 領域は、5 0 0 keV を超える高エネルギーのホウ素インプラントであってよい。

#### 【 0 1 1 7 】

深部生成キャリアを排出するための別の技法は、深部生成キャリアを表面から引き込むドリフトの場を基板に生成することである。ドリフトの場は基板に縦方向電位勾配を生成することによって生成されてよい。

#### 【 0 1 1 8 】

深部生成キャリアを回避する別の技法は、半導体領域（たとえばエピタキシャル領域）を、3 マイクロメートルよりも薄く、2 マイクロメートルよりも薄くまたは 1 マイクロメートルよりも薄くなど、非常に薄く作製することである。

#### 【 0 1 1 9 】

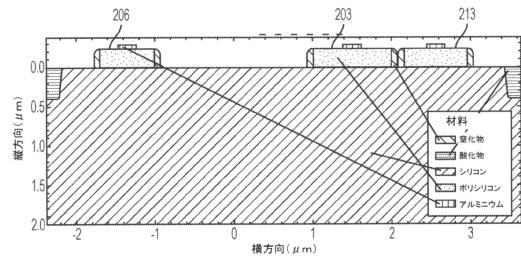

##### 追加の実施形態

図 21 は、集積回路が作製され得る材料の例を示す。ピクセルは半導体領域に形成されやすく、いくつかの実施形態では半導体領域はシリコンであってよい。酸化シリコン領域などの絶縁領域は、集積回路のエリアを互いに絶縁してよい。電極（たとえば電極 206, 203 および 213 ）は、ポリシリコンまたは別の導体から形成されてよい。絶縁スペーサは電極の側に配置されてよい。たとえば、絶縁領域は窒化シリコンから形成されてよい。アルミニウムなどの金属が電極に対して電気的に接触するように電極上に配置されてよい。しかしながら、本明細書に説明されるデバイスは特定の材料に関して限定されないので、他の材料が用いられてよい。

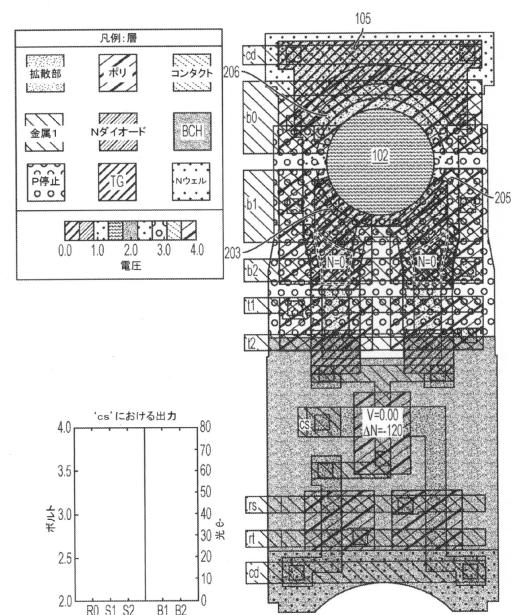

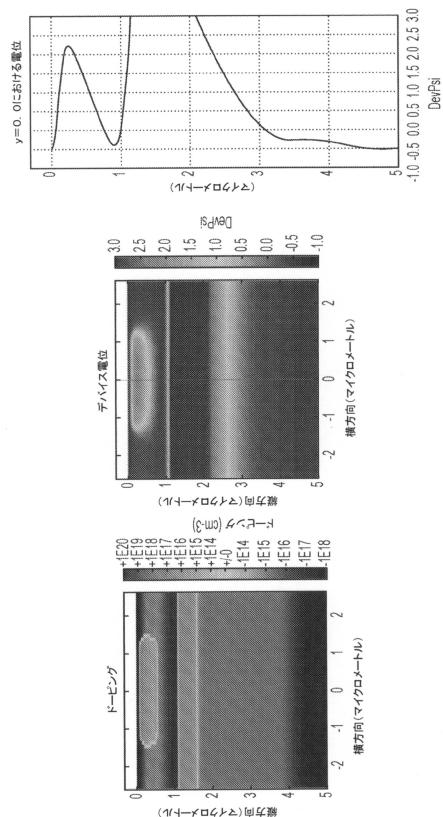

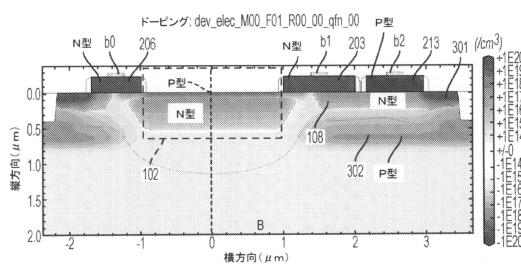

#### 【 0 1 2 0 】

図 22 は、いくつかの実施形態による、ピクセル 200 についてのドーピング・プロファイルの一例を示す。光検出領域 102 は、P 型領域を表面に、また埋設 N 型領域を有するフォトダイオードを含む。電極 206 および 203 は、N 型にドーピングされてよい。電極 213 は P 型にドーピングされてよい。電極 203 と電極 213 との間のドーピングの差は、複数のインプラントとは対照的に、領域 108 に形成された 1 つのインプラントによって電荷キャリアの閉じ込めができるこことを可能とする仕事関数の差を生じ得る。しかしながら、これは選択的であり、いくつかの実施形態では、領域 108 は複数のインプ

10

20

30

40

50

ラントを含んでよい。電極 203 および / または 213 の下の電荷貯蔵領域 108 は、この例では N 型にドーピングされている。高添加された領域 301 は、フォトダイオードの反対にある電極 213 の向こう側の半導体領域に形成されてよい。障壁インプラント 302 は、キャリアが基板内の深くから電荷貯蔵領域 108 に入ることを防止するように形成されてよい。この例では、障壁インプラントは P 型であってよい。

#### 【0121】

10 ピンは、213 電極を通じて拡散部へと、電極 203 の半分にわたるインプラントを含んでよい。出力に対するピンの障壁は、P+ と N+ とにドーピングされたゲート電極間の仕事関数差によって形成されてよい。これは充分な 1.1 V の障壁の差を形成することが可能である。この差は、電極 203 と電極 213 との間に異なる電圧を印加することによって拡張されることが可能である。たとえば、電極 213 は 0 V に設定されることが可能であり、電極 203 は 0.4 V に設定されることが可能である。これは 1.5 V の差を生じる。

#### 【0122】

20 入力に対する電位障壁は、ダイオードのインターフェースにてホウ素インプラントによって形成されてよい。障壁の電位は、ピンのインプラントの最大空乏電圧と関連する。ピンのインプラントのドーズ量およびエネルギーは、ピンの最大電位深さを決定してよい。これは、ピンの入力側に対する充分な障壁を可能とするように、処理において調節されてよい。出力側は、仕事関数の差のため頑強な障壁を有し、また電圧によって調節可能である。入力障壁は調節するために、より重要である。ピンの電位深さは、電極 203 に電圧を印加されることによって調整されてよい。しかしながら、これはまた入力ダイオードに対する障壁に影響を与える。入力ダイオードに対する障壁は、ゲート制御されてよい。したがって、ピンのインプラントのドーズ量およびエネルギーは、最大のピンの空乏電位に充分な障壁を与えるように調節されてよい。ピンのインプラントと同一のマスクを使用して、深部高ドーズ量ホウ素インプラントは、迷走電子のピックアップを防止するための障壁を基板に形成することができる。

#### 【0123】

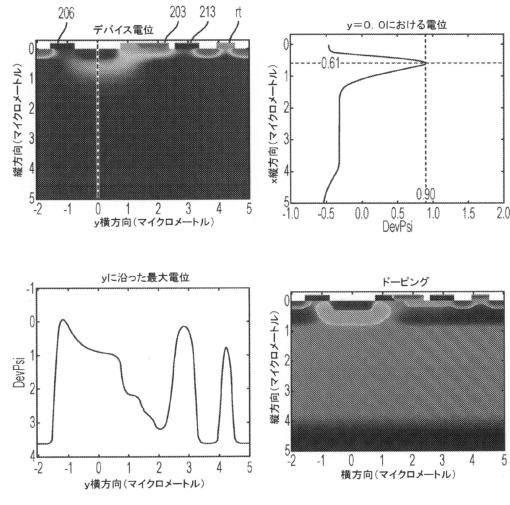

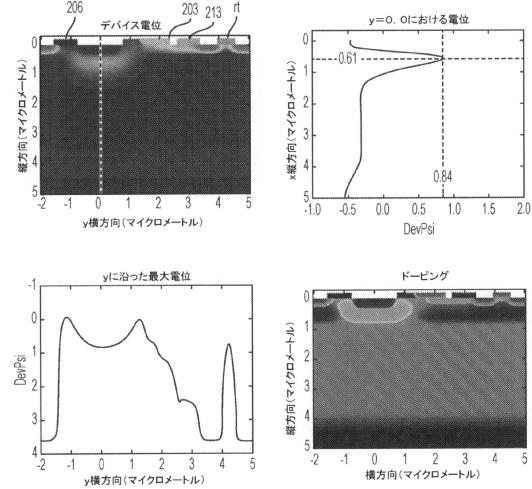

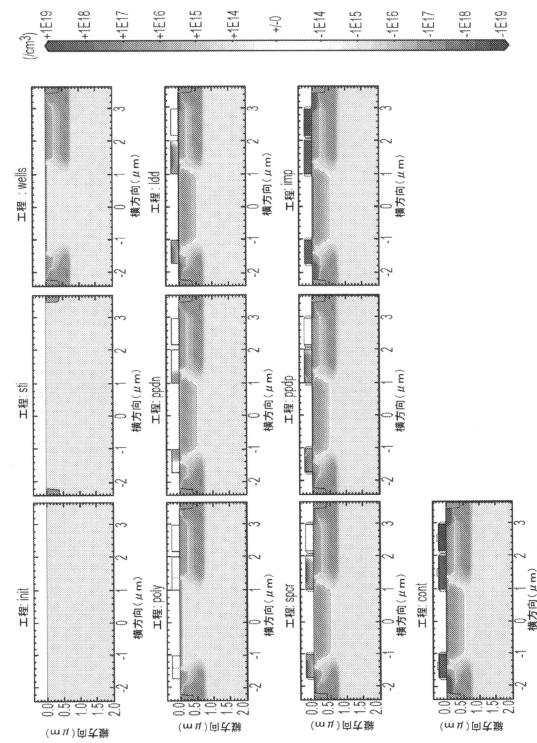

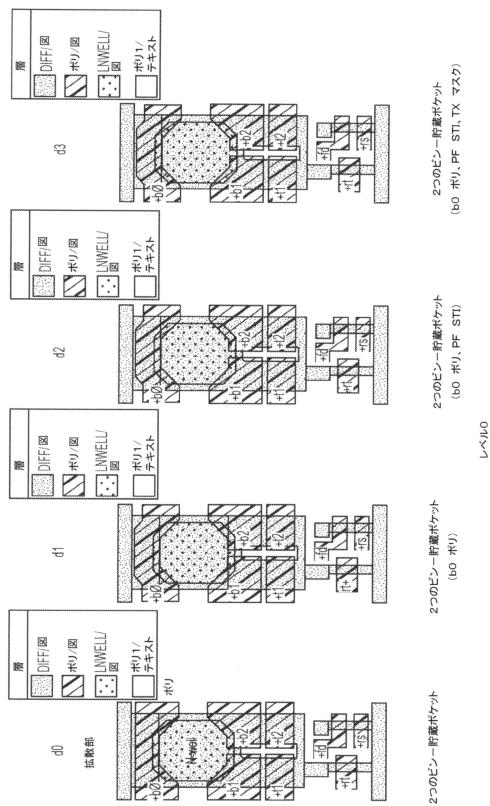

30 図 23 は、図 22 に示されるドーピング・プロファイルとともにピクセル 200 を形成するための例示的な処理シーケンスを示す。処理はドーパント・インプラントおよび / または拡散部の任意の適切なシーケンスを含んでよい。しかしながら、図 23 の処理は例であり、また他の適切な処理が用いられてよいことが理解される。

#### 【0124】

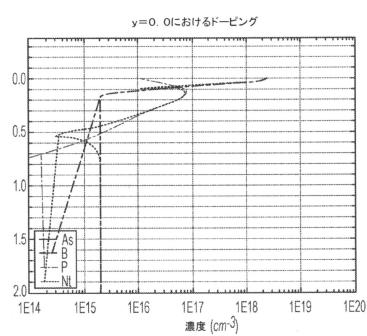

図 24 は、図 22 の線  $y = 0$  に沿ったヒ素、ホウ素、リンおよび N<sub>t</sub> についての例示的なドーピング・プロファイルのプロットを示す図。基板への深さが縦軸に、濃度が横軸に示される。

#### 【0125】

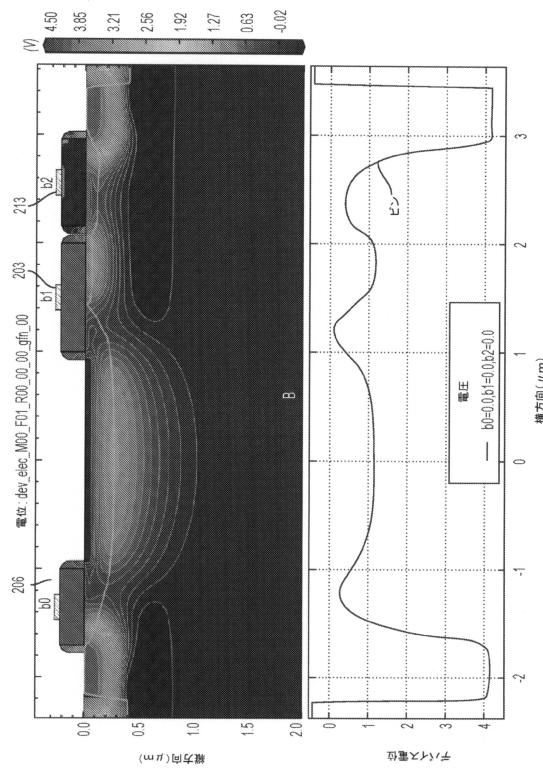

図 25 は、すべての電極の電圧を 0 V に設定することによってすべての障壁が閉じられるときの、図 22 のピクセルにおける電位のプロットを示す。示されるように、ピンにキャリアを閉じ込めることができるポテンシャル井戸が生成される。

#### 【0126】

40 図 26 は、電極 213 の電圧が 3 V に設定されるときの、図 22 のピクセルにおける電位のプロットを示す。電極 213 の電圧を上昇させることは、ピンと読出ノード 111 との間の障壁を低下させる。

#### 【0127】

図 27 は、電極 206, 203 および 213 の電圧が変化したときの基板内の電位の曲線を示す。

#### 例示的な集積回路の実現および集積光検出器の形成方法

いくつかの実施形態では、チップ 1300 は、標準的な CMOS ( 相補型金属酸化膜半導体 ) プロセスを使用してシリコン基板に形成され得る。しかしながら、本明細書に説明されている技法はこれに関して限定されず、任意の適切な基板または製造プロセスが使用

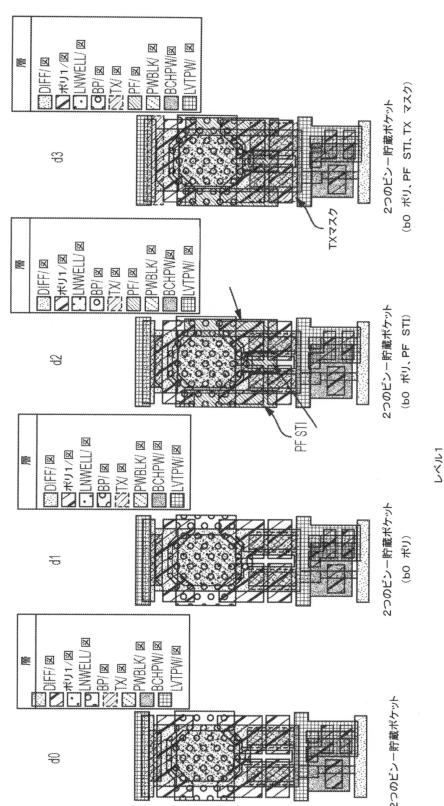

されてよい。図28～図32は、光検出器を形成する例示的な処理と4つの異なるピクセル設計d0～d3とを示す。図28は、半導体領域における拡散部およびNウェル領域、ならびに上に位置するポリ電極層とともにレベル0を示す。図29はレベル1を示し、図30はレベル2を示し、図31はレベル3を示し、図32はレベル4を示す。

#### 【0128】

##### ピクセル・アレイ／チップ・アーキテクチャ

図33は、いくつかの実施形態によるチップ・アーキテクチャの図を示す。図33に示されるように、集積回路またはチップ1300は、複数のピクセル100を含むピクセル・アレイ1302と、タイミング回路1306を含む制御回路1304と、電圧／電流バイアス発生回路1305と、インターフェース1308とを含むことができる。

10

#### 【0129】

ピクセル・アレイ1302は、たとえば矩形パターンなど任意の適切なパターンで配置されたピクセル・アレイ101を含む。ピクセル・アレイ1302は、任意の適切な数のピクセルを有することができる。ピクセル・アレイは、ピクセル・アレイ1302の行または列を読み出すための行導体および／または列導体を有することができる。ピクセルは、並列、直列、またはこれらの組合せで読み出され得る。たとえば、いくつかの実施形態では、ピクセルの行が並列に読み出されてよく、ピクセル・アレイの各行は順次読み出されてよい。しかしながら、本明細書に説明されている技法はこれに関して限定されず、ピクセルは任意の適切な方法で読み出されてよい。

#### 【0130】

ピクセル・アレイ1302は制御回路1304によって制御され得る。制御回路1304は、ピクセル・アレイ1302の動作を含むチップ1300上の動作を制御するための任意の適切なタイプの制御回路であり得る。いくつかの実施形態では、制御回路1304は、ピクセル・アレイ1302の動作およびチップ1300上の他の任意の動作を制御するようにプログラムされたマイクロプロセッサを含むことができる。制御回路は、そのような動作をマイクロプロセッサに行わせるためのコンピュータ可読命令（たとえばコード）を記憶するコンピュータ可読媒体（たとえばメモリ）を含むことができる。たとえば、制御回路1304は、各ピクセルにおける電荷キャリア分離構造の電極に印加される電圧を生成するのを制御することができる。制御回路1304は、上述されたように、キャリアを捕獲し、キャリアを移送し、またピクセルおよびアレイの読出を行うように、1つまたは複数の電極の電圧を変化させることができる。制御回路は、記憶されたタイミング方式に基づいて電荷キャリア分離構造の動作のタイミングを設定することができる。記憶されたタイミング方式は、上述されたように、固定式、プログラム可能、および／または適応性であり得る。

20

#### 【0131】

制御回路1304は、ピクセルの電荷キャリア分離構造の動作またはチップの他の動作のタイミングを取るためのタイミング回路1306を含むことができる。いくつかの実施形態では、タイミング回路1306は、電荷キャリアを精密に時間ビニングするために、電荷キャリア分離構造における電圧変化のタイミングを正確に制御するための信号の生成を可能にすることができる。いくつかの実施形態では、タイミング回路1306は、電荷キャリア分離構造に対して提供される信号のタイミングを正確に設定するための外部基準クロックおよび／または遅延ロック・ループ（DLL）を含むことができる。いくつかの実施形態では、2つのシングルエンド遅延線が使用されてよく、それぞれ段の半数は位相が180度ずれて配列される。しかしながら、任意の適切な技法が、チップ上の信号のタイミングを制御するために使用されてよい。

30

#### 【0132】

チップ1300は、チップ1300からの信号を送る、チップ1300で信号を受け取る、またはその両方のためのインターフェース1308を含むことができる。インターフェース1308は、ピクセル・アレイ1302によって検知された信号を読み出すのを可能にすることができる。チップ1300からの読出は、アナログ・インターフェースおよ

40

50

び／またはデジタル・インターフェースを使用して行われてよい。チップ 1300 からの読み出しがデジタル・インターフェースを使用して行われる場合、チップ 1300 は、ピクセル・アレイ 1302 から読み出された信号をデジタル信号に変換するための 1つまたは複数のアナログ - デジタル・コンバータを有することができる。いくつかの実施形態では、読み出しひ回路は、プログラマブル利得増幅器を含むことができる。1つまたは複数の制御信号が、インターフェース 1308 を介して外部ソースからチップ 1300 に対して提供され得る。たとえば、そのような制御信号は、行われる測定のタイプを制御することができ、これは、時間ビンのタイミングを設定することを含んでよい。

#### 【0133】

ピクセル・アレイ 1302 から読み出された信号の分析は、オンチップまたはオフチップの回路構成によって行われてよい。たとえば、蛍光寿命測定のコンテキストでは、光子到着のタイミングの分析は、フルオロフォアの蛍光寿命を近似することを含むことができる。任意の適切なタイプの分析が行われてよい。ピクセル・アレイ 1302 から読み出された信号の分析がオンチップで行われる場合、チップ 1300 は、分析を行うための任意の適切な処理回路構成を有してよい。たとえば、チップ 1300 は、制御回路 1304 の一部またはそれとは別個の、分析を行うためのマイクロプロセッサを有することができる。分析がオンチップで行われる場合、いくつかの実施形態では、分析の結果は、インターフェース 1308 を介して外部デバイスに送られてよく、または別様にオフチップに提供されてもよい。いくつかの実施形態では、分析のすべてまたは一部がオフチップで行われてよい。分析がオフチップで行われる場合、ピクセル・アレイ 1302 から読み出された信号および／またはチップ 1300 によって行われた任意の分析の結果は、インターフェース 1308 を介して外部デバイスに提供され得る。

#### 【0134】

いくつかの実施形態では、チップ 1300 は、以下のうちの 1つまたは複数を含むことができる。

- 1 ) オンチップのデジタル制御されるピクセル・バイアス発生器 (D A C)

- 2 ) シングルエンドのピクセル出力電圧信号を差動信号に変換し利得を信号に適用する

- 、オンチップのデジタル・プログラマブル利得増幅器

- 3 ) 出力レートで電力損失をスケーリングすることを可能にする、デジタル制御される増幅バイアス発生器 (amplifier bias generators)。

#### 【0135】

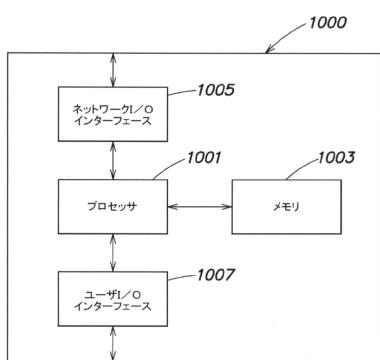

図 34 は、ピクセル・アレイを制御するため、またはピクセルからのデータの分析を行うための制御回路を実装するために使用され得る、例示的コンピューティング・デバイス 1000 のブロック図である。コンピューティング・デバイス 1000 は、1つまたは複数のプロセッサ 1001、および 1つまたは複数の有形の非一時的なコンピュータ可読記憶媒体（たとえばメモリ 1003）を含むことができる。メモリ 1003 は、実行されたときに上記の機能性のいずれかを実装するコンピュータ・プログラム命令を有形の非一時的なコンピュータ記録可能媒体に記憶することができる。プロセッサ 1001 は、メモリ 1003 に結合されてよく、そのようなコンピュータ・プログラム命令を実行して機能性を実現および実施させることができる。

#### 【0136】

コンピューティング・デバイス 1000 はまた、コンピューティング・デバイスが（たとえば、ネットワークを介して）他のコンピューティング・デバイスと通信できるネットワーク入力 / 出力 (I / O) インターフェース 1005 を含むことができ、また、1つまたは複数のユーザ I / O インターフェース 1007 を含むことができ、これを介して、コンピューティング・デバイスは、ユーザに対して出力を提供し、かつユーザから入力を受け取ることができる。ユーザ I / O インターフェースは、キーボード、マウス、マイクロフォン、ディスプレイ・デバイス（たとえば、モニタまたはタッチ・スクリーン）、スピーカ、カメラ、および／または様々な他のタイプの I / O デバイスなどのデバイスを含むことができる。

10

20

30

40

50

**【 0 1 3 7 】**

上述の実施形態は、多数の方法のいずれかで実装され得る。たとえば、実施形態は、ハードウェア、ソフトウェア、またはこれらの組合せを使用して実装されて得る。ソフトウェアで実装されるとき、ソフトウェア・コードは、単一のコンピューティング・デバイスに提供されるか、または複数のコンピューティング・デバイス間に分散されるかにかかわらず、任意の適切なプロセッサ（たとえばマイクロプロセッサ）またはプロセッサの集合において実行され得る。上述された機能を実施する任意の構成要素または構成要素の集合は、上述された機能を制御する1つまたは複数のコントローラとして総称的に考慮され得ることを理解されたい。1つまたは複数のコントローラは、専用ハードウェアを用いる、または上記に列挙された機能を実施するためにマイクロコードまたはソフトウェアを使用してプログラムされた汎用ハードウェア（たとえば、1つまたは複数のプロセッサ）を用いるなど、多くの方法で実装され得る。

**【 0 1 3 8 】**

これに関して、本明細書に説明されている実施形態の1つの実装は、1つまたは複数のプロセッサで実行されたとき、1つまたは複数の実施形態の上述された機能を実施するコンピュータ・プログラム（複数の実行可能命令）でエンコードされた少なくとも1つのコンピュータ可読記憶媒体（たとえば、RAM、ROM、EEPROM、フラッシュ・メモリもしくは他のメモリ技術、CD-ROM、デジタル多用途ディスク（DVD）もしくは他の光ディスク・ストレージ、磁気カセット、磁気テープ、磁気ディスク・ストレージ、もしくは他の磁気記憶デバイス、または他の有形の非一時的コンピュータ可読記憶媒体）を含むことを理解されたい。コンピュータ可読媒体は、本明細書に論じられた技法の態様を実装するために、媒体上に記憶されたプログラムが任意のコンピューティング・デバイス上にロードされ得るように可搬であってよい。加えて、実行されると上述された機能のいずれかを実施するコンピュータ・プログラムへの参照は、ホスト・コンピュータ上で動作するアプリケーション・プログラムに限定されないことを理解されたい。むしろ、コンピュータ・プログラムおよびソフトウェアという用語は、本明細書では一般的に、本明細書で論じられた技法の態様を実装するために1つまたは複数のプロセッサをプログラムするのに利用され得る任意のタイプのコンピュータ・コード（たとえば、アプリケーション・ソフトウェア、ファームウェア、マイクロコード、または他の任意の形態のコンピュータ命令）を参照するために使用される。

**【 0 1 3 9 】****追加の態様**

本発明の様々な態様は、単独で、組み合わせて、または上記に説明された実施形態において特に議論されていない様々な構成で使用されてよく、したがって、その用途において、上記の説明に記載されまたは図面に示されている構成要素の詳細および構成に限定されない。たとえば、一実施形態において説明された態様が、他の実施形態において説明された態様と任意の様式で組み合わされてよい。

**【 0 1 4 0 】**

また、発明は方法として具現化されることが可能であり、その例が提供されている。方法の一部として行われる動作は、任意の適切なやり方で順序付けられ得る。したがって、図示されているのと異なる順序で動作が行われる実施形態が構築されてもよく、それは、例示的実施形態で連続的な動作として示されたとしても、いくつかの動作を同時に実施することを含み得る。

**【 0 1 4 1 】**

特許請求の範囲において請求項要素を修飾するための「第1の」、「第2の」、「第3の」などの序数用語の使用は、それ自体では、別の請求項要素に対する1つの請求項要素のいかなる優先度、順位、もしくは順序も含意しておらず、または方法の動作が実施される時間的な順序も含意しておらず、それらは、単に、特定の名前を有する1つの請求項要素を（序数用語の使用がなければ）同じ名前を有する別の要素から区別するための標識として使用されて、請求項要素を区別する。

10

20

30

40

50

## 【0142】

また、本明細書で使用されている表現および用語は、説明のためのものであり、限定とみなされるべきではない。本明細書における「含む (including)」、「備える (comprising)」、または「有する (having)」、「含有する (containing)」、「含む (involving)」およびそれらの変形の使用は、その後に列挙される要素およびその均等物、ならびに追加的な要素を包含することを意図している。

## 【図面】

【図1A】

【図1B】

10

20

30

40

50

【図 2 A】

【図 2 B】

10

20

【図 3】

【図 4】

30

40

50

【図 5 A】

【図 5 B】

10

【図 5 C】

【図 5 D】

20

30

40

50

【図 5 E】

【図 5 F】

【図 6】

【図 7】

FIG. 7

10

20

30

40

50

【図 8】

【図 9】

【図 10】

【図 11】

【図 1 2】

【図 1 3】

10

20

【図 1 4】

【図 1 5】

30

40

50

【図 1 6】

【図 1 7】

10

20

【図 1 8】

【図 1 9】

30

40

50

【図 2 0】

【図 2 1】

10

【図 2 2】

【図 2 3】

20

30

40

50

【図 2 4】

【図 2 5】

10

20

30

40

【図 2 6】

【図 2 7】

50

【図 28】

【図 29】

10

20

30

40

【図 30】

【図 31】

50

【図 3 2】

【図 3 3】

10

20

【図 3 4】

30

40

50

---

フロントページの続き

## (51)国際特許分類

G 0 1 N 21/64 (2006.01)

F I

|         |        |   |

|---------|--------|---|

| G 0 1 J | 1/02   | Q |

| H 0 1 L | 27/146 | A |

| G 0 1 N | 21/64  | B |

アメリカ合衆国 0 6 4 3 7 コネチカット州 ギルフォード アンカス ポイント ロード 2 1 5

(72)発明者 ファイフ、キース ジー。

アメリカ合衆国 9 4 3 0 6 カリフォルニア州 パロ アルト マタデロ アベニュー 6 3 5

(72)発明者 ボワヴェール、デイビッド

アメリカ合衆国 9 5 1 2 0 カリフォルニア州 サン ノゼ グレイストーン レーン 1 8 9 0 0

審査官 鈴木 明

(56)参考文献 国際公開第2 0 0 7 / 1 1 9 6 2 6 ( WO , A 1 )

特開2 0 0 2 - 1 7 0 9 4 5 ( J P , A )

(58)調査した分野 (Int.Cl. , DB名)

|         |                         |

|---------|-------------------------|

| H 0 4 N | 5 / 3 0 - 5 / 3 7 8     |

| H 0 1 L | 2 7 / 1 4 - 2 7 / 1 4 8 |

| H 0 1 L | 3 1 / 1 0               |

| G 0 1 J | 1 / 0 2                 |

| G 0 1 N | 2 1 / 6 4               |