(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(51) Int. Cl.

H01L 27/108 (2006.01)

(45) 공고일자 2006년11월24일

(11) 등록번호 10-0648846

(24) 등록일자 2006년11월16일

|           |                 |           |                 |

|-----------|-----------------|-----------|-----------------|

| (21) 출원번호 | 10-2000-0025627 | (65) 공개번호 | 10-2001-0014906 |

| (22) 출원일자 | 2000년05월13일     | (43) 공개일자 | 2001년02월26일     |

| 심사청구일자    | 2005년05월13일     |           |                 |

|            |           |             |        |

|------------|-----------|-------------|--------|

| (30) 우선권주장 | 11-134992 | 1999년05월14일 | 일본(JP) |

|------------|-----------|-------------|--------|

(73) 특허권자

가부시키가이샤 한도오따이 에네루기 켄큐쇼

일본국 가나가와肯 아쓰기시 하세 398

(72) 발명자

무라카미사토시

일본국가나가와켄아쓰기시하세398가부시키가이샤한도오따이에네루기

켄큐쇼내

히라카타요시하루

일본국가나가와켄아쓰기시하세398가부시키가이샤한도오따이에네루기

켄큐쇼내

후지모토에츠코

일본국가나가와켄아쓰기시하세398가부시키가이샤한도오따이에네루기

켄큐쇼내

야마자키유

일본국가나가와켄아쓰기시하세398가부시키가이샤한도오따이에네루기

켄큐쇼내

야마자키스훈페이

일본국가나가와켄아쓰기시하세398가부시키가이샤한도오따이에네루기

켄큐쇼내

(74) 대리인

이병호

정상구

신현문

이범래

심사관 : 최봉목

전체 청구항 수 : 총 39 항

(54) 커패시터, 반도체 장치 및 이의 제조 방법

(57) 요약

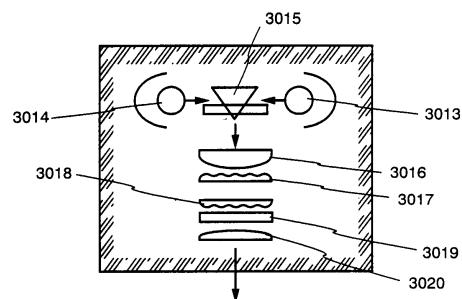

신뢰도가 높은 커패시터, 우수한 동작 성능과 신뢰성을 갖는 반도체 장치 및 그의 제조 방법이 제공된다. 제 1 도전막(102), 절연 재료로 이루어진 유전체(103) 및 제 2 도전막(104)으로 형성된 커패시터는 유전체(103) 내에 우연히 형성된 편 훌(106)이 수지 재료로 이루어진 절연 재료(충전재; 107)로 충전되는 것을 특징으로 한다. 이것은 제 1 도전막(102)과 제 2 도전막(104) 사이에 단락을 방지할 수 있다. 이 커패시터는 반도체 장치의 꽂 셀 내에 제공된 저장 커패시터로서 사용된다.

## 대표도

도 1

## 특허청구의 범위

### 청구항 1.

삭제

### 청구항 2.

삭제

### 청구항 3.

삭제

### 청구항 4.

삭제

### 청구항 5.

삭제

### 청구항 6.

삭제

### 청구항 7.

삭제

### 청구항 8.

삭제

### 청구항 9.

삭제

### 청구항 10.

삭제

### 청구항 11.

삭제

### 청구항 12.

삭제

### 청구항 13.

삭제

청구항 14.

삭제

청구항 15.

삭제

청구항 16.

삭제

청구항 17.

삭제

청구항 18.

삭제

청구항 19.

삭제

청구항 20.

삭제

청구항 21.

삭제

청구항 22.

삭제

청구항 23.

삭제

청구항 24.

삭제

청구항 25.

삭제

청구항 26.

삭제

청구항 27.

삭제

청구항 28.

삭제

청구항 29.

삭제

청구항 30.

삭제

청구항 31.

삭제

청구항 32.

삭제

청구항 33.

삭제

청구항 34.

삭제

청구항 35.

삭제

청구항 36.

삭제

청구항 37.

삭제

청구항 38.

삭제

청구항 39.

삭제

청구항 40.

삭제

청구항 41.

삭제

청구항 42.

삭제

청구항 43.

삭제

청구항 44.

삭제

청구항 45.

삭제

청구항 46.

삭제

청구항 47.

삭제

청구항 48.

삭제

청구항 49.

삭제

청구항 50.

삭제

청구항 51.

삭제

청구항 52.

삭제

청구항 53.

삭제

청구항 54.

삭제

청구항 55.

삭제

청구항 56.

삭제

청구항 57.

삭제

청구항 58.

삭제

청구항 59.

삭제

청구항 60.

삭제

청구항 61.

삭제

청구항 62.

삭제

청구항 63.

삭제

청구항 64.

삭제

청구항 65.

삭제

청구항 66.

삭제

청구항 67.

삭제

청구항 68.

삭제

청구항 69.

삭제

청구항 70.

삭제

청구항 71.

삭제

청구항 72.

삭제

청구항 73.

삭제

청구항 74.

삭제

청구항 75.

삭제

청구항 76.

삭제

청구항 77.

삭제

청구항 78.

삭제

청구항 79.

삭제

청구항 80.

삭제

청구항 81.

삭제

청구항 82.

삭제

청구항 83.

삭제

청구항 84.

삭제

청구항 85.

삭제

청구항 86.

삭제

청구항 87.

삭제

청구항 88.

삭제

청구항 89.

삭제

청구항 90.

삭제

청구항 91.

삭제

청구항 92.

삭제

청구항 93.

삭제

청구항 94.

삭제

청구항 95.

삭제

청구항 96.

삭제

청구항 97.

커패시터에 있어서:

제 1 도전막;

상기 제 1 도전막과 접촉하여 제공된 절연층; 및

상기 절연층과 접촉하여 제공된 제 2 도전막을 포함하며,

상기 절연층은 수지 재료로 충전된 영역을 갖는, 커패시터.

### 청구항 98.

제 97 항에 있어서,

상기 절연층은 상기 제 1 도전막의 산화물을 포함하는, 커패시터.

### 청구항 99.

제 97 항에 있어서,

상기 제 1 도전막은 알루미늄을 포함하고,

상기 제 2 도전막은 투명 도전막을 포함하는, 커패시터.

### 청구항 100.

제 97 항에 있어서,

상기 제 2 도전막은 상기 수지 재료로 충전된 상기 영역 위에 있는, 커패시터.

### 청구항 101.

반도체 장치에 있어서:

기판 위에 형성된 박막 트랜지스터로서, 상기 박막 트랜지스터는 적어도 반도체막과 게이트 전극을 포함하며, 이들 사이에는 게이트 절연막이 삽입되는, 상기 박막 트랜지스터; 및

상기 반도체막에 전기적으로 접속된 픽셀 전극 및 저장 커패시터를 구비하는 픽셀을 포함하고,

상기 저장 커패시터는 절연막이 삽입된 상기 박막 트랜지스터 위에 제공된 차폐막, 상기 차폐막을 덮는 절연층, 및 상기 절연층과 접촉하여 제공된 상기 픽셀 전극을 포함하고,

상기 절연층은 수지 재료로 충전된 영역을 갖는, 반도체 장치.

### 청구항 102.

반도체 장치에 있어서:

기판 위에 형성된 박막 트랜지스터로서, 상기 박막 트랜지스터는 적어도 반도체막과 게이트 전극을 포함하며, 이들 사이에는 게이트 절연막이 삽입되는, 상기 박막 트랜지스터;

상기 반도체막에 전기적으로 접속된 픽셀 전극 및 저장 커패시터를 구비하는 픽셀; 및

스페이서를 포함하고,

상기 저장 커패시터는 절연막이 삽입된 상기 박막 트랜지스터 위에 제공된 차폐막, 상기 차폐막을 덮는 절연층, 및 상기 절연층과 접촉하여 제공된 상기 픽셀 전극을 포함하고,

상기 절연층은 수지 재료로 충전된 영역을 갖고,

상기 절연층 및 상기 스페이서는 동일 재료를 포함하는, 반도체 장치.

### 청구항 103.

반도체 장치에 있어서:

기판 위에 형성된 박막 트랜지스터로서, 상기 박막 트랜지스터는 적어도 반도체막과 게이트 전극을 포함하며, 이들 사이에는 게이트 절연막이 삽입되는, 상기 박막 트랜지스터;

상기 반도체막에 전기적으로 접속된 픽셀 전극 및 저장 커패시터를 구비하는 픽셀; 및

스페이서를 포함하고,

상기 저장 커패시터는 절연막이 삽입된 상기 박막 트랜지스터 위에 제공된 차폐막, 상기 차폐막을 덮는 절연층, 및 상기 절연층과 접촉하여 제공된 상기 픽셀 전극을 포함하고,

상기 절연층은 수지 재료로 충전된 영역을 갖고,

상기 스페이서는 상기 박막 트랜지스터와 상기 픽셀 전극이 서로 접속되는 접촉부 위에 형성되는, 반도체 장치.

### 청구항 104.

반도체 장치에 있어서:

기판 위에 형성된 픽셀 박막 트랜지스터로서, 상기 픽셀 박막 트랜지스터는 적어도 반도체막과 게이트 전극을 포함하며, 이들 사이에는 게이트 절연막이 삽입되는, 상기 픽셀 박막 트랜지스터; 및

제 1 도전막, 상기 제 1 도전막과 접촉하는 절연층, 및 상기 절연층과 접촉하고 상기 반도체막에 전기적으로 접속된 제 2 도전막을 포함하는 저장 커패시터를 포함하고,

상기 절연층은 수지 재료로 충전된 홀(hole)을 갖는, 반도체 장치.

### 청구항 105.

반도체 장치에 있어서:

제 1 기판 위의 박막 트랜지스터;

접촉 홀로 상기 박막 트랜지스터에 전기적으로 접속된 픽셀 전극;

상기 접촉 홀 상의 스페이서로서, 적어도 상면 및 측면을 갖는 상기 스페이서; 및

상기 제 1 기판에 대향하는 제 2 기판을 포함하고,

상기 상면은 상기 제 2 기판의 표면을 향하는, 반도체 장치.

### 청구항 106.

반도체 장치에 있어서:

기판 위의 박막 트랜지스터;

접촉 홀로 상기 박막 트랜지스터에 전기적으로 접속된 픽셀 전극; 및

상기 접촉 홀 상의 스페이서로서, 상기 접촉 홀은 상기 스페이서로 충전되는, 상기 스페이서를 포함하는, 반도체 장치.

### 청구항 107.

제 101 내지 제 103 항 중 어느 한 항에 있어서,

상기 절연층은 상기 차폐막의 산화물을 포함하는, 반도체 장치.

### 청구항 108.

제 101 내지 제 103 항 중 어느 한 항에 있어서,

상기 차폐막은 알루미늄을 포함하는, 반도체 장치.

### 청구항 109.

제 101 내지 제 103 항 중 어느 한 항에 있어서,

상기 픽셀 전극은 상기 수지 재료로 충전된 상기 영역 위에 있는, 반도체 장치.

### 청구항 110.

제 102 항에 있어서,

상기 스페이서는 밀봉재가 형성된 영역 내에 형성되는, 반도체 장치.

### 청구항 111.

제 102 항에 있어서,

상기 스페이서는 밀봉재가 형성된 영역과 픽셀부 내에 형성되는, 반도체 장치.

### 청구항 112.

제 102 항에 있어서,

상기 스페이서는 밀봉재가 형성된 영역과, 구동 회로와 픽셀부 사이의 영역 내에 형성되는, 반도체 장치.

### 청구항 113.

제 102 항에 있어서,

상기 스페이서는 구동 회로와 픽셀부 사이의 영역과 픽셀부 내에 형성되는, 반도체 장치.

### 청구항 114.

제 104 항에 있어서,

상기 절연층은 상기 제 1 도전막의 산화물을 포함하는, 반도체 장치.

### 청구항 115.

제 104 항에 있어서,

상기 제 1 도전막은 알루미늄을 포함하는, 반도체 장치.

### 청구항 116.

제 101 항 내지 제 104 항에 있어서,

상기 수지 재료는 폴리이미드 또는 아크릴 수지를 포함하는, 반도체 장치.

### 청구항 117.

제 102 항, 제 103 항, 제 105 항 및 제 106 항 중 어느 한 항에 있어서,

상기 스페이서는 수지 재료를 포함하는, 반도체 장치.

### 청구항 118.

제 101 항 내지 제 106 항 중 어느 한 항에 있어서,

상기 반도체 장치는 액정 표시 장치인, 반도체 장치.

### 청구항 119.

제 101 항 내지 제 106 항 중 어느 한 항에 있어서,

상기 반도체 장치는 휴대용 전화기, 비디오 카메라, 휴대용 컴퓨터, 고글형 표시부, 프로젝터, 퍼스널 컴퓨터, 전자 게임기 및 디지털 카메라로 이루어진 그룹에서 선택되는, 반도체 장치.

### 청구항 120.

커패시터 제조 방법에 있어서:

제 1 도전막을 형성하는 단계;

상기 제 1 도전막을 덮는 절연 재료를 형성하는 단계;

상기 절연 재료 상에 절연막을 형성하는 단계;

상기 절연막을 제거하는 단계; 및

상기 절연 재료 상에 제 2 도전막을 형성하는 단계를 포함하며,

상기 절연막으로 충전된 영역이 상기 제거 단계에 의해 상기 절연 재료 내에 남겨지는, 커패시터 제조 방법.

### 청구항 121.

제 120 항에 있어서,

상기 절연 재료는 양극 산화에 의해 형성되는, 커패시터 제조 방법.

### 청구항 122.

제 120 항에 있어서,

상기 제 1 도전막은 알루미늄을 포함하는, 커패시터 제조 방법.

### 청구항 123.

제 120 항에 있어서,

상기 절연막은 수지 재료를 포함하는, 커패시터 제조 방법.

### 청구항 124.

제 120 항에 있어서,

상기 제거 단계는 산소 분위기에서의 플라즈마 처리인, 커패시터 제조 방법.

### 청구항 125.

제 120 항에 있어서,

상기 제거 단계는 포토리소그래피를 사용하는 현상 처리인, 커페시터 제조 방법.

### 청구항 126.

반도체 장치 제조 방법에 있어서:

기판 위에 박막 트랜지스터를 형성하는 단계로서, 상기 박막 트랜지스터는 적어도 반도체막과 게이트 전극을 포함하며, 이들 사이에는 게이트 절연막이 삽입되는, 상기 박막 트랜지스터 형성 단계;

상기 박막 트랜지스터를 덮는 평탄화막(leveling film)을 형성하는 단계;

상기 평탄화막 상에 차폐막을 형성하는 단계;

상기 차폐막을 덮는 절연 재료를 형성하는 단계;

상기 절연 재료 상에 절연막을 형성하는 단계;

상기 절연막을 제거하는 단계; 및

상기 반도체막에 전기적으로 접속되며, 상기 차폐막과 겹치도록 상기 절연 재료와 접촉하여 픽셀 전극을 형성하는 단계를 포함하며,

상기 절연막으로 충전된 영역이 상기 제거 단계에 의해 상기 절연 재료 내에 남겨지는, 반도체 장치 제조 방법.

### 청구항 127.

반도체 장치 제조 방법에 있어서:

기판 위에 박막 트랜지스터를 형성하는 단계로서, 상기 박막 트랜지스터는 적어도 반도체막과 게이트 전극을 포함하며, 이들 사이에는 게이트 절연막이 삽입되는, 상기 박막 트랜지스터 형성 단계;

상기 박막 트랜지스터를 덮는 평탄화막을 형성하는 단계;

상기 평탄화막 상에 차폐막을 형성하는 단계;

상기 차폐막을 덮는 절연 재료를 형성하는 단계;

상기 절연 재료 상에 절연막을 형성하는 단계;

스페이서를 형성하기 위해 상기 절연막을 패터닝하는 단계; 및

상기 반도체막에 전기적으로 접속되며, 상기 차폐막과 겹치도록 상기 절연 재료와 접촉하여 픽셀 전극을 형성하는 단계를 포함하며,

상기 스페이서의 재료와 동일한 재료로 충전된 영역이 상기 절연 재료 내에 형성되는, 반도체 장치 제조 방법.

### 청구항 128.

반도체 장치 제조 방법에 있어서:

기판 위에 박막 트랜지스터를 형성하는 단계로서, 상기 박막 트랜지스터는 적어도 반도체막과 게이트 전극을 포함하며, 이들 사이에는 게이트 절연막이 삽입되는, 상기 박막 트랜지스터 형성 단계;

상기 박막 트랜지스터를 덮는 평탄화막을 형성하는 단계;

상기 평탄화막 상에 차폐막을 형성하는 단계;

상기 차폐막을 덮는 절연 재료를 형성하는 단계;

상기 절연 재료 상에 절연막을 형성하는 단계;

상기 절연막을 제거하는 단계;

상기 반도체막에 전기적으로 접속되며, 상기 차폐막과 겹치도록 상기 절연 재료와 접촉하여 핵셀 전극을 형성하는 단계; 및

상기 박막 트랜지스터와 상기 핵셀 전극이 서로 접속되는 접촉부 위에 절연막을 포함하는 스페이서를 형성하는 단계를 포함하는, 반도체 장치 제조 방법.

### 청구항 129.

제 126 항 내지 제 128 항 중 어느 한 항에 있어서,

상기 절연 재료는 상기 차폐막의 양극 산화에 의해 형성되는, 반도체 장치 제조 방법.

### 청구항 130.

제 126 항 내지 제 128 항 중 어느 한 항에 있어서,

상기 차폐막은 알루미늄을 포함하는, 반도체 장치 제조 방법.

### 청구항 131.

제 126 항 내지 제 128 항 중 어느 한 항에 있어서,

상기 절연막은 수지 재료를 포함하는, 반도체 장치 제조 방법.

### 청구항 132.

제 126 항 내지 제 128 항 중 어느 한 항에 있어서,

상기 제거 단계는 산소 분위기에서의 플라즈마 처리인, 반도체 장치 제조 방법.

### 청구항 133.

제 126 항 내지 제 128 항 중 어느 한 항에 있어서,

상기 제거 단계는 포토리소그래피를 사용하는 현상 처리인, 반도체 장치 제조 방법.

### 청구항 134.

제 126 항 내지 제 128 항 중 어느 한 항에 있어서,

상기 반도체 장치는 액정 표시 장치인, 반도체 장치 제조 방법.

### 청구항 135.

제 126 항 내지 제 128 항 중 어느 한 항에 있어서,

상기 반도체 장치는 휴대용 전화기, 비디오 카메라, 휴대용 컴퓨터, 고글형 표시부, 프로젝터, 퍼스널 컴퓨터, 전자 게임기 및 디지털 카메라로 이루어진 그룹에서 선택되는, 반도체 장치 제조 방법.

### 명세서

#### 발명의 상세한 설명

##### 발명의 목적

##### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 절연 표면을 갖는 절연체(기판) 상에 박막 트랜지스터(이하 TFT로 칭함)로 형성된 회로를 갖는 반도체 장치 및 그의 제조 방법에 관한 것이다. 특히, 본 발명은 픽셀부 및 그 주변에 제공된 구동 회로가 동일한 절연체 상에 제공되는 액정표시 장치 등의 전기 광학 장치 및 그 위에 장착된 전기 광학 장치 등을 갖는 전기 장치(전자 장치)에 관한 것이다. 본원에 사용된 반도체 장치는 반도체 특성을 이용하여 동작하는 임의의 장치를 의미하며, 상기 절연체 상에 장착된 전기 광학 장치를 갖는 상술된 전기 광학 장치 및 전기 장치가 반도체 장치에 포함되어 있음을 알 수 있다.

절연 표면을 갖는 기판상에 TFT가 형성된 대규모 집적 회로를 갖는 반도체 장치의 개발이 진행되고 있다. 공지된 반도체 장치의 전형적인 예로는 액정 표시 장치, EL(electroluminescence) 표시 장치 및 접촉형 화상 센서 등이 있다. 특히, 액티브 층(이하, 폴리실리콘 TFT라 칭함)으로서 폴리실리콘막(다결정 실리콘막)을 갖는 TFT는 높은 전계효과 이동성을 가짐으로, 다양한 기능을 갖는 회로에 사용된다.

예를 들면, 액티브 매트릭스 액정 표시 장치에 있어서, 화상을 표시하기 위한 픽셀부 및 CMOS 회로에 근거하여 시프트 레지스터, 레벨 시프터, 버퍼 및 샘플링 회로 등을 포함하는 구동 회로가 동일한 기판상에 형성된다. 접촉형 화상 센서에 있어서, 샘플 홀드 회로, 시프트 레지스터, 멀티플렉서 등을 포함하는 픽셀부를 제어하기 위한 구동 회로가 TFT를 사용하여 형성된다.

액티브 매트릭스 액정 표시 장치의 픽셀부에 있어서, TFT(이하 픽셀 TFT라 칭함)는 수십 내지 수백만의 픽셀 각각에 증착되고, 이 각각의 픽셀 TFT는 픽셀 전극으로 제공된다. 액정 넘어 반대 기판 측 상에 반대 전극이 제공되며, 유전체로서 존재하는 액정을 갖는 일종의 커페시터가 형성된다. 각각의 픽셀에 인가되는 전압은 커페시터의 전하를 제어하도록 픽셀 TFT의 스위칭 기능에 의해 제어되어, 액정을 구동하며, 광 투과량을 제어하여 화상을 표시한다.

그러나 커페시터의 저장된 정전용량이 예를 들면, 픽셀 TFT의 OFF 전류(TFT의 OFF 상태임에도 불구하고 존재하는 드레인 전류)에 의한 누설 전류로 인해 감소하기 때문에, 광 투과량이 변하여 화상 표시의 콘트라스트를 감소시킨다. 그러므로 종래에는, 유전체로서 존재하는 액정을 갖는 커페시터에 의해 정전 용량에 대해 보상하는 커페시터(저장 커페시터)는 유전체로서 존재하는 액정을 갖는 커페시터에 병렬로 부가로 제공되었다.

전기 광학 장치의 픽셀부에 제공되는 저장 커패시터 등의 예로서는, 본 발명의 출원인은 이미 일본 특허 제 평11-045558, 평 11-053424 및 평 11-059455 등을 보유하며, 이 특허들은 차폐막(또는 광 차폐막)으로 형성된 저장 커패시터, 차폐막에 형성된 산화물 및 픽셀 전극을 개시한다.

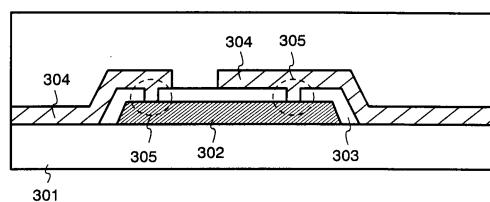

그러나 상술된 출원에 개시된 저장 커패시터는 문제를 유발할 수 있으며, 이 문제를 후술한다. 도 3을 참조하면, 광이 수지 재료로 형성된 절연막(301) 상에 형성되는 막은 금속막으로 형성 차폐막(302), 양극 산화물에 의해 형성된 양극 산화물(303) 및 픽셀 전극(304)은 저장 커패시터를 형성하기 위해 차폐막(302) 상에 형성된다. 그러나 양극 산화물(303)이 형성될 때 차폐막(302) 상에 먼지 등이 있을 경우, 그 부분은 양극으로 산화되지 않을 수도 있어서 미세한 구멍(305; 이하 편홀로 칭함)을 형성한다.

픽셀 전극(304)이 존재하는 편홀(305)로 형성되면, 차폐막(302) 및 픽셀 전극(304)이 편홀(305)을 통해 단락이 되는 불편한 점이 있다. 다시 말해, 전기 누설 또는 단락으로 인한 영역이 전극쌍 사이에 형성된다.

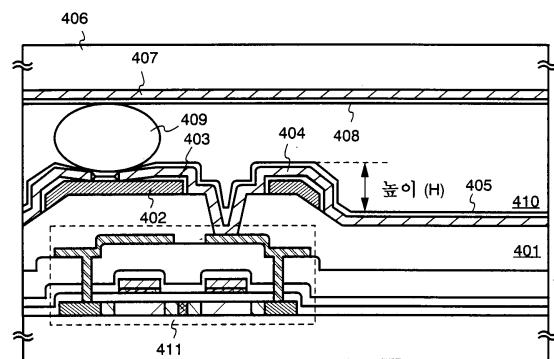

도 4를 참조하면, 차폐막(402)으로 구성된 저장 커패시터, 양극 산화물(403) 및 픽셀 전극(404)은 수지 재료로 구성된 절연막(401) 상에 형성된다. 참조 번호들(405, 406, 407, 408)은 각각 배향막(alignment), 대향 기판, 대향 전극 및 배향막이다. 액정(410)은 스페이서(409)를 통해 배향막(405, 406) 사이에 유지된다. 상기 스페이서(409)는 액정 셀에서 셀 갭을 유지하기 위해 제공된다.

여기서, 수지 재료로 이루어진 절연막(401)이 충분히 평평하지 않다면, TFT(411)의 상단은 다른 영역보다 더 높게 된다. 저장 커패시터는, TFT(411)에 형성되기 때문에, 여전히 더 높아서, 상기 셀 갭에서 높이(H)로 된다. 스페이스(409)가 저장 커패시터 위에 증착되면, 스페이스는 액정 셀의 스택과정에서 압축되어, 저장 커패시터를 봉괴하거나 파괴할 수 있다. 특히, 스페이서가 실리카 볼(silica ball) 등의 비드형(bead-like) 스페이서인 경우, 스페이서가 한 점에서 집중하기 때문에, 스페이서에 의해 압축으로 인해 픽셀 전극에 틈이 쉽게 생성된다.

상술된 단점들이 항상 발생하는 것은 아니지만, 수율(yield)을 감소시키는 요인이 될 수 있다.

### 발명이 이루고자 하는 기술적 과제

따라서, 본 발명은 상술한 문제를 해결하는 것을 목적으로 한다. 본 발명의 다른 목적은 상술된 특허 출원에 개시된 저장 커패시터에 관한 발명을 더 개선하여, 반도체 장치의 동작 성능 및 신뢰성을 개선하는 것이다. 본 발명의 다른 목적은 반도체 장치 등을 금속화하기 위한 제조 방법을 제공하는 것이다.

본 발명의 일 국면에 따라, 상술한 문제를 해결하기 위해, 상술한 출원에 개시된 저장 장치가 형성될 때, 저장 커패시터의 낮은 전극이 되는 도전막 상에 형성된 양극 산화물은 양극 산화물에 형성된 편홀을 절연 재료로 충전하기 위해 한 시간 동안 절연 재료로 덮여진다.

이것을 도 1에 도시하였다. 도면에서, 제 1 도전막(102; 특히, 차폐막)은 하부 절연막(101) 상에 형성되며, 유전체(103; 특히, 차폐막의 산화물)로 이루어진 저장 커패시터(105) 및 제 2 도전막(104; 특히, 픽셀 전극)은 제 1 도전막(102) 상에 형성된다. 여기서, 양극 산화물(103)에 형성된 편홀(106)은 절연 재료로 이루어진 충전재(107)로 충전된다.

충전재(107)는 수지 재료로 이루어진 절연 재료(절연막)가 양호하다. 수지 재료로 이루어진 이러한 절연막은 용액을 인가함으로써 형성될 수 있다. 절연막의 이러한 용액 코팅 형태는 미세 개구부를 충전하는데 특히 적절하다. 물론, 용액 등을 인가함으로 형성된 실리콘 산화막이 사용될 수도 있다.

수지 재료로 이루어진 절연막이 사용될 경우, 이것은 선택적으로 중합된 절연막이 될 수 있거나, 온도로 중합된 절연막이 될 수 있다. 포토 저하를 회피하기 위해 네거티브 감광성을 가지는 수지 재료를 사용하는 것이 더 바람직하지만, 또한, 이것은 네거티브 감광성 또는 포지티브 감광성을 가질 수 있다.

도 4에 도시된 스페이서에 의해 압축에 기인하는 저장 커패시터의 단락은 수지 재료로 이루어진 스페이서를 사용하여 회피될 수 있다. 수지 재료로 이루어진 스페이서는 그로부터 인가된 압력을 충분히 흡수할 만큼 탄성이 있으며, 비드형 스페이서의 경우와는 다르다. 이것은, 스페이서의 영역에 의해 장치에 힘이 인가되기 때문이며, 압력이 분산되어 한 지점에서 집중되는 초과 압력을 분산시킨다.

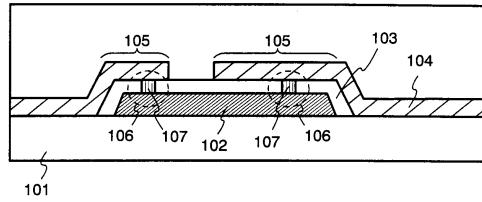

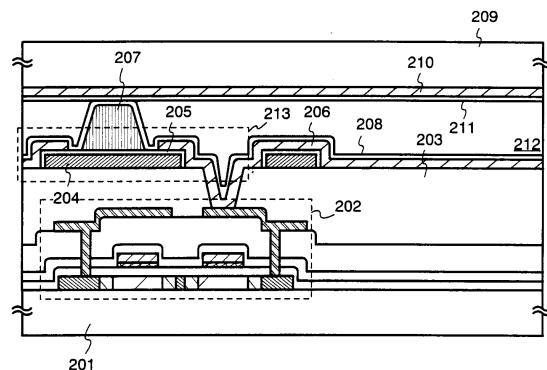

도 2a를 참조하면, 픽셀 TFT(202), 픽셀 TFT(202)가 형성될 때 형성된 단계를 평탄하게 하는 평탄화막(leveling film; 203; 중간 절연막), 차폐막(204), 이 차폐막(204)을 산화시켜 얻어진 산화막(205) 및 픽셀 전극(206)이 기판(201) 상에 형성된다. 차폐막(204) 및 픽셀 전극(206)이 산화막(205)을 통해 서로 겹쳐진 영역이 저장 커패시터를 형성함을 알 수 있다.

또한, 수지 재료로 이루어진 스페이서(207)는 패터닝(포토리소그래피)에 의해 산화물(205) 상에 형성된다. 스페이서(207)는 배향막(208)으로 덮여진다. 참조 번호 209, 210 및 211은 대향 기판, 대향 전극 및 대향측 상의 배향막을 각각 나타낸다. 액정(212)은 배향막(208, 211) 사이에 유지된다.

도 2a에 도시된 구조는 수지 재료로 이루어진 스페이서뿐만 아니라, 이 스페이스가 형성될 때 인가된 수지 재료가 산화물(205) 내의 편홀을 충전하는데 전적으로 사용되는 것을 특징으로 한다. 편홀에 한번 충전된 수지 재료는 스페이서를 형성하기 위해 패터닝할 때 에친트가 편홀에 들어갈 수 없기 때문에 제거되지 않은 채 남겨질 것으로 생각된다.

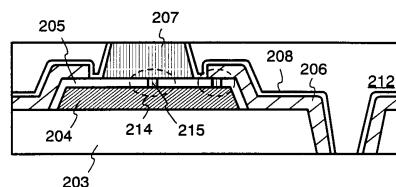

도 2b에는 도 2a의 213 표시한 접선으로 둘러싸인 영역을 확대하여 나타내었다. 도 2a를 통해 설명하지는 않았지만, 실제로, 산화물(205) 내에서 우연히 형성된 편홀(214)은 수지 재료로 이루어진 충전재(215)로 충전되거나 스페이서(207)에 의해 밀봉된다. 다시 말하면, 산화물(205)은 수지 재료로 이루어진 절연재로 충전된 영역을 갖는다.

상술한 바와 같이, 본 발명에 따라, 먼저, 저장 커패시터의 유전체 내에 우연히 형성된 편홀로 인한 단락을 방지하기 위해, 편홀은 저장 커패시터의 형성으로 인한 결점을 방지하기 위해 절연재로 충전된다. 또한, 수지 재료로 이루어진 절연막의 스페이서를 형성함으로써, 장치는 저장 커패시터 위에 스페이서에 의해 인가된 압력으로 인해 파괴되는 것을 방지한다.

또한, 본 발명에 따라, 저장 커패시터의 유전체 내에 동시에 형성된 편홀을 수지 재료로 이루어진 스페이서를 형성함으로 형성된 편홀을 충전하는 것이 가능하다. 그러므로 부가의 처리 과정 없이, 저장 커패시터에 관한 결점들은 제조 공정의 수율을 개선하도록 제거될 수 있다.

## 발명의 구성

### 제 1 실시예

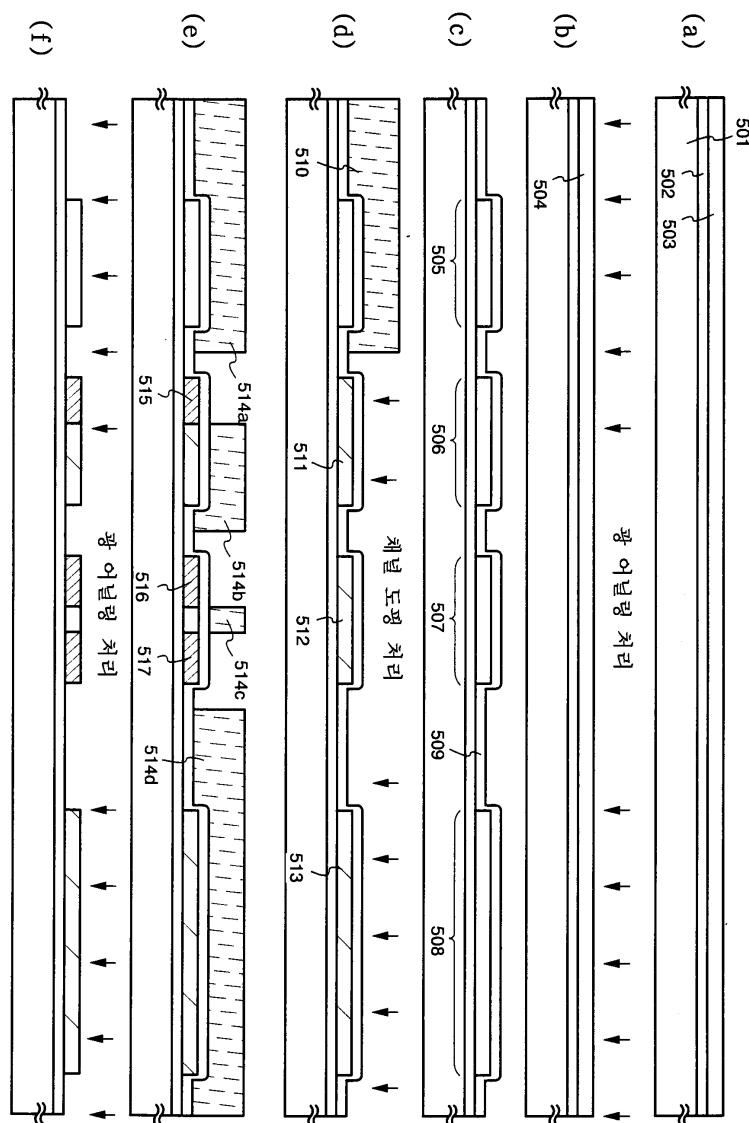

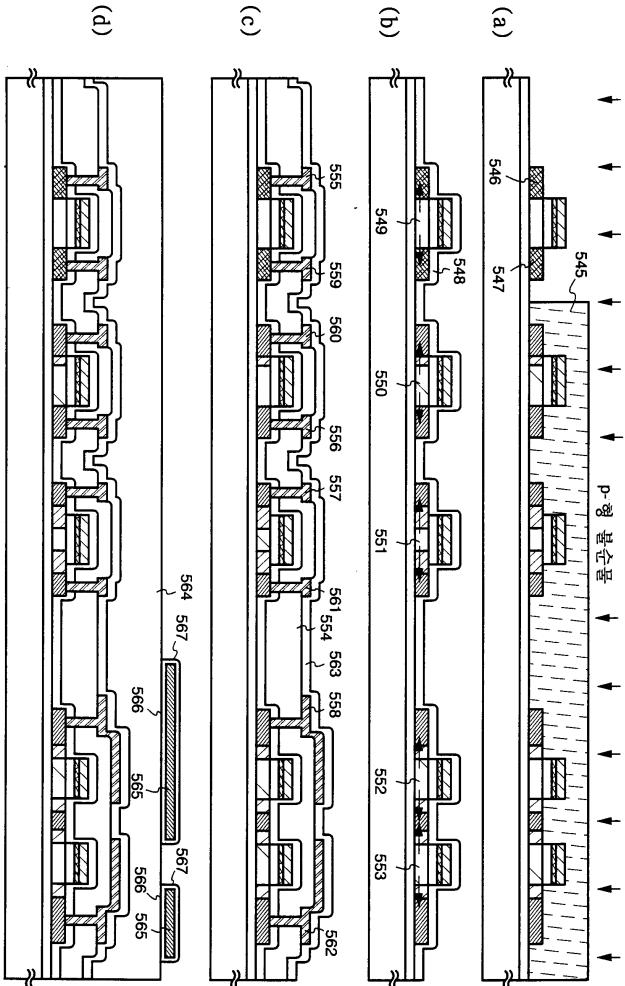

본 발명에 따른 실시예를 도 5 내지 8b를 사용하여 설명하였다. 픽셀부 및 그 주변에 제공된 구동 회로에 대한 TFT 제조 방법이 설명되어 있다. 시프트 레지스터 및 버퍼 등을 위한 기본 회로 및 샘플링 회로(전송 게이트)를 형성하는 n 채널 TFT인 CMOS 회로가 간단한 설명을 위해 구동 회로에 대해 도시함을 알 수 있다.

도 5의 (a)에서, 기판(501)용으로는 유리 기판이나 수정 기판을 사용하는 것이 양호하다. 그 밖에, 그 표면에 형성된 절연막을 갖는 실리콘 기판, 금속 기판 또는 스테인레스강 기판 등이 사용될 수 있다. 열 고유 저항이 허용되면, 플라스틱 기판 사용도 가능하다.

실리콘을 포함하는 절연막(실리콘을 포함하는 절연막은 현재의 명세서에서 일반적으로 산화 실리콘막, 실리콘 질화막 및 실리콘 산화질화막(oxynitride film)을 나타낸다)을 포함하는 베이스막(502)은 플라즈마 CVD에 의해 형성되거나, 스퍼터링에 의해 형성되어 TFT가 제조되는 기판(501)의 표면에 100 내지 400nm 정도의 두께가 된다.

실리콘 산화질화물이  $SiO_xNy$ 로 표시되는 질화막이더라도, 소정의 비율로 실리콘, 산소 및 질소를 포함하는 질화막을 나타낸다. 본 실시예에서, 20 내지 50 원자 % (일반적으로 20 내지 30원자 %) 질소가 함유된 100nm의 두께의 실리콘 산화질화막의 적층막 및 1 내지 20 원자 % (일반적으로 5 내지 10 원자 %) 질소가 함유된 200nm 두께의 실리콘 질화막이 베이스막(502)으로 사용된다. 이 두께는 이러한 값에서 제한되지 않음을 알아야 한다. 실리콘 산화질화막에 포함된 질소와 산소의 비율(원자 % 비율)은 3:1 내지 1:3(일반적으로 1:1)이 될 수 있다. 실리콘 산화질화막은 미가공 재료 기체들로서  $SiH_4$ ,  $N_2O$  및  $NH_3$ 를 사용하여 제조될 수 있다.

베이스막(502)은 기판으로부터 불순물 오염을 막기 위해 배치되며, 수정 기판을 사용하는 경우에는 필수적으로 배치하지 않아도 된다.

비결정질 구조를 포함하는 반도체막(본 실시예에서는 비결정질 실리콘막(미 도시))은 공지된 막 배치 방법을 사용하여 30 내지 120nm 정도의 두께로 베이스막(502)에 형성된다. 비결정질 구조를 포함한 반도체막처럼, 비결정질 반도체막과 미정

질의 반도체막이 있다. 또한, 비결정질 실리콘 게르마늄막 등의 비결정질 구조를 포함하는 합성 반도체막이 포함될 수도 있다. 이 막이 상술한 두께로 형성되면, TFT를 최종으로 완료하는 지점에서 액티브층의 두께는 10 내지 100nm(양호하게는 30 내지 50nm)가 된다.

결정질 구조를 포함하는 반도체막(503: 제 1 실시예의 결정질 실리콘막)은 일본 특개평 7-130652호(대응 미국공보 제 5,643,826)에 개시된 기술에 따라 형성된다. 이 공보에 개시된 기술은 비결정질 실리콘막을 결정화할 때 결정화를 개선하기 위한 촉매요소(니켈, 코발트, 게르마늄, 주석, 납, 파라듐, 철 및 구리; 일반적으로 니켈 중에서 선택된 하나 이상의 원소)로 사용되는 결정화 수단이다.

보다 구체적으로, 열 처리는 촉매 요소가 비결정질 실리콘막을 결정질 실리콘막으로 전환하기 위해 비결정질 실리콘막의 표면에 홀딩되는 상태에서 실행된다. 실시예가 상기 공보의 제 1 실시예에 개시된 기술을 사용하고 있지만, 제 2 실시예에 개시된 기술도 사용될 수 있다. 단결정 실리콘막과 다결정 실리콘막이 결정질 실리콘막에 모두 포함되어 있더라도, 본 실시예의 비결정질 실리콘막은 결정 입자 영역(도 5의 (a))을 갖는 실리콘막이 된다.

이것은 비결정질 실리콘막의 수소 함량에 의존하더라도, 함유된 수소량을 5 원자 % 이하로 줄이기 위해 몇 시간 동안 400 내지 550°C로 가열하는 탈수소처리과정 및 결정화 처리를 실행하는 것이 바람직하다. 비결정질 실리콘막은 스퍼터링 또는 증발 탈수법 등의 그 밖의 증착법을 사용하여 제조될 수 있지만, 그 막에 함유된 산소나 질소 같은 불순물 원소를 충분히 제거하는 것이 바람직한 방법이다.

베이스막과 비결정질 실리콘막이 동일한 증착 방법으로 제조될 수 있기 때문에, 이들은 연속하여 형성될 수 있다. 베이스 막 형성 후, 대기에 노출되지 않음으로써 표면의 오염물을 제거할 수 있는 것이 가능하여, 제조된 TFT의 특성에서 스퍼터링이 감소될 수 있다.

그 다음, 레이저광원(레이저광)으로부터 생성된 광은 결정질 실리콘막(503)으로 비춰지며, 결정이 개선된 결정질 실리콘 막(504)이 형성된다. 펄스 발진형 또는 연속 발진형 엑시머 레이저광(excimer laser light)이 상기 레이저광으로 바람직하며, 연속 발진형 아르곤 레이저광 또는 Nd:YAG 레이저광이 상기 레이저광으로 사용될 수도 있다. 이 레이저광의 빔 형태는 선형이 될 수 있거나, 직각형이 될 수도 있다(도 5의 (b) 참조).

레이저광 대신에, 램프(램프 방사)로부터 발생된 광(이하, 램프 어닐링으로 칭함)이 비춰질 수 있다. 램프 방사처럼, 예를 들면, 할로겐 램프 또는 적외선 램프로부터 발생된 램프 방사가 사용될 수 있다.

본원에 개시된 것처럼 레이저광 또는 램프 광에 의한 열 처리(어닐링)를 실행하기 위한 처리 과정은 광 어닐링 처리라 칭한다. 광 어닐링 처리가 높은 오도의 열 처리로 짧은 시간 동안 이루어지기 때문에, 유리 기판 등의 낮은 열 저항을 갖는 기판을 사용하는 경우에도, 효과적인 열 처리 처리는 높은 작업처리량으로 실행된다. 물론, 이들은 전기 용광로(열 어닐링이라 칭해짐)를 사용하여 용광로 어닐링(furnace annealing)에 의해 대체될 수 있고, 이러한 조합은 물체가 어닐링되기 때문에 사용될 수도 있다.

제 1 실시예에서, 레이저 어닐링 처리는 펄스 발진형 엑시머 레이저광을 선형으로 형성함으로써 실행될 수 있다. 레이저 어닐링 조건은: XeCL 기체가 여기 기체로 사용되며, 처리온도는 실온으로 설정되고, 펄스 발진 주파수는 30Hz로 설정되며, 레이저 에너지 밀도는 250 내지 500mJ/cm<sup>2</sup>(일반적으로 350 내지 400mJ/cm<sup>2</sup>)로 설정된다.

상술된 조건하에서 실행된 레이저 어닐링 처리는 열 결정화 이후에 남은 비결정 영역의 완전한 결정화뿐만 아니라 이미 결정화된 결정질 영역의 결점을 줄이는 효과를 갖는다. 따라서, 본 처리는 반도체막의 결정화 개선 처리 또는 반도체막의 결정화 증진 처리라고 불릴 수도 있다. 램프 어닐링의 조건을 최적화함으로써 이러한 효과를 얻는 것이 가능하다. 현재 명세서 조건은 제 1 광 어닐링이라 칭해진다.

아일랜드 반도체막(505 내지 508; 이하 액티브층으로 칭함)은 결정질 실리콘막(504)을 패턴화함으로써 형성된다. 차후의 패턴화의 위치를 조절하는데 사용된 배향 마커들(alignment markers)은 결정질 실리콘막을 사용하여 형성된다. 본 실시 예에서, 배향 마커들을 분리 형성(마크들의 수가 증가)하는데 요구되는 시간은 배향 마커들이 액티브층의 형성과 더불어 동일한 시간에 형성될 수 있기 때문에 절감될 수 있다.

이어서, 보호막(509)은 차후의 불순물 도핑을 위해 액티브층(505 내지 608) 위에 형성된다. 이 보호막(509)은 100 내지 200nm(양호하게는 130 내지 170) 두께의 실리콘 산화막 또는 실리콘 산화질화막을 사용한다. 이 보호막(509)은 불순물 도핑 시 플라즈마에 직접적으로 결정질 실리콘막이 노출되지 않도록 하는 수단을 갖지며 추적 농도 제어(도 5의 (c))를 가능하게 한다.

이때, 레지스트 마스크(510)가 그 위에 형성되며, 불순물 원소 첨가 p 형(이하 p형 불순물 원소라 칭해짐)이 보호막(509)을 통해 도핑된다. p형 불순물 원소처럼, 전형적으로 주기율표의 13족에 속하는 원소들, 특히, 붕소 또는 갈륨이 사용될 수 있다. 이 처리(이하 채널 도핑 처리라 칭함)는 TFT의 임계 전압을 제어하는 처리이다. 여기서, 붕소는 질량 분할(mass separation) 없이,  $B_2H_6$  이 플라즈마에 의해 여기되는 이온 도핑에 의해 도핑된다. 또한, 질량 분할이 실행되지 않는 이온 주입을 사용하는 것도 가능하다.

이 처리에 의해,  $1 \times 10^{18}$  atoms/cm<sup>3</sup>(일반적으로  $5 \times 10^{16}$  내지  $5 \times 10^{17}$  atoms/cm<sup>3</sup>)의 농도로 p형 불순물 원소가 첨가된 액티브층(511 내지 513)이 형성된다. 이러한 액티브층(511 내지 513)은 차후에 n 채널 TFT용 액티브층이 된다. 본 명세서에서 상술된 농도는 SIMS(secondary ion mass spectroscopy)에 의해 측정된 값임을 알아야 한다.

본 명세서를 통해, 적어도 상기 상술된 농도 범위 내에서 p형 불순물 영역을 포함하는 불순물 영역은 p형 불순물 영역(b)으로 정의됨(그러나, 일반적으로 인 또는 비소는  $1 \times 10^{16}$  atoms/cm<sup>3</sup>으로 도핑된 n형을 첨가하는 불순물 원소가 배제되었음)을 알아야 한다(도 5의 (d)).

그 다음, 레지스트 마스크(510)가 제거되고 새로운 레지스트 마스크(514z 내지 514d)가 형성된다. 이때, n형을 첨가하는 불순물 영역(515 내지 517)이 n형을 첨가하는 불순물 원소(이하 n형 불순물 원소라 칭함)를 도핑함으로써 형성된다. n형 불순물 원소처럼, 전형적으로 15족에 속하는 원소들, 특히 인 또는 비소가 사용될 수 있다(도 5의 (e)).

이러한 저 밀도 불순물 영역(515 내지 517)은 차후 형성된 CMOS 회로 및 샘플링 회로의 n 채널 TFT내의 LDD 영역으로 동작하는 불순물 영역이 된다. 이렇게 형성된 불순물 영역에 있어서, n형 불순물 원소는  $2 \times 10^{16}$  내지  $5 \times 10^{19}$  atoms/cm<sup>3</sup>(일반적으로  $5 \times 10^{17}$  내지  $5 \times 10^{18}$  atoms/cm<sup>3</sup>)의 농도로 함유된다. 본 명세서에서, 상술된 농도 범위 내에서 n형 불순물 영역을 함유하는 불순물 영역은 n형 불순물 영역(b)으로서 정의된다.

여기서, PH<sub>3</sub>(phosphine)가 질량 분할 없이 플라즈마에 의해 여기는 농도  $1 \times 10^{18}$  atoms/cm<sup>3</sup>로 이온 도핑하여 도핑된다. 물론, 질량 분할이 실행되는 이온 주입도 사용될 수 있다. 이 처리에서, 인은 보호막(509)을 통해 결정질 실리콘막으로 도핑된다.

그 다음, 레지스트 마스크(514a 내지 514b) 및 보호막(509)이 제거되며, 레이저광에 의해 방사 처리(irradiation process)가 재실행된다. 다시, 펄스 발진형 또는 연속 발진형의 엑시머 레이저광이 레이저광이 바람직하지만, 연속 발진형의 아르곤 레이저광도 사용될 수 있다. 이러한 레이저광의 빔 형태는 선형이거나 직각형태일 수 있다. 그러나 도핑된 불순물 원소의 활성화가 물체이기 때문에, 결정질 실리콘막을 녹이지 않는 수준에서 에너지가 방사되는 것이 바람직하다. 그 위에 남겨지는 보호막(509)에 레이저 어닐링 처리를 실행하는 것도 가능하다(도 5의 (f)).

제 1 실시예에서, 레이저 어닐링 처리는 선형으로 펄스 발진형 엑시머 레이저광을 형성함으로써 실행된다. 레이저 어닐링 조건은 다음과 같다: XeCL 기체는 여기 기체로 사용되며, 처리 온도는 실온이며, 펄스 발진 주파수는 30 Hz이고, 레이저 에너지 농도는 100 내지 300mJ/cm<sup>2</sup>(일반적으로는 150 내지 250mJ/cm<sup>2</sup>)이다.

## 작제

상술된 조건으로 실시된 광 어닐링 처리는 불순물 원소 도핑 시 비결정질도 이루어진 반도체막을 재결정하는 효과뿐만 아니라 도핑된 n형 또는 p형을 첨가한 불순물 원소를 활성화하는 효과를 갖는다. 상술된 조건들은 반도체막을 녹이지 않고 조정된 원자 배열을 만들고 동시에, 불순물 원소를 활성화하는 것이 바람직하다. 본 처리는 광 어닐링에 의해 불순물 첨가 n형 또는 p형을 활성화하는 처리 또는 이를 모두를 동시에 실행하는 처리 또는 반도체막을 재결정화하는 처리라 칭해질 수도 있다. 이러한 효과는 램프 어닐링 조건을 최적화함으로도 얻을 수 있다. 본 명세서에서, 이 조건은 제 2 광 어닐링이라 칭해진다. 제 2 광 어닐링을 생략할 수도 있음을 알아야 한다.

이 처리로 인해, n형 불순물 영역(b: 515 내지 517)의 경계, 즉, n형 불순물 영역(b) 주위에 존재하는 진성 영역을 갖는 접합영역(p형 불순물 영역(b))은 충분히 진성 영역이 될 수 있다)이 깨끗해진다. 이것은 LDD 영역 및 채널 형성 영역이 TFT가 차후에 종결될 때 매우 양호한 접합을 형성할 수 있음을 의미한다.

이 레이저광에 의한 불순물 원소의 활성화시, 전기 용광로(용광로 어닐링)를 사용하는 열 처리에 의한 활성화가 병합될 수도 있으며, 이 활성화는 용광로 어닐링에 의해서만 실행될 수도 있다. 열 처리에 의해 활성화를 실행하는 경우, 대략 450 내지 650°C(양호하게는 500 내지 550°C)의 열 처리 온도가 기판의 열 저항을 고려하여 실행될 수 있다.

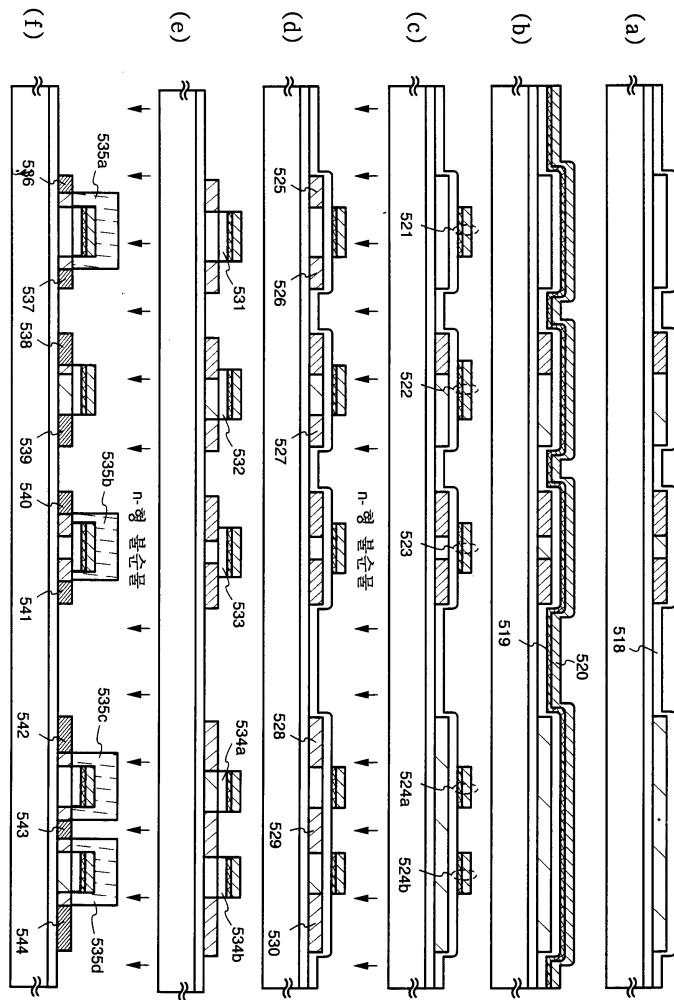

다음으로, 게이트 절연막(518)이 액티브층(505, 511 내지 513)을 덮도록 형성된다. 게이트 절연막(518)은 10 내지 200nm(양호하게는 50 내지 150nm) 두께로 형성될 수 있다. 본 실시예에서, 실리콘 산화질화막은  $N_2O$  및  $SiH_4$ 의 미가공재료들로 플라즈마 CVD에 의해 115 nm 두께로 형성된다(도 6의 (a)).

이어서, 게이트 배선(gate wiring)을 형성하는 도전막이 형성된다. 게이트 배선은 단일 층의 도전막에 의해 형성될 수 있지만, 2중 또는 필요에 따라 3중층의 적층막을 형성하는 것이 바람직하다. 본 실시예에서, 제 1 도전막(519) 및 제 2 도전막(520)을 포함하는 적층이 형성된다(도 6의 (b)).

제 1 도전막(519) 및 제 2 도전막(520)으로는, Ta, Ti, Mo, W, Cr, Nb 및 Si로부터 선택된 원소로 이루어진 금속막, 이러한 주요 성분(일반적으로 탈타늄 질화막, 텅스텐 질화막 또는 티타늄 질화막)으로서 상기 원소들로 구성된 금속 합성막, 상기 원소들(일반적으로 Mo-W 합금, Mo-Ta 합금, 텅스텐 질화막)을 조합한 합금막 또는 이러한 막들의 적층막이 사용될 수 있다.

제 1 도전막(519)은 10 내지 50 nm(양호하게는 20 내지 30nm)로 형성될 수 있고, 제 2 도전막(520)은 200 내지 200nm(양호하게는 250 내지 350)으로 형성될 수 있다. 제 1 실시예에서, 50nm 두께의 탈타늄 질화막(TaN막)은 제 1 도전막(519)으로서 사용되었고, 350 nm 두께의 탈타늄(Ta)막은 제 2 도전막(520)으로 사용되었다.

또한, 텅스텐 질화막 및 텅스텐막의 적층, 텅스텐 질화막의 단일 층 및 텅스텐 질화막 모두가 적절하다. 또한, 제 1 도전막(519; 폴리사이드구조)아래에 형성된 대략 2 내지 20 nm의 두께의 실리콘막을 갖는 구조가 사용되는 경우, 상기 실리콘막 상에 형성된 도전막의 밀접 응착력이 개선되며, 도전막의 산화가 방지될 수 있다.

또한, 제 1 실시예처럼 제 2 도전막(520)용 금속막을 사용하는 경우에, 이것은 암모니아 기체 또는 질화 기체를 사용하여 플라즈마 대기에서 표면을 노출하여 질화시키는데 효과적이다. 이처럼 행하여, 금속막의 표면의 산화를 방지하는 것이 가능하다.

게이트 배선(이들은 게이트 전극들이라고도 칭해짐)(512 내지 524a, 524b)은 제 1 도전막(5190 및 제 2 도전막(520)을 동시에 예칭함으로써 400 nm 두께로 형성된다. 구동 회로에 형성된 게이트 배선들(522,523)은 층간 게이트 절연막에 의해 n형 불순물 영역(b; 515 내지 5217)의 부분을 겹쳐지도록 형성된다. 이 게이트 배선(524a,524b)은 단면도 상에서 2 개의 전극처럼 보이지만, 효과면에서, 하나의 연속된 패턴으로 구성되어 있다(도 6의 (c)).

그 다음, n형 불순물 원소(제 1 실시예에서 인)는 마스크들로서 게이트 전극들(521 내지 524b)을 사용하여 자체 정렬(self-aligned)되는 방식으로 도핑된다. 이렇게 형성된 불순물 영역들(525 내지 530)로 도핑된 인의 농도는 상술된 n형 불순물 영역(b)(채널 도핑 처리에 부가된 붕소 농도보다 1 내지 10배 더 높게 제공됨, 특히  $1 \times 10^{16}$  내지  $5 \times 10^{18} atoms/cm^3$ , 통상적으로  $3 \times 10^{17}$  내지  $3 \times 10^{18}$ )의 1/2 내지 1/10(특히 1/3 내지 1/4)의 농도로 설정된다. 본 명세서에서, 상술된 농도 범위에 있는 n형 불순물 원소를 함유하는 불순물 영역은 n형 불순물 영역(c)으로 규정된다(도 6의 (d)).

붕소가 채널 도핑 처리에서  $1 \times 10^{15}$  내지  $5 \times 10^{18} atoms/cm^3$ 의 농도에서 n형 불순물 영역들(c; 527 내지 530)로 이미 도핑되었지만, 인이 p형 불순물 영역(b) 내에 함유된 붕소의 5 내지 10배의 농도로 도핑되기 때문에, 붕소의 효과는 무시될 수 있다.

그러나 엄격히 말해서, 게이트 배선들과 겹쳐진 n형 불순물 영역(b; 515 내지 517)의 부분들의 인의 농도는  $2 \times 10^{16}$  내지  $5 \times 10^{19} atoms/cm^3$ 로 남아 있고, 게이트 배선들과 겹쳐지지 않은 부분들은  $1 \times 10^{16}$  내지  $5 \times 10^{18} atoms/cm^3$ 의 인이 더 추가되며, 약간 더 높은 농도로 인을 함유한다.

다음, 게이트 절연막(518)은 마스크들로서 게이트 전극들(521 내지 524b)과 자체 정렬되는 방식으로 예칭된다. 전식 예칭은 예칭 처리용으로 사용되고,  $\text{CHF}_3$  기체가 예천트로 사용된다. 예천트는 이 재료에 한정되지 않음을 알아야 한다. 따라서, 게이트 배선 아래에 게이트 절연막들(531 내지 534a 및 534b)이 형성된다(도 6의 (e)).

이러한 방식으로 액티브층을 노출함으로써, 차후에 실시될 불순물 원소의 도핑 처리시 가속 전압을 낮게 유지시킬 수 있다. 따라서, 필요한 1회 분의 양이 적기 때문에, 작업처리량이 증가한다. 말할 것도 없이, 불순물 영역은 게이트 절연막을 예칭하지 않고도 도핑을 통해서 형성될 수 있다.

그 다음, 레지스트 마스크(535a 내지 535d)가 게이트 배선을 덮도록 형성되며, 고농도의 인을 함유한 불순물 영역(536 내지 544)이 n형 불순물 원소(제 1 실시예의 인)을 첨가함으로써 형성된다. 다시, 이온 도핑(이온 주입도 가능함)은  $\text{PH}_3$ 를 이용함으로써 실행되며, 이러한 영역의 인의 농도는  $1 \times 10^{26}$  내지  $1 \times 10^{21}$  atoms/cm<sup>3</sup>(특히  $2 \times 10^{20}$  내지  $5 \times 10^{20}$  atoms/cm<sup>3</sup>)로 설정된다(도 6의 (f)).

이 명세서에서, 상술된 조건 범위 내에서 n형 불순물 원소를 함유한 불순물 영역은 n형 불순물(a)로서 정의됨을 알아야한다. 또한, 처리 과정 중 첨가된 인 또는 봉소가 이미 불순물 영역(536 내지 544)에 함유되어 있더라도, 이 과정에서 첨가된 인 또는 봉소의 영향은 고려할 필요가 없는데, 이는 인은 충분히 고농도에서 차후에 첨가되기 때문이다. 그러므로 이 명세서에서 n형 불순물 영역(a)으로서 불순물 영역(536 내지 544)이라 칭해질 수 있다.

이어서, 레지스트 마스크(535a 내지 535d)가 제거되고, 새로운 레지스트 마스크(5450)가 형성된다. 그 다음, p형 불순물 원소(본 실시예에서는 봉소)가 도핑되며, 고농도의 봉소가 포함되어 있는 불순물 영역(546,547)이 형성된다. 여기서, 봉소는  $\text{B}_2\text{H}_6$ 을 사용하여 이온 도핑에 의해  $3 \times 10^{20}$  내지  $3 \times 10^{21}$  atoms/cm<sup>3</sup>(일반적으로  $5 \times 10^{20}$  내지  $1 \times 10^{21}$  atoms/cm<sup>3</sup>)로 형성된다. 본 명세서에서, 상술된 농도의 범위 내에서 p형 불순물을 포함하는 불순물 영역은 p형 불순물(a)로서 정의된다(도 7의 (a)).

$1 \times 10^{20}$  내지  $1 \times 10^{21}$  atoms/cm<sup>3</sup> 농도로 불순물 영역(546,547; 상술한 n형 불순물 영역(a; 536,537))부분에 인이 이미 도핑되어 있다. 그러나 봉소는 적어도 3회에 의해 더 높은 농도로 도핑된다. 그러므로 n형 불순물 영역이 p형에 반대로 형성되며, p형 불순물 영역으로서 동작한다. 따라서, p형 불순물 영역(a)으로서 불순물 영역(546,547)을 정의하는 것이 가능하다.

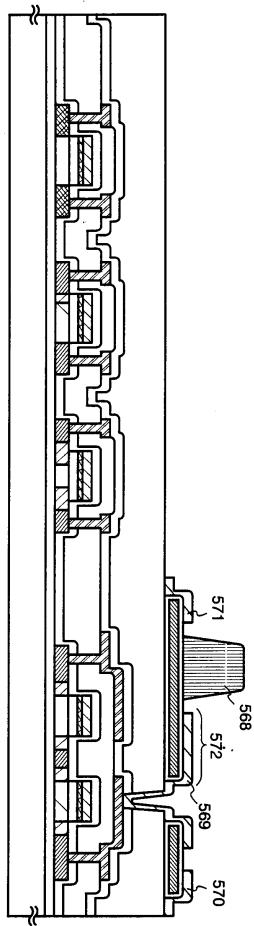

레지스트 마스크(545)를 제거한 이후, 제 1 층간 절연막(548)으로서, 실리콘, 실리콘 질화막, 실리콘 산화막, 실리콘 산화질화막 또는 이러한 것들을 조합한 적층막을 포함하는 절연막이 형성될 수 있다. 막 두께는 50 내지 400nm(양호하게는 100 내지 200nm)이다.

본 실시예에서, 200nm 두께의 실리콘 산화질하막(질화물 농도는 25 내지 50 원자 %이다)이 사용되며, 이는  $\text{SiH}_4$ ,  $\text{N}_2\text{O}$  및  $\text{NH}_3$  기체의 미가공 재료들로부터 플라즈마 CVD에 의해 형성된다. 이 제 1 층간 절연막(548)은 그 다음 실행된 열 처리(활성화 처리)에서 게이트 배선(521 내지 524a,524b)의 산화로 인한 저항의 증가를 방지하는 효과가 있다.

그 다음, 열 처리 처리는 이들 각각의 농도로 도핑된 n형 또는 p형 도전성의 불순물 원소를 활성화하기 위해 실행된다. 용광로 어닐링, 레이저 어닐링, 신속한 열 어닐링(RTA) 또는 램프 어닐링이 이러한 처리를 위해 실행될 수 있다. 이 활성화 처리는 제 1 실시예의 용광로 어닐링에 의해 실행된다. 열 처리는 300°C와 650°C 사이, 양호하게는 400 내지 550°C에서, 질소 대기에서 실행된다(여기서는 550°C 4시간 동안 실시되었음)(도 7의 (b)).

제 1 실시예에서 비결정질 실리콘막을 결정화하는데 사용된 촉매원소(제 1 실시예에서는 니켈)는 화살표 방향으로 이동하며, 도 6의 (f)의 처리로 형성된 고농도(게터링)로 인을 포함하는 영역에서 포착된다. 이것은 인에 의해 금속 원소의 게터링 효과로부터 유래되는 현상이다. 결과적으로, 차후에 형성될 채널 형성 영역(549 내지 553)에 함유된 니켈의 농도는  $1 \times 10^{17}$  atoms/cm<sup>3</sup>이하로 줄어든다. 그러나  $1 \times 10^{17}$  atoms/cm<sup>3</sup>이하의 농도는 니켈용 SIMS의 검출 한계이므로, 현재의 기술로 측정하는 것은 불가능하다.

반대로, 촉매원소는 이 촉매 원소(불순물 영역(536 내지 544)이 도 6의 (f)의 처리로 형성된 영역)의 게터링 사이트로서 기능하는 영역 내에 고 농도로 침전된다. 촉매원소는  $5 \times 10^{18}$  atoms/cm<sup>3</sup>의 농도(양호하게는  $5 \times 10^{19}$  내지  $5 \times 10^{28}$  atoms/cm<sup>3</sup>의 농도)로 이러한 영역에 존재한다. 그러나 게터링 사이트가 되는 영역이 소스 영역 또는 드레인 영역으로서 동작하는 지의 여부를 받아들일 수 있기 때문에, 니켈의 존재가 어떠한 문제를 발생시키지 않는다고 가정한다.

또한, 수소 첨가 처리는 1 내지 12 시간 동안, 300 내지 450°C에서 3 내지 100% 수소를 함유하는 대기에서 열 처리를 실행하여 액티브층 상에서 실행된다. 이것은 온도로 활성화된 수소에 의해 반도체층 내의 땅글링 본드(dangling bond)를 제거하기 위한 처리이다. 플라즈마 추소 첨가(플라즈마에 의해 활성화된 수소를 사용하여)는 다른 수소 첨가 수단으로서 동작할 수 있다.

제 2 층간 절연막(554)은 제 1 층간 절연막(548) 위에 500nm 내지 1.5mm로 형성된다. 제 1 실시예에서, 제 2 층간 절연막(554)은 플라즈마 CVD에 의해 800nm 두께로 실리콘 산화막에 의해 형성된다. 따라서, 1mm 두께의 층간 절연막은 제 1 층간 절연막(실리콘 산화질화막; 548) 및 제 2 층간 절연막(실리콘 산화막; 554)의 적층으로부터 형성된다.

제 2 층간 절연막(554)용으로 폴리이미드(polyimide), 아크릴, 폴리아미드(polyamide), 폴리이미드 아미드, BCB (benzocyclobutene)등의 유기 수지막들을 사용하는 것이 가능하다는 것을 알아야 한다.

그 뒤, 접촉 홀은 각각의 TFT의 드레인 영역 또는 소스 영역에 이르기 위해 형성되며, 소스 배선(555 내지 558) 및 드레인 배선(559 내지 562)이 형성된다. 이어서, 도면에 도시되지는 않았지만, 드레인 배선(559, 560)은 CMOS 회로를 형성하기 위해 동일한 배선으로부터 형성됨을 알아야 한다. 또한, 제 1 실시예에서, 100nm Ti막, Ti를 함유한 300 nm 알루미늄막 및 스퍼터링에 의해 연속적으로 형성된 150 nm Ti막의 전극들은 3중층 구조 적층막으로 이루어짐을 알아야 한다.

실리콘 질화막, 실리콘 산화막 또는 실리콘 산화질화막은 패시베이션막(563)으로서 그 다음에 50 내지 500nm(일반적으로 200 내지 300nm)의 두께로 형성된다(도 7의 (c)).

$H_2$  및  $NH_3$ 등의 수소를 함유한 기체를 사용하여 막형성 과정을 진행하는 플라즈마 처리를 실행하는 것과 이 막이 형성된 이후 열 처리를 실행하는 것이 효과적이다. 이러한 진행 과정은 제 1 및 제 2 층간 절연막으로 여기된 수소를 제공한다. 이 상태로 열 처리를 실행함으로써, 액티브층은 효율적으로 수소화되고, 패시베이션막(563)의 막질이 개선되는데, 이는 층간 절연막에 첨가된 수소가 이 층 아래에서 확산되기 때문이다.

또한, 패시베이션막(563)을 형성한 이후, 부가의 수소화 처리가 실행될 수 있다. 예를 들면, 3 내지 100% 수소를 포함하는 대기에서 300 내지 450°C로 1 내지 12 시간 동안 열 처리를 실행하는 것이 바람직하다. 또는, 플라즈마 수소화를 이용함으로써 유사한 결과를 얻을 수 있다.

접촉 홀이 핵셀 전극 및 드레인 배선을 연결하기 위해 층을 형성되는 위치에서 패시베이션막(563)에 개구부를 형성할 수 있음을 알 수 있다.

수지막(이하 수지 절연막으로 칭함, 본 실시예에서는 평탄화막이라고도 칭해짐)을 포함하는 제 3 층간 절연막(564)은 도 7의 (d)에 도시된 바와 같이, 1 내지 3μm(일반적으로 1.5 내지 2μm)정도로 형성된다.

폴리이미드, 아크릴 수지, 폴리아미드, 폴리이미드 아미드, BCB 또는 사이크로텐(Cycotene)이 수지 재료로서 사용될 수 있다. 그 다음 지점은 유기 수지막을 사용하여 이익을 얻을 수 있다: 우수한 평탄화; 및 플라스틱 커페시턴스가 제거되는 데, 이는 특정 유전체 정수가 낮기 때문이다. 상술한 것에 덧붙여서, 다른 유기 수지막, 유기 SiO 성분 등이 사용될 수 있다. 우수한 평탄성을 갖는다면, 무기 재료를 포함하는 절연막을 사용하는 것이 가능하다.

기판에 적용한 이후 열에 의해 중합되는 아크릴막이 여기에서 사용되었더라도, 광 방사에 의해서 중합된 막도 사용될 수 있음을 주지한다. 뿐만 아니라, 포지티브 형 또는 네가티브 형의 포토 감지 재료가 사용될 수도 있다.

또한, 제 3 층간 절연막(564)의 일부로서 안료에 의해 착색된 수지 절연막을 제공하는 것이 가능하며 이것은 컬러 필터로서 사용된다.

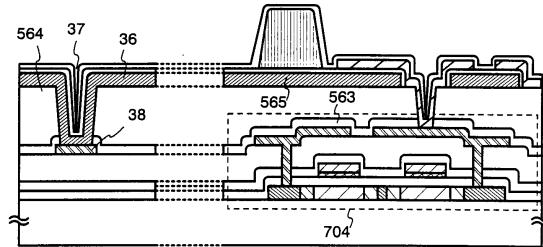

이어서, 차폐막(565)은 픽셀부 내의 수지 재료를 포함하는 제3층간 절연막(평탄화; 564) 상에 형성된다. 용어 "차폐막"은 차폐광 또는 전자기파 특성을 갖는 도전막으로 명세서를 통해 사용된다.

다양한 금속막이 차폐막(565)용으로 사용될 수 있더라도, 알루미늄, 티타늄 및 탈타늄 또는 금속막으로부터 선택된 원소를 포함하는 금속막 또는 이들 원소들의 중요한 구성 성분으로서 이를 중 하나를 갖는 금속막(본 실시예에서는 원소가 50 중량% 이상 포함될 때 그 주요 구성 성분으로 간주된다)이 바람직하며, 그 두께는 100 내지 300nm 가 될 수 있다. 제1실시예에서, 1wt% 티타늄을 함유하는 알루미늄막은 125nm 두께로 형성된다. 이 차폐막은 본 명세서에서 "제1도전막"이라 고도 칭해짐을 알아야 한다.

실리콘 산화막은 5 내지 50nm 두께(일반적으로 20 내지 30nm)로 차폐막(565)이 형성되기 전에 형성됨을 알아야 한다. 그 뒤, 차폐막(565)이 그 위에 형성되고, 참조 번호(565)로 기재된 실리콘 산화막은 마스크로서 차폐막(565)처럼 상기 상술된 절연막 상에 에칭 처리를 실행하여 형성된다.

실리콘 산화막(566)은 제3층간 절연막(564)과 차폐막(565)의 점착성을 증가시키도록 증착되며, 차폐막이 존재하지 않는 영역으로부터 이것을 제거하는 것이 바람직한데, 그 이유는 제3층간 절연막 내의 접촉 홀을 형성할 때 장애가 되기 때문이다. 이 막 상에 형성된 차폐막에 대한 점착성은 제3층간 절연막(564)의 표면에  $DF_4$  기체를 사용하여 플라즈마 처리를 실행함으로써 표면 정제에 의해 증가될 수 있다.

또한, 차폐막이 아니라, 티타늄을 함유한 알루미늄막을 사용하여 다른 접속 배선을 형성하는 것이 가능하다. 예를 들면, 회로 사이를 접속하는 접속 배선이 구동 회로 내에 형성될 수 있다. 그러나 이 경우, 차폐막 또는 접속 배선을 형성하는 금속을 증착하기 전에, 제3층간 절연막 내의 접촉 홀을 미리 형성하는 것이 필수적이다.

그 다음, 20 내지 100nm(바람직하게는 30 내지 50nm) 두께의 산화물을 공지된 양극 산화 또는 플라즈마 산화를 이용하여 차폐막(565)의 표면상에 형성한다(본 실시예에서는 양극 산화). 알루미늄 산화막(알루미늄막)은 그 주요 구성 성분으로서 알루미늄을 갖는 막 때문에 양극 산화막(567)으로서 형성되며, 제1실시예에서 차폐막(565)으로서 사용되었다. 이 양극 산화막(567)은 본 실시예의 저장 커패시터용 유전체이다.

또한, 본원에 사용된 구조는 차폐막의 표면 상에만 양극 산화를 함으로써 형성된 절연막을 갖지만, 그 밖의 절연막은 플라즈마 CVD, 열 CVD 또는 스퍼터링 등의 기체 상(phase) 방법을 사용하여 형성할 수도 있다. 또한, 이 경우, 20 내지 100nm(더 양호하게는 30 내지 50nm) 두께의 막을 제조하는 것이 가능하다.

4mm 두께의 수지 절연막(네가티브형 아크릴 수지막)이 도8a에 도시된 바와 같이 형성되며, 스페이서(568)는 패턴화를 실행함으로써 형성된다. 동시에, 핀 홀이 양극 산화물(567)에 존재할 때조차도, 이것은 도2a 및 2b를 이용하여 설명된 바와 같이 스페이서(568)를 형성할 때 스페이서(568)를 갖는 동일한 재료의 수지 절연막에 의해 덮여진다.

또한, 스페이서(568)가 어떤 형태가 되더라도, 본 실시예의 경우에는 끝이 뾰족한 형태로 형성되는 것이 바람직하다. 본 실시예의 구조의 경우, 배향막은 스페이스(568) 상에 부득이하게 형성되며, 마찰 처리(rubbing process)가 실행되지만, 스페이서(568)를 갖는 스텝(stEEP) 단계가 있을 때 이 스페이서 앞서, 마찰 처리가 적절히 실행되지 않는 영역을 유발하는 위험이 있다. 이를 회피하기 위해, 끝이 뾰족한 모양을 스페이서(568)를 형성하는 것이 효과적이다. 예를 들면, 테이프의 각은 40 내지 90도(양호하게는 50 내지 70도)로 설정할 수 있다.

그 뒤, 드레인 배선(562)에 도달하기 위해 제3층간 절연막(564)과 패시베이션막(563) 내에 접촉 홀을 형성하며, 픽셀 전극(569)을 형성한다. 이 픽셀 전극(570, 571)은 인접하는 픽셀에 대해 각각 분리된 픽셀 전극이다. 투명 도전막은 픽셀 전극(569 내지 571)용으로 사용될 수 있고, 구체적으로, 110nm 두께의 주석 산화물 및 인듐 산화물의 합성막(ITO막이라 칭해짐)을 스퍼터링에 의해 형성한다. 픽셀 전극은 본 명세서에서는 "제2도전막"이라 칭해지는 경우가 있음을 알아야 한다.

알루미늄막 또는 실버막 등의 금속성막은 반사형 액정 표시 장치를 형성하는 경우, 픽셀 전극용 재료로서 사용될 수 있다.

또한, 저장 커패시터(572)는 픽셀 전극(569)과 차폐막(565)이 양극 산화막(567)을 통해 겹쳐지는 지점에 형성된다. 저장 커패시터(572)를 통해서만 계산되며, 차폐막과 픽셀 전극이 겹쳐지는 모든 영역이 저장 커패시터로서 기능한다.

이 경우, 차폐막(565)을 플로팅 상태(전기적으로 분리된 상태) 또는 일정한 전위에서 설정하는 것이 바람직하며, 더 양호하게는 공통 전위(데이터로서 전송된 화상 신호의 중간 전위)에서가 더 양호하다.

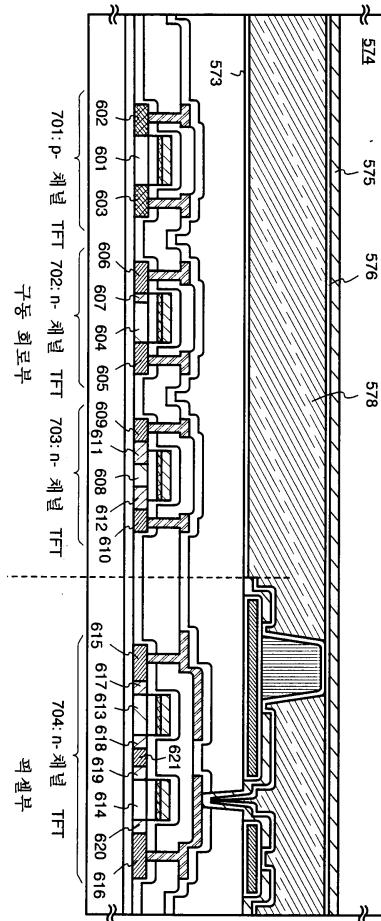

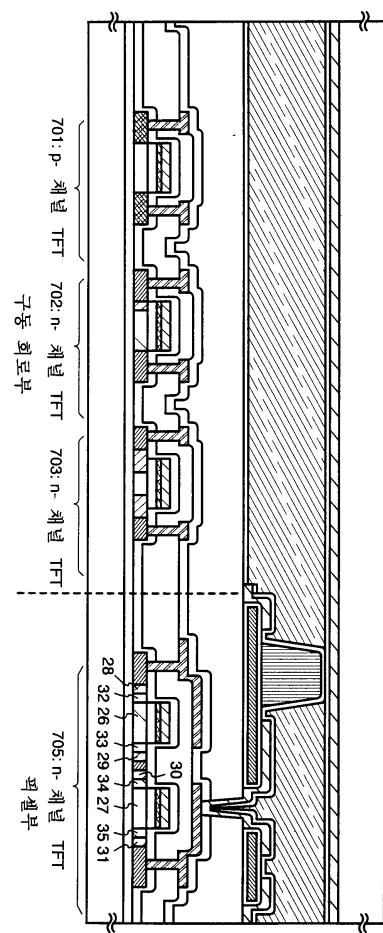

따라서, 구동 회로와 픽셀부가 동일한 기판(이하 액티브 매트릭스 기판이라 칭함) 상에 형성되어 기판이 완성된다. 도 8b의 p-채널 TFT(701) 및 n-채널 TFT(702,703)이 구동 회로 내에 형성되며, 이 픽셀 TFT(704)는 형성된 픽셀부 내에 n-채널 TFT로부터 형성됨을 알아야 한다.

제 1 실시예의 처리 순서는 적절히 변경될 수 있음을 알아야 한다. 순서가 무엇이든, 액티브 매트릭스 기판의 기본 기능은 최종 형성된 TFT의 기판이 도 8v에 도시된 바와 다르지 않고, 본 발명의 효과도 감소되지 않는다.

채널 형성 영역(601), 소스 영역(602) 및 드레인 영역(603)은 각각 구동 회로의 p-채널 TFT(701) 내의 p=형 불순물 영역(a)에 의해 형성된다.  $1 \times 10^{20}$  내지  $1 \times 10^{21}$  atoms/cm<sup>3</sup>의 농도의 인을 함유한 영역은 효과면에서 소스 영역 또는 드레인 영역의 부분에 존재함을 알 수 있다. 또한, 그 영역 내에 도 7의 (b)의 처리에서 제거된 측면 원소는 과도하게  $5 \times 10^{18}$  atoms/cm<sup>3</sup> 농도(양호하게는  $1 \times 20^{19}$  내지  $5 \times 20^{28}$  atoms/cm<sup>3</sup>의 농도)로 존재한다.

또한, 채널 형성 영역(604), 소스 영역(605) 및 드레인 영역(606)을 형성하는 채널은 n-채널 TFT(702) 내에 형성되며, 게이트 절연막을 삽입함으로써 게이트 배선과 겹치는 LDD 영역(이러한 영역은 Lov영역이라 칭하며, 'ov'는 겹침(overlap)을 의미한다)은 채널 형성 영역의 한 쪽(드레인 영역측)에 형성된다. 여기서, Lov 영역(607)은  $2 \times 10^{16}$  내지  $5 \times 10^{19}$  atoms/cm<sup>3</sup>의 농도의 인을 포함하며, 게이트 배선과 완전히 겹쳐지도록 형성된다.

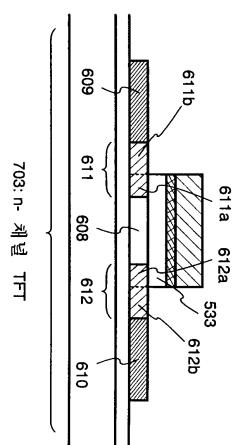

또한, 채널 형성 영역(608), 소스 영역(609) 및 드레인 영역(610)은 n-채널 TFT(703) 내에 형성된다. LDD 영역(611,612)은 채널 형성 영역의 양쪽에 형성된다. 절연막(Lov 영역)을 삽입함으로 게이트 배선과 겹치는 영역과 이 게이트 배선과 겹치지 않는 영역(이러한 영역은 Loff 영역이라 칭하며, 여기서, 'off'는 오프셋(offset)을 의미한다)은 실현되는데, 이는 LDD 영역(611,612)부가 이 구조에서 게이트 배선과 겹쳐지도록 배치되기 때문이다.

도 9의 단면도는 도 7의 (b)의 처리에서 제조되는 상태의 도 8b에 도시된 n-채널 TFT(703)을 도시하는 확대도이다. 여기에 도시된 바와 같이, LDD 영역(611)은 Lov 영역(611)과 Loff 영역(611b)으로 더 특징화되며, LDD 영역(612)은 Lov 영역(612)과 Loff 영역(612b)으로 더 특징화된다.  $2 \times 10^{16}$  내지  $5 \times 10^{19}$  atoms/cm<sup>3</sup>의 농도의 인이 Lov 영역(611a,611b)에 포함되어 있으며, Loff 영역(611a,612b)에는 1 내지 2배의 농도(일반적으로 1.2 내지 1.5배)가 포함되어 있다.

또한, 채널 형성 영역(613), 소스 영역(615), 드레인 영역(616), Loff 영역(618,619)과 접촉하여 제공된 Loff 영역(619) 및 n-형 불순물 영역(a)(612)은 픽셀 TFT(704) 내에 형성된다. 소스 영역(615) 및 드레인 영역(616) 각각은 n-형 불순물 영역(a)으로부터 형성되며, Loff 영역(617 내지 620)은 n-형 불순물 영역(c)에 의해 형성된다.

픽셀부의 회로 및 구동 회로 각각을 형성하는 TFT 구조는 요청된 회로 명세서에 대응하여 최적화될 수 있고, 반도체 장치의 동작 실행 및 그 신뢰성은 본 실시예에서 증가될 수 있다. 특히, n-채널 TFT내에 배치된 LDD 영역은 회로 명세서에 근거하여 Lov 영역 또는 Loff 영역을 적절히 사용함으로써 다르게 형성되며, 카운터 핫 캐리어(hot carrier)에 대한 측정에 매우 중요한 고속으로 동작하는 TFT 구조 및 낮은 off 전류 동작시 매우 중요한 TFT 구조가 동일한 기판상에서 실현될 수 있다.

액티브 매트릭스형 액정 표시 장치의 경우에, 예를 들면, n-채널 TFT(702)는 고속으로 동작하는, 즉, 시프트 레지스터 회로, 신호 분배 회로, 레벨 시프터 회로 및 버퍼 회로에 매우 중요한 구동 회로용으로 적절하다. 다시 말하면, 채널 형성 영역의 한쪽 면(드레인 영역측)에만 Lov 영역을 배치함으로써, 이것은 핫 캐리어 역측정들(hot carrier countermeasures)에 매우 중요하게 배치되는 반면, 저항성분이 줄어드는 구조가 된다. 이는, 상기 회로 그룹의 경우에, 소스 영역 및 드레인 영역이 변하지 않고 동작하며, 캐리어(전자) 이동 방향이 일정하기 때문이다. 그러나 필요하다면, Lov 영역은 채널 형성 영역의 양쪽에 배치될 수도 있다.

또한, n-채널 TFT(704)는 샘플링 회로(전송 게이트라고도 칭해짐)에 적절하며, 상기 샘플링 회로는 핫 캐리어 역측정들 및 낮은 off 전류 동작 모두에 강조를 둔다. 달리 말하면, 핫 캐리어 역탐지들은 Lov 영역의 배치에 의해 실현될 수 있고, 또한 낮은 off 전류 동작은 Loff 영역의 배치에 의해 실현된다. 더욱이, 샘플링 회로의 소스 영역 및 드레인 영역의 기능들이 반대로 되고, 180°만큼 캐리어 이동 방향이 변경된다; 따라서, 게이트 배선의 중심과 선형 대칭되는 구조가 사용되어야 한다. 이러한 환경들에 의존하여, Lov 영역을 형성하는 것만이 가능함을 알아야 한다.

또한, n-채널 TFT(704)는 픽셀부 또는 낮은 off 전류 동작에 매우 중요한 샘플링 회로용으로 적절하다. 즉, 상기 off 전류 값을 증가시키는 원인이 되는 Lov 영역은 사용되지 않으며, 단지 Loff 영역만 사용되었고, 이는 낮은 off 전류 동작을 실현시킨다. 더욱이, Loff 영역으로써 구동 회로 LDD 영역보다 농도가 더 낮은 LDD 영역을 사용함으로써, on 전류 값이 떨어지더라도, off 전류값은 전체적으로 낮게 측정될 수 있다. 또한, n-형 불순물 영역(a)(612)은 off 전류값을 낮게 하는 극단적인 효과가 있음을 알 수 있다.

또한, n-채널 TFT(702)의 Lov 영역(607)의 길이(폭)는 0.1 내지 3.0 $\mu\text{m}$ (일반적으로 0.2 내지 1.5 $\mu\text{m}$ )가 된다. 또한, n-채널 TFT(703)의 Lov 영역(611, 612a)의 길이(폭)는 0.1 내지 3.0 $\mu\text{m}$ (일반적으로 0.2 내지 1.5 $\mu\text{m}$ )가 되며, Lov 영역(611b, 612b)의 길이(폭)는 0.1 내지 3.5 $\mu\text{m}$ (일반적으로 1.5 내지 2.0 $\mu\text{m}$ )가 된다. 더욱이, 픽셀 TFT(704) 내에 형성된 Loff 영역(617 내지 620)의 길이(폭)는 0.5 내지 3.5 $\mu\text{m}$ (일반적으로 2.0 내지 2.5 $\mu\text{m}$ )가 된다.

또한, 본 실시예는 저장 정전 용량의 전자로서 7 내지 9의 높은 유전체 계수를 갖는 알루미늄막을 사용함으로써 요구되는 정전용량을 형성하기 위한 영역을 줄일 수 있다. 또한, 본 실시예에서 저장 정전 용량의 전자로서 픽셀 TFT 상에 형성된 차폐막을 사용함으로써, 액티브 액정 표시 장치의 화상 표시 부분의 구경비가 증가될 수 있다.

액티브 매트릭스 기판으로부터 액티브 매트릭스로부터 액정 표시 장치를 제조하는 처리를 이하 설명한다. 먼저, 배향막(573)을 도 8b에 도시된 구조를 갖는 액티브 매트릭스 기판상에 형성한다. 본 실시예에서, 폴리이미드막을 배향막으로서 사용한다. 투명 도전막과 배향막(576)을 포함하는 대향 전극(575)을 대향 기판(574) 상에 형성한다. 컬러 필터 또는 차폐막을 상기 대향 기판상에 필요하다면 형성할 수도 있음을 알아야 한다.

배향막을 형성한 이후, 마찰 처리를 실행하여, 액정 미립자 방위가 소정의 프리-틸트각을 갖도록 한다. 액티브 매트릭스 기판상에 픽셀부와 구동 회로가 형성되며, 대향 기판은 널리 공지된 셀 조립 처리를 통해 재료를 밀봉함으로써 적재된다.

액정(578)이 두 개의 기판 사이에 주입된 이후, 밀봉재(도시되지 않음)에 의해 완전히 밀봉된다. 공지된 액정 재료는 액정 용으로 사용될 수 있다. 따라서, 도 8b에 도시된 액티브 매트릭스 액정 표시 장치가 완성된다.

삽입 기판을 덮는 것이 가능해지며, 본 발명의 실행에 의해 저장 커패시터의 유전체 내에 우연히 형성된 핀 홀 및 차폐막과 픽셀 전극 사이의 단락을 발생시키는 결점이 해결될 수 있다. 따라서, 전반적인 제조 공정이 매우 개선될 수 있다.

그러나 본 발명에 도시된 수지 재료를 사용하는 경우에, 핀 홀을 충전할 때, 핀 홀 자체를 검출하는 것은 어렵고, 수지 재료의 많은 양이 핀 홀이 다른 영역에 비교되는 위치에 존재하여야 한다. 이 사실은 높은 탄소 농도를 갖는 영역이 저장 커패시터의 유전체 상에 부분적으로 존재함을 의미한다. SIMS(secondary ion mass spectroscopy) 또는 EDX(energy dispersion X-ray diffraction spectroscopy)등의 공지된 분석방법이 유전체 기판 내의 탄소 농도의 분산을 분석하는데 사용될 수 있다.

또한, 본 실시예의 수지 재료를 포함하는 스페이서가 본 실시예의 적응력에서 우수하기 때문에, 도 4를 이용하여 설명한 압착 처리에서 저장 커패시터에 인가된 압력이 완화(경감)될 수 있다. 더욱이, 본 실시예의 스페이서가 비드형의 스페이서에 비해 원소에 큰 접촉 영역을 가지기 때문에, 초과 압력이 특정 영역에 인가되지 않는다.

또한, 형성 위치가 자유롭게 설계되기 때문에, 화상 표시 영역이 효과적으로 이용될 수 있다. 이들은 본 실시예에서 형성될 수 있고, 이 영역은 차폐막 또는 소스 배선 상과 같은 화상 표시 영역으로서 사용되지 않는다. 뿐만 아니라, 스페이서는 수지 재료에 한정되어 형성되는 것은 아니며, 무기 재료로부터도 형성될 수 있다. 배향막(또는 픽셀 전극)으로 접촉 영역을 형성하기 위해 끝이 첨예한 형태로 스페이서를 형성하는 것과 압력을 분산하는 것이 효과적이다.

## 제 2 실시예

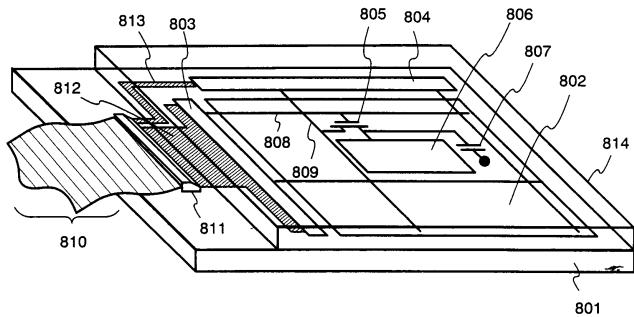

본 실시예에서, 제 1 실시예의 액티브 매트릭스 액정 표시 장치의 구조는 도 10의 도면을 참조하여 설명되었다. 액티브 매트릭스 기판은 픽셀부(802)에 형성되며, 게이트측의 구동회로(803) 및 소스측의 구동 회로(804)는 유리 기판(8012) 상에 형성된다. 픽셀부 내의 픽셀 TFT(805)는(도 8b에 도시된 픽셀 TFT(704)에 대응함) n-채널 TFT이며, 픽셀 전극(806) 및 저장 커패시터(807)와 접촉되어 있다(도 8a에 도시된 저장 커패시터(572)에 대응함).

주변에 제공된 구동 회로는 CMOS에 근거하여 형성되며, 게이트 측의 구동 회로(803) 와 소스측의 구동 회로(804)는 게이트 배선(808) 및 소스 배선(809)을 통해 각각 핀셀부(802)와 접촉된다. FPC(810)에 연결된 외부 입력/출력단(811)은 구동 회로에 신호를 전달하기 위한 입력/출력 배선(연결 배선; 812,813)과 함께 제공된다. 참조 번호(814)는 대향 기판이다.

도 10에 도시된 반도체 장치는 액티브 매트릭스 액정 표시 장치라 칭해지며, 도 10에 도시된 FPC를 갖는 액정 패널은 액정 모듈로 일반적으로 칭해짐을 알아야 한다. 따라서, 본 실시예의 액티브 매트릭스 액정 표시 장치는 액정 모듈이라 칭해질 수도 있다.

### 제 3 실시예

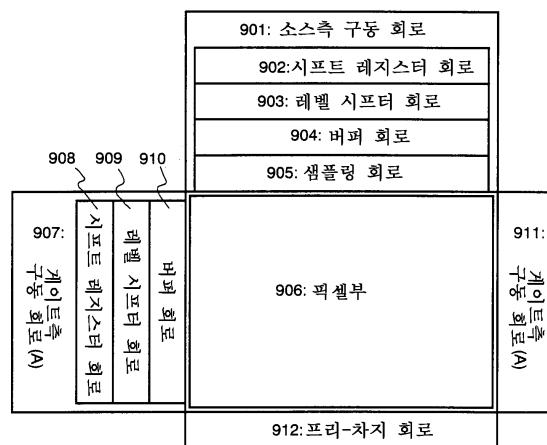

도 11은 제 2 실시예에 도시된 액티브 매트릭스 기판의 회로 구조의 일례를 도시한다. 제 3 실시예의 액정 표시 장치는 소스측 구동 회로(901), 게이트측 구동 회로A; 907), 게이트측 구동 회로B; 911), 프리-차지 회로(912) 및 핀셀부(906)를 포함한다. 명세서를 통해, 구동 회로는 소스측 처리 회로 및 게이트측 구동 회로를 포함하는 일반적인 명칭이다.

소스측 구동 회로(901)는 시프트 레지스터(902), 레벨 시프터(903), 버퍼 회로(904) 및 샘플링 회로(905)와 함께 제공된다. 또한, 게이트측 구동 회로(A; 907)는 시프트 레지스터(908), 레벨 시프터(909) 및 버퍼 회로(910)와 함께 제공된다. 스캐닝 신호 구동 회로(B; 911)가 유사한 구조를 갖는다.

시프트 레지스터(902,908)용의 구동 전압은 5 내지 16v(일반적으로 10v)로 높게 설정되며, 도 8v의 참조 번호(702)에 의해 도시된 구조는 회로를 형성하는 CMOS 회로에서 사용되는 n-채널 TFT용으로 적당하다.

더욱이, 구동 전압은 레벨 시프터(903,909)용의 14 내지 16v로 높지만, 비슷하게, 도 8b에 도시된 n-채널 TFT(702)를 포함하는 시프트 레지스터 CMOS 회로가 적절하다. 게이트 배선용 3중 게이트 구조 및 2중 게이트 구조 등의 멀티 게이트 구조를 사용하면, 각각의 회로의 신뢰성을 증가시키는 효과를 얻을 수 있다.

또한, 샘플링 회로(905)는 14 내지 16v의 구동 전압을 갖지만, 소스 영역과 드레인 영역은 반전되며, off 전류값을 감소시키는 것이 필수적이며, 도 8b에 도시된 n-채널 TFT(703)을 포함하는 CMOS 회로가 절절하게 된다. n-채널 TFT는 도 8b에만 도시하였지만, 샘플링 회로 형성시 n-채널 TFT 및 p-채널 TFT가 조합됨을 알아야 한다.

또한, 핀셀부(906)는 14 재지 16v의 구동 전압을 갖지만, 샘플링 회로(905)보다 낮은 off 전류값을 감소시키는 것이 필수적이다. 그러므로 off 전류의 증가를 유도하는 Lov 영역 내에 증착되지 않는 구조를 사용하는 것이 바람직하며, 핀셀 TFT 용으로는 도 8b의 n-채널 TFT(704)를 사용하는 것이 바람직하다.

제 3 실시예의 구조는 제 1 실시예에 도시된 제조 방법에 따라 TFT를 제조함으로써 용이하게 실행될 수 있다. 제 3 실시예가 핀셀부의 구조 및 구동 회로만 도시함으로써 제 1 실시예의 제조 방법을 따름으로써 동일한 구조 위에 신호 분배기 회로, D/A 컨버터 회로, 연산 증폭 회로 및 보상 회로 등의 구동 회로보다 논리 회로(신호 처리 회로)를 형성하는 것이 가능해지며, 더욱이, 메모리부와 마이크로 프로세서 등을 형성하는 것이 가능해진다.

### 제 4 실시예

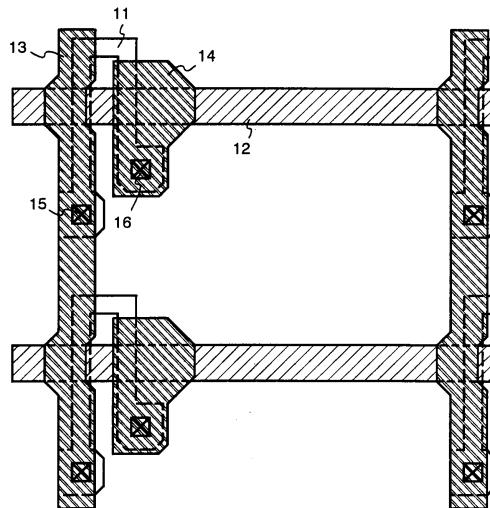

본 실시예는 도 12a 및 12b를 참조하여 설명한 핀셀부를 형성하는 복수의 핀셀의 구조에 관련된 실시예이다.

먼저, 도 12a에서, 참조 번호(11,12,13,14)는 액티브층, 게이트 배선(게이트 전극을 포함), 소스 배선 및 드레인 배선을 각각 나타낸다. 참조 번호(15,16)는 소스 배선(13)과 드레인 배선(14)가 액티브층(11)과 접속되어 있는 접속 부분이 각각 된다. 이 구조는 제 1 실시예의 도 7의 (c)에 설명된 상태의 평면도와 일치한다.

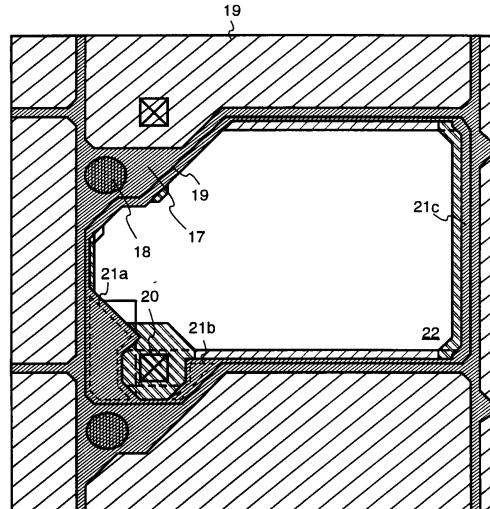

또한, 도 12b에 도시된 바와 같이, 차폐막(17), 이 차폐막(17)에 형성된 산화물(도시되지 않음), 이 산화물에 형성되어 수지 재료로 구성된 스페이서(18) 및 핀셀 전극(19)이 형성된다. 참조 번호(20)는 드레인 배선(14)이 핀셀 전극(19)과 접속되어 있는 접촉부를 나타낸다. 이 구조는 제 1 실시예의 도 8b에 설명된 상태의 평면도와 일치한다.

여기서, 차폐막(17), 도시되지 않은 산화막 및 핀셀 전극(19)이 서로 겹쳐진 영역이 저장 커패시터를 형성한다. 도 12b에서, 영역(21a 재지 21c)은 저장 커패시터이다. 핀셀 전극(19)은 핀셀의 외부 주변부에서도 차폐막(17)과 겹쳐지며, 저장 커패시터는 그 영역 내에 형성된다.

상술한 바와 같이, 본 발명에 따라, 작은 영역으로 큰 용량을 보장할 수 있는 저장 커패시터가 형성될 수 있다. 도한, 스페이서(18)가 차폐막(17)과 함께 제공되며, 화상 표시 영역(22)이 스페이서(18)에 의해 더 작게 구성되지 않는다.

상기 픽셀 구조는 본 실시예의 구조로 제한되지 않음을 알아야 한다. 또한, 본 실시예의 구조는 제 1 실시예의 제조 공정에 따라 형성될 수 있고, 제 2 및 제 3 실시예의 액정 표시 장치 내의 픽셀로서 사용될 수 있다.

## 제 5 실시예

본 실시예에서, 제 1 실시예의 구조와 상이하게 구성된 픽셀부를 갖는 액티브 매트릭스 액정 표시는 도 13을 참조하여 설명하였다. 그 기본 구조는 도 8b에 설명된 구조와 유사하기 때문에, 상이한 부분만을 설명하였다. 특히 설명되지 않은 그밖의 부분들은 도 8b에 설명되어 있다.

도 13에 설명된 구조에 있어서, 픽셀부를 형성하는 픽셀 TFT(n-채널형 TFT)의 구조는 제 2 실시예와는 상이하다. 특히, 본 실시예에서, 오프셋 영역(32 내지 35)은 n형 불순물 영역(c)으로 구성된 영역(26,27) 및 LDD 영역(Loff 영역; 28 내지 31)을 형성하는 채널 사이에 형성된다.

오프셋 영역(32 내지 35)은 채널 형성 영역(채널 형성 영역 내에 함유된 것과 같은 영역 내에 포함된 불순물 원소)의 것과 동일하며, 게이트 전극과 겹쳐지지 않는 구성성분, 반도체층을 의미한다. 이 오프셋 영역(32 내지 35)은 오프-상태 전류값을 감소시키는 효과가 있으며, 단순 저항으로서 기능한다.

제 1 실시예의 도 6의 (d)에 설명된 과정에서 예를 들면, 이 구조를 구체화하기 위해, n형 불순물 원소를 첨가하기 전에, 실리콘을 함유한 절연막이 게이트 배선 등을 덮기 위해 20 내지 200nm(양호하게는 25 내지 150nm)의 두께로 형성된다.

불순물 원소가 그 위에 형성된 절연막을 갖는 게이트 전극(524a, 524b)의 측벽에 부가되기 때문에, 오프셋 영역(32 내지 35)이 마스크가 존재하는 부분에 형성된다. 따라서, 절연막의 두께와 충분히 동일한 방식으로 형성된 오프셋 영역(32 내지 35)의 길이는 20 내지 200nm(양호하게는 25 내지 150nm)가 된다.

절연막의 재료는 게이트 절연막과 동일한 재료가 양호하며, 이 경우, 절연막은 도 6의 (e)에 도시되 공정으로 게이트 절연막과 동시에 제거될 수 있다.

본 실시예의 구조는 제 1 실시예에 설명된 공정 일부를 수정함으로써 구체화될 수 있고, 제 2 내지 제 4 실시예에 설명된 임의의 구조와 자유롭게 결합될 수 있다.

## 제 6 실시예

픽셀 전극(본 실시예의 차폐막)과 접속되지 않은 전위를 고정함으로써, 저장 커패시터는 이 픽셀부의 각 픽셀에 형성될 수 있다. 이 경우, 차폐막의 전위는 플로팅 상태(전기적으로 분리된 상태)로 설정되며, 공통 전위(데이터로서 전송된 픽셀의 순간 전위)로 양호하게 설정된다.

본 실시예에서, 차폐막이 공통 전위로 고정되는 경우, 접속 방법은 도 14a, 14b를 참조하여 설명하였다. 그 기본 구조는 도 8b에 도시된 픽셀 구조와 유사하기 때문에 참조 번호를 그 부분과 일치시켰다.

도 14a를 참조하면, 참조 번호(704)는 제 1 실시예와 동일하게 형성된 픽셀 TFT(n 채널 TFT)을 나타내며, 참조 번호(565)는 저장 커패시터의 하나의 전극으로서 기능하는 차폐막을 나타낸다. 픽셀부 외부로 연장하여 있는 차폐막(36)은 제 3 층간 절연막(564)을 통해 공통 전위를 제공하는 전원 공급선로(38)와 패시베이션막(563)에 제공된 접촉 홀(37)에 접속된다. 전원 공급선로(38)는 소스 배선 또는 드레인 배선과 동시에 형성될 수 있다.

이 방식으로, 차폐막(36)을 공통 전위 제공용 전원 공급 선로(38)를 픽셀부의 외부에 전기적으로 연결함으로써, 차폐막(565)을 공통 전위에 연결할 수 있다.

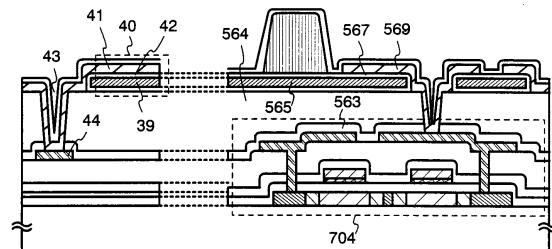

다음으로, 도 14b를 참조하면, 참조 번호(704)는 제 1 실시예와 비슷한 방식으로 형성된 픽셀 TFT를 도시하며, 참조 번호(565)는 저장 커패시터의 하나의 전극으로 동작하는 차폐막을 나타낸다. 차폐막(39)은 참조 번호(40)로 표시된 영역 내의 산화물(42)을 통해 도전막(41)과 겹쳐지는 픽셀부 외부에 존재한다. 도전막(41)은 픽셀 전극(569)과 동시에 형성된다.

도전막(41)은 접촉 홀(43)을 통해 공통 전위 제공용 전원 공급 라인(44)과 접속된다. 여기서, 영역(40)에서, 차폐막(39), 산화물(420 및 도전막(41)으로 이루어진 커페시터가 형성된다. 커페시터의 정전 용량이 충분히 큰 경우(하나의 스캐닝 선로용의 모든 픽셀과 연결된 모든 저장 커페시터의 전체 정전 용량의 10배 정도), 차폐막(39,565)의 전위 파동(potential fluctuation)은 영역(40) 내에 형성된 정전커플링에 의해 감소될 수 있다.

도 14b에서 설명된 구조가 채용되는 경우, 소스 선로 반전 구동은 액티브 매트릭스 액정 표시 장치를 구동하는 방법으로서 양호하게 채용될 수 있다. 소스 선로 반전 구동에서, 픽셀 전극에 인가된 전압의 극성이 하나의 각 프레임에 관하여 반전되기 때문에, 차폐막(565)에 누적된 전하는 일시적으로 평균화될 때 거의 0이 되며, 전위 파동이 매우 작게 되는 상태가 유지될 수 있으므로, 안정한 저장 커페시터가 형성될 수 있다.

이 방식에서, 도 14b에 설명된 구조를 선택하는 경우, 차폐막은 상기 과정의 수를 증가시키지 않고 공통 전위로 유지할 수 있다.

본 실시예의 구조는 제 1 실시예에서 설명된 제조 공정 일부를 수정함으로써, 구체화될 수 있으며, 이 공정의 나머지는 제 1 실시예의 것과 동일하다. 또한, 본 실시예의 구조는 제 2 내지 5 실시예에 설명된 임의의 구조와 자유롭게 결합될 수 있다.

### 제 7 실시예

제 1 실시예의 양극 산화막(567) 형성시의 양극 산화 방법의 실례가 제 7 실시예에 설명되어 있다.

본 실시예에서, 먼저, 충분히 낮은 알칼리 이온 농도를 갖는 주석 산화 에틸렌 글리콜이 형성된다. 이것은 15%의 주석 산화 암모늄 수성 용액과 에틸렌 글리콜 용액이 2:8 비율로 혼합된 용액이다. 수성 암모니아는 pH가  $7 \pm 0.5$ 로 조절되도록 첨가된다. 백금 전자는 음극으로서 용액에 첨가되며, 차폐막(565)이 형성된 기판은 용액 속에 가라앉히고, 일정한 dc 전류는 애노드로서 차폐막(565)에 인가된다. dc 전류량은 양극 산화물에 놓여진 차폐막(565)의 표면에 의해 변하고, 이것은 30 내지  $100\mu\text{A}/\text{cm}^2$ , 양호하게는 50 내지  $70\mu\text{A}/\text{cm}^2$ 으로 설정될 수 있다. 본 실시예에서는  $60\mu\text{m}/\text{cm}^2$ 으로 설정하였다.

용액의 음극과 양극 사이의 전압은 산화막 성장에 따른 시간에 따라 변한다. 이 전압은 일정한 전류하의  $100\text{v}/\text{min}$  비율로 증가하며, 양극 산화 처리는 전압이 45V가 될 때 정지한다. 따라서, 양극 산화 기판(567)은 차폐막(565)의 표면상에 대략 50 nm의 두께로 형성될 수 있다. 그 결과, 차폐막(565)의 두께는 90nm가 된다. 양극 산화 처리에 대해 도시한 많은 값은 단지 예로서 도시되었고, 이들은 제조되는 원소의 크기에 의존하여 가장 적절한 값으로 다양하게 변화될 수 있다.

상술한 바와 같은 양극 산화 처리를 실행함으로써, 제 3 층간 절연막(564) 상의 차폐막(565)을 직접적으로 형성하는 경우에도, 차폐막(565)의 열등한 점착성이 문제가 되지 않는다. 다시 말하면, 실리콘 산화막(566)을 제조하는 처리는 도 7의 (d)의 처리에서 생략될 수 있다.

본 실시예에서는 제 1 실시예의 양극 산화 처리에 대한 조건만이 변경되었으며, 본 실시예와 다른 제 2 내지 제 6 실시예의 임의의 구조와 자유롭게 결합할 수 있다.

### 제 8 실시예

제 1 실시예에서, 도 5의 (b)에 설명된 처리후, 결정질의 실리콘막(504)이 패턴화되며, 액티브층(505 내지 508)이 형성된 이후, p형 불순물 영역(b)과 n형 불순물 영역(b)이 형성된다. 다른 한편, 본 발명에 따라, p형 불순물 영역(b)과 n형 불순물 영역(b)은 결정질 실리콘막(504)이 패턴화되기 전에 형성될 수 있다.

이 경우, p형 불순물 영역(b)과 n형 불순물 영역(b)(제 1 실시예의 도 5의 (f)에서 설명된 레이저 어닐링 처리에 따라)을 활성화하는 처리가 결정질 실리콘막이 패턴화되기 전에 수행될 수 있다. 그러므로 레이저 어닐링 처리의 최적 상태가 패턴설계(액티브층 등의 위치 및 형태)에 의존하여 변하는 불편함을 방지할 수 있다. 다시 말하면, TFT가 형성될 때 설계의 자유도가 개선되는 장점이 있다.

본 실시예는 제 1 실시예의 처리의 순서만을 변화시킴으로써 구체화할 수 있음을 알 수 있고, 제 2 내지 7 실시예에서 설명된 임의의 구조와 자유롭게 결합될 수 있다.

### 제 9 실시예

제 1 실시예에 설명된 제조 공정에서, 채널 도핑 처리가 임계 전압을 제어하기 위해 n-채널 TFT가 되도록 영역에 관해서만 실행되며, 채널 도핑 처리는 n-채널 TFT 및 p-채널 TFT를 구별함 없이 전체 표면에 관하여 실행될 수 있다. 이 경우, 제조 공정시 필요한 포토마스크의 수가 감소하기 때문에, 처리의 작업량 및 수율이 개선될 수 있다.

또한, 이 상황에 의존하여, 채널 도핑 처리는 전체 표면 및, 이 전체 표면에 첨가된 불순물 원소가 n-채널 TFT 또는 p-채널 TFT 중 하나에 첨가될 수 있는 반대의 도전성 형태를 제공하기 위한 불순물 원소와 전체 표면에 관련하여 실행될 수 있다.

본 실시예의 구조가 제 1 내지 제 8 실시예에 설명된 임의의 구조와 자유롭게 결합할 수 있음을 알 수 있다.

### 제 10 실시예

본 실시예의 제조 공정에서, 결정 구조를 포함하는 반도체막은 결정화 제조용의 촉매원소를 이용하여 형성된다. 본 실시예에서, 결정 구조를 포함하는 반도체막이 촉매 원소 없이 그리고, 레이저 결정화 또는 열 결정화를 이용하여 형성되는 경우를 설명한다.

열 결정화의 경우, 비결정질 구조를 포함하는 반도체막을 형성한 이후, 열 처리는 600 내지 650°C로 15 내지 24 시간 동안 실행된다. 600°C 이상으로 열 처리를 실행함으로써, 자연 핵(natural nuclei)이 생성되고 결정화가 진행된다.

레이저 결정화의 경우, 비결정질 구조를 포함하는 반도체막이 형성된 이후, 레이저 어닐링 처리가 제 1 실시예에서 설명된 제 1 어닐링 조건으로 실행된다. 이것은 짧은 시간에 결정구조를 포함하는 반도체막을 형성할 수 있게 한다. 물론, 램프 어닐링이 레이저 어닐링을 대신하여 실행될 수 있다.

상술된 바와 같이, TFT용 결정 구조를 포함하는 반도체막은 임의의 공지된 수단을 사용하여 형성될 수 있다. 본 실시예가 실시예들 1 내지 9에 기술된 임의의 구조로 자유롭게 조합될 수 있다는 것을 알아야 한다.

### 제 11 실시예

본 실시예에서, TFT의 액티브 레이저를 형성하는 결정질 실리콘막에 대한 제조 방법이 일본 특허 출원 제 평 11-76967의 명세서의 제 1 실시예에 설명되어 있다. 상술된 상태의 명세서의 제 1 실시예의 제조 공정에 따라, 특정 결정질 구조의 결정질 실리콘막이 획득된다.

본 출원인에 의한 일본 특허 출원 제 평 10-044659, 평 10-152316, 평 10-152308 또는 평 10-152305에는 결정질 실리콘에 대해 상세히 언급되어 있다. 출원인에 의해 실험적으로 분석된 결정질 구조의 특성에 대한 요약을 후술한다. 이 특징은 본 실시예를 실행함으로써 완성된 TFT의 액티브층을 형성하는 반도체층의 특성과 일치한다고 가정한다.

상술된 결정질 실리콘막은 현미경으로 봤을 때 복수의 바늘형 또는 원통형 결정(이하 원통형 결정이라 칭함)이 모여서 정렬된다. 이것은 TEM(transmission electron microscopy)을 사용하는 관찰을 통해 쉽게 확증할 수 있다.

{110} 평면은 그 결정축이 (채널이 형성되는) 그 표면상에서 전자 회절에 의해 더 또는 덜 이동되는 지향된 막(orientated film)으로서 관찰될 수 있다. 이것은 {110} 평면에 규칙적인 특성을 갖는 확산 스폿이 1.35μm의 스폿 직경을 갖는 전자 확산 사진을 통해 발견됨으로써 확증될 수 있다. 또한, 이 스폿이 동심원 상에 분산됨이 확증된다.

또한, 방위율(orientation ratio)이 X-선 확산(특히,  $\bar{e}$ -2 $\bar{e}$  방법을 사용하는 X-선 확산)에 의해 계산될 때, {220} 평면의 방위율은 0.7 이상(일반적으로 0.85 이상)이 된다. 방위비의 계산을 위해, 일본 특허 출원 Laid-open 제 평 7-321339호에 개시된 방법이 사용된다.

서로 접촉하는 기동형 결정으로부터 형성된 결정 입자 경계가 HR-TEM(high resolution transmissive electron microscopy)에 의해 관찰될 때 결정 입자 경계 내의 결정 격자에 연속성이 있음이 확증된다. 관찰된 격자 스트라이프들이 결정 입자 경계에 연속하여 접속되어 있는 사실에 의해 쉽게 확증된다.

결정 입자 경계 내의 결정 격자의 연속성은 결정 입자 경계가 '평면 입자 경계'로 불리는 입자 경계 내에서 시작된다. 이 명세서에서 용어, 평면 입자 경계의 정의는 Ryuichi Shimokawa 및 Yutaka Hayashi에 의해 1998년 Japanese Journal of Applied Physics, 27권 5호의 pp. 751-758에 발표된 "Characterization of High-Efficiency Cast-Si Solar Cell Wafers by MBIC Measurement"에 개시된 '평면 경계'와 일치한다.

상술된 논문에 따라, 평면 경계는 쌍의 입자 경계, 특별한 스태킹 결점(stacking fault), 특별한 트위스트 입자 경계등을 포함한다. 평면 경계는 전기적으로 활성이 없다. 다시 말하면, 결정 입자 경계가 있음에도 캐리어들의 이동을 방해하는 장해물로 동작하지 않기 때문에, 실질적으로 존재하지 않는 것으로 간주될 수 있다.

결정축(결정 평면에 수직인 축)이  $<110>$  축일 때, 실질적으로, {211} 쌍 입자 경계는 또한,  $\Sigma 3$ 의 대응하는 입자 경계로 불린다. 상기  $\Sigma$  값은 대응하는 경계 내의 배향의 정도를 보여주는 지시자로서 역할하는 파라미터이며, 이것은 작은  $\Sigma$  값이 양호한 배향을 보여주는 입자 경계로 알려져 있다. 본 실시예의 결정질 실리콘막이 TEM을 사용하여 실제로 상세히 관찰될 때, 대부분의 결정 입자 경계(90% 이상, 일반적으로 95% 이상)는  $\Sigma 3$ 의 대응하는 입자 경계가 되면, 일반적으로 {211} 쌍 입자 경계가 됨을 알 수 있다.

{110}의 결정 평면 방위를 갖는 두 개의 결정 입자 사이에 형성된 결정 입자 경계에 있어서, {111} 평면에 대응하는 격자 스트립에 의해 형성된 각  $\Theta$ 가 70.5도인 경우,  $\Sigma 3$ 의 대응하는 입자 경계를 만드는 것은 공지되어 있다. 본 실시예에서 확보된 결정질 실리콘막에서, 격자 스트라이프는 결정 입자 경계 내의 인접한 결정 입자에서 약 70.5도의 각으로 유지된다. 그러므로 결정 입자 경계가  $\Sigma 3$ 의 대응하는 입자 경계인 것을 알 수 있다.

$\Theta = 70.5$ 도인 경우,  $\Sigma 9$ 의 대응하는 입자 경계가 형성되고, 다른 대응하는 입자 경계가 존재함을 알아야 한다. 이것이 자력(inert)이 없다는 점에서 차이가 없다.

이러한 결정 구조(엄격히, 결정 입자 경계의 구조)는 상이한 2개의 결정 입자가 결정 입자 경계에서 매우 잘 정렬되는 방식으로 접속됨을 나타낸다. 즉, 결정 격자들은 결정 입자 경계에 연속적으로 접속되어 있어서, 결정 결합 등에 의한 트랩 레벨(trap level)이 거의 형성되지 않는다. 그러므로 결정 구조를 갖는 반도체 박막은 결정 입자 경계를 실질적으로 갖지 않는다고 고려할 수 있다.

TEM 관찰은 결정 입자에 존재하는 대부분의 결함이 800 내지 1150°C(열 산화 처리 또는 활성화 처리)의 고온에서 열 처리 단계에 의해 제거될 수 있는 것을 변경한다. 또한, 이것은 열 처리 단계이전의 결함에 비해 열 처리 단계 이후에 많은 결함이 감소하는 사실로부터 명확해 진다.

결함의 수에서 이 차이는 전자 스핀 공명(ESR) 분석의 스핀 밀도에서 차이로서 나타난다. 이러한 환경하에, 본 실시예의 결정질 실리콘막이  $5 \times 10^{17}$  스핀/cm<sup>3</sup>(양호하게는  $3 \times 10^{17}$  스핀/cm<sup>3</sup> 이하)의 스핀 밀도를 가짐을 알 수 있다. 그러나 이 측정된 값은 기존 측정 장비의 검출 한계에 이른 값이므로, 실제 상기 막의 스핀 밀도는 더 낮을 것으로 기대된다.

상술된 사실로부터, 본 실시예의 결정 실리콘막은 결정 입자의 극히 작은 수의 결점을 가지며, 실제적으로 결정 입자 경계가 없다. 그러므로 단결정 실리콘막 또는 본질적으로 단결정 실리콘막으로서 가정될 수 있다.

본 실시예에서 설명된 TFT의 액티브층으로서 상술된 특정 결정 구조를 갖는 결정질 실리콘막을 사용하는 것이 가능하다. 따라서, 우수한 전자 성능을 보여준 TFT가 형성되며, 반도체 장치의 동작 성능을 강화하는 것을 가능하게 한다.

제 1 실시예의 처리중 일부를 변경함으로써 본 실시예의 구조를 실행하는 것이 가능함을 알아야 한다. 제 2 내지 10 실시예의 임의의 구성과 본 실시예를 결합하는 것이 가능하다.

## 제 12 실시예

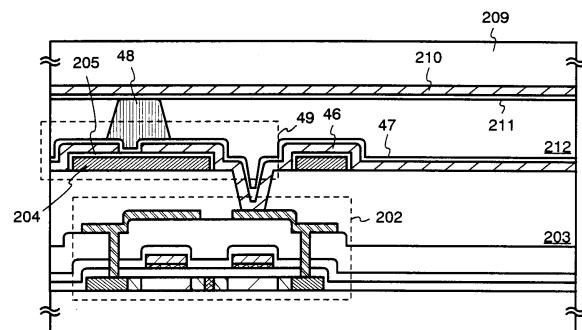

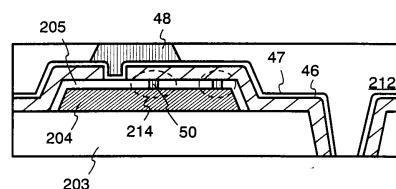

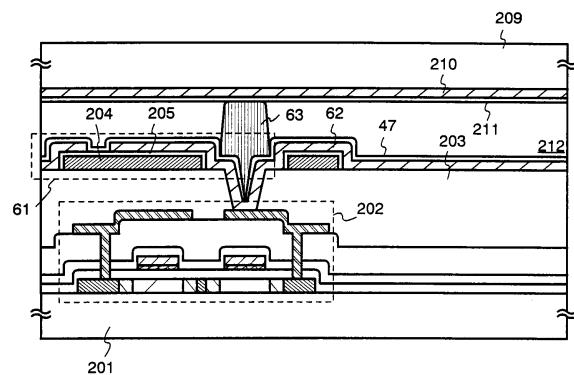

본 실시예에서, 저장 커패시터의 유전체 내에 형성된 핀 홀은 제 1 실시예와는 다른 처리에 따라 충전된다. 먼저, 본 실시예의 팩셀 구조를 설명하는 도 15a를 참조하면, 도 2a 및 2b에 설명된 경우와 비슷하게, 차폐막(204)과 산화막(205)은 TFT(2020상의 평탄화막(203)을 통해 제공된다.

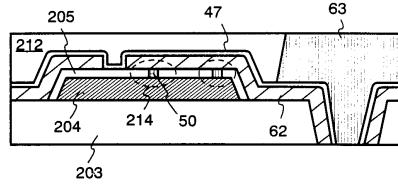

그 뒤, 픽셀 전극(46)은 산화물(205)을 통해 차폐막(204)과 겹쳐지도록 제공되며, 배향막(47)은 픽셀 전극과 겹쳐지도록 제공되고, 수지 재료로 이루어진 스페이서(48)는 배향막(47) 상에 형성된다. 도 15b는 도 15a의 점선(49)에 의해 둘러싸인 영역의 확대도 임을 알 수 있다. 도 15b에서 설명한 바와 같이, 산화물(205) 내에 형성된 핀 홀(214)은 충전재(50)로 충전된다.

제 1 실시예에서, 저장 커패시터의 유전체 내의 핀 홀은 수지 재료로 이루어진 스페이서가 형성될 때, 동시에 스페이서의 재료를 이용하여 충전된다. 본 실시예에서, 핀 홀은 픽셀 전극(46)이 형성되지 이전에 미리 충전되며, 그 이후, 픽셀 전극(46), 배향막(47) 및 스페이서(48)가 형성된다.

여기서, 본 실시예에서 사용된 핀 홀을 충전하는 처리는 도 16A 내지 17B를 참조하여 설명하였다.

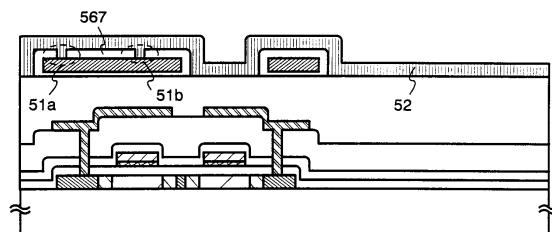

먼저, 제 1 실시예의 제조 과정에 따라, 도 17D에서 설명된 처리가 완료된다. 여기서, 핀 홀(51a, 51b)은 양극 산화물이 투과될 때 부착된 먼지 등으로 인해 양극 산화물(567) 내에 형성된다고 가정하자.

그 뒤, 수지 절연막(본 실시예에서, 폴리이미드막)(52)은 0.1 내지 1 $\mu\text{m}$ (일반적으로 0.2 내지 0.3 $\mu\text{m}$ )의 두께로 형성된다. 여기서, 핀 홀(51a, 51b)은 수지 절연막(52)으로 충전된다(도 16a).

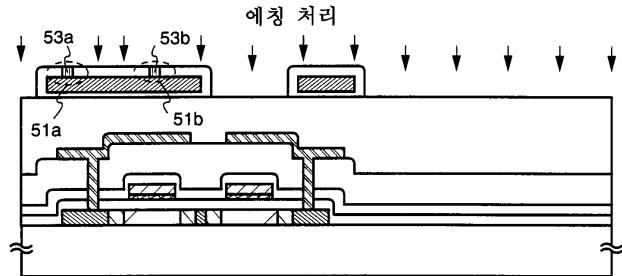

그 다음, 산소를 이용하여 플라즈마가 형성된다. 처리될 기판을 플라즈마에 노출하여 수지 절연막(52)이 에칭된다. 이에 칭은 수지 재료의 애싱(ashing) 처리로 공지되어 있다(도 16b).

이 처리에 의해, 양극 산화물(567) 상에 형성된 수지 절연막(52)이 완전히 제거되며, 핀 홀(51a, 51b) 내에 충전된 수지 절연막의 일부가 제거되지 않은 상태로 남겨진다. 다시 말하면, 도 16b에 설명된 바와 같이, 핀 홀(51a, 51b)이 수지 절연막(52)의 일부(충전재(53a, 53b))를 충전하는 상태가 얻어질 수 있다.

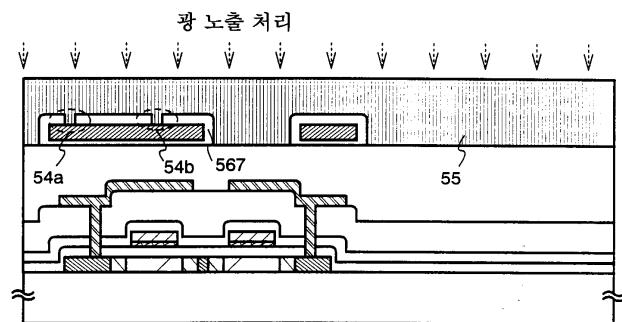

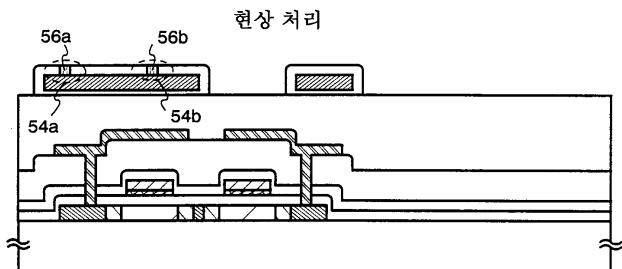

대안으로, 도 17a 및 17b에 설명된 처리가 사용될 수 있다. 먼저, 제 1 실시예의 제조 공정에 따라, 도 17d에 설명된 처리가 완료된다. 여기서, 핀 홀(54a, 54b)은 양극 산화물이 투과될 때 부착된 먼지 등으로 인한 양극 산화물(567) 내에 형성된다고 가정한다.

그 뒤, 합성 절연막(본 실시예에서는 포지티브 감광성을 갖는 아크릴 수지막)(55)이 0.1 내지 1 $\mu\text{m}$ (일반적으로 0.2 내지 0.3 $\mu\text{m}$ )의 두께로 형성된다. 여기서, 핀 홀(54a, 54b)은 수지 절연막(55)으로 충전된다(도 17a).

그 다음, 수지 절연막(55)은 통상의 노출 상태하에서 빛에 노출되고, 노출된 수지 절연막(55)은 통상의 현상 처리에 의해 제거된다. 이 처리에 의해, 양극 산화물(567) 상에 형성된 수지 절연막(55)이 완전히 제거되며, 핀 홀(54a, 54b)을 충전하는 수지 절연막의 일부가 노출되지 않은 상태로 남아 있게 된다. 다시 말하면, 도 17b에 설명된 바와 같이, 핀 홀(54a, 54b)이 수지 절연막(55)의 일부(충전재(56a, 56b))를 충전하는 상태가 얻어질 수 있다.

도 16b 또는 17b에 설명된 상태가 얻어진 이후, 픽셀 전극(46), 배향막(47) 및 스페이서(48)가 형성된다. 그 뒤, 셀 조립 처리를 실행함으로써, 도 15a에 설명된 픽셀 구조를 얻을 수 있다.

보 실시예의 구조는 제 2 내지 11 실시예에서 설명된 임의의 구조와도 자유롭게 결합할 수 있음을 알아야 한다.

### 제 13 실시예

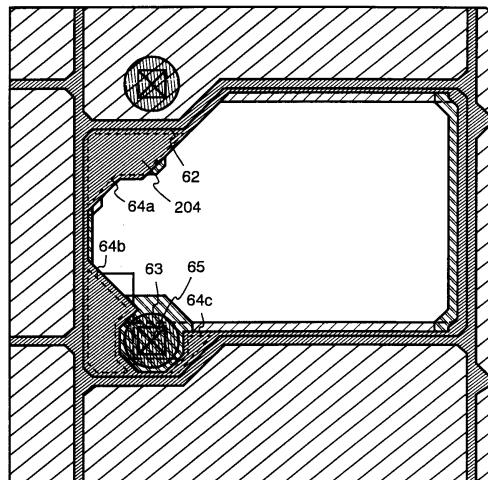

본 실시예에서, 수지 재료로 이루어진 스페이서는 도 15a 및 15b를 참조로 설명한 픽셀 구조와는 상이한 위치에서 형성된다. 도 18a에 설명한 픽셀 구조 그 자체가 도 15a에서 설명한 것과 동일함을 알 수 있고, 스페이서가 형성되는 위치만 다름을 알 수 있다. 도 18b는 도 18a의 점선(61)에 의해 둘러싸인 영역의 확대도이다.

본 실시예에서, 스페이서(63)는 픽셀TFT(202)이 픽셀 전극(62)과 접촉되어 있는 접촉부 위에 제공된다. 본 실시예의 구조는 접촉부(충간 절연막(203)의 두께)에 형성되는 단계를 충전하는 것을 가능하게 하며, 상기 단계로 인한 액정 미립자의 잘못된 방위를 방지할 수 있다.

도 19는 본 실시예의 픽셀 구조를 도시하는 평면도이다. 도 19에서, 픽셀 전극(62)은 도시되지는 않았지만, 산화물(205)을 통해 차폐막(204) 상에 제공된다. 여기서, 차폐막(204), 산화물(205) 및 픽셀 전극(62)은 저장 커패시터(64a 내지 64c)를 형성한다.

또한, 수지 재료로 이루어진 스페이서(63)는 픽셀 전극의 접촉부(65) 위에 형성된다. 수지 재료로 이루어진 이러한 스페이서는 그 위치가 설계시 자유롭게 결정될 수 있는 장점을 가진다.

본 실시예의 스페이서(63)와 제 12 실시예에서 설명된 스페이서(48)(도 15a 참조) 모두는 결합되어 사용될 수 있고, 픽셀의 위치에 의존하여 이를 개별적으로 사용될 수 있다. 또한, 본 실시예의 구조는 제 2 및 12 실시예에서 설명된 임의의 구조와 자유롭게 결합될 수 있다.

#### 제 14 실시예

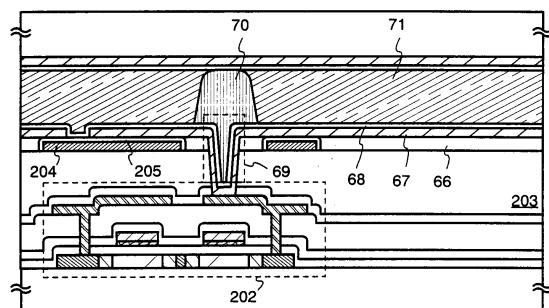

본 실시예에서, 제 12 실시예에서 설명된 픽셀 구조와 상이한 구조가 도 20을 참조하여 설명되어 있다. 도 15a 및 15b의 동일한 부품에 대해서는 동일한 참조 번호를 기재하였다.

도 20에 도시된 바와 같이, 차폐막(204)은 중간 절연막(203)을 통해 TFT(202) 상에 제공된다. 산화물(205)은 차폐막(204) 상에 형성된다. 본 실시예에서, 산화물(205)이 형성된 이후, 수지 절연막(66)은 차폐막(204) 및 산화물(205)에 의해 형성되는 단계를 평탄화하도록 형성된다.

수지 절연막(66)은 충분한 두께(적어도 차폐막(204) 및 산화막(205)이 평탄화됨으로써 형성되는 단계까지)가 되도록 먼저 형성된다. 플라즈마에 의한 에칭, 기계 연마 또는 전자 연마에 의해 막 두께는 상기 단계의 높이와 실질적으로 동일한 수지 절연막이 되는 두께까지 감소한다.

그 이후, 픽셀 전극(67) 및 배향막(68)이 형성된다. 이어서, 스페이서(70)가 픽셀 전극의 접촉부(69) 위에 패턴화함으로써 형성된다.

본 실시예에 따라, 차폐막(204) 및 산화물(205)에 의해 형성이 평탄화되는 것뿐만 아니라, 픽셀 전극의 접촉부가 패턴화되기 때문에, 고도로 평탄화된 픽셀 전극이 형성될 수 있다. 결과적으로, 액정(71)에 형성된 전기장이 높아지므로, 액정의 잘못된 방위 현저히 감소될 수 있다. 따라서, 밝기 및 고도의 정밀한 화상 표시가 이루어질 수 있다.

본 실시예의 구조는 제 2 및 13 실시예에서 설명된 임의의 구조와도 자유롭게 결합할 수 있음을 알아야 한다.

#### 제 15 실시예

본 실시예에서, 픽셀부 외부의 스페이서의 배열은 도 21a 및 21b를 참조하여 설명된다.

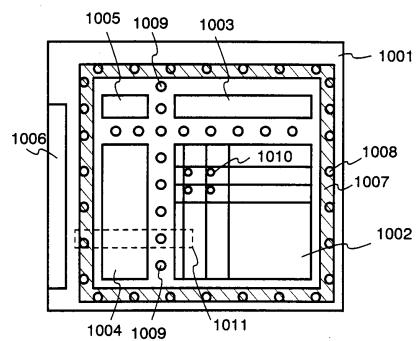

도 21a에 있어서, 제 1 실시예에서 설명된 처리에 따라 제조된 액티브 매트릭스 기판(1001)에서, 픽셀부(1002), 케이트측 구동 회로(1003), 소스측 구동 회로(1004), 신호 분배 회로(1005) 및 회부 접속단(I/O포트)(1006)이 형성된다.

도시되지는 않았지만, 대량 기판은 밀봉재(일반적으로 에폭시 수지 재료)(1007)를 통해 액티브 매트릭스 기판(1001)에 적층되며, 액정은 밀봉재(1007)에 의해 둘러싸인 영역 내에 캡슐에 둘러싸인다. 충전재로 불리는 벨 모양 또는 막대기 모양의 하드 스페이서(무기 재료로 이루어진 스페이서) 밀봉재(1007)에 미리 첨가되며, 밀봉재가 액티브 매트릭스 기판상에 인쇄될 때 동시에 증착된다.

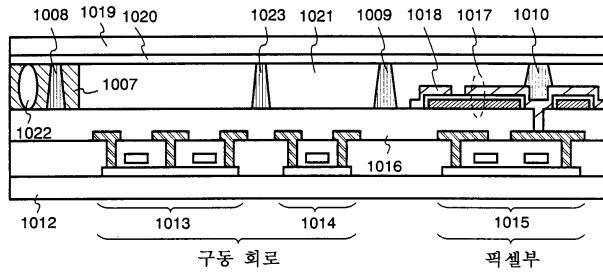

본 실시예에서, 스페이서(제 1 스페이서)(1008)는 밀봉재(1007)가 형성되는 부분에 관련하여 포토리소그래피를 실행함으로써 형성된다. 또한, 스페이서(제 2 스페이스)(1009)는 픽셀부(1002), 케이트측 구동 회로(1003), 소스측 구동 회로(1004), 신호 분배 회로(1005) 등 그 사이의 캡 내에 포토리소그래피를 사용하여 형성된다. 또한, 픽셀부에서, 스페이서(제 3 스페이서)(1010)는 도 12b 및 도 19에 설명된 위치에서 포토리소그래피에 의해 형성된다.

도 21b는 참조 번호(1011)로 기재된 영역의 확대한 개략도이다. 시프트 레지스터 회로들을 형성하는 CMOS 회로(1013), 챔플링 회로(1014) 및 픽셀부 내에 형성된 픽셀 TFT(1015) 등이 기판(1012) 상에 형성되며, 저장 커패시터(1017) 및 픽셀 전극(1018)은 중간 절연막(1016)을 통해 형성된다.

참조 번호(1019, 1020)는 대향 기판 및 대향 전극을 나타낸다. 액정(1021)은 대향 기판(1019)과 액티브 매트릭스 기판 사이에 스페이서를 통해 캡슐로 둘러 싸인다. 여기서, 밀봉재(1007)는 수지 재료로 이루어진 스페이서(제 1 스페이서)(1008), 무기재료로 이루어진 스페이서(충전재)(1022)를 포함한다.

수지 재료로 형성된 스페이서(제 2 스페이서)(1009)는 CMOS 회로(1013), 샘플링 회로(1014) 및 픽셀부로 이루어진 구동 회로 사이의 캡 내에 형성된다. 구동 회로에 있어서, 수지 재료로 이루어진 스페이서(제 4 스페이서)(1023)는 시프트 레지스터 회로와 샘플링 회로 사이의 캡 등의 장치 사이 또는 회로들 사이의 캡에 제공될 수 있다.

도 12b에서, 수지 재료로 이루어진 스페이서(제 3 스페이서)(1010)는 픽셀 TFT(1015)가 픽셀 전극(1018)과 접촉하는 접촉부 위에 형성된다. 수지 재료로 이루어진 스페이서는 저장 커패시터(1017) 위에 부가로 제공될 수 있다. 또는, 상기 접촉부 위에는 제외하고, 상기 저장 커패시터(1017) 위에만 수지 재료로 이루어진 스페이서를 제공하는 것이 가능해진다.

상술한 바와 같이, 수지 재료로 이루어진 스페이서가 포토리소그래피에 의해 형성되기 때문에, 이들의 배열은 설계시 자유롭게 결정될 수 있다. 본 실시예는 이러한 장점을 이용하여 이루어졌으며, TFT가 형성되지 않은 영역 내에 선택적으로 스페이서를 제공하는 특징이 있다.

도 21b의 스페이서(1008 내지 1010, 1023)는 동시에 사용되도록 필수적으로 요구되지 않으며, 이들 중 하나 또는 이들의 결합하여 자유롭게 결정하여 사용될 수 있다.

예를 들면, 액티브 매트릭스 액정 표시 장치에 있어서, 대각선의 길이는 1인치 이하이며, 어떤 경우에는, 패널 크기가 충분히 작기 때문에, 제 1 스페이서(1008)만이 밀봉재가 형성되는 장소에 제공되는 것으로 충분하다. 물론, 제 1 스페이서(1008)와 제 2 스페이서(1009)의 결합, 제 1 스페이서(1008)와 제 4 스페이서(1023) 또는 제 1 스페이서(1008), 제 2 스페이서(1009) 및 제 4 스페이서(1023)의 결합이 사용될 수 있다.

또는, 밀봉재가 형성되는 위치는 무기 재료로 이루어진 스페이서(1022)만이 될 수 있으며, 제 2 스페이서(1009)와 제 3 스페이서(1010)의 결합 또는 제 4 스페이서(1023)와 제 3 스페이서(1010)의 결합이 사용될 수 있다.

또는, 구동 회로에 인접하여 증착된 스페이서가 없을 수도 있으며, 제 1 스페이서(1008)과 제 3 스페이서(1010)의 결합이 사용될 수 있다.

또는, 제 1 스페이서(1008), 제 3 스페이서(1010)와 제 4 스페이서(1023)의 결합 또는 제 1 스페이서(1008), 제 2 스페이서(1009) 및 제 3 스페이서(1010)의 결합이 사용될 수 있다.

또한, 제 1 실시예의 픽셀부의 구조는 도 18a 및 18b를 참조하여 설명된 구조를 통해, 이것은 도 2a 및 2b를 참조하여 설명된 구조가 될 수 있다.

본 실시예의 구조는 제 1 내지 14 실시예에서 설명된 임의의 구조와 자유롭게 결합될 수 있다.

#### 제 16 실시예

본 발명은 또한, 층간 절연막이 반도체 기판을 사용하여 종래의 MOSFET 상에 형성되고, TFT가 그 위에 형성된 경우에도 적용될 수 있다. 즉, 3차원 구조의 반도체 장치가 실현되는 것도 또한 가능하다.

반사형의 액정 표시 장치를 제조하는 경우에는, SIMOX, Smart-CUT(SOTEC INC에 의해 등록된 상표), ELTRAN(CANON INC에 의해 등록된 상표) 등의 SOI 기판을 사용하는 것이 가능하다. 말할 것도 없이, 단결정 반도체 박막을 SOI 기법을 사용하여 투명 기판 위에 형성하는 기술이 설정되는 경우, 투과형 표시 장치를 위해 이들을 사용할 수 있다.

본 실시예의 구조는 제 1 내지 15 실시예의 임의의 구조와 자유롭게 결합할 수 있다.

#### 제 17 실시예

본 발명을 액티브 매트릭스 EL(electro luminescence) 표시 장치 또는 액티브 매트릭스 EC(electrochromic) 표시 장치에 적용하는 것이 가능하다. 액티브 매트릭스 EL 표시 장치상에서 본 발명을 실시하는 실례는 본 실시예의 도 22에 도시되어 있다.

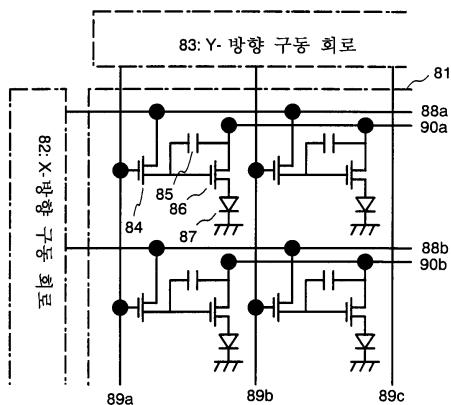

도 22는 액티브 매트릭스 EL 표시 장치의 회로도이다. 참조 번호(81)는 표시부분을 도시하며, X-방향(소스측) 구동 회로(82)와 Y-방향(게이트측) 구동 회로(83)는 그 주변부에 제공된다. 표시부(81)의 각각의 픽셀은 스위칭 TFT(84), 회로 제어 TFT(86) 및 유기의 EL 원소(87)를 포함한다. X-방향(소스측) 신호 선로(88a)(또는 88b) 및 Y-방향(게이트측) 신호 선로(89a)(또는 89b 또는 89c)는 스위칭 TFT(84)에 연결된다. 전원 공급 선로(90a, 90b)는 전류 제어 TFT(86)에 연결된다.

본 발명의 액티브 매트릭스 EL 표시 장치에 있어서, X 방향 구동 회로(82) 및 Y 방향 구동 회로(83)는 p-채널 TFT(701)와 n-채널 TFT(702, 703)를 결합함으로써 형성된다. 스위칭 TFT(84)는 도 8b의 n-채널 TFT(704)로부터 형성되며, 전류 제어 TFT(86)는 도 8c의 p-채널 TFT(701)로부터 형성된다. 커패시터(85)는 본 발명에 따른 도 8a의 저장 커패시터(572)를 사용하여 형성된다.

한편, 광이 TFT의 상부측을 향하여 조사되는 동작 모드를 갖는 EL 표시 장치의 경우, 픽셀 전극은 대향 전극으로부터 형성된다. 픽셀 구조에 의해 EL 표시 장치의 픽셀의 EL 원소를 배치함으로써, 띠 원소는 동작 모드의 경우 저장 커패시터 위에도 형성될 수 있는데, 이는 픽셀 전극 위의 모든 것이 효과적인 표시 영역으로서 사용될 수 있기 때문이다.

차폐막에 의한 단계가 존재하는 경우(이 경우, 전기장 차폐의 효과만을 가짐), 띠 원소는 또한 하나의 단계를 가지는데, 이 단계는 광 조사 방향이 분산되기 때문에 표시된 화상의 색 및 명암이 분해되는 원인이 될 수 있다. 본 발명은 또한, 이러한 환경에서도 해결하는 수단으로서 효과적이다.

본 실시예의 액티브 매트릭스 EL 표시 장치의 커패시터(85) 상에 수지 재료를 포함하는 충만 재료에 의해 펀 홀을 충전하는 것이 가능해 진다. 제 5 내지 11, 12(특히 도 16a 내지 17b의 제조 공정), 14 및 16 실시예의 임의의 구성과 본 실시예가 자유롭게 결합할 수 있다.

### 제 18 실시예

본 발명에 따라 제조된 액정 표시 장치에는 다양한 액정 재료를 사용하는 것이 가능하다. 이하, 이러한 재료의 예를 기재하였다. 상기 재료에는 TN 액정, PDL(polymer diffusion type liquid crystal) 및 스메틱 액정(smectic liquid crystal) 등이 있다. 특히 스메틱 액정, FLC(ferroelectric liquid crystal), AFLC(antiferroelectric liquid crystal) 및 FLC와 AFLC의 혼합물(antiferroelectric mixed liquid crystal) 등이 사용된다.

예를 들면, 1998년, Fure, H. 등에 의한, "Characteristics and Driving Scheme of Polymer-stabilized Monostable FLLCD Exhibition Fast Response Time and High Contrast Ratio 조소 Gray-scale Capability," SID; 1997년, Yoshida, T., 등의 "A Full-color Thresholdless Antiferroelectric LCD Exhibition Wide Viewing Angle with Fast Response Time,: SID 97 Digest 841; 1996년, S. Inui 등의 "Thresholdless antiferroelectricity in Liquid Crystals and its Application to Displays", 671-673, J. Mater. Chem. 6(4); 및 미국 특허 제 5,596,569등에 개시된 액정 재료가 사용될 수 있다.

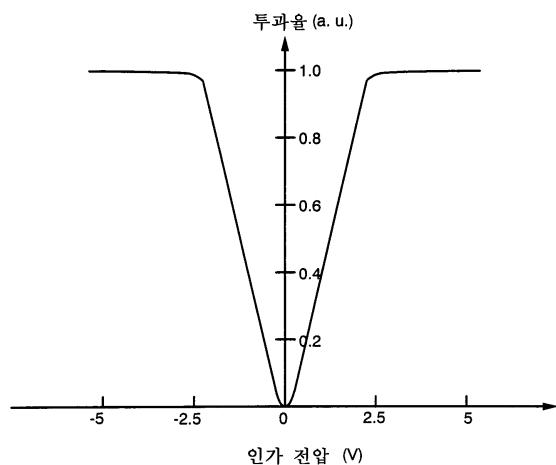

특히, 연속적으로 투과율을 전기장에 대해 미분하는 임계값(임계치가 없는 강유전성 LCD: 간략화된 TL-AFLC)을 가지지 않는 강유전성 액정 사이에 V형(또는 U형)의 전자 광학 응답 특성을 보여주는 몇 가지가 있고, ±2.5V 정도(셀 두께는 대략 1 내지 2mm)의 구동 전압을 갖는 것이 발견된다. V형 전자 광학 응답을 도시하는 임계치가 없는 강유전체의 혼합된 액정의 인가된 전압에 대응하여 광 투과율의 특성을 도시하는 예는 도 23에 도시되어 있다.

도 23에 도시된 그래프의 수직 축은 투과율(임의의 유닛에서)을 나타내며, 수평축은 인가된 전압을 나타낸다. 입사축 상의 편광판의 투과축은 액정 표시 장치의 마찰 방향과 거의 일치하게 설정되며, 임계치가 없는 강유전체의 혼합된 액정의 스메틱층에 평범한 방향과 거의 평행하게 설정됨을 알아야 한다. 또한, 외부축 상의 편광판의 투과축은 입사축 상의 편광판의 투과축에 거의 수직(교차된 나콜(nicol))으로 설정된다.

도 23에 도시된 바와 같이, 임계치가 없는 강유전체의 혼합된 액정 형태가 사용되는 경우에는 명확해지며, 낮은 전압 구동과 계조 표시(gray scaled display)를 갖는 것이 가능해진다.

따라서, 픽셀 회로용 전원 전압이 5 내지 8V로 요구되는 경우가 있고, 동일한 전원 공급 전압으로 구동 회로 및 픽셀 전류를 구동하는 가능성이 제안된다. 즉, 전체 액정 표시 장치는 낮은 전원을 소비하도록 할 수 있다.

또한, 강유전성 액정 및 반-강유전성(anti-ferroelectric) 액정은 TN 액정에 비해 고속응답을 가지는 장점이 있다. 본 발명에 사용된 극단적으로 고속동작하는 TFT를 실현하는 것이 가능하기 때문에, 강유전성 액정 및 반-강유전성 액정의 고속응답을 충분히 이용함으로써 고속 화상응답을 갖는 액정 표시 장치를 실현할 수 있다.

또한, 임계치가 없는 반-강유전성 혼합 액정은 일반적으로 큰 자발적 극성을 가지며, 액정 그 자체의 유전 계수가 높다. 그러므로 상대적으로 큰 저장 정전 용량은 액정 표시 장치의 임계치가 없는 반-강유전성의 혼합 액정을 사용하는 경우 픽셀에서 욕된다. 따라서, 작은 자발적 극성을 갖는 임계치가 없는 반-강유전성의 혼합 액정을 사용하는 것이 바람직하다.

또한, 퍼스널 컴퓨터용 표시에 본 발명의 액정 표시 장치를 사용하는 것은 효과적이다.

제 1 내지 16 실시예의 임의의 구성과 본 실시예의 구성을 자유롭게 조합하는 것도 가능하다.

### 제 19 실시예

본 발명의 전자-광학 장치는 전기 장비(전자 기계 및 전자 장치라 칭해짐)의 표시부로서 사용될 수 있다. 이하, 전자 장치의 실례를 나타내었다. 실례로는 비디오 카메라, 디지털 카메라, 프로젝터, 프로젝션 TV, 고글형 표시부(헤드 장착 표시부), 네비게이션 시스템, 음향 재생 장치, 노트북 형태의 퍼스널 컴퓨터, 게임기, 휴대용 정보 단말기(휴대용 컴퓨터, 휴대용 전화기 및 전자 노트북) 및 기록 매체와 병합된 화상 재생 장치 등이 있다. 이러한 실례는 도 24a 내지 26b에 도시되어 있다.

도 24a는 본체(2001), 음성 출력부(2002), 음성 입력부(2003), 표시부(2004), 동작 스위치(2005) 및 안테나(2006)를 포함하는 휴대용 전화기이다. 본 발명의 전기 광학 장치는 표시부(2004)용으로 사용될 수 있다.

도 24b는 본체(2101), 표시부(2102), 음성 입력부(2103), 동작 스위치(2104), 배터리(2105) 및 화상 수신부(2106)를 포함하는 비디오 카메라이다. 본 발명의 전기 광학 장치는 표시부(2102)용으로 사용될 수 있다.

도 24c는 본체(2201), 카메라부(2202), 화상 수신부(2203), 동작 스위치(2204) 및 표시부(2205)를 포함하는 휴대용 컴퓨터이다. 본 발명의 전기 광학 장치는 표시부(2302)용으로 사용될 수 있다.

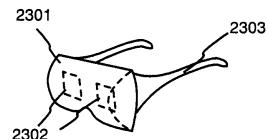

도 24d는 본체(2301), 표시부(2302) 및 아암부(2303; arm section)를 포함하는 고글형 표시부이다. 본 발명의 전자 광학 장치는 표시부(2302)용으로 사용될 수 있다.

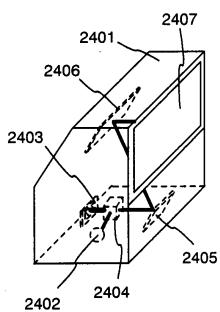

도 24e는 본체(2401), 광원(2402), 액정 표시 장치(2403), 편광 빔 스플리터(2404), 반사기(2405, 2406) 및 스크린(2407)을 포함하는 유사 프로젝터(near projector; 프로젝션 TV)이다. 본 발명은 액정 표시 장치(2502)용으로 사용될 수 있다.

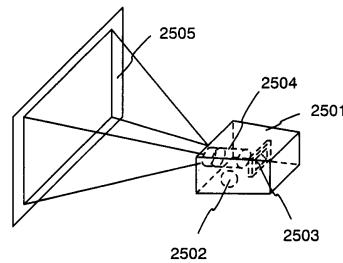

도 24f는 본체(2501), 광원(2502), 액정 표시 장치(2503), 광 시스템(2504) 및 스크린(2505)을 포함하는 프런트 프로젝터이다. 본 발명은 액정 표시 장치(2503)용으로 사용될 수 있다.

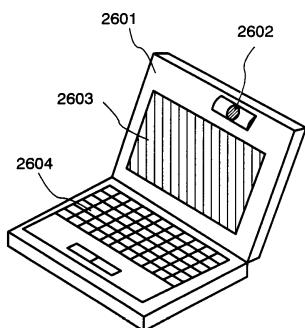

도 25a는 본체(2601), 화상 입력부(2602), 표시부(2603) 및 키보드(2604)를 포함하는 퍼스널 컴퓨터이다. 본 발명에 따른 전기 광학 장치는 표시부(2603)용으로 사용될 수 있다.

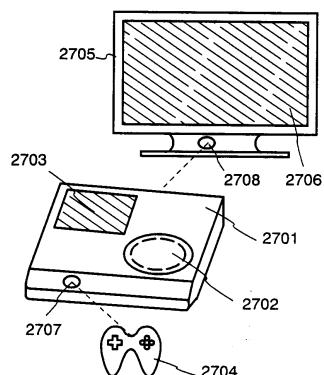

도 25b는 본체(2701), 기록 매체(2702), 표시부(2703) 및 제어기(2704)를 포함하는 전자 게임기이다. 전자 게임기로부터 출력된 음향과 화상은 커버(2705) 및 표시부를 포함하는 표시부에서 재생된다. 유선통신, 무선통신 또는 광통신은 제어기(2704) 와 본체(2701) 사이, 또는 전자 게임기와 표시 사이에서 통신 수단으로서 사용될 수 있다. 본 실시예에서, 이것은 센터부(2707, 2708)에서 적외선을 검출하기 위해 구성되었다. 본 발명의 전기 광학 장치는 표시부(2703, 2706)용으로 사용될 수 있다.

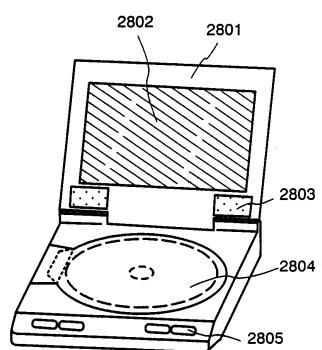

도 25c는 프로그램이 기록된 기록 매체(이하 기록 매체라 칭함)를 사용하는 플레이어로서, 본체(2801), 표시부(2802), 스파커부(2803), 기록 매체(2804) 및 동작 스위치(2805)를 포함한다. 음악 감상, 영화 감상, 게임 및 인터넷의 사용 등은 DVD(digital versatile disk), CD등의 기록매체를 사용하여 이 장치로 실행될 수 있다. 본 발명의 전기 광학 장치는 표시부(2802)용으로 사용될 수 있다.

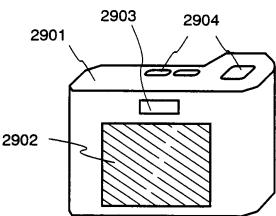

도 25d는 본체(2901), 표시부(2902), 뷰 파인더부(2903; view finder section), 동작 스위치(2904) 및 화상 수신부(도시되지 않음)를 포함하는 디지털 카메라이다. 본 발명의 전기 광학 장치는 표시부(2902)용으로 사용될 수 있다.

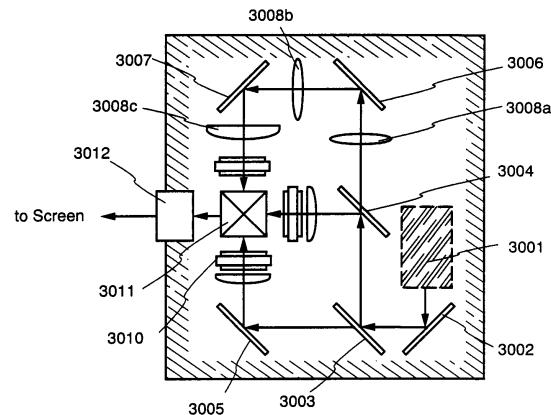

도 24e의 유사 프로젝터 및 도 24f의 프런트 프로젝터에 사용될 수 있는 광학 엔진에 대한 상세한 설명은 도 26a 및 26b에 도시되어 있다. 도 26a는 광학 엔진이며, 도 26b는 광학 엔진과 병합된 광학 광원 시스템이다.

도 26a에 도시된 광학 엔진은 광학 광원 시스템(26a), 미러들(3002,3005 내지 3007), 이색성 미러들(3003,3004; dichroic mirrors), 광학 렌즈(3008a 내지 3008b), 프리즘(3011), 액정 표시 장치(3010) 및 프로젝션 광학 시스템(3012)을 포함한다. 프로젝션 광학 시스템(3012)은 프로젝션 렌즈와 병합된 광학 시스템이다. 3개의 액정 표시 장치(3010)를 사용하는 3-플레이트 형의 예가 도시된 본 실시예를 통해, 그것은 단일 플레이트형이 될 수 있다. 광학 렌즈, 편광 기능을 갖는 막, 위상차를 조절하는 막 또는 IR막 등이 도 26a에 화살표에 의해 도시된 광학 경로에 제공될 수 있다.

도 26b에 도시된 바와 같이, 광학 광원 시스템(3001)은 광원(3013,3014), 합성 프리즘(3015), 시준 렌즈(3016,3020), 렌즈 배열(3017,3018) 및 극성 반전 요소(3015)를 포함한다. 도 26b에 도시된 광학 광원 시스템이 2개의 광원을 사용함으로써, 그것은 1 또는 3 이상이 될 수 있다. 광학 렌즈, 편광 기능을 갖는 막, 위상차를 조절하는 막, 또는 IF막 등이 광학 광원 시스템의 광학 경로 내에 제공될 수 있다.

상술한 바와 같이, 본 발명의 액티브 매트릭스 장치의 적용범위는 매우 광범위하며, 다양한 분야의 전자 장치에 적용될 수 있다. 또한, 본 발명의 전기 장비들은 필요에 따라, 제 1 내지 18 실시예의 구성과 결합하여 실현될 수 있다.

### 발명의 효과

본 발명은 다음과 같은 장점을 갖는다:

- 1) 저장 커패시터의 유전체 내 편 훌이 충전될 수 있고,

- 2) 배향막의 평탄화(픽셀 전극의 평탄화)가 개선된다. 1)은 저장 커패시터 내의 전극 간에 단락을 방지할 수 있고, 2)는 액정의 잘못된 방위를 방지할 수 있다.

또한, 탄성 수지 재료로 이루어진 스페이서를 사용함으로써, 장치상의 부하가 감소되어, 장치의 파손 등으로 인한 수율 및 신뢰성의 저하를 방지한다. 이러한 방식에서, 액정 표시 장치에 의해 표시되는 전기 광학 장치의 신뢰성 및 동작 성능이 개선된다.

따라서, 표시로서 전기 광학 장치 등을 갖는 전기 장치의 신뢰성 및 동작 성능이 개선될 수 있다.

### 도면의 간단한 설명

도 1은 커패시터의 구조를 도시하는 도면.

도 2a 및 2b는 액정 표시 장치의 픽셀 구조를 도시하는 도면.

도 3은 본 발명에 따른 개선 전의 커패시터의 구조를 도시하는 도면.

도 4는 본 발명에 따른 개선 전의 액정 표시 장치의 픽셀 구조를 도시하는 도면.

도 5의 (a) 내지 (f)는 픽셀부 및 구동 회로의 제조 단계를 도시하는 도면.

도 6의 (a) 내지 (f)는 픽셀부 및 구동 회로의 제조 단계를 도시하는 도면.

도 7의 (a) 내지 (d)는 픽셀부 및 구동 회로의 제조 단계를 도시하는 도면.

도 8a 및 8b는 픽셀부 및 구동 회로의 제조 단계를 도시하는 도면.

도 9는 n-채널 TFT의 LDD 구조를 도시하는 도면.

도 10은 액티브 매트릭스 액정 표시 장치를 도시하는 투시도.

도 11은 액티브 매트릭스 액정 표시 장치를 도시하는 회로블록도.

도 12a 및 12b는 픽셀 구조를 도시하는 평면도.

도 13은 액티브 매트릭스 액정 표시 장치를 도시하는 단면도.

도 14a 및 14b는 픽셀부와 전원 라인 사이의 접속 구조 및 차폐막을 도시하는 단면도.

도 15a 및 15b는 액정 표시 장치의 픽셀 구조를 도시하는 도면.

도 16a 및 16b는 액정 표시 장치의 픽셀 구조의 제조 단계를 도시하는 도면.

도 17a 및 17b는 액정 표시 장치의 픽셀 구조의 제조 단계를 도시하는 도면.

도 18a 및 18v는 액정 표시 장치의 픽셀 구조를 도시하는 도면.

도 19는 픽셀 구조를 도시하는 평면도.

도 20은 액정 표시 장치의 픽셀 구조를 도시하는 도면.

도 21a 및 21b는 스페이서가 형성된 부분을 도시하는 도면.

도 22는 액티브 매트릭스 EL 표시 장치의 구조를 도시하는 도면.

도 23은 임계치가 없는 반-강유전체 혼합의 액정의 광투과 특성을 도시하는 그래프.

도 24a 내지 24f는 전기 장비의 예를 도시하는 도면.

도 25a 내지 25d는 전기 장비의 다른 예를 도시하는 도면.

도 26a 내지 26b는 광학 엔진의 구조를 도시하는 도면.

\* 도면의 주요부분에 대한 부호의 설명 \*

102: 제 1 도전막 103: 유전체

104: 제 2 도전막 106: 펀 홀

107: 충전재 409: 스페이서

501: 기판 505 내지 508: 액티브층

도면

도면1

도면2a

도면2b

도면3

도면4

도면5

## 도면6

도면7

도면8a

도면8b

도면9

도면10

도면11

도면12a

도면12b

도면13

도면14a

도면14b

도면15a

도면15b

도면16a

도면16b

도면17a

도면17b

도면18a

도면18b

도면19

도면20

도면21a

도면21b

도면22

도면23

도면24a

도면24b

도면24c

도면24d

도면24e

도면24f

도면25a

도면25b

도면25c

도면25d

도면26a

도면26b