## (19) 대한민국특허청(KR)

## (12) 특허공보(B1)

|                                           |                             |

|-------------------------------------------|-----------------------------|

| (51) Int. Cl. <sup>6</sup><br>H01L 21/027 | (45) 공고일자<br>1996년 10월 23일  |

| (21) 출원번호<br>1993-0021405                 | (11) 공고번호<br>특 1996-0014963 |

| (22) 출원일자<br>1993년 10월 15일                | (24) 등록일자<br>1996년 10월 23일  |

|                                           | (65) 공개번호<br>특 1995-0012591 |

|                                           | (43) 공개일자<br>1995년 05월 16일  |

(73) 특허권자 현대전자산업주식회사 김주용

경기도 이천군 부발읍 아미리 산 136-1

(72) 발명자 배상만

서울특별시 송파구 방이동 111-13호 대승빌라 301호

(74) 대리인 이권희, 서종완, 이정훈

**심사관 : 김승조 (책자공보 제4707호)****(54) 반도체 장치의 제조 방법****요약**

내용 없음.

**대표도****도1****명세서**

[발명의 명칭]

반도체 장치의 제조 방법

[도면의 간단한 설명]

제1a~1c도는 종래 감광막 패턴 제조 공정도.

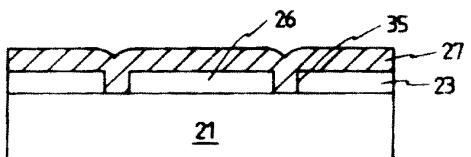

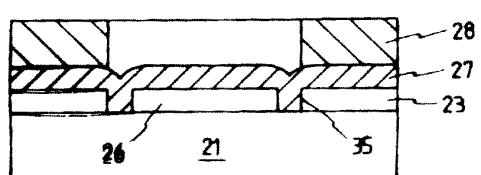

제2a~2c도는 본 발명에 따른 감광막 패턴 제조 공정도.

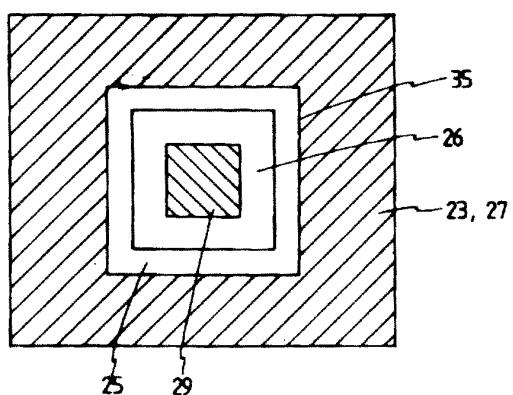

\* 도면의 주요부분에 대한 부호의 설명

|                      |                |

|----------------------|----------------|

| 11, 21, 41 : 반도체 웨이퍼 | 13, 23 : 제1잔류층 |

| 15, 25, 45 : 외부 박스   | 17, 27 : 제2잔류층 |

| 19, 29, 49 : 내부박스    | 22 : 제1감광막     |

| 24 : 제1노광 마스크        | 26 : 보조 패턴     |

| 28 : 제2감광막           | 30 : 제2노광 마스크  |

| 32 : 제3잔류층           | 33 : 제3감광막     |

| 34 : 제3노광 마스크        | 35 : 흙         |

[발명의 상세한 설명]

본 발명은 반도체 장치의 제조 방법에 관한 것으로서, 특히 패턴의 중첩 정밀도 측정에서 마크가 되는 단차 부분이 중복 적층에 의해 측정이 어려워지는 것을 방지하기 위하여 패턴의 중첩 정밀도(pattern overlay) 측정 마크의 하부에 보조패턴을 형성하여 중첩 정밀도 측정 마크의 측정이 용이한 반도체 장치의 제조 방법에 관한 것이다.

일반적으로 반도체 장치는 스텝퍼에 의해 다수개의 노광 마스크가 중첩 사용되는 복잡한 공정을 거치게 된다. 상기 반도체 장치는 제조 공정에 사용되는 스텝 앤 리비트(step and repeat) 방식의 축소 노광 장비인 스텝퍼(stripper)는, 스텝이지가 X-Y방향으로 움직이며 반복적으로 이동 정렬하여 노광하는 장치이다. 상기 스텝이지의 기계적 움직임에 의해 정렬오차가 발생되고, 정렬오차가 허용 범위를 초과하면 소자의 불량이 발생된다. 상기 오정렬에 따른 중첩 정밀도의 조정범위는 소자의 디자인 룰(design rule)에 따르며, 통상 디자인 룰의 20~30% 정도이다.

이때 단계별로 사용되는 노광 마스크의 정렬은 특정 형상의 측정 마크를 기준으로 이루어지고, 이때 사용되는 측정 마크로는 정렬 마크(alignment mark)와 중첩 정밀도 측정 마크가 있다.

상기 측정 마크는 다른 노광 마스크간의 정렬(layer to layer alignment; 이하 '총간 정렬'이라 칭함)이

나, 하나의 노광 마스크에 대한 다이 간 정렬에 사용된다. 상기 정렬 마크는 노광 공정 전에 스테퍼의 인식 장치가 인식하는 것이며, 상기 중첩 정밀도 측정 마크는 두개의 패턴을 형성한 후, 별도의 중첩 정밀도 측정 장비가 인식하여 중첩 정밀도를 보정하는데 필요한 마크이다.

여기서 다이라 험은 한번의 노광 공정으로 형성되는 영역 전체를 의미하며, 하나의 다이내에 다수개의 반도체 칩이 포함될 수도 있다.

상기 정렬마크와 중첩 정밀도 측정 마크는 웨이퍼에서 반도체 칩이 형성되지 않는 부분인 스크라이브 라인(scribe line) 상에 형성되며, 상기 측정 마크를 이용한 오정렬 정도를 측정하는 방법으로는 베어니어(venier) 정렬 마크를 이용한 시각 점검 방법과, 박스 인 박스(box in box)나 바아 인 바아(bar in bar) 정렬 마크를 이용한 자동 점검 방법이 있다.

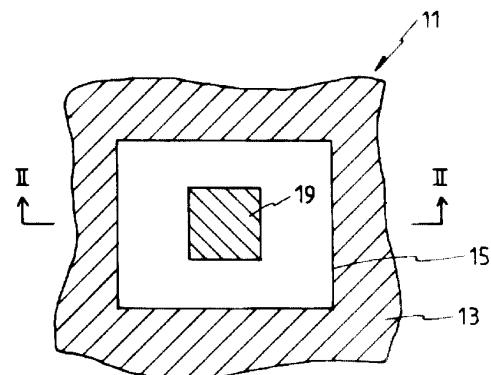

종래 중첩 정밀도 측정 마크는 박스 인 박스 방식은 제1도 및 제2도에 도시되어 있는 바와 같이, 전체적으로 반도체 웨이퍼(11)의 스크라이브 라인 상에 형성되어 있다.

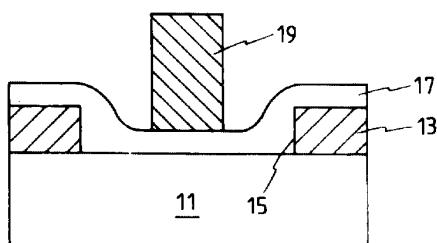

먼저, 반도체 웨이퍼(11) 상에 소정의 물질, 예를들어 폴리 실리콘으로 된 제1잔류층(13)이 소정의 크기, 예를들어 일변이  $20\mu m$ 인 정사각 형상으로 제거되어 외부 박스(15)가 형성되어 있으며, 상기 구조의 전표면에 상측 도포물질, 예를들어 금속층으로된 제2잔류층(17)이 도포되어 있다. 또한 상기 외부 박스(15)의 내측에 감광막 패턴으로된 소정 크기, 예를들어 일변의 길이가  $10\mu m$ 인 정사각 형상의 내부 박스(19)가 형성되어 있다.

상기와 같이 외부 박스와 내부 박스로 구성되는 중첩 정밀도 측정 마크를 이용한 측정 방법은 측정 장비로 외부 박스와 내부 박스의 경계선에서 각 변간의 거리를 측정하여, 각 변간의 오차를 계산함으로서, 스테이지의 X-Y축 오정렬을 보정한다.

그러나 상기에서 외부 박스의 경계선이 되는 단차 부분은 후속 도포층인 제2잔류층의 단차 피복에 의해 완만해져서 측정이 어려워지므로 반복 측정하거나, 상기 외부 박스 상에 도포된 물질을 식각하여 측정하여야 한다. 따라서 반도체 장치의 제조 공정이 복잡해지고, 상기 식각 공정시 결함이 발생되어 신뢰성을 떨어뜨리는 등의 문제점이 있다.

본 발명은 상기와 같은 문제점을 해결하기 위한 것으로서, 본 발명의 목적은 중첩 정밀도 측정 마크에서 외부 박스와 내부 박스의 사이 공간에 별도의 보조패턴을 형성하여 후속 도포층의 피복에 의해 외부 박스 경계선이 불확실해지는 것을 방지하여 제조 공정이 간단하고, 신뢰성을 향상시킬 수 있는 반도체 장치의 제조 방법을 제공함에 있다.

상기와 같은 목적을 달성하기 위한 본 발명에 따른 반도체 장치 제조 방법의 특징은, 소정 형상의 아웃박스가 형성되어 있는 잔류층의 하부에 선행 공정에서 사용된 물질로 상기 아웃박스와 같은 경계선을 갖고 내부 박스 보다는 큰 보조패턴을 별도로 형성하여 중첩 정밀도 측정을 용이하게 함에 있다.

이하, 첨부 도면을 참조하여 본 발명에 따른 반도체 장치의 제조 방법을 상세히 설명한다.

본 발명에 따른 중첩 정밀도 측정 마크의 제조 방법을 제3도를 참조하여 살펴보면 다음과 같다.

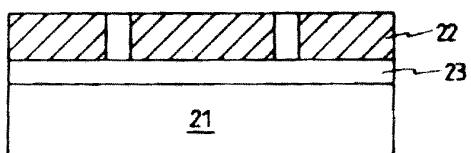

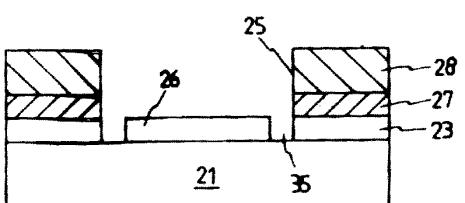

먼저, 반도체 웨이퍼(21) 상에 보조 패턴을 형성하기 위하여 소정 물질, 예를들어 인터 폴리 산화막으로 된 제1잔류층(23)을 선행 공정에서 측정 마크를 형성할 부분에 남겨둔다. 그다음 상기 제1잔류층(23) 상에 포지티브 감광액으로 제1감광막(22)을 형성하고, 보조 패턴으로 예정된 부분인 사각 띠 형상의 노광을 방지하는 제1노광 마스크(24)를 사용하여 노광한다. 이때 상기 제1노광 마스크(24)는 외부 박스의 경계선과 보조 패턴의 경계선 사이의 소정 크기, 예를들어 외측이  $20\mu m$ , 내측이  $17\sim19\mu m$ 인 정사각 틀체 형상으로 형성된다(제3a도 참조).

그후, 상기 제1감광막(22)의 노광된 부분을 제거하여 제1감광막(22)패턴을 형성하고, 상기 제1감광막(26) 패턴에 의해 노출되어 있는 제1잔류층(23)을 통상의 식각 방법으로 제거한 후, 상기 제1감광막(24)을 제거한다. 이때 상기 제1잔류층(23)의 타족과 분리된 부분이 소정 크기, 예를들어 일변이  $17\sim19\mu m$ 인 정사각 형상의 보조 패턴(26)이 되며, 상기 남아있는 제1잔류층(23)과 상기 보조 패턴(26)과의 사이에는 사각띠 형상의 흄(35)에 의해 반도체 웨이퍼(21)가 노출되어 있다. 그다음 상기 구조의 전표면에 소정의 물질, 예를들어 폴리실리콘으로 된 제2잔류층(27)을 도포한다(제3b도 참조).

그다음 상기 제2잔류층(27) 상에 포지티브 제2감광막(28)을 도포하고, 상기 보조 패턴(26)과 분리되어 있는 제1잔류층(23)의 에지 부분 즉 외측 박스(25)의 경계선의 내측을 노광시키는 제2노광 마스크(30)를 사용하여 노광한다(제3c도 참조).

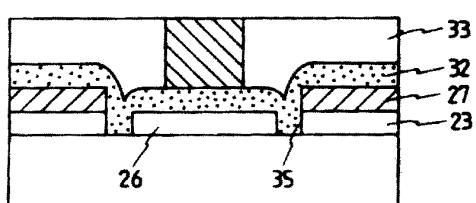

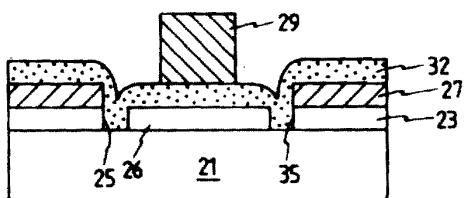

그후, 상기 제2감광막(28)의 노광된 부분을 제거하여 제2감광막(28) 패턴을 형성한 후, 상기 제2감광막(28) 패턴에 의해 노출되어 있는 제2잔류층(27)을 제거하여 상기 보조 패턴(26)과 그 외부의 사각 띠 형상의 반도체 기판(21)과 보조 패턴(26)을 노출시키는 외부 박스(25)를 소정 크기, 예를들어 일변이  $20\mu m$ 인 정사각 형상으로 형성한다(제3d도 참조).

그다음 상기 제2감광막(28) 패턴을 제거한 후, 상기 구조의 전표면에 소정 물질, 예를들어 금속층으로된 제3잔류층(32)과 포지티브 제3감광막(33)을 순차적으로 형성한 후, 상기 외부 박스(25)의 내측 중앙 부분을 비노광시키는 제3노광 마스크(34)를 사용하여 노광한다(제3e도 참조).

그후, 상기 제3감광막(33)의 노광된 부분을 제거하여 제3감광막(33) 패턴으로된 소정 크기, 예를들어, 일변이  $10\mu m$ 인 내부 박스(29)를 형성한다. 상기와 같은 중첩 정밀도 측정 마크는 외부 박스(25)의 내측에 요부가 형성되므로 반도체 장치의 제조공정중에서 리프로우되는 물질이 흘러드는 완충대의 역할도 수행한다(제3f도 참조).

상기와 같이 형성된 중첩 정밀도 측정 마크는 제4도에 도시되어 있는 바와같은 평면배치를 갖는데, 상기 보조 패턴(26)과 외부 박스(25)의 사이에 소정폭, 예를들어  $1\sim3\mu m$  폭의 정사각형 띠 형상의 흄(35)이 선명하게 나타나며, 상기 흄(35)의 내부에 내부 박스(29)가 형성되어 있다.

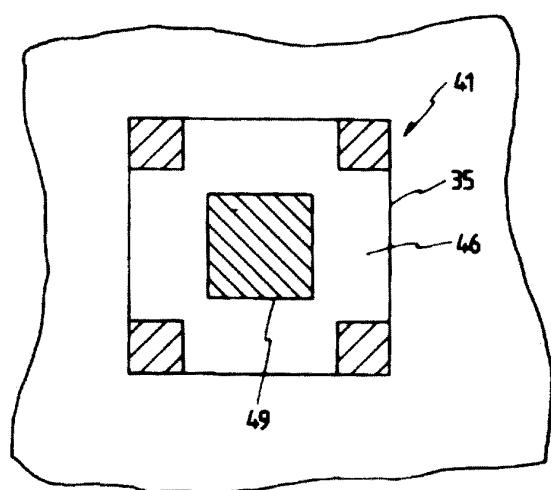

본 발명 사상에 따른 중첩 정밀도 측정 마크는 상기와 같은 정사각 형상의 보조 패턴을 형성하는 방법 이외에도, 제5도에 도시되어 있는 바와 같은 다른 실시예로도 실현할 수 있다.

제5도는 본 발명의 다른 실시예에 따른 중첩 정밀도 측정 마크의 레이아웃도이다.

반도체 웨이퍼(41) 상에 소정 형상, 예를들어 일변이  $20\mu\text{m}$ 인 정사각 형상의 외부 박스(45)가 형성되어 있으며, 상기 외부 박스(45)의 내측에 소정 형상, 예를들어 폭이  $15\mu\text{m}$ 인 십자(+) 형상의 모서리 강조형 보조 패턴(46)이 형성되어 있고, 상기 보조 패턴(46)의 중앙에 소정 형상, 예를들어 일변의 길이가  $10\mu\text{m}$ 인 정사각 형상의 내부 박스(49)가 형성되어 있다.

도시되어 있지는 않으나, 상기에서 감광막 패턴을 네가티브 감광막을 사용할 경우에는 상기 노광 마스크의 패턴을 반대로 하여 동일한 방법으로 중첩 정밀도 측정 마크를 형성할 수 있다.

이상에서 설명한 바와 같이, 본 발명에 따른 반도체 장치의 중첩 정밀도 측정 마크 제조 방법은, 외부 박스와 내부 박스로 구성되는 중첩 정밀도 측정 마크에서 내부 박스와 외부 박스의 경계선의 사이에 단차를 증가시키기 위한 별도의 보조 패턴을 상기 내, 외부 박스의 하부에 선행 공정에서 도포되는 물질의 잔류층으로 형성하였으므로, 상기 보조 패턴에 의해 외부 및 내부 박스의 사이에 단차를 증가시키는 소정형상의 흙이 형성되어 외부 및 내부 박스간의 중첩 정밀도 측정을 용이하게 한다. 따라서 반도체 장치의 제조 공정이 간단해지고, 신뢰성이 향상되는 효과가 있다.

### (57) 청구의 범위

#### 청구항 1

노광 공정 후 선행 공정에서 형성된 패턴과의 중첩 정밀도 측정에 사용되는 중첩 정밀도 측정 마크를 반도체 웨이퍼 상에 형성하는 반도체 장치의 제조 방법에 있어서, 반도체 웨이퍼 상에 중첩 정밀도 측정 마크로 예정된 부분에 측정하고자 하는 두개 층을 형성하기 전의 선행 공정에서 제1잔류층을 형성하는 공정과, 상기 제1잔류층을 사진 식각하여 상기 반도체 웨이퍼를 노출시키는 소정 형상의 보조 패턴을 형성하는 공정과, 상기 구조의 전표면에 제2잔류층을 형성하는 공정과, 상기 제2잔류층을 사진 식각하여 상기 보조 패턴을 내부에 포함하며, 상기 보조 패턴과 반도체 웨이퍼를 노출시키는 사각 형상의 외부 박스를 형성하는 공정과, 상기 구조의 전표면에 제3잔류층을 형성하는 공정과, 상기 잔류층 표면에, 상기 보조 패턴의 내부에 포함되는 사각형상의 내부 박스를 감광막으로 형성하는 공정을 포함하는 반도체 장치의 제조방법.

#### 청구항 2

제1항에 있어서, 상기 보조 패턴이 정사각 형상 또는 +자 형상으로 형성되는 것을 특징으로 하는 반도체 장치의 제조 방법.

#### 도면

##### 도면1

##### 도면2

도면3a

도면3b

도면3c

도면3d

도면3e

도면3f

도면4

도면5