(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5484372号

(P5484372)

(45) 発行日 平成26年5月7日(2014.5.7)

(24) 登録日 平成26年2月28日(2014.2.28)

(51) Int.Cl.

H01L 25/07 (2006.01)

H01L 25/18 (2006.01)

F 1

H01L 25/04

C

請求項の数 5 (全 9 頁)

(21) 出願番号 特願2011-28184 (P2011-28184)

(22) 出願日 平成23年2月14日 (2011.2.14)

(65) 公開番号 特開2012-169397 (P2012-169397A)

(43) 公開日 平成24年9月6日 (2012.9.6)

審査請求日 平成25年6月13日 (2013.6.13)

(73) 特許権者 000006013

三菱電機株式会社

東京都千代田区丸の内二丁目7番3号

(74) 代理人 100088672

弁理士 吉竹 英俊

(74) 代理人 100088845

弁理士 有田 貴弘

(72) 発明者 加藤 正博

東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内

(72) 発明者 中川 信也

東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内

審査官 越本 秀幸

最終頁に続く

(54) 【発明の名称】半導体モジュール

## (57) 【特許請求の範囲】

## 【請求項 1】

カソード同士が接続した第1および第2ダイオード並びにアノード同士が接続した第3および第4ダイオードを有し、前記第1および第3ダイオードが直列接続し、前記第2および第4ダイオードが直列接続して成るダイオードブリッジと、

前記第1ダイオードと第3ダイオードとの接続ノードである第1ノードに接続した第1スイッチング素子と、

前記第2ダイオードと第4ダイオードとの接続ノードである第2ノードに接続した第2スイッチング素子とを備え、

前記第1および第2ノードに交流電源が印加され、前記第1および第2スイッチング素子により前記交流電源の力率改善の動作が行われる力率改善回路を含む半導体モジュールであって、

前記第1および第2ダイオードはワイドバンドギャップ半導体を用いて形成したショットキーバリアダイオードであり、

前記第3および第4ダイオード、並びに前記第1および第2スイッチング素子はシリコンを用いて形成したダイオード並びにスイッチング素子であることを特徴とする半導体モジュール。

## 【請求項 2】

請求項1記載の半導体モジュールであって、

前記第1および第2ダイオードを搭載した第1リードフレームと、

10

20

前記第3ダイオードおよび第1スイッチング素子を搭載した第2リードフレームと、

前記第4ダイオードおよび第2スイッチング素子を搭載した第3リードフレームと、

前記第1～第4ダイオード、第1および第2スイッチング素子並びに前記第1～第3リードフレームを保持すると共に、当該半導体モジュールの筐体を構成するモールド樹脂とをさらに備え、

前記第1～第3リードフレームの一部は、外部接続端子として、前記モールド樹脂から成る前記筐体の一側面から突出しており、

前記筐体の内部において、前記第1および第2ダイオードは、前記第3および第4ダイオード並びに前記第1および第2スイッチング素子よりも前記一側面の近くに配設されている

10

ことを特徴とする半導体モジュール。

【請求項3】

請求項2記載の半導体モジュールであって、

前記筐体の内部において、前記第1リードフレームは、前記第1および第2ダイオードの搭載面の垂直方向に屈曲していない

ことを特徴とする半導体モジュール。

【請求項4】

請求項2または請求項3記載の半導体モジュールであって、

前記筐体には当該筐体を貫通する貫通孔が形成されており、

前記第1および第2ダイオードの少なくとも片方は、平面視で前記筐体の前記貫通孔と前記一側面との間に配設されている

ことを特徴とする半導体モジュール。

20

【請求項5】

請求項1から請求項4のいずれか一項記載の半導体モジュールであって、

前記第1および第2スイッチング素子を駆動するドライバICをさらに備える

ことを特徴とする半導体モジュール。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は力率改善 (Power Factor Correction; PFC) 回路を含む半導体モジュールの構造に関するものである。

30

【背景技術】

【0002】

従来、電力制御用の半導体モジュール(パワーモジュール)に、シリコン(Si)を用いて形成したPiN(P-intrinsic-N)ダイオードを用いた場合、少数キャリアの蓄積効果によるリカバリー電流が発生するため、パワーモジュールの損失が増大する要因の1つとなる。一方、ショットキーバリアダイオードではこれを著しく低減できる。そのため従来のパワーモジュールでは、多くの場合、Siを用いて形成したショットキーバリアダイオード(SBD)が用いられていた。

【0003】

40

また、高耐電圧、低損失および高耐熱を実現できる次世代のスイッチング素子として、ワイドバンドギャップ半導体を用いた半導体素子が有望視されている。下記の特許文献1～5には、代表的なワイドバンドギャップ半導体である炭化珪素(SiC)を用いて形成した半導体デバイス(SiCデバイス)をパワーモジュールへ適用した例が示されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開平10-93015号公報

【特許文献2】特開平11-233712号公報

50

【特許文献3】特表平11-510000号公報

【特許文献4】特開2003-18862号公報

【特許文献5】特開2006-149195号公報

#### 【発明の概要】

##### 【発明が解決しようとする課題】

##### 【0005】

ダイオードを備えるパワーモジュールの一つとして、整流用のダイオードブリッジと力率改善（Power Factor Correction；PFC）回路とを備えるPFCモジュールが知られている。従来のPFCモジュールのダイオードブリッジには、Siのショットキーバリアダイオードが用いられていた。しかし、Siのショットキーバリアダイオードは、耐電圧を数百V以上にすると順方向の電圧降下（順電圧（VF））が著しく高くなるため、高電圧制御用のパワーモジュールにおいてはPINダイオードの場合よりも損失の増大を招く場合もある。10

##### 【0006】

一方、SiCを用いて形成したショットキーバリアダイオードは、耐電圧を数百V以上にしても順電圧を低く維持できる。従って、パワーモジュールにSiCのショットキーバリアダイオードを適用することにより、低損失で且つリカバリー特性に優れたパワーモジュールを実現できる。しかしSiCデバイスはSiデバイスに比べて高価なため、パワーモジュールをSiCデバイス化すると製造コストの増大を伴う。20

##### 【0007】

本発明は以上のような課題を解決するためになされたものであり、リカバリー特性に優れ、低損失で低コストなPFCモジュールを提供することを目的とする。

##### 【課題を解決するための手段】

##### 【0008】

本発明に係る半導体モジュールは、カソード同士が接続した第1および第2ダイオード並びにアノード同士が接続した第3および第4ダイオードを有し、前記第1および第3ダイオードが直列接続し、前記第2および第4ダイオードが直列接続して成るダイオードブリッジと、前記第1ダイオードと第3ダイオードとの接続ノードである第1ノードに接続した第1スイッチング素子と、前記第2ダイオードと第4ダイオードとの接続ノードである第2ノードに接続した第2スイッチング素子とを備え、前記第1および第2ノードに交流電源が印加され、前記第1および第2スイッチング素子により前記交流電源の力率改善の動作が行われる力率改善回路を含む半導体モジュールであって、前記第1および第2ダイオードはワイドバンドギャップ半導体を用いて形成したショットキーバリアダイオードであり、前記第3および第4ダイオード、並びに前記第1および第2スイッチング素子はシリコンを用いて形成したダイオード並びにスイッチング素子であるものである。30

##### 【発明の効果】

##### 【0009】

ダイオードブリッジの上アームである第1および第2ダイオードは、整流素子として機能する他、第1および第2スイッチング素子によるPFC動作時の還流ダイオードとしても機能する。特にPFC制御では第1および第2スイッチング素子は高周波動作するため、第1および第2ダイオードにおける還流動作時のリカバリー損失はPFCモジュール全体の損失に大きく寄与する。第1および第2ダイオードを、低損失で且つリカバリー特性に優れたSiCデバイスとすることにより、PFCモジュールの損失を大きく低減させることができる。またパワーチップの全てではなく、第1および第2ダイオードのみをSiCデバイス化するに留めているため、コストの上昇も抑制できる。さらにSiCデバイスは低損失であり小型化が可能なため、PFCモジュールの小型化にも寄与できる。40

##### 【図面の簡単な説明】

##### 【0010】

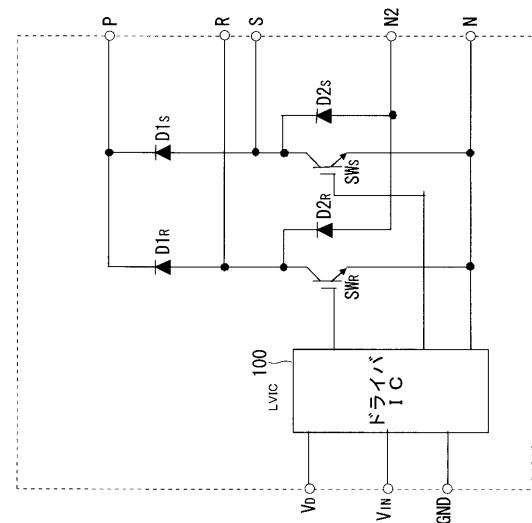

【図1】本発明に係るPFCモジュールの回路図である。

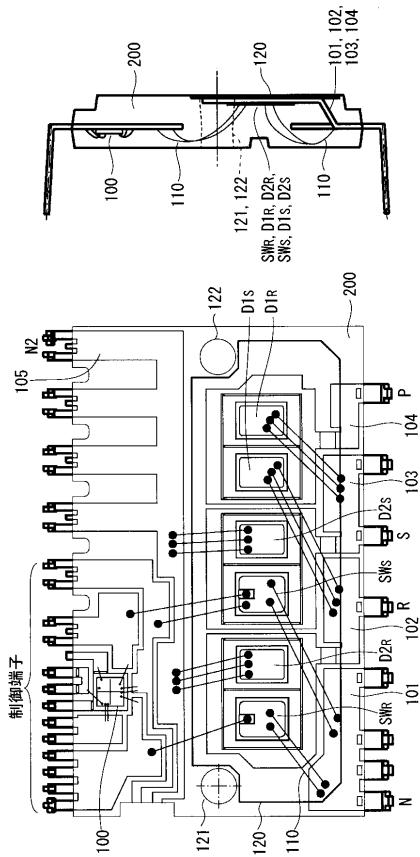

【図2】従来のPFCモジュールの構成図である。

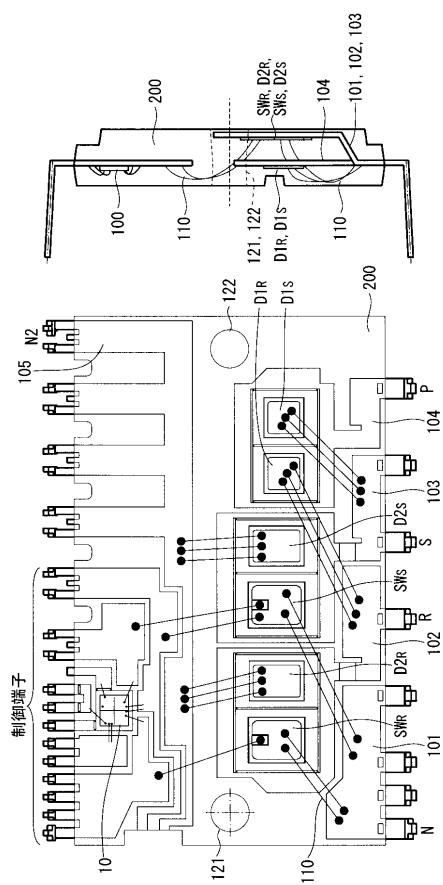

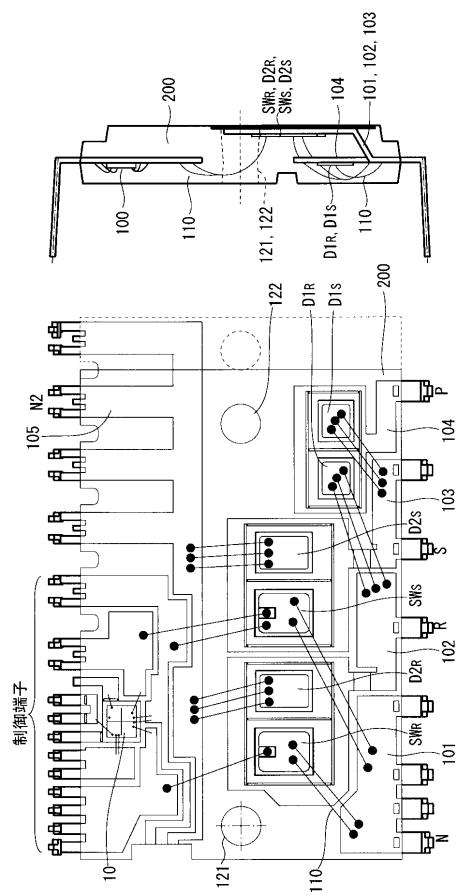

【図3】実施の形態1に係るPFCモジュールの構成図である。

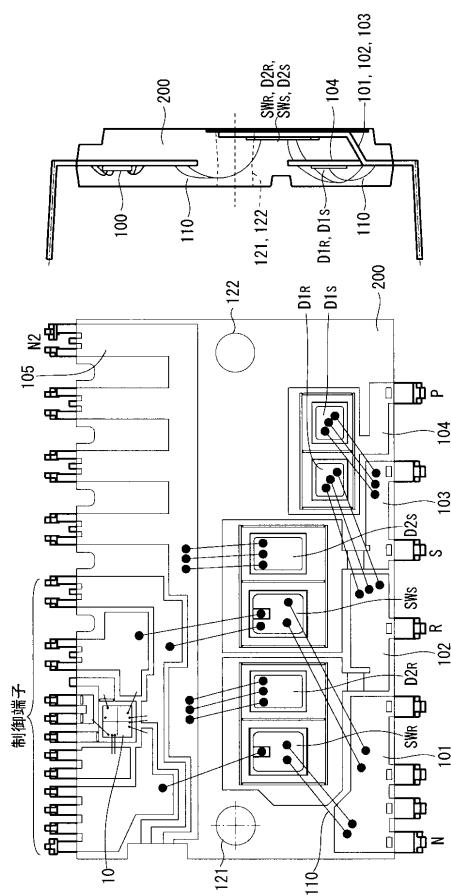

【図4】実施の形態2に係るPFCモジュールの構成図である。

【図5】実施の形態3に係るPFCモジュールの構成図である。

【発明を実施するための形態】

【0011】

<実施の形態1>

図1は、本発明に係る半導体モジュールであるPFCモジュールの回路図である。同図の如く当該PFCモジュールは、第1～第4ダイオードD<sub>1R</sub>, D<sub>1S</sub>, D<sub>2R</sub>, D<sub>2S</sub>から成るダイオードブリッジと、力率改善用の第1および第2スイッチング素子SW<sub>R</sub>, SW<sub>S</sub>と、当該第1および第2スイッチング素子SW<sub>R</sub>, SW<sub>S</sub>を制御するドライバIC100を備えている。

10

【0012】

ダイオードブリッジは、カソード同士が接続した上アームの第1および第2ダイオードD<sub>1R</sub>, D<sub>1S</sub>およびアノード同士が接続した下アームの第3および第4ダイオードD<sub>2R</sub>, D<sub>2S</sub>を有し、第1ダイオードD<sub>1R</sub>と第3ダイオードD<sub>2R</sub>とが直列接続し、第2ダイオードD<sub>1S</sub>と第4ダイオードD<sub>2S</sub>とが直列接続することにより構成される。第1ダイオードD<sub>1R</sub>のアノードと第3ダイオードD<sub>2R</sub>のカソードが接続するR端子、および、第2ダイオードD<sub>1S</sub>のアノードと第4ダイオードD<sub>2S</sub>のカソードが接続するS端子が、交流電源を印加する入力端子である。

【0013】

また第1および第2ダイオードD<sub>1R</sub>, D<sub>1S</sub>のカソードが接続するP端子は高電位側出力端子である。第1スイッチング素子SW<sub>R</sub>は、第1ダイオードD<sub>1R</sub>と第3ダイオードD<sub>2R</sub>との間の接続ノード(R端子)と低電位側出力端子であるN端子との間に接続される。第2スイッチング素子SW<sub>S</sub>は、第2ダイオードD<sub>1S</sub>と第4ダイオードD<sub>2S</sub>との間の接続ノード(S端子)とN端子との間に接続される。

20

【0014】

第3および第4ダイオードD<sub>2R</sub>, D<sub>2S</sub>のアノードが接続するN<sub>2</sub>端子には、外部の制御IC(不図示)が接続される。この制御ICは、N<sub>2</sub>端子の信号に基づいてドライバIC100のVIN端子に制御信号を供給することにより第1および第2スイッチング素子SW<sub>R</sub>, SW<sub>S</sub>を制御し、所定の力率改善の動作を行わせる。なお、図1に示すVD端子はドライバIC100の電源端子であり、GND端子は接地端子である。

30

【0015】

ここで、本発明に対する比較例として、従来のPFCモジュールの構造を説明する。図2はその構造を示す平面図および断面図である。従来のPFCモジュールでは、第1～第4ダイオードD<sub>1R</sub>, D<sub>1S</sub>, D<sub>2R</sub>, D<sub>2S</sub>は、Siを用いて形成したダイオードであり、先に説明されているように、耐電圧を数百V以上にする場合はPINダイオードが用いられ、耐電圧を数百V以下にする場合はSiのショットキーバリアダイオードが用いられる。また、第1および第2スイッチング素子SW<sub>R</sub>, SW<sub>S</sub>は、Siを用いて形成した例えばIGBTである。すなわち第1～第4ダイオードD<sub>1R</sub>, D<sub>1S</sub>, D<sub>2R</sub>, D<sub>2S</sub>および第1および第2スイッチング素子SW<sub>R</sub>, SW<sub>S</sub>は、いずれもSiデバイスであった。

40

【0016】

図2の如く、当該PFCモジュールにおいて、第1および第2ダイオードD<sub>1R</sub>, D<sub>1S</sub>のチップは、P端子として機能するリードフレーム104(第1リードフレーム)上に搭載されている。また第3ダイオードD<sub>2R</sub>および第1スイッチング素子SW<sub>R</sub>のチップは、R端子として機能するリードフレーム102(第2リードフレーム)上に搭載されている。第4ダイオードD<sub>2S</sub>および第2スイッチング素子SW<sub>S</sub>のチップは、S端子として機能するリードフレーム103(第3リードフレーム)上に搭載されている。またドライバIC100は、その制御に用いられる制御端子(VIN端子、VD端子、GND端子等)として機能する所定のリードフレーム上に搭載される。

【0017】

10

20

30

40

50

図2においてリードフレーム101は、N端子として機能するものであり、リードフレーム105は、N2端子として機能するものである。各チップとリードフレームとはワイヤ配線110を介して接続されている。

【0018】

以上の各構成要素は、当該PFCモジュールの筐体200を構成するモールド樹脂により保持される。リードフレーム101～104の一部は、外部接続端子として、筐体200の一側面から突出し、リードフレーム105は、ドライバIC100の制御端子(VIN端子、VD端子、GND端子等)と共に筐体200の他側面から突出している。また当該PFCモジュールには、筐体200を貫通する取り付け用の貫通孔121, 122が設けられている。

10

【0019】

図2の右側に示す断面図に示すように、従来のPFCモジュールでは、リードフレーム101～104が筐体200の内部で下方へ屈曲し、それらリードフレーム101～104におけるチップ搭載部の下面を筐体200の底面から露出させていた。リードフレーム101～104が露出した部分には、熱導電率の高い絶縁シート120が貼り付けられていた。この構造により、第1～第4ダイオードD1<sub>R</sub>, D1<sub>S</sub>, D2<sub>R</sub>, D2<sub>S</sub>および第1および第2スイッチング素子SW<sub>R</sub>の熱が外部に放出されやすくしている。

【0020】

以下、本発明の実施の形態1に係るPFCモジュールの構造を説明する。図3にその構造を示す。図3において、図2に示したものと同様の機能を有する要素には同一符号を付してある。

20

【0021】

本実施の形態では、電力制御用のチップ(パワーチップ)である第1～第4ダイオードD1<sub>R</sub>, D1<sub>S</sub>, D2<sub>R</sub>, D2<sub>S</sub>および第1および第2スイッチング素子SW<sub>R</sub>, SW<sub>S</sub>のうち、ダイオードブリッジの上アームである第1および第2ダイオードD1<sub>R</sub>, D1<sub>S</sub>をSiCデバイスのショットキーバリアダイオードにしている。その他のパワーチップは従来と同様に、第3および第4ダイオードD2<sub>R</sub>, D2<sub>S</sub>はSiCデバイスのダイオードであり、耐電圧を数百V以上にする場合はPINダイオードが用いられ、耐電圧を数百V以下にする場合はSiのショットキーバリアダイオードが用いられる。また、第1および第2スイッチング素子SW<sub>R</sub>, SW<sub>S</sub>はSiCデバイスのIGBT等である。

30

【0022】

ダイオードブリッジの上アームである第1および第2ダイオードD1<sub>R</sub>, D1<sub>S</sub>は、整流素子として機能する他、第1および第2スイッチング素子SW<sub>R</sub>, SW<sub>S</sub>によるPFC動作時の還流ダイオードとしても機能する。特にPFC制御では第1および第2スイッチング素子SW<sub>R</sub>, SW<sub>S</sub>は高周波動作するため、第1および第2ダイオードD1<sub>R</sub>, D1<sub>S</sub>における還流動作時のリカバリー損失はPFCモジュール全体の損失に大きく寄与する。第1および第2ダイオードD1<sub>R</sub>, D1<sub>S</sub>を、低損失で且つリカバリー特性に優れたSiCデバイスとすることにより、PFCモジュールの損失を大きく低減させることができる。またパワーチップの全てではなく、第1および第2ダイオードD1<sub>R</sub>, D1<sub>S</sub>のみをSiCデバイス化するに留めているため、コストの上昇も抑制できる。

40

【0023】

また図3に示す断面図のように、第1および第2ダイオードD1<sub>R</sub>, D1<sub>S</sub>を搭載するリードフレーム104は、筐体200の内部において、下方(第1および第2ダイオードD1<sub>R</sub>, D1<sub>S</sub>搭載面の垂直方向)に屈曲していない。この場合、第1および第2ダイオードD1<sub>R</sub>, D1<sub>S</sub>の放熱性が損なわれるようにも思われるが、SiCデバイスは耐熱性に優れるため問題はない。また従来損失が大きかった第1および第2ダイオードD1<sub>R</sub>, D1<sub>S</sub>の損失が小さくなり発熱も抑制されるため、図2に示した絶縁シート120を省略することによってコストの削減を図ることもできる。

【0024】

<実施の形態2>

50

図4は実施の形態2に係るPFCモジュールの構成図である。本実施の形態では、筐体200の内部において、SiCデバイスである第1および第2ダイオードD<sub>1R</sub>, D<sub>1S</sub>を、第3および第4ダイオードD<sub>2R</sub>, D<sub>2S</sub>や第1および第2スイッチング素子S<sub>WR</sub>, S<sub>WS</sub>よりも外側に配設している。すなわち第1および第2ダイオードD<sub>1R</sub>, D<sub>1S</sub>は、リードフレーム101～104が突出する筐体200の一側面の近くに配設される。また実施の形態1と同様に、第1および第2ダイオードD<sub>1R</sub>, D<sub>1S</sub>を搭載する第1リードフレーム104は、筐体200の内部において、下方（第1および第2ダイオードD<sub>1R</sub>, D<sub>1S</sub>搭載面の垂直方向）に屈曲していない。

#### 【0025】

この構成によれば、第1および第2ダイオードD<sub>1R</sub>, D<sub>1S</sub>とリードフレーム102, 103とを接続するワイヤ配線110を短くすることができる。このワイヤ配線110の長さはPFCモジュールのサージ電流耐量に影響し、それを短くすればサージ電流耐量を向上させることができる。例えば600V・20A(rms)定格のPFCモジュールでは、第1および第2ダイオードD<sub>1R</sub>, D<sub>1S</sub>とリードフレーム102, 104とを接続するワイヤ配線110の長さを従来の半分程度（従来10mmだったのものを5mmに）することができる。

#### 【0026】

＜実施の形態3＞

図5は実施の形態3に係るPFCモジュールの構成図である。本実施の形態でも、実施の形態2と同様に、筐体200の内部において、SiCデバイスである第1および第2ダイオードD<sub>1R</sub>, D<sub>1S</sub>を、第3および第4ダイオードD<sub>2R</sub>, D<sub>2S</sub>や第1および第2スイッチング素子S<sub>WR</sub>, S<sub>WS</sub>よりも外側（リードフレーム101～104が突出する筐体200の一側面の近く）に配設している。

#### 【0027】

またSiCデバイスは低抵抗であるため、チップの小型化が可能である。例えば600V・20A(rms)定格のモジュールでは、第1および第2ダイオードD<sub>1R</sub>, D<sub>1S</sub>のチップサイズを半分程度にできる。そのため第1および第2ダイオードD<sub>1R</sub>, D<sub>1S</sub>を外側に寄せると、筐体200の中央部にスペースができる。本実施の形態では、そのスペースに貫通孔122を配設する。すなわち第1および第2ダイオードD<sub>1R</sub>, D<sub>1S</sub>の少なくとも片方は、平面視で貫通孔122と上記筐体200の一側面との間に配設される（図5の平面図において、貫通孔122と第1および第2ダイオードD<sub>1R</sub>, D<sub>1S</sub>とが縦に並ぶ）。

#### 【0028】

本実施の形態によれば、貫通孔122を筐体200の内側に寄せて配設できるため、PFCモジュールのパッケージサイズの小型化が可能になる。例えば600V・20A(rms)定格のモジュールでは、パッケージの長さ（筐体200の長さ）を実施の形態1, 2（図3および図4）よりも4mm程度の短くできた。なお図5の点線は、実施の形態1, 2における筐体200の形状および貫通孔122の位置を示している。

#### 【0029】

以上のように本発明は、高耐電圧、低損失および高耐熱というSiCデバイスの特性を効果的に利用している。これらの特性はSiCデバイスに限らず、他のワイドバンドギャップ半導体を用いた半導体デバイスも有している。よって第1および第2ダイオードD<sub>1R</sub>, D<sub>1S</sub>を、SiC以外のワイドバンドギャップ半導体を用いて形成したショットキーバリアダイオードとしてもよく、上記と同様の効果を得ることができる。

#### 【符号の説明】

#### 【0030】

D<sub>1R</sub> 第1ダイオード、D<sub>1S</sub> 第2ダイオード、D<sub>2R</sub> 第3ダイオード、D<sub>2S</sub> 第4ダイオード、S<sub>WR</sub> 第1スイッチング素子、S<sub>WS</sub> 第2スイッチング素子、100ドライバIC、101～105 リードフレーム、110 ワイヤ配線、121, 122貫通孔、200 筐体。

10

20

30

40

50

【 図 1 】

【 図 2 】

【 四 3 】

【図4】

【図5】

---

フロントページの続き

(56)参考文献 特開2009-272482(JP,A)

特開2003-219687(JP,A)

特開2000-138343(JP,A)

特開2004-047883(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 25/07

H01L 25/18

H02M 7/42 - 7/98