(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2016-524722

(P2016-524722A)

(43) 公表日 平成28年8月18日(2016.8.18)

(51) Int.Cl.

G02F 1/025 (2006.01)

F 1

G02F 1/025

テーマコード(参考)

2K102

審査請求 未請求 予備審査請求 未請求 (全 24 頁)

(21) 出願番号 特願2016-513918 (P2016-513918)

(86) (22) 出願日 平成25年10月22日 (2013.10.22)

(85) 翻訳文提出日 平成27年12月16日 (2015.12.16)

(86) 国際出願番号 PCT/US2013/066134

(87) 国際公開番号 WO2014/185951

(87) 国際公開日 平成26年11月20日 (2014.11.20)

(31) 優先権主張番号 61/823,344

(32) 優先日 平成25年5月14日 (2013.5.14)

(33) 優先権主張国 米国(US)

(71) 出願人 515318186

コリアント・アドヴァンスド・テクノロジー・エルエルシー

アメリカ合衆国ニューヨーク州10016

, ニューヨーク, マディソン・アベニュー

171, スイート 1100

(74) 代理人 100140109

弁理士 小野 新次郎

(74) 代理人 100075270

弁理士 小林 泰

(74) 代理人 100101373

弁理士 竹内 茂雄

(74) 代理人 100118902

弁理士 山本 修

最終頁に続く

(54) 【発明の名称】空乏モードシリコン変調器のための超応答移相器

## (57) 【要約】

キャリア空乏化に基づくシリコン変調器の新奇な移相器設計について、実験的に確認されたモデルに基づいて、記載される。以前は無視されていた不完全なイオン化の効果が超応答移相器に著しい影響を及ぼすと思われる。20dB/cmの低い伝搬損失に関連付けられた0.3V/cmの低いV<sub>L</sub>積が観察されると予想される。移相器は、注入ステップをオーバラップさせることに基づき、ドーズ量およびエネルギーがカウンタドーピングを利用してS字形の接合を生成するように注意深く選ばれる。この接合は、特に魅力的なV<sub>L</sub>性能指数を有し、一方で魅力的に低い静電容量および光損失を同時に達成する。この改善によって、著しく小さくできるにもかかわらず低駆動電圧を有し、挿入損失が実質的に低下したマッハ-ツエンダー変調器を構築することができる。記載された作製プロセスは、最低限の複雑さであり、特に、高解像度のリソグラフィステップを必要としない。

FIG. 4A

## 【特許請求の範囲】

## 【請求項 1】

3を超える屈折率を有する半導体を備える光導波路と、

前記光導波路内に作製され、p型コンタクト端子を有する半導体材料のp型領域と、

前記光導波路内に作製され、n型コンタクト端子を有する半導体材料のn型領域と、

を備え、

前記n型領域および前記p型領域が長さ寸法(length dimension)を有する非平面(non-planar)の接合界面(junction interface)を有し、前記非平面の共通の接合が、前記光変調器半導体デバイスが動作しているときに前記光導波路における光学モードと前記接合領域の間のオーバラップを向上させる(enhance)ように、前記接合の前記長さ寸法の単位長当たりの、前記n型領域と前記p型領域の間の接合領域を増加させるように構成されている、光変調器半導体デバイス。

10

## 【請求項 2】

前記非平面の接合界面が凸面側および凹面側を有する湾曲面(curved surface)を備える、請求項1に記載の光変調器半導体デバイス。

## 【請求項 3】

前記湾曲面が英文字「U」、「C」および「S」の1つに似ている、請求項2に記載の光変調器半導体デバイス。

## 【請求項 4】

前記p型領域が前記非平面の接合界面の前記凹面側にあり、前記n型領域が前記非平面の接合界面の前記凸面側にある、請求項2に記載の光変調器半導体デバイス。

20

## 【請求項 5】

前記n型領域が前記非平面の接合界面の前記凹面側にあり、前記p型領域が前記非平面の接合界面の前記凸面側にある、請求項2に記載の光変調器半導体デバイス。

## 【請求項 6】

光変調器半導体デバイスを作製する方法であって、

平面形態の半導体材料を用意するステップと、

異方性(anisotropic)エッチングによって前記半導体材料からスラブ導波路構造を形成するステップと、

前記スラブ(slab)導波路の上に絶縁体の薄層を共形的に(conformally)堆積させるステップと、

n型およびp型の領域をそれぞれ生成するために複数の注入ステップで前記スラブ導波路にn型およびp型のドーパントを注入するステップと、

前記注入されたスラブ導波路構造をアニールするステップと、

を含み、

それによって、前記スラブ導波路構造内部に長さ寸法を有する非平面の接合界面を有するp型領域およびn型領域を形成し、前記非平面の共通の接合が、前記光変調器半導体デバイスが動作しているときに前記光導波路の光学モードと前記接合領域の間のオーバラップを向上させるように、前記接合の前記長さ寸法の単位長当たりの、前記n型領域と前記p型領域の間の接合領域を増加させるように構成されている、方法。

40

## 【請求項 7】

前記平面形態の半導体材料がシリコン・オン・インシュレータ・ウェーハである、請求項6に記載の光変調器半導体デバイスを作製する方法。

## 【請求項 8】

複数の注入ステップで前記スラブ導波路にn型およびp型のドーパントを注入する前記ステップが、表1のパラメータにより行われる、請求項6に記載の光変調器半導体デバイスを作製する方法。

## 【請求項 9】

前記アニールステップが急速熱アニール(RTA: rapid thermal annealing)を使用して行われる、請求項6に記載の光変調器半導体デバイスを作製する方法。

50

**【請求項 1 0】**

前記 n 型領域および前記 p 型領域の少なくとも 1 つに隣接する領域を、前記領域と同じ型のドーパントを用いて多量にドープすることによって、前記 n 型領域および前記 p 型領域の前記少なくとも 1 つにコンタクトが設けられる、請求項 6 に記載の光変調器半導体デバイスを作製する方法。

**【請求項 1 1】**

光変調を達成するために、カウンタドーピング(counter-doping)技法が適用され、いくつかの注入が線形に(linear fashion)組み合わさってシリコン内に非線形の形状を有する p n 接合を生成することを可能にする、請求項 6 に記載の光変調器半導体デバイスを作製する方法。

10

**【請求項 1 2】**

前記非平面の接合界面が英文字「U」、「C」および「S」の 1 つに形状が類似する幾何学形状を有する、請求項 1 1 に記載の光変調器半導体デバイスを作製する方法。

**【請求項 1 3】**

複数の注入ステップで前記スラブ導波路に n 型および p 型のドーパントを注入する前記ステップが表 2 のパラメータによって行われる、請求項 6 に記載の光変調器半導体デバイスを作製する方法。

**【請求項 1 4】**

3 を超える屈折率を有する半導体を備える光導波路と、前記光導波路内に作製され、p 型のコンタクト端子を有する半導体材料の p 型領域と、前記光導波路内に作製され、n 型のコンタクト端子を有する半導体材料の n 型領域と、を有し、前記 n 型領域および前記 p 型領域が長さ寸法を有する非平面の接合界面を有する、光変調器半導体デバイスにおいて光搬送波を変調する方法であって、

20

前記光変調器半導体デバイスの入力ポートにおいて光搬送波を提供するステップと、

前記 n 型コンタクト端子と前記 p 型コンタクト端子の両端間に、前記 p n 接合を逆バイアスして前記 p n 接合の空乏領域のサイズを変えるように動作する電気信号を提供し、それによって前記光搬送波を変調する、ステップと、

前記光変調器半導体デバイスの出力ポートにおいて前記変調された光搬送波を出力信号として受信するステップと、

を含む方法。

30

**【請求項 1 5】**

前記非平面の接合界面が英文字「U」、「C」および「S」の 1 つに形状が類似する幾何学形状を有する、請求項 1 4 に記載の光変調器半導体デバイスにおいて光搬送波を変調する方法。

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

関連出願の相互参照

[0001] 本出願は、その全体が参照により本明細書に組み込まれる、2013年5月14日に出願した同時係属中の米国仮特許出願第 61/823,344 号の優先権および利点を主張する。

40

**【0 0 0 2】**

[0002] 本発明は、一般に移相器、詳細には光移相器に関する。

**【背景技術】****【0 0 0 3】**

[0003] 過去十年間、高性能コンピューティングおよびデータセンタから通信帯域幅が急速に求められている（例えば、G. T. Reed, G. Mashanovich, F. Y. Gardes, and D. J. Thomson, "Silicon optical modulators," *Nat. Photonics* 4(8), 518-526 (2010) 参照）。シリコンフォトニクス技術は、CMOS 技術との両立性により次世代

50

相互接続のための低成本で信頼性のある解決策になる大きな可能性を示した（例えば、Y. A. Vlasov, "Silicon CMOS-integrated nano-photronics for computer and data communications beyond 100 G," IEEE Commun. Mag. 50 (2), 67-72 (2012) 参照）。しかしながら、シリコンフォトニクス技術が広く採用されるために、取り組む必要のある重要な課題は、シリコンで効率的かつ高速の変調を達成する一方で、ダイ面積の消費を最小量にすることである。光学的および電気的なパワー消費量を最小化するために、シリコン変調器が低い挿入損失および駆動電圧を有する一方で、高いデータレートで動作することが期待される（例えば、Miller, D. "Device requirements for optical interconnects to silicon chips". Proc. IEEE 97, 1166-1185 (2009) 参照）。

#### 【0004】

[0004] 今日、キャリア空乏化に基づく変調器は、比較的簡単な作製プロセスおよび速い動作速度のために、データ通信用途にとって最も競争力のある手法の1つである。この手法では、注入によってPN接合がリブシリコン導波路内部に形成される。PN接合の自由キャリアを激減させることによるキャリア分散効果を介して、光変調が得られる（例えば、R. A. Soref, and B. R. Bennett, "Electrooptical effects in silicon," IEEE J. Quantum Electron. 23 (1), 123-129 (1987) 参照）。光位相変調は、マッハツエンダー干渉計およびリング共振器などの構造によって輝度変調に変換することができる。この考え方に基づいて、25Gb/s以上で動作するシリコン変調器がいくつかのグループによって実証された（例えば、L. Liao, A. Liu, D. Rubin, J. Basak, Y. Chetrit, H. Nguyen, R. Cohen, N. Izhaky, and M. Paniccia, "40 Gbit/s silicon optical modulator for high-speed applications," Electron. Lett. 43 (22), 1196-1197 (2007)、T. Baehr-Jones, R. Ding, Y. Liu, A. Ayazi, T. Pinguet, N. C. Harris, M. Streshinsky, P. Lee, Y. Zhang, A. E. Lim, T. Y. Liow, S. H. Teo, G. Q. Lo, and M. Hochberg, "Ultralow drive voltage silicon traveling-wave modulator," Opt. Express 20 (11), 12014-12020 (2012)、M. Ziebell, D. Marriss-Morini, G. Rasigade, J. - M. Fedeli, P. Crozat, E. Cassan, D. Bouville, and L. Vivien, "40 Gbit/s low-loss silicon optical modulator based on a pin diode," Opt. Express 20 (10), 10591-10596 (2012)、D. J. Thomson, F. Y. Gardes, Y. Hu, G. Mashanovich, M. Fournier, P. Gross, J. - M. Fedeli, and G. T. Reed, "High contrast 40 Gbit/s optical modulation in silicon," Opt. Express 19 (12), 11507-11516 (2011)、J. Ding, H. Chen, L. Yang, L. Zhang, R. Ji, Y. Tian, W. Zhu, Y. Lu, P. Zhou, R. Min, and M. Yu, "Ultralow-power carrier-depletion Mach-Zehnder silicon optical modulator," Opt. Express 20 (7), 7081-7087 (2012)、Long Chen, Christopher R. Doerr, Po Dong, and Young-kai Chen, "Monolithic silicon chip with 10 modulator channels at 25 Gbps and 100-GHz spacing" 10 20 30 40 50

ng, "Opt. Express 19, B946-B951 (2011)、J. C. Rosenberg, W. M. J. Green, S. Assefa, D. M. Gill, T. Barwicz, M. Yang, S. M. Shank, and Y. A. Vlasov, "A 25 Gbps silicon microring modulator based on an interleaved junction," Opt. Express 20, 26411-26423 (2012)、Xi Xiao, Hao Xu, Xianyao Li, Yingtao Hu, Kang Xiong, Zhiyong Li, Tao Chu, Yude Yu, and Jinzhong Yu, "25 Gbit/s silicon microring modulator based on misalignment-tolerant interleaved PN junctions," Opt. Express 20, 2507-2515 (2012)、およびGuoliang Li, Xuezhe Zheng, Jin Yao, Hiren Thacker, Ivan Shubin, Ying Luo, Kannan Raj, John E. Cunningham, and Ashok V. Krishnamoorthy, "25 Gb/s 1V-driving CMOS ring modulator with integrated thermal tuning," Opt. Express 19, 20435-20443 (2011) 参照)。これらの結果の大部分は、導波路内部に横方向または縦方向の簡単なPN接合幾何学形状を有する移相器に基づく。

## 【0005】

[0005]現在一般に行われている手法に関して留意すべき重要な1つの事実は、進行波デバイスが長く、しばしば数mm以上になる傾向があるということである。これは、シリコンにおけるかなり弱い電気光学効果による。シリコンpn接合に関連付けられた単位電圧当たりの位相偏移(FOM  $V_L$ によって特徴づけられる)を増加させることは可能であるが、ドーパント濃度を増加させることによってのみ可能であり、これは後で導波路損失を増加させる。この基本的なトレードオフは、他で観察され(例えば、Hui Yu, Marianna Pantouvaki, Joris Van Campenhout, Dietmar Korn, Katarzyna Komorowska, Pieter Dumon, Yanlu Li, Peter Verheyen, Philippe Absil, Luca Alloatti, David Hillekuss, Juerg Leuthold, Roel Baets, and Wim Bogaerts, "Performance tradeoff between lateral and interdigitated doping patterns for high speed carrier-depletion based silicon modulators," Opt. Express 20, 12926-12938 (2012)、およびHui Yu; Bogaerts, W.; De Keersgieter, A., "Optimization of Ion Implantation Condition for Depletion-Type Silicon Optical Modulators," Quantum Electronics, IEEE Journal of, vol. 46, no. 12, pp. 1763, 1768, Dec. 2010 参照)、損失・効率性能指数(例えば、Xiaoguang Tu, Tsung-Yang Liow, Junfeng Song, Mingbin Yu, and Guo Qiang Lo, "Fabrication of low loss and high speed silicon optical modulator using doping compensation method," Opt. Express 19, 18029-18035 (2011) 参照)(F値)が移相器の損失と $V_L$ のトレードオフを特徴づけるために導入された。より低いF値を有する移相器は、より低い光挿入損失で同一の $V_L$ を達成することができ、これが大いに望ましい。したがって、F値がより低い方がよい。これまでのところ、文献では、高解像度のインターディジテーションを必要としない簡単な接合幾何学形状に対するF値は、典型的には1

10

20

30

40

50

0 ~ 30 であり、(例えば、Watts, M. R.; Zortman, W. A.; Trotter, D. C.; Young, R. W.; Lentine, A. L., "Low-Voltage, Compact, Depletion-Mode, Silicon Mach-Zehnder Modulator," Selected Topics in Quantum Electronics, IEEE Journal of, vol. 16, no. 1, pp. 159, 164, Jan. - Feb. 2010 参照)、報告された最も低い  $F$  値は、1.5 V/cm の  $V_L$  で 10.5 dBV である(例えば、Xi Xiao, Hao Xu, Xianyao Li, Zhiyong Li, Tao Chu, Yude Yu, and Jinzhong Yu, "High-speed, low-loss silicon Mach-Zehnder modulators with doping optimization," Opt. Express 21, 4116 - 4125 (2013) 参照)。

#### 【0006】

[0006] 単純にドーパント濃度を上げることは、実際にそれほど好ましい  $F$  メトリックにつながらない。しかしながら、交互配置された接合および「ジグザグ」接合などのより複雑な接合幾何学形状(例えば、Xi Xiao; Xianyao Li; Hao Xu; Yingtao Hu; Kang Xiong; Zhiyong Li; Tao Chu; Jinzhong Yu; Yude Yu, "44-Gb/s Silicon Micro-ring Modulators Based on Zigzag PN Junctions," Photonics Technology Letters, IEEE, vol. 24, no. 19, pp. 1712, 1714, Oct. 1, 2012 参照)は、より好ましい  $F$  値を示す。これらの設計では、キャリアと光の相互作用を向上させるために単位長当たりの接合領域を意図的に増加させている。この手段によって、16 dB/cm の光損失で 0.24 V/cm の  $V_L$  が理論的に予測されている(例えば、Zhi-Yong Li, Dan-Xia Xu, W. Ross McKinnon, Siegfried Janz, Jens H. Schmid, Pavel Cheben, and Jin-Zhong Yu, "Silicon waveguide modulator based on carrier depletion in periodically interleaved PN junctions," Opt. Express 17, 15947 - 15958 (2009) 参照) ( $F = 3.84 \text{ dBV}$ )。これらは有望な結果であるが、この極めて低い  $V_L$  を達成するためには、200 nm のインターディジテーション周期が必要であり、現在、ほとんどのシリコンフォトニクス注入層が比較的低い解像度のマスクによって作製されているため、これは困難を呈するであろう。これまでのところ、193 nm のリソグラフィプロセスでさえも実験的に達成された最良の  $V_L$  は、35 dB/cm の光損失に関連付けられた 0.62 V/cm である( $F = 21.7 \text{ dBV}$ )。また、光損失を低減するために補償ドーピングおよび PIN 接合幾何学形状のような他の方法が検討されたが、報告された  $V_L$  は、なお比較的高く、 $F$  値は、典型的には 19 dBV 以上である。

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0007】

[0007] 光変調器の作製のために高解像度のリソグラフィを必要としない光変調器が必要である。

#### 【課題を解決するための手段】

#### 【0008】

[0008] 一態様によれば、本発明は、光変調器半導体デバイスを主に扱う。光変調器半導体デバイスは、3 を超える屈折率を有する半導体を備える光導波路と、光導波路内に作製され、p 型コンタクト端子を有する半導体材料の p 型領域と、光導波路内に作製され、n 型コンタクト端子を有する半導体材料の n 型領域と、を備え、n 型領域および p 型領域が長さ寸法を有する非平面の接合界面を有し、非平面の共通の接合が、光変調器半導体デバ

10

20

30

40

50

イスが動作しているときに光導波路における光学モードと接合領域の間のオーバラップを向上させるように、接合の長さ寸法の単位長当たりの、n型領域とp型領域の間の接合領域を増加させるように構成されている。

【0009】

[0009]一実施形態において、非平面の接合界面は、凸面側および凹面側を有する湾曲面を備える。

[0010]別の実施形態では、湾曲面は、英文字「C」に似ている。

【0010】

[0011]さらに別の実施形態では、湾曲面は、英文字「U」に似ている。

[0012]さらに別の実施形態では、湾曲面は、英文字「S」に似ている。 10

[0013]さらなる実施形態では、p型領域は、非平面の接合界面の凹面側にあり、n型領域は、非平面の接合界面の凸面側にある。

【0011】

[0014]さらなる実施形態では、n型領域は、非平面の接合界面の凹面側にあり、p型領域は、非平面の接合界面の凸面側にある。

[0015]別の態様によれば、本発明は、光変調器半導体デバイスを作製する方法に関する。本方法は、平面形態の半導体材料を用意するステップと、異方性エッチングによって半導体材料からスラブ導波路構造を形成するステップと、スラブ導波路の上に絶縁体の薄層を共形的に堆積させるステップと、n型およびp型の領域をそれぞれ生成するために複数の注入ステップでスラブ導波路にn型およびp型のドーパントを注入するステップと、注入されたスラブ導波路構造をアニールするステップと、を含み、それによって、スラブ導波路構造内部に長さ寸法を有する非平面の接合界面を有するp型領域およびn型領域を形成し、非平面の共通の接合が、光変調器半導体デバイスが動作しているときに光導波路の光学モードと接合領域の間のオーバラップを向上させるように、接合の長さ寸法の単位長当たりの、n型領域とp型領域の間の接合領域を増加させるように構成されている。 20

【0012】

[0016]一実施形態において、平面形態の半導体材料は、シリコン・オン・インシュレータ・ウェーハである。

[0017]別の実施形態では、複数の注入ステップでスラブ導波路にn型およびp型のドーパントを注入するステップは、表1のパラメータにより行われる。 30

【0013】

[0018]さらに別の実施形態では、アニールステップは、急速熱アニール(RTA)を使用して行われる。

[0019]さらに別の実施形態では、n型領域およびp型領域の少なくとも1つに隣接する領域を、この領域と同じ型のドーパントを用いて多量にドープすることによって、n型領域およびp型領域の少なくとも1つにコンタクトが設けられる。

【0014】

[0020]さらなる実施形態では、光変調を達成するために、カウンタドーピング技法が適用され、いくつかの注入が線形に組み合わさせてシリコン内に非線形の形状を有するp-n接合を生成することを可能にする。 40

【0015】

[0021]さらなる実施形態では、非平面の接合界面は、英文字「U」、「C」および「S」の1つに形状が類似する幾何学形状を有する。

[0022]さらなる実施形態では、複数の注入ステップでスラブ導波路にn型およびp型のドーパントを注入するステップは、表2のパラメータにより行われる。

【0016】

[0023]別の態様によれば、本発明は、3を超える屈折率を有する半導体を備える光導波路と、光導波路内に作製され、p型コンタクト端子を有する半導体材料のp型領域と、光導波路内に作製され、n型コンタクト端子を有する半導体材料のn型領域と、を有し、n型領域およびp型領域が長さ寸法を有する非平面の接合界面を有する、光変調器半導体デ 50

バイスにおいて光搬送波を変調する方法に関し、本方法は、光変調器半導体デバイスの入力ポートにおいて光搬送波を提供するステップと、n型コンタクト端子とp型コンタクト端子の両端間に、p-n接合を逆バイアスしてp-n接合の空乏領域のサイズを変えるように動作する電気信号を提供し、それによって光搬送波を変調するステップと、光変調器半導体デバイスの出力ポートにおいて変調された光搬送波を出力信号として受信するステップと、を含む。

【0017】

[0024]一実施形態において、非平面の接合界面は、英文字「U」、「C」および「S」の1つに形状が類似する幾何学形状を有する。

[0025]本発明の前述のならびに他の目的、態様、特徴および利点は、以下の説明から、10 および特許請求の範囲からより明らかになるだろう。

【0018】

[0026]本発明の目的および特徴は、以下に記載された図面および特許請求の範囲を参照することによって一層よく理解され得る。図面は、必ずしも縮尺通りではなく、その代りに、全体的に、本発明の原理を示すことに重点が置かれている。図面において、様々な図全体を通して同様の部分を指すために同様の数字が使用される。

【図面の簡単な説明】

【0019】

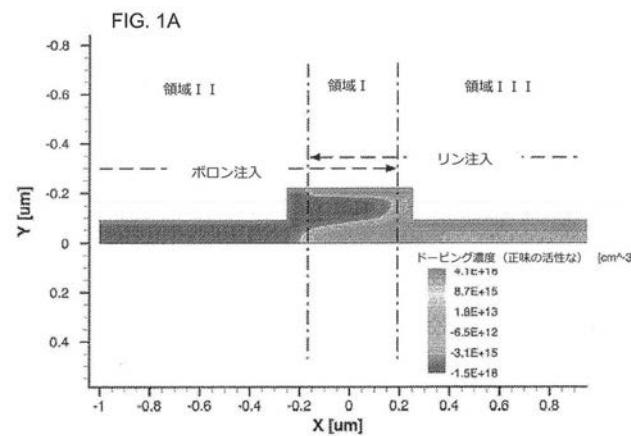

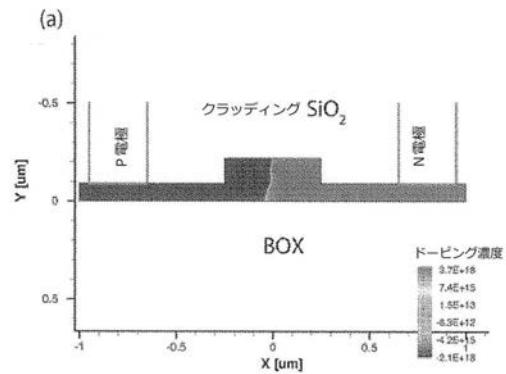

【図1A】[0027]表1にリストされた注入およびアニール条件の後の、移相器の断面のシミュレートされたドーパント分布を示す概略図である。

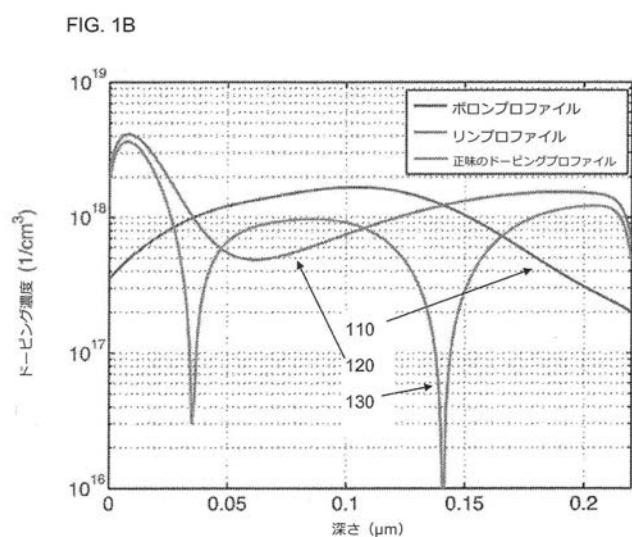

【図1B】[0028]図1Aの領域Iを通る断面のボロン(曲線110)、リン(曲線120)の深さ分布、および正味のプロファイル(曲線130)を示すグラフである。

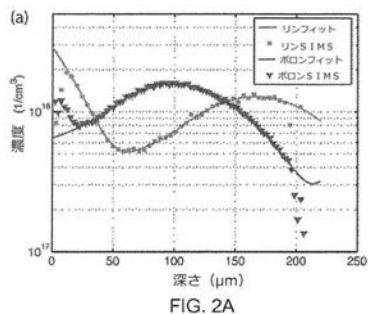

【図2A】[0029]SIMSによって測定されたボロン(三角形)およびリン(四角形)の濃度を深さの関数として示すグラフである。複数のピークのガウス関数を使用してデータポイントをフィッティングしている。

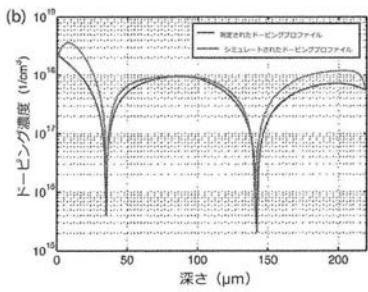

【図2B】[0030]測定された、および設計された正味のドーピングプロファイルのグラフである。

【図3A】[0031]横方向接合移相器の断面の非平面のドーピングプロファイルを示す図面である。

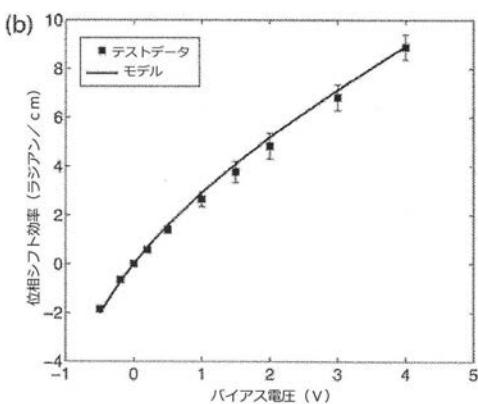

【図3B】[0032]測定された、およびシミュレートされた位相偏移をバイアス電圧の関数として示すグラフである。

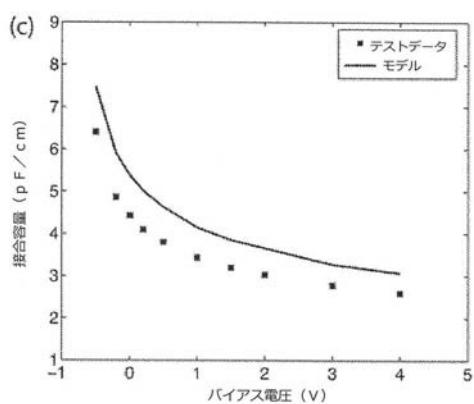

【図3C】[0033]測定された、およびシミュレートされた接合容量をバイアス電圧の関数として示すグラフである。

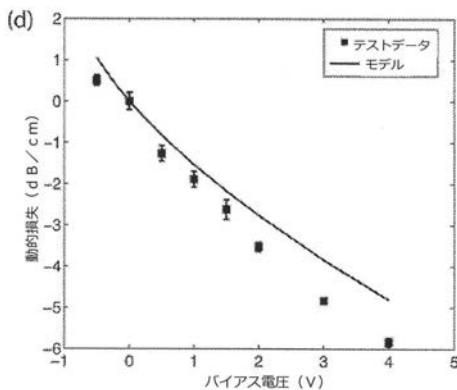

【図3D】[0034]測定された、およびシミュレートされた動的損失をバイアス電圧の関数として示すグラフである。

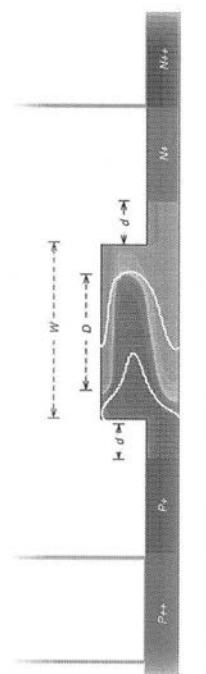

【図4A】[0035]記載される移相器の構成を示す図面である。白線は、3Vの逆バイアスでの空乏領域を示す。

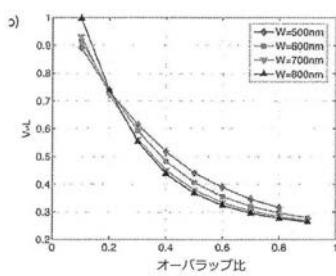

【図4B】[0036]推定されたV<sub>L</sub>を導波路幅およびオーバラップ比の関数として示すグラフである。

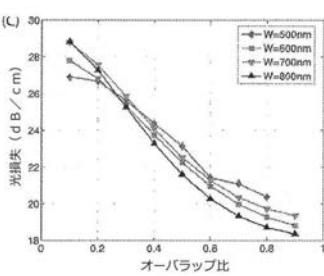

【図4C】[0037]光損失を導波路幅およびオーバラップ比の関数として示すグラフである。

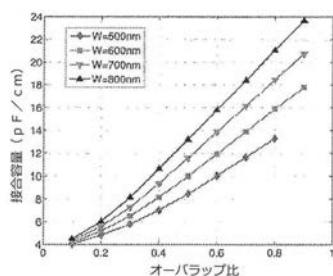

【図4D】[0038]接合容量を導波路幅およびオーバラップ比の関数として示すグラフである。

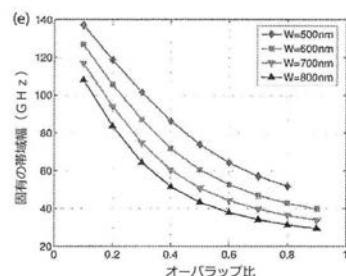

【図4E】[0039]固有の帯域幅を導波路幅およびオーバラップ比の関数として示すグラフである。

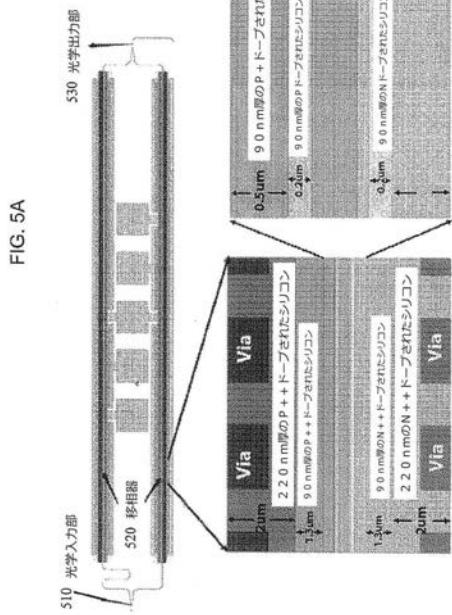

【図5ABC】[0040]図5Aは本発明の原理により作製されたデバイスを使用して構築されたマッハツエンダー干渉計の図である。[0041]図5BはNおよびPの注入が導波路の中心でオーバラップする、移相器用の詳細なドーピングマスクを示す図面である。[0042]図5Cは図5Bのドーピングマスクの一部についてのより詳細な図を示す図面である。

10

20

30

40

50

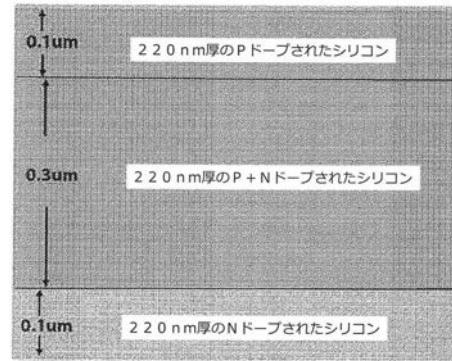

【図 5 D】[0043]導波路の中心における層の寸法を示す図面である。

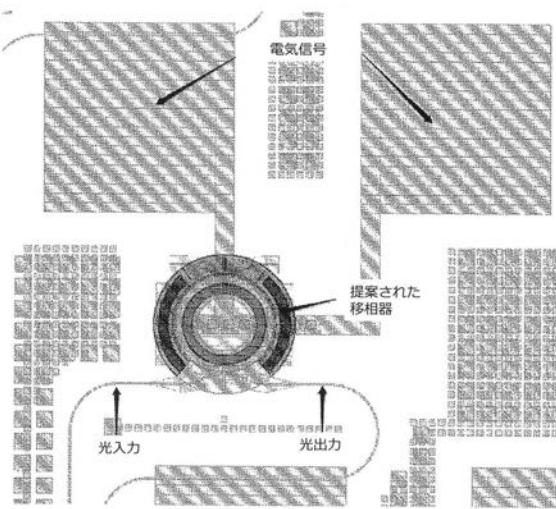

【図 6】[0044]本発明の原理により作製されたデバイスを使用して構築されたリング変調器の図である。

【発明を実施するための形態】

【0020】

[0045]わずか 20 dB / cm の光損失 ( $F = 6 \text{ dBV}$ ) に関連付けられた 0.3 V . cm の極めて低い  $V_L$  を提供する S 字形接合幾何学形状に関する新奇な移相器の設計について記載する。接合幾何学形状の微細構造は、リソグラフィではなく注入条件によって制御され、解像度に対する要求、したがって注入マスクのコストを最小にする。

【0021】

[0046] S 字形幾何学形状は、最終のアニールされたシリコン中のドーパントのその形状構成に大きく依存する。ドーパント濃度が高いため、注入の設計において一般には無視されるいくつかの効果を考慮に入れなければならない。特に、表面偏析によりもたらされるドーズ量の損失（例えば、P. B. Griffin, S. W. Crowder, and J. M. Knight "Dose loss in phosphorus implants due to transient diffusion and interface segregation" Appl. Phys. Lett. 67, 482 (1995) 参照）、および注入に基づくダメージを考慮しなければならない。表面偏析の重要性を立証し、我々の注入レシピを較正して所望の目標を達成することができる SIMS データを示す。さらに、不完全なイオン化、すなわち高ドーズ量レベルの半導体においてよく知られている効果（例えば、Wieslaw Kuzmicz, Ionization of impurities in silicon, Solid-State Electronics, Volume 29, Issue 12, December 1986, Pages 1223 - 1227、および S. M. Sze and K. K. Ng, Physics of Semiconductor Devices. New York: Wiley, 2007, pp. 79 - 90 参照）を考慮しなければならないことに言及する。不完全なイオン化の効果が測定され、他の方法では以下で提示する実験データと比較して、何が著しい食い違いとなるかを説明するのに役立つ。この効果は、シリコン空乏変調器設計において、影響が小さいとして今まで無視されてきた。しかしながら、より複雑な注入構造を有するさらに高度な接合では、我々が議論する効果のすべてについての完全な理解が重要になる可能性が高まる。

動作原理

[0047] 以前に論じたように、高い光損失をこうむることなくシリコン移相器の変調効率を改善するための重要な考慮すべき点は、適度なドーピングレベルを維持しながら、光学モードと空乏領域の間のオーバラップを増加させることである。我々の設計では、この目標は、導波路において接合線が S 字形のように取り巻く新奇な接合幾何学形状を実施することによって達成される。他の実施形態では、接合は、英文字の「C」または「U」に類似したやり方で成形されてもよい。従来の横方向の接合と比較して、S 字形の接合幾何学形状は、単位長当たり実質的により大きな表面積を有する。このようにして、高い変調効率および比較的低い光損失を同時に達成することができる。空乏領域のサイズを変えるように p-n 接合を逆バイアスすることによってこの変調を起こし、したがって変調を達成することが予想される。最初に、フォトニクスファウンドリにおいてこの S 接合をどのように作製するかについて述べ、次に、作製ステップについて詳細に説明する。

【0022】

[0048] 光変調は、自由キャリアのプラズマ分散効果および p-n 界面固有の p-n 接合ダイオードの逆バイアスに基づいて、1550 nm ~ 1310 nm 近辺の自由空間の波長を有する放射に対して達成される。図 1 A に示すように、変調効果は、導波路の光学モードと接合幾何学形状間のオーバラップを最大化することによって増強される。

【0023】

[0049] 図 1 A は、表 1 にリストされた注入およびアニール条件の後の、移相器の断面の

10

20

30

40

50

シミュレートされたドーパント分布を示す概略図である。

[0050] 図 1 B は、図 1 A の領域 I を通る断面でのボロン（曲線 110）、リン（曲線 120）の深さプロファイル、および正味のプロファイル（曲線 130）を示すグラフである。

【0024】

[0051] 作製は、220 nm の上部シリコン層および 2 μm の埋込み酸化物層（BOX）を有する SOI ウェーハから開始する。シリコンスラブ導波路構造は、130 nm の異方性エッティングによって形成される。結果として生じるスラブ導波路は、500 nm の幅、220 nm のリブ高さ、および 90 nm のスラブ高さを有する。エッティング後、後続の注入ステップでのチャネリング効果を最小化するために、SiO<sub>2</sub> の薄層（10 nm）をシリコン面の上に共形的に堆積させる。次いで、複数の注入ステップが表 1 にリストされた注入条件で行われる。ボロンおよびリンのビームは、4 つの基本方向から異なる傾斜角でウェーハに注入される。ステップ 1 ~ 4 では、7° の傾斜角を使用してイオンチャネリング効果を最小化する。ステップ 5 で、45° の傾斜角を使用して、側壁に沿った電気的な接続性を保証するためにリンを導波路の右側壁に注入する。注入後、1030 で 5 秒の急速熱アーナー（RTA）ステップを使用してドーパントを活性化する。移相器の断面のドーパントの分布は、半導体プロセスシミュレータ Sentaurus Process を用いてシミュレートされ、図 1 B にプロットされている。特定の注入エネルギーが表 1 にリストされているが、注入を、他の、わずかに修正されたエネルギーによって行い、それでもなお、有用な結果を得ることができることが知られている。例えば、表 1 にリストされた 32 keV のエネルギーではなく 33 keV でステップ 2 を行うことができる。

10

20

30

【0025】

【表 1】

表 1：基本設計に対する注入条件

| ステップ | 種     | エネルギー / KeV | ドーズ量 / cm <sup>2</sup> | 注入窓        | 傾斜角 |

|------|-------|-------------|------------------------|------------|-----|

| 1    | Boron | 14          | $3.5 \times 10^{12}$   | (-1, 0.15) | 7   |

| 2    | Boron | 32          | $2.0 \times 10^{13}$   | (-1, 0.15) | 7   |

| 3    | Phos  | 160         | $3.0 \times 10^{13}$   | (-0.15, 1) | 7   |

| 4    | Phos  | 15          | $1.0 \times 10^{13}$   | (-0.15, 1) | 7   |

| 5    | Phos  | 10          | $7.0 \times 10^{12}$   | (-0.15, 1) | 45  |

| 6    | RTA   |             | 1030°C                 | 5s         |     |

【0026】

[0052] 上記のレシピでは、シリコン導波路のリブ高さおよびスラブ高さは、簡単にするため今日のフォトニクスファウンドリによって提供される典型的な値に選ばれている（例えば、R. Ding, T. Baehr-Jones, T. Pinguet, J. Li, N. C. Harris, M. Streshinsky, L. He, A. Novack, E. Lim, T. Liow, H. Teo, G. Lo, and M. Hochberg, "A Silicon Platform for High-Speed Photonic Systems," in Optical Fiber Communication Conference, OSA Technical Digest (Optical Society of America, 2012), paper OM2E.6 参照）。導波路の S 字形の接合幾何学形状は、注意深く制御された注入条件によって達成される。まず第 1 に、ボロンおよびリンの深さ（導波路の垂直方向の）プロファイルは、以下のように設計される。リンは、プロファイルが 2 つのピークを、すなわち一方が導波路の上部近くに、もう一方が底部近くに有するように高いエネルギーステップおよび低いエネルギーステップによって注入される。ボロンの主たるドーズ量は、プロファイルが導波路の真中に 1 つのピークのみを示すように单一のエネルギーによって注入される。第 2 に、横方向には、ボロンおよびリンの注入窓が、導波路のコアにおいてオーバラップ領域を有するように設計される。

40

50

## 【0027】

[0053]カウンタドーピング（例えば、J. D. Plummer, Michael Deal, and P. D. Griffin "Silicon VLSI Technology: Fundamentals, Practice, and Modeling", Prentice-Hall, 2000参照）として知られている技法を我々の接合において利用する。この技法では、アクセプタ（ボロン）およびドナー（リンまたはヒ素）の両方がシリコンへ注入され、シリコンの極性は、アクセプタ濃度とドナー濃度との差によって最終的に決定される。シリコンは、アクセプタ濃度がドナー濃度を上回る場合は、p型のように見え、ドナー濃度がアクセプタ濃度を上回る場合は、n型のように見える。光学デバイスにこの技法を適用する場合、導波路の単結晶特性を維持することが重要である。これには、注入プロセスにおいて蓄積されたダメージが $5 \times 10^{21}$ 欠陥/ $\text{cm}^3$ の非晶質しきい値未満であることが必要である。

10

## 【0028】

[0054]S字形接合幾何学形状の形成は、以下のように理解することができる。図1Aに関して、横方向（x方向）に、スラブ移相器は、ボロンおよびリンの注入マスクによって3つの領域に分割される。領域Iは、ボロンおよびリン注入の両方にさらされる。図1Bに示されるように、垂直方向において、リン濃度（曲線120）は、導波路の上部および底部近くでボロン（曲線110）を上回り、一方ボロン濃度は、導波路の真中近くでリンを上回るため、導波路の真中部分はP型のように見え、一方導波路の上部および底部はN型となる。移相器の左側エッジおよびシリコンスラブの左側を含む領域IIは、ボロン注入にのみさらされるため、P型ドープされる。一方、導波路コアの右側エッジおよびシリコンスラブの右側を含む領域IIIは、リン注入にのみさらされるため、N型ドープされる。領域IIおよびIIIは、接合領域と電極を接続する電気経路として働く。アニール後、接合線は、N型ドープ領域とP型ドープ領域の間に形成され、導波路の中心を取り巻く。

20

## 【0029】

[0055]注入の設計では、いくつかの重要な事実が考慮に入れられる。まず第1に、RTAステップにおいて、リン原子が表面偏析により $\text{Si}/\text{SiO}_2$ 表面にトラップされ得ることが報告されている。この効果は、リンドーズ量の損失、したがって導波路の上部近くでリン濃度の減少を引き起こす。我々の設計では、低エネルギーのリン注入ステップのドーズ量を意図的に増加させて表面偏析を補償し、シリコンリップの上部が確実にN型になるようとする。第2に、P/Nのオーバラップした領域のために、ボロンおよびリンの注入によるダメージが蓄積する。注入ステップ後の蓄積されたダメージをシリコン非結晶質しきい値の $5 \times 10^{21}/\text{cm}^3$ 未満に維持することが重要である。そうでなければ、シリコン層は非晶質化され、アニールステップで治すのが困難となり、余分な光損失を引き起こす。

30

## 【0030】

[0056]前述の議論から、ボロンおよびリンの深さ分布は、この設計を実施するために重要な考慮すべき点である。S字形の接合線を確実にするために、ボロンおよびリンの注入がオーバラップする領域に異なる深さの2つのPN接合を形成しなければならない。注入実験を行ってプロファイル設計を確認した。注入実験では、ボロンおよびリンは、いかなるマスクを行なうことなく $220\text{nm}$ の厚さの上部シリコン層および $10\text{nm}$ の厚さのスクリーニング $\text{SiO}_2$ 層を有するSOIウェーハに均一に注入された。エッチングステップを行わずに導波路構造を画成し、深さドーピングプロファイルの測定をより容易にした。注入およびアニールステップは、表1にリストされるものと同一である。アニール後、 $10\text{nm}$ のスクリーニング $\text{SiO}_2$ 層を除去した。二次イオン質量分析法(SIMS: Secondary Ion Mass Spectrometry)解析を行い、ボロンおよびリンの濃度を深さの関数として特徴づけた。ボロンおよびリンのプロファイルは、SIMSデータを図2Aに示すような複数のピークのガウス関数でフィッティングすることによって抽出された。急速に変わる表面の化学作用が不安定なイオン収率をもたらすた

40

50

め、シリコンの上面近く（約20nm）のSIMSデータは不正確である。そのため、これらのデータポイントは、フィッティングから除外された。SIMS測定された正味のドーピングプロファイルおよび設計されたプロファイルが、図2Bに示されている。見てはっきりとわかるように、2つのPN接合が表面から約35nmおよび140nmのシリコン中に形成されている。上部領域（0～35nm）および底部領域（140～220nm）は、N型ドープされ、一方中間の領域（35～140nm）は、P型ドープされている。図2Bに示すように、測定されたドーピングプロファイルおよびシミュレートされたドーピングプロファイルは、よく一致している。この深さプロファイルによって、設計されたマスキング窓を有するスラブ導波路に同一の注入レシピが適用されると、所望のS接合幾何学形状を首尾よく形成することができる期待される。

10

#### 移相器の性能

[0057]ここでS接合移相器設計の性能の分析について提示する。移相器にとっての重要なメトリックには、変調効率（ $V_L$ ）、光損失、ならびに接合容量および抵抗など電気的特性が含まれる。ここで、半導体プロセスシミュレーション、電気デバイスシミュレーション、および光学モード解法を組み合わせることによってシリコン移相器の性能を正確に予測するシミュレーション技法を提示する。モデルは、初めに横方向接合シリコン移相器に関して実験的に較正され、次に、S接合移相器設計の性能およびトレードオフを分析するために使用される。

#### シミュレーション方法

[0058]シミュレーションフローは、半導体プロセスシミュレーションから開始する。Sentaurus Process (Synopsys, Inc., 700 East Middlefield Rd., Mountain View, California 94043-4033 U.S.A. から入手可能なモデリングツール)を使用して、移相器作製のエッチング、注入、およびアニールステップをモデリングする。プロセスシミュレーションの最後に、導波路幾何学形状およびドーパントの空間的分布に関する情報を含む仮想移相器モデルを作成する。次に、仮想移相器モデルが、異なるバイアス電圧の下で有限要素半導体デバイスソルバSentaurus Device (Synopsys, Inc., 700 East Middlefield Rd., Mountain View, California 94043-4033 U.S.A. から入手可能なモデリングツール)を使用して解かれる。自由電子および正孔の分布は、電子および正孔の電流連続の方程式に完全に結合されたポアソン方程式を解くことによって得られる。小信号ACシミュレーションを行い、各バイアス電圧で構造の静電容量を抽出する。デバイスシミュレーション中に、以下の物理モデルが使用される。

20

#### 【0031】

1. ドーピング依存および高電界飽和を含む移動度モデル、

2. ドーピング依存寿命を伴うショックレー・リード・ホール再結合、および

3. 不完全なイオン化モデル。

#### 【0032】

[0059]デバイスシミュレーションが完了した後、接合容量および寄生抵抗などの電気的特性が完全に求められる。仮想移相器の変調効率および光学伝搬損を計算するために、光学モードソルバを用いて導波路の横光学モードを計算する。モードソルバは、入力としてシミュレートされた導波路幾何学形状を取り込み、自由キャリアが導波路中に存在しないと仮定する。シリコンの屈折率と比較して、自由キャリアによって引き起こされる屈折率の変化は小さいため（<0.1%）、これはよい近似である。自由キャリアが存在する状態で、1.55μmの波長での屈折率の局所的な変化は、プラズマ分散公式によって予測される。

40

#### 【0033】

$$n(x, y) = -8.8 \times 10^{-22} Ne(x, y) - 8.5 \times 10^{-18} N_h(x, y) = 8.5 \times 10^{-18} Ne(x, y) + 6.0 \times 10^{-18} N_h$$

50

( x , y ) ( 1 )

ここで  $N_e(x, y)$  および  $N_h(x, y)$  は、デバイスシミュレーションから得られる自由電子および正孔の寄与である。導波路の断面の屈折率および光損失の局所的な変化がわかると、導波路の実効屈折率および光損失の全体的な変化を、モード摂動理論を適用することによって導き出すことができる（例えば、Baehr-Jones, T. ; Hochberg, M. ; Walker, C ; Eric Chan ; Koshinz, D. ; Krug, W. ; Scherer, Axel, "Analysis of the tuning sensitivity of silicon-on-insulator optical ring resonators," Lightwave Technology, Journal of, vol. 23, no. 12, pp. 4215, 4221 参照）。結果として、次式が得られる。

【 0 0 3 4 】

【 数 1 】

$$\Delta n_{eff} = \frac{n_{si} \iint_{si} \Delta n(x, y) |\vec{E}(x, y)|^2 dx dy}{Z_0 \iint_{si} \text{Re}(\vec{E} \times \vec{H}^*) dx dy}$$

$$\Delta \alpha = \frac{n_{si} \iint_{si} \Delta \alpha(x, y) |\vec{E}(x, y)|^2 dx dy}{Z_0 \iint_{si} \text{Re}(\vec{E} \times \vec{H}^*) dx dy} \quad (2)$$

【 0 0 3 5 】

[0060] ここで、 $n_{si} = 3.48$  は、 $1.55 \mu m$  での結晶シリコンの屈折率を表わし、 $Z_0 = 377$  は、自由空間のインピーダンスを表わす。 $E(x, y)$  および  $H(x, y)$  は、摂動を受けてない導波路の横モデルプロファイルである。重なり積分 (2) を実行した後、実効屈折率および光損失の変化は、電極に印加されたバイアス電圧の関数のみであり、このことは、自由電子および正孔の分布に暗黙に含まれていることに留意されたい。実効屈折率の変化は、移相器の変調効率の性能指標  $V_L$  に容易に変換され得る。 - 0.5 V ~ 0.5 V の小信号  $V_L$  の定義に従う。

【 0 0 3 6 】

[0061] 移相器のモデリングにおいて、不完全なイオン化 (I.I) が重要な役割を果たすことに言及する価値がある。室温では、ドーパントのほとんど 100 % が注入後に電気的に活性化されても、ドーパント原子のごく一部はイオン化されない。これは、フェルミ統計の結果である。基本的に、シリコンが多量にドープされ、フェルミ準位が不純物エネルギー準位に近くなると、ドナー／アクセプタのステートの一部は、電子／正孔によってそれぞれ占有され、その結果、これらのステートは、もはやドナー／アクセプタとして働かない。 $1E18 (1 \times 10^{18})$  に近いドーピングレベルに対しては、ドーパントの約 80 % のみが室温でイオン化され、（例えば、Altermatt, P. P. ; Schenk, A. ; Schmitthuesen, B. ; Heiser, G. , "A simulation model for the density of states and for incomplete ionization in crystalline silicon. II. Investigation of Si:As and Si:B and usage in device simulation," Journal of Applied Physics , vol. 100, no. 11, pp. 113715, 113715-7, Dec. 2006 参照）、このことは、自由キャリア濃度が、通常仮定されるもの (100 % のイオン化) よりも 20 % 低い可能性があり、その結果 I.I のないモデルが実験から逸脱する原因となることを意味する。

【 0 0 3 7 】

10

20

30

40

50

[0062]興味深いことに、ドープされたシリコンのP N接合静電容量および導電率などの一部の電気的性質は、I . I .によって影響を受けない。接合容量については、空乏領域のフェルミ準位が不純物準位からはるか遠くにあるため、本質的に、100%のイオン化が起こる。したがって、空乏幅はI . I .によって影響を受けない。導電率については、I . I .の効果は、測定される移動度の値に吸収され、したがって、キャリア濃度に対する補正は必要でない。

#### シミュレーションモデルの較正

[0063]上で提示されたモデリング技法の精度を確認するために、横方向P N接合に基づいたシリコン移相器を作製した。V L、光損失、および接合容量が、実験的に測定され、シミュレーションモデルと比較される。

10

#### 【0038】

[0064]移相器は、220nmの上部シリコンおよび2μmのBOXを有するSOIウェーハ上に作製された。500nm幅の導波路が、帯状荷重領域に90nm厚のシリコン層を残して、異方性の部分シリコンエッチングによってパターニングされ、形成された。次いで、右半分をフォトレジストによってカバーした状態で導波路にポロンが注入された。同様に、左半分をカバーした状態で導波路の右半分にリンが注入された。横方向P N接合は、P側に $2 \times 10^{18} / \text{cm}^3$ およびN側に $3 \times 10^{18} / \text{cm}^3$ のほぼ均一のドーピング濃度を有するように設計される。次いで、全体構造が以前に述べたものと同様のRTAステップでアニールされた。注入ステップおよびRTAステップの詳細は、表2にリストされている。

20

#### 【0039】

#### 【表2】

表2：横方向接合移相器の注入およびアニール条件

| ステップ | 種     | エネルギー/<br>KeV | ドーズ量 / cm <sup>2</sup> | 注入窓     | 傾斜角 |

|------|-------|---------------|------------------------|---------|-----|

| 1    | Boron | 10            | $1.2 \times 10^{13}$   | (-1, 0) | 0   |

| 2    | Boron | 35            | $3.0 \times 10^{13}$   | (-1, 0) | 0   |

| 3    | Phos  | 40            | $2.5 \times 10^{13}$   | (0, 1)  | 0   |

| 4    | Phos  | 135           | $6.0 \times 10^{13}$   | (0, 1)  | 0   |

| 5    | RTA   |               | 1030°C                 | 5s      |     |

30

#### 【0040】

[0065]移相器の性能について2つのタイプの構造に基づいて実験的に特徴づけられた。第1に、移相器が両方のアームに装荷された不平衡マッハツエンダー干渉計を使用して、移相器のV Lおよび接合容量を測定した。DC位相偏移は、MZの一方のアームにバイアス電圧を印加し、透過スペクトルの変化を記録することによって測定される。移相器の接合容量は、T . Bae hr - Jones , R . Ding , Y . Liu , A . Ayazi , T . Pinguet , N . C . Harris , M . Streshinsky , P . Lee , Y . Zhang , A . E . Lim , T . Y . Liow , S . H . Teo , G . Q . Lo , and M . Hochberg , "Ultralow drive voltage silicon traveling-wave modulator , " Opt . Express 20 ( 11 ) , 12014 - 12020 ( 2012 ) に記載された方法と同様に、MZIおよび金属非埋込み構造に関するS11パラメータの位相によって決定される。電極を有する単一の移相器構造を作製し、異なるバイアス電圧で光損失を特徴づけた。同一の導波路長を有するがP / N注入のない制御構造がリファレンスとして同時に測定される。

40

#### 【0041】

[0066]テスト結果およびシミュレーションモデルとの比較が図3A～図3Dに提示されている。図3Aに示される例は、図1Aおよび図4Aに描かれるような数100ナノメートルではなく数10ナノメートルのオーバラップを有する非平面の領域を有したテストプ

50

ロファイルである。モデリングが測定されたデータとどのくらいよく合うかを決定するために、測定することができ、モデリングすることができるサンプルを提供するためにこのテスト構造が作製された。

#### 【0042】

[0067]図3Bは、測定された、およびシミュレートされた位相偏移をバイアス電圧の関数として示すグラフである。

[0068]図3Cは、測定された、およびシミュレートされた接合容量をバイアス電圧の関数として示すグラフである。

#### 【0043】

[0069]図3Dは、測定された、およびシミュレートされた動的損失をバイアス電圧の関数として示すグラフである。

[0070]PN接合は、プロットでは正バイアス電圧に対して逆バイアスされている。見てわかるように、予測された位相偏移効率は、実験データと非常によく一致している。我々のモデルでは、不完全なイオン化のため、予測された位相偏移が15%だけ低いことに気付く。この予測された位相偏移は、この補正の結果、測定されたデータとほぼ完全に一致する。わずかな食い違いは、他のメトリックにおいて見られ、光損失（動的および静的の両方）は、予想を約22%上回り、静電容量は、予想を18%下回る。

#### S接合性能分析

[0071]移相器の性能は、較正されたモデルに基づいて分析される。我々の調査は、移相器のメトリックに対する導波路幅およびオーバラップ比の影響に焦点を当てた。導波路幅および注入オーバラップ比を調整することによって、移相器のV<sub>L</sub>、損失、および帯域幅は、異なるタイプのデバイスの要求を満たすように容易に調整され得ることを示す。ここで報告される最終的な接合性能は、観察データと比較されたシミュレーション結果から較正されるように、モデルよりも光損失が22%高く、静電容量が18%低いと仮定することによって、上で提示されたモデルから推定される。

#### 【0044】

[0072]移相器の構成は、図4Aに示されている。リブ導波路の幅は、Wであり、スラブ高さは、90nmである。異なる実施形態において、Wは、500nm、600nm、700nmおよび800nmであった。注入のオーバラップは、D（ボロンおよびリンの注入マスクによって画成される）である。Dは、Wよりも少なくとも100nm小さくなるように維持され、導波路では少なくとも50nmの、P型およびN型がドープされるマージンを確保する。1.5E19の濃度をターゲットとする中程度の注入P+およびN+が導電率を改善するためにスラブシリコンに施される。P+およびN+注入は、余分な光損失を低減させるために導波路のエッジから200nm離れて配置される。電極は、導波路から700nm離れて配置される。

#### 【0045】

[0073]図4B～図4Eは、異なる導波路幅Wおよびオーバラップ比D/Wについて移相器のシミュレートされた性能を示す。それぞれの導波路幅について、変調効率V<sub>L</sub>および光損失は、オーバラップする割合が増加するとともに減少する。600nmの導波路については、0.8のオーバラップ比に対して0.3V.cmのV<sub>L</sub>および20dB/cmの損失が達成されている。注入のオーバラップする長さが長いほど、結果としてPN接合領域が大きくなり、したがって光学モードとのより強い相互作用が生じるため、これは予想通りである。同じオーバラップ比に対しては、光学モードが導波路のコアにより集中されるため、導波路の幅が広いほどより低いV<sub>L</sub>値を有するように見える。光損失は、オーバラップ比が増加するとともに、減少する。これは、オーバラップ領域では、P型およびN型のドーパントが互いに補償し合い、結果として実効的なドーピングレベルが低くなり、光損失が低減するためである。図4Aに見られるように、オーバラップ領域または非平面の接合界面は、英文字「C」または英文字「U」のように見えてもよい。図4Aでは、p型領域は、非平面の接合界面の凹面側にあり、n型領域は、非平面の接合界面の凸面側にある。n型領域が非平面の接合の凹面側にあり、p型領域が非平面の接合の凸面側

10

20

30

40

50

にある同様の p n 接合、例えば、図 4 A に示されるものと反対方向に湾曲した非平面の接合界面を構築することも可能であると思われる。他の実施形態では、英文字「 S 」の形状を有する非平面の接合を作製することができる。

#### 【 0 0 4 6 】

[0074] 移相器の固有の帯域幅は、接合容量および直列抵抗によって推定され、 $f_{3dB} = 1 / (2RC)$  である。接合容量は、S e n t a u r u s D e v i c e において小信号 A C シミュレーションによって得られ、直列抵抗は、シリコンスラブおよび導波路コアの周縁領域の抵抗を加えることによって推定される。結果として得られた固有の帯域幅が、図 4 E にプロットされている。図 4 D で見てわかるように、導波路幅およびオーバラップ比が増加するとともに、帯域幅は、主として静電容量の増加のため、相当減少する。600 nm の導波路幅および 0.8 のオーバラップ比に対して、42 GHz の注目すべき固有の帯域幅をなおも得ることができる。必要な場合は、より高い帯域幅を容易に達成することができる。

10

#### 【 0 0 4 7 】

[0075] 図 4 B および図 4 C にそれぞれ目を向けると、推定された 0.3 V. cm の低い V<sub>L</sub>、および 20 dB / cm の光損失は、極めて高解像度のインターディジテーションを必要としない幾何学形状に対して、現在の記録 0.62 V. cm、36 dB / cm を両方の面で超える著しい改善である。

20

#### 【 0 0 4 8 】

[0076] S 接合形状に基づいた新しいシリコン変調幾何学形状について説明した。表面偏析および不完全なイオン化などの二次効果を含めることによって、ドーパント分布における高ドーパント濃度および微細構造を有する領域において完全に正確となるように、シリコン p n 接合幾何学形状のモデリングに対する典型的な手法を較正する必要があることを示した。我々の説明した幾何学形状およびモデリングの手法は両方とも当業者に役に立つと思われる。

20

#### 応用例

[0077] 図 5 A は、本発明の原理によって作製されたデバイスを使用して構築されたマッハツエンダー干渉計の図である。図 5 A において、説明した移相器を使用するマッハツエンダー干渉計 ( M Z I ) 変調器は、左の導波路からの光入力部 ( 光学入力部 510 ) および右からの出力部 ( 光学出力部 530 ) を有する。移相器 520 は、両方のアームに装荷されている。

30

#### 【 0 0 4 9 】

[0078] 図 5 B は、N および P の注入が導波路の中心でオーバラップする移相器に対する詳細なドーピングマスクを示す図面である。

30

[0079] 図 5 C は、図 5 B のドーピングマスクの一部についてのより詳細な図を示す図面である。

#### 【 0 0 5 0 】

[0080] 図 5 D は、導波路の中心における層の寸法を示す図面である。本図面に提示された寸法は、好ましい実施形態における典型的な寸法である。

40

[0081] 図 6 は、本発明の原理により作製されたデバイスを使用して構築されたリング変調器の図である。図 6 では、( 図示される実施形態では円形の形状構成を有する ) 移相器に電気信号を伝えるための電気パッドが示されている。移相器内を循環する光は、電気パッドにおいて提供される電気信号によって変調され得る。移相器と光通信する光導波路の両端部に光入力ポートおよび光出力ポートが示されている。光学入力ポートに入った光は移相器を通過し、エバネッセント波によって移相器内を循環する変調された光と相互作用し、それによって、光学入力ポートから入った光を変調する。変調された光は、光学出力ポートから出て、送信され、さもなければ変調器の外部で使用されてもよい。

#### 定義

[0082] 本明細書においてその他の方法で明示的に列挙されていない限り、電子信号または電磁信号 ( またはそれらの均等物 ) に対するいかなる言及も、非一時的な電子信号また

50

は非一時的な電磁信号を指すものと理解されるべきである。

【0051】

[0083]動作またはデータ収集の結果を記録すること、例えば、特定の周波数または波長で記録することなどは、本明細書では記憶素子、機械可読記憶媒体、または記憶装置に非一時的なやり方で出力データを書き込むことを意味すると理解され、規定される。本発明で使用することができる非一時的な機械可読記憶媒体は、電子、磁気および/または光記憶媒体、例えば、磁気フロッピー（登録商標）ディスクおよびハードディスク、一部の実施形態ではDVDディスク、CD-ROMディスク（すなわち、読み出し専用光記憶ディスク）、CD-Rディスク（すなわち、一回書き込み、多数回読み出し光記憶ディスク）およびCD-RWディスク（すなわち、書き換え可能光記憶ディスク）のいずれかを用いることができるDVD駆動装置、CD駆動装置、RAM、ROM、EPROM、コンパクトフラッシュ（登録商標）カード、PCMciaカードまたは代替としてSDもしくはSDIOメモリなどの電子記憶媒体、ならびに記憶媒体を収容し、記憶媒体を読み取るおよび/または記憶媒体に書き込む電子構成部品（例えば、フロッピー（登録商標）ディスク駆動装置、DVD駆動装置、CD/CD-R/CD-RW駆動装置もしくはコンパクトフラッシュ（登録商標）/PCMcia/SDアダプター）を含む。その他の方法で明示的に列挙されない限り、「記録」または「記録する」に対する本明細書におけるいかなる言及も、非一時的な記録または非一時的に記録することを指すものと理解される。

10

【0052】

[0084]機械可読記憶媒体の当業者には知られているように、データ記憶のための新しい媒体およびフォーマットは、絶えず考案されており、特に、より大きな記憶容量、より速いアクセス速度、より小さなサイズ、および記憶される情報の単位ビット当たりのより低いコストのいずれかが提供される場合、将来利用可能になる可能性のある任意の都合のよい市販の記憶媒体および対応する読み書きデバイスが、使用するのに適切になると思われる。よく知られている、より古い機械可読媒体、例えば、穿孔紙テープもしくはカード、テープもしくはワイヤへの磁気記録、印刷された文字（例えば、OCRおよび磁気的にコード化された記号）ならびに一次元および二次元バーコードなどの機械可読記号の光学または磁気読み取りも、ある一定の条件の下で使用するのに利用可能である。後で使用するために画像データの記録（例えば、メモリまたはディジタルメモリへの画像の書き込み）を行うことができ、記録情報を出力として、ユーザへの表示用データとして、または後で使用するために利用可能になるデータとして使用することができる。そのようなディジタルメモリ素子またはチップは、スタンドアロンのメモリデバイスであってもよく、または対象とするデバイス内部に組み込まれてもよい。「出力データの書き込み」または「メモリへの画像の書き込み」は、本明細書ではマイクロコンピュータ内部のレジスタに変換されたデータを書き込むことを含むとして規定される。

20

30

【0053】

[0085]「マイクロコンピュータ」は、本明細書ではマイクロプロセッサ、マイクロコントローラおよびデジタル信号プロセッサ（「DSP」）と同義なものとして、規定される。例えば、「ファームウェア」としてコード化されたデータ処理のための命令を含む、マイクロコンピュータによって使用されるメモリは、マイクロコンピュータチップの内部のメモリに物理的に、マイクロコンピュータ外部のメモリに、または内部および外部のメモリを組み合わせたものに存在することができると理解される。同様に、アナログ信号は、スタンドアロンのアナログデジタル変換器（「ADC」）または1つまたは複数のADCによってデジタル化されてもよく、あるいは多重化されたADCチャネルがマイクロコンピュータパッケージ内部に存在してもよい。また、フィールド・プログラマブル・アレイ（「FPGA」）チップまたは特定用途向け集積回路（「ASIC」）チップは、ハードウェアロジック、マイクロコンピュータのソフトウェアエミュレーションにおいて、またはこの2つの組合せによって、マイクロコンピュータの機能を行うことができると理解される。本明細書に記載された発明性のある特徴のいずれかを有する装置は、完全に1つのマイクロコンピュータ上で動作することができ、または2つ以上のマイクロコンピ

40

50

ュータを含むことができる。

【0054】

[0086] 本明細書による計測の制御、信号の記録、および信号またはデータの分析に有用な汎用のプログラマブルコンピュータは、パーソナルコンピュータ（P C）、マイクロプロセッサベースのコンピュータ、ポータブルコンピュータ、または他のタイプの処理デバイスのいずれかであってもよい。汎用のプログラマブルコンピュータは、典型的には、中央処理ユニット、機械可読記憶媒体を使用して、情報およびプログラムを記録し読み取ることができる記録またはメモリユニット、有線通信デバイスまたは無線通信デバイスなどの通信端末、ディスプレイ端末など出力デバイス、ならびにキーボードなどの入力デバイスを備える。ディスプレイ端末は、タッチスクリーンディスプレイであってもよく、その場合、ディスプレイ端末はディスプレイデバイスおよび入力デバイスの両方として機能することができる。マウスもしくはジョイスティックといったポインティングデバイスなどの異なるおよび／または追加の入力デバイスが存在してもよく、発音装置、例えばスピーカ、第2のディスプレイ、もしくはプリンタなどの異なるまたは追加の出力デバイスが存在してもよい。コンピュータは、様々なオペレーティングシステムのいずれか1つ、例えば、いくつかのバージョンのWindows（登録商標）、Mac OS、またはUNIX（登録商標）、あるいはLinuxのいずれか1つを実行することができる。汎用コンピュータの動作で得られた計算結果は、後で使用するために記憶されてもよく、および／またはユーザに表示されてもよい。少なくとも、マイクロプロセッサに基づく汎用コンピュータそれぞれは、マイクロプロセッサ内部にそれぞれの計算ステップの結果を記憶するレジスタを有し、その場合、これらの結果は、後で使用するためにキャッシュメモリに通常記憶され、それによって結果が表示され、不揮発性メモリに記録され、またはさらなるデータ処理もしくは分析において使用されることがある。

【0055】

[0087] 電気および電子装置の多くの機能は、ハードウェア（例えば、ハードワイヤードロジック）で、ソフトウェア（例えば、汎用プロセッサ上で動作するプログラムにコード化されたロジック）で、およびファームウェア（例えば、必要に応じてプロセッサ上で動作するために呼び出される不揮発性メモリにコード化されたロジック）で実施されてもよい。本発明は、ハードウェア、ファームウェアおよびソフトウェアの1つの実施態様を、ハードウェア、ファームウェアおよびソフトウェアの別の1つを使用する等価な機能性の別の実施態様の代替とすることが意図されている。実施態様を伝達関数によって数学的に表わすことができる、すなわち、伝達関数を表わす「ブラックボックス」の入力端子に印加された特定の刺激に対して指定された応答が出力端子で生成される限り、伝達関数の一部もしくはセグメントを実施するハードウェア、ファームウェアおよびソフトウェアの任意の組合せを含む、伝達関数の任意の実施態様が、実施態様の少なくとも一部がハードウェアで行われる限り、本明細書で意図されている。

理論的な議論

[0088] 本明細書で提供される理論的な説明は正確であると思われるが、本明細書に記載され、特許請求されるデバイスの動作は、理論的な説明の正確さまたは妥当性に依存しない。すなわち、観察された結果を、本明細書に提示された理論と異なる根拠に基づいて説明することができる将来の理論的な展開は、本明細書に記載される本発明を損ねることはないであろう。

【0056】

[0089] いかなる特許、特許出願、特許出願公開、雑誌記事、本、出版された論文、または本明細書で識別される他の公に利用可能な資料も、その全体が参照により本明細書に組み込まれる。参照により本明細書に組み込まれているとは言うものの、本明細書に明示的に述べられている既存の定義、記述、または他の開示資料と矛盾するいかなる資料、またはその一部も、組み込まれている資料と本開示資料との間に矛盾が生じない限り、単に組み込まれる。矛盾する場合は、その矛盾は、本開示を優先して好ましい開示として解決されるものとする。

10

20

30

40

50

## 【 0 0 5 7 】

[0090]図面で示されるような好ましいモードを参照して本発明について具体的に示し説明したが、特許請求の範囲によって規定されるような本発明の趣旨および範囲から逸脱せずに細部における様々な変更がなされてもよいことが当業者には理解されるだろう。

【 図 1 A 】

【 図 1 B 】

【図2A】

【図2B】

【図3A】

【図3B】

【図3C】

【図 3 D】

FIG. 3D

【図 4 A】

FIG. 4A

【図 4 B】

FIG. 4B

【図 4 D】

FIG. 4D

【図 4 C】

FIG. 4C

【図 4 E】

FIG. 4E

【図 5 A B C】

FIG. 5A

【図 5 D】

FIG. 5D

FIG. 5B

FIG. 5C

【図 6】

FIG. 6

## 【国際調査報告】

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                    |                                                                                         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| <b>INTERNATIONAL SEARCH REPORT</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                    | International application No.<br>PCT/US 2013/066134                                     |

| <b>A. CLASSIFICATION OF SUBJECT MATTER</b><br><i>G02F 1/025 (2006.01)<br/>H01L 21/02 (2006.01)</i><br>According to International Patent Classification (IPC) or to both national classification and IPC                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                    |                                                                                         |

| <b>B. FIELDS SEARCHED</b><br>Minimum documentation searched (classification system followed by classification symbols)<br><b>G02F 1/025, 1/03, H01L 21/00, 21/336, 21/8234, 27/088</b>                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                    |                                                                                         |

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                    |                                                                                         |

| Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)<br><b>PatSearch (RUPTO internal), USPTO, PAJ, Esp@cenet, DWPI, EAPATIS, PATENTSCOPE, Information Retrieval System of FIPS</b>                                                                                                                                                                                                                                                                                                                                                |                                                                                    |                                                                                         |

| <b>C. DOCUMENTS CONSIDERED TO BE RELEVANT</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                    |                                                                                         |

| Category*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Citation of document, with indication, where appropriate, of the relevant passages | Relevant to claim No.                                                                   |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | US 5771257 A (MITSUBISHI DENKI KABUSHIKI KAISHA) 23.06.1998                        | 1-15                                                                                    |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | JP 2001358153 A (FUJI ELECTRIC CO LTD) 26.12.2001                                  | 1-15                                                                                    |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | US 6556610 B1 (E20 COMMUNICATIONS, INC.) 29.04.2003                                | 1-15                                                                                    |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | US 2006/0024066 A1 (MASAMICHI FUJIWARA et al.) 02.02.2006                          | 1-15                                                                                    |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | GB 1463886 A (HUGHES AIRCRAFT COMPANY) 09.02.1977                                  | 1-15                                                                                    |

| <input type="checkbox"/> Further documents are listed in the continuation of Box C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                    | <input type="checkbox"/> See patent family annex.                                       |

| * Special categories of cited documents:<br>"A" document defining the general state of the art which is not considered to be of particular relevance<br>"E" earlier document but published on or after the international filing date<br>"L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)<br>"O" document referring to an oral disclosure, use, exhibition or other means<br>"P" document published prior to the international filing date but later than the priority date claimed |                                                                                    |                                                                                         |

| Date of the actual completion of the international search<br><b>19 March 2014 (19.03.2014)</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                    | Date of mailing of the international search report<br><b>24 April 2014 (24.04.2014)</b> |

| Name and mailing address of the ISA/ FIPS<br>Russia, 123995, Moscow, G-59, GSP-5,<br>Berezovskaya nab., 30-1<br>Facsimile No. +7 (499) 243-33-37                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                    | Authorized officer<br><b>E. Rodionova</b><br>Telephone No. 499-240-25-91                |

---

フロントページの続き

(81)指定国 AP(BW,GH,GM,KE,LR,LS,MW,MZ,NA,RW,SD,SL,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,RU,TJ,TM),EP(AL,AT,BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,HR,HU,IE,IS,IT,LT,LU,LV,MC,MK,MT,NL,NO,PL,PT,RO,R,S,SE,SI,SK,SM,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,KM,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AO,AT,AU,AZ,BA,BB,BG,BH,BN,BR,BW,BY,BZ,CA,CH,CL,CN,CO,CR,CU,CZ,DE,DK,DM,DO,DZ,EC,EE,EG,ES,FI,GB,GD,GE,GH,GM,GT,HN,H,R,HU,ID,IL,IN,IR,IS,JP,KE,KG,KN,KP,KR,KZ,LA,LC,LK,LR,LS,LT,LU,LY,MA,MD,ME,MG,MK,MN,MW,MX,MY,MZ,NA,NG,NI,NO,NZ,OM,PA,PE,PG,PH,PL,PT,QA,RO,RS,RU,RW,SA,SC,SD,SE,SG,SK,SL,SM,ST,SV,SY,TH,TJ,TM,TN,TR,TT,TZ,UA,UG,US

(特許庁注：以下のものは登録商標)

1. Linux

(74)代理人 100119781

弁理士 中村 彰吾

(72)発明者 リウ, ヤーン

アメリカ合衆国デラウェア州 19711, ニューアーク, ウェッジウッド・ロード 115

(72)発明者 バエルジョーンズ, トム

アメリカ合衆国デラウェア州 19711, ニューアーク, ウェッジウッド・ロード 115

F ターム(参考) 2K102 AA17 BA02 BB01 BB04 BC04 CA28 DA02 DA05 DB02 DB04

DD03 DD09 EA02