(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2018년06월20일

(11) 등록번호 10-1853754

(24) 등록일자 2018년04월25일

- (51) 국제특허분류(Int. Cl.)

*H01L 25/065* (2006.01)

- (21) 출원번호 10-2013-7005325

- (22) 출원일자(국제) 2011년08월04일

심사청구일자 2016년04월08일

- (85) 번역문제출일자 2013년02월28일

- (65) 공개번호 10-2013-0136446

- (43) 공개일자 2013년12월12일

- (86) 국제출원번호 PCT/US2011/046519

- (87) 국제공개번호 WO 2012/030470

국제공개일자 2012년03월08일

- (30) 우선권주장

12/874,446 2010년09월02일 미국(US)

- (56) 선행기술조사문헌

JP05211281 A\*

JP2006032875 A\*

JP2002009221 A\*

\*는 심사관에 의하여 인용된 문헌

전체 청구항 수 : 총 18 항

심사관 : 곽혁용

(54) 발명의 명칭 고정 벤드를 구비한 램프 스택 칩 패키지

**(57) 요약**

램프 스택 칩 패키지가 설명된다. 이 칩 패키지는 수평 방향으로 서로 오프셋된 반도체 다이 또는 칩들의 수직 스택을 포함하며, 이로써 노출된 패드를 구비한 테라스(terrace)를 정의한다. 테라스에 대략 평행하게 위치하는 고대역폭 램프 컴포넌트는 노출된 패드에 전기적으로 및 기계적으로 결합된다. 예를 들어, 램프 컴포넌트는 솔더(solder), 마이크로스프링(microspring), 및/또는 이방성 도전 필름(anisotropic conducting film)을 사용하여 반도체 다이들에 결합될 수 있다. 또한, 반도체 다이 각각은 반도체 다이 각각의 엔드 세그먼트가 그 방향에 평행하며, 램프 컴포넌트에 기계적으로 결합되도록 고정 벤드를 포함한다. 이들 엔드 세그먼트는 예를 들어, 근접 통신(proximity communication)을 통해 칩들과 램프 컴포넌트 사이의 신호의 고대역폭 통신을 용이하게 할 수 있다.

**대 표 도**

## 명세서

### 청구범위

#### 청구항 1

칩 패키지로서,

수직 스택 내의 제1 반도체 다이에 실질적으로 직각인 수직 방향으로 상기 수직 스택에 배열된 반도체 다이들의 세트 - 상기 제1 반도체 다이 뒤의 각각의 반도체 다이는 상기 수직 스택에서 바로 앞의 반도체 다이로부터 오프셋 값만큼 수평 방향으로 오프셋되어, 상기 수직 스택의 일측에 계단형 테라스(stepped terrace)를 정의함 -; 및

상기 반도체 다이들에 전기적으로 그리고 단단히(rigidly) 기계적으로 결합된 램프 컴포넌트(ramp component) - 상기 램프 컴포넌트는 상기 수직 스택의 일측에 위치함 -

를 포함하고,

상기 램프 컴포넌트는 상기 수평 방향과 상기 수직 방향 사이의 상기 계단형 테라스를 따른 방향에 평행하고,

상기 반도체 다이들 각각은, 상기 반도체 다이들 각각의 엔드 세그먼트가 상기 계단형 테라스를 따른 방향에 평행하며 상기 램프 컴포넌트에 기계적으로 결합되도록 고정 벤드(static bend)를 포함하고,

상기 램프 컴포넌트는, 용량성 결합 근접 통신(capacitively coupled proximity communication)을 이용하여 상기 반도체 다이들 각각의 엔드 세그먼트와 상기 램프 컴포넌트 사이에 전기 신호들을 전기적으로 결합하도록 구성되는 칩 패키지.

#### 청구항 2

제1항에 있어서,

상기 고정 벤드와 연관된 상기 반도체 다이들 각각에서의 응력은 상기 반도체 다이의 항복 강도(yield strength) 미만인 칩 패키지.

#### 청구항 3

제1항에 있어서,

상기 반도체 다이들 각각의 두께는, 상기 반도체 다이들 각각이 상기 고정 벤드를 용이하게 하는 벤딩 모멘트(bending moment)를 갖도록 정의되는 칩 패키지.

#### 청구항 4

제1항에 있어서,

상기 램프 컴포넌트는 상기 반도체 다이들 각각에 솔더링되는 칩 패키지.

#### 청구항 5

제1항에 있어서,

상기 램프 컴포넌트는 마이크로스프링들에 의해 상기 반도체 다이들 각각의 엔드 세그먼트에 전기적으로 결합되는 칩 패키지.

#### 청구항 6

제1항에 있어서,

상기 램프 컴포넌트는 솔더에 의해 상기 반도체 다이들 각각의 엔드 세그먼트에 전기적으로 결합되는 칩 패키지.

### 청구항 7

제1항에 있어서,

상기 램프 컴포넌트는 이방성 도전 필름(anisotropic conductive film)에 의해 상기 반도체 다이들 각각의 엔드 세그먼트에 전기적으로 결합되는 칩 패키지.

### 청구항 8

제1항에 있어서,

상기 램프 컴포넌트는,

상기 계단형 테라스에 평행한 방향을 따라 광학 신호를 운반하도록 구성된 광도파로; 및

광학 결합 요소들의 세트 - 광학 결합 컴포넌트들의 세트 내의 주어진 광학 결합 컴포넌트는, 상기 반도체 다이들의 세트 내의 주어진 반도체 다이의 엔드 세그먼트에 상기 광학 신호를 광학적으로 결합하도록 구성됨 - 를 포함하는 칩 패키지.

### 청구항 9

제8항에 있어서,

상기 광학 결합 요소들의 세트 내의 광학 결합 요소들은 광학-전기 트랜스듀서들(optical to electrical transducers)을 포함하는 칩 패키지.

### 청구항 10

삭제

### 청구항 11

제1항에 있어서,

상기 반도체 다이들 각각의 엔드 세그먼트의 표면은 에치 피트(etch pit)를 포함하고,

상기 반도체 다이들의 에치 피트들 각각에 대해, 상기 램프 컴포넌트는 대응하는 에치 피트를 포함하고,

상기 칩 패키지는 볼들의 세트를 더 포함하며, 상기 볼들의 세트 내의 주어진 볼은 상기 엔드 세그먼트의 표면에서의 에치 피트와 상기 램프 컴포넌트에서의 대응하는 에치 피트를 기계적으로 결합하는 칩 패키지.

### 청구항 12

칩 패키지를 포함하는 전자 컴퓨팅 디바이스로서,

상기 칩 패키지는,

수직 스택 내의 제1 반도체 다이에 실질적으로 직각인 수직 방향으로 상기 수직 스택에 배열된 반도체 다이들의 세트 - 상기 제1 반도체 다이 뒤의 각각의 반도체 다이는 상기 수직 스택에서 바로 앞의 반도체 다이로부터 오프셋 값만큼 수평 방향으로 오프셋되어, 상기 수직 스택의 일측에 계단형 테라스를 정의함 -; 및

상기 반도체 다이들에 전기적으로 그리고 단단히 기계적으로 결합된 램프 컴포넌트 - 상기 램프 컴포넌트는 상기 수직 스택의 일측에 위치함 -

를 포함하고,

상기 램프 컴포넌트는 상기 수평 방향과 상기 수직 방향 사이의 상기 계단형 테라스를 따른 방향에 평행하고,

상기 반도체 다이들 각각은, 상기 반도체 다이들 각각의 엔드 세그먼트가 상기 계단형 테라스를 따른 방향에 평행하며 상기 램프 컴포넌트에 기계적으로 결합되도록 고정 벤드를 포함하고,

상기 램프 컴포넌트는, 용량성 결합 근접 통신을 이용하여 상기 반도체 다이들 각각의 엔드 세그먼트와 상기 램프 컴포넌트 사이에 전기 신호들을 전기적으로 결합하도록 구성되는 전자 컴퓨팅 디바이스.

### 청구항 13

제12항에 있어서,

상기 고정 벤드와 연관된 상기 반도체 다이들 각각에서의 응력은 상기 반도체 다이의 항복 강도 미만인 전자 컴퓨팅 디바이스.

### 청구항 14

제12항에 있어서,

상기 반도체 다이들 각각의 두께는, 상기 반도체 다이들 각각이 상기 고정 벤드를 용이하게 하는 벤딩 모멘트를 갖도록 정의되는 전자 컴퓨팅 디바이스.

### 청구항 15

제12항에 있어서,

상기 램프 컴포넌트는 상기 반도체 다이들 각각에 솔더링되는 전자 컴퓨팅 디바이스.

### 청구항 16

제12항에 있어서,

상기 램프 컴포넌트는, 마이크로스프링들, 솔더 및 이방성 도전 필름 중 하나에 의해 상기 반도체 다이들 각각의 엔드 세그먼트에 전기적으로 결합되는 전자 컴퓨팅 디바이스.

### 청구항 17

제12항에 있어서,

상기 램프 컴포넌트는,

상기 계단형 테라스를 따른 방향을 따라 광학 신호를 운반하도록 구성된 광도파로; 및

광학 결합 요소들의 세트 - 광학 결합 컴포넌트들의 세트 내의 주어진 광학 결합 컴포넌트는, 상기 반도체 다이들의 세트 내의 주어진 반도체 다이의 엔드 세그먼트에 상기 광학 신호를 광학적으로 결합하도록 구성됨 -

를 포함하는 전자 컴퓨팅 디바이스.

### 청구항 18

제17항에 있어서,

상기 광학 결합 요소들의 세트 내의 광학 결합 요소들은 광학-전기 트랜스듀서들을 포함하는 전자 컴퓨팅 디바이스.

### 청구항 19

삭제

### 청구항 20

신호를 통신하는 방법으로서,

수직 방향으로 수직 스택에 배열되는 반도체 다이들의 세트에 전기적으로 그리고 단단히 기계적으로 결합된 램프 컴포넌트에서 상기 신호를 운반하는 단계 - 상기 반도체 다이들은 수평 방향으로 서로 오프셋되어, 상기 수직 스택의 일측에 계단형 테라스를 정의하며, 상기 램프 컴포넌트는, 상기 수평 방향과 상기 수직 방향 사이의 상기 계단형 테라스를 따른 방향에 평행하게 상기 수직 스택의 일측에 위치함 -; 및

상기 반도체 다이들의 세트 내의 주어진 반도체 다이의 엔드 세그먼트에서 상기 주어진 반도체 다이에 상기 신호를 결합하는 단계 - 상기 주어진 반도체 다이는, 상기 엔드 세그먼트가 상기 계단형 테라스를 따른 방향에 평행하며 상기 램프 컴포넌트에 기계적으로 결합되도록 고정 벤드를 포함함 -

를 포함하는 방법.

## 발명의 설명

### 기술 분야

[0001] 본 발명은 일반적으로 반도체 칩 패키지의 설계에 관한 것이다. 더 구체적으로, 본 발명은 스택 내에 배열된 칩 그룹, 및 스택에 대해 비스듬히 있고 고정 벤드를 포함하는 반도체 다이들의 엔드 세그먼트들에서 칩들과 통신하는 램프 컴포넌트를 포함하는 칩 패키지에 관한 것이다.

### 배경 기술

[0002] 적층형 반도체 칩들(stacked semiconductor chips)을 포함하는 칩 패키지는 인쇄 회로 기판에 연결되는 개별적으로 패키지화된 종래의 칩들에 비해 상당히 높은 성능을 제공할 수 있다. 또한, 이들 칩 패키지는 스택 내의 상이한 칩들에 대해 상이한 공정들을 사용할 수 있고, 고밀도의 로직 및 메모리를 조합할 수 있고, 저전력을 사용하여 데이터를 전송할 수 있는 능력과 같은 여러 이점을 제공한다. 예를 들어, DRAM(dynamic random access memory)을 구현하는 칩들의 스택은 입출력(I/O) 기능과 컨트롤러 기능을 구현하기 위한 베이스 칩에서 높은 금속-층-카운트의 고성능 로직 공정을 사용할 수 있고, 스택의 나머지에 대해서는 낮은 금속-층-카운트의 디램-특수 처리 칩(DRAM-specialized processed chip)들의 세트가 사용될 수 있다. 이러한 방식으로, 조합된 칩 세트는 DRAM 공정을 사용하여 제조된 I/O 기능과 컨트롤러 기능을 포함하는 단일 칩; 로직 공정을 사용하여 제조된 메모리 회로를 포함하는 단일 칩; 또는 로직 구조 및 메모리 물리 구조 모두를 형성하기 위해 단일 공정을 사용하려고 시도함으로써 구성되는 시스템에 비해 성능이 우수하고 비용이 낮다.

[0003] 그러나, 적층형 반도체 칩들 사이에서 저비용, 고성능(예를 들어, 고대역폭)의 상호연결을 획득하는 것은 어려울 수 있다. 예를 들어, 반도체 칩들은 칩들이 서로 오프셋되어 칩 에지의 계단부(staircase)를 정의하는 칩 스택의 표면에 노출된 본드 패드(bond pad)들 사이에서 와이어 본드(wire bond)들을 사용하여 전기적으로 결합될 수 있다. 그러나, 이들 와이어 본드는 저비용 조립 기법을 사용하여 구현될 수 있지만, 최종 와이어 본드들은 통상적으로 낮은 대역폭을 갖는다.

[0004] 반대로, 관통형 실리콘 비아(TSV)들은 통상적으로 와이어 본드보다 대역폭이 높다. TSV 제조 기법에서, 활성면(active face)의 금속층들 중 하나 이상이 후면에 있는 새로운 패드에 전도성 연결되도록 칩들이 처리된다. 그 후, 칩들은 스택에 접착연결되어, 칩의 후면에 있는 새로운 패드들이 인접 칩의 활성면에 있는 대응 패드와 전도성 접촉하도록 한다.

[0005] 그러나, TSV는 통상적으로 와이어 본드보다 비용이 높다. 이는 TSV가 칩의 활성 실리콘층을 관통하기 때문이다. 결과적으로, TSV는 트랜지스터 또는 와이어링에 사용될 수 있었던 영역을 점유한다. 이러한 기회비용은 클 수 있다. 예를 들어, TSV 배제 또는 금지 지름이  $20\text{ }\mu\text{m}$ 이고, TSV가  $30\text{ }\mu\text{m}$  피치에 위치하고 있으면, 실리콘 영역의 약 45%가 TSV에 의해 소모된다. 이는 스택에 있는 칩들의 임의의 회로를 위한 면적당 비용을 거의 2배로 만든다. (실제로, 통상적으로 회로들이 TSV를 수용하기 위해 넓은 공간을 차지하여 더 많은 영역을 소모하기 때문에, 오버헤드는 훨씬 더 클 수 있다.) 또한, TSV의 제조는 보통 추가적인 처리 동작을 수반하며, 이로써 비용이 증가한다.

[0006] 그러므로, 앞서 설명된 문제점 없이 적층된 칩들의 이점들을 제공하는 칩 패키지에 대한 필요성이 있다.

### 발명의 내용

[0007] 본 발명의 일 실시예는 칩 패키지를 제공한다. 이러한 칩 패키지는 수직 스택 내의 제1 반도체 다이에 실질적으로 직각인 수직 방향으로 수직 스택에 배열된 반도체 다이 세트를 포함한다. 또한, 제1 반도체 다이 다음에 있는 각각의 반도체 다이는 수직 스택에서 바로 앞의 반도체 다이로부터 오프셋 값만큼 수평 방향으로 오프셋되며, 이로써 수직 스택의 일측에 계단형 테라스를 정의한다. 또한, 램프 컴포넌트는 반도체 다이에 전기적으로 및 단단히 기계적으로(rigidly mechanically) 결합된다. 이러한 램프 컴포넌트는 수직 스택의 일측에 위치하며, 수평 방향과 수직 방향 사이인 계단형 테라스를 따르는 방향에 대략 평행이다. 또한, 반도체 다이 각각은 반도체 다이 각각의 엔드 세그먼트가 그 방향에 평행하며, 램프 컴포넌트에 기계적으로 결합되도록 고정 벤드(static bend)를 포함한다.

[0008] 고정 벤드와 관련된 반도체 다이 각각에서의 응력은 반도체 다이의 항복 강도 미만일 수 있다는 점에 유의한다.

또한, 반도체 다이 각각의 두께는 반도체 다이 각각이 고정 벤드를 용이하게 하는 벤딩 모멘트(bending moment)를 갖도록 정의될 수 있다.

[0009] 램프 컴포넌트는 다양한 기법을 사용하여 반도체 다이에 전기적으로 결합될 수 있다. 예를 들어, 램프 컴포넌트는 반도체 다이 각각의 엔드 세그먼트에서와 같이 반도체 다이 각각에 솔더링될 수 있다. 다르게 또는 추가적으로, 램프 컴포넌트는 마이크로스프링 및/또는 이방성 도전 필름에 의해 반도체 다이 각각의 엔드 세그먼트에 전기적으로 결합될 수 있다. 또한, 일부 실시예에서, 램프 컴포넌트는 용량성 결합 근접 통신을 사용하여 반도체 다이 각각의 엔드 세그먼트와 램프 컴포넌트 사이에서 전기 신호들을 전기적으로 결합할 수 있다.

[0010] 일부 실시예에서, 램프 컴포넌트는 방향을 따라 광학 신호를 운반하도록 구성된 광도파로; 및 광학 결합 요소 세트를 포함하며, 광학 결합 컴포넌트 세트 내의 주어진 광학 결합 컴포넌트는 반도체 다이 세트 내의 주어진 반도체 다이의 엔드 세그먼트에 광학 신호를 광학적으로 결합할 수 있다. 광학적 결합은 광학 근접 통신을 포함할 수 있다는 점에 유의한다.

[0011] 또한, 칩 패키지에서 컴포넌트들을 정렬하는데 다양한 기법들이 사용될 수 있다. 예를 들어, 반도체 다이 각각의 엔드 세그먼트의 표면은 에치 피트(etch pit)를 포함할 수 있으며, 반도체 다이의 에치 피트들 각각에 대해, 램프 컴포넌트는 대응 에치 피트를 포함한다. 또한, 칩 패키지는 볼 세트를 포함할 수 있는데, 볼 세트 내의 주어진 볼은 엔드 세그먼트의 표면에서의 에치 피트와 램프 컴포넌트에서의 대응 에치 피트를 기계적으로 결합한다.

[0012] 다른 실시예가 칩 패키지를 포함하는 (컴퓨터 시스템과 같은) 전자 디바이스를 제공한다.

[0013] 다른 실시예는 신호를 통신하는 방법을 제공한다. 이 방법에서, 수직 방향으로 수직 스택에 배열된 반도체 다이 세트에 전기적으로 및 단단히 기계적으로 결합된 램프 컴포넌트에서 신호가 운반된다. 반도체 다이들은 수평 방향으로 서로 오프셋되어 수직 스택의 일측에서 계단형 테라스를 정의한다는 점에 유의한다. 또한, 램프 컴포넌트는 수평 방향과 수직 방향 사이인 계단형 테라스를 따르는 방향에 대략 평행하게 수직 스택의 일측에 위치한다. 그러면, 신호는 반도체 다이 세트 내의 주어진 반도체 다이의 엔드 세그먼트에서 주어진 반도체 다이에 결합되는데, 여기서 주어진 반도체 다이는 엔드 세그먼트가 그 방향에 평행하고, 램프 컴포넌트에 기계적으로 결합되도록 고정 벤드를 포함한다.

### 도면의 간단한 설명

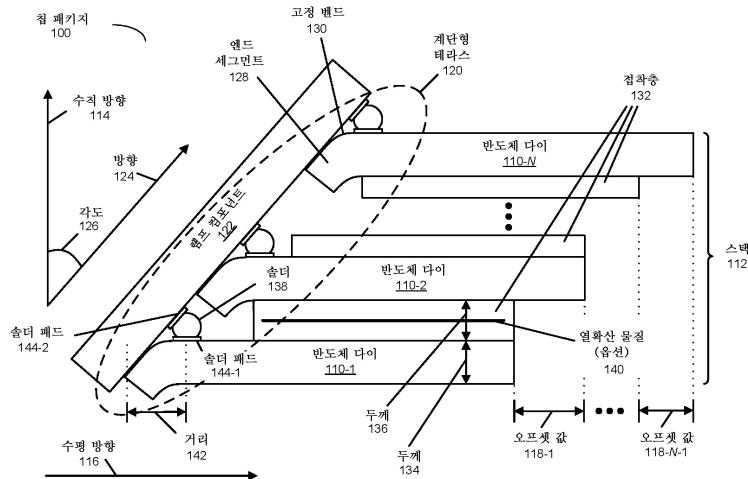

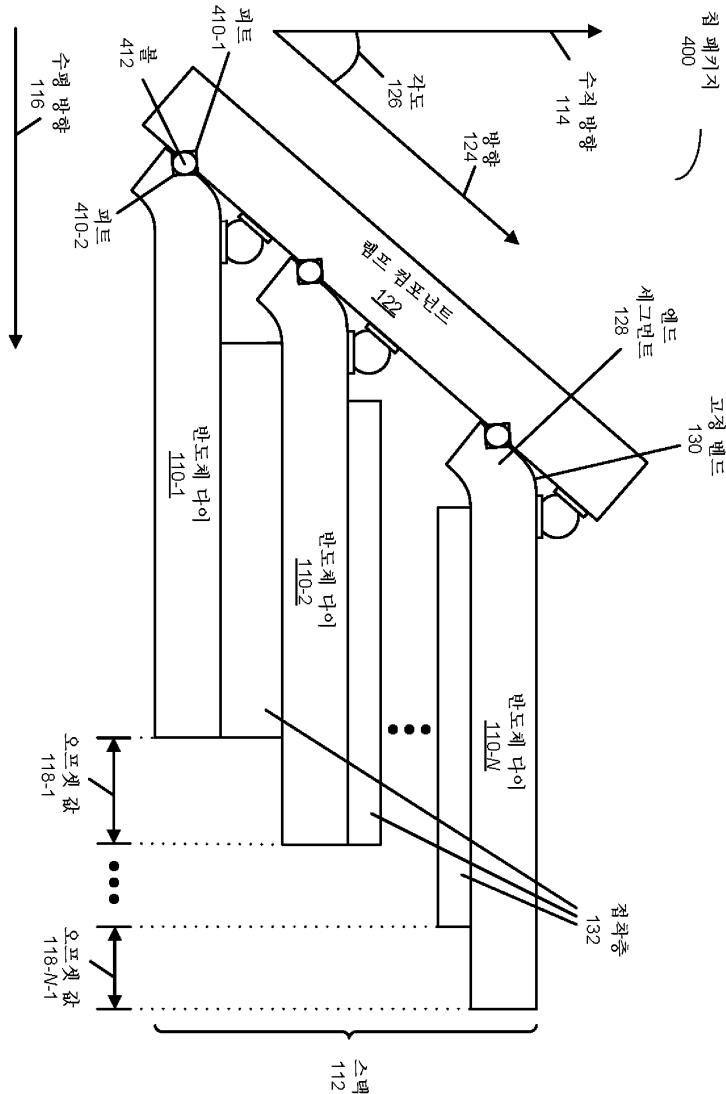

[0014] 도 1은 본 발명의 실시예에 따른 칩 패키지의 측면도를 예시한 블록도이다.

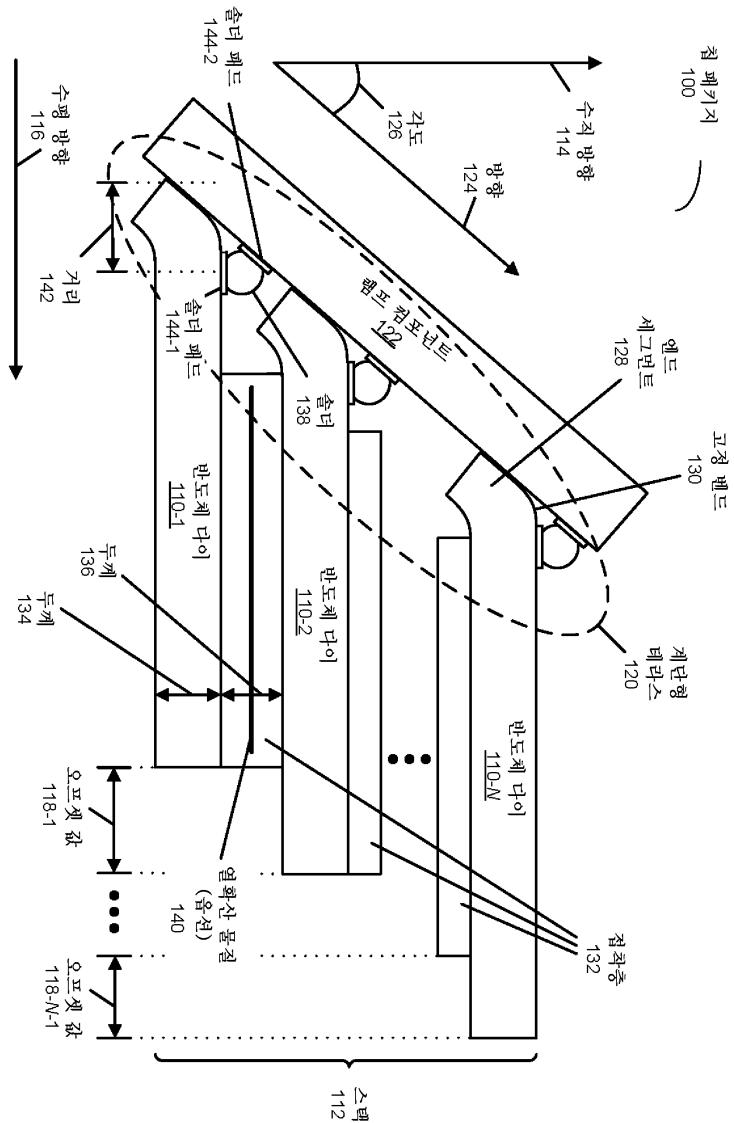

도 2는 본 발명의 실시예에 따른 도 1의 칩 패키지의 상면도를 예시한 블록도이다.

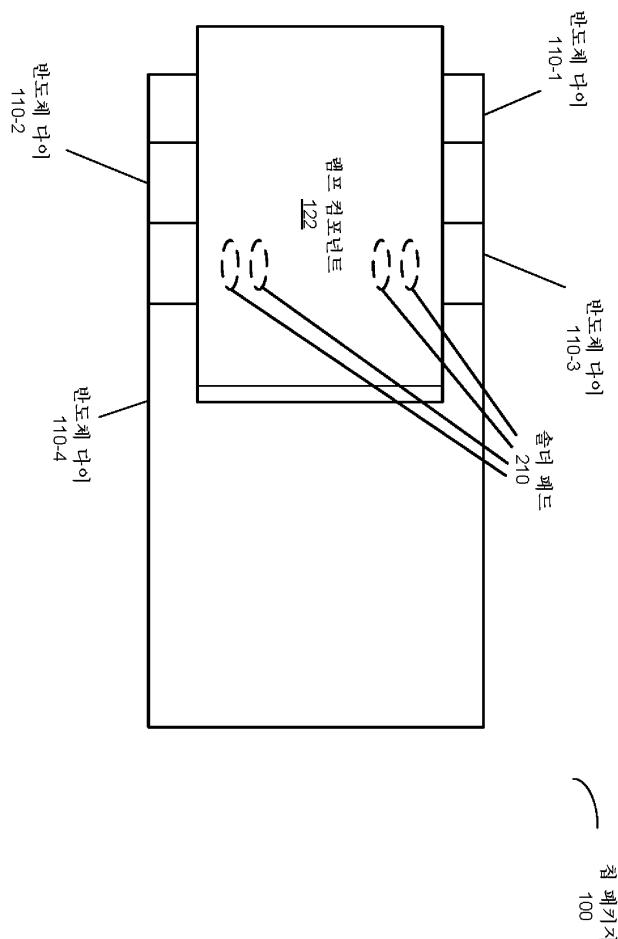

도 3은 본 발명의 실시예에 따른 칩 패키지의 측면도를 예시한 블록도이다.

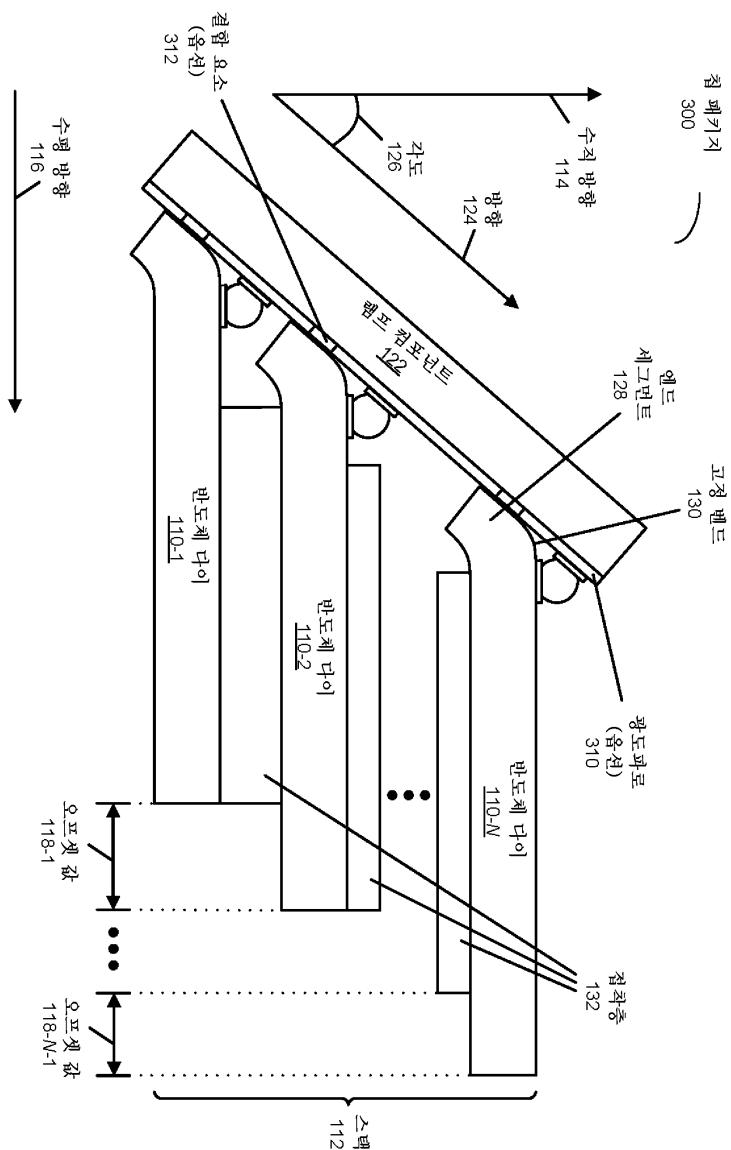

도 4는 본 발명의 실시예에 따른 칩 패키지의 측면도를 예시한 블록도이다.

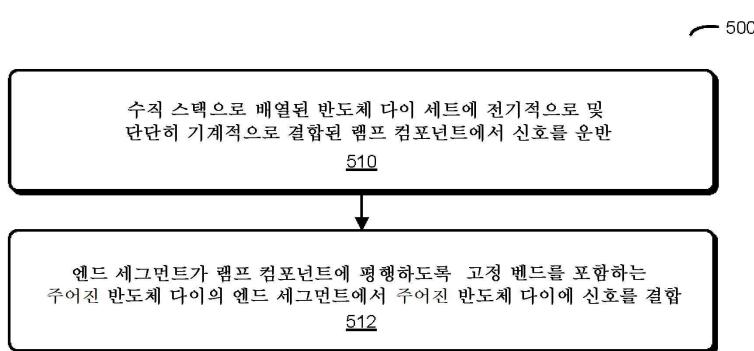

도 5는 본 발명의 실시예에 따른 칩 패키지에서의 신호 통신 방법을 예시한 흐름도이다.

도 6은 본 발명의 실시예에 따른 칩 패키지를 포함하는 전자 디바이스를 예시한 블록도이다.

동일한 참조 부호는 도면 전체를 통해 대응하는 부분을 지칭한다는 점에 유의한다. 또한, 동일한 부분의 여러 예시들은 대시(dash)에 의해 예시 번호로부터 분리된 공통의 접두 부호에 의해 지시된다.

### 발명을 실시하기 위한 구체적인 내용

[0015] 칩 패키지, 칩 패키지를 포함하는 전자 디바이스, 및 칩 패키지에서 신호들을 통신하는 방법의 실시예들이 설명된다. 칩 패키지는 수평 방향으로 서로 오프셋된 반도체 다이 또는 칩들의 수직 스택을 포함하며, 이로써 패드가 노출된 테라스(terrace)를 정의한다. 테라스에 대략 평행하게 위치하는 고대역폭 램프 컴포넌트는 노출된 패드에 전기적으로 및 기계적으로 결합된다. 예를 들어, 램프 컴포넌트는 솔더(solder), 마이크로스프링(microspring), 및/또는 이방성 도전 필름(anisotropic conducting film)을 사용하여 반도체 다이들에 결합될 수 있다. 또한, 반도체 다이 각각은 반도체 다이 각각의 엔드 세그먼트가 그 방향에 평행하고 램프 컴포넌트에 기계적으로 결합되도록 고정 벤드(static bend)를 포함한다. 이들 엔드 세그먼트는 예를 들어, 근접 통신(proximity communication)을 통해 반도체 다이들과 램프 컴포넌트 사이에 신호의 고대역폭 통신을 용이하게 할 수 있다.

- [0016] 비용이 많이 들고 면적을 많이 차지하는 관통형 실리콘 비아(TSV)에 대한 필요성을 반도체 다이에서 제거함으로써, 칩 패키지는 높은 대역폭과 낮은 비용을 제공할 수 있다. 예를 들어, 반도체 다이에서 TSV와 관련된 처리 동작 및 낭비 면적을 회피함으로써 비용이 줄어들 수 있다. 이로 인해, 스택 내의 칩들은 표준 처리를 사용하여 제조될 수 있다. 또한, 솔더, 마이크로스프링, 및/또는 이방성 필름은 와이어 본딩보다 비용이 낮으며/낮거나, 개선된 신뢰성을 제공할 수 있다. 또한, 램프 컴포넌트는 와이어 본딩보다 더 높은 인터-컴포넌트 통신 대역폭을 제공하고, 더 감소된 레이턴시를 제공할 수 있으며, TSV를 포함하는 반도체 다이에 의해 제공되는 것에 비해 상당한 통신 대역폭 및 레이턴시를 가질 수 있다.

- [0017] 이하, 칩 패키지의 실시예들을 설명한다. 도 1은 칩 패키지(100)의 측면을 예시한 블록도를 제시한다. ('램-스택 칩 패키지'라고도 지칭되는) 칩 패키지에서, 반도체 다이 세트(110)가 수직 방향(114)으로 스택(112)에 배열된다. 수직 방향(114)은 스택(112) 내의 반도체 다이(110-1)에 실질적으로 직각이라는 점에 유의한다(따라서, 반도체 다이(110-1)의 평면의 수평 방향(116)에 실질적으로 직각임). 또한, 반도체 다이(110-1) 다음에 있는 각각의 반도체 다이는 스택(112)에서 바로 앞의 반도체 다이로부터 오프셋 값(118) 중 관련된 값만큼 수평 방향(116)으로 오프셋될 수 있으며, 이로써 스택(112)의 일측에서 계단형 테라스(120)를 정의한다. 이들 오프셋 값은 반도체 다이 세트(110)에 대해 거의 고정 값을 가질 수 있거나, 반도체 다이 세트(110)에 걸쳐 달라질 수 있다(즉, 계단형 테라스(120)에서 상이한 계단에 대한 오프셋 값들은 상이할 수 있음).

- [0018] 또한, 고대역폭 램프 컴포넌트(122)는 반도체 다이들(110)에 단단히 기계적으로 및 전기적으로 결합되며, 이로써 반도체 다이들(110) 사이의 통신을 용이하게 하고/하거나 전력을 반도체 다이들(110)에 공급한다. 이러한 램프 컴포넌트(122)는 스택(112)의 일측에 위치하며, 수평 방향(116)과 수직 방향(114) 사이인 계단형 테라스(120)를 따르는 방향(124)(각도(126))에 대략 평행하다. 또한, 반도체 다이들(110)과 램프 컴포넌트(122) 사이의 단단한 기계적 및/또는 전기적 결합은 반도체 다이들(110)의 (엔드 세그먼트(128)와 같은) 엔드 세그먼트들에서 일어날 수 있으며, 여기서 반도체 다이들(110)은 반도체 다이들(110) 각각의 엔드 세그먼트가 방향(124)에 평행하도록 (고정 벤드(130)와 같은) 고정 벤드를 포함한다. 예를 들어, 엔드 세그먼트에 대한 단단한 기계적 및 전기적 결합은 솔더 볼(138)과 같은 솔더 볼을 통해 일어날 수 있다. 후술되는 바와 같이, 이들 엔드 세그먼트는 램프 컴포넌트(122)와 반도체 다이들(110) 사이의 (광학 신호 또는 전기 신호와 같은) 신호의 통신을 용이하게 하는 넓은 영역(coplanar area)을 제공할 수 있다.

- [0019] 고정 벤드와 관련된 반도체 다이들(110) 각각에 대한 응력(stress)은 반도체 다이들(110) 각각의 반도체의 항복 강도(yield strength) 미만일 수 있다는 점에 유의한다. 또한, 반도체 다이들(110) 각각의 두께(134)는 반도체 다이(110) 각각이 고정 벤드를 용이하게 하는 벤딩 모멘트(bending moment)를 갖도록 정의될 수 있다. 그러므로, 고정 벤드들은 벤드 반지름이 작을 수 있는데, 이는 엔드 세그먼트와 램프 컴포넌트(122) 사이에 공면 중첩(coplanar overlap)을 위한 더 넓은 영역이 존재한다 것을 보장할 수 있다.

- [0020] 스택(112) 내의 반도체 다이들(110)은 150°C에서 10초 내로 경화되는 에폭시 또는 글루(glue) 등의 접착층(132)에 의해 서로 기계적으로 결합될 수 있다. 또한, 반도체 다이 세트(110) 내의 주어진 반도체 다이는 공칭 두께(nominal thickness)(134)를 가질 수 있으며, 접착층(132)은 공칭 두께(136)를 가질 수 있다. 그러나, 일부 실시예에서, 스택(112) 내의 반도체 다이들(110) 및/또는 접착층들(132) 중 적어도 일부의 두께는 상이할 수 있음을 유념한다(예를 들어, 반도체 다이들(110)과 접착층들(132) 중 어느 하나 또는 이들 모두의 두께가 수직 방향(114)을 따라 달라질 수 있음).

- [0021] 일 실시예에서, 공칭 두께(134)는 50  $\mu\text{m}$ 와 100  $\mu\text{m}$  사이이다(그러나, 다른 실시예에서, 두께(134)는 30  $\mu\text{m}$ 와 250  $\mu\text{m}$  사이일 수 있음). 50  $\mu\text{m}$ 와 100  $\mu\text{m}$  사이의 공칭 두께(134)의 경우, 각도(126)는 10° 와 15° 사이에 있을 수 있다는 점에 유의한다. 일반적으로, 공칭 두께(134)는 부분적으로 스택(112) 내의 반도체 다이들(110)의 개수에 의존한다. 또한, 접착층(132)의 공칭 두께(136)는 최대 600  $\mu\text{m}$ 일 수 있다는 점에 유의한다(그러나, 다른 실시예에서, 두께(136)는 10  $\mu\text{m}$  정도로 작을 수 있음).

- [0022] 추가적으로, 오프셋 값들(118)은 램프 컴포넌트(122)를 반도체 다이 세트(110)에 단단히 기계적으로 결합하는데 사용되는 (솔더 볼(138)과 같은) 솔더의 공칭 두께 및 방향(124)(또는 각도(126))에 기반하여 결정될 수 있다. 솔더의 두께는 스택(112)에 걸쳐 거의 고정적이거나, 스택에 걸쳐(즉, 수직 방향(114)을 따라) 달라질 수 있다 는 점에 유의한다.

- [0023] 일부 실시예에서, 수직 방향(114)으로 반도체 다이 세트(110) 상에 축적된 위치 오류(즉, 스택(112) 상에 반도체 다이들의 수직 위치에서 축적된 위치 오류)는 반도체 다이 세트(110), 및 반도체 다이들(110) 사이의 접착층

(132)과 관련된 수직 오류의 합산보다 작다. 예를 들어, 축적된 위치 오류는 반도체 다이들(110)의 두께 변화, 접착층들(132)의 두께 변화, 및/또는 접착층들(132)의 적어도 일부에서의 옵션의 (압착된 그래파이트 섬유와 같은) 열확산 물질(140)의 두께 변화와 관련될 수 있다. 일부 실시예에서, 축적된 위치 오류는  $1\text{ }\mu\text{m}$  미만일 수 있으며,  $0\text{ }\mu\text{m}$  정도로 작을 수 있다. 추가적으로, 반도체 다이 세트(110)는 평면에서의 최대 위치 오류(즉, 거리(142)에서의 최대 오류)를 가질 수 있으며, 이는 (쏘우-라인(saw-line) 위치 변화와 같은) 반도체 다이들(110)의 에지 변화와 관련되어 있으며, 미리정의된 값 미만일 수 있다(예를 들어, 최대 위치 오류는  $1\text{ }\mu\text{m}$  미만일 수 있으며,  $0\text{ }\mu\text{m}$  정도로 작을 수 있음). 이는, 반도체 다이들(110)을 위한 쏘우 레인(saw lane)의 중심에 대해 거리(142)가 측정되도록 반도체 다이들(110)의 (피듀셜 마커(fiducial marker)와 같은) 광학 정렬 마커를 사용하여 칩 패키지(100)를 조립하기 위해 퍽-앤-플레이스 도구(pick-and-place tool)를 사용함으로써 달성될 수 있다. 또한, 조립 중에, 반도체 다이들(110)은 (스택(112)에서 반도체 다이(110-1) 다음에 있는 각각의 반도체 다이가 바로 앞의 반도체 다이를 참조하게 하는 대신에) 계단식 테라스(120)를 미러링하는 계단식 테라스를 포함하는 어셈블리 컴포넌트 또는 퍽스처(fixture)를 참조할 수 있다.

[0024] 수직 방향(114)의 기계적 정렬 오류들을 수용하기 위해, (솔더 패드(144-1) 및/또는 솔더 패드(144-2)와 같은) 솔더 범프 또는 패드 및/또는 솔더 볼(138)의 높이와 피치는 수직 방향(114)을 따라 반도체 다이들(110)의 적어도 일부 사이에서 달라질 수 있다는 점에 유의한다. 예를 들어, 거리(142)(즉, 반도체 다이(110-1)를 위한 쏘우 레인의 중심에 대한 솔더 패드(144-1)의 위치)는  $60\text{ }\mu\text{m}$ 일 수 있으며, 솔더 패드(144) 각각은 폭이  $80\text{ }\mu\text{m}$ 일 수 있다. 또한, (솔더 볼(138) 등의) 솔더 볼은 리플로잉(reflowing) 또는 멜팅(melting) 전에 지름이  $120\text{ }\mu\text{m}$  일 수 있으며, 멜팅 후의 대략적인 두께는 약  $40\text{ }\mu\text{m}$ 와  $60\text{ }\mu\text{m}$  사이일 수 있다. 일부 실시예에서, 2 줄 이상의 솔더 볼들은 램프 컴포넌트(122)를 주어진 반도체 다이에 단단히 결합할 수 있다.

[0025] 도 2는 스택(112)(도 1)이 4개의 반도체 다이(110)를 포함하는 칩 패키지(100)의 상면을 예시한 블록도를 제시한다. 칩 패키지(100)의 이 도면은 일부 실시예에서 솔더 패드(210)들의 형상이 직사각형이 아닐 수 있다는 점을 예시한다. 예를 들어, 솔더 패드(210)들의 형상은 폭이  $80\text{ }\mu\text{m}$ 이고, 길이가  $120\text{ }\mu\text{m}$ 인 오블롱과 같은 오블롱일 수 있다. 반도체 다이(110) 및/또는 램프 컴포넌트(122)에서의 이들 솔더-패드 형상은 약간의 수평 및/또는 수직 위치 오류를 용인할 수 있다.

[0026] 일부 실시예에서, 솔더 패드들은 램프 컴포넌트(122)의 에지로 옮겨질 수 있다. 이는 직각 배향을 용이하게 할 수 있다(즉, 도 1의 각도(126)가  $0^\circ$  일 수 있음). 이 구성은 입출력(I/O) 신호 라인 및 전력 라인과 관련된 컨택트 또는 패드가 ('스파인(spine)' 아래 대신) 램프 컴포넌트의 에지에 있는 메모리 모듈을 용이하게 할 수 있다. 이 방법으로, 램프 컴포넌트 내의 확산층의 개수가 줄어들 수 있다. 예를 들어, 이러한 메모리 모듈에는 램프 컴포넌트(122)의 에지를 따라 60개의 컨택트 또는 패드가 존재할 수 있다.

[0027] 칩 패키지(300)의 측면을 예시한 블록도를 제시하는 도 3에 도시된 바와 같이, 일부 실시예에서, 램프 컴포넌트(122)는 방향(124)을 따라 광학 신호를 운반하도록 구성된 옵션의 광도파로(310)를 포함한다. 또한, (옵션의 결합 요소(312)와 같은) 옵션의 결합 요소 세트는 반도체 다이들(110)의 엔드 세그먼트 중 하나 이상으로 및/또는 그로부터 광학 신호를 광학적으로 결합할 수 있는데, 여기서 주어진 결합 요소는 주어진 반도체 다이로 및/또는 그로부터 광학 신호를 광학적으로 결합할 수 있다(이로써, 옵션의 결합 요소(312)는 반도체 다이(110-2)의 엔드 세그먼트로 및/또는 그로부터 광학 신호를 광학적으로 결합할 수 있음). 옵션의 결합 요소들은 회절 격자, 각진 반사판 또는 미러, 빔 스플리터, 및/또는 렌즈 등의 광학 결합 요소일 수 있다는 점에 유의한다. 또한, 광학 결합 요소는 광학-전기 트랜스듀서들(optical to electrical transducers)을 포함할 수 있다. 후술하는 바와 같이, 일부 실시예에서, 엔드 세그먼트(들)와의 광학 신호의 통신은 (고대역폭(high-bandwidth) 및 저레이턴시(low-latency) 통신을 제공할 수 있는) 광학 결합 신호의 광학 근접 통신을 포함할 수 있다.

[0028] 또한, 다른 실시예에서, 도 1에 도시된 바와 같이, 램프 컴포넌트(122)는 전기 신호를 운반하는 신호 라인을 포함한다. 이들 실시예에서, 램프 컴포넌트(122)는 (도 4를 참조하여 후술되는 볼-인-피트(ball-in-pit) 구성의) 솔더, 마이크로스프링, 마이크로 중공구(micro-sphere), 및/또는 ('이방성 도전 필름'이라고도 지칭되는 이방성 탄성중합체 막 등의) 이방성 도전 필름을 포함하는 다양한 기법을 사용하여 반도체 다이들(110)의 엔드 세그먼트에 전기적으로 및/또는 기계적으로 결합될 수 있다. 또한, 후술되는 바와 같이, 엔드 세그먼트(들)와의 전기 신호의 통신은 엔드 세그먼트 및 램프 컴포넌트(122)의 표면 또는 그 부근의 PxC 커넥터(미도시)를 통해 (고대역폭 및 저레이턴시 통신을 제공할 수 있는) 용량성 결합 신호의 용량성 결합 근접 통신과 같은 근접 통신(Px C)을 포함할 수 있다.

[0029] 이로 인해, 일부 실시예에서, 반도체 다이들(110)의 엔드 세그먼트와 램프 컴포넌트(122) 사이(및 더 일반적으

로, 칩 패키지 내의 컴포넌트들 사이 또는 칩 패키지와 외부 디바이스 사이)의 통신은 용량성 결합 신호의 통신 ('전기 근접 통신'이라고 지칭됨), 광학 결합 신호의 통신('광학 근접 통신'이라고 지칭됨), 전자기 결합 신호의 통신('전자기 근접 통신'이라고 지칭됨), 유도성 결합 신호의 통신, 및/또는 전도성 결합 신호의 통신과 같은 전자기 결합 신호의 PxС를 포함할 수 있다.

[0030] 전기 신호들이 PxС를 사용하여 통신되는 실시예에서, 최종 전기 컨택트들의 임피던스는 일반적으로, 전도성 및/또는 용량성일 수 있는데, 다시 말하면 동위상(in-phase) 컴포넌트 및/또는 이상(out-of-phase) 컴포넌트를 포함하는 복소 임피던스를 가질 수 있다. (솔더, 마이크로스프링, 이방성 층 등과 같은) 전기 컨택트 메커니즘과 무관하게, 컨택트와 관련된 임피던스가 전도성이면, 종래의 송수신 I/O 회로들이 칩 패키지의 실시예들에서의 컴포넌트에 사용될 수 있다. 그러나, 복소(및, 가능하다면 가변) 임피던스를 갖는 컨택트들의 경우, 송수신 I/O 회로들은 2009년 4월 17일에 출원되어, 대리인 관리 번호가 SUN09-0285이고, 출원인이 Robert J. Drost 등이고, 발명의 명칭이 "Receive Circuit for Connectors with Variable Complex Impedance"인 미국 특허출원 제12/425,871호에 설명된 하나 이상의 실시예들을 포함할 수 있으며, 그 내용은 참조로서 여기에 원용되어 있다.

[0031] 앞선 실시예들에서는 칩 패키지의 특정 구성들을 예시하였지만, 컴포넌트의 기계적 정렬을 구현하는데 수많은 기법 및 구성이 사용될 수 있다. 예를 들어, 칩 패키지(400)의 측면을 예시한 블록도를 제시하는 도 4에 도시된 바와 같이, 반도체 다이(110) 및/또는 램프 컴포넌트(122)는 볼-앤피트(ball-and-pit) 정렬 기법(및 더 일반적으로 포지티브-피처-인-네거티브-피처(positive-feature-in-negative-feature) 정렬 기법)을 사용하여 서로에 대해 위치할 수 있다. 특히, (볼(412)과 같은) 볼들이 (에치 피트(410)와 같은) 에치 피트(etch pit) 내에 위치하여 램프 컴포넌트(122)와 반도체 다이들(110)의 엔드 세그먼트를 기계적으로 결합하여 상대적으로 정렬할 수 있다. 일부 실시예에서, 스택(112)에서 반도체 다이들(110)을 정렬하기 위해 볼-앤피트 정렬 기법이 사용된다. 도 4는 볼들을 예시하고 있지만, 반구형의 범프(bump)와 같은 다양한 포지티브 피처들이 사용될 수 있다. 이로 인해, 일반적으로, 칩 패키지의 컴포넌트에 대한 포지티브 표면 피처 및 네거티브 표면 피처의 기계적 잡금의 조합이 칩 패키지를 정렬 및/또는 조립하는데 사용될 수 있다.

[0032] 이하, 본 발명의 방법의 실시예를 설명한다. 도 5는 (도 1 및 도 2의 칩 패키지(100)와 같은) 칩 패키지에서 신호를 통신하는 방법(500)을 예시한 흐름도를 제시한다. 이 방법에서, 수직 방향으로 수직 스택에 배열된 반도체 다이 세트에 전기적으로 및 단단히 기계적으로 결합된 램프 컴포넌트에서 신호가 운반된다(동작(510)). 반도체 다이들은 수평 방향으로 서로 오프셋되어 수직 스택의 일측에서 계단형 테라스를 정의한다는 점에 유의한다. 또한, 램프 컴포넌트는 수평 방향과 수직 방향 사이인 계단형 테라스를 따르는 방향에 대략 평행하게 수직 스택의 일측에 위치한다. 그러면, 신호는 반도체 다이 세트 내의 주어진 반도체 다이의 엔드 세그먼트에서 주어진 반도체 다이에 결합되며(동작(512)), 여기서 주어진 반도체 다이는 엔드 세그먼트가 이 방향에 평행하고, 램프 컴포넌트에 기계적으로 결합되도록 고정 벤드를 포함한다.

[0033] 본 발명의 방법(500)의 일부 실시예에서, 추가 동작이 있거나, 동작이 더 적을 수 있다. 또한, 동작 순서는 변할 수 있으며/있거나, 2 이상의 동작이 단일 동작으로 결합될 수 있다.

[0034] 이하, 본 발명의 전자 디바이스의 실시예를 설명한다. 도 6은 (칩 패키지의 앞선 실시예들 중 하나일 수 있는) 칩 패키지(610)를 포함하는 전자 디바이스(600)를 도시하는 블록도를 제시한다.

[0035] 일부 실시예에서, (칩 패키지의 앞선 실시예들 중 하나와 같은) 칩 패키지는 고성능 디바이스를 용이하게 할 수 있다. 예를 들어, 일부 실시예에서, 램프 스택 칩 패키지는 듀얼 인-라인 메모리 모듈에 포함된다. 예를 들어, 램프 스택 칩 패키지에 (다이내믹 랜덤 액세스 메모리 또는 다른 타입의 메모리 저장 디바이스와 같은) 최대 80개의 메모리 디바이스가 있을 수 있다. 필요하다면, '성능이 나쁜' 또는 고장 난 메모리 디바이스들이 디스에이블될 수 있다. 이로 인해, (80개 중) 72개의 메모리 디바이스가 사용될 수 있다. 또한, 이러한 구성은 메모리 디바이스 중 어느 하나를 액세스할 때 레이턴시 딜레이가 거의 또는 아예 없도록 메모리 모듈 내의 메모리 디바이스들의 전체 대역폭을 노출할 수 있다.

[0036] 또한, 듀얼 인-라인 메모리 모듈은 각각이 램프 스택 칩 패키지를 포함할 수 있는 다수의 필드를 포함할 수 있다. 예를 들어, 듀얼 인-라인 메모리 모듈에 (각각이 9개의 메모리 디바이스를 포함하는) 4개의 램프 스택 칩 패키지들이 존재할 수 있다.

[0037] 일부 실시예에서, (하나 이상의 램프 스택 칩 패키지들을 포함할 수 있는) 이를 듀얼 인-라인 메모리 모듈 중 하나 이상이 프로세서에 결합될 수 있다. 예를 들어, 프로세서는 용량성 결합된 신호의 용량성 근접 통신을 사

용하여 하나 이상의 듀얼 인-라인 메모리 모듈들에 결합될 수 있다. 결과적으로, 프로세서는 C4 솔더 볼을 사용하여 기판에 실장될 수 있다.

[0038] 이에 따라, 전자 디바이스(600)는 VLSI 회로, 스위치, 허브, 브릿지, 라우터, 통신 시스템, 저장 영역 네트워크, 데이터 센터, (로컬 영역 네트워크 등의) 네트워크, 및/또는 (멀티-코어 프로세서 컴퓨터 시스템 등의) 컴퓨터 시스템과 같은 디바이스 또는 시스템을 포함할 수 있다. 또한, 컴퓨터 시스템은 이들로 제한되는 것은 아니지만, (멀티 소켓, 멀티 랙 서버(multi-rack server) 등의) 서버, 랩탑 컴퓨터, 통신 디바이스 또는 시스템, 개인용 컴퓨터, 워크 스테이션, 메인프레임 컴퓨터, 블레이드, 기업용 컴퓨터, 데이터 센터, 휴대용 컴퓨팅 디바이스, 슈퍼 컴퓨터, 네트워크 저장 장치(network-attached-storage (NAS)) 시스템, 저장 영역 네트워크(storage-area-network (SAN)) 시스템, 및/또는 다른 전자 컴퓨팅 디바이스를 포함할 수 있다. 주어진 컴퓨터 시스템이 하나의 위치에 있거나, 지리적으로 흩어져 있는 다수의 위치에 분산될 수 있다는 점에 유의한다.

[0039] 전자 디바이스(600)뿐 아니라 칩 패키지(100(도 1 및 도 2), 300(도 3), 및 400(도 4))는 더 적은 컴포넌트를 포함하거나 추가 컴포넌트를 포함할 수 있다. 예를 들어, 램프 컴포넌트의 반도체 다이들 중 하나 이상을 위한 솔더 패드들을 포함하지 않음으로써, 램프 스택 칩 패키지의 반도체 다이들의 스택에서 정의되는 브레이크들이 존재할 수 있다. 추가적으로, 칩 패키지의 일 실시예에서의 하나 이상의 컴포넌트들은 광학 모듈레이터, (애드 필터(add filter)와 같은) 광학 멀티플렉서, (드롭 필터(drop filter)와 같은) 광학 디멀티플렉서, 광학 필터, 및/또는 광학 스위치를 포함할 수 있다.

[0040] 또한, 이들 디바이스 및 시스템들은 다수의 이산 아이템들을 갖는 것으로 예시되었지만, 이들 실시예는 여기에 설명된 실시예들의 구조적 도식이 아니라 제시할 수 있는 다양한 특징들의 기능적 설명을 위한 것이다. 결과적으로, 이들 실시예에서, 2 이상의 컴포넌트들이 단일 컴포넌트로 결합되고/거나, 하나 이상의 컴포넌트의 위치가 변경될 수 있다. 또한, 앞선 실시예에서의 기능성은 당업계에 공지된 바와 같이 하드웨어로 더 많이 구현되고 소프트웨어로 더 조금 구현되거나, 소프트웨어로 더 많이 구현되고 하드웨어로 더 조금 구현될 수 있다.

[0041] 앞선 실시예들은 칩 패키지 내의 (실리콘과 같은) 반도체 다이를 사용하지만, 다른 실시예에서, 반도체와 상이한 물질이 이를 칩 중 하나 이상에 기판 물질로서 사용될 수 있다. 그러나, 실리콘이 사용되는 실시예에서, 반도체 다이들(110)(도 1 내지 도 4)은 표준 실리콘 처리를 사용하여 제조될 수 있다. 이들 반도체 다이들은 로직 및/또는 메모리 기능성을 지원하는 실리콘 영역을 제공할 수 있다.

[0042] 또한, 도 1을 다시 참조하면, 램프 컴포넌트(122)는 반도체 다이들(110)에 전기적 결합된 금속 트레이스를 구비한 플라스틱 기판과 같은 수동 컴포넌트일 수 있다. 예를 들어, 램프 컴포넌트(122)는 사출 성형 플라스틱을 사용하여 제조될 수 있다. 또한, 램프 컴포넌트(122)는 하나 이상의 리소그래피 방식으로 정의된 와이어, 신호 라인, 또는 광도파로를 구비한 다른 반도체 다이일 수 있다. 예를 들어, 옵션의 광도파로(310)(도 3)가 실리콘-온-인슐레이터(silicon-on-insulator) 기술을 사용하여 구현될 수 있다. 램프 컴포넌트(122)가 반도체 다이를 포함하는 실시예에서, 증폭기와 같은 능동 디바이스가 포함되어 신호 라인 사이의 크로스 토크를 감소시킬 수 있다. 또한, 크로스 토크는 차동 신호 전송(differential signaling)을 사용하여 능동 또는 수동 램프 컴포넌트(122)에서 감소될 수 있다.

[0043] 일부 실시예에서, 램프 컴포넌트(122)는 (솔더 볼(138)과 같은) 솔더 볼들을 통해 반도체 다이들(110) 사이에서 데이터 및 전력 신호들을 나르는 와이어 및 트랜지스터를 포함한다. 예를 들어, 램프 컴포넌트(122)는 고압 신호를 포함할 수 있다. 이들 신호는 반도체 다이들(110)에 결합된 커패시터 및/또는 인덕터 이산 컴포넌트뿐 아니라 (커패시터-투-커패시터 스텝 다운 레귤레이터와 같은) 스텝 다운 레귤레이터(step-down regulator)를 사용하여 반도체 다이(110)에서의 사용을 위해 스텝 다운될 수 있다.

[0044] 또한, 램프 컴포넌트(122)는 메모리용 버퍼 또는 로직 칩 및/또는 외부 디바이스(들) 및/또는 시스템(들)에 대한 I/O 커넥터를 포함할 수 있다. 예를 들어, I/O 커넥터들은 외부 디바이스에 결합하기 위한 하나 이상의 볼 본드, 와이어 본드, 에지 커넥터, 및/또는 PxC 커넥터를 포함할 수 있다. 일부 실시예에서, 이들 I/O 커넥터들은 램프 컨포넌트(122)의 후면에 있을 수 있고, 램프 컴포넌트(122)는 PxC 커넥터 또는 솔더 패드(예를 들어, 솔더 패드(144-2))와 같은 반도체 다이(110) 근처의 추가 커넥터에 I/O 커넥터들을 결합시키는 하나 이상의 판통형 실리콘 비아(TSV)를 포함할 수 있다.

[0045] 일부 실시예에서, 칩 패키지의 하나 이상의 실시예들의 램프 컴포넌트(122) 및 반도체 다이들(110)이 (인쇄 회로 기판 또는 반도체 다이와 같은) 옵션의 기판에 실장된다. 이러한 옵션의 기판은 외부 디바이스에 결합하기

위한 볼 본드, 와이어 본드, 에지 커넥터, 및/또는 PxC 커넥터를 포함할 수 있다. 이들 I/O 커넥터들이 옵션의 기판의 후면에 있으면, 옵션의 기판은 하나 이상의 TSV를 포함할 수 있다.

[0046] 전술한 바와 같이, 일부 실시예에서, 옵션의 열확산 물질(140)(및 더 일반적으로 반도체 다이(110) 사이에 있는 열전도성이 높은 중간 물질(intermediate material))이 하나 이상의 반도체 다이(110) 및/또는 램프 컴포넌트(122)에 있는 회로들의 동작 중에 생성된 열을 제거하는데 도움이 될 수 있다. 이러한 열 관리는 다음의 열 경로, 즉 반도체 다이(110) 평면에 있는 제1 열 경로, 접착층(132) 평면에 있는 제2 열 경로, 및/또는 옵션의 열확산 물질(140) 평면에 있는 제3 열 경로 중 어느 하나를 포함할 수 있다. 특히, 이들 열 경로와 관련된 열 풀렉스(thermal flux)는 칩 패키지의 에지에서의 열 결합(thermal coupling)을 통해 서로 독립적으로 관리될 수 있다. 이러한 열 관리는 위상 변화 냉각, 액침 냉각(immersion cooling), 및/또는 냉각판의 사용을 포함할 수 있다는 점에 유의한다. 또한, 칩 패키지의 에지에 있는 단면 영역을 통해 확산하는 제1 열 경로와 관련된 열 풀렉스는 공칭 두께(134)의 함수라는 점에 유의한다. 이에 따라, 열 관리는 반도체 다이(110)의 공칭 두께가 더 큰 칩 패키지와 더 작은 칩 패키지에서 상이할 수 있다.

[0047] 패키징 및 조립 전에 대규모 테스트에 대한 높은 비용 또는 낮은 반도체 다이 수율에 직면한 경우, 일부 재작업을 허용하는 패키징 기법들이 더 비용 효율적이라는 점에 유의한다. 그러므로, 반도체 다이들(110)과 램프 컴포넌트(122) 사이의 기계적 및/또는 전기적 결합이 리메이트(remate) 가능한 실시예에서, (조립, 테스트, 또는 번-인(burn-in) 중에) 식별된 나쁜 성능의 칩을 교체하는 것과 같은 재작업을 허용함으로써 칩 패키지의 수율이 증가할 수 있다. 이러한 관점에서, 리메이트 가능한 기계적 또는 전기적 결합은 (예를 들어, 솔더를 이용한) 재작업 또는 가열을 요구하지 않고 반복적으로(즉, 2 번 이상) 구축되고 파손될 수 있는 기계적 또는 전기적 결합이라는 것이 이해되어야 한다. 일부 실시예에서, (함께 스냅(snap)되는 컴포넌트들과 같이) 리메이트 가능한 기계적 또는 전기적 결합은 서로 결합하도록 설계된 수(male) 컴포넌트와 암(female) 컴포넌트를 포함한다.

[0048] 일부 실시예에서, 앞선 실시예에서의 칩 패키지의 적어도 일부 주변에서의 옵션의 캡슐화가 있을 수도 있다. 또한, 칩 패키지 내의 컴포넌트들 사이의 공극(air gap)들은 열 제거를 개선하기 위해 언더필릴 수 있다. 이는 각도(126)를 감소시킴으로써 용이해 질 수 있으며, 즉 반도체 다이들(110)은 수직 방향(114)을 향해 더 뾰족할 수 있다.

[0049] 앞선 설명은 당업자가 본 개시를 만들고 사용하는 것을 가능하게 하기 위한 것으로서, 특정 애플리케이션 및 그 요구사항의 문맥에서 제공된다. 또한, 본 발명의 실시예들의 이전 설명들은 예시 및 설명의 목적만으로 제시되었다. 이들은 모든 것을 망라하거나 본 발명을 개시된 형태로 제한하려는 것이 아니다. 따라서, 여러 변형 예 및 변경 예들은 당업자에게 명백할 것이며, 여기에 정의된 일반적인 원리들은 본 발명의 사상 및 범위로부터 벗어나지 않는 한 다른 실시예 및 분야에 적용될 수 있다. 또한, 앞선 실시예들의 설명은 본 발명을 제한하려는 것이 아니다. 따라서, 본 발명은 도시된 실시예들로 제한하려는 것이 아니라 여기에 개시된 원리 및 특징에 부합하도록 최광의로 해석되어야 한다.

## 도면

## 도면1

도면2

### 도면3

## 도면4

## 도면5

## 도면6

【심사관 직권보정사항】

【직권보정 1】

【보정항목】 청구범위

【보정세부항목】 청구항 18

【변경전】

광학-전기 튜랜스듀서들을 포함하는

【변경후】

광학-전기 트랜스듀서들을 포함하는