(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6162902号

(P6162902)

(45) 発行日 平成29年7月12日(2017.7.12)

(24) 登録日 平成29年6月23日(2017.6.23)

(51) Int.Cl.

G 11 C 11/16 (2006.01)

F 1

G 11 C 11/16 240

G 11 C 11/16 230

請求項の数 30 (全 20 頁)

(21) 出願番号 特願2016-536640 (P2016-536640)

(86) (22) 出願日 平成26年11月26日 (2014.11.26)

(65) 公表番号 特表2016-540336 (P2016-540336A)

(43) 公表日 平成28年12月22日 (2016.12.22)

(86) 國際出願番号 PCT/US2014/067756

(87) 國際公開番号 WO2015/088790

(87) 國際公開日 平成27年6月18日 (2015.6.18)

審査請求日 平成29年5月8日 (2017.5.8)

(31) 優先権主張番号 14/106,730

(32) 優先日 平成25年12月14日 (2013.12.14)

(33) 優先権主張国 米国(US)

早期審査対象出願

(73) 特許権者 507364838

クアルコム、インコーポレイテッド

アメリカ合衆国 カリフォルニア 921

21 サンディエゴ モアハウス ドラ

イブ 5775

(74) 代理人 100108453

弁理士 村山 靖彦

(74) 代理人 100163522

弁理士 黒田 晋平

(72) 発明者 ジエン・シェン

アメリカ合衆国・カリフォルニア・921

21-1714・サン・ディエゴ・モアハ

ウス・ドライブ・5775

最終頁に続く

(54) 【発明の名称】低電力メモリ動作を実行するためのシステムおよび方法

## (57) 【特許請求の範囲】

## 【請求項1】

方法であって、

单一のメモリクロックサイクル中に、

磁気トンネル接合(MTJ)記憶素子に記憶される第1の値を読み出すステップと、

メモリ書き込み動作中に、マルチプレクサ(MUX)が論理値を受信するステップと、

前記第1の値を前記論理値と比較するステップと、

前記比較に基づいて、前記MTJ記憶素子に前記論理値を選択的に書き込むステップと

によって、前記MTJ記憶素子においてメモリ書き込み動作を実行するステップと、前記MTJ記憶素子においてメモリ読み出し動作を実行するステップであって、前記メモリ

読み出し動作は、前記MUXから基準値を受信するステップを含む、ステップと

を含む、方法。

## 【請求項2】

前記第1の値が前記論理値に一致しないと判断するのに応答して、前記論理値が前記MTJ

記憶素子に書き込まれる、請求項1に記載の方法。

## 【請求項3】

前記第1の値が前記論理値に一致すると判断するのに応答して、前記MTJ記憶素子に前記

論理値を書き込むのを抑制するステップをさらに含む、請求項1に記載の方法。

## 【請求項4】

前記単一のメモリクロックサイクル中に、

10

20

MTJ記憶素子のアレイに記憶される第1の複数の値を読み出すステップであって、前記第1の複数の値は前記第1の値を含み、前記MTJ記憶素子のアレイは前記MTJ記憶素子を含む、読み出すステップと、

前記第1の複数の値の各々を第2の複数の値の各々と比較するステップであって、前記第2の複数の値は前記論理値を含み、前記第2の複数の値は前記MTJ記憶素子のアレイに書き込まれることになる、比較するステップと、

前記第1の複数の値の各々と前記第2の複数の値の各々との前記比較に基づいて、前記MTJ記憶素子のアレイの対応するMTJ記憶素子に前記第2の複数の値の各々を選択的に書き込むステップと

をさらに含む、請求項1に記載の方法。

10

#### 【請求項5】

第1の電流を用いて前記第1の値を読み出すステップと、第2の電流を用いて前記MTJ記憶素子に前記論理値を書き込むステップとをさらに含み、前記第2の電流は前記第1の電流よりも大きな量を有する、請求項1に記載の方法。

#### 【請求項6】

第1の期間中に前記第1の値を読み出すステップと、第2の期間中に前記MTJ記憶素子に前記論理値を書き込むステップとをさらに含み、前記第2の期間は前記第1の期間よりも長い、請求項1に記載の方法。

#### 【請求項7】

前記第1の値は前記单一のメモリクロックサイクルの最初の半分以内に読み出される、請求項1に記載の方法。

20

#### 【請求項8】

装置であって、

書込み動作中に論理値を出力し、かつ読み出し動作中に基準値を出力するように構成されるマルチプレクサ(MUX)と、

磁気トンネル接合(MTJ)記憶素子に結合される回路であって、メモリ動作の单一のメモリクロックサイクル中に、

前記MTJ記憶素子に記憶される第1の値を受信し、

前記MUXから前記論理値を受信し、

前記第1の値を前記論理値と比較し、

30

前記比較に基づいて、前記MTJ記憶素子への前記論理値の書き込みを選択的に可能にする

ように構成される回路と

を備える、装置。

#### 【請求項9】

前記回路は、前記第1の値が前記論理値に一致しないと判断するのに応答して、書き込みイネーブル信号を生成することによって前記書き込みを可能にするようにさらに構成される、請求項8に記載の装置。

#### 【請求項10】

前記MUXは、前記基準値を受信するように構成される第1の入力と、前記論理値を受信するように構成される第2の入力と、制御信号を受信するように構成される第3の入力と、出力とを含み、前記制御信号は読み出し動作または前記書き込み動作を指示するように構成され、前記出力値は前記読み出し動作を指示する第1の値を有する前記制御信号に応答して前記基準値に対応し、前記出力値は前記書き込み動作を指示する第2の値を有する前記制御信号に応答して前記論理値に対応する、請求項8に記載の装置。

40

#### 【請求項11】

前記MUXは、前記読み出し動作を指示する第1の値を有する前記制御信号に基づいて、メモリ読み出し動作中に前記基準値を与えるように構成される、請求項10に記載の装置。

#### 【請求項12】

前記回路は、書き込みパルス発生器に前記書き込みイネーブル信号を送信するようにさらに

50

構成され、前記書込みパルス発生器は、前記書込みイネーブル信号に応答して、前記MTJ記憶素子への前記論理値の書き込みを可能にするように構成される、請求項8に記載の装置。

### 【請求項13】

前記回路は、前記単一のメモリクロックサイクル中に、

MTJ記憶素子のアレイに記憶される第1の複数の値を受信することであって、前記第1の複数の値は前記第1の値を含み、前記MTJ記憶素子のアレイは前記MTJ記憶素子を含む、受信することと、

前記MTJ記憶素子のアレイに書き込まれることになる第2の複数の値を受信することであって、前記第2の複数の値は前記論理値を含む、受信することと、

前記第1の複数の値を前記第2の複数の値と比較することと、

前記第1の複数の値と前記第2の複数の値との前記比較に基づいて、前記MTJ記憶素子のアレイの対応するMTJ記憶素子への前記第2の複数の値の各々の書き込みを選択的に可能にすることと

を行うようにさらに構成される、請求項8に記載の装置。

### 【請求項14】

前記第1の複数の値は前記単一のメモリクロックサイクルの最初の半分以内に受信される、請求項13に記載の装置。

### 【請求項15】

前記回路は少なくとも1つの半導体ダイに集積される、請求項8に記載の装置。

### 【請求項16】

モバイルフォン、セットトップボックス、音楽プレーヤ、ビデオプレーヤ、エンターテインメントユニット、ナビゲーションデバイス、通信デバイス、携帯情報端末(PDA)、固定位置データユニット、およびコンピュータからなるグループから選択されるデバイスをさらに備え、前記回路は前記デバイスに組み込まれる、請求項8に記載の装置。

### 【請求項17】

前記回路は、センス増幅器と、コンパレータとを含む、請求項8に記載の装置。

### 【請求項18】

前記回路は、

前記MTJ記憶素子への前記論理値の前記書き込みが完了した後に、前記MUXから前記基準値を受信し、

前記論理値と前記基準値を比較し、

前記比較に基づいて、前記MTJ記憶素子への前記基準値の第2の書き込みを選択的に可能にする

ようにさらに構成される、請求項8に記載の装置。

### 【請求項19】

装置であって、

第1の磁気トンネル接合(MTJ)記憶素子を含むMTJ記憶素子のアレイと、

単一のメモリクロックサイクル中に、メモリ書き込み動作中に論理値を出力し、かつメモリ読み出し動作中に基準値を出力するように構成されるマルチプレクサ(MUX)と、

前記MTJ記憶素子のアレイと、前記MUXとに結合される回路であって、メモリ動作中に、

前記第1のMTJ記憶素子に記憶される第1の値を受信し、

前記MUXから前記論理値を受信し、

前記第1の値を前記論理値と比較し、

前記比較に基づいて、書き込みパルス発生器に書き込みイネーブル信号を選択的に送信する

ように構成される回路と

を備え、

前記回路は、前記メモリ読み出し動作中に、前記MUXから前記基準値を受信するように構成される、装置。

10

20

30

40

50

**【請求項 20】**

前記書込みパルス発生器は、前記書込みイネーブル信号に応答して、前記MTJ記憶素子への前記論理値の書き込みを可能にするように構成される、請求項19に記載の装置。

**【請求項 21】**

前記MUXは、前記メモリ読み出し動作または前記メモリ書き込み動作を指示する値を有する制御信号を受信するように構成される、請求項19に記載の装置。

**【請求項 22】**

前記MUXは、前記制御信号によって指示される前記メモリ書き込み動作に基づいて、前記回路に前記論理値を出力するように構成され、前記MUXは、前記制御信号によって指示される前記メモリ読み出し動作に基づいて、基準値を出力するように構成される、請求項21に記載の装置。 10

**【請求項 23】**

前記回路は、前記第1の値が前記論理値と異なるとの判断に応答して、前記書込みパルス発生器に前記書込みイネーブル信号を送信するようにさらに構成される、請求項19に記載の装置。

**【請求項 24】**

前記回路は、前記第1の値が前記論理値に一致するとの判断に応答して、前記書込みパルス発生器への前記書込みイネーブル信号の送信を抑制するようにさらに構成される、請求項19に記載の装置。

**【請求項 25】**

前記回路は、単一のメモリクロックサイクル中に、前記第1の値を受信し、前記論理値を受信し、かつ、前記書込みイネーブル信号を選択的に送信するようにさらに構成される、請求項19に記載の装置。 20

**【請求項 26】**

前記回路は、

前記MTJ記憶素子のアレイに記憶される第1の複数の値を受信することであって、前記第1の複数の値は前記第1の値を含む、受信することと、

前記MUXから、前記MTJ記憶素子のアレイに書き込まれることになる第2の複数の値を受信することであって、前記第2の複数の値は前記論理値を含む、受信することと、

前記第1の複数の値を前記第2の複数の値と比較することと、 30

前記第1の複数の値と前記第2の複数の値との前記比較に基づいて、複数の書き込みパルス発生器に書き込みイネーブル信号を選択的に送信することと

を行うようにさらに構成される、請求項19に記載の装置。

**【請求項 27】**

前記MTJ記憶素子のアレイ、前記MUX、前記回路および前記書込みパルス発生器は少なくとも1つの半導体ダイに集積され、前記回路はセンス増幅器と、コンパレータとを含む、請求項19に記載の装置。

**【請求項 28】**

モバイルフォン、セットトップボックス、音楽プレーヤ、ビデオプレーヤ、エンターテインメントユニット、ナビゲーションデバイス、通信デバイス、携帯情報端末(PDA)、固定位置データユニット、コンピュータからなるグループの中から選択されるデバイスをさらに備え、前記MTJ記憶素子のアレイ、前記MUX、前記回路および前記書込みパルス発生器は前記デバイスに組み込まれる、請求項19に記載の装置。 40

**【請求項 29】**

装置であって、

第1のデータ要素を含む複数のデータ要素を記憶するための手段と、

前記第1のデータ要素に記憶される第1の値を受信するための手段と、

メモリ書き込み動作中にマルチブレクサ(MUX)から論理値を受信し、かつメモリ読み出し動作中に前記MUXから基準値を受信するための手段と、

前記第1の値を第2の値と比較するための手段と、 50

前記比較するための手段からの結果に基づいて、書き込みパルスを生成するための手段に書き込みイネーブル信号を選択的に送信するための手段であって、前記書き込みパルスは、前記第1のデータ要素への前記第2の値の書き込みを可能にする、送信するための手段とを備える、装置。

【請求項 30】

モバイルフォン、セットトップボックス、音楽プレーヤ、ビデオプレーヤ、エンターテインメントユニット、ナビゲーションデバイス、通信デバイス、携帯情報端末(PDA)、固定位置データユニット、コンピュータからなるグループの中から選択されるデバイスをさらに備え、前記記憶するための手段、前記第1の値を受信するための手段、前記論理値を受信するための手段、前記比較するための手段、前記選択的に送信するための手段、および前記書き込みパルスを生成するための手段は、前記デバイスに組み込まれる、請求項29に記載の装置。10

【発明の詳細な説明】

【技術分野】

【0001】

関連出願の相互参照

本出願は、参照によりその内容全体が本明細書に明確に組み込まれる、同一出願人が所有する2013年12月14日に出願の米国非仮特許出願第14/106,730号の優先権を主張する。

【0002】

本開示は包括的には、低電力メモリ動作を実行するためのシステムおよび方法に関する20。

【背景技術】

【0003】

技術が進歩した結果、コンピューティングデバイスがより小型に、そしてより強力になった。たとえば、小型、軽量で、ユーザによって容易に携帯されるポータブルワイヤレス電話、携帯情報端末(PDA)、およびページングデバイスなどのワイヤレスコンピューティングデバイスを含む、種々のポータブルパーソナルコンピューティングデバイスが現存している。より具体的には、セルラー電話、インターネットプロトコル(IP)電話などのポータブルワイヤレス電話は、ワイヤレスネットワークを介して音声およびデータパケットを通信することができる。さらに、多くのそのようなワイヤレス電話は、その内部に組み込まれた他のタイプのデバイスを含む。たとえば、ワイヤレス電話は、デジタルスチールカメラ、デジタルビデオカメラ、デジタルレコーダ、およびオーディオファイルプレーヤも含むこともできる。また、そのようなワイヤレス電話は、インターネットにアクセスするために用いることができるウェブブラウザアプリケーションのようなソフトウェアアプリケーションを含む、実行可能命令を処理することができる。したがって、これらのワイヤレス電話は、著しいコンピューティング能力を含むことができる。30

【0004】

ワイヤレス電話のような電子デバイスは、磁気トンネル接合(MTJ)記憶素子を含む場合がある。磁気トンネル接合(MTJ)記憶素子では、書き込み動作が、読み出し動作よりも大きなエネルギーを使用する場合がある。たとえば、45ナノメートル(nm)MTJにおける単一ビット書き込み動作は、100ナノ秒にわたって25マイクロアンペア( $\mu A$ )パルスを使用する場合がある。45nm MTJにおける単一ビット読み出し動作は、1nsにわたって $10 \mu A$ 未満のパルスを使用する場合がある。したがって、単一ビット書き込み動作は、単一ビット読み出し動作において使用されるエネルギーの250倍以上のエネルギーを使用する場合がある。40

【0005】

1つのエネルギー節約手法は、最初に低い書き込み電圧(たとえば、書き込みしきい値電圧よりもわずかに高い電圧)を用いて書き込み動作を実行し、記憶位置に値を書き込むことを含む。記憶位置から記憶された値を読み出すために、読み出し動作を実行することができる。書き込み値が記憶された値と一致しない場合には、高い書き込み電圧を用いて、別の書き込み動作を実行することができる。この手法を用いることは、初期低電圧書き込み動作が成功する50

ときに、メモリ動作を実行するエネルギー消費量を削減することができる。しかしながら、初期低電圧書き込み動作が失敗し、さらに高い電圧の書き込み動作が実行されるとき、メモリ動作に関連付けられるサイクルレイテンシが生じる。サイクルレイテンシの結果として、命令パイプライン内にギャップ(またはバブル)が生じ、性能の非効率を引き起こすおそれがある。

**【発明の概要】**

**【課題を解決するための手段】**

**【0006】**

低電力メモリ動作を実行するシステムおよび方法が開示される。本開示によれば、MTJ記憶素子のメモリ動作が、MTJ記憶素子から記憶された値を読み出すことと、記憶された値をMTJ記憶素子に書き込まれることになる書き込み値と比較することと、比較に基づいて、書き込み値をMTJ記憶素子に選択的に書き込むことを含むことができる。たとえば、書き込み動作は、記憶された値が変更されることになるときにのみ実行することができる。この手法を用いることは、記憶された値を変更しない書き込み動作を実行するのにエネルギーを費やすのを回避することによって、エネルギー消費量を削減することができる。さらに、多くても一度の書き込み動作しか実行されないので、上記の手法は、命令実行パイプライン内にギャップを導入するのを回避することができる。

10

**【0007】**

特定の実施形態では、方法は、単一のメモリクロックサイクル中に、磁気トンネル接合(MTJ)記憶素子に記憶された第1の値を読み出すことと、第1の値をMTJ記憶素子に記憶されることになる第2の値と比較することと、比較に基づいて、第2の値をMTJ記憶素子に選択的に書き込むことによって、MTJ記憶素子においてメモリ動作を実行することを含む。

20

**【0008】**

別の特定の実施形態では、装置が、磁気トンネル接合(MTJ)記憶素子に結合される回路を含む。上記回路は、単一のメモリクロックサイクル中に、MTJ記憶素子に記憶される第1の値を受信し、MTJ記憶素子に書き込まれることになる第2の値を受信し、第1の値を第2の値と比較し、比較に基づいて、MTJ記憶素子への第2の値の書き込み動作を選択的に可能にするように構成される。

**【0009】**

別の特定の実施形態では、装置が、第1の磁気トンネル接合(MTJ)記憶素子を含むMTJ記憶素子のアレイと、マルチプレクサ(MUX)と、MTJ記憶素子のアレイに、およびMUXに結合される回路と、書き込みパルス発生器とを含む。上記回路は、第1のMTJ記憶素子に記憶された第1の値を受信し、MUXから、第1のMTJ記憶素子に書き込まれることになる第2の値を受信し、第1の値を第2の値と比較し、比較に基づいて、書き込みパルス発生器に書き込みイネーブル信号を選択的に送信するように構成される。

30

**【0010】**

開示される実施形態のうちの少なくとも1つによって提供される1つの特定の利点は、メモリ動作を実行するエネルギー消費量が削減される場合があることである。以下のセクション:図面の簡単な説明、発明を実施するための形態、および特許請求の範囲を含む本出願全体を検討した後、本開示の他の態様、利点、および特徴が明らかになるであろう。

40

**【図面の簡単な説明】**

**【0011】**

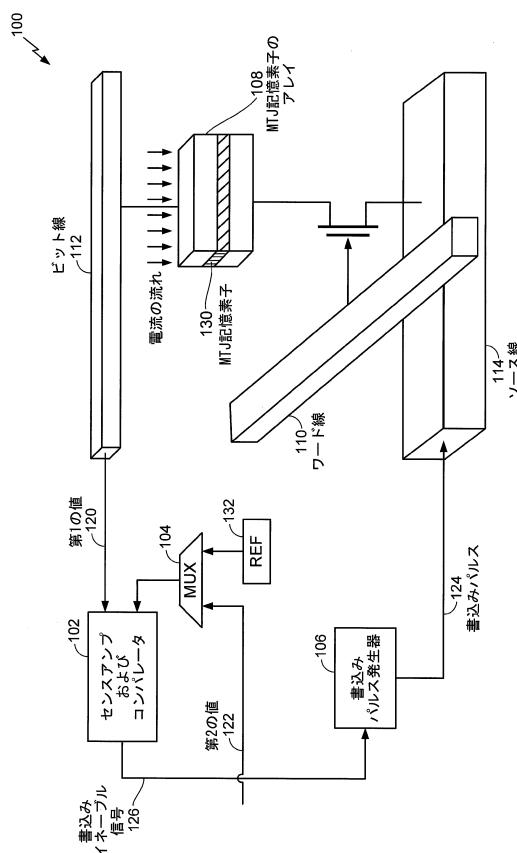

**【図1】**低電力メモリ動作を実行するように動作可能であるシステムの特定の実施形態を例示する図である。

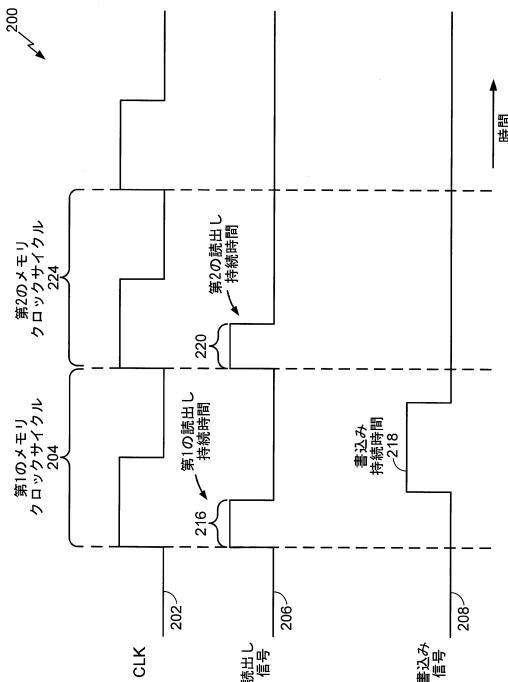

**【図2】**低電力メモリ動作に対応する信号トレースを例示するタイミング図である。

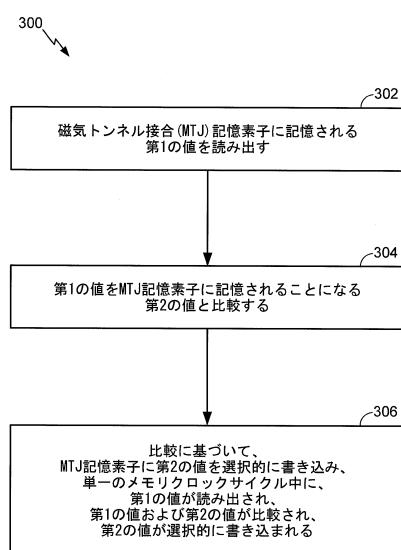

**【図3】**低電力メモリ動作を実行する方法の特定の実施形態を例示する流れ図である。

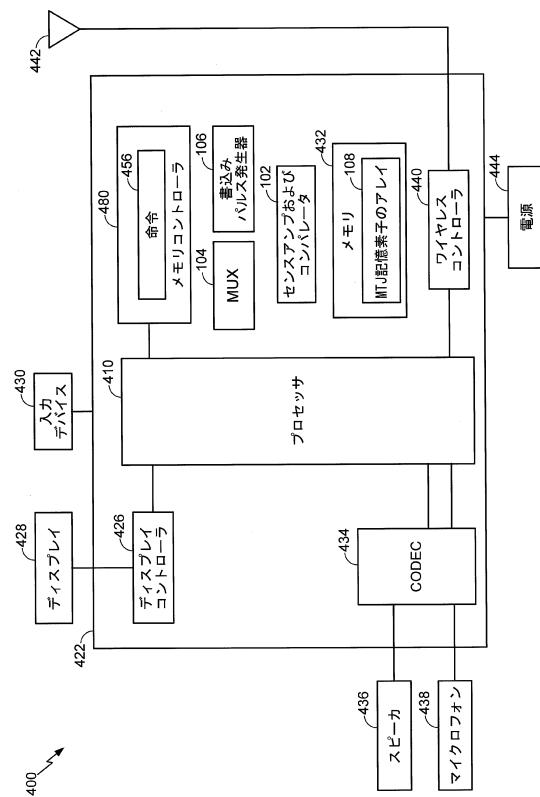

**【図4】**低電力メモリ動作を実行するように動作可能な構成要素を含むデバイスのプロック図である。

**【図5】**図1のシステムを含む電子デバイスを製造するための製造プロセスの特定の例示的な実施形態のデータフロー図である。

50

**【発明を実施するための形態】**

**【0012】**

図1を参照すると、低電力メモリ書き込み動作を実行するシステムの特定の例示的な実施形態が開示され、全体として100で示される。システム100は、MTJ記憶素子のアレイ108を含む。たとえば、システム100は、磁気抵抗ランダムアクセスメモリ(MRAM)デバイスを含む場合がある。MRAMデバイスは、MTJ記憶素子のアレイ108を含む場合がある。各MTJ記憶素子(たとえば、例示的なMTJ記憶素子130)は、論理状態(たとえば、論理0または論理1)を記憶するように構成される場合がある。たとえば、電流を用いて、MTJ記憶素子130の固定磁気層に対してMTJ記憶素子130の自由磁気層の磁気モーメントの向きを揃えることができる。自由磁気層が固定磁気層と同じ向きを有するとき、MTJ記憶素子130は平行状態にある場合があり、第1の抵抗値を有する場合がある。第1の抵抗値は特定の論理状態(たとえば、論理0)を表す場合がある。自由磁気層が固定磁気層と異なる向きを有するとき、MTJ記憶素子130は逆平行状態にある場合があり、第2の抵抗値を有する場合がある。第2の抵抗値は別の特定の論理状態(たとえば、論理1)を表す場合がある。MTJ記憶素子130が読み出されるとき、第1の抵抗値は、特定の論理状態を示す第1の電流値(または第1の電圧値)に対応する場合があり、第2の抵抗値は、他の論理状態を示す第2の電流値(または第2の電圧値)に対応する場合がある。10

**【0013】**

MTJ記憶素子のアレイ108は、複数のMTJ記憶素子の列と、複数のMTJ記憶素子の行とを含む場合がある。たとえば、MTJ記憶素子130は、MTJ記憶素子の第1の列およびMTJ記憶素子の第1の行に含まれる場合がある。MTJ記憶素子のアレイ108の各列は、特定のビット線に対応する場合がある(たとえば、特定のビット線を用いてアクセスされる場合がある)。たとえば、MTJ記憶素子130を含む、第1の列の各MTJ記憶素子は、ビット線112に結合される場合がある。MTJ記憶素子のアレイ108の各行は特定のワード線に対応する場合がある。たとえば、MTJ記憶素子130を含む、第1の行の各MTJ記憶素子は、ワード線110に結合される場合がある。記憶素子のアレイ108の各MTJ記憶素子(たとえば、MTJ記憶素子130)は、図示されるように、ソース線114にも結合される場合がある。20

**【0014】**

各ビット線(たとえば、ビット線112)は、回路(たとえば、センス増幅器(AMP)およびコンパレータ102)に結合される場合がある。特定の実施形態では、センス増幅器およびコンパレータ102は、マルチプレクサ(MUX)104にも結合される場合がある。MUX104は、第1の入力および第2の入力を有する場合がある。MUX104は、制御信号(図示せず)に基づいて、センスAMPおよびコンパレータ102に第1の入力または第2の入力を選択的に与えるように構成される場合がある。たとえば、MUX104は、制御信号が書き込み動作を指示するとき、センスAMPおよびコンパレータ102に第1の入力を与えることができ、制御信号が読み出し動作を指示するとき、センスAMPおよびコンパレータ102に第2の入力を与えることができる。例示するために、MUX104は、制御信号が読み出し動作を指示するとき、センスAMPおよびコンパレータ102に基準値(REF)132を与えることができる。REF132は、特定の論理値(たとえば、論理1)と見なされる最も低い抵抗値を表す基準電圧(または基準電流)に対応することができる。センスAMPおよびコンパレータ102は、書き込みパルス発生器106に結合される場合がある。書き込みパルス発生器106は、ソース線114に結合される場合がある。3040

**【0015】**

動作中に、MTJ記憶素子130に最初に第1の値120が記憶される場合がある。たとえば、MTJ記憶素子130は、特定の論理状態(たとえば、論理0または論理1)に対応する特定の抵抗値を有することができる。システム100に結合されるメモリコントローラが、書き込み要求を(たとえば、プロセッサから)受信することができる。書き込み要求は、指定されたメモリ位置(たとえば、MTJ記憶素子130)に書き込まれることになる第2の値122を含むことができる。書き込み要求に応答して、メモリコントローラは、ビット線112およびワード線110を選択し、それにより、ビット線112とソース線114との間に第1の電流が流れることによって、MTJ記憶素子130において読み出し動作を開始することができる。第1の電流は、MTJ記憶素子150

30を通過することができる。第1の電流は第1の電流量(たとえば、 $10\mu A$ 未満)を有することができ、第1の期間(たとえば、1ナノ秒(ns))にわたって印加することができる。MTJ記憶素子130の論理状態(たとえば、第1の値120)は、MTJ記憶素子130の特定の抵抗に基づいて決定することができる。センス増幅器およびコンパレータ102は、ピット線112から第1の値120を受信することができる。たとえば、センスAMPおよびコンパレータ102は、MTJ記憶素子130を通過した第1の電流を受信することができる。ある特定の実施形態では、第1の電流は第1の電圧に変換される場合がある。この実施形態では、センスAMPおよびコンパレータ102は第1の電圧を受信することができる。

#### 【 0 0 1 6 】

また、メモリコントローラは、センスAMPおよびコンパレータ102に第2の値122も与えることができる。たとえば、メモリコントローラは、MUX104の第1の入力に第2の値122を、そして、MUX104に書き込み動作を指示する制御信号を与えることができる。MUX104は、制御信号が書き込み動作を指示すると判断するのに応答して、センスAMPおよびコンパレータ102に第2の値122を送信することができる。たとえば、MUX104は、センスAMPおよびコンパレータ102に、第2の値122に対応する第2の電流(または第2の電圧)を送信することができる。

。

#### 【 0 0 1 7 】

センスAMPおよびコンパレータ102は、第1の値120および第2の値122を比較することができる。センスAMPおよびコンパレータ102は、その比較に基づいて、MTJ記憶素子130への第2の値122の書き込みを選択的に可能にすることができる。たとえば、センスAMPおよびコンパレータ102は、(たとえば、論理0に対応する)第1の値120および(たとえば、論理1に対応する)第2の値122が一致しないと判断するのに応答して、書き込みイネーブル信号126を生成することができる。この場合、センスAMPおよびコンパレータ102は、書き込みパルス発生器106に書き込みイネーブル信号126を送信することができる。書き込みイネーブル信号126を受信するのに応答して、書き込みパルス発生器106は、ソース線114に書き込みパルス124を送信する。書き込みパルス124に応答して、第2の値122がMTJ記憶素子130に書き込まれる。たとえば、ソース線114およびピット線112が設定され、MTJ記憶素子130の自由磁気層の磁気モーメントの向きを反転することによって、第2の電流がMTJ記憶素子130に記憶された論理値をトグルさせる(たとえば、「反転させる(flip)」)ことができる。特定の実施形態では、ワード線110がアクティブにされるとき、ソース線114を接地し、ピット線112を電源に接続し、ピット線112とソース線114との間に第2の電流を生成することによって、MTJ記憶素子130に論理0を記憶することができる。この実施形態では、ワード線110がアクティブにされるときに、ピット線112を接地し、ソース線114を電源に接続し、ピット線112とソース線114との間に第2の電流を生成することによって、MTJ記憶素子130に論理1を記憶することができる。第2の電流は第2の電流量(たとえば、 $25\mu A$ )を有することができ、第2の期間(たとえば、100ns)にわたって印加することができる。

#### 【 0 0 1 8 】

センスAMPおよびコンパレータ102は、第1の値120および第2の値122が一致すると判断するのに応答して、MTJ記憶素子130に第2の値122が書き込まれるのを抑制することができる。たとえば、センスAMPおよびコンパレータ102は、第1の値120および第2の値122がいずれも論理0または論理1に対応すると判断するのに応答して、書き込みイネーブル信号126を生成するのを抑制することができる。このようにして、センスAMPおよびコンパレータ102は、書き込み動作がMTJ記憶素子内に記憶される値を変更しない状況において、書き込み電流の生成を回避することができる。

#### 【 0 0 1 9 】

特定の実施形態では、メモリコントローラによって開始されるメモリ動作は、单一のメモリクロックサイクル内で実行することができる。たとえば、センスAMPおよびコンパレータ102は、单一のメモリクロックサイクル内で、第1の値120を受信し、第1の値120を第2の値122と比較し、MTJ記憶素子130に第2の値122を選択的に書き込むことができる。

#### 【 0 0 2 0 】

10

20

30

40

50

特定の実施形態では、センスAMPおよびコンパレータ102は、個別のセンスAMPとコンパレータとを含むことができる。この実施形態では、センスAMPはビット線112から第1の値120を受信することができ、REF132を受信することができる。センスAMPは第1の値120を増幅し、増幅された第1の値120をコンパレータに与えることができる。コンパレータは第2の値122も受信することができる。たとえば、メモリコントローラは、第2の値122をコンパレータに与えることができる。コンパレータは第1の値120および第2の値122を比較することができ、比較に基づいて、書き込みイネーブル信号126を選択的に生成することができる。たとえば、コンパレータは、第1の値120および第2の値122に関する排他的論理和(XOR)演算を実行することができ、XOR演算の結果が書き込みイネーブル信号126に対応する。

## 【0021】

10

特定の実施形態では、第1の複数の値(たとえば“01010100”)が、MTJ記憶素子のアレイ108の特定のメモリ位置(たとえば、特定のワード)に記憶される場合がある。プロセッサからの書き込み要求は、第2の複数の値(たとえば“10010100”)が、その特定のワードに書き込まれるであろうことを指示することができる。MTJ記憶素子130は、その特定のワードの特定のビット(たとえば、第2のビット)に対応することができる。書き込み要求に応答して、メモリコントローラは、その特定のワードにおけるメモリ動作を開始することができる。たとえば、メモリコントローラは、その特定のワードに関連付けられる複数のMTJ記憶素子に対応するワード線110および(ビット線112を含む)複数のビット線を選択することができる。センスAMPおよびコンパレータ102は、その特定のワードに記憶される第1の複数の値(たとえば“01010100”)を読み出すことができる。たとえば、センスAMPおよびコンパレータ102は、複数のビット線から、第1の値120を含む第1の複数の値を受信することができる。

## 【0022】

20

センスAMPおよびコンパレータ102は、第1の複数の値を第2の複数の値と比較することができ、比較に基づいて、対応するMTJ記憶素子に第2の複数の値のうちの1つまたは複数を選択的に書き込むことができる。たとえば、センスAMPおよびコンパレータ102は、第1のビット(たとえば、0)および第2のビット(たとえば、1)に対応するMTJ記憶素子に記憶される論理値が、第1のビット(たとえば1)および第2のビット(たとえば0)に記憶されるべき論理値と一致しないと判断することができる。上記判断に応答して、センスAMPおよびコンパレータ102は、第1のビットおよび第2のビットへの書き込みを可能にすことができ、残りのビットへの書き込みを禁止することができる。たとえば、センスAMPおよびコンパレータ102は、第1のビットおよび第2のビットに対応する書き込みパルス発生器(たとえば、書き込みパルス発生器106)に、書き込みイネーブル信号126を送信することができ、残りのビットに対応する書き込みパルス発生器に書き込みイネーブル信号126を送信するのを抑制することができる。特定の実施形態では、センスAMPおよびコンパレータ102は、単一のメモリクロックサイクル内で、第1の複数の値を受信し、第2の複数の値を受信し、第1の複数の値を第2の複数の値と比較し、第2の複数の値のうちの1つまたは複数の書き込み動作を選択的に可能にすることができる。

## 【0023】

30

MTJ記憶素子への書き込みは、MTJ記憶素子からの読み出しよりも、エネルギー消費量が大きい場合がある。MTJ記憶素子に記憶される値がMTJ記憶素子に書き込まれることになる値と一致するときに、MTJ記憶素子に書き込むのを抑制することによって、メモリへの書き込み動作に関連付けられるエネルギー消費量を削減する。さらに、単一のメモリクロックサイクル内でメモリ動作を実行することによって、単一のメモリクロックサイクルよりも長い時間を要するメモリ動作から生じる命令パイプライン内のギャップを防ぐことができる。

## 【0024】

図2を参照すると、低電力メモリ動作に対応する信号トレースを例示するためのタイミング図が開示され、全体として200で示される。特定の実施形態において、このタイミング図は、図1のシステム100におけるメモリ動作に対応することができる。

## 【0025】

40

50

タイミング図200は、クロック信号(CLK)202を含む。CLK202の1サイクルは、メモリクロックサイクル(たとえば、第1のメモリクロックサイクル204または第2のメモリクロックサイクル224)に対応する。また、タイミング図200は、読み出し信号206および書き込み信号208も含む。

#### 【0026】

動作中に、メモリコントローラは、図1を参照しながら詳述されたように、MTJ記憶素子(たとえば、MTJ記憶素子130)の読み出し動作を開始することができる。たとえば、メモリコントローラは、ビット線112とソース線114との間に第1の電流が流れるように、読み出し信号206をアサートすることができる。特定の実施形態では、メモリコントローラは、プロセッサからの書き込み要求に応答して、読み出し信号206を生成することができる。

10

#### 【0027】

たとえば、第1のメモリクロックサイクル204中に、第1の読み出し持続時間216にわたって、読み出し信号206をアサートすることができる。図2に示されるように、第1の読み出し持続時間216は、メモリクロックサイクル204の最初の半分未満に対応することができる。センスAMPおよびコンパレータ102は、第1の読み出し持続時間216の終了時に、または終了付近に第1の値120を受信することができる。センスAMPおよびコンパレータ102は、図1を参照しながら詳述されたように、第1の値120および第2の値122を比較することができ、書き込みイネーブル信号126を選択的に生成することができる。たとえば、センスAMPおよびコンパレータ102は、第1の値120および第2の値122が一致しないと判断するのに応答して、書き込みイネーブル信号126をアクティブにすることができます。書き込みイネーブル信号126に応答して、書き込みパルス発生器106は、ビット線112とソース線114との間に第2の電流が流れるように書き込みパルス124を生成することができる。特定の実施形態において、書き込み信号208は、書き込みパルス124に対応することができる。書き込み信号208は、書き込み持続時間218にわたってアクティブにされる場合がある。図2に示されるように、書き込み持続時間218は第1の読み出し持続時間216よりも長い場合があるが、第1の読み出し持続時間216および書き込み持続時間218はいずれも単一の第1のメモリクロックサイクル204中に生じることができます。

20

#### 【0028】

別の例として、第2のメモリクロックサイクル224中に、メモリコントローラは、MTJ記憶素子(たとえば、MTJ記憶素子130)に対するプロセッサからの別の書き込み要求に応答して、読み出し信号206を再アサートすることができる。先行する書き込み要求が単一の第1のメモリクロックサイクル204内で処理され、命令実行パイプライン内にギャップを導入しないので、読み出し信号206は、第1のメモリクロックサイクル204後の次のメモリクロックサイクル(たとえば、第2のメモリクロックサイクル224)中にアサートすることができる。読み出し信号206は、第2の読み出し持続時間220にわたってアサートされる場合がある。センスAMPおよびコンパレータ102は、MTJ記憶素子130によって記憶される値が、MTJ記憶素子130に書き込まれることになる別の値と一致すると判断する場合がある。上記判断に応答して、センスAMPおよびコンパレータ102は、第2のメモリクロックサイクル224中に書き込み信号208をアクティブにしないことができる。

30

#### 【0029】

単一のメモリクロックサイクル内でメモリ動作を実行することによって、単一のメモリクロックサイクルよりも長い時間を要するメモリ動作から生じる命令パイプライン内のギャップを防ぐことができる。

40

#### 【0030】

図3は、低電力メモリ動作を実行する方法300の特定の実施形態を例示する流れ図である。例示的な実施形態では、方法300は、図1のシステム100によって実行される場合がある。

#### 【0031】

方法300は、302において、磁気トンネル接合(MTJ)記憶素子に記憶された第1の値を読み出すことを含む。たとえば、図1のセンスAMPおよびコンパレータ102は、図1を参照しながら詳述されたように、MTJ記憶素子130に記憶された第1の値120を読み出すことができる。

50

## 【 0 0 3 2 】

また、方法300は、304において、第1の値を、MTJ記憶素子に記憶されることになる第2の値と比較することも含む。たとえば、センスAMPおよびコンパレータ102は、図1を参照しながら詳述されたように、第1の値120を第2の値122と比較することができる。

## 【 0 0 3 3 】

方法300はさらに、306において、比較に基づいて、MTJ記憶素子に第2の値を選択的に書き込むことを含む。単一のメモリクロックサイクル中に、第1の値が読み出され、第1の値および第2の値が比較され、第2の値が選択的に書き込まれる。たとえば、センスAMPおよびコンパレータ102は、図1を参照しながら詳述されたように、比較に基づいて、MTJ記憶素子130に第2の値122を選択的に書き込むことができる。例示するために、第1の値120が第2の値122と一致しないと判断するのに応答して、センスAMPおよびコンパレータ102は、MTJ記憶素子130に第2の値122を書き込むために、書き込みイネーブル信号126を生成することができる。第1の値120が第2の値122と一致すると判断するのに応答して、センスAMPおよびコンパレータ102は、書き込みイネーブル信号126を生成するのを抑制することができる。図1～図2を参照しながら詳述されたように、単一のメモリクロックサイクル中に、センスAMPおよびコンパレータ102は、第1の値120を読み出し、第1の値120および第2の値122を比較し、第2の値122を選択的に書き込むことができる。10

## 【 0 0 3 4 】

方法300は、MTJ記憶素子に記憶された値がMTJ記憶素子に書き込まれることになる値に一致するときに、MTJ記憶素子に書き込むのを抑制することができ、それにより、メモリへの書き込み動作に関連付けられるエネルギー消費量を削減することができる。さらに、単一のメモリクロックサイクル中にメモリ動作を実行することによって、命令パイプライン内のギャップの導入を防ぐことができる。20

## 【 0 0 3 5 】

図3の方法300は、中央処理装置(CPU)、フィールドプログラマブルゲートアレイ(FPGA)デバイス、特定用途向け集積回路(ASIC)、コントローラ、別のハードウェアデバイス、ファームウェアデバイス、またはそれらの任意の組合せなどの処理ユニットによって開始される場合がある。

## 【 0 0 3 6 】

図4を参照すると、デバイスのブロック図が開示され、全体として400で示される。デバイス400(たとえば、ワイヤレスデバイス)は、メモリ432に結合される、デジタルシグナルプロセッサ(DSP)または中央処理装置(CPU)のようなプロセッサ410を含む。メモリ432は、図1のMTJ記憶素子のアレイ108を含むことができる。また、デバイス400は、プロセッサ410およびディスプレイ428に結合されるディスプレイコントローラ426を含む。コーダ/デコーダ(CODEC)434も、プロセッサ410に結合される場合がある。スピーカ436およびマイクロフォン438が、CODEC434に結合される場合がある。30

## 【 0 0 3 7 】

図4はさらに、ワイヤレスコントローラ440がプロセッサ410およびアンテナ442に結合される場合があることを示す。デバイス400は、図1のMUX104、書き込みパルス発生器106、センスAMPおよびコンパレータ102、またはその組合せを含むことができる。デバイス400は、メモリコントローラ480を含む場合がある。メモリコントローラ480は、実行可能命令456を含む有形の非一時的プロセッサ可読記憶媒体とすることができます。命令456は、動作、関数および/または方法のうちの1つまたは複数を実行するか、またはその実行を開始するために、メモリコントローラ480内のプロセッサのようなプロセッサによって実行される場合がある。特定の実施形態では、メモリコントローラ480は、図1に関して説明されたメモリコントローラに対応することができる。40

## 【 0 0 3 8 】

特定の実施形態では、プロセッサ410、ディスプレイコントローラ426、メモリ432、CODEC434、メモリコントローラ480、MUX104、書き込みパルス発生器106、センスAMPおよびコンパレータ102、ならびにワイヤレスコントローラ440は、システムインパッケージまたはシ50

システムオンチップデバイス422に含まれる。特定の実施形態において、入力デバイス430および電源444がシステムオンチップデバイス422に結合される。さらに、特定の実施形態では、図4に示されるように、ディスプレイ428、入力デバイス430、スピーカ436、マイクロフォン438、アンテナ442、および電源444は、システムオンチップデバイス422の外部にある。しかしながら、ディスプレイ428、入力デバイス430、スピーカ436、マイクロフォン438、アンテナ442、および電源444の各々は、インターフェースまたはコントローラなどのシステムオンチップデバイス422の構成要素に結合することができる。

#### 【 0 0 3 9 】

説明された実施形態に関連して、本装置が、第1のデータ要素を含む複数のデータ要素を記憶するための第1の手段を含む。たとえば、記憶するための第1の手段は、図1または図4のMTJ記憶素子のアレイ108、または複数のデータ要素を記憶するように構成される1つまたは複数の他のデバイスもしくは回路、またはその任意の組合せを含むことができる。10

#### 【 0 0 4 0 】

また、本装置は、第1のデータ要素において記憶される第1の値を受信するための第1の手段も含む。たとえば、受信するための第1の手段は、図1または図4のセンスAMPおよびコンパレータ102、または第1の値を受信するように構成される1つまたは複数の他のデバイスもしくは回路、またはその任意の組合せを含むことができる。

#### 【 0 0 4 1 】

本装置はさらに、マルチプレクサ(MUX)から、第1のデータ要素に書き込まれることになる第2の値を受信するための第2の手段を含む。たとえば、受信するための第2の手段は、図1または図4のセンスAMPおよびコンパレータ102、または第2の値を受信するように構成される1つまたは複数の他のデバイスもしくは回路、またはその任意の組合せを含むことができる。20

#### 【 0 0 4 2 】

また、本装置は、第1の値を第2の値と比較するための手段を含む。たとえば、比較するための手段は、図1または図4のセンスAMPおよびコンパレータ102、または比較するように構成される1つまたは複数の他のデバイスもしくは回路、またはその任意の組合せを含むことができる。

#### 【 0 0 4 3 】

本装置はさらに、比較するための手段からの結果に基づいて、書き込みパルスを生成するための手段に書き込みイネーブル信号を選択的に送信するための手段を含む。書き込みパルスは、第1のデータ要素への第2の値の書き込みを可能にする。たとえば、選択的に送信するための手段は、図1または図4のセンスAMPおよびコンパレータ102、または書き込みイネーブル信号を選択的に送信するように構成される1つまたは複数の他のデバイスもしくは回路、またはその任意の組合せを含むことができる。たとえば、選択的に送信するための手段は、第1の値が第2の値と一致することを指示する比較するための手段からの結果に応答して、書き込みイネーブル信号を送信するのを抑制することができる。別の例として、選択的に送信するための手段は、第1の値が第2の値に一致しないことを指示する比較するための手段からの結果に応答して、書き込みイネーブル信号を送信することができる。30

#### 【 0 0 4 4 】

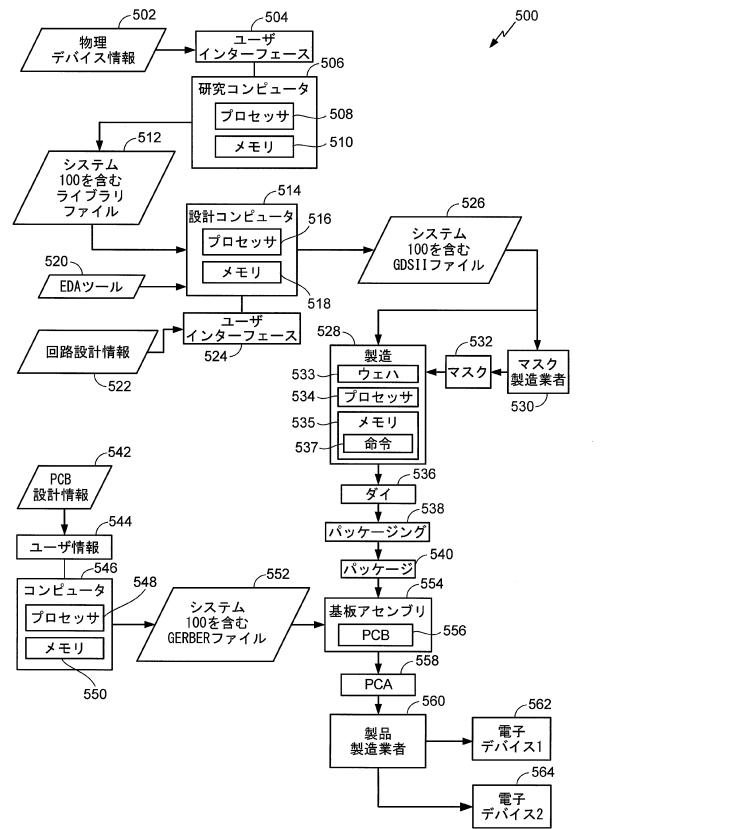

上記の開示されたデバイスや機能は、コンピュータ可読媒体上に記憶されるコンピュータファイル(たとえばRTL、GDSII、GERBERなど)の形に設計し、構成することができる。一部のまたはすべてのそのようなファイルは、そのようなファイルに基づいてデバイスを製造する製造取扱者に供給することができる。結果として生じる製造物は、その後にダイに切断され、チップにパッケージされるウェハを含む。それらのチップは、その後、限定はしないが、モバイルフォン、通信デバイス、セットトップボックス、音楽プレーヤ、ビデオプレーヤ、エンターテインメントユニット、ナビゲーションデバイス、携帯情報端末(PDA)、固定位置データユニット、またはコンピュータを含むデバイスにおいて利用される。図5は、電子デバイス製造プロセス500の特定の例示的実施形態を示す。

#### 【 0 0 4 5 】

10

20

30

40

50

物理デバイス情報502が、製造プロセス500、たとえば、研究コンピュータ506において受信される。物理デバイス情報502は、システム100(または図1のMUX104、書き込みパルス発生器106、センスAMPおよびコンパレータ102、MTJ記憶素子のアレイ108のようなその任意の構成要素、またはその任意の組合せ)のような、半導体デバイスの少なくとも1つの物理的特性を表す設計情報を含むことができる。たとえば、物理デバイス情報502は、研究コンピュータ506に結合されたユーザインターフェース504を介して入力される物理パラメータ、材料特性、および構造情報を含むことができる。研究コンピュータ506は、メモリ510などのコンピュータ可読媒体に結合された、1つまたは複数の処理コアなどのプロセッサ508を含む。メモリ510は、プロセッサ508に、物理デバイス情報502をファイルフォーマットに準拠するように変換させ、ライブラリファイル512を生成させるように実行可能なコンピュータ可読命令を記憶することができる。10

#### 【 0 0 4 6 】

特定の実施形態では、ライブラリファイル512は、変換された設計情報を含む少なくとも1つのデータファイルを含む。たとえば、ライブラリファイル512は、電子設計自動化(EDA:electronic design automation)ツール520で使用するために提供される、システム100(または図1のMUX104、書き込みパルス発生器106、センスAMPおよびコンパレータ102、MTJ記憶素子のアレイ108のようなその任意の構成要素、またはその任意の組合せ)を含むデバイスを含む半導体デバイスのライブラリを含むことができる。

#### 【 0 0 4 7 】

ライブラリファイル512は、メモリ518に結合された、1つまたは複数の処理コアなどのプロセッサ516を含む設計コンピュータ514において、EDAツール520とともに使用することができる。EDAツール520は、設計コンピュータ514のユーザが、ライブラリファイル512から、システム100(または図1のMUX104、書き込みパルス発生器106、センスAMPおよびコンパレータ102、MTJ記憶素子のアレイ108のようなその任意の構成要素、またはその任意の組合せ)を含む回路を設計できるようにするために、メモリ518においてプロセッサ実行可能命令として記憶することができる。たとえば、設計コンピュータ514のユーザは、設計コンピュータ514に結合されたユーザインターフェース524を介して回路設計情報522を入力することができる。回路設計情報522は、システム100(または図1のMUX104、書き込みパルス発生器106、センスAMPおよびコンパレータ102、MTJ記憶素子のアレイ108のようなその任意の構成要素、またはその任意の組合せ)のような、半導体デバイスの少なくとも1つの物理的特性を表す設計情報を含むことができる。例示するために、回路設計特性は、特定の回路の識別および回路設計内の他の要素に対する関係、位置決め情報、フィーチャサイズ情報、相互接続情報、または半導体デバイスの物理的特性を表す他の情報を含むことができる。2030

#### 【 0 0 4 8 】

設計コンピュータ514は、回路設計情報522を含む設計情報をファイルフォーマットに準拠するように変換するように構成することができる。例示するために、ファイルフォーマットは、回路レイアウトについての平面幾何形状、テキストラベル、および他の情報をグラフィックデータシステム(GDSII)ファイルフォーマットなどの階層フォーマットにおいて表すデータベースバイナリファイルフォーマットを含むことができる。設計コンピュータ514は、他の回路または情報に加えて、システム100(または図1のMUX104、書き込みパルス発生器106、センスAMPおよびコンパレータ102、MTJ記憶素子のアレイ108のようなその任意の構成要素、またはその任意の組合せ)を記述する情報を含む、GDSIIファイル526のような変換された設計情報を含むデータファイルを生成するように構成することができる。例示するために、データファイルは、システム100(または図1のMUX104、書き込みパルス発生器106、センスAMPおよびコンパレータ102、MTJ記憶素子のアレイ108のようなその任意の構成要素、またはその任意の組合せ)を含み、システムオンチップ(SOC)内に追加の電子回路および構成要素をさらに含む、SOCに対応する情報を含むことができる。40

#### 【 0 0 4 9 】

GDSIIファイル526は、システム100(または図1のMUX104、書き込みパルス発生器106、セン50

スAMPおよびコンパレータ102、MTJ記憶素子のアレイ108のようなその任意の構成要素、またはその任意の組合せ)を、GDSIIファイル526の中の変換された情報に従って製造するために、製造プロセス528において受信される場合がある。たとえば、デバイス製造プロセスは、典型的なマスク532として示される、フォトリソグラフィプロセスとともに使用されるマスクなどの、1つまたは複数のマスクを作製するために、マスク製造業者530にGDSIIファイル526を提供することを含むことができる。マスク532は、試験され、その後、典型的なダイ536などのダイに分離することができる1つまたは複数のウェハ534を生成するために製作プロセス中に使用される場合がある。ダイ536は、システム100(または図1のMUX104、書き込みパルス発生器106、センスAMPおよびコンパレータ102、MTJ記憶素子のアレイ108のようなその任意の構成要素、またはその任意の組合せ)を含むデバイスを含む回路を含む。

10

#### 【 0 0 5 0 】

ダイ536は、パッケージングプロセス538に与えられる場合があり、そのプロセスにおいて、ダイ536は、典型的なパッケージ540に組み込まれる。たとえば、パッケージ540は、システムインパッケージ(SiP)配置などの、単一のダイ536または複数のダイを含むことができる。パッケージ540は、電子デバイスエンジニアリング連合評議会(JEDEC)規格などの1つまたは複数の規格または仕様に準拠するように構成することができる。

#### 【 0 0 5 1 】

パッケージ540に関する情報は、コンピュータ546に記憶されるコンポーネントライブリなどを介して、種々の製品設計者に配布することができる。コンピュータ546は、メモリ550に結合された1つまたは複数の処理コアなどのプロセッサ548を含むことができる。プリント回路板(PCB)ツールを、ユーザインターフェース544を介してコンピュータ546のユーザから受信されたPCB設計情報542を処理するために、プロセッサ実行可能命令としてメモリ550に記憶することができる。PCB設計情報542は、回路基板上のパッケージングされた半導体デバイスの物理的な位置決め情報を含むことができ、パッケージングされた半導体デバイスは、システム100(または図1のMUX104、書き込みパルス発生器106、センスAMPおよびコンパレータ102、MTJ記憶素子のアレイ108のようなその任意の構成要素、またはその任意の組合せ)を含む、パッケージ540に対応する。

20

#### 【 0 0 5 2 】

コンピュータ546は、PCB設計情報542を変換して、回路基板上のパッケージングされた半導体デバイスの物理的な位置決め情報とともに、配線およびビアのような電気的な接続のレイアウトを含むデータを有するGERBERファイル552のようなデータファイルを生成するように構成することができ、パッケージングされた半導体デバイスは、システム100(または図1のMUX104、書き込みパルス発生器106、センスAMPおよびコンパレータ102、MTJ記憶素子のアレイ108のようなその任意の構成要素、またはその任意の組合せ)を含む、パッケージ540に対応する。別の実施形態では、変換されたPCB設計情報によって生成されるデータファイルは、GERBERフォーマット以外のフォーマットを有することができる。

30

#### 【 0 0 5 3 】

GERBERファイル552は、基板組立てプロセス554において受信される場合があり、GERBERファイル552内に記憶される設計情報に従って製造される、典型的なPCB556などのPCBを作製するために使用される場合がある。たとえば、GERBERファイル552は、PCB生産プロセスの種々のステップを実行するために、1つまたは複数の機械にアップロードすることができる。PCB556には、パッケージ540を含む電子構成要素が実装され、典型的なプリント回路アセンブリ(PCA)558を形成することができる。

40

#### 【 0 0 5 4 】

PCA558は、製品製造プロセス560において受け取られ、第1の典型的な電子デバイス562および第2の典型的な電子デバイス564などの1つまたは複数の電子デバイスに組み込まれる場合がある。例示的で非限定的な例として、第1の典型的な電子デバイス562、第2の典型的な電子デバイス564、または両方は、システム100(または図1のMUX104、書き込みパルス発生器106、センスAMPおよびコンパレータ102、MTJ記憶素子のアレイ108のようなその任

50

意の構成要素、またはその任意の組合せ)が組み込まれるモバイルフォン、セットトップボックス、音楽プレーヤ、ビデオプレーヤ、エンターテインメントユニット、ナビゲーションデバイス、通信デバイス、携帯情報端末(PDA)、固定位置データユニット、およびコンピュータのグループから選択することができる。別の例示的で非限定的な例として、電子デバイス562および564のうちの1つまたは複数は、モバイルフォン、ハンドヘルドパソコン通信システム(PCS)ユニット、携帯情報端末などのポータブルデータユニット、全地球測位システム(GPS)対応デバイス、ナビゲーションデバイス、メータ検針機器などの固定位置データユニット、または、データもしくはコンピュータ命令を記憶するか、もしくは引き出す任意の他のデバイス、またはそれらの任意の組合せなどの、遠隔ユニットとすることができる。図5は、本開示の教示による遠隔ユニットを示しているが、本開示は、これらの例示されたユニットに限定されない。本開示の実施形態は、メモリおよびオンチップ回路を含む能動集積回路を含む任意のデバイスにおいて適切に使用することができる。

#### 【0055】

システム100(または図1のMUX104、書き込みパルス発生器106、センスAMPおよびコンパレータ102、MTJ記憶素子のアレイ108のようなその任意の構成要素、またはその任意の組合せ)を含むデバイスは、例示的なプロセス500において説明されるように、製造され、処理され、電子デバイスに組み込まれる場合がある。図1～図4に関して開示した実施形態の1つまたは複数の態様が、ライブラリファイル512、GDSIIファイル526、およびGERBERファイル552内など様々な処理段階で含まれてよいのと同様に、研究コンピュータ506のメモリ510、設計コンピュータ514のメモリ518、コンピュータ546のメモリ550、基板組立てプロセス554など様々な段階で使用される1つまたは複数の他のコンピュータまたはプロセッサ(図示せず)のメモリに記憶され、さらにマスク532、ダイ536、パッケージ540、PCA558、プロトタイプ回路もしくはデバイス(図示せず)などの他の製品、またはそれらの任意の組合せなどの、1つまたは複数の他の物理的な実施形態に組み込まれてよい。物理デバイス設計から最終製品まで生産の種々の典型的な段階が表されるが、他の実施形態では、より少ない段階を使用される場合があるか、または追加の段階が含まれる場合がある。同様に、プロセス500は単一のエンティティによってまたはプロセス500の種々の段階を実行する1つまたは複数のエンティティによって実行される場合がある。

#### 【0056】

当業者はさらに、本明細書において開示される実施形態に関連して説明された種々の例示的な論理ブロック、構成、モジュール、回路、およびアルゴリズムステップが、電子ハードウェア、プロセッサによって実行されるコンピュータソフトウェア、または両方の組合せとして実現できることは理解されよう。種々の例示的な構成要素、ブロック、構成、モジュール、回路、およびステップは、これまで、それらの機能の観点から包括的に説明されてきた。そのような機能が、ハードウェアとして実現されるか、プロセッサ実行可能命令として実現されるかは、特定のアプリケーションと、システム全体に課される設計制約とによって決まる。当業者は、説明された機能を特定のアプリケーションごとに種々の方法で実現することができるが、そのような実施態様の決定は、本開示の範囲からの逸脱を引き起こすと解釈されるべきではない。

#### 【0057】

本明細書において開示される実施形態との関連において説明された方法またはアルゴリズムのステップは、ハードウェアにおいて直接に、または、プロセッサによって実行されるソフトウェアモジュールにおいて、またはこの2つの組合せにおいて具現される場合がある。ソフトウェアモジュールは、ランダムアクセスメモリ(RAM)、フラッシュメモリ、読み取り専用メモリ(ROM)、プログラム可能読み取り専用メモリ(PROM)、消去可能プログラム可能読み取り専用メモリ(EPROM)、電気的消去可能プログラム可能読み取り専用メモリ(EEPROM)、レジスタ、ハードディスク、リムーバブルディスク、コンパクトディスク読み取り専用メモリ(CD-ROM)、または当技術分野において既知の任意の他の形の非一時的記憶媒体内に存在することができる。例示的な記憶媒体は、プロセッサが記憶媒体から情報を読み取り

10

20

30

40

50

、記憶媒体に情報を書き込むことができるように、プロセッサに結合される。代替形態では、記憶媒体は、プロセッサと一緒に構成することができる。プロセッサおよび記憶媒体は特定用途向け集積回路(ASIC)内に存在することができる。ASICは、コンピューティングデバイスまたはユーザ端末内に存在することができる。代替形態では、プロセッサおよび記憶媒体は、コンピューティングデバイスまたはユーザ端末内に別個の構成要素として存在することができる。

## 【0058】

開示される実施形態のこれまでの説明は、当業者が開示される実施形態を作製または使用できるようにするために提供される。これらの実施形態に対する種々の変更は、当業者には容易に明らかになり、本明細書において規定された原理は、本開示の範囲から逸脱することなく、他の実施形態に適用することができる。したがって、本開示は、本明細書に示される実施形態に限定されることを意図するものではなく、以下の特許請求の範囲によって規定される原理および新規な特徴と一致する、取り得る最も広い範囲を与えられるべきである。

## 【符号の説明】

## 【0059】

|     |                             |    |

|-----|-----------------------------|----|

| 100 | システム                        |    |

| 102 | センス増幅器(AMP)およびコンパレータ        |    |

| 104 | マルチプレクサ(MUX)                |    |

| 108 | MTJ記憶素子のアレイ                 | 20 |

| 110 | ワード線                        |    |

| 112 | ビット線                        |    |

| 114 | ソース線                        |    |

| 120 | 第1の値                        |    |

| 122 | 第2の値                        |    |

| 124 | 書き込みパルス                     |    |

| 126 | 書き込みイネーブル信号                 |    |

| 130 | MTJ記憶素子                     |    |

| 132 | 基準値(REF)                    |    |

| 200 | タイミング図                      | 30 |

| 202 | クロック信号(CLK)                 |    |

| 204 | 第1のメモリクロックサイクル              |    |

| 206 | 読み出し信号                      |    |

| 208 | 書き込み信号                      |    |

| 216 | 第1の読み出し持続時間                 |    |

| 218 | 書き込み持続時間                    |    |

| 220 | 第2の読み出し持続時間                 |    |

| 224 | 第2のメモリクロックサイクル              |    |

| 400 | デバイス                        |    |

| 410 | プロセッサ                       | 40 |

| 422 | システムインパッケージまたはシステムオンチップデバイス |    |

| 426 | ディスプレイコントローラ                |    |

| 428 | ディスプレイ                      |    |

| 430 | 入力デバイス                      |    |

| 432 | メモリ                         |    |

| 434 | コーダ/デコーダ(CODEC)             |    |

| 436 | スピーカ                        |    |

| 438 | マイクロフォン                     |    |

| 440 | ワイヤレスコントローラ                 |    |

| 442 | アンテナ                        | 50 |

|     |                  |    |

|-----|------------------|----|

| 444 | 電源               |    |

| 456 | 実行可能命令           |    |

| 480 | メモリコントローラ        |    |

| 500 | 電子デバイス製造プロセス     |    |

| 502 | 物理デバイス情報         |    |

| 504 | ユーザインターフェース      |    |

| 506 | 研究コンピュータ         |    |

| 508 | プロセッサ            |    |

| 510 | メモリ              |    |

| 512 | ライブラリファイル        | 10 |

| 514 | 設計コンピュータ         |    |

| 516 | プロセッサ            |    |

| 518 | メモリ              |    |

| 520 | 電子設計自動化(EDA)ツール  |    |

| 522 | 回路設計情報           |    |

| 524 | ユーザインターフェース      |    |

| 526 | GDSIIファイル        |    |

| 528 | 製造プロセス           |    |

| 530 | マスク製造業者          |    |

| 532 | マスク              | 20 |

| 534 | ウェハ              |    |

| 536 | ダイ               |    |

| 538 | パッケージングプロセス      |    |

| 540 | パッケージ            |    |

| 542 | PCB設計情報          |    |

| 544 | ユーザインターフェース      |    |

| 546 | コンピュータ           |    |

| 548 | プロセッサ            |    |

| 550 | メモリ              |    |

| 552 | GERBERファイル       | 30 |

| 554 | 基板組立てプロセス        |    |

| 556 | PCB              |    |

| 558 | プリント回路アセンブリ(PCA) |    |

| 560 | 製品製造プロセス         |    |

| 562 | 第1の典型的な電子デバイス    |    |

| 564 | 第2の典型的な電子デバイス    |    |

【図1】

【図2】

【図3】

【図4】

【図5】

---

フロントページの続き

(72)発明者 ルー・ゴー・チュア - エオアン

アメリカ合衆国・カリフォルニア・92121-1714・サン・ディエゴ・モアハウス・ドライ

ヴ・5775

審査官 後藤 彰

(56)参考文献 国際公開第2013/105414 (WO, A1)

特開2010-33620 (JP, A)

特開2007-193931 (JP, A)

米国特許出願公開第2009/0097336 (US, A1)

特表2013-529350 (JP, A)

米国特許出願公開第2010/0232206 (US, A1)

米国特許第6052302 (US, A)

特開2003-16778 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G11C 11/16