(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2008-252068

(P2008-252068A)

(43) 公開日 平成20年10月16日(2008.10.16)

| (51) Int.Cl.                 | F 1        | テーマコード (参考) |

|------------------------------|------------|-------------|

| <b>H01L 29/786 (2006.01)</b> | H01L 29/78 | 626C 5F083  |

| <b>H01L 21/336 (2006.01)</b> | H01L 29/78 | 627G 5F110  |

| <b>H01L 21/20 (2006.01)</b>  | H01L 29/78 | 616T 5F152  |

| <b>H01L 27/28 (2006.01)</b>  | H01L 29/78 | 618D        |

| <b>H01L 51/05 (2006.01)</b>  | H01L 21/20 |             |

審査請求 未請求 請求項の数 18 O.L. (全 27 頁) 最終頁に続く

|              |                            |          |                                                |

|--------------|----------------------------|----------|------------------------------------------------|

| (21) 出願番号    | 特願2008-22286 (P2008-22286) | (71) 出願人 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (22) 出願日     | 平成20年2月1日(2008.2.1)        | (72) 発明者 | 大沼 英人<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (31) 優先権主張番号 | 特願2007-58582 (P2007-58582) | (72) 発明者 | 磯部 敦生<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (32) 優先日     | 平成19年3月8日(2007.3.8)        | (72) 発明者 | 郷戸 宏充<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (33) 優先権主張国  | 日本国(JP)                    |          |                                                |

最終頁に続く

(54) 【発明の名称】半導体装置及びその作製方法

## (57) 【要約】

【課題】S値が小さくオン電流の低下が抑えられた応答性のよい半導体装置の構成及び作製方法を提案する。

【解決手段】ソース領域又はドレイン領域の膜厚がチャネル形成領域の膜厚より厚く形成されている。このような半導体装置の作製方法としては、まず基板上に設けられた絶縁層により形成される凹凸上に非晶質半導体層を形成し、非晶質半導体層にレーザビームを照射して非晶質半導体を溶融することにより膜厚の異なる結晶質半導体層を形成する。そして、結晶質半導体層の膜厚の厚い部分に不純物を添加することによりソース領域又はドレイン領域を形成し、不純物が添加されない領域をチャネル形成領域とし、ソース領域又はドレイン領域と電気的に接続する導電層を形成することにより作製することができる。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

絶縁基板上に設けられた第1の絶縁層と、

前記第1の絶縁層上に設けられた複数の第2の絶縁層と、

前記第1の絶縁層及び前記複数の第2の絶縁層上に設けられた結晶質半導体層と、を有し、

前記第1の絶縁層と前記複数の第2の絶縁層によって凹部と凸部が設けられ、

前記結晶質半導体層は、前記凸部上にチャネル形成領域と、前記凹部上にソース領域又はドレイン領域とを有し、

前記結晶質半導体層は、非晶質半導体層を溶融することにより形成されることを特徴とする半導体装置。 10

**【請求項 2】**

請求項1において、

前記複数の第2の絶縁層の形状は、ストライプパターンであることを特徴とする半導体装置。

**【請求項 3】**

絶縁基板上に設けられた第1の絶縁層と、

前記第1の絶縁層上に設けられた第2の絶縁層と、

前記第2の絶縁層上にチャネル形成領域と、前記第1の絶縁層上であって前記第2の絶縁層が設けられない部分にソース領域又はドレイン領域とを有する結晶質半導体層と、を有し、

前記結晶質半導体層は、非晶質半導体層を溶融することにより形成されることを特徴とする半導体装置。 20

**【請求項 4】**

請求項1乃至請求項3のいずれか一項において、

前記結晶質半導体層上に設けられた第3の絶縁層と、

前記第3の絶縁層を介して前記チャネル形成領域上に設けられた導電層と、を有することを特徴とする半導体装置。

**【請求項 5】**

請求項1乃至請求項4のいずれか一項において、

前記チャネル形成領域の膜厚は10nm以上50nm以下であることを特徴とする半導体装置。 30

**【請求項 6】**

請求項1乃至請求項5のいずれか一項において、

前記ソース領域又は前記ドレイン領域の膜厚が、前記チャネル形成領域の膜厚よりも厚いことを特徴とする半導体装置。

**【請求項 7】**

絶縁基板上に第1の絶縁層を形成し、

前記第1の絶縁層上に複数の第2の絶縁層を形成し、

前記第1の絶縁層と前記複数の第2の絶縁層によって設けられる凹部及び凸部上に非晶質半導体層を形成し、

前記非晶質半導体層にレーザビームを照射して結晶質半導体層を形成し、

前記結晶質半導体層の一部に不純物元素を添加することによって、前記凹部上の前記結晶質半導体層に前記不純物元素が添加されたソース領域又はドレイン領域と、前記凸部上の前記結晶質半導体層に前記不純物元素が添加されないチャネル形成領域とを形成することを特徴とする半導体装置の作製方法。 40

**【請求項 8】**

請求項7において、

前記複数の第2の絶縁層は、前記第1の絶縁層上に層を設け、当該層をエッチングすることによりストライプパターンに形成することを特徴とする半導体装置の作製方法。 50

**【請求項 9】**

請求項 7 において、

前記複数の第 2 の絶縁層は、前記第 1 の絶縁層上に層を設け、当該層をエッチングすることによりストライプパターンに形成し、

前記レーザビームは線状ビームであり、

前記ストライプパターンが延在する方向と平行な方向に前記レーザビームを走査することを特徴とする半導体装置の作製方法。

**【請求項 10】**

請求項 7 乃至請求項 9 のいずれか一項において、

前記結晶質半導体層上に第 3 の絶縁層を形成し、

前記第 3 の絶縁層を介して前記凸部上に導電層を形成し、

前記導電層をマスクとして、前記結晶質半導体層の一部に前記不純物元素を添加することを特徴とする半導体装置の作製方法。

10

**【請求項 11】**

絶縁基板上に第 1 の絶縁層を形成し、

前記第 1 の絶縁層上に第 2 の絶縁層を形成し、

前記第 1 の絶縁層及び前記第 2 の絶縁層上に非晶質半導体層を形成し、

前記非晶質半導体層にレーザビームを照射して結晶質半導体層を形成し、

前記結晶質半導体層の一部に不純物元素を添加することによって、前記第 1 の絶縁層上であって前記第 2 の絶縁層が設けられない部分に形成された結晶質半導体層に前記不純物元素が添加されたソース領域又はドレイン領域と、前記第 2 の絶縁層上の前記結晶質半導体層に前記不純物元素が添加されないチャネル形成領域とを形成することを特徴とする半導体装置の作製方法。

20

**【請求項 12】**

請求項 11 において、

前記第 2 の絶縁層は、前記第 1 の絶縁層上に層を設け、当該層をエッチングすることによりストライプパターンに形成することを特徴とする半導体装置の作製方法。

**【請求項 13】**

請求項 11 において、

前記第 2 の絶縁層は、前記第 1 の絶縁層上に層を設け、当該層をエッチングすることによりストライプパターンに形成し、

30

前記レーザビームは線状ビームであり、

前記ストライプパターンが延在する方向と平行な方向に前記レーザビームを走査することを特徴とする半導体装置の作製方法。

**【請求項 14】**

請求項 11 乃至請求項 13 のいずれか一項において、

前記結晶質半導体層上に第 3 の絶縁層を形成し、

前記第 3 の絶縁層を介して前記第 2 の絶縁層上に導電層を形成し、

前記導電層をマスクとして、前記結晶質半導体層の一部に前記不純物元素を添加することを特徴とする半導体装置の作製方法。

40

**【請求項 15】**

請求項 7 乃至請求項 14 のいずれか一項において、

前記非晶質半導体層に前記レーザビームを照射することによって、前記非晶質半導体層が溶融されることを特徴とする半導体装置の作製方法。

**【請求項 16】**

請求項 7 乃至請求項 15 のいずれか一項において、

前記レーザビームは、連続発振のレーザから発振するレーザビーム又は 10 MHz 以上の周波数で発振するレーザビームであることを特徴とする半導体装置の作製方法。

**【請求項 17】**

請求項 7 乃至請求項 16 のいずれか一項において、

50

前記チャネル形成領域の膜厚は10nm以上50nm以下であることを特徴とする半導体装置の作製方法。

【請求項18】

請求項7乃至請求項17のいずれか一項において、

前記ソース領域又は前記ドレイン領域の膜厚が、前記チャネル形成領域の膜厚よりも厚いことを特徴とする半導体装置の作製方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置およびその作製方法に関する。

10

【背景技術】

【0002】

近年、ガラス等の絶縁表面を有する基板上に薄膜トランジスタ（以下、TFTともいう）を形成し、薄膜トランジスタをスイッチング素子等として利用する半導体装置の作製が盛んに行われている。また、薄膜トランジスタとして、絶縁表面を有する基板上にCVD法、フォトリソグラフィ法等を用いて島状の半導体層を形成し、島状の半導体層の一部をトランジスタのチャネル形成領域として利用する構成が提案されている。

【0003】

そのような中、薄膜トランジスタの特性を向上させるために、半導体層の膜厚を薄くすることによりS値（ここでS値とは、ドレイン電圧一定にてドレイン電流を1ケタ変化させるサブスレッシュホールド領域でのゲート電圧値をいう）を小さくした薄膜トランジスタを作製する方法が提案されている。しかしながら、半導体層の膜厚を薄くすることにより、ソース領域及びドレイン領域の抵抗及びコンタクト抵抗が増大し、オン電流の低下を招くといった問題があった。

20

【0004】

そこで、これらの問題を解消するために、ソース領域又はドレイン領域の膜厚に比べてチャネル形成領域の膜厚を薄く形成した半導体層を用いた薄膜トランジスタが提案されている（例えば、特許文献1～2、非特許文献1）。例えば、特許文献1には、平坦な絶縁基板表面に半導体層を形成し、選択的なエッティングによりチャネル形成領域の膜厚を局的に薄くした薄膜トランジスタを作製する方法が開示されている。また、特許文献2には、チャネル形成領域に対応する箇所に突起が形成された絶縁基板上に半導体層を形成し、突起上に形成された半導体層の上面をエッティングすることにより半導体層を平坦化してチャネル形成領域の膜厚を薄くする方法が開示されている。また、非特許文献1には、p-Si膜上にn<sup>+</sup>-Si膜を堆積した後にn<sup>+</sup>-Si膜を部分的にドライエッティングし、エッティングされたn<sup>+</sup>-Si膜の下のp-Si膜をチャネル形成領域として用い、p-Si膜とn<sup>+</sup>-Si膜とが積層した部分をソース領域又はドレイン領域として用いる薄膜トランジスタの作製方法が開示されている。

30

【特許文献1】特開昭61-48975

【特許文献2】特開平5-110099

【非特許文献1】Electrochemical Society Proceedings

n g s V o l u m e 9 8 - 2 2 , P P . 2 0 4 - 2 2 0

40

【発明の開示】

【発明が解決しようとする課題】

【0005】

しかしながら、特許文献1に示すように膜厚の異なる半導体層を平坦な絶縁基板表面に形成するには、所定の膜厚のチャネル形成領域を形成するために半導体層を選択的にエッティングする必要があり工程が不安定であるという問題がある。また、特許文献2に示す方法では、半導体層の表面を平坦化するためにエッティング処理を行うため、工程数が増加し、また半導体層の表面が平坦になるように選択的にエッティング処理を行なう必要があり工程が不安定であるという問題がある。また、非特許文献1に示す方法では、Si膜を2回堆

50

積した後にエッティングする必要があり、工程数が増加する。特に、Nチャネル型トランジスタとPチャネル型トランジスタとを形成する場合、Si膜の堆積回数及びエッティング回数が更に増加する。またSi膜のエッティング処理を制御する必要があり工程が不安定であるという問題がある。また、チャネル形成領域を50nm以下の膜厚で形成する場合、膜厚の制御が困難であるという問題がある。

#### 【0006】

本願発明はこのような課題を解決するための技術を提供するものであり、S値が小さく且つオン電流の低下を抑えた応答性のよい半導体装置を複雑な工程を経ることなく作製する方法を提案することを目的とする。

#### 【課題を解決するための手段】

#### 【0007】

本発明の半導体装置では、ソース領域又はドレイン領域の膜厚がチャネル形成領域の膜厚より厚く形成されている。このような半導体装置の作製方法としては、まず基板上に設けられた絶縁層により形成される凹凸上に非晶質半導体層を形成し、非晶質半導体層にレーザビームを照射して結晶質半導体層を形成することにより膜厚の異なる結晶質半導体層を形成する。そして、結晶質半導体層の膜厚の厚い部分に不純物を添加することによりソース領域又はドレイン領域を形成し、不純物が添加されない領域をチャネル形成領域とする。ソース領域又はドレイン領域と電気的に接続する配線を形成することにより本発明の半導体装置を作製することができる。

#### 【0008】

本発明の半導体装置は、基板上に形成された少なくともチャネル形成領域に対応する箇所に凸部を有する第1の絶縁層と、前記第1の絶縁層上に設けられた非晶質半導体層を溶融することにより形成された結晶質半導体層と、前記結晶質半導体層上に形成された第2の絶縁層と、前記第2の絶縁層上に形成されたゲート電極と、前記ゲート電極上に形成された第3の絶縁層と、前記第3の絶縁層に形成されたコンタクトホールを介して前記ソース領域又はドレイン領域と電気的に接続する配線と、を有し、前記第1の絶縁層の凸部上にチャネル形成領域が形成され、前記第1の絶縁層の凹部上に前記ソース領域又はドレイン領域が形成されている。

#### 【0009】

本発明の半導体装置は、少なくともチャネル形成領域に対応する箇所に凸部を有する第1の絶縁層を形成し、前記第1の絶縁層上に非晶質半導体層を形成し、前記非晶質半導体層にレーザビームを照射して結晶質半導体層を形成し、前記第1の絶縁層の凹部上に形成された前記結晶質半導体層に不純物を添加してソース領域又はドレイン領域を形成し、前記結晶質半導体層上に第2の絶縁層を形成し、前記凸部上に形成された結晶質半導体層上に前記第2の絶縁層を介してゲート電極を形成し、前記ゲート電極及び前記ソース領域又はドレイン領域上に第3の絶縁層を形成し、前記第3の絶縁層に前記ソース領域又はドレイン領域を露出するコンタクトホールを形成し、前記第3の絶縁層上に前記ソース領域又はドレイン領域と接続する導電層を形成することにより作製することができる。なお、基板上のチャネル形成領域に対応する箇所にのみ第1の絶縁層を形成してもよい。この場合、基板と第1の絶縁層とにより凹凸が形成され、膜厚の異なる半導体層が形成される。

#### 【発明の効果】

#### 【0010】

本発明の半導体装置では、凹凸が設けられた絶縁層上に形成された半導体層を溶融して、半導体層の表面を平坦化することにより、ソース領域又はドレイン領域の膜厚をチャネル形成領域の膜厚より厚くするため、S値が小さく且つオン電流の低下が抑えられた半導体装置を作製することができる。また、半導体層を溶融して平坦化するため、プロセスを増加させることなく容易に半導体装置を作製することが可能である。

#### 【0011】

従って、本発明において、S値が小さく且つオン電流の低下が抑えられた応答性のよい半導体装置を容易に作製することが可能である。

10

20

30

40

50

## 【発明を実施するための最良の形態】

## 【0012】

本発明の実施の形態について、図面を用いて以下に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構成において、同じものを指す符号は異なる図面間で共通して用いる場合がある。

## 【0013】

## (実施の形態1)

本実施の形態では、ソース領域又はドレイン領域の膜厚をチャネル形成領域の膜厚より厚く形成した半導体層を用いた半導体装置の構造及び作製方法について説明する。

10

## 【0014】

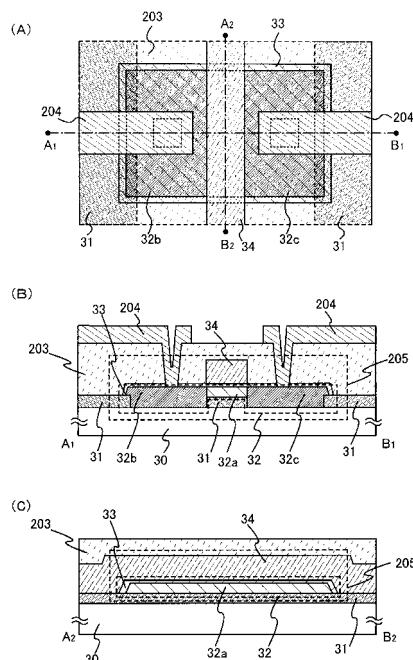

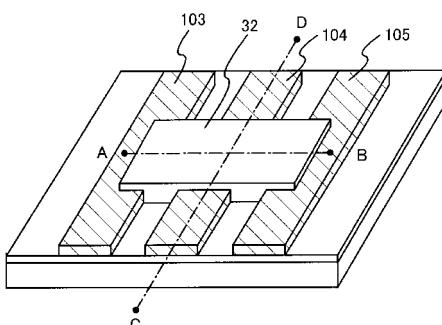

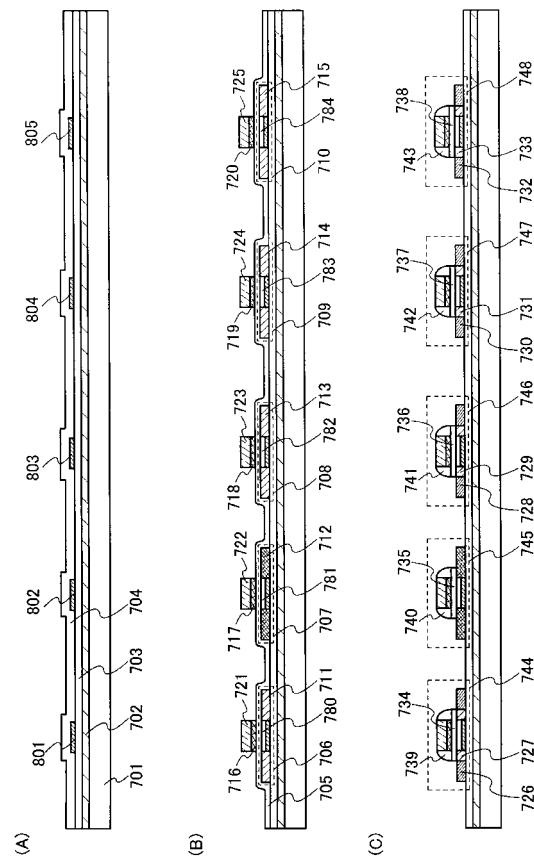

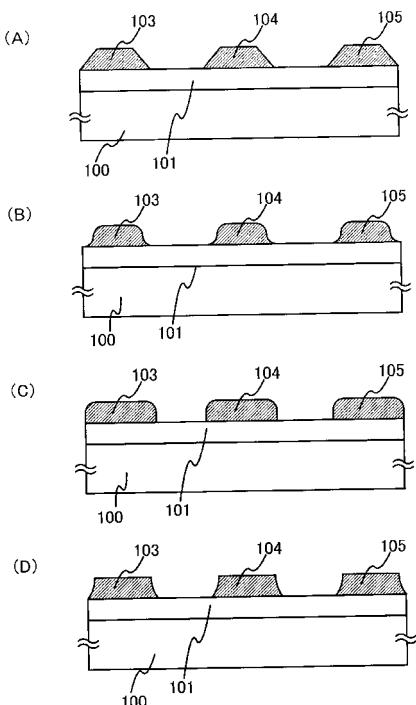

図1は本発明に係る半導体装置の構成を説明するための上面図及び断面図である。図1(A)は、薄膜トランジスタを利用した半導体装置の上面図を示し、図1(B)は図1(A)の点A<sub>1</sub>と点B<sub>1</sub>とを結ぶ破線における断面図を示し、図1(C)は図1(A)の点A<sub>2</sub>と点B<sub>2</sub>とを結ぶ破線における断面図を示している。

20

## 【0015】

本実施の形態に示す半導体装置は、基板30上に凹凸が形成されるように設けられた絶縁層31と、基板30及び絶縁層31上に島状に設けられた半導体層32と、半導体層32上に形成されたゲート絶縁層33と、半導体層32の上方にゲート絶縁層33を介して設けられたゲート電極として機能する導電層34と、を含む薄膜トランジスタ205と、ゲート絶縁層33及び導電層34を覆って設けられた絶縁層203と、絶縁層203上に設けられたソース電極又はドレイン電極として機能する導電層204とを有している(図1(A)～(C))。なお、半導体層32は、チャネル形成領域32aとソース領域又はドレイン領域として機能する不純物領域32b、32cとを有している。なお、チャネル形成領域32a中に、不純物領域32b、32cに添加した不純物と同じ不純物、又は不純物領域32b、32cの導電型とは逆の導電型を与える不純物が添加されていてもよい。なお、基板30と絶縁層31との間に更に絶縁層が形成されていてもよい。

20

## 【0016】

図1に示す半導体装置においては、基板30と絶縁層31とで段差を設けることにより凹凸を形成し、その上に形成される半導体層32の膜厚を変化させている。本実施の形態では、基板30上の絶縁層31によって形成された凹凸上に形成された半導体層を溶融して平坦化することにより、チャネル形成領域32aの膜厚に比べてソース領域又はドレイン領域として機能する不純物領域32b、32cの膜厚が大きい半導体層を形成している。ソース領域又はドレイン領域の膜厚がチャネル形成領域の膜厚と比較して大きいため、イオンドープ法等による不純物元素の添加後に行われる、不純物元素の熱活性化のための熱処理における結晶性回復に有利である。結晶性回復が効果的に行われることにより、ソース領域又はドレイン領域の高抵抗化を抑制することができる。また、ソース領域又はドレイン領域の膜厚と比較してチャネル形成領域の膜厚が小さいためS値を小さくでき、オシ電流の低下を抑制することができる。また、半導体層を溶融して平坦化するため、プロセスを増加させることなく容易に半導体装置を作製することが可能である。従って、S値が小さく且つオシ電流の低下が抑えられた応答性のよい半導体装置を容易に作製することが可能である。

30

40

## 【0017】

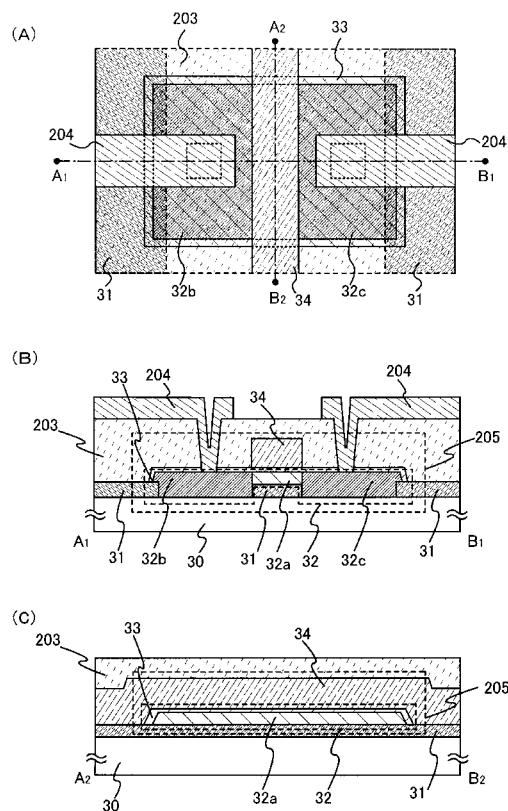

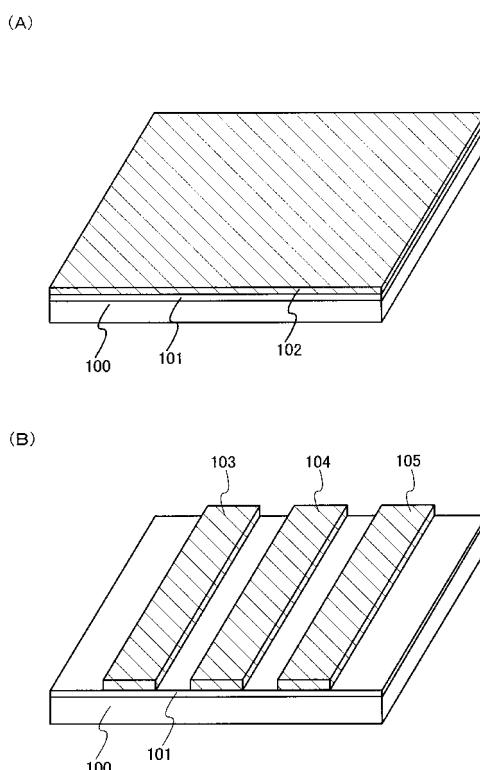

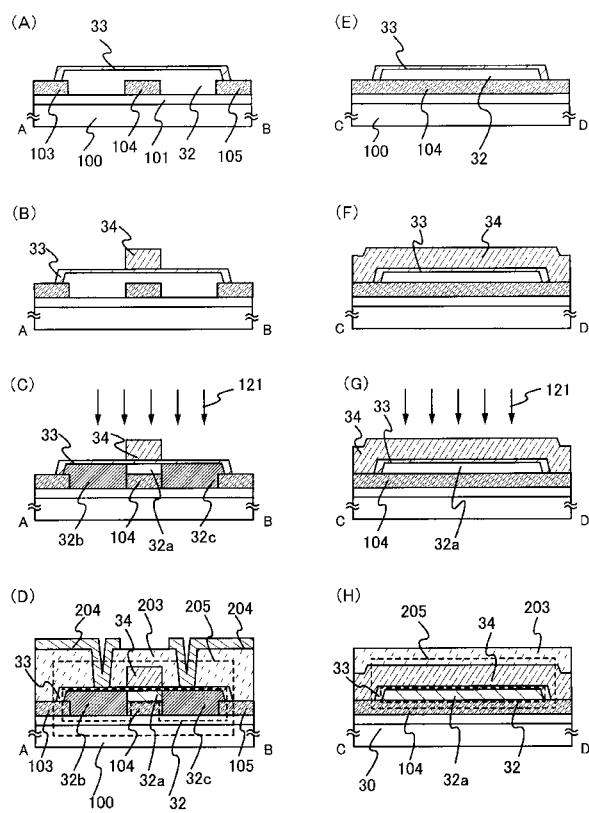

以下に、図1に示す半導体装置の作製方法の一例について説明する。図2～図4に本実施の形態の半導体装置の作製工程を斜めから見た模式図を示す。

## 【0018】

まず、基板100上に第1の絶縁層101を形成し、第1の絶縁層101上に第2の絶縁層102を形成する(図2(A))。次に、第2の絶縁層102をエッティングして、第1の絶縁層101上に第2の絶縁層103～105を直線状のストライプパターンに形成

50

する(図2(B))。第2の絶縁層102のエッティングは、例えば緩衝フッ酸を用いたエッティング、又はCHF<sub>3</sub>を用いたドライエッティングにより行うことができる。なお、図2(B)では第2の絶縁層102から形成される直線状のストライプパターンが3本示されているが、勿論その数に限定されることはない。

#### 【0019】

ここで、基板100としては、ガラス基板、石英基板、金属基板(例えばステンレス基板など)、セラミック基板、Si基板等の半導体基板などを用いることができる。また、他にもプラスチック基板として、ポリエチレンテレフタレート(PET)、ポリエチレンナフタレート(PEN)、ポリエーテルサルファン(PES)、アクリルポリマーなどで作製された基板を選択することもできる。なお、サブミクロンのデザインルールで直線状のストライプパターンを形成するには、基板表面の凹凸、基板のうねり又はねじれを露光装置(特にステッパー)の焦点深度以下にしておくことが望ましい。具体的には、基板のうねり又はねじれが、露光装置による1回の光照射領域内において1μm以下、好ましくは0.5μm以下とする。

10

#### 【0020】

また、第2の絶縁層103～105の形状は規則的な周期パターンである必要はなく、後に形成される半導体層の形状に合わせて適宜形成すればよい。従って、第2の絶縁層103～105の幅及び長さには特に数値的な限定はなく、少なくとも後に形成されるTFTのチャネル形成領域に対応する位置に第2の絶縁層103～105が形成されなければよい。また、第1の絶縁層101と第2の絶縁層103～105で形成される凹部の側面部の角度は5～120度、好ましくは60～90度の範囲で適宜設定すれば良い。また、第2の絶縁層103～105の角部や第1の絶縁層101と第2の絶縁層103～105とで形成される段差部は必ずしも直線で形成された形状でなくてもよく、丸みを帯びてもよい。図16に、本実施の形態の半導体装置の構成における、第1の絶縁層101と第2の絶縁層103～105の形状の一例を示す。図16(A)～(D)に示すように、第1の絶縁層101と第2の絶縁層103～105は様々な形状をとることが可能である。

20

#### 【0021】

ここで、第1の絶縁層101は、第2の絶縁層102とのエッティングの選択比が確保できる材料で形成すれば良い。第1の絶縁層101よりも第2の絶縁層102のエッティング速度が相対的に早くなるように材料及び成膜条件を適宜調整することが望ましい。例えば、第1の絶縁層101として、窒化珪素、酸化珪素、酸素含有量が窒素含有量よりも大きな酸窒化珪素(SiO<sub>x</sub>N<sub>y</sub>と示す)、窒素含有量が酸素含有量よりも大きな窒酸化珪素(SiN<sub>x</sub>O<sub>y</sub>と示す)、窒化アルミニウム(Al<sub>x</sub>N<sub>y</sub>と示す)、酸素含有量が窒素含有量よりも大きな酸窒化アルミニウム(AlO<sub>x</sub>N<sub>y</sub>と示す)、窒素含有量が酸素含有量よりも大きな窒酸化アルミニウム(AlN<sub>x</sub>O<sub>y</sub>と示す)または酸化アルミニウムから選ばれた材料を用いることができる。その場合、第1の絶縁層101を30～300nmの厚さで形成すればよい。特に、第1の絶縁層101として酸化アルミニウム膜を用いると、ナトリウム(Na)に対するプロッキング効果が得られるため、ガラス基板からの汚染対策として有効である。なお、第1の絶縁層101は必ずしも設ける必要はなく、必要に応じて適宜設ければよい。また、必ずしも第1の絶縁層101と第2の絶縁層102とを異なる材料で形成する必要はなく、同じ材料で形成してもよい。また、第1の絶縁層101又は第2の絶縁層102は、それぞれ単層でなくてもよく、複数の層を積層した構造としてもよい。

30

#### 【0022】

なお、酸窒化珪素(SiO<sub>x</sub>N<sub>y</sub>)膜としては、Siが25～35原子%、酸素が55～65原子%、窒素が1～20原子%、水素が0.1～10原子%で含まれるもの要用いれば良い。また、窒酸化珪素(SiN<sub>x</sub>O<sub>y</sub>)膜としては、Siが25～35原子%、酸素が15～30原子%、窒素が20～35原子%、水素が15～25原子%で含まれるもの要用いれば良い。また、酸窒化アルミニウム(AlO<sub>x</sub>N<sub>y</sub>)膜としては、Alが30

40

50

~40原子%、酸素が50~70原子%、窒素が1~20原子%で含まれるもの用いれば良い。また、窒酸化アルミニウム( $\text{AlN}_x\text{O}_y$ )膜としては、Alが30~50原子%、酸素が0.01~20原子%、窒素が30~50原子%で含まれるもの用いれば良い。

#### 【0023】

また、第2の絶縁層102は、酸化珪素、窒酸化珪素または酸窒化珪素等を用い、10~3000nm、好ましくは10~200nm、より好ましくは20~100nmの厚さで形成することができる。酸化珪素膜はオルトケイ酸テトラエチル(Tetraethyl Ortho Silicate: TEOS)と $\text{O}_2$ とを混合しプラズマCVD法で形成することができる。また、窒酸化珪素膜は $\text{SiH}_4$ 、 $\text{NH}_3$ 、 $\text{N}_2\text{O}$ を原料として用い、酸窒化珪素膜は $\text{SiH}_4$ 、 $\text{N}_2\text{O}$ を原料として用い、それぞれプラズマCVD法で形成することができる。なお、第2の絶縁層102としては、CVD法(代表的には、プラズマCVD法もしくは熱CVD法)やPVD法(代表的には、スパッタ法もしくは蒸着法)によって形成された絶縁膜を用いることが好ましい。これは、非晶質半導体層を結晶化する際、結晶化に伴う応力を緩和しうる程度の柔らかさを絶縁層が持つことが、良好な結晶性を得るにあたって重要な役割を果たしていると考えられるからである。

10

#### 【0024】

次に、図3(A)で示すように、第2の絶縁層103~105の表面及び第1の絶縁層101と第2の絶縁層103~105から成る凹部を覆う非晶質半導体層106を形成する。つまり、非晶質半導体層106は図示するように、下地の第1の絶縁層101と第2の絶縁層103~105とで形成される凹凸部を覆うように形成する。なお、非晶質半導体層106の膜厚は、第1の絶縁層101と第2の絶縁層103~105とで形成される凹部の深さと同程度かそれ以上の厚さとすることが望ましい。非晶質半導体層106は珪素、珪素とゲルマニウムの化合物( $\text{Si}_x\text{Ge}_{1-x}$ )、珪素と炭素の化合物等を用いることができる。例えば、非晶質半導体層106として、膜厚0.01~3μm(好ましくは0.1~1μm)の非晶質珪素膜を用いることができる。

20

#### 【0025】

また、第1の絶縁層101及び第2の絶縁層103~105の表面に付着した硼素などによる化学汚染の影響を排除し、しかもその絶縁表面と非晶質半導体層が直接接しないように、非晶質半導体層106を形成する直前に第3の絶縁層(図示せず)として酸窒化珪素膜を非晶質半導体層と同一の成膜装置内で大気に触れさせることなく連続的に成膜すると良い。この第3の絶縁層は、前述の化学汚染の影響の排除と、第1の絶縁層及び第2の絶縁層と非晶質半導体層との密着性の向上を狙うものであり、膜厚が小さいものでも十分に効果がある。第3の絶縁層の膜厚は、典型的には5~50nm(化学汚染のブロッキング効果を高めるには20nm以上が好ましい)とすれば良い。

30

#### 【0026】

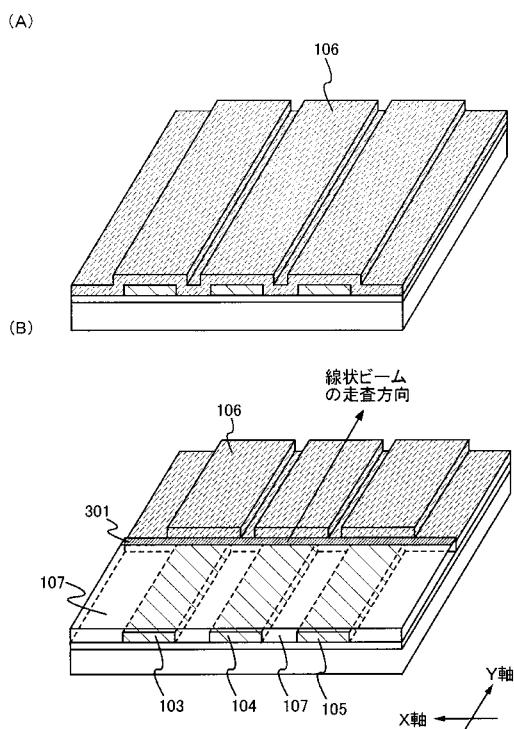

次に、図3(B)中に矢印で示すように、非晶質半導体層106上に線状ビームを照射する。非晶質半導体層106に線状ビームを照射することにより結晶質半導体層107を形成することができる。ここで、図3(B)において、領域301は線状ビームの照射領域を示す。線状ビームは、領域301の長辺方向(図中、X軸方向)と第2の絶縁層103~105の各々が延在する方向とが交差するように照射する。そして領域301の短辺方向(図中、Y軸方向)に線状ビームを走査する。なお、線状ビームとは、被照射面における形状が線状であるレーザビームのことである。ここでいう「線状」とは、厳密な意味で「線」を意味しているのではなく、アスペクト比が大きい矩形(例えば、アスペクト比が10以上(好ましくは100以上))を意味する。なお、線状とするのは、被照射体に対して十分なアニールを行うためのエネルギー密度を確保するためであり、矩形状や橢円形状であっても被照射体に対して十分なアニールを行うことができればよい。

40

#### 【0027】

本実施の形態において、線状ビームは直線状のストライプパターンが延在する方向と平行な方向に走査され、溶融した非晶質半導体は表面張力が働いて凹部に流れ込み凝固する

50

。従って、図3(B)で示すように表面がほぼ平坦な結晶質半導体層107が形成される。なお、溶融して平坦な表面が形成された半導体層と気相との界面は平衡状態に達している。

#### 【0028】

なお、レーザ結晶化法で結晶質半導体層を形成する場合、気体レーザ又は固体レーザを用いることができる。気体レーザと固体レーザは、連続発振又はパルス発振のどちらでもよい。例えば、Arレーザ、Krレーザ、エキシマレーザなどの気体レーザ、単結晶のYAG、YVO<sub>4</sub>、フォルステライト(Mg<sub>2</sub>SiO<sub>4</sub>)、YAlO<sub>3</sub>、GdVO<sub>4</sub>、若しくは多結晶(セラミック)のYAG、Y<sub>2</sub>O<sub>3</sub>、YVO<sub>4</sub>、YAlO<sub>3</sub>、GdVO<sub>4</sub>に、ドーパントとしてNd、Yb、Cr、Ti、Ho、Er、Tm、Taのうち1種または複数種添加されているものを媒質とするレーザ、ガラスレーザ、ルビーレーザ、アレキサンドライトレーザ、Ti:サファイアレーザ、銅蒸気レーザまたは金蒸気レーザのうち一種または複数種から発振されたレーザビームを用いることができる。このようなレーザビームの基本波、及びこれらの基本波の第2高調波から第4高調波のレーザビームを照射することで、大粒径の結晶を得ることができる。

#### 【0029】

なお、単結晶のYAG、YVO<sub>4</sub>、フォルステライト(Mg<sub>2</sub>SiO<sub>4</sub>)、YAlO<sub>3</sub>、GdVO<sub>4</sub>、若しくは多結晶(セラミック)のYAG、Y<sub>2</sub>O<sub>3</sub>、YVO<sub>4</sub>、YAlO<sub>3</sub>、GdVO<sub>4</sub>に、ドーパントとしてNd、Yb、Cr、Ti、Ho、Er、Tm、Taのうち1種または複数種添加されているものを媒質とするレーザ、Arイオンレーザ、またはTi:サファイアレーザは、連続発振をさせることができ、Qスイッチ動作やモード同期などを行うことによって10MHz以上の発振周波数でパルス発振をさせることも可能である。連続発振のレーザから発振するレーザビーム若しくは10MHz以上の周波数で発振するレーザビームを照射することで、結晶化された半導体層の表面を平坦なものとすることができます。それにより、後の工程で形成するゲート絶縁層を薄膜化することが可能であり、より薄型の半導体装置を作製することができます。また、表面が平坦な結晶質半導体層を形成することで、ゲート絶縁層の耐圧の向上に寄与することができる。

#### 【0030】

また、連続発振のレーザビームの波長は、非晶質半導体層の光吸収係数を考慮して200~700nmであることが望ましい。このような波長帯の光は、波長変換素子を用いて基本波の第2高調波、第3高調波を取り出すことで得られる。波長変換素子としてはADP(リン酸二水素化アンモニウム)、Ba<sub>2</sub>NaNb<sub>5</sub>O<sub>15</sub>(ニオブ酸バリウムナトリウム)、CdSe(セレンカドミウム)、KDP(リン酸二水素カリウム)、LiNbO<sub>3</sub>(ニオブ酸リチウム)、Se、Te、LBO、BBO、KB5などが適用される。特にLBOを用いることが望ましい。また、レーザからレーザビームをTEM<sub>00</sub>(シングル横モード)で発振して射出すると、被照射面において得られる線状のビームスポットのエネルギーの均一性を上げることができるので好ましい。なお、本実施の形態では非晶質半導体層上で線状ビームを走査することにより結晶質半導体層を形成しているが、レーザ等の電磁波の照射時に被照射物が移動しない露光方法を用いてもよい。例えば、一括露光やステップ露光等の露光方法を用いてもよい。

#### 【0031】

その後、好ましくは500~600の加熱処理を行い、結晶質半導体層に蓄積された歪みを除去すると良い。この歪みは、結晶化によって起こる半導体の体積収縮、下地との熱応力や格子不整合などにより発生するものである。この加熱処理は、通常の熱処理装置を用いて行えば良いが、例えばガス加熱方式の瞬間熱アニール(RTA)法を用いて1~10分の処理を行えば良い。RTA法を用いる場合、より高温での熱処理が可能である。例えば、500~700程度の熱処理を行ってもよい。尚、この工程は本発明において必須な要件ではなく、適宜選択して行えばよい。

#### 【0032】

その後、結晶質半導体層107をドライエッティングして薄膜トランジスタの島状の半導

10

20

30

40

50

体層32を形成する(図4)。なお、ドライエッチングのときのエッチングガスとしては、 $\text{CF}_4$ 、 $\text{NF}_3$ 、 $\text{SF}_6$ 、 $\text{CHF}_3$ 、 $\text{C}_2\text{F}_4$ 等のフッ素系のガス、又は該フッ素系ガスに $\text{O}_2$ ガス、 $\text{H}_2$ ガス、不活性ガスである $\text{He}$ や $\text{Ar}$ 等を適宜加えた混合ガス等を用いることができる。好ましくは、 $\text{CF}_4$ と $\text{O}_2$ との混合ガス、 $\text{SF}_6$ と $\text{O}_2$ との混合ガス、 $\text{CHF}_3$ と $\text{He}$ との混合ガス、又は $\text{CF}_4$ と $\text{H}_2$ との混合ガスを用いるとよい。また、エッチングはドライエッチングに限られずウエットエッチングで行ってもよい。その場合、結晶質半導体層107に対してTMAH(tetramethylammonium hydroxide、テトラメチルアンモニウムヒドロキシド)に代表される有機塩基を含むアルカリ性溶液を用いたウエットエッチングを行うことにより半導体層32を形成することができる。なお、エッチング液としてTMAH等の溶液を用いた場合、結晶質半導体層107のみが選択的にエッチングされるため、下地の絶縁層にダメージを与えずにエッチングすることができる。

10

## 【0033】

上記の工程により、凸部を有する絶縁表面上に島状の半導体層を形成することができる。なお、本実施の形態において、凸部上に形成された部分の半導体層は、10nm～200nm、好ましくは10nm～50nm程度、更に好ましくは10nm～30nm程度の膜厚である。なお、50nm以下の半導体層は、50nm以上の膜厚の半導体層をドライエッチング処理によって薄膜化することにより形成してもよい。このときのエッチングの際のエッチングガスとしては、 $\text{Cl}_2$ 、 $\text{BCl}_3$ 、 $\text{SiCl}_4$ 等の塩素系のガス、 $\text{CF}_4$ 、 $\text{NF}_3$ 、 $\text{SF}_6$ 、 $\text{CHF}_3$ 、 $\text{C}_2\text{F}_4$ 等のフッ素系のガス、又はフッ素系ガスに $\text{O}_2$ ガス、 $\text{H}_2$ ガス、 $\text{He}$ や $\text{Ar}$ 等の不活性ガスを適宜加えた混合ガス等を用いることができる。なお、ドライエッチングの前に、半導体層表面を希フッ酸処理して半導体表面に形成される自然酸化層を除去し、その後半導体表面をオゾン水などで処理して半導体表面に酸化層を形成しておいてもよい。

20

## 【0034】

ここで、TFTのしきい値電圧を制御するためにチャネル形成領域への不純物元素のドープ量を増加させた場合でも、凸部上に形成された部分の半導体層を50nm以下程度の薄膜で形成することにより、完全空乏型のTFTを作製しやすくなるため、良好なS値でしきい値電圧が制御されたTFTを作製することができる。

30

## 【0035】

次に、半導体層32を利用してTFTを作製する工程を図5を用いて説明する。なお、図4の点Aと点Bとを結ぶ破線における断面図を図5(A)～(D)に示し、点Cと点Dとを結ぶ破線における断面図を図5(E)～(H)に示す。

## 【0036】

次に、半導体層32上にゲート絶縁層33を形成する(図5(A)、(E))。ゲート絶縁層33は、酸化シリコン( $\text{SiO}$ )膜、窒化シリコン( $\text{SiN}$ )膜、酸化窒化シリコン( $\text{SiO}_x\text{N}_y$ )( $x > y > 0$ )膜、窒化酸化シリコン( $\text{SiN}_x\text{O}_y$ )( $x > y > 0$ )膜、 $\text{Hf}$ 系酸化膜等を単層又は積層した膜を用いて形成することができる。このような絶縁層は、気相成長法やスパッタリング法で形成することができる。なお、気相成長法やスパッタリング法で形成されたゲート絶縁層表面をプラズマ処理してもよい。

40

## 【0037】

また、半導体層32を形成した後に、酸素を含む雰囲気又は窒素を含む雰囲気下で半導体層表面をプラズマ処理することにより、半導体層表面に形成された酸化シリコン( $\text{SiO}$ )膜、窒化シリコン( $\text{SiN}$ )膜、酸化窒化シリコン( $\text{SiO}_x\text{N}_y$ )( $x > y > 0$ )膜、又は窒化酸化シリコン( $\text{SiN}_x\text{O}_y$ )( $x > y > 0$ )膜をゲート絶縁層として用いることもできる。

## 【0038】

次に、ゲート絶縁層33上にゲート電極として機能する導電層34を形成する(図5(B)、(F))。ここでは、導電層34は単層で形成した例を示しているが、もちろん導電性材料を2層又は3層以上の積層で設けた構造としてもよい。なお、ここでは図示しな

50

いが、導電層34は、ゲート絶縁層33上を覆って形成された導電層を選択的にエッティングすることにより形成することができる。なお、ゲート電極下以外のゲート絶縁層33をエッティングにより除去してもよい。

#### 【0039】

また、導電層34は、タンタル(Ta)、タングステン(W)、チタン(Ti)、モリブデン(Mo)、アルミニウム(Al)、銅(Cu)、クロム(Cr)、ニオブ(Nb)等から選択された元素またはこれらの元素を主成分とする合金若しくは化合物で形成することができる。また、リン等の不純物元素をドーピングした多結晶珪素に代表される半導体材料により形成することもできる。例えば、導電層34を第1の導電膜と第2の導電膜との積層構造とする場合、第1の導電膜として窒化タンタルを用い、第2の導電膜としてタングステンを用いて形成するとよい。なお、この組み合わせに限らず、導電層34を積層して形成する場合には、上記材料を自由に組み合わせて設けることができる。

#### 【0040】

続いて、導電層34をマスクとして半導体層32に不純物元素121を導入することによって、不純物領域32b、32c及び不純物元素121が導入されないチャネル形成領域32aを形成する(図5(C)、(G))。なお、ここでは、導電層34を島状の半導体層32を横断するように形成した後に不純物元素を導入するため、導電層34に覆われていない領域に不純物が導入されて不純物領域32b、32cが形成され、導電層34に覆われた領域には不純物元素121が導入されないチャネル形成領域32aが形成される。

#### 【0041】

ここで、不純物元素121としては、n型の導電性を付与する不純物元素又はp型の導電性を付与する不純物元素を用いることができる。n型の導電性を付与する不純物元素としては、リン(P)やヒ素(As)等を用いることができる。p型の導電性を付与する不純物元素としては、ボロン(B)やアルミニウム(Al)やガリウム(Ga)等を用いることができる。例えば、不純物元素121として、リン(P)を $1 \times 10^{-8} \sim 1 \times 10^{-1}$ /cm<sup>3</sup>の濃度で含まれるように半導体層32に導入し、n型を示す不純物領域32b、32cを形成すればよい。なお、チャネル形成領域32aとソース領域又はドレイン領域との間に、ソース領域又はドレイン領域より低濃度に不純物が添加された低濃度不純物領域(LDD領域ともいう)を形成してもよい。

#### 【0042】

また、チャネル形成領域32a中に、不純物領域32b、32cに添加した不純物と同じ又は逆の導電型を有する不純物元素を添加してもよい。チャネル形成領域32a中に同じ又は逆の導電型の不純物を添加することにより、TFTのしきい値電圧を制御することができる。なお、この不純物元素はゲート電極を介してドープすることによって添加してもよいし、ゲート電極形成前に予め添加しておいてもよい。

#### 【0043】

次に、導電層34、ゲート絶縁層33、絶縁層103～105等を覆うように絶縁層203を形成する(図5(D)、(H))。その後、ゲート絶縁層33及び絶縁層203にコンタクトホールを形成し、絶縁層203上にソース電極又はドレイン電極として機能する導電層204を選択的に形成する(図5(D)、(H))。ここで、導電層204は、半導体層32のソース領域又はドレイン領域として機能する不純物領域32b、32cと電気的に接続されるように設ける。

#### 【0044】

ここで、絶縁層203は、CVD法やスパッタリング法等で形成した、酸化シリコン膜、酸化窒化シリコン(SiO<sub>x</sub>N<sub>y</sub>)膜(x>y>0)、窒化酸化シリコン膜(SiN<sub>x</sub>O<sub>y</sub>)(x>y>0)などを用いることができる。また、ポリイミド、ポリアミド、ポリビニルフェノール、ベンゾシクロブテンポリマー、アクリルポリマー、エポキシ等の有機材料、またはシロキサン樹脂等のシロキサン材料、オキサゾール樹脂などからなる膜を単層または積層構造で設けることができる。なお、シロキサン材料とは、Si-O-Si結

合を含む材料に相当する。シロキサンは、シリコン(Si)と酸素(O)との結合で骨格構造が構成される。置換基として、少なくとも水素を含む有機基(例えばアルキル基、芳香族炭化水素)が用いられる。置換基として、フルオロ基を用いることもできる。オキサゾール樹脂は、例えば、感光性ポリベンゾオキサゾール等である。感光性ポリベンゾオキサゾールは、誘電率が低く(常温1MHzで誘電率2.9)、耐熱性が高く(昇温5/minの条件における示差熱熱重量同時測定(TG/DTA: Thermogravimetry-Differential Thermal Analysis)で熱分解温度550)、吸水率が低い(常温24時間で0.3%)材料である。オキサゾール樹脂は、ポリイミド等の比誘電率(3.2~3.4程度)と比較すると、比誘電率が低いため(2.9程度)、寄生容量の発生を抑制し、 TFT の高速動作を行うことができる。ここでは、絶縁層203は、CVD法で形成した酸化シリコン、酸化窒化シリコン(SiO<sub>x</sub>N<sub>y</sub>)(x>y>0)又は窒化酸化シリコン(SiN<sub>x</sub>O<sub>y</sub>)(x>y>0)からなる膜を単層又は積層して形成する。また、さらに、ポリイミド、ポリアミド、ポリビニルフェノール、ベンゾシクロブテンポリマー、アクリルポリマー、エポキシポリマー等の有機材料、シロキサン樹脂等のシロキサン材料、又はオキサゾール樹脂からなる膜を積層して形成してもよい。

10

## 【0045】

また、導電層204は、アルミニウム、タングステン、チタン、タンタル、モリブデン、ニッケル、ネオジムから選ばれた一種の元素または当該元素を複数含む合金からなる膜を用いて単層構造または積層構造を用いることができる。例えば、当該元素を複数含む合金からなる導電膜として、チタンを含有したアルミニウム合金、ネオジムを含有したアルミニウム合金などで形成することができる。また、積層構造で設ける場合、例えば、アルミニウム層若しくは前記したようなアルミニウム合金層を、チタン層で挟んで積層させた構造としても良い。

20

## 【0046】

以上の工程により、薄膜トランジスタ205を含む半導体装置を作製することができる。

## 【0047】

本実施の形態に示す半導体装置では、第1の絶縁層101及び第2の絶縁層103~105によって形成された凹凸を有する絶縁表面上に形成された半導体層を溶融して平坦化することにより、ソース領域又はドレイン領域の膜厚がチャネル形成領域の膜厚より大きい半導体層を形成している。この特徴は、イオンドープ法等による不純物元素の添加後に行われる、不純物元素の熱活性化のための熱処理における結晶性回復に有利であり、ソース領域又はドレイン領域の高抵抗化を抑制することができる。また、チャネル形成領域の膜厚がソース領域又はドレイン領域の膜厚と比較して小さいためS値を小さくでき、オン電流の低下を抑制することができる。また、半導体層を溶融して平坦化するため、プロセスを増加させることなく容易に半導体装置を作製することが可能である。従って、S値が小さく且つオン電流の低下が抑えられた応答性のよい半導体装置を容易に作製することができる。

30

## 【0048】

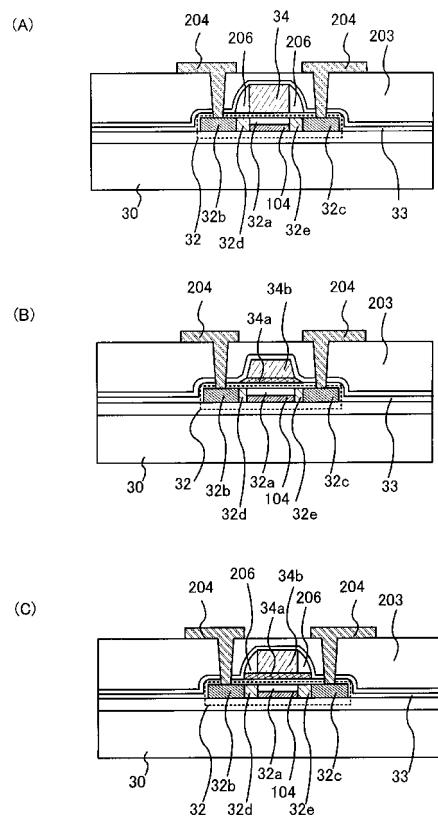

なお、薄膜トランジスタの形状は図1に示すものに限られるものではなく、例えばゲート電極として機能する導電層34の側壁に接する絶縁物からなるサイドウォール206を形成してもよいし、ソース領域又はドレイン領域として機能する不純物領域32b、32cとチャネル形成領域32aとの間に、不純物領域32b、32cより低濃度に不純物が添加された低濃度不純物領域32d、32e(LDD領域ともいう)が形成されていてもよい(図6(A))。また、薄膜トランジスタの構造として上述した構造に限られず、チャネル形成領域が1つ形成されるシングルゲート構造でもよいし、2つ形成されるダブルゲート構造または3つ形成されるトリプルゲート構造等のマルチゲート構造を用いることができる。また、ゲート電極を積層構造で設けてもよい。例えば、ゲート電極を第1の導電層34aと第1の導電層34a上に形成される第2の導電層34bとの2層構造とし、

40

50

第1の導電層をテーパー状で形成し、第1の導電層にのみ重なるように低濃度不純物領域32d、32eを設ける構造(図6(B))としてもよい。また、ゲート電極を第1の導電層34aと第1の導電層34a上に形成される第2の導電層34bで設け、第2の導電層34bの側壁に接し且つ導電層34aの上方に形成されるようにサイドウォール206を設ける構造(図6(C))としてもよい。また、ソース領域またはドレイン領域として機能する不純物領域32b、32cをNi、Co、W等のシリサイドで形成することも可能である。

#### 【0049】

##### (実施の形態2)

本実施の形態では、薄膜トランジスタ、記憶素子およびアンテナを含む本発明の半導体装置の作製方法について、図面を参照して説明する。

#### 【0050】

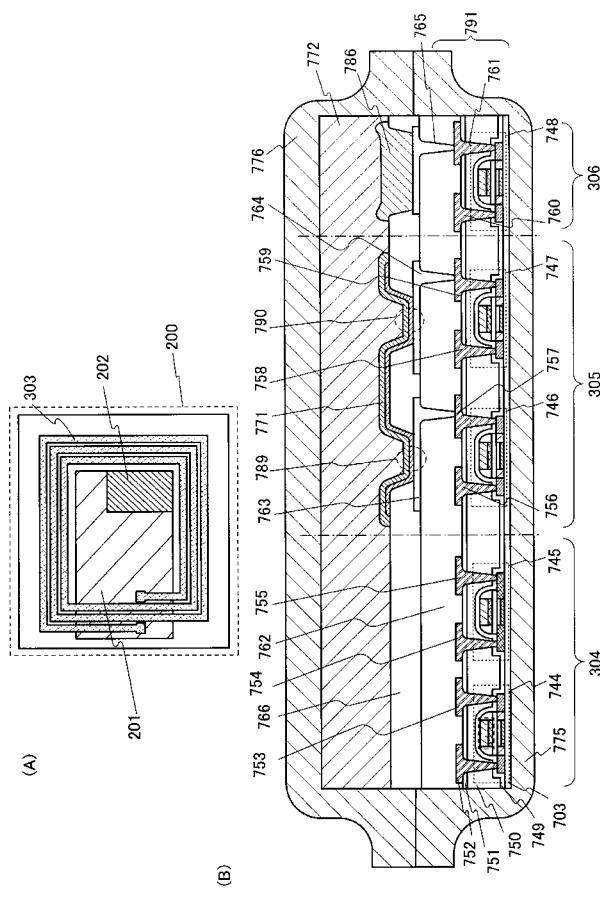

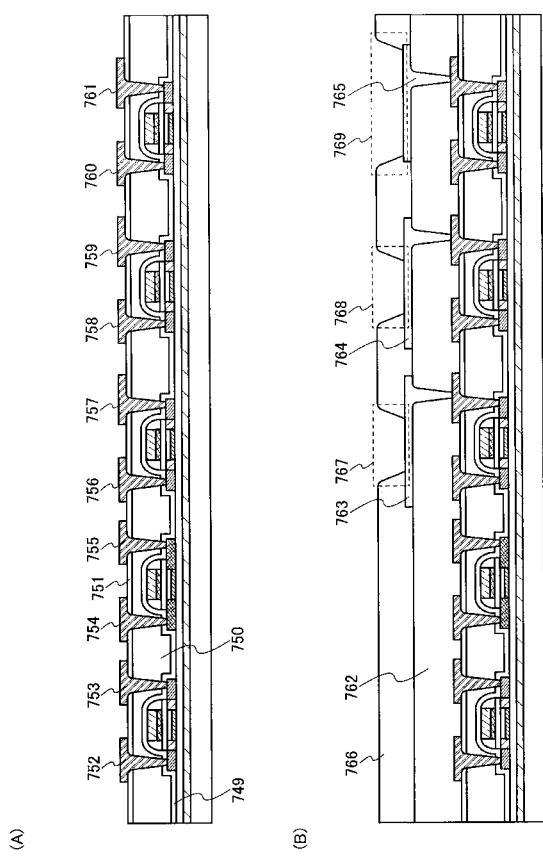

本実施の形態で示す半導体装置の構成を説明する上面図および断面図を図7に示す。なお、図7(A)は本実施の形態で示す半導体装置の上面構造の一例を示し、図7(A)の断面構造の一部を図7(B)に示している。

#### 【0051】

本実施の形態において、半導体装置200は集積回路部201、メモリ部202、アンテナ303を有している(図7(A))。なお、図7(B)において、領域304は図7(A)の集積回路部201の断面構造の一部に対応し、領域305は図7(A)のメモリ部202の断面構造の一部に対応し、領域306は図7(A)のアンテナ303の断面構造の一部に対応している。

#### 【0052】

本実施の形態の半導体装置は、図7(B)に示すように第1の基体775上に絶縁層703を介して設けられた薄膜トランジスタ744～748(TFT)と、薄膜トランジスタ744～748上に設けられた絶縁層750と、当該絶縁層750上に設けられたソース電極又はドレイン電極として機能する導電層752～761とを有する。また、絶縁層750上に設けられた絶縁層751と、絶縁層751及び導電層752～761上に設けられた絶縁層762と、絶縁層762上に設けられた導電層763～765と、絶縁層762及び導電層763～765の一部を覆うように設けられた絶縁層766と、導電層763、764上に設けられた記憶素子789、790と、導電層765上に設けられたアンテナとして機能する導電層786と、絶縁層766、記憶素子に含まれる導電層771及びアンテナとして機能する導電層786を覆うように設けられた絶縁層772と、絶縁層772上に設けられた第2の基体776を有している。なお、第1の基体775及び第2の基体776によって、半導体装置の集積回路部201、メモリ部202、アンテナ303は封止されている。

#### 【0053】

次に、図7に示す半導体装置の作製工程の一例について図8～図11を用いて説明する。

#### 【0054】

まず、基板701の一表面に、剥離層702を形成する(図8(A))。基板701は、ガラス基板、石英基板、金属基板やステンレス基板の一表面に絶縁層を形成した基板、本工程の処理温度に耐えうる耐熱性があるプラスチック基板等を用いるとよい。このような基板701であれば、その面積や形状に大きな制限はない。そのため、基板701として、例えば、1辺が1メートル以上であって、矩形状のものを用いれば、生産性を格段に向上させることができる。このような点において、円形のシリコン基板を用いる場合と比較して、非常に優位である。なお、本工程では、剥離層702を基板701の全面に設けているが、必要に応じて、基板701の全面に剥離層となる層を形成した後に、フォトリソグラフィ法を用いて選択的に剥離層を設けてもよい。また、基板701に接するよう剥離層702を形成しているが、必要に応じて、基板701と剥離層702との間に下地となる絶縁層を形成してもよい。

10

20

30

40

50

## 【0055】

剥離層702は、スパッタリング法やプラズマCVD法等により、タンゲステン(W)、モリブデン(Mo)、チタン(Ti)、タンタル(Ta)、ニオブ(Nb)、ニッケル(Ni)、コバルト(Co)、ジルコニウム(Zr)、亜鉛(Zn)、ルテニウム(Ru)、ロジウム(Rh)、鉛(Pb)、オスミウム(Os)、イリジウム(Ir)、珪素(Si)から選択された元素または前記元素を主成分とする合金若しくは化合物からなる層を、単層又は積層して形成する。珪素を含む層は、非晶質、微結晶、多結晶のいずれの構造を有していてもよい。

## 【0056】

剥離層702が単層構造の場合、例えば、タンゲステンを含む層、モリブデンを含む層またはタンゲステンとモリブデンの混合物を含む層を形成する。あるいは、タンゲステンの酸化物若しくは酸化窒化物を含む層、モリブデンの酸化物若しくは酸化窒化物を含む層またはタンゲステンとモリブデンの混合物の酸化物若しくは酸化窒化物を含む層を形成する。なお、タンゲステンとモリブデンの混合物とは、例えば、タンゲステンとモリブデンの合金に相当する。また、タンゲステンの酸化物は、酸化タンゲステンと表記することがある。

10

## 【0057】

剥離層702が積層構造の場合、1層目としてタンゲステンを含む層、モリブデンを含む層またはタンゲステンとモリブデンの混合物を含む層を形成し、2層目としてタンゲステン、モリブデンまたはタンゲステンとモリブデンの混合物の酸化物、窒化物、酸化窒化物又は窒化酸化物を含む層を形成する。

20

## 【0058】

なお、剥離層702として、タンゲステンを含む層とタンゲステンの酸化物を含む層の積層構造を形成する場合、タンゲステンを含む層を形成し、その上に酸化珪素を含む層を形成することで、タンゲステンを含む層と酸化珪素を含む層との界面に、タンゲステンの酸化物を含む層が形成されることを活用してもよい。この構造は、タンゲステンを含む層と、タンゲステンの窒化物、酸化窒化物または窒化酸化物を含む層との積層構造を形成する場合も同様であり、タンゲステンを含む層を形成後、その上層に窒化珪素を含む層、酸化窒化珪素を含む層、窒化酸化珪素を含む層を形成するとよい。また、タンゲステンの酸化物は、 $W O_x$ で表され、Xは2~3であり、Xが2の場合( $W O_2$ )、Xが2.5の場合( $W_2 O_5$ )、Xが2.75の場合( $W_4 O_{11}$ )、Xが3の場合( $W O_3$ )などがある。タンゲステンの酸化物を含む層を形成するにあたり、上記に挙げたXの値に特に制約はなく、エッチングレート等を基に、どの酸化物を形成するかを決めるとい。なお、エッチングレートとして最も良いものは、酸素雰囲気下で、スパッタリング法により形成するタンゲステンの酸化物を含む層( $W O_x$ 、 $0 < X < 3$ )である。従って、作製時間を短縮する場合には、剥離層として、酸素雰囲気下でスパッタリング法によりタンゲステンの酸化物を含む層を形成するとよい。また、剥離層702として、金属層と金属酸化物を含む層の積層構造で設ける場合、金属層を形成後、当該金属層にプラズマ処理を行うことによって金属層上に金属酸化物を含む層として金属酸化膜を形成してもよい。プラズマ処理を行う場合、酸素雰囲気下や窒素雰囲気下または $N_2 O$ 雰囲気下等で行うことによって、金属層上に金属酸化物を含む層として金属酸化膜や金属酸窒化膜等を形成することができる。

30

## 【0059】

次に、剥離層702を覆うように、下地となる絶縁層703を形成する。絶縁層703は、スパッタ法やプラズマCVD法等により、珪素の酸化物または珪素の窒化物を含む層を、単層又は積層で形成する。珪素の酸化物とは、珪素(Si)と酸素(O)を含む物質であり、酸化珪素、酸化窒化珪素、窒化酸化珪素等が該当する。珪素の窒化物とは、珪素(Si)と窒素(N)を含む物質であり、窒化珪素、酸化窒化珪素、窒化酸化珪素等が該当する。例えば、下地となる絶縁層が2層構造の場合、1層目として窒化酸化珪素層を形成し、2層目として酸化窒化珪素層を形成するとよい。下地となる絶縁層が3層構造の場

40

50

合、1層目の絶縁層として酸化珪素層を形成し、2層目の絶縁層として窒化酸化珪素層を形成し、3層目の絶縁層として酸化窒化珪素層を形成するとよい。または、1層目の絶縁層として酸化窒化珪素層を形成し、2層目の絶縁層として窒化酸化珪素層を形成し、3層目の絶縁層として酸化窒化珪素層を形成するとよい。下地となる絶縁層は、基板701からの不純物の侵入を防止するプロッキング膜として機能する。

#### 【0060】

次に、絶縁層703上に絶縁層801～805を形成する。なお、絶縁層801～805は、後に形成される薄膜トランジスタ744～748のチャネル形成領域に対応する位置に配置されるように形成する。

#### 【0061】

次に、絶縁層703及び絶縁層801～805上に、非晶質半導体層704（例えば非晶質珪素を含む層）を形成する。その後、実施の形態1と同様な方法を用いて非晶質半導体層704を結晶化して得られた結晶質半導体層を所望の形状にエッチングして、結晶質半導体層706～710を形成する（図8（B））。

10

#### 【0062】

次に、結晶質半導体層706～710を覆うゲート絶縁層705を形成する。ゲート絶縁層705は、プラズマCVD法やスパッタ法により、珪素の酸化物又は珪素の窒化物を含む層を、単層又は積層して形成する。具体的には、酸化珪素を含む層、酸化窒化珪素を含む層、窒化酸化珪素を含む層を、単層又は積層して形成する。

20

#### 【0063】

次に、ゲート絶縁層705上に、第1の導電層と第2の導電層を積層して形成する。第1の導電層は、プラズマCVD法やスパッタリング法により、20～100nmの厚さで形成する。第2の導電層は、100～400nmの厚さで形成する。第1の導電層と第2の導電層は、タンタル（Ta）、タングステン（W）、チタン（Ti）、モリブデン（Mo）、アルミニウム（Al）、銅（Cu）、クロム（Cr）、ニオブ（Nb）等から選択された元素又はこれらの元素を主成分とする合金若しくは化合物で形成する。または、リン等の不純物元素をドーピングした多結晶珪素に代表される半導体材料により形成する。第1の導電層と第2の導電層の組み合わせの例を挙げると、窒化タンタル層とタングステン層、窒化タングステン層とタングステン層、窒化モリブデン層とモリブデン層等が挙げられる。タングステンや窒化タンタルは、耐熱性が高いため、当該材料で第1の導電層と第2の導電層を形成した後に、不純物元素の熱活性化を目的とした加熱処理を行うことができる。また、2層構造ではなく、3層構造の場合は、モリブデン層とアルミニウム層とモリブデン層の積層構造を採用するとよい。

30

#### 【0064】

次に、フォトリソグラフィ法を用いてレジストからなるマスクを形成し、ゲート電極とゲート線を形成するためのエッチング処理を行って、ゲート電極として機能する導電層716～725（ゲート電極層とよぶことがある）を形成する。

#### 【0065】

次に、フォトリソグラフィ法により、レジストからなるマスクを形成して、結晶質半導体層706、708～710に、イオンドープ法又はイオン注入法により、N型を付与する不純物元素を低濃度に添加して、N型不純物領域711、713～715とチャネル形成領域780、782～784を形成する。N型を付与する不純物元素は、15族に属する元素を用いれば良く、例えばリン（P）、砒素（As）を用いる。

40

#### 【0066】

次に、フォトリソグラフィ法によりレジストからなるマスクを形成して、結晶質半導体層707に、P型を付与する不純物元素を添加して、P型不純物領域712とチャネル形成領域781を形成する。P型を付与する不純物元素は、例えばボロン（B）を用いる。

#### 【0067】

次に、ゲート絶縁層705と導電層716～725を覆うように、絶縁層を形成する。絶縁層は、プラズマCVD法やスパッタ法により、珪素、珪素の酸化物又は珪素の窒化物

50

の無機材料を含む層や、有機樹脂などの有機材料を含む層を、単層又は積層して形成する。次に、絶縁層を、基板表面に対して垂直方向を主体とした異方性エッチングにより選択的にエッチングして、導電層 716～725 の側面に接する絶縁層 739～743（サイドウォールともよばれる）を形成する（図 8（C））。また、絶縁層 739～743 の作製と同時に、絶縁層 705 がエッチングされ絶縁層 734～738 を形成する。絶縁層 739～743 は、後に LDD（Lightly Doped drain）領域を形成する際のドーピング用のマスクとして用いる。

#### 【0068】

次に、フォトリソグラフィ法を用いて形成したレジストからなるマスクと、絶縁層 739～743 をマスクとして用いて、結晶質半導体層 706、708～710 に N 型を付与する不純物元素を添加して、第 1 の N 型不純物領域 727、729、731、733（LDD 領域ともいう）と、第 2 の N 型不純物領域 726、728、730、732（ソース領域又はドレイン領域ともいう）とを形成する。第 1 の N 型不純物領域 727、729、731、733 が含む不純物元素の濃度は、第 2 の N 型不純物領域 726、728、730、732 の不純物元素の濃度よりも低い。上記工程を経て、N 型の薄膜トランジスタ 744、746～748 と、P 型の薄膜トランジスタ 745 が完成する。

#### 【0069】

なお、LDD 領域を形成するためにサイドウォールの絶縁層をマスクとして用いる手法は、LDD 領域の幅の制御が容易であり、また、LDD 領域を確実に形成することができる。

10

20

30

40

#### 【0070】

続いて、薄膜トランジスタ 744～748 を覆うように、絶縁層を単層又は積層して形成する（図 9（A））。薄膜トランジスタ 744～748 を覆う絶縁層は、SOG 法、液滴吐出法等により、珪素の酸化物や珪素の窒化物等の無機材料、ポリイミド、ポリアミド、ベンゾシクロブテンポリマー、アクリルポリマー、エポキシポリマー、シロキサンポリマー等の有機材料等により、単層又は積層で形成する。例えば、薄膜トランジスタ 744～748 を覆う絶縁層が 3 層構造の場合、1 層目の絶縁層 749 として酸化珪素を含む層を形成し、2 層目の絶縁層 750 として樹脂を含む層を形成し、3 層目の絶縁層 751 として窒化珪素を含む層を形成するとよい。

#### 【0071】

なお、絶縁層 749～751 を形成する前、又は絶縁層 749～751 のうちの 1 つ又は複数の薄膜を形成した後に、半導体層の結晶性の回復や半導体層に添加された不純物元素の活性化、半導体層の水素化を目的とした加熱処理を行うとよい。加熱処理には、熱アニール法、レーザアニール法又は RTA 法などを適用するとよい。

#### 【0072】

次に、フォトリソグラフィ法を用いて絶縁層 749～751 をエッチングして、第 2 の N 型不純物領域 726、728、730、732、P 型不純物領域 712 を露出させるコントラクトホールを形成する。続いて、コントラクトホールを充填するように、導電層を形成し、当該導電層をパターン加工して、ソース電極又はドレイン電極として機能する導電層 752～761 を形成する。

#### 【0073】

導電層 752～761 は、プラズマ CVD 法やスパッタリング法により、チタン（Ti）、アルミニウム（Al）、ネオジム（Nd）から選択された元素、又はこれらの元素を主成分とする合金若しくは化合物で、単層又は積層で形成する。アルミニウムを主成分とする合金とは、例えば、アルミニウムを主成分としニッケルを含む材料、又は、アルミニウムを主成分とし、ニッケルと、炭素と珪素の一方又は両方とを含む合金に相当する。導電層 752～761 は、例えば、バリア層とアルミニウムシリコン（Al-Si）層とバリア層の積層構造、バリア層とアルミニウムシリコン（Al-Si）層と窒化チタン層とバリア層の積層構造を採用するとよい。なお、バリア層とは、チタン、チタンの窒化物、モリブデン、又はモリブデンの窒化物からなる薄膜に相当する。アルミニウムやアルミニ

50

ウムシリコンは抵抗値が低く、安価であるため、導電層 752～761を形成する材料として最適である。また、積層構造の上層と下層にバリア層を設けると、アルミニウムやアルミニウムシリコンのヒロックの発生を防止することができる。また、チタンを含むバリア層を形成すると、結晶質半導体層上に薄い自然酸化膜ができていたとしても、結晶質半導体層と導電層の間に良好なコンタクトを取ることができる。これは、還元性の高い元素であるチタンがこの自然酸化膜を容易に還元することができるからである。

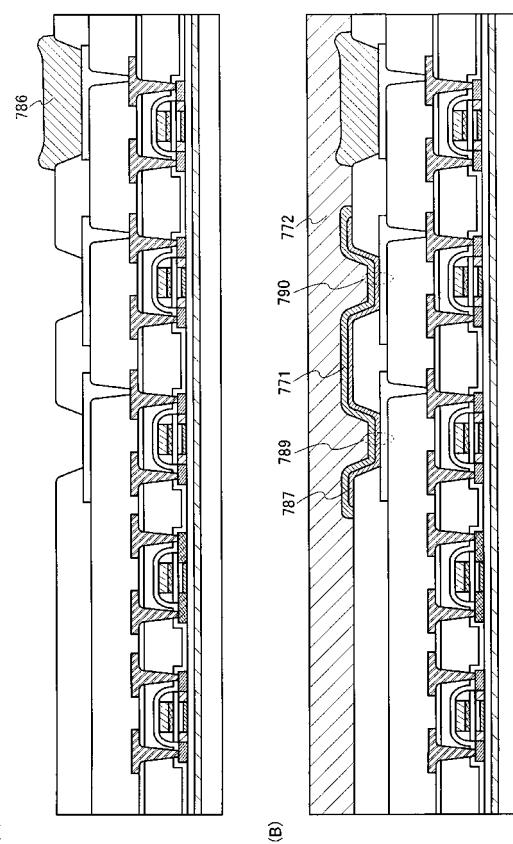

#### 【0074】

次に、導電層 752～761を覆うように、絶縁層 762を形成する(図9(B))。絶縁層 762は、SOG法、液滴吐出法等を用いて、無機材料又は有機材料により、単層又は積層で形成する。また、絶縁層 762は、好適には、0.75μm～3μmの厚さで形成する。

10

#### 【0075】

続いて、フォトリソグラフィ法を用いて絶縁層 762をエッチングして、導電層 757、759、761を露出させるコンタクトホールを形成する。続いて、コンタクトホールを充填するように、導電層を形成する。導電層は、プラズマCVD法やスパッタリング法を用いて、導電性材料により形成する。次に、導電層をパターン加工して、導電層 763～765を形成する。なお、導電層 763、764は、記憶素子が含む一対の導電層のうちの一方の導電層となる。従って、好適には、導電層 763～765は、チタン、又はチタンを主成分とする合金若しくは化合物により、単層又は積層で形成するとよい。チタンは、抵抗値が低いため、記憶素子のサイズを縮小することができ、高集積化を実現することができる。また、導電層 763～765を形成するためのエッチング工程においては、下層の薄膜トランジスタ 744～748にダメージを与えないために、ウエットエッチング加工を行うとよく、エッチング剤にはフッ化水素酸(HF)又はアンモニアと過酸化水素の水溶液を用いるとよい。

20

#### 【0076】

次に、導電層 763～765を覆うように、絶縁層 766を形成する。絶縁層 766は、SOG法、液滴吐出法等を用いて、無機材料又は有機材料により、単層又は積層で形成する。また、絶縁層 766は、好適には、0.75μm～3μmの厚さで形成する。続いて、フォトリソグラフィ法を用いて、絶縁層 766をエッチングして、導電層 763～765を露出させるコンタクトホール 767～769を形成する。

30

#### 【0077】

次に、導電層 765に接するようにアンテナとして機能する導電層 786を形成する(図10(A))。導電層 786は、プラズマCVD法、スパッタリング法、印刷法、液滴吐出法等を用いて、導電性材料により形成する。好ましくは、導電層 786は、アルミニウム(A1)、チタン(Ti)、銀(Ag)、銅(Cu)から選択された元素、又はこれらの元素を主成分とする合金材料若しくは化合物材料で、単層又は積層で形成する。具体的には、導電層 786は、スクリーン印刷法により、銀を含むペーストを用いて膜を形成し、その後、50～350度の加熱処理を行って形成する。又は、スパッタリング法によりアルミニウム層を形成し、当該アルミニウム層をパターン加工することにより形成する。アルミニウム層のパターン加工は、ウエットエッチングによる加工を用いるとよく、ウエットエッチングによる加工後は200～300度の加熱処理を行うとよい。

40

#### 【0078】

次に、導電層 763、764に接するように有機化合物層 787を形成する(図10(B))。有機化合物層 787は、蒸着法、液滴吐出法、スピンドルコート法、スクリーン印刷法等により形成する。続いて、有機化合物層 787に接するように、導電層 771を形成する。導電層 771は、スパッタリング法や蒸着法等により形成する。

#### 【0079】

以上の工程を経て、導電層 763、有機化合物層 787および導電層 771の積層体からなる記憶素子 789と、導電層 764、有機化合物層 787および導電層 771の積層体からなる記憶素子 790が完成する。

50

## 【0080】

なお、上記の作製工程では、有機化合物層787の耐熱性が強くないため、アンテナとして機能する導電層786を形成する工程の後に、有機化合物層787を形成する工程を行うことを特徴とする。

## 【0081】

次に、記憶素子789、790、アンテナとして機能する導電層786を覆うように、SOG法、液滴吐出法等により、保護層として機能する絶縁層772を形成する。絶縁層772は、DLC(ダイヤモンドライクカーボン)などの炭素を含む層、窒化珪素を含む層、窒化酸化珪素を含む層、有機材料により形成した層、好ましくはエポキシ樹脂により形成した層を用いる。

10

## 【0082】

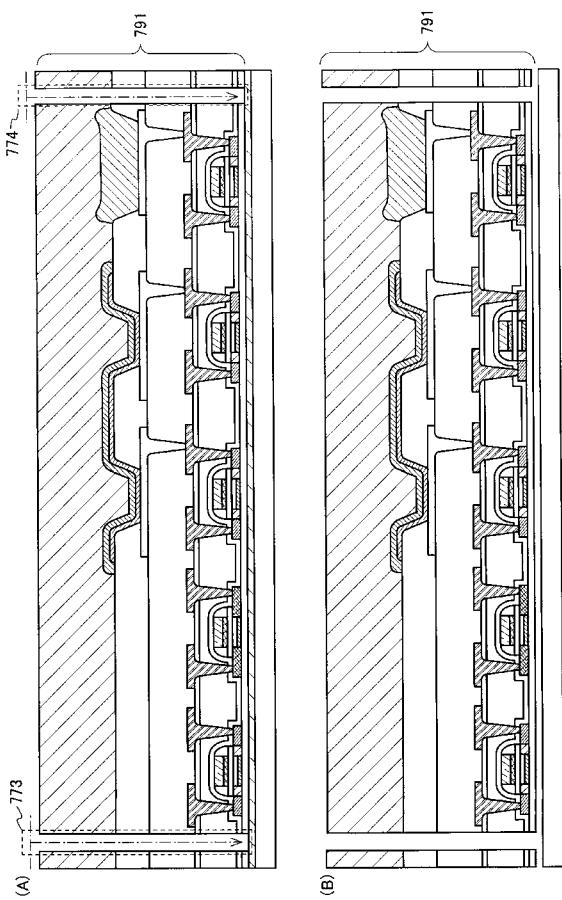

次に、薄膜集積回路791を基板701から剥離する。ここでは、レーザビーム(例えばUV領域の波長のレーザ光)を照射することによって開口部773、774を形成後(図11(A))、物理的な力を用いて基板701から薄膜集積回路791を剥離することができる。また、開口部773、774を形成後、基板701から薄膜集積回路791を剥離する前に、開口部773、774にエッティング剤を導入して、剥離層702を除去した後(図11(B))に剥離してもよい。エッティング剤は、フッ化ハロゲンまたはハロゲン化合物を含む気体又は液体を使用する。例えば、フッ化ハロゲンを含む気体として三フッ化塩素(C<sub>1</sub>F<sub>3</sub>)を使用する。このエッティングプロセスによって剥離層702を除去することにより、薄膜集積回路791は、基板701から剥離された状態となる。なお、剥離層702は、全て除去せず一部分を残存させてもよい。こうすることによって、エッティング剤の消費量を抑え剥離層の除去に要する処理時間を短縮することが可能となる。また、剥離層702の一部を残存させることで、剥離層702の除去プロセス後でも、基板701上に薄膜集積回路791を保持しておくことが可能となる。

20

## 【0083】

薄膜集積回路791が剥離された基板701は、製造コストの削減のために、再利用するとよい。また、絶縁層772は、剥離層702を除去した後に、薄膜集積回路791が飛散しないように形成したものである。薄膜集積回路791は小さく薄く軽いために、剥離層702を除去した後は、基板701に密着していないために飛散しやすい。しかしながら、薄膜集積回路791上に絶縁層772を形成することで、薄膜集積回路791に絶縁層772の重みが付くため、基板701からの飛散を防止することができる。また、薄膜集積回路791単体では薄くて軽いが、絶縁層772を形成することで、巻かれた形状になることがなく、ある程度の強度を確保することができる。

30

## 【0084】

次に、薄膜集積回路791の一方の面を、第2の基体776に接着させて、基板701から完全に剥離する。続いて、薄膜集積回路791の他方の面を、第1の基体775に接着させ、その後加熱処理と加圧処理の一方又は両方を行って、薄膜集積回路791を、第1の基体775と第2の基体776により封止する。これにより、図7(B)に示す半導体装置を作製することができる。第1の基体775と第2の基体776は、ポリプロピレン、ポリエステル、ポリフッ化ビニル、塩化ビニルなどからなるフィルム、繊維質な材料からなる紙、基材フィルム(ポリエステル、ポリアミド、無機蒸着フィルム、紙類等)と接着性合成樹脂フィルム(アクリル系合成樹脂、エポキシ系合成樹脂等)との積層フィルムなどを用いることができる。フィルムは、熱圧着により被処理体(すなわち、薄膜集積回路791)と接着される。加熱処理と加圧処理を行う際には、フィルムの最表面に設けられた接着層か、又は最外層に設けられた層(接着層ではない)を加熱処理によって溶かし、加圧により被処理体に接着する。また、第1の基体775と第2の基体776の表面には接着層が設けられていてもよいし、接着層が設けられていてもよい。接着層は、熱硬化樹脂、紫外線硬化樹脂、エポキシ樹脂系接着剤、樹脂添加剤等の接着剤を含む層を用いることができる。

40

## 【0085】

50

以上の工程により、記憶素子およびアンテナを有する非接触でデータの入出力が可能な半導体装置を作製することができる。

#### 【0086】

本実施の形態に示す半導体装置では、凸部が設けられた絶縁層上に形成された半導体層を溶融して平坦化することにより、ソース領域又はドレイン領域の膜厚をチャネル形成領域の膜厚より厚く形成する。ソース領域又はドレイン領域の膜厚がチャネル形成領域の膜厚と比較して大きいためイオンドープ法等による不純物元素の添加後に行われる、不純物元素の熱活性化のための熱処理における結晶性回復に有利であり、ソース領域又はドレイン領域の高抵抗化を抑制することができる。また、チャネル形成領域の膜厚がソース領域又はドレイン領域の膜厚と比較して小さいためS値を小さくでき、オン電流の低下を抑制することができる。また、半導体層を溶融して平坦化するため、プロセスを増加させることなく容易に半導体装置を作製することが可能である。従って、S値が小さく且つオン電流の低下が抑えられた応答性のよい半導体装置を容易に作製することが可能である。

10

#### 【0087】

##### (実施の形態3)

本実施の形態では、非接触でデータの入出力が可能である半導体装置のブロック図の一例について説明する。なお、非接触でデータの入出力が可能である半導体装置は利用の形態によっては、RFIDタグ、IDタグ、ICタグ、ICチップ、RFタグ、無線タグ、電子タグまたは無線チップともよばれる。

20

#### 【0088】

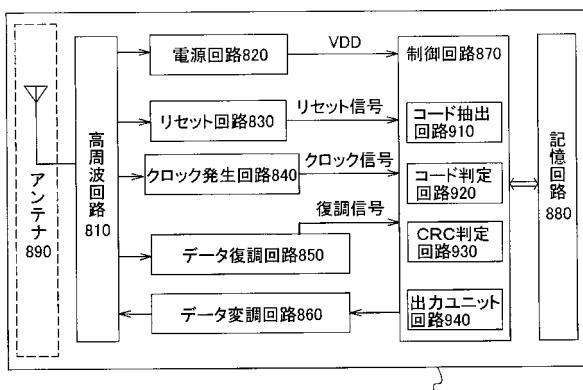

図12に非接触でデータの入出力が可能である半導体装置の構成を説明するブロック図を示す。非接触でデータの入出力が可能である半導体装置800は、非接触でリーダ/ライタとデータを交信する機能を有し、高周波回路810、電源回路820、リセット回路830、クロック発生回路840、データ復調回路850、データ変調回路860、他の回路の制御を行う制御回路870、記憶回路880およびアンテナ890を有している。なお、図12に示す記憶回路880は図7に示すメモリ部202に相当し、図12に示す高周波回路810、電源回路820、リセット回路830、クロック発生回路840、データ復調回路850、データ変調回路860、及び制御回路870は図7に示す集積回路部201に相当し、図12に示すアンテナ890は図7に示すアンテナ303に相当する。

30

#### 【0089】

高周波回路810はアンテナ890より信号を受信して、データ変調回路860より受信した信号をアンテナ890から出力する回路であり、電源回路820は受信信号から電源電位を生成する回路であり、リセット回路830は受信信号からリセット信号を生成する回路であり、クロック発生回路840はアンテナ890から入力された受信信号を基に各種クロック信号を生成する回路であり、データ復調回路850は受信信号を復調して制御回路870に出力する回路であり、データ変調回路860は制御回路870から受信した信号を変調する回路である。また、制御回路870としては、例えばコード抽出回路910、コード判定回路920、CRC判定回路930および出力ユニット回路940が設けられている。なお、コード抽出回路910は制御回路870に送られてきた命令に含まれる複数のコードをそれぞれ抽出する回路であり、コード判定回路920は抽出されたコードとリファレンスに相当するコードとを比較して命令の内容を判定する回路であり、CRC判定回路930は判定されたコードに基づいて送信エラー等の有無を検出する回路である。

40

#### 【0090】

次に、上述した半導体装置の動作の一例について説明する。まず、アンテナ890により無線信号が受信される。無線信号は高周波回路810を介して電源回路820に送られ、高電源電位(以下、VDDと記す。)が生成される。VDDは半導体装置800が有する各回路に供給される。また、高周波回路810を介してデータ復調回路850に送られた信号は復調される(以下、復調信号と記す)。さらに、高周波回路810を介してリセ

50

ット回路 830 およびクロック発生回路 840 を通った信号及び復調信号は制御回路 870 に送られる。制御回路 870 に送られた信号は、コード抽出回路 910、コード判定回路 920 およびCRC判定回路 930 等によって解析される。そして、解析された信号にしたがって、記憶回路 880 内に記憶されている半導体装置の情報が出力される。出力された半導体装置の情報は出力ユニット回路 940 を通って符号化される。さらに、符号化された半導体装置 800 の情報はデータ変調回路 860 を通って、アンテナ 890 により無線信号に載せて送信される。なお、半導体装置 800 を構成する複数の回路においては、低電源電位（以下、VSS）は共通であり、VSS は GND とすることができます。また、上記した薄膜トランジスタに代表される半導体素子を用いて高周波回路 810、電源回路 820、リセット回路 830、クロック発生回路 840、データ復調回路 850、データ変調回路 860、他の回路の制御を行う制御回路 870、記憶回路 880 等を形成することができる。10

#### 【0091】

このように、リーダ／ライタから半導体装置 800 に信号を送り、当該半導体装置 800 から送られてきた信号をリーダ／ライタで受信することによって、半導体装置のデータを読み取ることが可能となる。

#### 【0092】

また、半導体装置 800 は、各回路への電源電圧の供給を電源（バッテリー）を搭載せず電磁波により行うタイプとしてもよいし、電源（バッテリー）を搭載して電磁波と電源（バッテリー）により各回路に電源電圧を供給するタイプとしてもよい。20

#### 【0093】

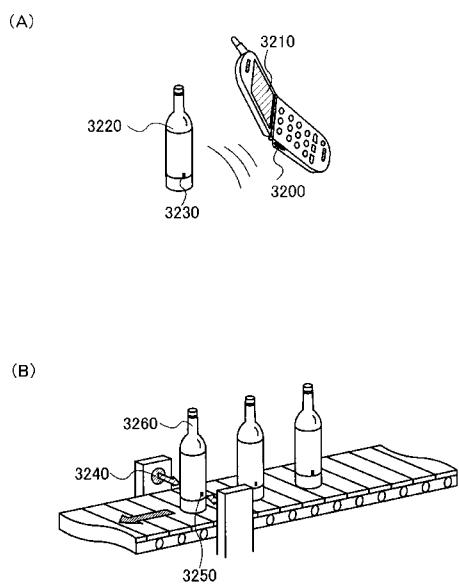

次に、非接触でデータの入出力が可能な半導体装置の利用形態の一例について図 13 を用いて説明する。表示部 3210 を含む携帯端末の側面には、リーダ／ライタ 3200 が設けられ、品物 3220 の側面には半導体装置 3230 が設けられる（図 13（A））。品物 3220 に含まれる半導体装置 3230 にリーダ／ライタ 3200 をかざすと、表示部 3210 に品物の原材料や原産地、生産工程ごとの検査結果や流通過程の履歴等、更に商品の説明等の商品に関する情報が表示される。また、商品 3260 をベルトコンベアにより搬送する際に、リーダ／ライタ 3240 と、商品 3260 に設けられた半導体装置 3250 を用いて、該商品 3260 の検品を行うことができる（図 13（B））。このように、システムに半導体装置を活用することで、情報の取得を簡単に行うことができ、種々の品物の高機能化と高付加価値化を実現する。30

#### 【0094】

本実施の形態の半導体装置は、例えば、紙幣、硬貨、有価証券類、証書類、無記名債券類、包装用容器類、書籍類、記録媒体等、身の回り品、乗物類、食品類、衣類、保健用品類、生活用品類、薬品類及び電子機器等に設けて使用することができる。これらの例に関して、本発明の半導体装置の利用形態を図 14、図 15 を用いて説明する。

#### 【0095】

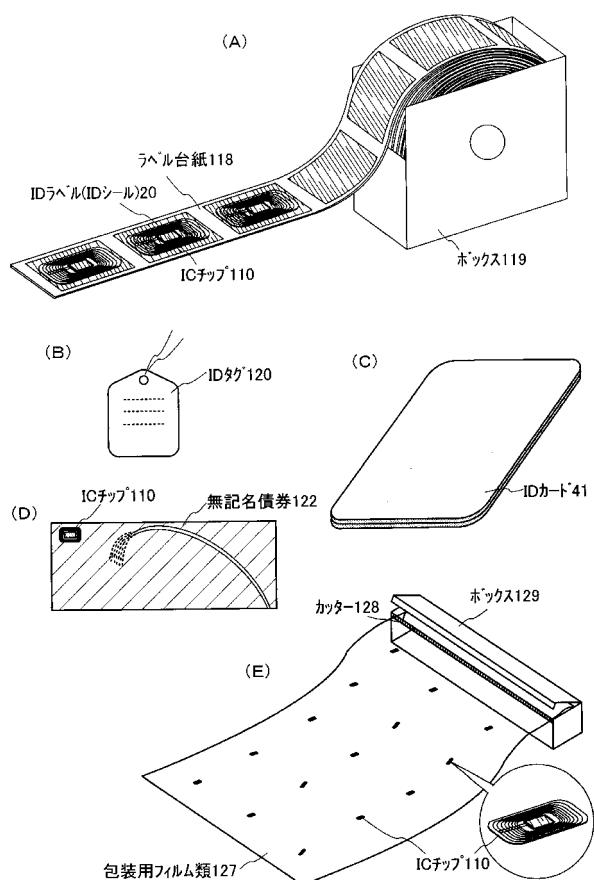

図 14（A）は、本発明に係る ID ラベルの完成品の状態の一例である。ラベル台紙（セパレート紙）118 上に、ICチップ 110 を内蔵した複数の ID ラベル 20（ID シール）が形成されている。ID ラベル 20 は、ボックス 119 内に収納されている。また、ID ラベル 20 上には、その商品や役務に関する情報（商品名、ブランド、商標、商標権者、販売者、製造者等）が記されており、一方、内蔵されている ICチップ 110 には、その商品（又は商品の種類）固有の ID ナンバーが付されており、偽造や、商標権、特許権等の知的財産権侵害、不正競争等の不法行為を容易に把握することができる。また、ICチップ 110 内には、商品の容器やラベルに明記しきれない多大な情報、例えば、商品の産地、販売地、品質、原材料、効能、用途、数量、形状、価格、生産方法、使用方法、生産時期、使用時期、賞味期限、取扱説明、商品に関する知的財産情報等を入力しておくことができ、取引者や消費者は、簡易なリーダによって、それらの情報にアクセスすることができる。また、生産者側からは容易に書換え、消去等も可能であるが、取引者、消費者側からは書換え、消去等ができない仕組みになっている。4050

## 【0096】

図14（B）は、本発明に係るICチップを内蔵したIDタグ120を示している。IDタグを商品に備え付けることにより、商品管理が容易になる。例えば、商品が盗難された場合に、商品の経路を辿ることによって、その犯人を迅速に把握することができる。このように、IDタグを備えることにより、所謂トレーサビリティ（traceability；複雑化した製造、流通の各段階で問題が生じた場合に、経路を遡ることによって、その原因を迅速に把握できる態勢を整えること。）に優れた商品を流通させることができる。

## 【0097】

図14（C）は、本発明に係るIDカード41の完成品の状態の一例である。上記IDカードとしては、キャッシュカード、クレジットカード、プリペイドカード、電子乗車券、電子マネー、テレフォンカード、会員カード等のあらゆるカード類が含まれる。

10

## 【0098】

図14（D）は、本発明に係るICチップ110を内蔵した無記名債券122の完成品の状態の一例である。上記無記名債券類としては、切手、切符、チケット、入場券、商品券、図書券、文具券、ビール券、おこめ券、各種ギフト券、各種サービス券等が含まれるが、勿論これらに限定されるものではない。また、無記名債権に限らず小切手、証券、約束手形等の有価証券類、運転免許証、住民票等の証書類等にICチップを設けることができる。

20

## 【0099】

図14（E）は、ICチップ110を内蔵した商品を包装するための包装用フィルム類127を示している。包装用フィルム類127は、例えば、下層フィルム上に、ICチップを任意にばらまき、上層フィルムで覆うことによって作製することができる。包装用フィルム類127は、ボックス129に収納されており、所望の量だけカッター128で切り離して利用することができる。なお、包装用フィルム類127としての素材は特に制限されない。例えば、薄膜樹脂、アルミ箔、紙等を用いることができる。

20

## 【0100】

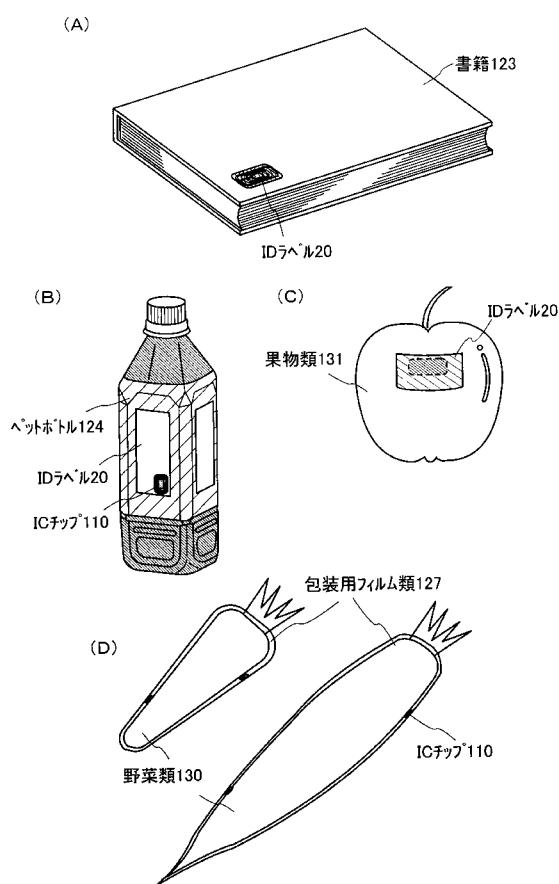

図15は本発明に係るIDラベル20を貼付した書籍123、図15（B）は本発明に係るICチップ110を内蔵したIDラベル20を貼付したペットボトル124を示している。なお、IDラベルを設ける物品はこれらに限定されない。お弁当等の包装紙等の包装用容器類、DVDソフト、ビデオテープ等の記録媒体、自転車等の車両、船舶等の乗物類、鞄、眼鏡等の身の回り品、食料品、飲料等の食品類、衣服、履物等の衣類、医療器具、健康器具等の保健用品類、家具、照明器具等の生活用品類、医薬品、農薬等の薬品類、液晶表示装置、EL表示装置、テレビジョン装置（テレビ受像機、薄型テレビ受像機）、携帯電話等の電子機器等様々な物品にIDラベルを設けることができる。本発明に用いられるIDラベル20は非常に薄いため、上記書籍等の物品にIDラベル20を搭載しても、機能、デザイン性を損ねることがない。更に、本発明に係るICチップ110が非接触でデータの入出力が可能である場合、アンテナを薄膜集積回路の一部として一体形成でき、曲面を有する商品に直接転写することができる。

30

## 【0101】

図15（C）は、果物類131の生鮮食品に、直接IDラベル20を貼り付けた状態を示している。また、図15（D）は、ICチップ110を内蔵した包装用フィルム類127によって、野菜類130等の生鮮食品を包装した一例を示している。なお、IDラベルを商品に貼り付けた場合、剥がされる可能性があるが、包装用フィルム類によって商品をくるんだ場合、包装用フィルム類を剥がすのは困難であるため防犯対策上のメリットがある。

40

## 【0102】

紙幣、硬貨、有価証券類、証書類、無記名債券類等にRFIDタグを設けることにより、偽造を防止することができる。また、包装用容器類、書籍類、記録媒体等、身の回り品、食品類、衣類、生活用品類、電子機器等にRFIDタグを設けることにより、検品シス

50

テムやレンタル店のシステムなどの効率化を図ることができる。乗物類、保健用品類、薬品類等にRFIDタグを設けることにより、偽造や盗難の防止、薬品類ならば、薬の服用の間違いを防止することができる。RFIDタグは、物品の表面に貼ったり、物品に埋め込んだりして設ける。例えば、本ならば紙に埋め込んだり、有機樹脂からなるパッケージならば当該有機樹脂に埋め込んだりするとよい。

#### 【0103】

このように、包装用容器類、書籍類、記録媒体等、身の回り品、食品類、衣類、生活用品類、電子機器等にRFIDタグを設けることにより、検品システムやレンタル店のシステムなどの効率化を図ることができる。また乗物類、保健用品類、薬品類等にRFIDタグを設けることにより、偽造や盗難を防止することができる。また、本発明の半導体装置は薄いため、動物等の生き物に容易に埋め込むことが可能であり、個々の生き物の識別を容易に行うことができる。例えば、家畜等の生き物にRFIDタグを埋め込むことによって、生まれた年や性別または種類等を容易に識別することが可能となる。

10

#### 【0104】

以上のように、本実施の形態の半導体装置は物品あればどのようなものにでも設けて使用することができる。

#### 【図面の簡単な説明】

#### 【0105】

【図1】本発明の半導体装置の構成を説明する上面図及び断面図。

20

【図2】本発明の半導体装置の作製工程を説明する図。

【図3】本発明の半導体装置の作製工程を説明する図。

【図4】本発明の半導体装置の作製工程を説明する図。

【図5】本発明の薄膜トランジスタの作製工程を説明する図。

【図6】本発明の薄膜トランジスタの構成を説明する図。

【図7】本発明の半導体装置の構成を説明する上面図及び断面図。

【図8】本発明の半導体装置の作製工程を説明する断面図。

【図9】本発明の半導体装置の作製工程を説明する断面図。

30

【図10】本発明の半導体装置の作製工程を説明する断面図。

【図11】本発明の半導体装置の作製工程を説明する断面図。

【図12】本発明の半導体装置の構成を説明するブロック図。

【図13】本発明の半導体装置の利用形態を説明する図。

【図14】本発明の半導体装置の利用形態を説明する図。

【図15】本発明の半導体装置の利用形態を説明する図。

【図16】本発明の半導体装置の構成を説明する図。

#### 【符号の説明】

#### 【0106】

40

3 0 基板

3 1 絶縁層

3 2 半導体層

3 3 ゲート絶縁層

3 4 導電層

2 0 3 絶縁層

2 0 4 導電層

2 0 5 薄膜トランジスタ

3 2 a チャネル形成領域

3 2 b 不純物領域

3 2 c 不純物領域

【図1】

【図2】

【図3】

【図4】

【図5】

【 図 6 】

【 図 7 】

【 四 8 】

【図 9】

【図 10】

【図 11】

【図 12】

【図 1 3】

【図 1 4】

【図 1 5】

【図 1 6】

---

フロントページの続き

| (51) Int.CI.                                                      | F I                 | テーマコード(参考) |

|-------------------------------------------------------------------|---------------------|------------|

| H 0 1 L 27/10 (2006.01)                                           | H 0 1 L 27/10 4 4 9 |            |

|                                                                   | H 0 1 L 27/10 4 8 1 |            |

| F ターム(参考) 5F083 FZ07 GA27 HA02 JA03 JA05 JA36 JA37 JA39 JA40 JA56 |                     |            |

| JA58 JA60 PR23 PR33 PR34 PR43 PR44 PR45 PR53 PR54                 |                     |            |

| PR55 ZA11                                                         |                     |            |

| 5F110 AA01 AA07 AA16 BB04 BB05 BB20 CC02 DD01 DD02 DD03           |                     |            |

| DD05 DD13 DD15 DD17 DD21 EE01 EE02 EE03 EE04 EE06                 |                     |            |

| EE09 EE14 EE15 EE22 EE23 EE27 EE32 EE44 EE45 FF01                 |                     |            |

| FF02 FF03 FF04 FF09 FF22 FF26 FF28 FF29 FF30 FF36                 |                     |            |

| GG01 GG02 GG13 GG25 GG54 GG58 HJ01 HJ04 HJ12 HJ13                 |                     |            |

| HJ23 HK05 HL01 HL02 HL03 HL04 HL06 HL11 HL12 HM15                 |                     |            |

| NN03 NN04 NN22 NN23 NN24 NN27 NN28 NN34 NN35 NN71                 |                     |            |

| PP02 PP04 PP05 PP06 PP10 PP26 PP29 QQ09 QQ11 QQ16                 |                     |            |

| QQ19 QQ22                                                         |                     |            |

| 5F152 AA06 BB02 CC02 CC03 CC04 CC05 CC06 CC08 CD12 CD13           |                     |            |

| CD14 CD15 CD17 CD22 CD23 CD24 CE05 CE06 CE24 FF02                 |                     |            |

| FF03 FF04 FF05 FF06 FF07 FF08 FF28 FF47 FG01 FG05                 |                     |            |

| FG23 FH02 LP01 LP06 MM04 NN03 NN12 NN14 NN16 NN19                 |                     |            |

| NN20 NP13 NP14 NQ03 NQ04                                          |                     |            |