(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3661890号

(P3661890)

(45) 発行日 平成17年6月22日(2005.6.22)

(24) 登録日 平成17年4月1日(2005.4.1)

(51) Int.C1.<sup>7</sup>

F 1

H04N 7/24

H04N 7/13

Z

H03M 7/14

H03M 7/14

B

H04L 7/10

H04L 7/10

H04L 25/49

H04L 25/49

A

請求項の数 8 (全 12 頁)

(21) 出願番号

特願平7-347780

(22) 出願日

平成7年12月15日(1995.12.15)

(65) 公開番号

特開平9-168147

(43) 公開日

平成9年6月24日(1997.6.24)

審査請求日

平成13年7月13日(2001.7.13)

(73) 特許権者 000002185

ソニー株式会社

東京都品川区北品川6丁目7番35号

(74) 代理人 100082740

弁理士 田辺 恵基

(72) 発明者 菊池 秀和

東京都品川区北品川6丁目7番35号ソニ

一株式会社内

審査官 清水 祐樹

最終頁に続く

(54) 【発明の名称】画像データ送信方法及び画像データ受信方法

## (57) 【特許請求の範囲】

## 【請求項 1】

m ビット単位の画像データを送信するための画像データ送信方法であつて、

上記画像データの同期タイミングを設定させるための同期データを送信せずに m ビット

の上記画像データを送信する場合には、m ビットの上記画像データを変換することにより

n (但し n > m) ビットの変換後データを生成し、当該生成した変換後データを直列送信

する第 1 のステップと、

上記同期データと m ビットの上記画像データとを送信する場合には、m ビットの上記画

像データに対して上記同期データを示す n - m ビットの直列コードを付加することにより

n ビットの付加後データを生成し、当該生成した付加後データを直列送信する第 2 のステ

ップと

を有し、上記第 1 のステップでは、

m ビットのデータと、いかなる組み合わせで順次直列送信されても同一論理ビットが k

(但し k < n - m ) 個以上連続しないように選択された n ビットのデータとを対応付けて

なる変換表に基づいて、m ビットの上記画像データを変換することにより n ビットの上記

変換後データを生成し、

上記第 2 のステップでは、

m ビットの上記画像データに対して、上記同一論理ビットが k 個以上連続した特定ビッ

ト列を含む上記直列コードを付加することにより、n ビットの上記付加後データを生成す

る

ことを特徴とする画像データ送信方法。

【請求項 2】

上記変換表は、

上記mビットのデータと上記nビットのデータとをそれぞれ分割して対応付けていることを特徴とする請求項1に記載の画像データ送信方法。

【請求項 3】

上記直列コードは、直列化された上記画像データの前に対して付加されることを特徴とする請求項 1 に記載の画像データ送信方法。

【請求項 4】

上記同期データは、垂直同期データ及び水平同期データである

ことを特徴とする請求項 1 に記載の画像データ送信方法。

【請求項 5】

mビット単位の画像データを受信するための画像データ受信方法であつて、

伝送路を介して直列受信したn(但し  $n > m$ )ビットの受信データから、上記画像データの同期タイミングを設定させるための同期データを示す  $n - m$  ビットの直列コードを検出する第1のステップと、

上記第1のステップによつてnビットの上記受信データから上記直列コードを検出した場合には、上記同期タイミングを設定すると共にnビットの上記受信データから上記直列コードを除くことによりmビットの上記画像データを得る第2のステップと、

上記第1のステップによつてnビットの上記受信データから上記直列コードを検出しない場合には、nビットの上記受信データを変換することによりmビットの上記画像データを得る第3のステップと

を有し、

上記第1のステップでは、

nビットの上記受信データから、同一論理ビットがk(但し  $k < n - m$ )個以上連続した特定ビット列が含まれる上記直列コード中の上記特定ビット列を検出することにより上記直列コードを検出し、

上記第3のステップでは、

いかなる組み合わせで順次直列送信されても上記同一論理ビットがk個以上連続しないように選択されたnビットのデータと、mビットのデータとを対応付けてなる変換表に基づいて、nビットの上記受信データを変換することによりmビットの上記画像データを得る

ことを特徴とする画像データ受信方法。

【請求項 6】

上記変換表は、

上記mビットのデータと上記nビットのデータとをそれぞれ分割して対応付けていることを特徴とする請求項5に記載の画像データ受信方法。

【請求項 7】

上記直列コードが検出された上記受信データは、直列化された上記画像データの前に対して上記直列コードが付加されてなる

ことを特徴とする請求項5に記載の画像データ受信方法。

【請求項 8】

上記同期データは、垂直同期データ及び水平同期データである

ことを特徴とする請求項5に記載の画像データ受信方法。

【発明の詳細な説明】

【0001】

【目次】

以下の順序で本発明を説明する。

発明の属する技術分野

10

20

30

40

50

従来の技術（図6及び図7）

発明が解決しようとする課題（図8及び図9）

課題を解決するための手段（図5）

発明の実施の形態（図1～図5）

（1）実施例の構成

（1-1）画像表示システムの構成

（1-2）画像データ変換の規則

（2）実施例の動作

（3）実施例の効果

（4）他の実施例

10

発明の効果

【0002】

【発明の属する技術分野】

本発明は画像データ送信方法及び画像データ受信方法に関し、例えばコンピュータで処理する画像を表示する液晶表示装置に代表されるデジタル制御の表示装置に画像データを伝送する際に適用し得る。

【0003】

【従来の技術】

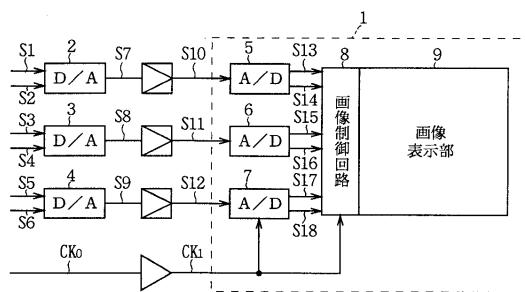

図6に示すように、この種の液晶表示装置1は、一般に、コンピュータで処理するデジタルの3原色画像データS1～S6をそれぞれの原色毎にアナログ化した画像信号S10～S12が伝送される。液晶表示装置1は、この画像信号S10～S12をアナログデジタルコンバータ5～7によってデジタルの画像データS13～S18に戻してリアルタイムで画像の表示状態を制御している。

20

【0004】

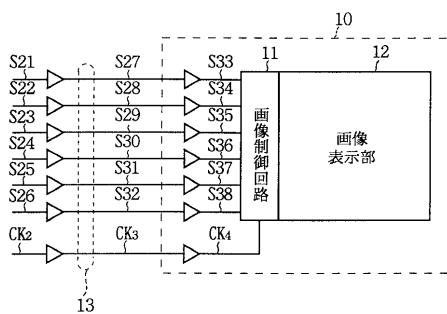

この方法は、表示画素数及び階調の増加に応じて高速、多ビットのアナログデジタルコンバータが必要になるため、液晶表示装置の製造コストが増大するという欠点があつた。このため、図7に示すように、コンピュータ内で並列に処理されている画像データS21～S26を並列で液晶表示装置10に伝送する方法が一部で採用されている。

【0005】

【発明が解決しようとする課題】

30

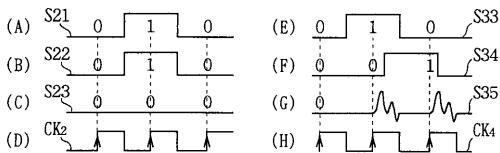

ところで、図8に示すように、複数の芯線を束ねた伝送ケーブル13で画像データS27～S32を並列に伝送する場合は、伝送された画像データS27～S32間の相互干渉によつてスキュー（同期ずれ）やクロストークが発生する。このため、伝送ケーブル13の伝送容量及び伝送距離が制限されると共に、伝送ケーブル13やコネクタが大型化するという問題があつた。

これを避けるため、画像データを直列化して伝送することが考えられる。この方法によれば、画像データのスキュー・クロストークを排除して画像データを伝送することができる。

【0006】

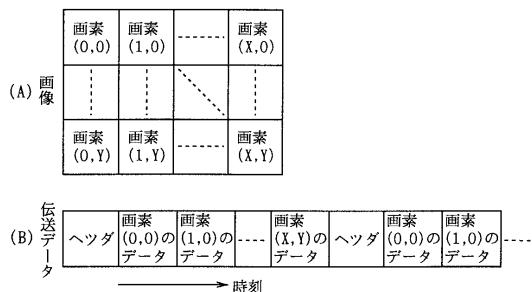

ところが、図9（B）に示すように、従来の直列化では、1枚の画像のそれぞれの画素(0,0)～(X,Y)の画像データを単純にあるビット数で1ワードとなる直列の画像データに変換していた。因みに、図9（A）に示すように、1枚の画像は、水平及び垂直方向にそれぞれX個及びY個の画素で構成されている。

40

この変換方法では、ヘッダと呼ばれる制御データを画像データに付加して、受信した直列の画像データを再び画素毎の画像データに戻すときのワード同期を確立する必要があつた。

【0007】

ところが、このヘッダの1ワードは、画像データの1ワードを構成するビット数と異なるビット数で構成されていた。このため、液晶表示装置内の画像制御回路は、直列の画像データからワード長さが異なるヘッダを識別して取り出す必要があるため、複雑な構成とな

50

るという欠点がある。

#### 【0008】

この方法では、ヘッドを取り出すとき画像データが中断され、安定して受信できないという問題があつた。さらにデジタルの画像データを並列に伝送する方法でも、画像データを伝送するケーブルに加えて、垂直同期データ及び水平同期データを伝送するそれぞれ専用のケーブルが別個に必要であるため、コネクタや伝送ケーブルが大きくなつて取扱いが煩雑になるという欠点があつた。

#### 【0009】

本発明は以上の点を考慮してなされたもので、画像データの送受信を中断させずに画像データ及び同期データを1つの伝送路によつて送受信し得る画像データ送信方法及び画像データ受信方法を提案しようとするものである。

10

#### 【0010】

##### 【課題を解決するための手段】

かかる課題を解決するため本発明においては、mビット単位の画像データを送信するための画像データ送信方法であつて、画像データの同期タイミングを設定させるための同期データを送信せずにmビットの画像データを送信する場合には、mビットの画像データを変換することによりn（但し $n > m$ ）ビットの変換後データを生成し、当該生成した変換後データを直列送信する第1のステップと、同期データとmビットの画像データとを送信する場合には、mビットの画像データに対して同期データを示すn-mビットの直列コードを付加することによりnビットの付加後データを生成し、当該生成した付加後データを直列送信する第2のステップとを有し、第1のステップでは、mビットのデータと、いかなる組み合わせで順次直列送信されても同一論理ビットがk（但し $k < n - m$ ）個以上連続しないように選択されたnビットのデータとを対応付けてなる変換表に基づいて、mビットの画像データを変換することによりnビットの変換後データを生成し、第2のステップでは、mビットの画像データに対して、同一論理ビットがk個以上連続した特定ビット列を含む直列コードを付加することにより、nビットの付加後データを生成するようにした。

20

#### 【0011】

また本発明においては、mビット単位の画像データを受信するための画像データ受信方法であつて、伝送路を介して直列受信したn（但し $n > m$ ）ビットの受信データから、画像データの同期タイミングを設定させるための同期データを示すn-mビットの直列コードを検出する第1のステップと、第1のステップによつてnビットの受信データから直列コードを検出した場合、同期タイミングを設定すると共にnビットの受信データから直列コードを除くことによりmビットの画像データを得る第2のステップと、第1のステップによつてnビットの受信データから直列コードを検出しない場合、nビットの受信データを変換することによりmビットの画像データを得る第3のステップとを有し、第1のステップでは、nビットの受信データから、同一論理ビットがk（但し $k < n - m$ ）個以上連続した特定ビット列が含まれる直列コード中の特定ビット列を検出することにより直列コードを検出し、第3のステップでは、いかなる組み合わせで順次直列送信されても同一論理ビットがk個以上連続しないように選択されたnビットのデータと、mビットのデータとを対応付けてなる変換表に基づいて、nビットの受信データを変換することによりmビットの画像データを得るようにした。

30

#### 【0012】

この結果、送信側から直列送信されるnビットのデータには常に画像データが含まれる。これにより受信側は、送信側から直列受信したnビットのデータから常に画像データを得ることができる。

40

#### 【0013】

##### 【発明の実施の形態】

以下図面について、本発明の一実施例を詳述する。

#### 【0014】

50

## (1) 実施例の構成

### (1-1) 画像表示システムの構成

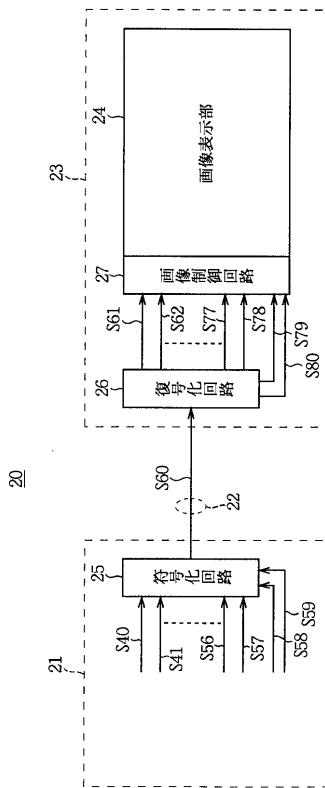

図1は全体として画像表示システム20を示し、本体21においてデータクロツクS40とmビット並列の画像データS41～S57とこれの同期データS58及びS59とを時分割多重によって重畠してnビット直列のデータコードS60を生成する。画像表示システム20は、このデータコードS60を1つの伝送路としての伝送ケーブル22を介して液晶表示装置23に与えて、データコードS60をデータクロツクS61とmビット並列の画像データS62～S78とこれの同期データS79及びS80とに戻す。

これにより、画像表示システム20は、本体21において並列処理している画像を液晶表示装置23の画像表示部24上に表示する際の表示状態を画素毎の画像データを途切れさせずにリアルタイムで制御する。10

#### 【0015】

本体21は、マイクロコンピュータ(図示せず)で制御され、外部より与えられた画像データをビデオRAM(図示せず)に展開している。本体21は、ビデオRAM上の画素毎のmビット並列の画像データをそれぞれのビットでなる画像データS40～S57によつて、集積回路構成の符号化回路25に与える。これにより、本体21は、符号化回路25において画素毎のmビットをm < nであるnビットコードに変換して、それぞれのnビットコードで1ワードを構成したデータコードS60を生成させる。

#### 【0016】

但し、同期データS58及びS59を伝送するとき、本体21は、符号化回路25において同期データS58及びS59を、k < n - mとして同一論理ビットがk個連續した特定ビット列を含むn - mビットコードに符号化する。またこのとき本体21は、画素の画像データの符号化を停止させる。続いて、本体21は、符号化回路25において同期データS58又はS59を示すn - mビットコードを、符号化しなかつたmビットの画像データの先頭に付加して、他のワードと同一のnビットでワードを構成する。20

#### 【0017】

液晶表示装置23は、集積回路構成の復号化回路26において直列のデータコードS60から同期データを得て、この同期データに基づいたタイミングでデータコードS60をnビット毎に区切つてそれぞれのワードを弁別する。データコードS60の全てのワードがnビットで構成されていることにより、復号化回路26内のワードを弁別する回路を簡単に構成することができる。液晶表示装置23は、復号化回路26においてそれぞれのワードをnビットコードからmビットに戻し、mビットのそれぞれのビットでなる並列の画像データS61～S78を画像制御回路27に与える。30

#### 【0018】

但し、ワードの先頭側のn - mビットから同一論理ビットがk個連續した特定ビット列を復号化回路26において検出すると、液晶表示装置23は同期データを得たと判断する。これにより、液晶表示装置23は、特定ビット列に応じて垂直同期データS79や水平同期データS80を復号化回路26において生成して、画像制御回路27に与える。

#### 【0019】

続いて、液晶表示装置23は、特定ビット列を含むn - mビットコードを除いたmビットを復号化回路26において復号することなく画像制御回路27に与える。これにより、液晶表示装置23は、途切れないmビット並列の画素データS61～S78のタイミングを画像制御回路27において垂直同期データS79や水平同期データS80によつて制御して、画像を画像表示部24に表示させる。40

#### 【0020】

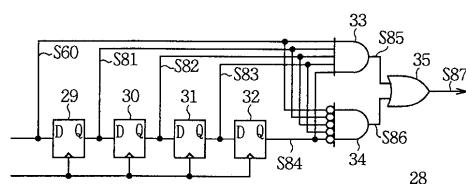

復号化回路26は、例えばkが5である場合、図2に示す同期データ検出回路28を有し、直列のデータコードS60をこの同期データ検出回路28に与えて、同一論理ビットが5個連續した特定ビット列を検出する。同期データ検出回路28は、データコードS60を4つのDフリップフロップ29～32で順次遅延させて1クロツク期間～4クロツク期間遅延させた遅延画像データS81～S84を生成する。50

**【0021】**

同期データ検出回路28は、現在のデータコードS60と遅延画像データS81～S84とをアンド回路33及び NAND 回路34に条件入力として与える。

同期データ検出回路28は、4入力アンド回路33及び4入力 NAND 回路34のそれぞれの出力S85及びS86をオア回路35に条件入力として与える。これにより、同期データ検出回路28は、データコードS60の論理「1」が5個連続した特定ビット列と、論理「0」が5個連続した特定ビット列とを検出することができる。

**【0022】****(1-2) 画像データ変換の規則**

本体21は、符号化回路25においてmビットをnビットコードに変換する際に、所定の変換表を使用して、データコードS60が以下に示す第1～第4の条件を満たすよう変換している。液晶表示装置23は、この所定の変換表を使用して、データコードS60のそれぞれのワードのnビットコードをmビットに逆変換する。

10

**【0023】**

この所定の変換表は、mビットをnビットコードに変換したときのnビットコードの全ての組合せにおいて同一論理ビットの最大連続数jがj < kを満たすようにnビットの任意の論理配列のみが採用されている。またこの所定の変換表によつて任意のmビットと任意のnビットコードとが重複しないよう対応付けられる。

**【0024】**

符号化回路25は、第1～第4の条件に加えて、上述したように、直列のデータコードS60のそれぞれのワードを常にnビットで構成すると共に、全てのワードに画素データを含ませて画素データの伝送を途切れさせないように処理している。

20

**【0025】**

第1の条件は、直列のデータコードS60からクロツクを抽出し易くするため、データコードS60が多量のデータ遷移を含んでいることである。第2の条件は、データコードS60の論理「1」と論理「0」の比が同等又はこれに近いことである。第3の条件は、データコードS60のnビットコードをmビットに戻すときのそれぞれのワードの区切りを検出できる性質をデータコードS60が有することである。第4の条件は、直列化のため冗長ビットを元データに付加する場合、付加ビット数が元データに比して少ないとある。

30

**【0026】**

第1の条件は、電圧が昇降を繰り返す直列のデータコードS60から直列データの論理「0」と論理「1」とを切り出すタイミング信号、即ちクロツクを復号化回路26において抽出するために必要である。復号化回路26は、クロツクをPLL(Phase Locked Loop)回路やSAWフィルタ共振等で抽出する。ところが、データ遷移が少ないと、PLL回路は離調し易くなり、フィルタの出力は低下する。このためデータ遷移は、4～5ビット毎に1回以上発生することが望ましい。

**【0027】**

例えば、撮像対象を撮像して得たいわゆる生の画像データでは、黒色を表示画面全面に表示した完全な黒色画像に対応した画像データが有り得るため、データ遷移が極端に少なくなることがある。このため、並列の画像データを直列に変換するとき、元の画像データは一般に何らかのデータ列に変換(コーディング)されてデータ遷移が増やされる。

40

**【0028】**

データ遷移を増やす際には、一般にスクランブルやmビットnビット変換が使用される。前者は、疑似乱数発生回路を用いて、同一論理ビットが長時間継続するデータが発生することを確率的に阻止する方法である。後者は、mビットの元データをある規則に従つてnビットのデータに変換することによつて、データ遷移を強制的に発生させる方法である。受信側においては、これらの逆変換によつて元データを再生する。

上述したように、符号化回路25は、後者を採用している。

**【0029】**

50

第2の条件は、直列データを高い伝送レートで伝送する過程で発生する信号波形の歪みや減衰に対して、受信マージンを確保する、即ち直流レベルを容易に再生するための条件である。この第2の条件を満たすには、論理「1」と論理「0」との比が1：7～7：1以内であることが望ましい。

#### 【0030】

第3の条件は、送信側において、ある時点の画素データとして1つのセットであつた多ビットのデータ(ワード)を受信側において1つのセットとして切り出すタイミングを検出するための条件である。この第3の条件を満たすには、一般に直列データのどこかに直列データの他の部分には絶対に存在しない、又は極めて稀にしか存在しない特定ビット列を含むデータ列いわゆるヘッダが挿入される。この直列コードとしてのヘッダによつて、ワードを切り出すタイミングを送信側から受信側に伝送することができる。上述したように、符号化回路25は、同一論理ビットがk個連続した特定ビット列を含むn-mビットコードをヘッダとして挿入して同期タイミングを伝える。10

#### 【0031】

第4の条件は、上述した第3の条件を満たす目的で付加されるビット、例えばmビットnビット変換で増えるビットやヘッダのビットが元データに比して少量であるということである。この第4の条件は、直列データの伝送レートが過度に上昇することを抑えて、直列伝送ハードウェアの負担を軽くするための条件であり、元データの1.4倍を越えないことが望ましい。

#### 【0032】

##### (2) 実施例の動作

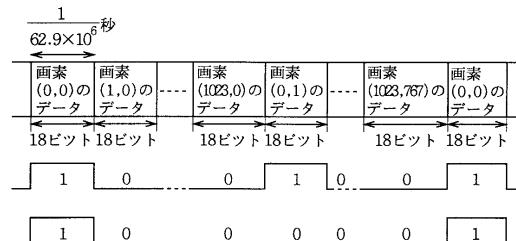

以上の構成において、液晶表示装置23の表示画面の横及び縦の画素数がそれぞれ1024及び768であるとし、画素毎に赤色、緑色及び青色のそれぞれの階調を6ビットで表示して $6 \times 3 = 18$ ビット分の262,144色を表示するとする。また表示速度は80[画面/秒]であるとし、同期データが垂直同期データ及び水平同期データで構成されるとする。この表示を実現する際、本体21は、80[画面/秒] × 1024[列] × 768[行] =  $62.9 \times 10^6$ [個/秒]の画素の画像データを画像制御回路27に与える必要がある。

#### 【0033】

このとき図3に示すように、本体21は、1枚の画像毎に走査線上の最初の画素(0,0)から最後の画素(1023,767)までの画素毎の18ビットの画像データを独立に、又は水平同期データや垂直同期データと共に、同期データの論理レベルに応じた異なる手順に従つて24ビットデータコードに変換して伝送する。30

#### 【0034】

まず水平同期データ及び垂直同期データが論理「0」レベルである(以下、これを同期データが不活性であるという)ときを説明する。このとき、本体21は、符号化回路25において画素毎の18ビット画像データを3ビット毎に区分し、それぞれの3ビットを図4で示す符号化変換表としての変換表TBL1に従つて対応付けて4ビットコードに変換する。

#### 【0035】

続いて、本体21は、18ビットに対応して得た6つの4ビットコードを順次直列に並べて24ビットコードのワードを生成する。これにより、画素毎の画像データは18ビットから24ビットに変換されたことになる。ここで、 $m = 18$ 、 $n = 24$ であり、これは、 $m < n$ を満たしている。

因みに、変換表TBL1上の4ビットコード「0010」、「0011」、「0101」、「0110」、「1001」、「1010」、「1011」及び「1100」は、任意の3ビットデータとそれぞれ対応付けて良い。

#### 【0036】

次に、水平同期データ又は垂直同期データが1である(以下、これを同期データが活性であるという)ときを説明する。図3に示すように、このときは、水平同期データだけが論理「1」である状態と、水平同期データ及び垂直同期データが同時に論理「1」である状

10

20

30

40

50

態とが存在する。

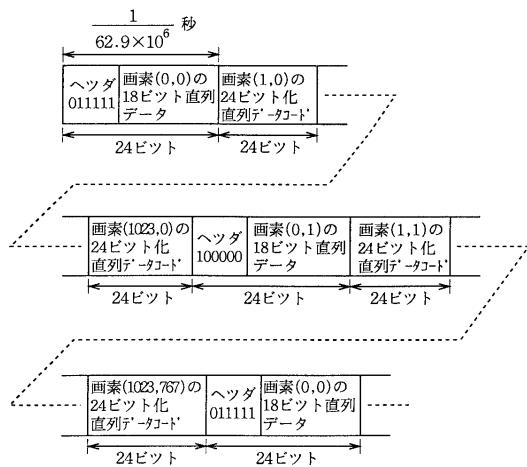

**【0037】**

同期データが活性であるとき、本体21は、符号化回路25において $n - m = 6$ ビットコードでなるヘッダの後に、18ビット画素データを順次並べて24ビットコードを生成する。水平同期データだけが論理「1」であるとき、本体21は、符号化回路25においてヘッダをビット列「100000」で構成する。また両方の同期データが論理「1」であるとき、本体21は、符号化回路25においてヘッダをビット列「011111」で構成する。

**【0038】**

これにより、ヘッダには論理「0」又は論理「1」が5個連續した特定ビット列が含まれていることになる。従つて、 $k = 5$ となり、これは、 $k < n - m$ を満たしている。このようにして図5に示すように、本体21は、18ビット画像データをヘッダと共に全て24ビットコードに変換して順次連結し、画素毎の画像データが途切れない直列のデータコードS60を生成する。

**【0039】**

次に、図5に示す直列のデータコードS60が、上述した第1の条件～第4の条件を満たしていることを説明する。まず、直列のデータコードS60を構成する1024ワードのうち、同期データが不活性であるときに対応したワードが圧倒的な比率(1023 / 1024)を占めることが分かる。図4に示した変換表TBL1では、4ビットコードのデータ遷移が少なくとも1回発生している。これにより、直列のデータコードS60は、全体として最低25%の確率でデータ遷移を発生させてクロツクを容易に抽出することができ、第1の条件を満足させている。

**【0040】**

また変換表TBL1の4ビットコードで最も論理「1」又は論理「0」に偏ったコードでも論理「1」と論理「0」との比は1 : 3である。これにより、画像データが特定の4ビットコードに全て変換されても、論理「1」と論理「0」との比は1 : 3 ~ 3 : 1に限定される。従つて、データコードS60は、直流レベルを容易に再生することができ、第2の条件を満足させている。

**【0041】**

次に、変換表TBL1上の4ビットコードは、いずれをどの順序で組合せて直列に並べても論理「1」が $k = 5$ 個以上連續することも、論理「0」が $k = 5$ 個以上連續することもない。これにより、24ビットコードの先頭6ビットから論理「1」又は論理「0」が5個連續した特定ビット列を検出したとき、液晶表示装置23は、ヘッダが挿入されて同期データが活性であるタイミングを伝送されたと判断することができる。

**【0042】**

従つて、液晶表示装置23は、画素の画像データを中断することなく、このヘッダを、直列のデータコードS60の1ワード = 24ビットの区切りを認識して $n$ ビット直列コードを $m$ ビット並列の画像データS61～S78に戻すためのワード同期を確立する基準として使用することができる。また液晶表示装置23は、ヘッダを受信しているときも画素の画像データを中断することがないことにより、画素の画像データを常に安定して受信することができる。

伝送中に画像データが途切れても、液晶表示装置23は、特定ビット列を検出することによつて、新しい水平走査線の同期タイミングを容易に得ることができる。従つて、データコードS60は、第3の条件を満足させている。

**【0043】**

また、データコードS60のワード長さが全て同一であることにより、ヘッダのワードと画像データのワードとを別個にカウントする必要がなく、ワードをカウントする回路を簡単に構成することができる。

**【0044】**

因みに、同期データが活性であるとき、ヘッダに続いて、変換されていない18ビットの画

10

20

50

30

40

50

像データが伝送される。この18ビットの画像データによつて、偶然論理「1」が5個以上連続したり、論理「0」が5個以上連続することがあり得る。このため、同期データ検出回路28においてヘッダ内の特定ビット列を一度検出した後、少なくとも次のワードに切り換わる迄、同期データ検出回路28の検出機能を停止して、同期データが活性であるタイミングの誤検出を防止することができる。

#### 【0045】

最後に、データコードS60は、画素毎のデータが元の画像データに比して6ビット増加している。このときのデータコードS60の伝送レートは、 $62.9 \times 10^6 \times 24 = 1.51 \times 10^9$  ビット/秒となる。一方、元の画像データの伝送レートは、 $62.9 \times 10^6 \times 18 = 1.13 \times 10^9$  [ビット/秒]となる。データコードS60と元の画像データとの伝送レートの比は1.33となり、元データの1.4倍を越えない。この比は、ハードウェアの負担の観点から、实际上、許容される。これにより、データコードS60は第4の条件を満足させている。10

#### 【0046】

##### (3) 実施例の効果

以上の構成によれば、 $n > m$ 及び $k < n - m$ として、同期データを送信しないときは、画素毎のmビットの画像データを、いかなる組み合わせで順次直列に送信しても同一論理ビットがk個以上連続しないnビットコードS60に変換してこれを直列に送信し、同期データを送信するときは、画素のmビットの画像データをコード化しないで直接直列に並べ、これに同一論理ビットがk個連続した特定ビット列を含むn-mビットを直列に並べたヘッダを付加することにより、並列の画像データの送受信を中断させずに並列の画像データ及び同期データを1つの伝送ケーブル22によって送受信することができる。20

#### 【0047】

また液晶表示装置23への画像データの伝送距離を並列デジタルやアナログで伝送する場合に比して一段と大きくすることができる。

さらに低コストで小さなコネクタと、1本だけであることによる一段と大きな柔軟性に富んだ伝送ケーブルとによって画像データを伝送することができる。

#### 【0048】

##### (4) 他の実施例

なお上述の実施例においては、 $m = 18$ 、 $n = 24$ 、 $k = 5$ 及び $j = 4$ とする場合について述べたが、本発明はこれに限らず、 $n$ 、 $m$ 、 $k$ 及び $j$ を $n > m$ 、 $k < n - m$ 及び $j < k$ となる条件下で任意の数に設定しても良い。30

#### 【0049】

また上述の実施例においては、18ビットから24ビットコードに変換する際、3ビットから4ビットコードに変換し、この4ビットコードを組合せて24ビットコードを得る場合について述べたが、本発明はこれに限らず、任意の数のビットコードを組合せて目的のビット数のコードを得る場合にも適用できる。

#### 【0050】

さらに上述の実施例においては、液晶表示装置を使用する場合について述べたが、本発明はこれに限らず、画像をデジタル信号で制御する任意の画像表示装置、例えばプラズマディスプレイを使用する場合にも適用できる。40

#### 【0051】

さらに上述の実施例においては、直列のデータコードS60を伝送ケーブル13によって伝送する場合について述べたが、本発明はこれに限らず、直列化した画像データを電波や赤外線で伝送する場合にも適用できる。

#### 【0052】

##### 【発明の効果】

上述のように本発明によれば、送信側から直列送信されるnビットのデータには常に画像データが含まれるので、これにより受信側は送信側から直列受信したnビットのデータから常に画像データを得ることができ、かくして画像データを安定して受信することができる画像データ送信方法及び画像データ受信方法を実現することができる。50

## 【図面の簡単な説明】

【図1】本発明による画像データ送信方法及び画像データ受信方法の一実施例による画像表示システムの構成を示す略線的プロツク図である。

【図2】同期データ検出回路の説明に供する接続図である。

【図3】画素毎の並列画像データ及び同期データのタイミングを示すタイミング図である。

【図4】3ビットデータと4ビットコードとを対応付けた変換表を示す図表である。

【図5】直列画像データのデータ配列を示す略線図である。

【図6】従来の画像データ伝送方法を示す略線図である。

【図7】従来の画像データ伝送方法を示す略線図である。

【図8】並列伝送によるスキュー及びクロストークを示す波形図である。

【図9】画素配置及び従来の直列化による画像データの配列を示す略線図である。

## 【符号の説明】

1、10……液晶表示装置、2～4……デジタルアナログコンバータ、5～7……アナログデジタルコンバータ、8、11、27……画像制御回路、9、12、24……画像表示部、13、22……传送ケーブル、20……画像表示システム、21……本体、23……液晶表示装置、25……符号化回路、26……復号化回路、28……同期データ検出回路、29～32……Dフリップフロップ、33……アンド回路、34…… NAND回路、35……オア回路。

10

【図1】

図1 実施例による画像表示システム

【図2】

図2 同期データ検出回路

【図3】

図3 画素毎の並列画像データ及び同期データのタイミング

【図4】

| 元データ<br>(3ビット) | データコード<br>(4ビット) | TBL1 |

|----------------|------------------|------|

| 0 0 0          | 0 0 1 0          |      |

| 0 0 1          | 0 0 1 1          |      |

| 0 1 0          | 0 1 0 1          |      |

| 0 1 1          | 0 1 1 0          |      |

| 1 0 0          | 1 0 0 1          |      |

| 1 0 1          | 1 0 1 0          |      |

| 1 1 0          | 1 0 1 1          |      |

| 1 1 1          | 1 1 0 0          |      |

図4 変換表

【図5】

図5 直列画像データのデータ配列

【図6】

図6 従来の画像データ伝送方法

【図7】

図7 従来の画像データ伝送方法

図8 並列伝送によるスキュー及びクロストーク

【図9】

図9 画素配置及び従来の直列化による画像データの配列

---

フロントページの続き

(56)参考文献 特開平04-113563(JP,A)

特開平02-227880(JP,A)

特開昭63-020920(JP,A)

特開昭62-032737(JP,A)

実開昭59-174758(JP,U)

(58)調査した分野(Int.Cl.<sup>7</sup>, DB名)

H04N 7/00 - 7/088

H04N 7/12

H04N 7/24 - 7/68

H04L 7/00 - 7/10

H04L 25/00 - 25/66

H04M 3/00 - 11/00

JSTPlusファイル(JOIS)