(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第4671600号

(P4671600)

(45) 発行日 平成23年4月20日(2011.4.20)

(24) 登録日 平成23年1月28日(2011.1.28)

(51) Int.Cl.

F 1

|                    |                  |            |         |

|--------------------|------------------|------------|---------|

| <b>H01L 21/02</b>  | <b>(2006.01)</b> | H01L 27/12 | B       |

| <b>H01L 27/12</b>  | <b>(2006.01)</b> | H01L 21/20 |         |

| <b>H01L 21/20</b>  | <b>(2006.01)</b> | H01L 29/78 | 6 1 3 Z |

| <b>H01L 29/786</b> | <b>(2006.01)</b> | H01L 29/78 | 6 2 7 D |

| <b>H01L 21/336</b> | <b>(2006.01)</b> | H01L 27/06 | 1 0 2 A |

請求項の数 20 (全 32 頁) 最終頁に続く

(21) 出願番号 特願2003-431911 (P2003-431911)

(22) 出願日 平成15年12月26日 (2003.12.26)

(65) 公開番号 特開2004-221570 (P2004-221570A)

(43) 公開日 平成16年8月5日 (2004.8.5)

審査請求日 平成18年12月25日 (2006.12.25)

(31) 優先権主張番号 特願2002-380726 (P2002-380726)

(32) 優先日 平成14年12月27日 (2002.12.27)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 山崎 舜平

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 高山 徹

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 丸山 純矢

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 大野 由美子

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

最終頁に続く

(54) 【発明の名称】半導体装置の作製方法

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の基板上に、タングステン膜を形成し、

前記タングステン膜上に酸化物膜を形成することにより、前記タングステン膜と前記酸化物膜との間に酸化タングステン膜を形成し、

前記酸化物膜上に絶縁膜を形成し、

前記絶縁膜上に水素含有膜を形成し、

前記水素含有膜上にインダクタ、コンデンサ、抵抗素子、S A W素子、または薄膜トランジスタを有する素子と、前記素子に電気的に接続する引出電極と、を含む被剥離層を形成し、

前記被剥離層上に樹脂層を形成し、

前記樹脂層に第1の接着層を介して第2の基板を貼り合わせて、前記被剥離層および前記樹脂層を前記第1の基板と前記第2の基板とで挟み、

前記第1の基板と前記被剥離層とを、前記酸化タングステン膜中、前記酸化タングステン膜と前記酸化物膜との界面、又は前記酸化タングステン膜と前記タングステン膜との界面で分離し、

前記被剥離層に第2の接着層を介して端子を有する第3の基板を貼り合わせて、前記被剥離層を前記第2の基板と前記第3の基板とで挟み、

前記被剥離層から前記第2の基板と前記第1の接着層を分離し、

前記樹脂層を除去して前記引出電極を露出させ、

10

20

前記第3の基板に設けられている前記端子と、前記引出電極とを電気的に接続することを特徴とする半導体装置の作製方法。

【請求項2】

請求項1において、

前記引出電極と前記端子とを接続する方法は、はんだ付け法、導電性微粒子を含む接着材による方法、熱圧着法、ワイヤボンディング法又はフリップチップ法であることを特徴とする半導体装置の作製方法。

【請求項3】

第1の基板上に、タングステン膜を形成し、

前記タングステン膜上に酸化物膜を形成することにより、前記タングステン膜と前記酸化物膜との間に酸化タングステン膜を形成し、10

前記酸化物膜上に絶縁膜を形成し、

前記絶縁膜上に水素含有膜を形成し、

前記水素含有膜上に埋め込み配線を含む被剥離層を形成する第1工程と、

第2の基板上にインダクタ、コンデンサ、抵抗素子、S A W素子、または薄膜トランジスタを有する素子と、前記素子に電気的に接続する引出電極とを形成する第2工程と、を有し、

前記被剥離層に接着層を介して前記第2の基板を貼り合わせて、前記被剥離層と、前記素子及び前記引き出し電極とを、前記第1の基板と前記第2の基板とで挟み、

前記第1の基板と前記被剥離層とを、前記酸化タングステン膜中、前記酸化タングステン膜と前記酸化物膜との界面、又は前記酸化タングステン膜と前記タングステン膜との界面で分離することを特徴とする半導体装置の作製方法。20

【請求項4】

請求項3において、

前記水素含有膜上に導電性を有するエッチングストッパー層を形成し、

前記エッチングストッパー層を覆う第1の絶縁膜を形成し、

前記第1の絶縁膜に選択的にエッチングを行い、前記エッチングストッパー層に達する開口を形成し、

前記開口を覆うように第1のバリア層を形成し、

前記第1のバリア層上に金属膜を形成し、30

前記開口に前記第1のバリア層及び前記金属膜が残るように平坦化処理を行うことにより前記埋め込み配線を形成し、

前記埋め込み配線上に第2のバリア層を形成することを特徴とする半導体装置の作製方法。

【請求項5】

請求項4において、

前記金属膜は、銅、銀、金、クロム、鉄、ニッケル、白金またはこれらの合金であることを特徴とする半導体装置の作製方法。

【請求項6】

請求項4又は5において、40

前記第1のバリア層は、 $WN_x$ 、 $TaN_x$ 、 $TiSi_y$ 、 $WSi_xN_y$ 又は $TaSi_xN_y$ であることを特徴とする半導体装置の作製方法。

【請求項7】

請求項4乃至6のいずれか一において、

前記エッチングストッパー層は、Ni、Ti、W、 $WSi_x$ 、Al、Mo、Ta、Cr又はMoから選ばれた元素であることを特徴とする半導体装置の作製方法。

【請求項8】

請求項4乃至6のいずれか一において、

前記エッチングストッパー層は、Ni、Ti、W、 $WSi_x$ 、Al、Mo、Ta、Cr又はMoから選ばれた元素を主成分とする合金であることを特徴とする半導体装置の作製50

方法。

**【請求項 9】**

請求項 4 乃至 6 のいずれか一において、

前記エッチングストッパー層は、Ni、Ti、W、WSix、Al、Mo、Ta、Cr又はMoから選ばれた元素を主成分とする化合物であることを特徴とする半導体装置の作製方法。

**【請求項 10】**

請求項 3 乃至 9 のいずれか一において、

前記分離後に前記第 2 の基板上の端子と、前記引出電極とを電気的に接続することを特徴とする半導体装置の作製方法。

10

**【請求項 11】**

第 1 の基板上に、タングステン膜を形成し、

前記タングステン膜上に酸化物膜を形成することにより、前記タングステン膜と前記酸化物膜との間に酸化タングステン膜を形成し、

前記酸化物膜上に絶縁膜を形成し、

前記絶縁膜上に水素含有膜を形成し、

前記水素含有膜上にインダクタ又はコンデンサを含む被剥離層を形成し、

前記被剥離層上に接着層を介して端子を有する第 2 の基板を貼り合わせて、前記被剥離層を前記第 1 の基板と前記第 2 の基板とで挟み、

前記第 1 の基板と前記被剥離層とを、前記酸化タングステン膜中、前記酸化タングステン膜と前記酸化物膜との界面、又は前記酸化タングステン膜と前記タングステン膜との界面で分離し、

前記分離後に外部電極を形成して前記端子と前記インダクタ又は前記コンデンサとを電気的に接続することを特徴とする半導体装置の作製方法。

20

**【請求項 12】**

請求項 11 において、

前記コンデンサは、内部電極層と誘電体層とを交互に積層して形成されており、

前記内部電極層は、前記被剥離層の 2 表面に交互に露出するように積層されることを特徴とする半導体装置の作製方法。

30

**【請求項 13】**

請求項 11 において、

前記インダクタは、内部電極層と磁性体層とを交互に積層して形成されており、

前記内部電極層は、前記被剥離層の端面上に前記内部電極層の引出電極部が露出するよう

に積層されることを特徴とする半導体装置の作製方法。

**【請求項 14】**

請求項 1 乃至 13 のいずれか一において、

前記水素含有膜は、水素を含む窒化珪素膜、水素を含むアモルファスシリコン膜、または水素を含む DLC 膜であることを特徴とする半導体装置の作製方法。

**【請求項 15】**

請求項 1 乃至 14 のいずれか一において、

前記水素含有膜の成膜中または成膜後に 400 以上の熱処理を行うことを特徴とする

半導体装置の作製方法。

40

**【請求項 16】**

第 1 の基板上に、タングステン膜を形成し、

前記タングステン膜上に酸化物膜を形成することにより、前記タングステン膜と前記酸化物膜との間に酸化タングステン膜を形成し、

前記酸化物膜上に絶縁膜を形成し、

前記絶縁膜上に水素を含むアモルファスシリコン膜を形成し、

前記アモルファスシリコン膜を結晶化させて、ポリシリコン膜を形成し、

前記ポリシリコン膜を活性層とする薄膜トランジスタと、前記薄膜トランジスタ上の第

50

1の層間絶縁膜と、前記第1の層間絶縁膜上のコンデンサと、前記コンデンサ上の第2の層間絶縁膜と、前記第2の層間絶縁膜に形成されたコンタクトホールを介して前記薄膜トランジスタに電気的に接続する第1の引出電極と、前記第2の層間絶縁膜に形成されたコンタクトホールを介して前記コンデンサに電気的に接続する第2の引出電極及び第3の引出電極と、を含む被剥離層を形成し、

前記被剥離層上に樹脂層を形成し、

前記樹脂層に第1の接着層を介して第2の基板を貼り合わせて、前記被剥離層および前記樹脂層を前記第1の基板と前記第2の基板とで挟み、

前記第1の基板と前記被剥離層とを、前記酸化タンゲステン膜中、前記酸化タンゲステン膜と前記酸化物膜との界面、又は前記酸化タンゲステン膜と前記タンゲステン膜との界面で分離し、 10

前記被剥離層に第2の接着層を介して端子を有する第3の基板を貼り合わせて、前記被剥離層および前記樹脂層を前記第2の基板と前記第3の基板とで挟み、

前記被剥離層から前記第2の基板と前記第1の接着層を分離し、

前記樹脂層を除去して前記第1乃至第3の引出電極を露出させ、

前記第3の基板に設けられている前記端子と、前記第1の引出電極とを電気的に接続することを特徴とする半導体装置の作製方法。

#### 【請求項17】

第1の基板上に、タンゲステン膜を形成し、

前記タンゲステン膜上に酸化物膜を形成することにより、前記タンゲステン膜と前記酸化物膜との間に酸化タンゲステン膜を形成し、 20

前記酸化物膜上に絶縁膜を形成し、

前記絶縁膜上にCMOS回路と、前記CMOS回路に電気的に接続する引出電極と、を含む被剥離層を形成し、

前記被剥離層上に導電性粒子を含む第1の接着層を介して端子を有する第2の基板を貼り合わせて、前記導電性粒子を介して前記引出電極と前記端子とを電気的に接続させ、

前記第1の基板と前記被剥離層とを、前記酸化タンゲステン膜中、前記酸化タンゲステン膜と前記酸化物膜との界面、又は前記酸化タンゲステン膜と前記タンゲステン膜との界面で分離し、

前記分離後に表面に残っている酸化タンゲステンを除去し、 30

前記分離した側の前記被剥離層に第2の接着層を介して放熱板を貼り付けることを特徴とする半導体装置の作製方法。

#### 【請求項18】

第1の基板上に、タンゲステン膜を形成し、

前記タンゲステン膜上に酸化物膜を形成することにより、前記タンゲステン膜と前記酸化物膜との間に酸化タンゲステン膜を形成し、

前記酸化物膜上に絶縁膜を形成し、

前記絶縁膜上に表面波伝搬膜として水素を含むDLC膜と、前記DLC膜上の櫛型電極と、前記櫛型電極上の圧電体膜と、を含む被剥離層を形成し、

前記被剥離層上に樹脂層を形成し、 40

前記樹脂層に第1の接着層を介して第2の基板を貼り合わせて、前記被剥離層および前記樹脂層を前記第1の基板と前記第2の基板とで挟み、

前記第1の基板と前記被剥離層とを、前記酸化タンゲステン膜中、前記酸化タンゲステン膜と前記酸化物膜との界面、又は前記酸化タンゲステン膜と前記タンゲステン膜との界面で分離し、

前記被剥離層に第2の接着層を介して第3の基板を貼り合わせて、前記被剥離層および前記樹脂層を前記第2の基板と前記第3の基板とで挟み、

前記被剥離層から前記第2の基板と前記第1の接着層とを分離し、

前記樹脂層を除去することを特徴とする半導体装置の作製方法。

#### 【請求項19】

第1の基板上に、タングステン膜を形成し、

前記タングステン膜上に酸化物膜を形成することにより、前記タングステン膜と前記酸化物膜との間に酸化タングステン膜を形成し、

前記酸化物膜上に絶縁膜を形成し、

前記絶縁膜上に半導体抵抗素子又は薄膜抵抗素子と、前記半導体抵抗素子又は前記薄膜抵抗素子に電気的に接続する引出電極と、を含む被剥離層を形成し、

前記被剥離層上に導電性粒子を含む第1の接着層を介して端子を有する第2の基板を貼り合わせて、前記導電性粒子を介して前記引出電極と前記端子とを電気的に接続させ、

前記第1の基板と前記被剥離層とを、前記酸化タングステン膜中、前記酸化タングステン膜と前記酸化物膜との界面、又は前記酸化タングステン膜と前記タングステン膜との界面で分離し、

前記分離後に表面に残っている酸化タングステンを除去し、

前記分離した側の前記被剥離層に第2の接着層を介して放熱板を貼り付けることを特徴とする半導体装置の作製方法。

#### 【請求項20】

請求項1乃至19のいずれか一において、

前記第1の基板と前記被剥離層との分離の前に400以上 の熱処理を行い、前記酸化タングステン膜を結晶化させることを特徴とする半導体装置の作製方法。

#### 【発明の詳細な説明】

##### 【技術分野】

20

##### 【0001】

本発明は、TFT、抵抗素子、所定の周波数帯域を減衰させるLC素子、およびこれらの素子を組み合わせた集積回路を搭載した半導体装置およびその作製方法に関する。

##### 【0002】

なお、本明細書中において半導体装置とは、半導体特性を利用して機能しうる装置全般を指し、電気光学装置、半導体回路および電子機器は全て半導体装置である。

##### 【背景技術】

##### 【0003】

トランジスタなどの能動素子と、容量や抵抗、インダクタなどの受動素子が、同一の半導体基板上に形成された高周波集積回路(MMICとも呼ばれる)が知られている。MMICでは半導体基板上にMESFET、HEMT、HBTなどの能動素子とキャパシタ、インダクタ、抵抗などの集中定数素子、マイクロストリップ線路、コプレーナ線路などの分布定数素子が一体に形成される。なお、接地はバイアホールを用いている。能動素子と受動素子が個別に実装されているものと比較して、小型、軽量であり、高周波特性も良好である。ただし、半導体プロセスは一般にコストが高いため、受動素子に大きな面積が必要となる場合は、コスト的に不利になる。

30

##### 【0004】

一般に高周波集積回路(MMIC)は、単結晶シリコンウェハーを用いてトランジスタや化合物半導体を利用したトランジスタと、チップ型のインダクタやコンデンサ、さらにSAW素子のようなフィルター素子とを集積化して構成されている。

40

##### 【0005】

MMICの開発により、アナログおよびデジタル携帯電話、PHS端末等で代表される移動体通信機器の集積化、多機能化が図られている。

##### 【0006】

また、能動素子、受動素子をそれぞれ個別に作製し、それらを同一の半絶縁性基板上に実装した回路はHMIC、もしくはHICと呼ばれ、また、単にMICと呼ぶこともある。HMICでは回路基板にアルミナおよびチタン酸バリウム系基板、能動素子にGaAs PHEMT、集中定数素子に板極形チップキャパシタ、ボンディングワイヤを用いたインダクタ、TaN薄膜抵抗、分布定数素子にマイクロストリップ線路が用いられている。なお、接地はスルーホールを用いている。

50

**【0007】**

また、特許文献1には、複合集積回路部品において、薄膜集積回路に薄膜プロセスで10層以内の薄膜積層体を形成することが記載されている。また、特許文献2には、TFTで形成される回路と高周波フィルターとを複合化し、高周波モジュールを形成することが記載されている。

**【0008】**

【特許文献1】特開平7-45787号公報

**【0009】**

【特許文献2】特開平10-209464号公報

**【発明の開示】**

10

**【発明が解決しようとする課題】****【0010】**

更なる小型軽量化、薄型化、低コスト化が要求されており、本発明は、さまざまな複合回路を集積化できる新規な構成を提供する。

**【課題を解決するための手段】****【0011】**

本発明は、従来、チップ部品(L、C、R)として搭載していた回路(または素子)を半導体基板を用いずに絶縁性基板上に形成して剥離技術により絶縁性基板から剥離し、回路基板やフィルムに貼りつけることを特徴とする。

**【0012】**

20

具体的に本発明は、基板上に内部電極層用のペーストと、誘電体層用のペーストとをシート法や印刷法により積層し、積層型コンデンサや積層型インダクタ(積層コイル)や抵抗回路などを形成し焼成した後、基板から剥離して回路基板やフィルムに転写することを特徴とする。

**【0013】**

また、本発明は、基板上にコンデンサ、インダクタ、および共振器(分布定数)を組み合わせた受動回路素子(LPF、BPF(代表的にはSAWフィルタ)、ダイプレクサ、カプラ、バランなど)を形成した後、基板から剥離して回路基板やフィルムに転写することを特徴とする。

**【0014】**

30

また、本発明は、高誘電体薄膜を容量絶縁膜として用いた容量素子をTFTからなるCMOS回路と同一基板上に形成した後、基板から剥離して回路基板やフィルムに転写することを特徴とする。

**【0015】**

また、本発明は、高周波領域においてマイクロストリップ線路やコプレナ線路のような分布定数線路からなるインピーダンス整合回路を基板上に形成した後、基板から剥離して回路基板やフィルムに転写することを特徴とする。

**【0016】**

また、本発明は、基板上に絶縁層を形成し、該絶縁層に埋め込み配線(Cu、Au、Ag、Ni、クロム、パラジウム、ロジウム、錫、鉛またはこれらの合金などを形成した後、基板から剥離して回路基板やフィルムに転写することによって各種配線として使用する。この場合、低抵抗な埋め込み配線のみを転写するのではなく、その周りの絶縁膜もシート状に転写する。また、金属保護膜(Ti、TiN、Ta、TaNなど)で囲まれた埋め込み配線を形成した後、基板から剥離して回路基板やフィルムに転写を行ってよい。

40

**【0017】**

また、本発明は、上記様々な回路、素子、配線のうち複数を同一基板上に形成した後、基板から剥離して回路基板やフィルムに転写することを特徴としている。様々な回路、素子、配線を同一基板上に作りこむことが可能な本発明によって、ノイズが低減できる。本発明によりRF回路、CPU、メモリ(SRAM、DRAM、フラッシュメモリ)などを同一基板上に作り込み、それらを転写することができる。本発明によりさらなる軽量化、集

50

積化、または低コスト化を実現する。

**【0018】**

本明細書で開示する発明の構成は、図2(C)にその一例を示したように、絶縁表面上にインダクタが形成された基板と、該インダクタに接続された薄膜トランジスタを有する層とが積層された複合集積回路を有する半導体装置である。

**【0019】**

また、他の発明の構成は、図2(D)にその一例を示したように、絶縁表面上にコンデンサが形成された基板と、該コンデンサに接続された薄膜トランジスタを有する層とが積層された複合集積回路を有する半導体装置である。

**【0020】**

また、他の発明の構成は、図1または図3にその一例を示したように、絶縁表面上にインダクタとコンデンサが形成された基板と、前記インダクタまたは前記コンデンサに接続された薄膜トランジスタが積層された複合集積回路を有する半導体装置である。

**【0021】**

また、他の発明の構成は、絶縁表面上にインダクタとコンデンサと抵抗素子が形成された基板と、前記インダクタ、前記コンデンサ、または前記抵抗素子に接続された薄膜トランジスタが積層された複合集積回路を有する半導体装置である。

**【0022】**

また、上記各構成においては、前記インダクタは積層型インダクタ、或いはスパイラル形状の伝送線路からなることを特徴としている。また、上記各構成においては、コンデンサは積層型コンデンサ、或いはMIM型コンデンサであることを特徴としている。

**【0023】**

また、他の発明の構成は、図5にその一例を示したように、絶縁表面上にSAW素子が形成された基板と、該SAW素子に接続された薄膜トランジスタとが積層された複合集積回路を有する半導体装置である。

**【0024】**

また、上記構成においては、ダイヤモンド薄膜を用いてSAW素子を構成していることを特徴としている。

**【0025】**

また、上記各構成においては、前記基板は、セラミック基板、石英基板、ガラス基板、またはプラスチック基板であることを特徴としており、実装する基板に合わせて適宜選択することができ、信頼性を向上させることができる。

**【0026】**

また、上記各構成において、絶縁表面を有する基板上には、CPU、メモリ素子、薄膜ダイオード、光電変換素子、または抵抗素子が設けられていることを特徴としている。

**【0027】**

また、上記各構成において、前記半導体装置は、ビデオカメラ、デジタルカメラ、ゴーグル型ディスプレイ、カーナビゲーションで代表されるナビゲーション装置、DVDプレーヤー、電子遊戯機器、カード(IDカードや機能回路または素子を有するカードやカードキーなど)、コンピュータ、データを記録できるメモリ、または携帯情報端末であることを特徴としている。

**【0028】**

また、剥離および転写方法としては、まず、基板上に金属膜(タンゲステン膜、窒化タンゲステン、タンゲステン合金など)を形成した後、スパッタ法で酸化シリコン膜を形成する。この段階でアモルファス状態の酸化タンゲステン膜が境界付近に形成される。そして酸化シリコン膜上に下地膜を形成した後、各種回路、素子、配線を形成する。これらの各種回路、素子、配線を形成する際に、水素を含む膜(アモルファシリコン膜、窒化珪素膜、DLC膜など)を形成し、400以上の熱処理を有するプロセスを行うことによ

10

20

30

40

50

つて、後の剥離工程において、結晶化した酸化タンゲステン膜の層内或いは界面で剥離を生じさせることができる。TFTを形成する場合には、水素を含むアモルファスシリコン膜を用いて活性層を形成すればよい。

#### 【0029】

また、配線などの場合、配線を覆って水素を含む窒化珪素膜を形成した後、400以上の熱処理を行うことによって剥離を生じさせることができる。或いは、配線を覆って水素を含むアモルファスシリコン膜を形成し、400以上の熱処理を行った後、シリコン膜をエッティングして除去してもよい。

#### 【0030】

なお、上記剥離方法は、基板が透光性を有している必要はなく、少なくとも400以上の熱処理に耐えうる基板であれば特に限定されない。 10

#### 【0031】

また、上記構造を実現するための発明の構成は、

第1の基板上にインダクタ、コンデンサ、抵抗素子、SAW素子、またはTFTを含む被剥離層を形成する第1工程と、

前記被剥離層上に溶媒に溶ける有機樹脂膜を塗布する第2工程と、

前記有機樹脂膜に第2の基板を第1の両面テープで接着させ、前記被剥離層および有機樹脂膜を前記第1の基板と前記第2の基板とで挟む第3工程と、

前記第1の基板と、前記被剥離層とを物理的手段で分離する第4工程と、

前記被剥離層に第3の基板を接着材で接着させ、前記被剥離層を前記第2の基板と前記第3の基板とで挟む第5工程と、 20

前記被剥離層および第1の両面テープと前記第2の基板とを分離する第6工程と、

前記被剥離層と前記第1の両面テープとを分離する第7工程と、

前記有機樹脂膜を溶媒で除去する第8工程と、

前記第3の基板に設けられている電極と、前記被剥離層に設けられている電極とを接続する第10工程と、を有することを特徴とする半導体装置の作製方法である。

#### 【0032】

また、上記構成において、前記第3の基板に設けられている電極と前記被剥離層に設けられている電極とを接続する方法は、はんだ付け法、導電性微粒子を含む接着材による方法、熱圧着法、ワイヤボンディング法、フリップチップ法であることを特徴としている。 30

#### 【0033】

また、作製方法に関する他の発明の構成は、

第1の基板上に埋め込み配線を含む被剥離層を形成する第1工程と、

第2の基板上にインダクタ、コンデンサ、抵抗素子、SAW素子、またはTFTと、これらの素子に接続する引出電極とを形成する第2工程と、

前記被剥離層に前記第2の基板を接着材で接着させ、前記被剥離層を前記第1の基板と前記第2の基板とで挟む第3工程と、

前記第1の基板と、前記被剥離層とを物理的手段で分離する第4工程と、を有することを特徴とする半導体装置の作製方法。

#### 【0034】

上記構成において、前記埋め込み配線は、

絶縁表面上に導電性を有するエッティングストッパー層を形成する第1の工程と、

前記エッティングストッパー層を覆う第1の絶縁膜を形成する第2の工程と、

前記第1の絶縁膜にエッティングを行い、前記エッティングストッパー層に達する開口を形成する第3の工程と、

シードを形成してメッキを行い、前記開口を覆う埋め込み配線を形成する第4の工程と、平坦化処理を行う第5の工程と、により形成されることを特徴としている。 40

#### 【0035】

なお、前記埋め込み配線の形成工程において平坦化処理(CMPなど)を行っても剥離は生じないが、平坦化処理後に400以上の熱処理を行うことで被剥離層を剥離しやす 50

くしてもよい。

**【0036】**

また、上記構成において、前記埋め込み配線は、銅、銀、金、またはこれらの合金であることを特徴としている。

**【0037】**

本発明によれば、携帯端末に様々な機能を付与することができる。例えば、本発明により基板上にCPU回路とGPS機能を有する回路とを含む被剥離層を形成し、基板から被剥離層を剥離し、回路基板に転写および実装することができる。或いは、基板上にGPS機能を有する回路を含む被剥離層を形成し、基板から被剥離層を剥離し、CPU回路が設けられた基板に転写して積層し、集積化することができる。なお、GPS (Global Positioning System) は、GPS用の衛星から送られる信号をとらえてその時間差を求め、これをもとに測位するシステムである。

10

**【0038】**

また、本発明は、高周波回路に使用される多層積層部品、例えばカプラ、ミキサ、分配器、VCO (電圧制御発振器)、チップアンテナ等に応用可能である。

**【発明の効果】**

**【0039】**

本発明により、更なる軽量化、薄型化、低コスト化、実装面積削減が実現でき、さまざまな複合回路を集積化できる。

**【発明を実施するための最良の形態】**

**【0040】**

本発明の実施形態について、以下に説明する。

**【0041】**

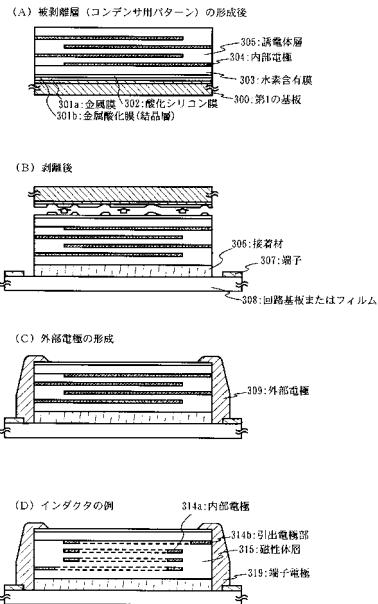

(実施の形態1)

ここでは半導体基板を用いることなく、積層型コンデンサや積層型インダクタを形成し、回路基板(プリント基板)に転写、および実装する例を示す。

**【0042】**

まず、耐熱性ガラス基板(例えば石英基板)またはセラミックス基板を用意する。

**【0043】**

基板(第1の基板300)上に積層型コンデンサを形成する例を図2(A)~図2(C)を用いて説明する。本実施例では高温の焼成を行うためセラミック基板を用いる。このセラミック基板上にスパッタ法で金属膜301a、ここではタンゲステン膜(膜厚10nm~200nm、好ましくは50nm~75nm)を形成し、さらに大気にふれることなく、酸化物膜302、ここでは酸化シリコン膜(膜厚150nm~200nm)を積層形成する。酸化物膜302の膜厚は、金属膜の膜厚の2倍以上とすることが望ましい。なお、積層形成の際、金属膜301aと酸化シリコン膜302との間にアモルファス状態の酸化金属膜(酸化タンゲステン膜)が2nm~5nm程度形成される。後の工程で剥離する際、酸化タンゲステン膜中、または酸化タンゲステン膜と酸化シリコン膜との界面、または酸化タンゲステン膜とタンゲステン膜との界面で分離が生じる。

30

**【0044】**

なお、スパッタ法では基板端面に成膜されるため、基板端面に成膜されたタンゲステン膜と酸化タンゲステン膜と酸化シリコン膜とをO<sub>2</sub>アッシングなどで選択的に除去することが好ましい。

**【0045】**

次いで、PCVD法で下地絶縁膜となる酸化窒化シリコン膜(膜厚100nm)(図示しない)を形成し、さらに大気にふれることなく、水素含有膜303として水素を含む窒化珪素膜(膜厚100nm)を積層形成する。

**【0046】**

次いで、内部電極層用のペーストと誘電体層用のペーストとをシート法や印刷法などにより積層した後、焼成する。ここでは、印刷法を用い、基板上に内部電極層用のペースト

50

と誘電体層用のペーストとを積層印刷し、所定形状に切断した後、基板から剥離してグリーンチップとする例を示す。

#### 【0047】

誘電体層305の材料としては高周波特性の良好なアルミナ系のセラミック、BaTiO<sub>3</sub>系のセラミックなどをペースト状にしたもの用いる。内部電極304の材料としては銅、銀、ニッケル、錫、亜鉛、Pd、アルミニウムなどを用い、端面がコンデンサチップ体の対向する2表面に交互に露出するように積層される。(図2(A))なお、焼成温度としては850～1400とする。また、焼成した際に結晶構造を有する酸化金属膜301bが得られる。

#### 【0048】

次いで、回路基板またはフィルム308に接着材306で接着する。なお、回路基板またはフィルムには端子307や配線(図示しない)が形成されており、さまざまな回路やチップを実装できるようになっている。

#### 【0049】

次いで、第1の基板300を引き剥がす。酸化タンゲステン膜中、または酸化タンゲステン膜と酸化シリコン膜との界面、または酸化タンゲステン膜とタンゲステン膜との界面で分離が生じる。(図2(B))

#### 【0050】

次いで、表面に残っている酸化タンゲステンを除去した後、外部電極309を形成する。外部電極309は、導電ペーストの焼き付きおよびメッキにより形成する。なお、表面に残っている酸化タンゲステンは除去しなくてもよく、特に限定されない。外部電極用のペーストをコンデンサチップ体の対向する2表面に形成し、コンデンサ回路を構成する。(図2(C))ここでは外部電極309の形成と同時に端子の接続を行っているが、外部電極309を形成した後、接続用の電極や半田によって端子との接続を行ってもよい。

#### 【0051】

なお、コンデンサは、各回路ブロックにおける電源電圧安定化やEMC対策のために電源ラインとグラウンド間に使用される、いわゆるデカップリング用途の需要が大きい素子である。

#### 【0052】

また、インダクタも同様にして形成することができる。

#### 【0053】

上記コンデンサの形成方法に従って、セラミック基板上にスパッタ法でタンゲステン膜、酸化シリコン膜を積層形成し、該酸化シリコン膜形成の際、酸化タンゲステン膜を形成する。PCVD法で下地絶縁膜となる酸化窒化シリコン膜(膜厚100nm)(図示しない)を形成し、さらに大気にふれることなく、水素含有膜として水素を含む窒化珪素膜(膜厚100nm)を積層形成する。

#### 【0054】

そして、次いで、内部電極層用のペーストと磁性体層用のペーストとをシート法や印刷法などにより積層した後、焼成する。

#### 【0055】

磁性体層315の材料としては、Ni-Cu-Zn系フェライト、Mn-Mg-Zn系フェライトなどをメチルセルロース、ブチラール樹脂などのバインダーで混練してペースト状にしたもの用いる。内部電極314aの材料としては銅、銀、ニッケル、錫、亜鉛、Pd、アルミニウムなどを用い、コイル状に積層させる。なお、コイル状とした内部電極の引出電極部314bが端面に露出するように積層させる。

#### 【0056】

次いで、回路基板またはフィルムに接着材で接着する。

#### 【0057】

次いで、第1の基板を引き剥がす。酸化タンゲステン膜中、または酸化タンゲステン膜と酸化シリコン膜との界面、または酸化タンゲステン膜とタンゲステン膜との界面で分離

10

20

30

40

50

が生じる。

**【0058】**

次いで、表面に残っている酸化タンゲステンを除去した後、端子電極319を形成する。端子電極319は、導電ペーストの焼き付きおよびメッキにより形成する。端子電極用のペーストをインダクタチップ体の対向する2表面に形成し、インダクタ回路を構成する。(図2(D))

**【0059】**

また、上記コンデンサと上記インダクタとを積層させて一体形成したLCフィルタを形成することもできる。上記作製方法に従って、コンデンサ部分を形成するための積層を行った後、インダクタ部分を形成するための積層を行えば複合積層体を形成することができる。

**【0060】**

本発明により、LCフィルタとして代表的なLPF(Low Pass Filter)を形成することも可能である。LPFは携帯電話などのモジュールに含まれる高周波回路で、パワー・アンプやアンテナスイッチやVCOの高長波取りの用途に使用される。LPFはL(インダクタ)2個、C(コンデンサ)5個により構成され、2個のLC並列共振回路で減衰帯域に適当なゼロ点を設け、通過周波数の2倍波、3倍波をバランスよく除去させるとともに、入出力に配されているC(コンデンサ)にてインピーダンスを50Ωに合わせることで、LPFとして通過帯域の挿入損失が最少になるよう最適化されている。

**【0061】**

またLPFの他にも、コンデンサやインダクタを組み合わせることで各種LCフィルタ、例えばBPF、ダイブレクサ、カプラ(方向性結合器)、バランなども作製することができる。

**【0062】**

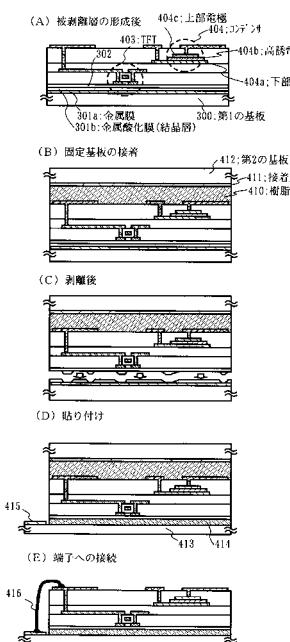

(実施の形態2)

ここでは、容量素子とTFTとを形成し、回路基板(プリント基板)に転写、および実装する例を示す。

**【0063】**

なお、途中の工程までは実施の形態1と同一であるため、同じ箇所には同じ符号を用いる。

**【0064】**

第1の基板300上にスパッタ法でタンゲステン膜301a、酸化シリコン膜302を積層形成し、該酸化シリコン膜形成の際、アモルファス状態の酸化タンゲステン膜を形成する。PCVD法で下地絶縁膜となる酸化窒化シリコン膜(膜厚100nm)(図示しない)を形成し、さらに大気にふれることなく、水素含有膜として水素を含むアモルファスシリコン膜(膜厚55nm)を積層形成する。なお、ここでは第1の基板300として石英基板を用いる。

**【0065】**

また、FT-IRを用いて上記水素を含むアモルファスシリコン膜の水素濃度を測定したところ、Si-Hは、 $1.06 \times 10^{22}$ (atoms/cm<sup>3</sup>)、Si-H<sub>2</sub>は $8.34 \times 10^{19}$ (atoms/cm<sup>3</sup>)であり、組成比における水素濃度を算出すると21.5%であった。また、PCVD法の成膜条件を変えて同様に水素濃度を算出したところ、組成比における水素濃度は16.4%、17.1%、19.0%が得られた。

**【0066】**

次いで、上記アモルファスシリコン膜を公知の技術(固相成長法、レーザー結晶化方法、触媒金属を用いた結晶化方法など)により結晶化させて、ポリシリコン膜を活性層とするTFTを用いる素子を形成する。ここでは、触媒金属を用いた結晶化方法を用いてポリシリコン膜を得る。重量換算で10ppmのニッケルを含む酢酸ニッケル塩溶液をスピナーで塗布する。なお、塗布に代えてスパッタ法でニッケル元素を全面に散布する方法を用いてよい。次いで、加熱処理を行い結晶化させて結晶構造を有する半導体膜(ここではボ

10

20

30

40

50

リシリコン層)を形成する。ここでは熱処理(500、1時間)の後、結晶化のための熱処理(550、4時間)を行って結晶構造を有するシリコン膜を得る。

#### 【0067】

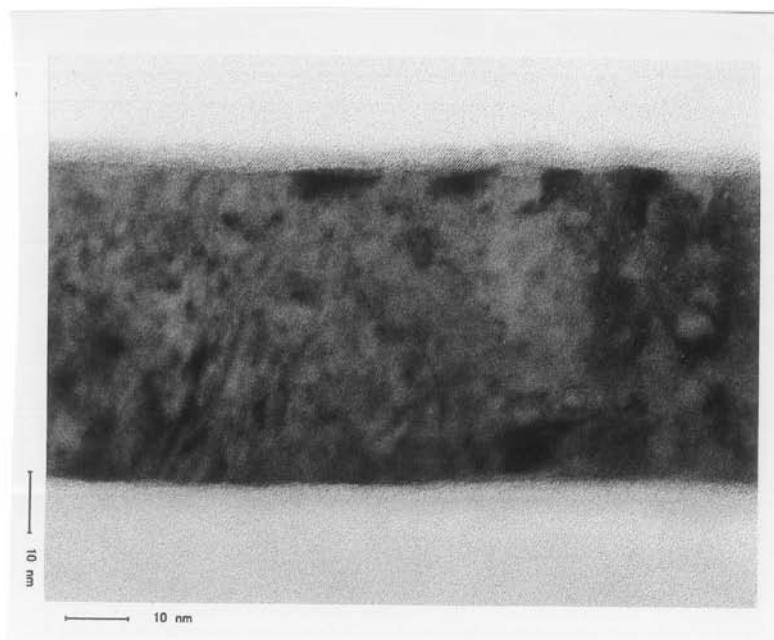

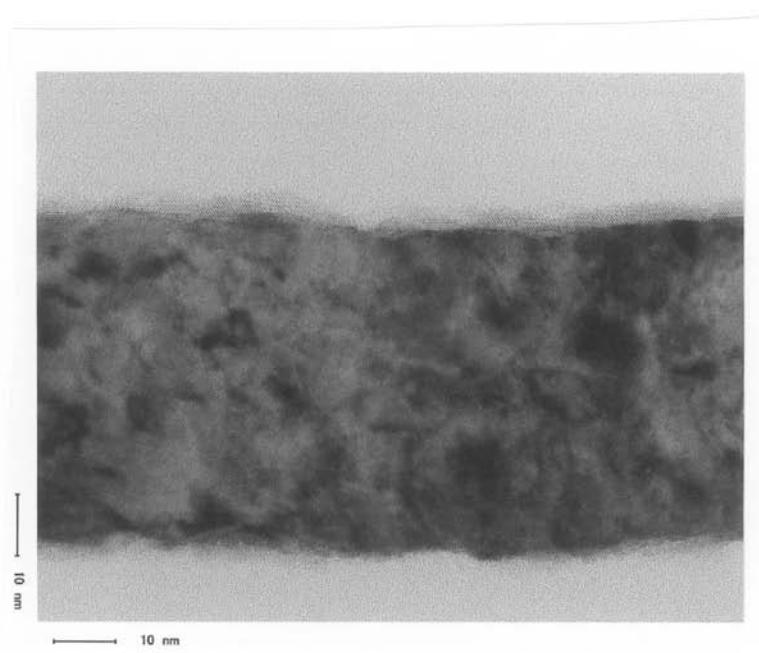

アモルファスシリコン膜は水素を含んでおり、加熱してポリシリコン膜を形成する場合、結晶化させるため410以上の中間温度の熱処理を行えば、ポリシリコン膜を形成すると同時に水素の拡散を行うことができる。また、400以上の熱処理を行うことで、アモルファス状態の酸化金属膜が結晶化し、結晶構造を有する酸化金属膜301bが得られる。図11に断面TEM写真を示す。従って、410以上の加熱処理を行うことによって結晶構造を有する酸化金属膜が形成され、水素の拡散が行われる。この410以上の熱処理が終了した段階で、比較的小さな力(例えば、人間の手、ノズルから吹付けられるガスの風圧、超音波等)を加えることによって、酸化タンゲステン膜中、または酸化タンゲステン膜と酸化シリコン膜との界面、または酸化タンゲステン膜とタンゲステン膜との界面で分離を生じさせることができる。なお、結晶構造を有する酸化金属膜が得られる温度の熱処理を行うと酸化金属膜の膜厚は若干薄くなる。10

#### 【0068】

また、得られたポリシリコン膜を用いて、TFTを代表とする様々な素子(薄膜ダイオード、シリコンのPIN接合からなる光電変換素子やシリコン抵抗素子やセンサ素子(代表的にはポリシリコンを用いた感圧式指紋センサー)をも形成することができる。

#### 【0069】

次いで、結晶構造を有するシリコン膜表面の酸化膜を希フッ酸等で除去した後、結晶化率を高め、結晶粒内に残される欠陥を補修するためのレーザー光(XeCl:波長308nm)の照射を大気中、または酸素雰囲気中で行う。レーザー光には波長400nm以下のエキシマレーザ光や、YAGレーザの第2高調波、第3高調波を用いる。ここでは、繰り返し周波数10~1000Hz程度のパルスレーザー光を用い、当該レーザー光を光学系にて100~500mJ/cm<sup>2</sup>に集光し、90~95%のオーバーラップ率をもって照射し、シリコン膜表面を走査させればよい。ここでは、繰り返し周波数30Hz、エネルギー密度470mJ/cm<sup>2</sup>でレーザー光の照射を大気中で行なった。なお、大気中、または酸素雰囲気中で行うため、レーザー光の照射により表面に酸化膜が形成される。なお、ここではパルスレーザーを用いた例を示したが、連続発振のレーザーを用いてもよく、非晶質半導体膜の結晶化に際し、大粒径に結晶を得るために、連続発振が可能な固体レーザーを用い、基本波の第2高調波~第4高調波を適用するのが好ましい。代表的には、Nd:YVO<sub>4</sub>レーザー(基本波1064nm)の第2高調波(532nm)や第3高調波(355nm)を適用すればよい。連続発振のレーザーを用いる場合には、出力10Wの連続発振のYVO<sub>4</sub>レーザーから射出されたレーザー光を非線形光学素子により高調波に変換する。また、共振器の中にYVO<sub>4</sub>結晶と非線形光学素子を入れて、高調波を射出する方法もある。そして、好ましくは光学系により照射面にて矩形状または橍円形状のレーザー光に成形して、被処理体に照射する。このときのエネルギー密度は0.01~100MW/cm<sup>2</sup>程度(好ましくは0.1~10MW/cm<sup>2</sup>)が必要である。そして、10~2000cm/s程度の速度でレーザー光に対して相対的に半導体膜を移動させて照射すればよい。2030

#### 【0070】

次いで、上記レーザー光の照射により形成された酸化膜に加え、オゾン水で表面を120秒処理して合計1~5nmの酸化膜からなるバリア層を形成する。このバリア層は、結晶化するために添加したニッケルを膜中から除去するために形成する。ここではオゾン水を用いてバリア層を形成したが、酸素雰囲気下の紫外線の照射で結晶構造を有する半導体膜の表面を酸化する方法や酸素プラズマ処理により結晶構造を有する半導体膜の表面を酸化する方法やプラズマCVD法やスパッタ法や蒸着法などで1~10nm程度の酸化膜を堆積してバリア層を形成してもよい。また、バリア層を形成する前にレーザー光の照射により形成された酸化膜を除去してもよい。40

#### 【0071】

次いで、バリア層上にスパッタ法にてゲッタリングサイトとなるアルゴン元素を含む非50

晶質シリコン膜を10nm～400nm、ここでは膜厚100nmで成膜する。本実施例では、アルゴン元素を含む非晶質シリコン膜は、シリコンターゲットを用いてアルゴンを含む雰囲気下で形成する。プラズマCVD法を用いてアルゴン元素を含む非晶質シリコン膜を形成する場合、成膜条件は、モノシランとアルゴンの流量比(SiH<sub>4</sub>:Ar)を1:99とし、成膜圧力を6.665Pa(0.05Torr)とし、RFパワー密度を0.087W/cm<sup>2</sup>とし、成膜温度を350°とする。

#### 【0072】

その後、650°に加熱された炉に入れて3分の熱処理を行いゲッタリングして、結晶構造を有する半導体膜中のニッケル濃度を低減する。炉に代えてランプアニール装置を用いてもよい。

10

#### 【0073】

次いで、バリア層をエッチングストッパーとして、ゲッタリングサイトであるアルゴン元素を含む非晶質シリコン膜を選択的に除去した後、バリア層を希フッ酸で選択的に除去する。なお、ゲッタリングの際、ニッケルは酸素濃度の高い領域に移動しやすい傾向があるため、酸化膜からなるバリア層をゲッタリング後に除去することが望ましい。

#### 【0074】

なお、触媒元素を用いて結晶化を行わない場合には、上述したバリア層の形成、ゲッタリングサイトの形成、ゲッタリングのための熱処理、ゲッタリングサイトの除去、バリア層の除去などの工程は不要である。

#### 【0075】

次いで、得られた結晶構造を有するシリコン膜(ポリシリコン膜とも呼ばれる)の表面にオゾン水で薄い酸化膜を形成した後、レジストからなるマスクを形成し、所望の形状にエッチング処理して島状に分離された半導体層を形成する。半導体層を形成した後、レジストからなるマスクを除去する。

20

#### 【0076】

次いで、フッ酸を含むエッチャントで酸化膜を除去すると同時にシリコン膜の表面を洗浄した後、ゲート絶縁膜となる珪素を主成分とする絶縁膜を形成する。本実施例では、プラズマCVD法により115nmの厚さで酸化窒化シリコン膜(組成比Si=32%、O=59%、N=7%、H=2%)で形成する。

#### 【0077】

次いで、ゲート絶縁膜上にゲート電極を形成し、活性層へのドーピングによるソース領域またはドレイン領域の形成、層間絶縁膜(無機絶縁膜)の形成、ソース電極またはドレイン電極の形成、活性化処理、水素化処理などを適宜行ってポリシリコン膜を活性層とするトップゲート型TFTを作製する。なお、ドーピングする不純物元素としてn型を付与するリンを添加した場合にはnチャネル型TFTを形成することができ、p型を付与するボロンを添加した場合にはpチャネル型TFTを形成することができ、これらを組み合わせればCMOS回路を作製することができる。

30

#### 【0078】

なお、ここではTFTの構造としてトップゲート型の例を示したが、特にTFTの構造は限定されず、例えばボトムゲート型や順スタガ型であってもよい。

40

#### 【0079】

次いでTFTを覆う層間絶縁膜を形成し、該層間絶縁膜上に下部電極404aと、高誘電体薄膜404bと、上部電極404cとからなるコンデンサ404を形成する。高誘電体薄膜(高誘電率を有する誘電体薄膜)404bとしては、BST(BaSrTiO<sub>3</sub>)、STO(SrTiO<sub>3</sub>)、或いはPZT(PbZrTiO<sub>3</sub>)を用いればよい。これらの高誘電体薄膜を得るためにには600～700°の熱処理を行う。なお、下部電極404aや上部電極404cは、高誘電体薄膜の材料に対して安定な金属材料を用いる。

#### 【0080】

次いで、コンデンサを覆う層間絶縁膜を形成し、該層間絶縁膜にコンタクトホールを形成し、引出電極を形成する。ここでは、TFTに接続する引出電極、コンデンサの下部電

50

極と接続する引出電極、上部電極と接続する引出電極などをそれぞれ形成する。（図3（A））

#### 【0081】

次いで、水またはアルコール類に可溶な接着材を全面に塗布、焼成する。この接着材の組成としては、例えば、エポキシ系、アクリレート系、シリコーン系等いかなるものでもよい。ここではスピンドルコートで水溶性樹脂（東亜合成製：VL-WSHL10）からなる樹脂層（膜厚30μm）410を塗布し、仮硬化するために2分間の露光を行ったあと、UV光を裏面から2.5分、表面から1.0分、合計12.5分の露光を行って本硬化させる。この水溶性樹脂膜は平坦化膜として機能し、後の基板貼り合わせの際、平坦化膜表面と基板面がほぼ平行になるように接着させることができる。この水溶性樹脂膜を用いない場合、圧着した時に電極やTFTによる凸凹が生じる恐れがある。10

#### 【0082】

次いで、接着層（両面テープ）411を用い、樹脂層410に第2の基板412を貼り付ける。（図3（B））なお、両面テープではなく、例えば紫外線照射によって剥離する接着材を用いてもよい。

#### 【0083】

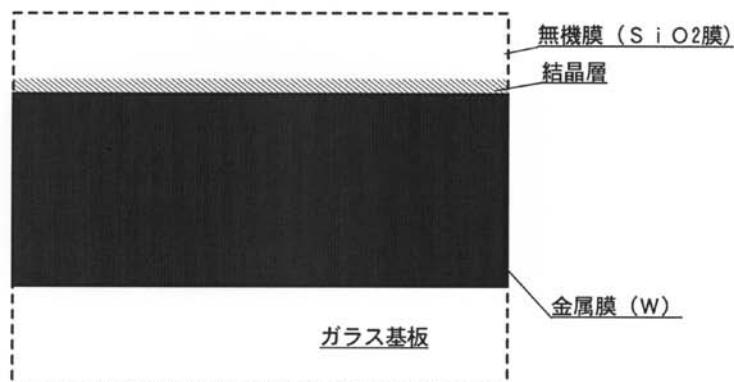

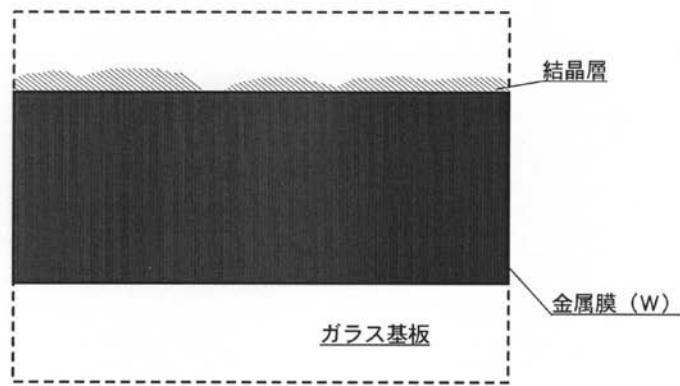

次いで、金属膜301aが設けられている第1の基板300を物理的手段により引き剥がす。比較的小さな力（例えば、人間の手、ノズルから吹付けられるガスの風圧、超音波等）で引き剥がすことができる。こうして、酸化シリコン層302上に形成された被剥離層を第1の基板300から分離することができる。剥離後の状態を図3（C）に示す。なお、剥離後の第1の基板300の断面TEM写真を図12に示す。なお、図12は、図11とは異なる箇所のTEM写真であり対応していない。図12に示すように部分的に酸化タンゲステン膜が薄い部分や、完全にない部分がある。被剥離層に酸化タンゲステン膜が部分的に残るが透明であるため、除去しなくてもよいし、除去してもよい。20

#### 【0084】

次いで、回路基板またはフィルム413に接着材414で接着する。（図3（D））なお、回路基板またはフィルムには端子415や配線（図示しない）が形成されており、さまざまな回路やチップを実装できるようになっている。

#### 【0085】

次いで、両面テープ411から第2の基板412を分離させ、両面テープ411を剥がす。そして、水を用いて水溶性樹脂からなる樹脂層410を溶かして除去する。30

#### 【0086】

次いで、引出電極と端子415とを接続するボンディングワイヤ416を形成する。また、引出電極と端子415とを半田付けや導電性接着材で接続してもよい。

#### 【0087】

本発明により容量素子とTFTとを含む被剥離層を回路基板に実装することができる。本発明を応用することによって半導体基板を用いることなく、不揮発性RAMや高集積DRAMを作製することができる。

#### 【0088】

また、nチャネル型TFTまたはpチャネル型TFTを適宜組み合わせた演算増幅器（オペアンプ）も作製できる。40

#### 【0089】

また、本実施の形態は実施の形態1と組み合わせることが可能であり、例えば、実施の形態1に示したインダクタを積層することも可能であり、様々な高周波回路を実現できる。

#### 【0090】

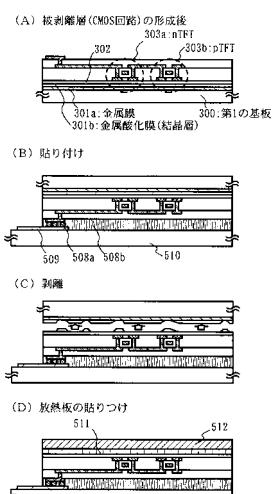

##### （実施の形態3）

ここでは実施の形態2に示した実装方法とは異なる例を図4に示す。

#### 【0091】

ここではpチャネル型TFT303aとnチャネル型TFT303bとを相補的に組み

50

合わせたC M O S回路を形成している。

【0092】

まず、実施の形態2に従って、第1基板上にpチャネル型T F T 3 0 3 aとnチャネル型T F T 3 0 3 bとを形成する。(図4(A))なお、C M O S回路を形成するプロセス温度は、600以下に抑えることが可能であるため、第1の基板3 0 0として本実施の形態ではガラス基板を用いることができる。

【0093】

図4(A)の状態が得られたら、導電性微粒子5 0 8 aを含む接着材5 0 8 bで端子5 0 9が設けられた回路基板5 1 0と第1の基板3 0 0とを貼り合わせる。(図4(B))貼り付けることによって端子5 0 9とT F Tに接続している引出電極とが導電性微粒子を介して電気的に接続される。

10

【0094】

次いで、第1の基板3 0 0を引き剥がす。酸化タンゲステン膜中、または酸化タンゲステン膜と酸化シリコン膜との界面、または酸化タンゲステン膜とタンゲステン膜との界面で分離が生じる。(図4(C))

【0095】

次いで、表面に残っている酸化タンゲステンを除去した後、接着材5 1 1で放熱板5 1 2を貼り付ける。(図4(D))特に、C M O S回路を用いてC P U回路などの高集積回路を形成した場合、発熱しやすいため、素子の発熱を放熱させる放熱板を貼り付けることが有用である。なお、発熱が問題にならない集積回路の場合には特に放熱板を貼り付ける必要はない。

20

【0096】

また、本実施の形態は実施の形態1や実施の形態2と自由に組み合わせることが可能であり、半導体基板を用いることなく、様々な複合集積回路を実現できる。

【0097】

(実施の形態4)

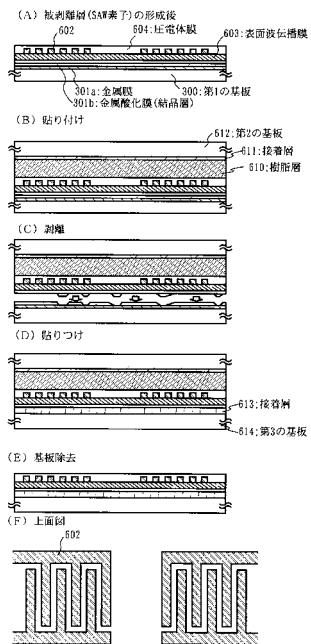

ここでは半導体基板を用いることなく、表面弹性波(S A W)素子を形成し、回路基板(プリント基板)に転写、および実装する例を図5に示す。S A W素子は表面波伝搬膜と圧電膜とが積層された構成となっており、圧電膜に櫛型電極により電界を印加して振動することにより、表面波伝搬膜に表面波を励振するものである。

30

【0098】

なお、途中の工程までは実施の形態1と同一であるため、同じ箇所には同じ符号を用いる。

【0099】

第1の基板3 0 0上にスパッタ法でタンゲステン膜3 0 1 a、酸化シリコン膜3 0 2を積層形成し、該酸化シリコン膜形成の際、アモルファス状態の酸化タンゲステン膜を形成する。P C V D法で下地絶縁膜となる酸化窒化シリコン膜(膜厚1 0 0 n m)(図示しない)を形成し、さらに大気にふれることなく、表面波伝搬膜6 0 3を積層形成する。なお、ここでは第1の基板3 0 0として石英基板を用い、表面波伝搬膜6 0 3として水素を含むD L C膜(膜厚1 0 ~ 5 0 μ m)を用いる。D L C膜の成膜方法は特に限定されず、C V D法、マイクロ波C V D法、P V D法、スパッタ法、イオンプレーティング法などを用いればよい。

40

【0100】

次いで、櫛型電極6 0 2を形成する。櫛型電極6 0 2としては導電性材料である限り特に限定されない。また、櫛型電極6 0 2の厚さは1 0 ~ 5 0 0 n m程度であることが好ましい。また、櫛型電極6 0 2の平面形状は、図5(F)に示すシングル電極であってもよいし、ダブル電極であってもよい。また、ここでは櫛型電極6 0 2を表面波伝搬膜6 0 3上に形成した例を示したが、表面波伝搬膜6 0 3に凹部を形成し、埋め込んでもよい。

【0101】

次いで、圧電体膜6 0 4を形成する。(図5(A))圧電体膜6 0 4としては、Z n O

50

、 AlN、水晶、LiNbO<sub>3</sub>、LiTaO<sub>3</sub>などを用いればよい。この圧電体膜604の厚さは材料の種類または目的とする表面弹性波素子の特性（中心周波数、比帯域幅、温度特性など）に応じて適宜選択することができる。圧電体膜604の成膜方法は特に限定されず、CVD法、マイクロ波CVD法、PVD法、スパッタ法、イオンプレーティング法などを用いればよい。

#### 【0102】

次いで、水またはアルコール類に可溶な接着材を全面に塗布、焼成する。この接着材の組成としては、例えば、エポキシ系、アクリレート系、シリコーン系等いかなるものでもよい。ここではスピンドルで水溶性樹脂（東亜合成製：VL-WSHL10）からなる樹脂層（膜厚30μm）610を塗布し、硬化させる。この水溶性樹脂膜は平坦化膜として機能し、後の基板貼り合わせの際、平坦化膜表面と基板面がほぼ平行になるように接着させることができる。この水溶性樹脂膜を用いない場合、圧着した時に電極やTFTによる凸凹が生じる恐れがある。10

#### 【0103】

次いで、接着層（両面テープ）611を用い、樹脂層610に第2の基板612を貼り付ける。（図5（B））なお、両面テープではなく、例えば紫外線照射によって剥離する接着材を用いてもよい。

#### 【0104】

次いで、金属膜301aが設けられている第1の基板300を物理的手段により引き剥がす。なお、DLC膜の成膜中または成膜後の処理で400以上に加熱することによって、比較的小さな力（例えば、人間の手、ノズルから吹付けられるガスの風圧、超音波等）で引き剥がすことができる。こうして、酸化シリコン層302上に形成された被剥離層を第1の基板300から分離することができる。剥離後の状態を図5（C）に示す。被剥離層に酸化タンゲステン膜が部分的に残るが透明であるため、除去しなくてもよいし、除去してもよい。20

#### 【0105】

次いで、回路基板またはフィルム614を接着材613で接着する。（図5（D））なお、回路基板またはフィルムには端子や配線（図示しない）が形成されており、さまざまな回路やチップを実装できるようになっている。

#### 【0106】

本実施の形態により、プラスチックフィルムを支持体とするSAW素子を作製でき、配線を有するプラスチックフィルムに貼り合わせると熱膨張係数を合わせることができ、装置全体の反りを防ぐことができる。30

#### 【0107】

次いで、両面テープ611から第2の基板612を分離させ、両面テープ611を剥がす。そして、水を用いて水溶性樹脂からなる樹脂層610を溶かして除去する。（図5（E））また、上面図を図5（F）に示す。

#### 【0108】

本発明により表面弹性波素子（SAW素子）を含む被剥離層を回路基板に実装することができる。この表面弹性波素子は、フィルタ、遅延線、発振器、共振器、コンボルバーおよび相関器などに応用でき、代表的には、携帯電話の高周波回路において、送受信の段間に挿入され、不要な周波数成分を除去するBPF（バンドパスフィルタ）を構成することができる。また、SAW素子は、送信周波数を通過帯域にもつBPFと受信周波数を通過帯域にもつBPFを組み合わせ、アンテナ端子を共通化するデュプレクサを作製することができる。40

#### 【0109】

また、上記表面弹性波素子において、必要に応じて短絡用電極を形成してもよい。短絡用電極は、電界を等電位とすることにより該素子のSAW特性を変化させる機能を有する電極である。また、上記表面弹性波素子において、必要に応じて保護膜を形成してもよい。

## 【0110】

また、本実施の形態は実施の形態1乃至3と自由に組み合わせることが可能である。

## 【0111】

## (実施の形態5)

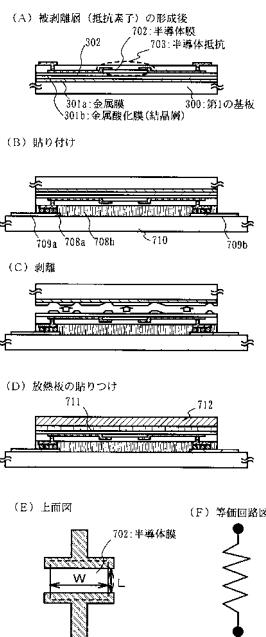

ここでは半導体基板を用いることなく、半導体抵抗素子を形成し、回路基板（プリント基板）に転写、および実装する例を示す。

## 【0112】

なお、途中の工程までは実施の形態1と同一であるため、同じ箇所には同じ符号を用いる。

## 【0113】

第1の基板300上にスパッタ法でタンゲステン膜301a、酸化シリコン膜302を積層形成し、該酸化シリコン膜形成の際、アモルファス状態の酸化タンゲステン膜を形成する。P C V D法で下地絶縁膜となる酸化窒化シリコン膜（膜厚100nm）（図示しない）を形成し、さらに大気にふれることなく、半導体膜702として水素を含むアモルファスシリコン膜（膜厚50～100nm）を積層形成する。なお、ここでは第1の基板300として石英基板を用いる。

10

## 【0114】

次いで、400以上 の熱処理を行い、アモルファス状態の酸化金属膜を結晶化させ、結晶構造を有する酸化金属膜301bを得る。また、600以上に加熱してポリシリコン膜を形成してもよい。次いで、所望の抵抗値とするために、n型の不純物元素（リン等）またはp型の不純物元素（ボロン等）を半導体膜702にドーピングする。

20

## 【0115】

次いで、半導体膜を所望の形状とした後、配線、層間絶縁膜、および引出電極を形成する。（図6（A））また、図6（E）に上面図、図6（F）に等価回路図を示す。なお、抗体となる半導体部分の幅W、長さL、シート抵抗値によって半導体抵抗素子の抵抗値が決定される。

## 【0116】

図6（A）の状態が得られたら、導電性微粒子708aを含む接着材708bで端子709a、709bが設けられた回路基板710と第1の基板300とを貼り合わせる。（図6（B））貼り付けることによって端子709a、709bと半導体膜702に接続している引出電極とが導電性微粒子を介して電気的に接続される。

30

## 【0117】

次いで、第1の基板300を引き剥がす。酸化タンゲステン膜中、または酸化タンゲステン膜と酸化シリコン膜との界面、または酸化タンゲステン膜とタンゲステン膜との界面で分離が生じる。（図6（C））

## 【0118】

次いで、表面に残っている酸化タンゲステンを除去した後、接着材711で放熱板712を貼り付ける。特に、半導体抵抗素子は発熱させることによって抵抗が決定されるため、素子の発熱を放熱させる放熱板を貼り付けることが有用である。

## 【0119】

40

また、上記半導体抵抗素子以外にもTa<sub>x</sub>N<sub>y</sub>やNiCrなどの材料を用いて薄膜抵抗素子を形成することも可能である。

## 【0120】

また、本実施の形態は実施の形態1乃至4と自由に組み合わせることが可能である。例えば、実施の形態2と組み合せた場合、大容量のコンデンサとTFTと半導体抵抗素子とを同時に作製することもできる。

## 【0121】

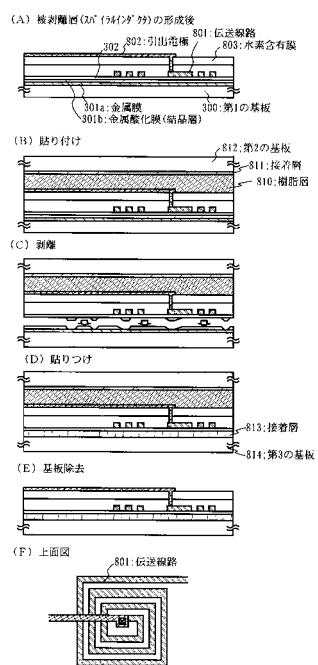

## (実施の形態6)

ここではスパイラルインダクタを形成し、回路基板（プリント基板）に転写、および実装する例を図7に示す。スパイラルインダクタは巻線コイルをイメージして、高インピー

50

ダンスの伝送線路をスパイラル状に巻いたものである。

**【0122】**

なお、途中の工程までは実施の形態1と同一であるため、同じ箇所には同じ符号を用いる。

**【0123】**

第1の基板300上にスパッタ法でタンゲステン膜301a、酸化シリコン膜302を積層形成し、該酸化シリコン膜形成の際、アモルファス状態の酸化タンゲステン膜を形成する。次いで、P C V D法で下地絶縁膜となる酸化窒化シリコン膜（膜厚100nm）（図示しない）を積層形成する。

**【0124】**

次いで、伝送線路801を形成する。伝送線路801としては導電性材料である限り特に限定されない。ここでは、伝送線路を等間隔に約3回スパイラル状に巻いている。

**【0125】**

次いで、層間絶縁膜、水素含有膜803、および引出電極802を形成する。（図7（A））なお、上面図を図7（F）に示す。水素含有膜803としては水素を含む窒化珪素膜を用いる。

**【0126】**

次いで、水またはアルコール類に可溶な接着材を全面に塗布、焼成する。この接着材の組成としては、例えば、エポキシ系、アクリレート系、シリコーン系等いかなるものでもよい。ここではスピンドルコートで水溶性樹脂（東亜合成製：V L - W S H L 10）からなる樹脂層（膜厚30μm）810を塗布し、硬化させる。この水溶性樹脂膜は平坦化膜として機能し、後の基板貼り合わせの際、平坦化膜表面と基板面がほぼ平行になるように接着させることができる。この水溶性樹脂膜を用いない場合、圧着した時に電極やTFTによる凸凹が生じる恐れがある。

**【0127】**

次いで、接着層（両面テープ）811を用い、樹脂層810に第2の基板812を貼り付ける。（図7（B））なお、両面テープではなく、例えば紫外線照射によって剥離する接着材を用いてもよい。

**【0128】**

次いで、金属膜301aが設けられている第1の基板300を物理的手段により引き剥がす。なお、水素含有膜803の成膜中または成膜後の処理で400以上に加熱することによって、比較的小さな力（例えば、人間の手、ノズルから吹付けられるガスの風圧、超音波等）で引き剥がすことができる。こうして、酸化シリコン層302上に形成された被剥離層を第1の基板300から分離することができる。剥離後の状態を図7（C）に示す。被剥離層に酸化タンゲステン膜が部分的に残るが透明であるため、除去しなくてもよいし、除去してもよい。

**【0129】**

次いで、回路基板またはフィルム814を接着材813で接着する。（図7（D））なお、回路基板またはフィルムには端子や配線（図示しない）が形成されており、さまざまな回路やチップを実装できるようになっている。

**【0130】**

次いで、両面テープ811から第2の基板812を分離させ、両面テープ811を剥がす。そして、水を用いて水溶性樹脂からなる樹脂層810を溶かして除去する。（図7（E））以上の工程でスパイラルインダクタを回路基板またはフィルム814に実装することができる。

**【0131】**

本実施の形態により、プラスチックフィルムを支持体とするスパイラルインダクタを作製でき、配線を有するプラスチックフィルムに貼り合わせると熱膨張係数を合わせることができ、装置全体の反りを防ぐことができる。

**【0132】**

10

20

30

40

50

また、複数のスパイラルインダクタを結合してもよい。

**【0133】**

また、本実施の形態は実施の形態1乃至5と自由に組み合わせることが可能である。

**【0134】**

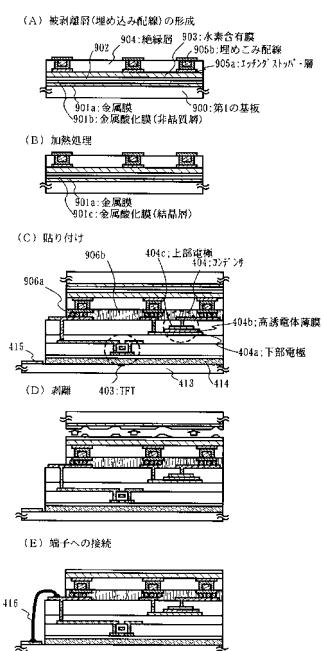

(実施の形態7)

ここでは埋め込み配線を形成し、上記実施の形態2で得られた回路基板(プリント基板)に転写、および実装する例を図8に示す。絶縁層を形成し、該絶縁層に埋め込み配線(Cu、Au、Ag、Ni、クロム、パラジウム、ロジウム、錫、鉛またはこれらの合金など)を形成し、さらに該絶縁層の表面を平坦化した後、露出する部分に金属保護膜(Ti、TiN、Ta、TaNなど)を形成する。

10

**【0135】**

まず、絶縁表面を有する基板900上にスパッタ法で金属膜901a、ここではタンゲステン膜(膜厚10nm～200nm、好ましくは50nm～75nm)を形成し、さらに大気にふれることなく、酸化物膜902、ここでは酸化シリコン膜(膜厚150nm～200nm)を積層形成する。なお、積層形成の際、金属膜901aと酸化シリコン膜902との間に非晶質(アモルファス状態とも呼ぶ)の酸化金属膜(酸化タンゲステン膜)901bが2nm～5nm程度形成される。なお、後の工程で埋め込み配線を形成するため、絶縁表面を有する基板900として表面が平坦な基板を用いることが好ましい。

**【0136】**

次いで、PCVD法で下地絶縁膜となる酸化窒化シリコン膜(膜厚100nm)(図示しない)を形成し、さらに大気にふれることなく、水素含有膜903として水素を含むアモルファシリコン膜(膜厚50nm)を積層形成する。

20

**【0137】**

次いで、エッチングストッパー層905aを形成する。エッチングストッパー層905aとしては、Ni、Ti、W、WSix、Al、Mo、Ta、Cr、またはMoから選ばれた元素、または前記元素を主成分とする合金材料もしくは化合物材料を主成分とする膜またはそれらの積層膜を用いればよい。このエッチングストッパー層905aは、後に行う電解メッキ処理のシード層(メッキ法での陰極)にもなる。また、エッティングストッパー層905a上にシード層を別途形成してもよい。次いで、エッティングストッパー層905aを覆う珪素を主成分とする絶縁膜を形成する。

30

**【0138】**

次いで、パターニングを行い、絶縁膜を選択的にエッティングして、エッティングストッパー層905aに達する開口(溝)を形成する。次いで、第1のバリア層を形成した後、電解メッキ処理を行って開口(溝)に十分な厚みの低抵抗金属膜を形成する。電解メッキ処理は、メッキ法により形成しようとする金属イオンを含む水溶液中に直流電流を流し、陰極面に金属膜を形成する方法である。メッキされる金属としては、電気抵抗が低い材料、例えば銅、銀、金、クロム、鉄、ニッケル、白金、またはこれらの合金などを用いることができる。電解メッキ処理において形成される金属膜の膜厚は電流密度と時間とを制御することにより実施者が適宜設定することができる。銅の電気抵抗は非常に低いため、ここでは低抵抗金属膜として電解メッキが可能な銅(Cu)を用いる例を示す。また、第1のバリア層は、酸化珪素を主成分とする絶縁膜904中の拡散が速い銅の拡散防止層、即ちバリアメタルであり、比抵抗値が300～500 $\mu$ cm程度以下である金属材料(WNx、TaNx、TiSi<sub>x</sub>Ny、WSi<sub>x</sub>Ny、TaSi<sub>x</sub>Nyなど)を用いることが好ましい。また、銅は、酸化珪素を主成分とする絶縁膜904との密着性が悪いため、密着性の良好な第1のバリア層を形成することは有用である。

40

**【0139】**

次いで、化学機械研磨法(以下、CMP法と呼ぶ)などで代表される平坦化処理を行うことによって、開口(溝)だけに銅と第1のバリア層を残し、不要な部分を除去して埋め込み型の配線(以下、埋め込み配線と呼ぶ)905bを形成する。なお、非晶質であるためCMPなどを行っても酸化金属膜901bの界面における密着性が高く、剥離は生じな

50

い。

#### 【0140】

次いで、露出した銅の耐酸化性を高めるため、第2のバリア層を形成する。（図8（A））また、第2のバリア層は、酸化珪素を主成分とする絶縁膜904中での拡散が速い銅の拡散防止層としても有用であり、窒化珪素膜、または金属材料（TiN、NbN、WN<sub>x</sub>、Ta<sub>x</sub>N<sub>y</sub>、TiSi<sub>x</sub>N<sub>y</sub>、WSi<sub>x</sub>N<sub>y</sub>、TaSi<sub>x</sub>N<sub>y</sub>など）を用いることが好ましい。また、銅は、酸化珪素を主成分とする絶縁膜との密着性が悪いため、密着性の良好な第2のバリア層を形成することは有用である。

#### 【0141】

次いで、加熱処理を行い、後の剥離工程で被剥離層を第1の基板から剥離しやすくする。（図8（B））ここで加熱処理は、金属酸化膜901bを結晶化させて結晶構造を有する金属酸化膜901cを形成するとともに水素含有膜903の膜中に含まれる水素を拡散するものである。なお、金属膜901aとしてタンゲステン膜を用いた場合には400、1時間以上の加熱処理を行えばよい。

#### 【0142】

また、金属膜901aとして合金、例えばW-Mo合金を用い、その組成比を調節することによって剥がれやすさを変化させることもできる。また、イオン注入法やイオンドーピング法を用い、酸化金属膜に窒素を注入して剥がれにくくしたり、酸素を注入して剥がれやすくする処理などを行ってもよい。

#### 【0143】

次いで、埋め込み配線905bが設けられた第1の基板900と、実施の形態2で得られる容量素子（コンデンサ404）とTFT403とが設けられた回路基板413とを接着層414で貼り合わせる。（図8（C））なお、実施の形態2と同一の部分には同じ符号を用いる。導電性微粒子906aを含む接着材906bで貼り合わせることによって、埋め込み配線とコンデンサ404に接続している電極との導通と、埋め込み配線とTFT403に接続している電極との導通とを行う。

#### 【0144】

また、高誘電体薄膜404bを形成する場合、比較的高温の熱処理を行うため、配線としては高耐熱性の材料を用いることとなり、配線の抵抗値を下げる事が困難である。引き回し配線部分として本実施の形態での埋め込み配線を貼り合わせることによって低抵抗な配線を備えた複合回路を提供することができる。

#### 【0145】

次いで、金属膜901aが設けられている第1の基板900を物理的手段により引き剥がす。比較的小さな力（例えば、人間の手、ノズルから吹付けられるガスの風圧、超音波等）で引き剥がすことができる。こうして、酸化シリコン層902上に形成された被剥離層を第1の基板900から分離することができる。剥離後の状態を図8（D）に示す。なお、被剥離層に酸化タンゲステン膜が部分的に残るが透明であるため、除去しなくてもよいし、除去してもよい。

#### 【0146】

次いで、実施の形態2と同様に、引出電極と端子415とを接続するボンディングワイヤ416を形成する。また、引出電極と端子415とを半田付けや導電性接着材で接続してもよい。

#### 【0147】

以上の工程により、低抵抗な埋め込み配線を備え、且つ、容量素子とTFTとを含む被剥離層を回路基板に重ねて実装することができる。また、埋め込み配線パターンを形成し、それに合わせて被剥離層を接続するように重ねることで回路基板への接続ポイントが減らせる。また、低抵抗な埋め込み配線を貼り付けることによって、複雑な引き回し配線を有する回路を単純化することができる。

#### 【0148】

ここでは引き回し配線として本発明の埋め込み配線を用いた例を図示したが特に限定さ

10

20

30

40

50

れず、様々な配線、例えばソース配線、引き出し配線、電源供給線、容量配線などに用いて配線の低抵抗化を図ることができる。

【0149】

また、本発明の埋め込み配線を用い、スパイラルインダクタやアンテナパターンやグラウンドパターンなどを作製することができる。

【0150】

また、本実施の形態は実施の形態1乃至6と自由に組み合わせることが可能である。

【0151】

(実施の形態8)

本発明は、半導体基板を用いることなく、上記実施の形態1乃至7のいずれか一を用いて様々な機能回路を形成し、回路基板100に実装することができる。回路基板100としてはセラミック基板(アルミナなど)や樹脂系基板(FR-4など)を用いればよい。

10

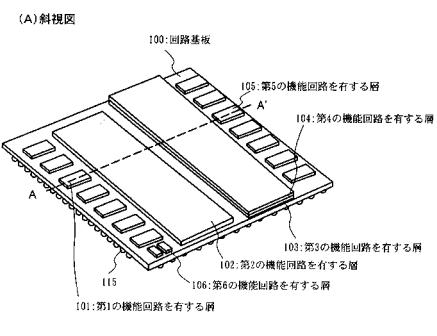

【0152】

ここでは、携帯電話等の情報端末に搭載される高周波回路(フロントエンド部)とCPUとを有するモジュールの斜視図を図9(A)に示す。

【0153】

アンテナスイッチ2個、LPF2個、ダイプレクサ1個を集積することによってフロントエンド部を構成する。アンテナスイッチとしては2個のダイオードと2個のインダクタと5個のコンデンサとで構成する。また、ダイプレクサは、アンテナからの入り口に位置し、デュアルバンドの2つの周波数域を分離する3ポートのフィルタ素子である。ダイプレクサは、高周波側を通過させるHPFと低周波側を通過させるLPFから構成される。ダイプレクサのLPFはL(インダクタ)2個、C(コンデンサ)3個により構成され、ダイプレクサのHPFはL(インダクタ)1個、C(コンデンサ)3個により構成される。

20

【0154】

例えば、実施の形態1で得られるコンデンサを第1の機能回路を有する層101として複数個実装し、実施の形態2で得られるCMOS回路と、実施の形態3で形成されるメモリとを用いたCPUを第2の機能回路を有する層102として実装し、実施の形態1および実施の形態2で得られるダイオードとインダクタとコンデンサとからなるアンテナスイッチを第3の機能回路を有する層103として実装し、アンテナパターンを第4の機能回路を有する層104として実装し、実施の形態1で得られるインダクタを第5の機能回路を有する層105として複数個実装し、実施の形態5で得られる抵抗を第6の機能回路を有する層106として複数個実装し、それぞれ適宜配線パターン114で接続を行い、素子同士を組み合わせることによってフロントエンド部とCPUとを回路基板100に形成する。CPUは装置全体をコントロールするものである。

30

【0155】

このように様々な回路を集積化することでノイズを低減することができる。

【0156】

また、半導体基板を用いることなく、各種フィルタ回路、音声や画像の処理回路、各種のインターフェース回路なども同様にして形成、実装することができる。

40

【0157】

例えば、半導体基板100に発振器としてのTFT、電圧可変とするためのバリキャップダイオード、およびそれらの周辺にコンデンサ、インダクタ、抵抗を適宜配置して発振条件を決定するVCO(電圧制御発振器)を形成することもできる。

【0158】

また、ここでは高周波回路を例としたが、さらに集積化を行い、高周波回路に加え、フラッシュメモリ、太陽電池、センサ素子、発光素子なども同一回路基板に搭載可能である。

【0159】

また、回路基板の上表面をモールド樹脂で覆ってもよいし、保護用のケースで覆っても

50

よい。さらに側面からリード（ピン）を設けてもよい。

#### 【0160】

ここでは回路基板に実装する例を示したが、特に限定されず、表示部や配線や回路が設けられたガラス基板やプラスチックフィルムなどにも実装することができる。

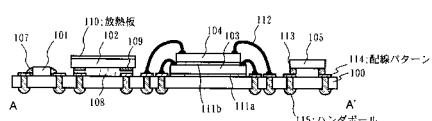

#### 【0161】

また、図9（B）は、図9（A）中の点線A-A'で切断した断面図である。図9（B）において、第1の機能回路を有する層101は半田107で配線パターン114と電気的に接続、実装されている。また、第2の機能回路を有する層102は導電性微粒子を含む接着材108で固定され、第2の機能回路を有する層102に設けられた電極109は導電性微粒子で配線パターン114と接続されている。また、第3の機能回路を有する層103は、接着材111aで固定され、ワイヤボンディング法によってワイヤ112で配線パターン114と接続されている。また、第4の機能回路を有する層104は、接着材111bで第3の機能回路を有する層103と固定され、ワイヤボンディング法によって形成されたワイヤ112で配線パターン114と接続されている。また、第5の機能回路を有する層105は転写バンプ法によって形成されたバンプ113で配線パターン114と接続されている。なお、配線パターン114は回路基板100に設けられたスールホールを通じ、外部端子となるハンダボール115と接続している。ハンダボール115の形成方法としては、超音波ハンダバンプ形成方法、無電解メッキによるハンダバンプ形成方法、または転写法によるハンダバンプ形成方法などがある。

#### 【0162】

また、図9では様々な実装方法で実装した例を示したが、1つの実装方法に統一してもよいし、適宜選択すればよい。

#### 【0163】

##### （実施の形態9）

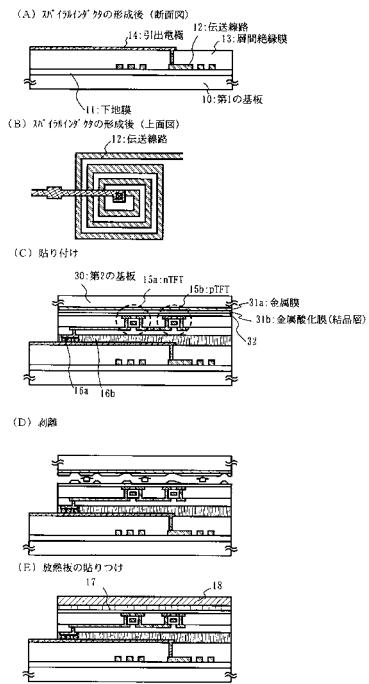

ここではスパイラルインダクタと、TFTとを積層する例を図1に示す。

#### 【0164】

まず、第1の基板10上に下地絶縁膜11を形成し、伝送線路12を形成する。伝送線路12としては導電性材料である限り特に限定されない。ここでは、伝送線路を等間隔に約3回スパイラル状に巻いている。第1の基板10はガラス基板であってもよいし、プラスチック基板であってもよいし、セラミックス基板や石英基板であってもよい。

#### 【0165】

次いで、層間絶縁膜13、および引出電極14を形成する。（図1（A））なお、上面図を図1（B）に示す。

#### 【0166】

次いで、nチャネル型TFT15a、pチャネル型TFT15bが設けられた第2の基板30と導電性微粒子16aを含む接着材16bで貼りあわせる。（図1（C））導電性微粒子16aにより引出電極14と、nチャネル型TFT15a、またはpチャネル型TFT15bとが接続される。なお、第1の基板30上にスパッタ法でタンゲステン膜31a、酸化シリコン膜32を積層形成し、該酸化シリコン膜形成の際、アモルファス状態の酸化タンゲステン膜を形成し、400以上の熱処理がTFT15a、15bの作製工程中に行われ、アモルファス状態の酸化金属膜を結晶化させ、結晶構造を有する酸化金属膜31bが得られている。

#### 【0167】

次いで、金属膜31aが設けられている第1の基板30を物理的手段により引き剥がす。比較的小さな力（例えば、人間の手、ノズルから吹付けられるガスの風圧、超音波等）で引き剥がすことができる。こうして、酸化シリコン層32上に形成された被剥離層を第1の基板30から分離することができる。剥離後の状態を図1（D）に示す。

#### 【0168】

次いで、表面に残っている酸化タンゲステンを除去した後、接着材17で放熱板18を貼り付ける。特に、CMOS回路を用いてCPU回路などの高集積回路を形成した場合、

10

20

30

40

50

発熱しやすいため、素子の発熱を放熱させる放熱板を貼り付けることが有用である。なお、発熱が問題にならない集積回路の場合には特に放熱板を貼り付ける必要はない。

#### 【0169】

以上の工程でスパイラルインダクタとCMOS回路とを積層し、且つ、接続することができる。ここではスパイラルインダクタとCMOS回路とを積層した例を示したが、実施の形態1乃至7で得られる様々な素子や配線を含む被剥離層を2層、またはそれ以上の積層を行うことができ、さらには互いに電極の引出や、配線の引き回しを行うことができる。

#### 【0170】

また、本実施の形態は実施の形態1乃至8と自由に組み合わせることが可能である。

10

#### 【0171】

以上の構成でなる本発明について、以下に示す実施例でもってさらに詳細な説明を行うこととする。

#### 【実施例1】

#### 【0172】

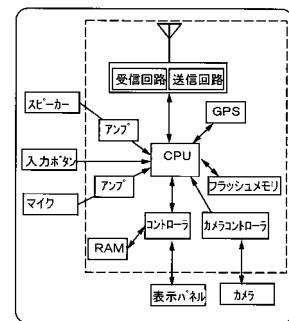

本実施例では、GPS機能を備えた携帯電話を一例として図10に説明する。

#### 【0173】

図10(A)には、アンテナ、受信回路、送信回路、GPSなどの機能回路が設けられ、さらに着信履歴などを記憶するフラッシュメモリ、カメラコントローラ、表示パネルに接続されたコントローラ、RAMなどが設けられている。また、マイクからの信号を増幅するアンプ、スピーカーに音声出力する信号を増幅するアンプなどが設けられている。また、これらに接続するCPUが設けられている。

20

#### 【0174】

本発明は、半導体基板を用いることなく、図10(A)中の点線で囲まれた部分の回路を作製し、回路基板に実装することができる。実施の形態1乃至7のいずれかに従って得られるコンデンサ、インダクタ、抵抗素子、SAW素子などを適宜組み合わせてそれぞれの機能回路を作製すればよい。

#### 【0175】

また、ここでは図示しないが信号処理部(DSP)が設けられている。

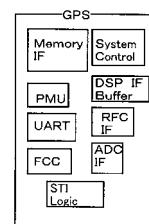

#### 【0176】

30

また、図10(B)にはGPSを構成する機能ブロックを示している。GPS機能は、System Control、Memory IF(メモリーインターフェース)、PMU(経路メモリユニット)、UART(受信部)、FCC、DSP IF Buffer(DSP(信号処理部)インターフェース バッファ)、RFC IF(Radio Frequency Choke coil interface)、ADC IF(A-Dコンバータインターフェース)、STI Logic(Set Interrupt Logic)などから構成されている。

#### 【0177】

なお、機能回路ブロックを並列に協調して動作させるグルーロジック(Glue Logic)でそれぞれ異なる上記機能ブロックを相互接続させてもよい。

#### 【0178】

40

また、これら点線で囲まれた部分の回路のうちいくつか、或いは全てを表示パネルの基板に実装することもできる。

#### 【0179】

また、ここでは携帯電話の例を示したが、本発明は、他の携帯情報端末、カード(レフロンカードやIDカードや回路を有するカードや半導体素子を有するカード)、ビデオカメラ、デジタルカメラ、ゴーグル型ディスプレイ、カーナビゲーションで代表されるナビゲーション装置、DVDプレーヤー、または電子遊技機器に実施可能であり、更なる軽量化、薄型化、低コスト化、実装面積削減が実現できる。

#### 【0180】

また、本実施例は実施の形態1乃至9と自由に組み合わせることが可能である。

50

**【実施例 2】****【0181】**

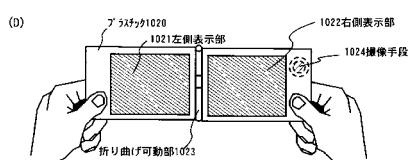

図13(A)中、1001は中央処理部(CPUとも呼ばれる)、1002は制御部、1003は演算部、1004は記憶部(メモリーとも呼ばれる)、1005は入力部、1006は出力部(表示部など)である。

**【0182】**

演算部1003と制御部1002とを合わせたものが、中央処理部1001であり、演算部1003は、加算、減算の算術演算やAND、OR、NOTなどの論理演算を行う算術論理演算部(arithmetic logic unit, ALU)、演算のデータや結果を一時格納する種々のレジスタ、入力される1の個数を数え上げるカウンタなどから成り立っている。演算部1003を構成する回路、例えば、AND回路、OR回路、NOT回路、バッファ回路、またはレジスタ回路などはTFTで構成することができ、高い電界効果移動度を得るために、連続発振型のレーザー光を用いて結晶化を行った半導体膜をTFTの活性層として作製すればよい。10

**【0183】**

まず、基板上にスパッタ法でタンゲステン膜と酸化シリコン膜を形成し、その上に下地絶縁膜(酸化珪素膜、窒化珪素膜、または酸化窒化珪素膜)を形成し、その上にアモルファスシリコン膜を形成する。なお、タンゲステン膜と酸化シリコン膜の界面に形成された酸化タンゲステン層を用いて後の工程で剥離を行う。

**【0184】**

結晶化方法としては、アモルファスシリコン膜に触媒となる金属元素を添加した後、加熱してポリシリコン膜を得た後にパルス発振型のレーザー光を照射したポリシリコン膜を得る方法を用いてもよいし、アモルファスシリコン膜に連続発振型のレーザー光を照射してポリシリコン膜を得る方法を用いてもよいし、アモルファスシリコン膜を加熱してポリシリコン膜を得た後に連続発振型のレーザー光を照射してポリシリコン膜を得る方法を用いてもよいし、アモルファスシリコン膜に触媒となる金属元素を添加した後、加熱してポリシリコン膜を得た後に連続発振型のレーザー光を照射してポリシリコン膜を得る方法を用いてもよい。なお、連続発振型のレーザー光を用いる場合、演算部1003、制御部1002、または記憶部1004を構成するTFTのチャネル長方向とレーザービームの走査方向とを揃えることが好ましい。30

**【0185】**

また、制御部1002は記憶部1004に格納された命令を実行して、全体の動作を制御する役割を担っている。制御部1002はプログラムカウンタ、命令レジスタ、制御信号生成部からなる。また、制御部1002もTFTで構成することができ、結晶化を行った半導体膜をTFTの活性層として作製すればよい。

**【0186】**

また、記憶部1004は、計算を行うためのデータと命令を格納する場所であり、CPUで頻繁に実行されるデータやプログラムが格納されている。記憶部1004は、主メモリ、アドレスレジスタ、データレジスタからなる。さらに主メモリに加えてキャッシュメモリを用いてもよい。これらのメモリは、SRAM、DRAM、フラッシュメモリなどで形成すればよい。また、記憶部1004もTFTで構成する場合には、結晶化を行った半導体膜をTFTの活性層として作製することができる。40

**【0187】**

また、入力部1005は外部からデータやプログラムを取り込む装置である。また、出力部1006は結果を表示するための装置、代表的には表示装置である。

**【0188】**

こうして得られたCPU(端子電極、引き出し配線を含む)を含む被剥離層を基板から剥離し、プラスチック基板に転写する。

**【0189】**

また、CPUだけでなく、電流回路、表示部、および駆動回路部を含む様々な機能回路50

も一緒に作製することができ、例えば非接触型の薄膜集積回路を有するカード、身体装着型コンピュータなどを作製することができる。

**【0190】**

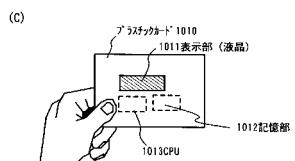

図13(B)は、非接触型の薄膜集積回路を有するカードの図である。

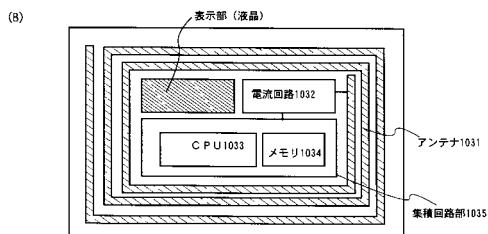

**【0191】**

図13(B)には、非接触型の薄膜集積回路の具体的な構成の上面図を示している。表示部と、アンテナ1031と、電流回路1032と、CPU1033やメモリ1034等を含む集積回路部1035を有し、アンテナは電流回路を介してICに接続されている。電流回路1032は、例えばダイオードと、容量とを有する構成であればよく、アンテナが受信する交流周波を直流に変換する機能を有する。また、アンテナ1031は、集積回路と同一工程で形成することもできる。10

**【0192】**

なお、非接触型のICの特徴は、コイル状に巻かれたアンテナの電磁誘導作用（電磁誘導方式）、相互誘導作用（電磁結合方式）又は静電気による誘導作用（静電結合方式）により電力が供給される点である。このアンテナの巻き数を制御することにより、受信する周波数の高さを選ぶことができる。

**【0193】**

周波数は、遠隔型ではマイクロ波、近傍型及び近接型では13.56MHz、密着型では4.91MHzが一般的に使用されているが、周波数を高め波長を短くすることによりアンテナの巻き数を小さくできる。20

**【0194】**

また非接触型薄膜集積回路は接触型薄膜集積回路と比較すると、リーダ／ライタに接触せず、非接触で電源供給及び情報通信を行うため、破損せず、高い耐久性を有し、静電気等によるエラーの心配がない。更にはリーダ／ライタ自体の構成は複雑にならならず、薄膜集積回路をリーダ／ライタにかざせばよいので、取り扱いが容易である。

**【0195】**

非接触型の集積回路は、CPUと、メモリと、I/Oポートと、コプロセッサを有し、バスを介してデータ交換を行っている。更にICはRF（無線）インターフェースと、非接触インターフェースとを有している。そして、読み取り手段であるリーダ／ライタは、非接触インターフェースと、インターフェース回路とを有し、ICをリーダ／ライタへかざし、各非接触インターフェース間で通信や電波により情報伝達・交換が行われる。そしてリーダ／ライタの、インターフェース回路によりホストコンピュータと情報伝達・交換をしている。もちろんホストコンピュータがリーダ／ライタ手段を有していても構わない。30

**【0196】**

図13(C)は、図13(B)に対応するプラスチックカードとした場合の外観図である。図13(C)において、1010はプラスチックカード本体、1011は表示部、1012は記憶部、1013はCPUである。認証カードとした場合には、軽量であり、フレキシブルなカードとすることができます。そして、認証カードが不用になった場合には簡単に切断、細分化することが可能であり、記憶部にある情報を完全に読み取り不能、または偽造複製防止することができる。40

**【0197】**

また、必要であれば表示部などを駆動させるバッテリー（シート状電池や太陽電池）も設けてもよい。シート状電池や太陽電池なども剥離、転写を用いて作りこむことができる。シート状電池は、シート上に正極活物質、固体電解質、負極活物質を層状に重ねた発電要素からなる固体発電セルを複数配置したものである。正極活物質、固体電解質、及び負極活物質としては、リチウムコバルト酸化物、リチウムニッケル酸化物、リチウムマンガン酸化物、リチウムバナジウム酸化物、リチウムチタン酸化物、金属リチウム、リチウム合金、二酸化マンガン、黒鉛やコーラスなどの炭素系材料、五酸化ニオブ、リチウム遷移金属複合窒化物、PEO（ポリエチレンオキシド）、リン酸リチウムなどを用いることができる。また、これらの材料にカーボン、アセチレンブラックなどの電子伝導材や高分子50

バインダーなどの添加材を混合して用いてもよい。

**【0198】**

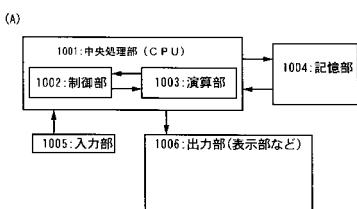

また、図13(D)に示す装置は、液晶表示部を複数有する情報携帯端末の例である。

**【0199】**

図13(D)に示す装置は、折り曲げ可動部1023により折りたたむことができ、名刺サイズとすることができます。折りたたむことによって小型化するとともに複数の表示部を保護することができる。プラスチック1020が本体となっているため、軽量であり、左側表示部1021と右側表示部1022を有している。表示部とは裏側に撮像手段(CCDカメラなどの固体撮像素子)1024を設けてもよい。撮像手段1024で撮像したデータをカメララインターフェース部などを介して左側表示部1021または右側表示部1022に直接表示することができる。左側表示部1021と右側表示部1022は、タッチパネルとして使用者が様々な操作入力を行えるようにすることが好ましい。10

**【0200】**

また、プラスチック1020の本体には、表示部および本体の各部を統括的に制御するようになされたCPUなどからなる主制御部や、記憶部、表示部駆動回路、電源回路部、操作入力制御部、変復調回路部、送受信回路部、アンテナなどを設ける。これらのうち、一部または全部を本発明によりプラスチック上に形成することもできる。

**【0201】**

例えば、データ送信する場合には、操作キー(図示しない)、もしくはタッチパネル操作により入力されたテキストデータを操作入力制御部を介して主制御部に送出する。主制御部はテキストデータを変復調回路部でスペクトラム拡散処理し、送受信回路部でデジタルアナログ変換処理および周波数変換処理を施した後にアンテナを介して基地局へ送信する。また、データ受信する場合には、基地局からアンテナを介して受信した受信信号を変復調回路部でスペクトラム逆拡散処理して、元のテキストデータを復元した後、表示部駆動回路を介して表示部にデータとして表示する。20

**【0202】**

なお、図13(D)に示す装置は、超小型コンピュータとして機能させてもよい。なお、図示しないが、プラスチック1020の本体にはバッテリー(シート状電池や太陽電池)も設ける。シート状電池や太陽電池なども剥離、転写を用いて作りこむことができる。また、プラスチック1020の本体にブルートゥース通信部を設けてもよい。30

**【産業上の利用可能性】**

**【0203】**

本発明により、様々な機能回路や素子が設けられたプラスチックシートを接続した集合体で電子機器の一部もしくは全部を作製することができ、情報端末機器のさらなる軽量化を実現する。

**【図面の簡単な説明】**

**【0204】**

【図1】実施の形態9を示す図である。

【図2】実施の形態1を示す図である。

【図3】実施の形態2を示す図である。

【図4】実施の形態3を示す図である。

【図5】実施の形態4を示す図である。

【図6】実施の形態5を示す図である。

【図7】実施の形態6を示す図である。

【図8】実施の形態7を示す図である。

【図9】実施の形態8を示す図である。

【図10】実施例1を示す図である。

【図11】剥離前の断面T E M写真を示す図。(実施の形態2)

【図12】剥離後の断面T E M写真を示す図。(実施の形態2)

【図13】実施例2を示す図である。

10

20

30

40

50

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

(B) A-A'断面図

【図10】

(A) 携帯電話のブロック図

(B) GPSのブロック図

【図13】

【図 11】

(A) TEM観察写真（断面）

(B) 模式図

【図12】

(A) TEM観察写真（断面）

(B) 模式図

---

フロントページの続き

(51)Int.Cl.

H 01 L 27/06 (2006.01)

H 01 L 21/8234 (2006.01)

H 01 L 27/08 (2006.01)

H 01 L 27/00 (2006.01)

H 01 L 23/12 (2006.01)

F I

H 01 L 27/08 331E

H 01 L 27/00 301B

H 01 L 23/12 B

(72)発明者 後藤 裕吾

神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内

(72)発明者 桑原 秀明

神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内

審査官 河本 充雄

(56)参考文献 特開平07-045786(JP,A)

特開平11-026733(JP,A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 21/02

H 01 L 21/20

H 01 L 21/336

H 01 L 21/8234

H 01 L 23/12

H 01 L 27/00

H 01 L 27/06

H 01 L 27/08

H 01 L 27/12

H 01 L 29/786