(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2011년12월22일

(11) 등록번호 10-1097694

(24) 등록일자 2011년12월15일

(51) Int. Cl.

*H01L 33/48* (2010.01) *H01L 33/50* (2010.01)

(21) 출원번호 10-2006-7011189

(22) 출원일자(국제출원일자) 2004년11월24일

심사청구일자 2009년10월16일

(85) 번역문제출일자 2006년06월07일

(65) 공개번호 10-2007-0041663

(43) 공개일자 2007년04월19일

(86) 국제출원번호 PCT/US2004/039619

(87) 국제공개번호 WO 2005/062393

국제공개일자 2005년07월07일

(30) 우선권주장

10/987,894 2004년11월12일 미국(US)

60/528,054 2003년12월09일 미국(US)

(56) 선행기술조사문헌

JP11251644 A

JP2001015815 A

KR1019880014692 A

전체 청구항 수 : 총 33 항

심사관 : 진수영

## (54) 반도체 발광소자, 서브마운트 및 이들의 제조방법

## (57) 요 약

반도체 발광소자용 서브마운트는 내부에 발광소자를 수용하도록 구성된 캐비티를 가지는 반도체 기판을 포함한다. 제 1 본드 패드는 캐비티 내에 수용된 발광소자의 제 1 노드와 결합하기 위하여 캐비티 내에 배치된다. 제 2 본드 패드는 내부에 배치된 발광소자의 제 2 노드와 결합하기 위하여 캐비티 내에 배치된다. 발광소자는 고상 파장변환 부재를 포함하며, 발광소자를 형성하는 방법이 또한 제공된다.

## 대 표 도 - 도2

(72) 발명자

엔드류스 피터 에스.

미국 노쓰캐롤라이나 27712 더럼 콘티넨탈 드라이

브 221

네글리 제럴드 에이치.

미국 노쓰캐롤라이나 27510 카보로 엔. 에스테스

드라이브 306에스테스 파크 아파트먼트 아이-14

힐러 노르베르트

미국 노쓰캐롤라이나 27516 채플 힐 아이언우즈 드

라이브 108

## 특허청구의 범위

### 청구항 1

반도체 발광소자를 수용하도록 구성된 캐비티(cavity)를 내부에 갖는 반도체 기판;

상기 반도체 기판을 통하여 상기 기판의 외부 표면으로 연장된 제 1 도전성 경로에 상기 캐비티 내에 수용된 발광소자의 제 1 노드를 결합하도록 배치된 상기 캐비티 내의 제 1 본드 패드; 및

상기 반도체 기판을 통하여 상기 기판의 외부 표면으로 연장된 제 2 도전성 경로에 상기 발광소자의 제 2 노드를 결합하도록 배치된 상기 캐비티 내의 제 2 본드 패드를 포함하는 반도체 발광소자용 서브마운트.

### 청구항 2

제 1 항에 있어서,

상기 캐비티는 플로우(floor) 및 상기 플로우에 대하여 적어도  $90^{\circ}$  의 각을 이루는 측벽을 포함하는 반도체 발광소자용 서브마운트.

### 청구항 3

제 2 항에 있어서,

상기 제 1 및 제 2 본드 패드는 상기 캐비티의 상기 플로우 상에 배치되는 반도체 발광소자용 서브마운트.

### 청구항 4

제 2 항에 있어서,

상기 캐비티는 상기 플로우로부터 적어도 내부에 수용된 상기 발광소자의 높이를 갖는 상기 반도체 기판의 상부 표면까지의 높이를 갖는 반도체 발광소자용 서브마운트.

### 청구항 5

제 2 항에 있어서,

고상 파장변환 부재(solid wavelength conversion element)를 수용하고 상기 캐비티 내의 발광소자로부터 방출되는 광을 수용하기 위해 상기 캐비티 상으로 상기 파장변환 부재를 배치하도록 구성된, 상기 캐비티에 인접한 상기 반도체 기판의 상부 표면에 수용 리세스(receiving recess)를 더 포함하는 반도체 발광소자용 서브마운트.

### 청구항 6

제 2 항에 있어서,

상기 캐비티의 상기 플로우 및 측벽 중 적어도 하나 상에 반사성 재료 코팅을 더 포함하는 반도체 발광소자용 서브마운트.

### 청구항 7

제 1 항에 있어서,

상기 제 1 및 제 2 도전성 경로는 모두 상기 반도체 기판의 상기 외부 표면의 하부측으로 연장되는 반도체 발광소자용 서브마운트.

### 청구항 8

제 1 항에 있어서,

상기 반도체 기판의 상기 외부 표면 상에 제 1 외부 마운팅 패드 및 제 2 외부 마운팅 패드를 더 포함하며,

상기 제 1 도전성 경로는 상기 제 1 외부 마운팅 패드로 연장되고, 상기 제 2 도전성 경로는 상기 제 2 외부 마운팅 패드로 연장되는 반도체 발광소자용 서브마운트.

**청구항 9**

제 1 항에 있어서,

상기 캐비티에 마운팅된 발광소자에 대하여 정전기 방전(ESD) 방지(protection)를 제공하기 위하여, 상기 제 1 및 제 2 도전성 경로들을 결합하는 적분 대향형 제너 다이오드 접합(integral opposing zener diode junctions)을 더 포함하는 반도체 발광소자용 서브마운트.

**청구항 10**

제 9 항에 있어서,

상기 적분 대향형 제너 다이오드 접합은 적어도 상기 제 1 도전성 경로의 일부 및 적어도 상기 제 2 도전성 경로의 일부를 형성하는 반도체 재료로 이루어진 제 1 도전형 도핑된 영역들 및 그 사이에 배치된 반도체 재료로 이루어진 반대 도전형 도핑된 영역을 포함하는 반도체 발광소자용 서브마운트.

**청구항 11**

제 10 항에 있어서,

상기 제 1 도전형은 n-형으로 이루어지고, 상기 반대 도전형은 p-형으로 이루어지는 반도체 발광소자용 서브마운트.

**청구항 12**

제 11 항에 있어서,

상기 n-형 도핑된 영역들은 각각 상기 제 1 및 제 2 본드 패드를 또는 제 1 및 제 2 외부 마운팅 패드들 중 하나와 콘택트되는 반도체 발광소자용 서브마운트.

**청구항 13**

제 12 항에 있어서,

상기 반도체 기판은 p-형 기판으로 이루어지며, 상기 n-형 도핑된 영역들은 상기 p-형 기판 내의 n-형 도핀트들의 웨들로 이루어지는 반도체 발광소자용 서브마운트.

**청구항 14**

제 10 항에 있어서,

상기 제 1 및 제 2 도전성 경로들은 각각 반도체 재료의 각각의 제 1 도전형 도핑된 영역들로부터 연장된 각각의 금속을 매립한 비아부를 더 포함하는 반도체 발광소자용 서브마운트.

**청구항 15**

제 11 항의 서브마운트를 포함하며,

상기 캐비티 내의 상기 발광소자; 및

상기 발광소자로부터 방출된 광을 수용하고 파장변환하기 위해, 상기 발광소자 상으로 상기 반도체 기판의 상부 표면 상에 배치된 고상 파장변환 부재를 더 포함하는 발광소자 패키지.

**청구항 16**

제 15 항에 있어서,

상기 발광소자와 상기 파장변환 부재 사이의 상기 캐비티 내에 인캡슐런트(encapsulant) 재료를 더 포함하는 발광소자 패키지.

**청구항 17**

제 16 항에 있어서,

상기 인캡슐런트 재료는 적어도 1.5의 굴절률을 가지는 발광소자 패키지.

### 청구항 18

제 15 항에 있어서,

상기 고상 과장변환 부재는 내부에 과장변환 재료를 가지는 유리, 실리콘 및 경화 애폭시 중 적어도 하나를 포함하는 경성(rigid) 과장변환 부재를 포함하는 발광소자 패키지.

### 청구항 19

제 18 항에 있어서,

상기 과장변환 재료는 형광체(phosphor)를 포함하는 발광소자 패키지.

### 청구항 20

제 15 항에 있어서,

상기 발광소자는 발광 다이오드(LED)를 포함하는 발광소자 패키지.

### 청구항 21

제 15 항에 있어서,

상기 발광소자에 대하여 정전기 방전(ESD) 방지를 제공하기 위하여, 상기 제 1 및 제 2 도전성 경로들을 결합하는 적분 대향형 제너 다이오드 접합을 더 포함하는 발광소자 패키지.

### 청구항 22

플로우 및 상기 플로우와 적어도 90 ° 의 각을 이루는 측벽을 가지며 발광소자를 수용하도록 구성된 캐비티를 반도체 기판 내에 형성하는 단계;

상기 반도체 기판을 통하여 상기 캐비티로부터 상기 반도체 기판의 외부 표면까지 연장된 제 1 도전성 경로를 형성하는 단계;

상기 반도체 기판을 통하여 상기 캐비티로부터 상기 반도체 기판의 외부 표면까지 연장된 제 2 도전성 경로를 형성하는 단계;

내부에 형성된 상기 제 1 도전성 경로의 단부 상에 상기 캐비티 내의 제 1 본드 패드를 형성하는 단계; 및

내부에 형성된 제 2 도전성 경로의 단부 상에 상기 캐비티 내의 제 2 본드 패드를 형성하는 단계

를 포함하는 반도체 발광소자용 서브마운트의 제조 방법.

### 청구항 23

제 22 항에 있어서,

상기 캐비티 내에 배치된 발광소자에 대하여 정전기 방전(ESD) 방지를 제공하기 위하여, 상기 제 1 및 제 2 도전성 경로들을 결합하는 적분 대향형 제너 다이오드 접합을 더 형성하는 단계를 포함하는 반도체 발광소자용 서브마운트의 제조 방법.

### 청구항 24

제 23 항에 있어서,

상기 반도체 기판은 반도체 재료로 이루어진 제 1 도전형 도핑된 영역들을 포함하며,

상기 적분 대향형 제너 다이오드 접합을 형성하는 단계는 상기 제 1 도전성 경로의 일부로서 상기 제 1 도전형 도핑된 영역 내에 반도체 재료로 이루어진 반대 도전형 도핑된 영역을 형성하는 단계 및 상기 제 2 도전성 경로의 일부로서 상기 제 1 도전형 도핑된 영역 내에 반도체 재료로 이루어진 제 2 반대 도전형 도핑된 영역을 형성하는 단계를 포함하는 반도체 발광소자용 서브마운트의 제조 방법.

## 청구항 25

제 24 항의 방법을 포함하며,

상기 제 1 본드 패드와 결합된 상기 발광소자의 제 1 노드 및 상기 제 2 본드 패드와 결합된 상기 발광소자의 제 2 노드를 갖는 상기 발광소자를 상기 캐비티 내에 배치하는 단계; 및

상기 발광소자로부터 방출된 광을 수용하고 과장변환하기 위하여, 상기 발광소자 상으로, 상기 기판 상에 고상 과장변환 부재를 배치하는 단계를 더 포함하는 발광소자 패키지의 제조 방법.

## 청구항 26

제 25 항에 있어서,

상기 서브마운트 상에 고상 과장변환 부재를 배치하는 단계 이전에, 그 과장변환 특성을 결정하기 위하여 상기 과장변환 부재를 테스트하는 단계를 수행하는 발광소자 패키지의 제조 방법.

## 청구항 27

제 26 항에 있어서,

상기 과장변환 부재는 상기 발광소자에 대향하는 표면 상에서 평평하고 오목한 것 중 적어도 하나인 발광소자 패키지의 제조 방법.

## 청구항 28

상부 표면이 캐비티와 인접한 리세스를 포함하는 반도체 기판 서브마운트의 상기 캐비티 내에 발광소자를 배치하는 단계; 및

상기 발광소자로부터 방출된 광을 수용하고 과장변환하기 위하여, 상기 리세스 내에 그리고 상기 발광소자 상으로, 상기 서브마운트 상에 고상 과장변환 부재를 배치하는 단계를 포함하는 반도체 발광소자의 패키징 방법.

## 청구항 29

제 28 항에 있어서,

상기 고상 과장변환 부재는 과장변환 재료를 내부에 갖는 유리, 실리콘 및 경화된 에폭시 중 적어도 하나로 이루어진 경성(rigid) 과장변환 부재를 포함하는 반도체 발광소자의 패키징 방법.

## 청구항 30

제 29 항에 있어서,

상기 과장변환 재료는 형광체인 반도체 발광소자의 패키징 방법.

## 청구항 31

제 29 항에 있어서,

상기 발광소자는 발광 다이오드(LED)를 포함하는 반도체 발광소자의 패키징 방법.

## 청구항 32

제 29 항에 있어서,

상기 과장변환 부재는 상기 발광소자에 대향하는 그 표면 상에서 평평하고 볼록한 것 중 적어도 하나인 반도체 발광소자의 패키징 방법.

## 청구항 33

제 29 항에 있어서,

상기 서브마운트 상에 경성 과장변환 부재를 배치하는 단계 이전에, 그 과장변환 특성을 결정하기 위하여 상기

경성 파장변환 부재를 테스트하는 단계를 수행하는 반도체 발광소자의 패키징 방법.

#### 청구항 34

삭제

#### 청구항 35

삭제

#### 청구항 36

삭제

#### 청구항 37

삭제

#### 청구항 38

삭제

#### 청구항 39

삭제

### 명세서

#### 기술 분야

(관련 출원)

[0001] 본 출원은 2003년 12월 9일자로 출원된 "리세스된 서브마운트를 포함하는 LED 패키지(LED Package Including Recessed Submount)" 제하의 미국 임시특허출원 제60/528,054호(문서번호 제P0393호)를 우선권 주장의 기초로 하며, 상기 문헌의 개시 사항은 본 명세서에서 완전하게 개시된 것과 같이 참조로서 포함된다.

[0003] 본 발명은 반도체 발광소자 및 그 제조방법에 관한 것이며, 더욱 상세하게는, 반도체 발광소자용 패키징 및 패키징 방법에 관한 것이다.

#### 배경 기술

[0004] 반도체 발광소자는 다양한 광원 응용장치에 이용될 수 있음이 알려져 있다. 예를 들면, 발광 다이오드(또는 LEDs)는 충분한 전압이 인가되면 광을 생성할 수 있는 고상 전자소자(solid state electronic devices)로서 알려져 있다. 일반적으로, 발광 다이오드는 사파이어, 실리콘, 실리콘탄화물 및 갈륨비소화물 등과 같은 기판 상에 증착된 에피택셜층(epitaxial layer)에 형성된 p-n 접합을 포함한다. LED에 의하여 생성된 광의 파장 분포는 일반적으로 상기 p-n 접합이 형성되는 재료와 상기 소자의 광 생성 영역을 포함하는 얇은 에피택셜층의 구조에 의존한다.

[0005] 일반적으로, LED는 n-형 기판, 상기 n형 기판 상에 형성된 n-형 에피택셜 영역 및 상기 n-형 에피택셜 영역 상에 형성된 p-형 에피택셜 영역을 포함한다. 상기 소자에 전압을 쉽게 인가하기 위해서, 상기 소자의 p-형 영역(일반적으로 노출된 p-형 에피택셜층) 상에 애노드 오믹 콘택을 형성하고, 상기 소자의 n-형 영역(상기 기판 또는 노출된 n-형 에피택셜층) 상에는 캐소드 오믹 콘택을 형성할 수 있다. 그 결과, 상기 오믹 콘택들은 전자회로에 상기 LED를 접속하기 위한 콘택 노드를 제공할 수 있다.

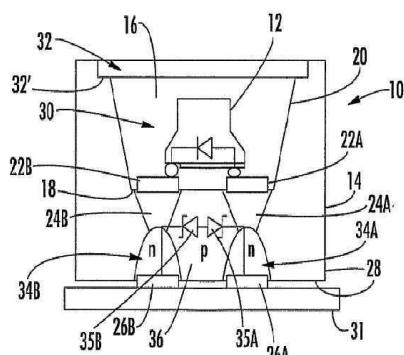

[0006] 도 1에 나타난 바와 같이, 종래의 LED(70)는 교대로 캐소드/애노드 리드(75A)에 접속될 수 있는 도전성/반사성 마운팅 컵(mounting cup; 73)을 포함할 수 있는 표준 패키지(72)에 패키징될 수 있다. 일반적으로, 상기 LED 칩(70)은 은 에폭시(silver epoxy)로 상기 컵 내에 마운팅(mounting)될 수 있다. 상기 LED 칩(70)의 애노드/캐소드는 애노드/캐소드 리드(75B)에 와이어본딩될 수 있다. 이 후, 상기 전체 패키지는 예를 들면, 투과성 에폭시(78)로 캡슐화될 수 있다. 백색-발광 LED칩용으로서, 인캡슐런트(encapsulant; 78)는 파장변환(wavelength converting) 형광체와 같은 파장변환 재료를 포함할 수 있다. 일반적인 백색 LED 응용장치에서는,

상기 칩(70)으로부터 방출되는 청색 광의 일부는 황색 광과 같은 더 긴 파장의 광을 방출시키도록 상기 파장변환 물질을 자극한다. 칩으로부터 방출된 "변환되지 않은" 청색 광은 상기 형광체로부터 방출된 더 긴 파장의 광과 결합하여 백색 광을 합성하고, 상기 백색 광이 패키지로부터 방출될 수 있다.

[0007] LED의 플립-칩 마운팅(Flip-chip mounting) 공정은 상기 서브마운트 기판 상에 거꾸로 상기 LED를 마운팅하는 단계를 포함한다. 이 후, 상기 투명 기판을 통하여 광이 추출되고 방출될 수 있다. 플립-칩 마운팅은 SiC계 LED들을 마운팅하기 위한 바람직한 기술일 수 있다. 일반적으로, SiC는 GaN 보다 더 큰 굴절률을 갖기 때문에, 상기 광방출 영역에서 생성된 광은 상기 GaN/SiC 계면에서 내부로 반사되지 않을 수 있다(즉, GaN-계 층의 내부로 반사되지 않을 수 있다). 당해 기술분야에서 공지된 소정의 칩-성형(chip-shaping) 기술을 채택하는 경우 SiC계 LED들의 플립-칩 마운팅은 개선된 광추출을 제공할 수 있다. 또한, SiC계 LED들의 플립-칩 패키징은 상기 칩의 특정 용도에 따라 바람직할 수 있는 개선된 열 추출(extraction)/발산(dissipation)과 같은 다른 이점을 제공할 수도 있다.

미리 형성된 형광성 판 LED 소자는 미국특허공개 제2002/0063520 A1호에 개시된다. 반도체 발광소자는 미국특허 제5,003,357호에 개시된다. 발광 다이오드 소자를 위하여 단일 와이어본딩이 가능하고 ESD 방지를 제공할 수 있는 발광 다이오드 소자는 미국특허 제6,642,550호에 개시된다.

[0008] 일반적으로, 종래의 백색 LED 패키지에서 부딪히는 일부 문제점들은 방출의 균일도와 상기 패키지에 의해서 생성된 광학 이미지의 크기와 관련된다. 종래의 패키지는 대형 광학 이미지 크기를 갖는 경향이 있으며, 이러한 광학 이미지 크기는 일반적으로 금속성 마운팅 컵의 크기의 함수이다. 또한, 상기 LED 칩의 크기와 비교되는 큰 면적에 걸쳐서 상기 파장변환 재료가 분포할 수 있기 때문에, 그리고, 상기 코팅 내의 파장변환 재료의 정확한 분포를 제어하는 것이 어려울 수 있기 때문에, 상기 광 출력의 균일성과 재현성을 확보하기가 어려울 수 있다.

### 발명의 상세한 설명

[0009] 본 발명의 실시예들은 반도체 발광소자의 패키징 방법을 제공한다. 상기 발광소자는 서브마운트의 캐비티(cavity) 내에 배치된다. 상기 발광소자로부터 방출된 광을 수용하고 파장변화시키기 위하여, 상기 발광소자의 상부로, 상기 서브마운트 상에 고상의 파장변환 부재(solid wavelength conversion member)가 배치된다. 상기 고상의 파장변환 부재는 파장변환 재료를 내부에 가지는 유리, 실리콘 및/또는 경화된 에폭시로 이루어진 강성(rigid) 파장변환 부재일 수 있다. 상기 파장변환 재료는 형광체일 수 있다. 상기 파장변환 부재는 상기 발광소자에 대향하는 표면 상에서 평평하거나 및/또는 오목할 수 있다. 상기 서브마운트 상에 상기 파장변환 부재를 배치하기 이전에, 그 파장변환 특성을 결정하기 위하여 상기 파장변환 부재를 테스트할 수 있다.

[0010] 본 발명의 다른 실시예들에서, 반도체 발광소자용 서브마운트는 내부에 상기 발광소자를 수용하도록 구성된 캐비티를 갖는 반도체 기판을 포함한다. 상기 캐비티 내의 제 1 본드 패드는 상기 캐비티 내에 수용된 발광소자의 제 1 노드에 결합되도록 배치된다. 상기 캐비티 내의 제 2 본드 패드는 내부에 배치된 발광소자의 제 2 노드에 결합되도록 배치된다. 상기 캐비티는 플로우(floor) 및 상기 플로우와 적어도 약 90°의 각을 이루는 측벽을 포함할 수 있다. 상기 캐비티의 플로우 상에 상기 제 1 및 제 2 본드 패드가 배치될 수 있다.

[0011] 본 발명의 또 다른 실시예에서, 상기 캐비티는 상기 플로우로부터 적어도 그 내부에 수용되는 상기 발광소자의 높이를 갖는 상기 반도체 기판의 상부 표면까지의 높이를 갖는다. 상기 캐비티에 인접하는 상기 반도체 기판의 상부 표면에 수용 리세스(receiving recess)가 제공될 수 있다. 상기 리세스는 상기 캐비티 내의 발광소자로부터 방출되는 광을 수용하도록 고상의 파장변환 부재를 수용하고 캐비티 상으로 상기 파장변환 부재를 배치할 수 있도록 구성될 수 있다. 상기 캐비티의 플로우 및/또는 측벽 상에 반사성 재료 코팅을 제공할 수 있다.

[0012] 본 발명의 다른 실시예에서, 상기 반도체 기판은 상기 기판을 통하여 상기 제 1 본드 패드로부터 상기 반도체 기판의 외부 표면까지 연장된 제 1 도전성 경로를 포함할 수 있다. 제 2 도전성 경로는 상기 기판을 통하여 상기 제 2 본드 패드로부터 상기 기판의 외부 표면까지 연장된다. 상기 제 1 및 제 2 도전성 경로는 모두 상기 반도체 기판의 외부 표면의 하부측까지 연장될 수 있다. 상기 반도체 기판의 외부 표면 상에, 제 1 외부 마운팅 패드 및 제 2 외부 마운팅 패드가 배치될 수 있다. 상기 제 1 도전성 경로는 상기 제 1 외부 마운팅 패드까지 연장될 수 있으며, 상기 제 2 도전성 경로는 상기 제 2 외부 마운팅 패드까지 연장될 수 있다.

[0013] 본 발명의 또 다른 실시예에서, 적분 대향형 제너 다이오드 접합(integral opposing zener diode junctions)은 상기 캐비티 내에 마운팅된 발광소자에 대하여 정전기 방전(electro-static discharge; ESD) 방지를 제공하기 위하여, 상기 제 1 및 제 2 도전성 경로를 결합한다. 상기 대향형 제너 다이오드 접합은 상기 제 1 도전성 경

로의 적어도 일부 및 제 2 도전성 경로의 적어도 일부를 형성하는 반도체 재료로 이루어진 제 1 도전형 도핑된 영역과 그들 사이에 개재된 반도체 재료로 이루어진 반대 도전형 도핑된 영역을 포함한다. 상기 제 1 도전형은 n-형이고 상기 반대 도전형은 p-형일 수 있다. 상기 n-형 도핑된 영역은 상기 제 1 및 제 2 본드 패드 또는 상기 제 1 및 제 2 외부 마운팅 패드 중 각각 하나와 접촉될 수 있다. 상기 제 1 및 제 2 도전성 경로는 각각의 제 1형 도핑된 영역으로부터 연장된 각각 금속으로 매큅된 비아부를 더 포함할 수 있다.

[0014] 본 발명의 다른 실시예에서, 상기한 바와 같은 서브마운트를 포함하는 발광소자 패키지는 상기 발광소자와 상기 과장변환 부재 사이의 상기 캐비티 내에 인캡슐런트 재료를 더 포함할 수 있다. 상기 인캡슐런트 재료는 적어도 약 1.5의 굴절률을 가질 수 있다.

[0015] 본 발명의 또 다른 실시예에서, 발광소자 패키지는 내부에 캐비티를 가지는 반도체 기판을 포함한다. 상기 캐비티는 플로우 및 상기 플로우와 적어도 약 90°의 각을 이루는 측벽을 가질 수 있다. 상기 캐비티 내의 제 1 본드 패드는 상기 캐비티에 수용되는 발광소자의 제 1 노드와 결합되도록 배치되고, 상기 캐비티의 제 2 본드 패드는 내부에 배치된 발광소자의 제 2 노드에 결합되도록 배치된다. 제 1 도전성 경로는 상기 기판을 통하여 상기 제 1 본드 패드로부터 상기 반도체 기판의 외부 표면까지 연장되며, 제 2 도전성 경로는 상기 기판을 통하여 상기 제 2 본드 패드로부터 상기 기판의 외부 표면까지 연장된다. 상기 캐비티에 발광소자가 수용되며, 발광소자는 상기 제 1 및 제 2 본드 패드와 결합된 노드들을 구비한다. 적분 대향형 제너 다이오드 접합은 상기 발광소자에 대한 정전기 방전(ESD)을 방지하기 위하여 상기 제 1 및 제 2 도전성 경로를 결합된다. 상기 발광소자로부터 방출된 광을 수용하고 과장변환시키기 위하여, 상기 발광소자 상으로, 상기 반도체 기판의 상부 표면 상에 고상의 과장변환 부재가 배치된다.

[0016] 본 발명의 다른 실시예에서, 반도체 발광소자용 서브마운트를 형성하는 방법은 반도체 기판에 발광소자를 수용하도록 구성된 캐비티를 형성하는 단계를 포함한다. 상기 캐비티는 플로우와 상기 플로우에 대하여 적어도 약 90°의 각을 이루는 측벽을 갖는다. 상기 캐비티로부터 상기 기판의 외부 표면까지 연장된 제 1 도전성 경로가 형성되고, 상기 캐비티로부터 상기 기판의 외부 표면까지 연장된 제 2 도전성 경로가 형성된다. 상기 캐비티 내에서, 그 내부에 형성된 상기 제 1 도전성 경로의 단부 상에 제 1 본드 패드가 형성되고, 상기 캐비티 내에서 그 내부에 형성된 상기 제 2 도전성 경로의 단부 상에 제 2 본드 패드가 형성된다.

[0017] 본 발명의 또 다른 실시예에서, 서브마운트를 사용하여 상기 캐비티 내에 상기 제 1 본드 패드에 결합된 발광소자의 제 1 노드 및 상기 제 2 본드 패드에 결합된 상기 발광소자의 제 2 노드를 가지는 상기 발광소자를 배치함으로써, 상기 발광소자 패키지가 형성된다. 상기 발광소자로부터 방출된 광을 수용하고 과장변환시키기 위하여, 상기 발광소자 상으로 상기 기판 상에 고상의 과장변환 소자가 배치된다. 상기 고상의 과장변환 부재는 그 과장변환 특성을 결정하기 위하여 상기 기판 상에 배치하는 단계 이전에 테스트될 수 있다.

## 실 시 예

[0024] 이하, 본 발명의 실시예가 도시된 첨부된 도면을 참조하여, 본 발명을 더욱 완전하게 개시한다. 그러나, 본 발명은 다양한 형태로 실시될 수 있으며, 본 명세서에서 상술한 실시예에 한정하는 것으로서 해석되어서는 아니된다. 이들 실시예는 본 개시를 더욱 충실히 완전하게 하도록 하고, 당업자에게 본 발명의 사상을 완전하게 전달하기 위하여 제공되는 것이다. 본 도면에서, 층들 및 영역들의 크기 및 상대적 크기는 명확성을 위하여 과장될 수 있다. 명세서 전체에 걸쳐 동일한 참조부호는 동일한 구성요소를 지칭한다.

[0025] 층, 영역 또는 기판과 같은 구성요소가 또 다른 구성요소 "～상에(on)" 또는 "～에 결합된(coupled to)" 것으로서 언급되는 경우에, 그것은 직접적으로(directly) 상기 또 다른 구성요소 상에, 또는 다른 구성요소에 결합될 수 있으며, 중간 구성요소가 개재될 수도 있다. 표면과 같은 구성 요소의 일부가 "내부에(inner)"라고 언급된다면, 그것은 그 구성요소의 다른 부분보다 상기 소자의 외부로부터 더 멀리 존재한다. 또한, 본 명세서에서, "～하부에(beneath)" 또는 "～상부에 배치된다(overlie)"와 같은 상대적인 용어는 본 도면들에서 도시된 바와 같은 기판 또는 기저층(base layer)과 대비되는 또 다른 층 또는 영역에 대한 어느 층의 관계를 설명하기 위하여 사용될 수 있다. 이들 용어는 본 도면에서 설명된 방향뿐만 아니라 상기 소자의 다른 방향들도 포함하도록 사용된 것임은 자명하다. "직접적으로"라는 용어는 어떠한 중간 구성요소가 없는 것을 의미한다. 본 명세서에서 사용된 바와 같이, "및/또는"이라는 용어는 하나 이상의 열거된 관련 항목 중 어느 하나 및 모든 조합을 포함한다.

[0026] 본 명세서에서 제 1, 제 2 등의 용어가 다양한 구성요소, 부품, 영역, 층들 및/또는 부분들(sections)을 설명하기 위하여 사용되지만, 이들 구성요소, 부품, 영역, 층들 및/또는 부분들은 이들 용어에 의해 한정되어서는 안

됨은 자명하다. 이들 용어는 하나의 구성요소, 부품, 영역, 층 또는 부분을 다른 영역, 층 또는 부분과 구별하기 위하여만 사용된다. 따라서, 이하 상술할 제 1 구성요소, 부품, 영역, 층 또는 부분은 본 발명의 가르침으로부터 벗어나지 않고 제 2 구성요소, 부품, 영역, 층 또는 부분을 지칭할 수도 있다.

[0027] 또한, 당업자에게 자명한 바와 같이, 반도체 웨이퍼 및 다이싱된(diced) 칩과 관련하여 본 발명이 기술될 때, 이러한 칩들은 임의의 크기로 다이싱될 수 있다. 따라서, 본 발명은 첨부한 도면들에 도시된 상대적 크기 및 간격에 한정되지 아니한다. 또한, 본 도면의 특정 형상은 도면의 명확화와 설명상의 편의를 위하여 과장된 크기로 나타낼 수도 있다.

[0028] 본 명세서에서 사용된 바와 같이, "반도체 발광소자"라는 용어는 발광 다이오드, 레이저 다이오드 및/또는 하나 이상의 반도체 층, 기판 및 하나 이상의 콘택층을 포함하는 다른 반도체 소자를 포함할 수 있다. 상기 반도체 층은 실리콘, 실리콘탄화물, 갈륨질화물 및/또는 다른 반도체 재료를 포함하며, 상기 기판은 사파이어, 실리콘, 실리콘탄화물 및/또는 다른 마이크로전자 기판을 포함하며, 상기 콘택층은 금속 및/또는 다른 도전층을 포함한다. 일부 실시예에서, 자외선, 청색 및/또는 녹색 발광 다이오드(LEDs)가 제공될 수도 있다.

[0029] 이하, 본 발명의 일부 실시예에 대하여 설명에 대한 이해가 쉽도록 일반적으로 실리콘 탄화물계 기판 상의 갈륨 질화물계 발광 다이오드와 관련하여 상술한다. 그러나, 당업자에게 있어서 본 발명의 다른 실시예가 기판과 에피택설층들의 다른 다양한 조합으로도 뒷받침될 수 있음을 자명하다. 예를 들면, 조합들은 GAP 기판 상의 AlGaInP 다이오드; GaAs 기판 상의 InGaAs 다이오드; GaAs 기판 상의 AlGaAs 다이오드; SiC 또는 사파이어 ( $\text{Al}_2\text{O}_3$ ) 기판 상의 SiC 다이오드; 및/또는 갈륨질화물, 실리콘탄화물, 알루미늄 질화물, 사파이어, 아연산화물 및/또는 다른 기판 상의 질화물계 다이오드를 포함할 수 있다.

[0030] 따라서, 예를 들면, 상기 반도체 발광소자는 노스캐롤라이나 더햄 소재의 크리사(Cree, Inc. of Durham, North Carolina)에 의하여 제조 판매된 소자와 같은, 실리콘탄화물계 기판 상에 제조된 갈륨질화물계 LED 또는 레이저가 될 수도 있다. 본 발명은 미국 특허 제6,201,262호; 제6,187,606호; 제6,120,600호; 제5,912,477호; 제5,739,554호; 제5,631,190호; 제5,604,135호; 제5,523,589호; 제5,416,342호; 제5,393,993호; 제5,338,944호; 제5,210,051호; 제5,027,168호; 제5,027,168호; 제4,966,862호; 및/또는 제4,918,497호에 개시된 바와 같은 LED들 및/또는 레이저용으로 사용하기에 적합할 수 있으며, 상기 문현의 개시 사항은 본 명세에 완전히 기재된 것과 같이 참조로서 본 명세서에 포함된다. 다른 적합한 LED들 및/또는 레이저들은 공개된 "광추출을 위한 변형을 포함하는 발광 다이오드 및 그 제조 방법(Light Emitting Diodes Including Modifications for Light Extraction and Manufacturing Methods Therfor)" 제하의 미국특허공보 제US2002/0123164 A1호뿐만 아니라, 2003년 1월 9일자로 공개된 "양자 우물 및 초격자를 갖는 3족 질화물계 발광 다이오드의 구조, 3족 질화물계 양자 우물의 구조 및 3족 질화물계 초격자의 구조(Group III Nitride Based Light Emitting Diode Structures With a Quantum Well and Superlattice, Group III Nitride Based Quantum Well Structures and Group III Nitride Based Superlattice Structures)" 제하의 미국특허공보 제US2003/0006418 A1호에 개시된다. 또한, 본 명세서에 완전하게 개시된 것과 참조로서 포함되어 있는 2003년 9월 9일자로 출원된 "테이퍼형 측벽을 포함하는 형광체가 코팅된 발광 다이오드 및 그 제조 방법(Phosphor-Coated Light Emitting Diodes Including Tapered Sidewalls and Fabrication Methods Therefor)" 제하의 미국출원 제10/659,241호에 개시된 바와 같은 형광체로 코팅된 LED들도 본 발명의 실시예에서 이용될 수 있다. 상기 LED들 및/또는 레이저들은 상기 기판을 통하여 광방출이 일어날 수 있도록 동작되는 구성을 가질 수 있다. 이러한 실시예에서, 상기 기판은 예를 들면 위에서 언급된 미국공개공보 제US 2002/0123164 A1호에서 개시된 바와 같이 상기 소자의 광출력을 개선하도록 패터닝될 수 있다.

[0031] 본 발명의 일부 실시예에서, 발광 다이오드(LED) 칩을 마운팅하기 위한 패키지는 LED 칩을 수용하기 위한 캐비티를 내부에 포함하는 반도체 서브마운트를 포함한다. 상기 캐비티는 플로우 및 상기 플로우와 적어도 90°의 각도를 갖는 측벽을 포함할 수 있다. 또한, 상기 패키지는 상기 캐비티의 플로우 상에 LED의 애노드와 캐소드 콘택을 부착하기 위한 적어도 애노드 및 캐소드 본드 패드를 더 포함할 수 있다. 상기 캐비티의 깊이는 내부에 마운팅될 LED 칩의 높이보다 약간 더 클 수 있다. 도전성 비아 커넥션이 상기 기판을 통해서 연장될 수 있으며, 상기 서브마운트의 하나 이상의 외부 측벽 상에 마운팅될 수 있는 각각의 외부 마운팅 패드에 상기 애노드와 캐소드 본드 패드를 전기적으로 연결할 수 있다. 특히, 상기 패키지가 특성상 절연성 및/또는 반절연성이 경우에 이러한 도전성 비아 커넥션이 사용될 수 있다. 일부 실시예에서, 상기 서브마운트의 하부측 상에 상기 외부 마운팅 패드가 형성된다. 상기 캐비티의 플로우 및 측벽 표면들은 반사율을 증가시키기 위하여 은과 같은 반사성 재료로 코팅될 수 있다.

- [0032] 본 발명의 일부 실시예에서, 광학적으로 깨끗한 인캡슐런트가 상기 캐비티 내에 마운팅된 LED 칩을 둘러싸고 보호할 수 있다. 상기 인캡슐런트는 약 1.5 이상의 굴절률을 가질 수 있으며, 이것은 광추출을 개선하기 위하여 상기 칩/인캡슐런트 경계에서의 반사를 감소시킬 수 있다. 상기 서브마운트의 외부 표면 상에 도금 또는 다른 방법에 의하여 외부 마운팅 패드가 형성될 수 있다.

- [0033] 일부 실시예에서 경성 광장변환 부재는 유리, 실리콘, 에폭시 또는 내장된(immersed) 광장변환 재료를 갖는 다른 광학적으로 깨끗한 재료일 수 있으며, 광장변환된 광 방출을 제공하도록 상기 캐비티로부터 나온 광이 상기 광장변환 부재를 경과하고 내부의 상기 광장변환 재료와 상호작용을 하도록 상기 LED 칩을 덮어 상기 캐비티를 피복할 수 있다. 상기 경성 광장변환 부재는 평평하거나 곡선형일 수 있으며, 소정의 광투과 패턴(optical transmission pattern)을 갖는 얇은 렌즈를 형성하도록 성형될 수 있다. 예를 들면, 상기 광장변환 부재는 특정 LED 칩 형상의 상기 광방출 패턴(optical emission pattern)과 정합(matching)되는 광투과 패턴을 가질 수 있다.

- [0034] 본 발명의 일부 실시예에서, 상기 서브마운트는 제 1 및 제 2 과도핑된(heavily doped) n-형 영역 및 상기 제 1 및 제 2 n-형 영역과 각각 제너 접합을 형성하는 과도핑된 p-형 영역을 포함한다. 상기 애노드 본드 패드는 상기 제 1 n-형 영역과 전기적으로 콘택되는 반면, 상기 캐소드 콘택은 상기 제 2 n-형 영역과 콘택된다. 그 결과, 상기 LED 칩의 상기 애노드 및 캐소드 리드는 한쌍의 대향형 제너 다이오드 접합에 의하여 연결될 수 있으며, 이것은 상기 마운팅된 LED 칩에 대하여 정전기 방전(ESD)을 방지할 수 있다. 일부 실시예에서, 상기 서브마운트 내의 제 1 및 제 2 과도핑된 n-형 영역은 p-형 기판 내로의 n-형 도편트의 주입 또는 웰의 확산에 의하여 형성될 수 있다. 금속으로 도금되거나 금속으로 매립된 비아는 외부 연결을 위하여 상기 서브마운트의 대향 표면에 상기 웰을 연결시킨다.

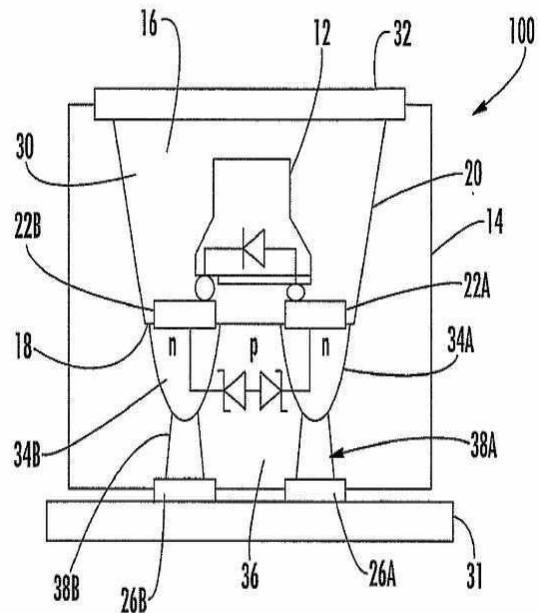

- [0035] 이하, 도 2-7에 도시된 다양한 실시예와 관련하여 본 발명의 실시예들을 더욱 상세히 설명하기로 한다. 더욱 상세히는, 발광소자 패키지 및 이를 위한 서브마운트에 관한 일부 실시예가 도 2-5에 도시된다.

- [0036] 상기 배경기술에서, 종래의 "글로부의 상부(glob top)" 백색 고상 이미터(즉, 에폭시로 이루어진 글로브로서 종래의 마운팅된 LED 칩의 상부로 광장변환 재료가 적용된 소자)에 있어서, 상기 패키징된 소자에 의해서 생성된 백색 이미지의 크기는 상기 컨버터를 한정하는 패키지 리플렉터(reflector)의 상기 광학적 캐비티에 의해서 정의된다. 본 발명의 일부 실시예는 상기 백색 컨버터를 상기 칩에 더욱 가깝게 배치할 수 있도록 하여, 가능한 한 그 이미지 크기를 감소시킨다. 이것은 상기 외부 전극 패드에 대한 상기 비아 전극 커넥터에 의해서 가능하며, 그에 따라 상기 광학적 캐비티 내부에 종래의 와이어본드 및 와이어본드 패드의 필요성을 제거시킬 수 있다. 또한, 상기 칩 수준에서 상기 백색 컨버터를 형성할 수 있어서, 다양한 패키징 플랫폼에서 채용될 수 있는 연성 백색 이미터 패키지를 제공할 수 있다.

- [0037] 기존의 코팅된 백색 칩 솔루션과 비교하여, 본 발명의 일부 실시예는 비교적 고가인 LED 칩과 결합되기 전에 올바른 색상 포인트를 제공하는지를 보장하기 위해서 사전에 걸려질 수 있는 미리 제조된 백색 컨버터를 사용할 수 있는 이점을 제공할 수 있다. 또한, 미리 제조된 광장변환 부재는 예를 들면, 특정 발광소자의 (상기 특정 발광소자를 사전에 테스팅함으로써 결정되는 주파수등과 같은) 출력 및 상기 패키징된 발광소자의 소정의 출력과 정합될 수 있다. 그에 따라, 저비용과 개선된 수율로 재현성있고 조절된 백색 또는 다른 광방출 소자를 제공할 수 있는 칩 패키지를 제조될 수 있다.

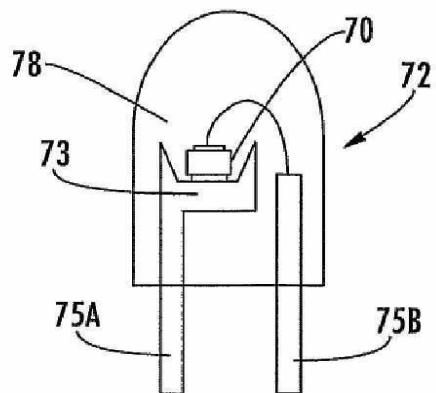

- [0038] 이하, 도 2의 단면도를 참조하여, 본 발명의 일부 실시예에 따른 서브마운트를 포함하는 반도체 광방출 소자 패키지를 설명한다. 도 2에 도시된 바와 같이, 발광 다이오드(LED) 칩(12)을 마운팅하기 위해 패키지(10)가 제공된다. 도 2에 도시된 본 실시예의 패키지(10)는 LED 칩(12)과 같은 발광소자를 수용하도록 구성된 캐비티(16)를 내부에 갖는 반도체 서브마운트/기판(14)을 포함한다. 캐비티(16)는 플로우(18) 및 측벽(20)을 포함할 수 있다. 측벽(20)은 상기 플로우와 적어도 약 90°의 각을 이룰 수 있다. 또한, 캐비티(16)는 플로우(18)로부터 예를 들면 적어도 내부에 마운팅될 LED 칩(12) 또는 다른 발광소자의 높이보다 약간 더 큰 높이의 반도체 기판(14)의 상부 표면까지의 높이(깊이)를 가질 수 있다.

- [0039] 또한, 도 2에 도시된 실시예에 대해서, 패키지(10)는 내부의 상기 LED(12) 또는 다른 발광소자의 애노드와 캐소드 콘택 노드를 붙이기 위하여, 상기 캐비티(16)의 상기 플로우(18) 상에 배치된 애노드 본드 패드(22A) 및 캐소드 본드 패드(22B)를 포함한다. 본 발명의 일부 실시예에 따른 본드 패드(22A, 22B)를 사용함으로써, 와이어본드가 필요하지 않아 상기 칩 및/또는 패키지의 크기를 감소시킬 수 있는 서브마운트 하이브리드가 제조될 수 있다.

- [0040] 일부 실시예에서, 상기 반도체 서브마운트/기판(14)은 실리콘이다. 식각 및/또는 다른 적합한 방법에 의하여 상기 실리콘 서브마운트 내에 캐비티(16)가 형성될 수 있다. 당해 반도체 기술분야에서 캐비티(16)와 같은 리세스를 형성하기 위한 실리콘 웨이퍼의 포로리소그래피, 도편트의 확산 및 주입, 제너 다이오드 접합의 형성 및 내부에 도전성 비아의 형성을 포함하는 실리콘 공정 기술은 공지되었으므로, 본 발명에 특별히 관련된 특징들을 제외하고 본 명세서에서는 더 이상 설명하지 않는다. 본 명세서에서 실시예들의 개시가 일반적으로 실리콘을 참조하여 제공되지만, 서브마운트/기판(14)용으로 다른 반도체 재료가 사용될 수 있다.

- [0041] 본 발명의 일부 실시예에서는, 비아 커넥션(24A, 24B) 및 도핑된 영역(34A, 34B)을 포함하는 도전성 경로는 서브마운트/기판(14)을 통하여 또는 그 내부로 연장되고, 각각의 외부 마운팅 패드(26A, 26B)에 애노드(24A) 및 캐소드(24B) 본드 패드를 전기적으로 연결한다. 외부 마운팅 패드(26A, 26B)는 서브마운트/기판(14)의 외부 표면(28)을 한정하는 하나 이상의 벽들 상에 마운팅될 수 있다. 상기 전기적 비아는 주입, 확산 및 도금 또는 다른 방법에 의하여 형성된 금속성 비아일 수 있다. 금속성 비아는 회로 보드 또는 히트 싱크 조립체(heat sink assembly)에 열발산에 대한 저항을 감소시키는 추가적인 이점을 가질 수 있다. 본 발명의 일부 실시예에서, 서브마운트/기판(14)의 외부 표면(28)의 하부측 상에 외부 마운팅 패드(26A, 26B)가 형성된다. 외부 마운팅 패드(26A, 26B)는 예를 들면 도금법 또는 다른 방법에 의하여 상기 서브마운트의 외부 표면 상에 형성될 수 있다.

- [0042] 캐비티(16)의 플로우(18) 및 측벽(20) 표면은 캐비티(16)의 반사율을 증가시키기 위하여, 은과 같은 반사성 재료로 코팅될 수 있다. 광학적으로 깨끗한 인캡슐런트(30)는 캐비티(16) 내의 LED 칩(12)과 같은 마운팅된 발광소자를 둘러싸고/또는 보호할 수 있다. 본 발명의 일부 실시예에서, 광추출을 개선하도록 칩/인캡슐런트 경계에서 반사를 감소시키기 위하여, 인캡슐런트(30)는 약 1.5 이상의 굴절률을 가질 수 있다.

- [0043] 파장변환 부재(32)는 발광소자/LED 칩(12) 상으로, 서브마운트/기판(14)의 상부 표면 상에 배치된다. 파장변환 부재(32)는 캐비티(16)에 인접한 반도체 서브마운트/기판(14)의 상부 표면의 리세스(32')에 배치될 수 있다. 파장변환 부재(32)는 형광체와 같은 내장된 파장변환 재료를 가지는 유리, 실리콘, 경화된 에폭시 및/또는 다른 광학적으로 깨끗한 재료 중 하나 이상일 수 있다. 파장변환 부재(32)는 캐비티(16)를 피복하여, 캐비티(16)로부터 방출된 광이 파장변환 부재(32)를 통과하고 내부에서 파장변환 재료와 상호작용을 하여, 예를 들면 합성된 백색 광과 같은 파장이 변환된 광 방출을 제공한다.

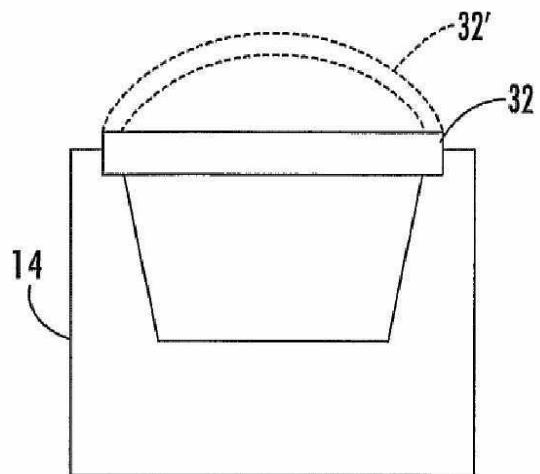

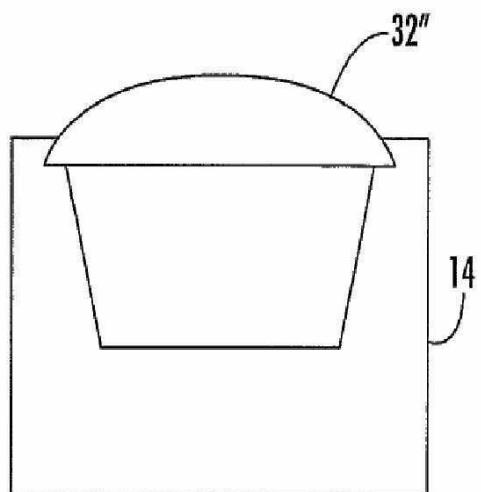

- [0044] 본 발명의 일부 실시예에서, 파장변환 부재(32)는 고상 부재이다. 특히, 이러한 실시예에서 파장변환 부재(32, 32', 32'')는 경성, 반경성 또는 연성 고상 부재일 수 있다. 도 3A 및 3B에 도시된 바와 같이, 파장변환 부재(32, 32', 32'')는 평평한 단면(32)을 가질 수 있으며, 또한, 소정의 광 투과 패턴(32'')을 갖는 얇은 렌즈를 형성하기 위하여 곡선 형상(32')이 형성될 수도 있다. 예를 들면, 파장변환 부재는 특정 LED 칩의 광방출 패턴과 정합되거나, 소정의 근거리(near)- 또는 원거리(far)-필드 광학 패턴(field optical pattern)을 형성하도록 성형된 광투과 패턴을 가질 수 있다. 파장변환 부재는 평판 형상(도 3a의 32 참조), 곡선 형상(32' 참조) 및/또는 볼록 형상(도 3b의 32'') 및/또는 발광소자(12)에 대향되는 상부 및/또는 하부 표면 상에 오목 형상을 가질 수 있다. 또한, 상기 파장변환 부재는 증착되거나 다른 방식으로 상기 인캡슐런트 내에 삽입된(embedded) 형광체막을 포함할 수 있다.

- [0045] 본 발명의 일부 실시예에서 파장변환 부재(32)는 예를 들면, 스크린 인쇄(screen printing), 잉크젯 인쇄(ink jet printing) 및 또는 균일한 몰딩 및 절단과 같은 저비용의 대면적 제조 기술을 이용하여, 미리 제조되고, 상기 서브마운트와 분리된 것일 수 있다. 또한, 파장변환 부재(32)는 서브마운트/기판(14) 상에 배치하기 전에, 광방출의 균일성을 개선하기 위하여 개별적으로 또는 별크 시트(bulk sheet) 상태로 몰딩되고 테스트될 수 있다. 파장변환 부재(32)를 미리 제조하고/또는 테스트하는 것은 수율 등, 특히 다중 형광체를 포함하는 파장변환 부재를 제조하는데 있어서 이점을 제공할 수 있다.

- [0046] 다시, 도 2를 참조하면, 본 발명의 일부 실시예에서, 서브마운트/기판(14)은 제 1 및 제 2 파도핑된 영역(34A, 34B)를 포함할 수 있다. 파도핑된 p-형 영역(36)은 제 1 및 제 2 n-형 영역(34A, 34B)과 함께 개념적으로 도시된 제너 접합(35A, 35B)을 형성할 수 있다. 그 제조 방법에 따라서, 접합은 수평으로 또는 수직으로 형성될 수 있다. 애노드 본드 패드(22A)는 제 1 n-형 영역(34A)과 전기적으로 콘택될 수 있으며, 반면에, 캐소드 본드 패드(22B)는 제 2 n-형 영역(34B)과 전기적으로 콘택될 수 있다. 그 결과, 캐비티(16) 내의 발광소자(12)의 애노드 및 캐소드 리드 노드들은 마운팅된 발광소자/LED 칩(12)에 대하여 함께 정전기 방전(ESD)을 방지할 수 있는 (도 2에 개념적으로 도시된) 한쌍의 대향형 제너 다이오드 접합에 의해서 연결될 수 있다. 또한, 도 2에서 도시된 바와 같이, 패키지(10)는 예를 들면 종래의 방법에 의하여 기판(31) 상에 마운팅될 수 있다. 기판(31)은 예를 들면 개선된 열발산을 제공하는 인쇄회로보드 또는 금속코어인쇄회로보드일 수 있다.

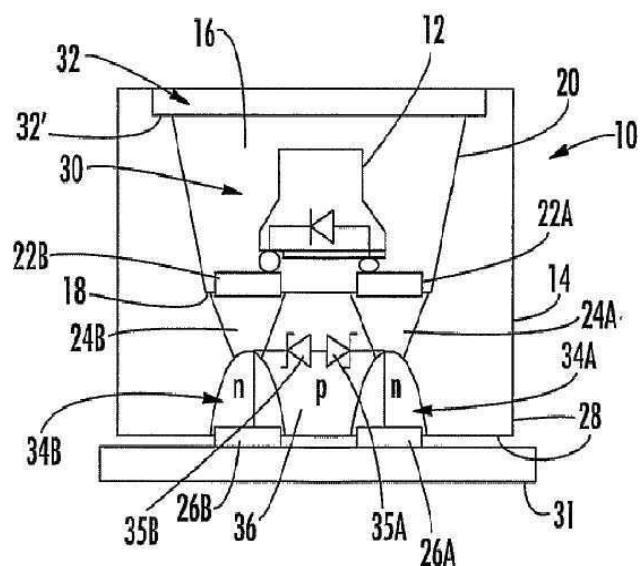

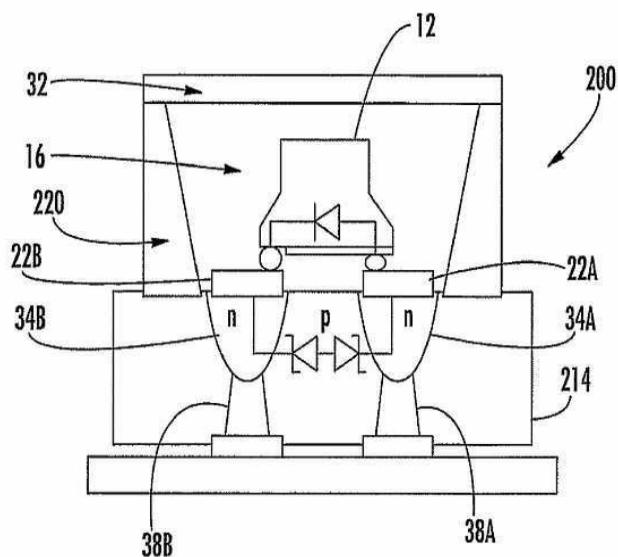

- [0047] 이하, 도 4를 참조하여 본 발명의 또 다른 실시예에 대하여 설명한다. 도 4에 도시된 바에 따르면, 패키지(100)의 서브마운트/기판(14) 내의 제 1 및 제 2 과도평된 n-형 영역(34A, 34B)은 예를 들면 p-형 기판 내로 n-형 도편트의 주입 또는 웰의 확산에 의하여 제조될 수 있다. 금속 도금된 비아(38A, 38B)는 상기 웰을 서브마운트/기판(14)의 대향 표면에 연결하여, 외부 연결을 위해 서브마운트/기판(14)의 외부 표면으로 제 1 및 제 2 도전성 경로를 완성할 수 있다. 또한, 이것은 상기 LED와 열발산 부재(햇 싱크, 금속코어 인쇄회로기판 등) 사이에서 열저항을 감소시킬 수 있다.

- [0048] 본드 패드(22A, 22B) 및 마운팅 패드(26A, 26B)는 일반적으로, p-형 영역(36)(또는 상호 사이에)이 아닌, n-형 영역(34A, 34B)과 각각 직접 전기적으로 콘택될 수 있다. 만약 이와 같지 않으면, LED 칩(12) 또는 상기 삽입된 제너 다이오드 접합(35A, 35B)의 애노드 및 캐소드 연결 노드의 단락이 초래될 수 있다. 따라서, 예를 들면, 패드(26A, 26B)와 반도체 기판의 상기 p-형 영역 사이에 절연 영역이 배치되거나, 패드(26A, 26B)는 상기 p-형 영역과 중첩되지 않도록 크기가 제한될 수도 있다. 본 발명의 일부 실시예에서, 정전기 방전(ESD) 방지 기능이 요구되지 않는 경우처럼, 상기 서브마운트는 반-절연 반도체, 세라믹 또는 유사한 재료와 같은 절연성 재료로 제조될 수 있다.

- [0049] 이하, 도 5를 참조하여 본 발명의 또 다른 실시예를 설명한다. 도 5에 도시된 본 발명의 실시예에서, 패키지(200)는 광 깔때기(light funnel; 220)가 상부에 마운팅되는 평판형 기판(214)을 포함할 수 있다. 광 깔때기(220)에 입사되는 광이, 광 깔때기(220)에 의하여 한정되는 캐비티(16)의 상부로 배치된 파장변환 부재(32)를 향하여 내부로 반사될 수 있도록, 광 깔때기(220)는 반사성 고상 재료 또는 내부에 배치된 인캡슐런트(16)의 굴절률보다 작은 굴절률을 갖는 투명한 재료로 이루어질 수 있다.

- [0050] 본 발명의 실시예는 예를 들면, 포화된 색상 및/또는 백색 LED, 패키지를 제공하기에 적합할 수 있다. 특히, 본 발명의 일부 실시예는 소형 풋프린트(footprint)를 갖는 백색 발광 패키지를 이용하는 칩-온-보드 조립체용 및 (예를 들면 웨이브가이드로 커플링하기 위한 또는 소형 화소 표시장치를 위하여) 소형 이미터 크기가 요구되는 다른 백색 광 응용장치용으로서 사용될 수 있다. 상술한 바와 같이, 본 발명의 일부 실시예는 반도체 발광 소자로부터 방출된 광을 수용하고 파장을 변환시키기 위하여, 상기 발광소자 상으로, 상기 서브마운트 상에 배치된 고상 파장변환 부재를 구비하는, 상기 서브마운트의 캐비티 내의 상기 반도체 발광소자의 패키징을 제공한다.

- [0051] 본 발명은 p-형 도평된 기판 내의 n-형 도평된 영역에 의해 형성된 제너 다이오드 접합을 포함하는 실시예에 관하여 설명되고 있지만, 본 발명의 다른 실시예에서는 n-형 도평된 기판 내에 p-형 도평된 영역이 제공될 수 있음을 자명하다. 본 발명의 또 다른 실시예는 기판 내에 제너 다이오드 접합을 포함할 필요가 없으며, 외부 회로에 대한 전기적 연결은 상기 기판(14)을 통하여 형성된 도전성 비아에 의한 것과 같이 다른 방법에 의하여 제공될 수 있다.

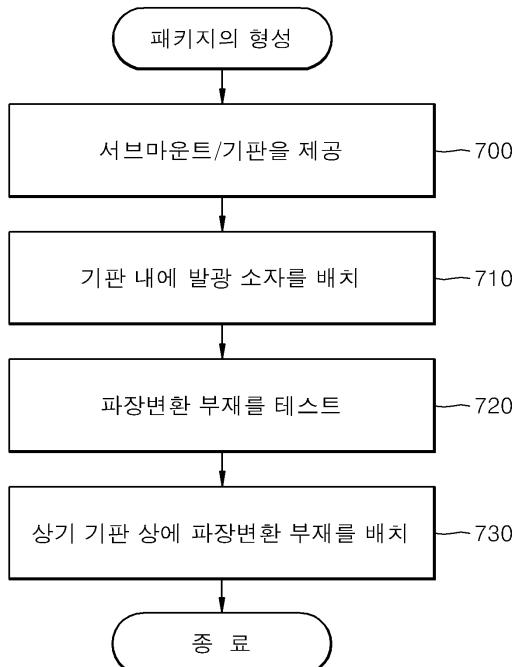

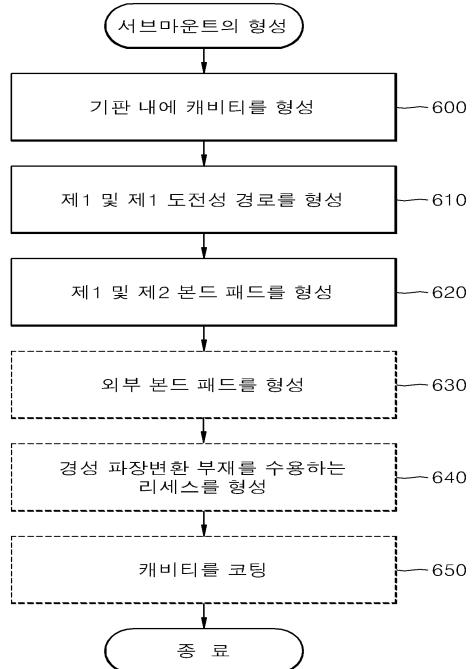

- [0052] 이하, 도 6의 순서도를 참조하여, 반도체 기판을 사용하여 반도체 발광소자용 서브마운트를 형성하는 방법에 대한 특정 실시예를 더욱 상세히 설명한다. 도 6에 도시된 바와 같이, 공정은 반도체 기판 내에 발광소자를 수용하도록 구성된 캐비티를 형성함으로써 시작된다(600). 상기 캐비티는 플로우 및 측벽을 포함할 수 있으며, 상기 측벽은 상기 플로우와 적어도 약 90°의 각을 이룰 수 있다. 상기 기판 내에 상기 캐비티로부터 상기 기판의 외부 표면으로 연장된 제 1 및 제 2 도전성 경로를 형성한다(610). 제 1 본드 패드는 상기 제 1 도전성 경로의 단부 상의 캐비티 내에 형성되고, 제 2 본드 패드는 제 2 도전성 경로의 단부 상의 캐비티 내에 형성된다(620).

- [0053] 이하, 도 6을 참조하여 더 설명되는 바와 같이, 본 발명의 특정 실시예에 따른 추가적 공정을 수행할 수 있다. 상기 기판의 외부 표면 상에 각각의 도전성 경로의 단부에 외부 본드 패드를 형성할 수 있다(630). 또한, 상기 반도체 기판의 상부 표면 상에 경성 파장변환 부재를 수용하도록 구성된 리세스를 형성할 수 있다(640). 본 발명의 일부 실시예에서, 플로우 및/또는 측벽을 포함하는 상기 캐비티의 내부 표면을 반사성 재료로 코팅한다(650).

- [0054] 이하, 도 7의 순서도를 참조하여, 본 발명의 일부 실시예에 따른 발광소자 패키지를 형성하는 방법에 대하여 상술한다. 도 7에 도시된 바와 같이, 공정은 서브마운트를 제공함으로써 시작된다(700). 예를 들면, 상기 서브마운트는, 예를 들면 상기 도 6을 참조하여 설명된 바와 같이 형성된 반도체 기판일 수 있다. 상기 서브마운트/기판 내에 발광소자를 배치한다(710). 상기 발광소자의 제 1 노드는 상기 캐비티에 형성된 상기 제 1 본드 패드와 콘택되도록 배치될 수 있으며, 상기 발광소자의 제 2 노드는 상기 기판의 캐비티 내에 형성된 제 2 본드

패드와 콘택트도록 배치될 수 있다.

[0055] 본 발명에 따른 방법의 특정 실시예에서, 고상 파장 전환 부재는 그것의 파장변환 특성을 결정하기 위하여 미리 테스트한다(720). 상기 발광소자 패키지에 파장변환 부재를 부착하기 전에 상기 파장변환 부재의 파장 특성을 테스트함으로써, 이러한 테스트는 형성된 발광소자 패키지에 있어서 더 높은 수율을 제공할 수 있다. 테스트한 후에, 상기 고상 파장변환 부재는 상기 발광소자로부터 방출된 광을 수용하고 파장변환하기 위하여 상기 발광소자 상으로, 상기 기판 상에 배치한다(730). 도 3A 및 3B에 도시된 바와 같이, 파장변환 부재는 상기 캐비티에 마운팅된 상기 발광소자와 대향되는, 상기 파장변환 부재의 상부 표면 상에 평판 형상 및/또는 볼록 형상을 가질 수 있다.

[0056] 도 6 및 7의 순서도 및 도 2 내지 도 5의 개념도는 본 발명의 일부 실시예에 따른 서브마운트 및/또는 발광소자 패키지를 형성하기 위한 방법의 가능한 실시형태에 대한 기능성 및 공정을 도시한다. 일부 선택적인 실시형태에서, 도면들에 대해 설명하면서 주지된 행위들은 본 도면에 표기된 순서로부터 발생할 수 있다. 예를 들면, 연속적으로 나타낸 2 개 블록들/공정들은 사실상, 관련된 기능성에 따라, 거의 동시에 실행될 수 있거나, 역의 순서로 실행될 수도 있다.

[0057] 위에서 주지된 바와 같이, 반도체 기판 칩 캐리어/서브마운트의 캐비티 내에 LED 칩을 마운팅하는 것은 상기 LED 칩 그 자체보다 실질적으로 더 크지 않는 소형 광학 이미지 크기를 갖는 백색 발광 칩을 제공할 수 있다. 상기 리세스된 캐비티는 광학 캐비티 및 집광기(light concentrator)로서 기능할 수 있다. 또한, 상기 마운팅된 LED 칩은 미리 제조되거나 즉석에서 형성된 백색 변환 부재를 상기 LED 칩 상으로 매우 근접하게 배치하는 방법을 제공할 수 있다. 이 배치는 LED 칩의 이미지 크기와 거의 동일한 상기 백색 이미터의 이미지 크기를 제공할 수 있다. 상기 바람직한 기능성에 따라, 상기 서브마운트는 종래의 전자 패키지 내에 접적될 수 있다. 또한, 상기 서브마운트는 그것의 기계적 안정성을 개선할 수 있도록 자체로 캡슐화되어, 단일 칩-스케일 패키지(stand alone chip-scale package)를 제공할 수 있다.

[0058] 이상과 같이 본 발명에 대해 설명하였으나, 이것은 본 발명을 한정하는 것으로 해석되어서는 아니 된다. 본 발명에 관하여 몇가지 실시예가 설명되었지만, 당업자에게 있어서, 본 발명의 신규한 가르침과 이점으로부터 실질적으로 벗어나지 않고서도 본 실시예에 있어서 많은 변형이 가능함은 자명하다. 따라서, 모든 변형은 청구의 범위에 정의된 바와 같이 본 발명의 범위 내에 포함되어야 한다. 그러므로, 상기 개시는 본 발명의 예시일 뿐이며, 개시된 특정 실시예에 한정되는 것으로 해석되어서는 안되며, 다른 실시예들뿐만 아니라 개시된 실시예들의 변형은 첨부한 청구의 범위의 범위 내에 포함되어야 한다. 본 발명은 본 명세서에 포함된 청구항들의 균등물과 함께, 다음의 청구항에 의하여 한정된다.

### 산업상 이용 가능성

[0059] 본 발명의 반도체 발광소자용 서브마운트 및 그 패키지에 따르면, 내부에 발광소자를 수용하도록 구성된 캐비티를 가지는 반도체 기판과 상기 발광소자로부터 방출되는 광을 수용하고 파장변환하기 위한 고상 파장변환 부재를 포함함으로써, 광방출의 균일도와 상기 패키지에 의해서 생성된 광학 이미지의 크기를 정밀하게 제어함으로써, 광출력의 균일성과 재현성을 확보할 수 있다.

[0060] 또한, 본 발명의 발광소자용 서브마운트 및 그 패키지의 제조방법에 따르면, 내부에 발광소자를 수용하도록 구성된 캐비티를 가지는 반도체 기판과 상기 발광소자로부터 방출되는 광을 수용하고 파장변환하기 위한 고상 파장변환 부재를 제공함으로써, 광방출의 균일도와 상기 패키지에 의해서 생성된 광학 이미지의 크기를 정밀하게 제어함으로써, 광출력의 균일성과 재현성을 확보할 수 있다.

### 도면의 간단한 설명

[0018] 도 1은 종래의 발광소자 패키지를 개략적으로 나타내는 단면도이다.

[0019] 도 2는 본 발명의 일부 실시예에 따른 발광소자를 개략적으로 나타내는 단면도이다.

[0020] 도 3a 및 3b는 본 발명의 일부 실시예에 따른 파장변환 부재를 개략적으로 나타내는 단면도이다.

[0021] 도 4 및 5는 본 발명의 다른 실시예에 따른 발광소자 패키지를 개략적으로 나타내는 단면도이다.

[0022] 도 6은 본 발명의 일부 실시예에 따른 반도체 발광소자용 서브마운트를 형성하는 공정을 나타내는 순서도이다.

[0023] 도 7은 본 발명의 일부 실시예에 따른 반도체 발광소자를 형성하는 공정을 나타내는 순서도이다.

도면

도면1

도면2

도면3a

도면3b

도면4

도면5

**도면6****도면7**