(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7348805号**

**(P7348805)**

(45)発行日 令和5年9月21日(2023.9.21)

(24)登録日 令和5年9月12日(2023.9.12)

(51)国際特許分類

|         |                  |     |         |        |         |

|---------|------------------|-----|---------|--------|---------|

| H 0 4 N | 25/78 (2023.01)  | F I | H 0 4 N | 25/78  |         |

| G 0 6 T | 7/00 (2017.01)   |     | G 0 6 T | 7/00   | 3 5 0 C |

| H 0 4 N | 25/772 (2023.01) |     | H 0 4 N | 25/772 |         |

請求項の数 9 (全20頁)

(21)出願番号 特願2019-188861(P2019-188861)

(22)出願日 令和1年10月15日(2019.10.15)

(65)公開番号 特開2021-64882(P2021-64882A)

(43)公開日 令和3年4月22日(2021.4.22)

審査請求日 令和4年10月17日(2022.10.17)

(73)特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74)代理人 110003281

弁理士法人大塚国際特許事務所

野村 修

東京都大田区下丸子3丁目30番2号

キヤノン株式会社内

(72)発明者 加藤 政美

東京都大田区下丸子3丁目30番2号

キヤノン株式会社内

審査官 鈴木 明

最終頁に続く

(54)【発明の名称】 認識装置、認識方法

**(57)【特許請求の範囲】****【請求項1】**

取得した入力に対応するアナログ電圧信号を出力するセンサ部と、

前記センサ部から出力されたアナログ電圧信号を基準電圧波形と比較してデジタルデータに変換する変換部と、

前記変換部が変換したデジタルデータに対して階層型畳み込みニューラルネットワークを用いて認識処理を行う認識部と

を備え、

前記基準電圧波形の波形特性を定めるパラメータは、前記階層型畳み込みニューラルネットワークのパラメータとともに学習処理に基づいて決定されることを特徴とする認識装置。

**【請求項2】**

前記階層型畳み込みニューラルネットワークのパラメータおよび前記基準電圧波形の波形特性を定めるパラメータは、当該階層型畳み込みニューラルネットワークにおける学習処理に基づいて決定されることを特徴とする請求項1に記載の認識装置。

**【請求項3】**

前記センサ部は、光電変換デバイスを有することを特徴とする請求項1または2に記載の認識装置。

**【請求項4】**

前記センサ部は、MEMS触覚センサを有することを特徴とする請求項1または2に記

載の認識装置。

**【請求項 5】**

前記変換部は、前記センサ部の列ごとに出力されたアナログ電圧信号をそれぞれ独立な基準電圧波形と比較してディジタルデータに変換する複数の変換回路を有することを特徴とする請求項 1 乃至 4 の何れか 1 項に記載の認識装置。

**【請求項 6】**

前記認識部は、前記複数の変換回路のそれぞれの出力するディジタルデータを前記階層型畳み込みニューラルネットワークの異なる入力特徴面に入力することを特徴とする請求項 5 に記載の認識装置。

**【請求項 7】**

前記認識部は、前記複数の変換回路のそれぞれの出力するディジタルデータを前記階層型畳み込みニューラルネットワークの入力特徴面の異なるブロックに入力することを特徴とする請求項 5 に記載の認識装置。

**【請求項 8】**

前記変換部は、前記センサ部の列ごとに出力されたアナログ電圧信号をそれぞれ独立な基準電圧波形と比較してディジタルデータに変換する複数の変換処理を時分割で実行することを特徴とする請求項 1 乃至 4 の何れか 1 項に記載の認識装置。

**【請求項 9】**

取得した入力に対応するアナログ電圧信号を出力するセンサ部を有する認識装置が行う認識方法であって、

前記認識装置の変換部が、前記センサ部から出力されたアナログ電圧信号を基準電圧波形と比較してディジタルデータに変換する変換工程と、

前記認識装置の認識部が、前記変換工程で変換したディジタルデータに対して階層型畳み込みニューラルネットワークを用いて認識処理を行う認識工程と

を備え、

前記基準電圧波形の波形特性を定めるパラメータは、前記階層型畳み込みニューラルネットワークのパラメータとともに学習処理に基づいて決定される

ことを特徴とする認識方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、認識技術に関するものである。

**【背景技術】**

**【0002】**

認識機能を実現する手法として、認識対象とするデータに対し、学習処理によりパラメータを決定した認識処理を実行するものが広く提案されている。ここで、「学習処理によりパラメータを決定した認識処理」としては、例えばニューラルネットワーク技術を応用したもののが知られている。

**【0003】**

ニューラルネットワーク技術を応用したものの例としては、階層型畳み込みニューラルネットワークがあり、認識対象の変動に対して頑健なパターン認識を可能にする技術として知られている。このような技術を適用した例として、特許文献 1 に、画像データを用いた顔認識を行う技術が提案されている。

**【0004】**

これらの認識処理を応用した認識装置においては、一般的にイメージセンサを内蔵するカメラにより取得した画像データや、音声センサを内蔵するマイクロホンにより取得した音声データを、認識処理に対する入力として、認識処理を行う。

**【0005】**

例えば、画像データに関しては、カメラに内蔵されたイメージセンサによって取得したセンサデータに対して所定の変換処理を適用し、変換後の画像データを認識処理に入力す

10

20

30

40

50

る。変換処理としては、カメラ内で実行されるA/D変換処理、ノイズ除去処理、および現像処理が含まれる。また音声データに関しても、音声センサからの出力データに対して、A/D変換処理を含む所定の変換処理を実行して音声データに変換した後に、認識処理に入力する。この場合、認識処理に入力される画像または音声等のデータは、一般的にはヒトの視覚機能または聴覚機能に適した変換処理が施されたデータとなる。

#### 【0006】

また一方で、センサから出力されるデータに対する変換処理を適応的に制御する技術が提案されている。例えば、特許文献2には、A/D変換特性を温度に関わらず基準変換特性に近づけるように補正するために、温度に基づいて基準電圧特性を制御する方法が開示されている。具体的には、特許文献2では、センサから出力される信号をA/D変換する際に、周囲環境の温度変化によらず常に所定のA/D変換特性を実現可能にする、基準電圧特性の制御方法を提供する。

10

#### 【先行技術文献】

#### 【特許文献】

#### 【0007】

【文献】特開平10-021406号公報

特開2011-229102号公報

20

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0008】

以上説明したように、センサで取得した信号に対して所定の変換処理を実行したデータを入力データとし、学習処理により決定したパラメータに基づいて認識処理を実行する認識装置が提案されている。

30

#### 【0009】

しかしながら上記の提案の場合、認識処理に入力される画像または音声等のデータは、センサで取得した信号に対して、ヒトの視覚機能または聴覚機能に適したデータに変換する変換処理が施されたデータであり、認識処理にて行われる処理に適した変換処理が施されたものではない。また、前述したように、センサで取得した信号に対して、所定の特性を満たすようにA/D変換特性を制御する方法が提案されているものの、この提案は、該信号に対して、認識処理で実行する処理に適するようにA/D変換特性を制御するものではなかった。本発明では、認識処理において行われる処理に適したデータ変換を実現可能な技術を提供する。

30

#### 【課題を解決するための手段】

#### 【0010】

本発明の一様態は、取得した入力に対応するアナログ電圧信号を出力するセンサ部と、前記センサ部から出力されたアナログ電圧信号を基準電圧波形と比較してディジタルデータに変換する変換部と、

前記変換部が変換したディジタルデータに対して階層型畳み込みニューラルネットワークを用いて認識処理を行う認識部と

を備え、

前記基準電圧波形の波形特性を定めるパラメータは、前記階層型畳み込みニューラルネットワークのパラメータとともに学習処理に基づいて決定される

ことを特徴とする。

40

#### 【発明の効果】

#### 【0011】

本発明の構成によれば、認識処理において行われる処理に適したデータ変換を実行することができる。

#### 【図面の簡単な説明】

#### 【0012】

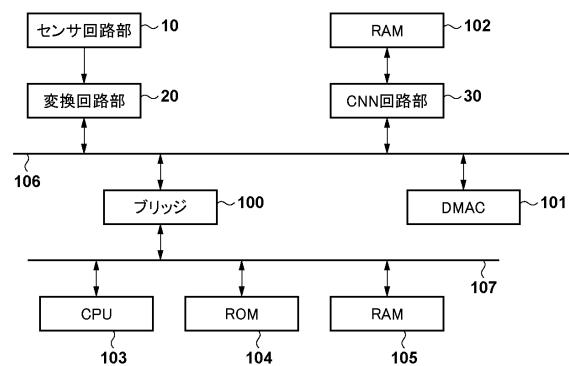

【図1】認識装置のハードウェア構成例を示すブロック図。

50

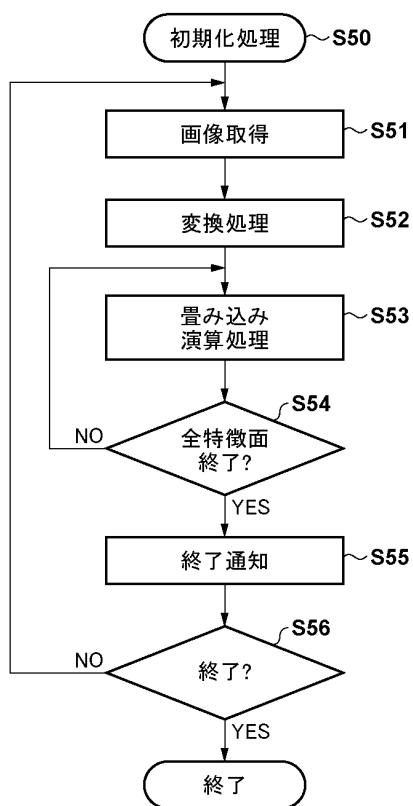

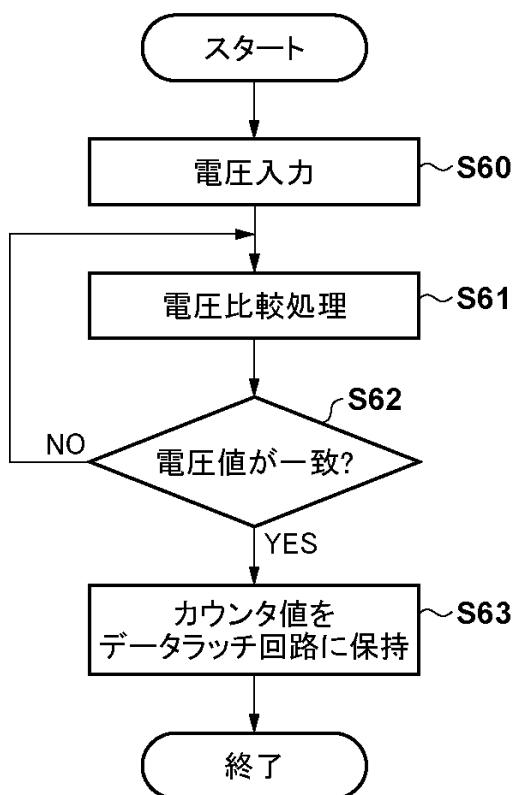

- 【図 2】認識装置の動作を示すフローチャート。

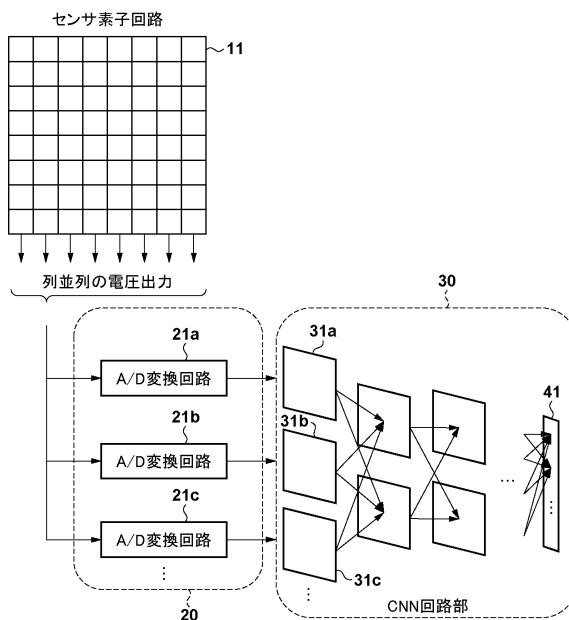

- 【図 3】変換回路部 20 の詳細を説明する図。

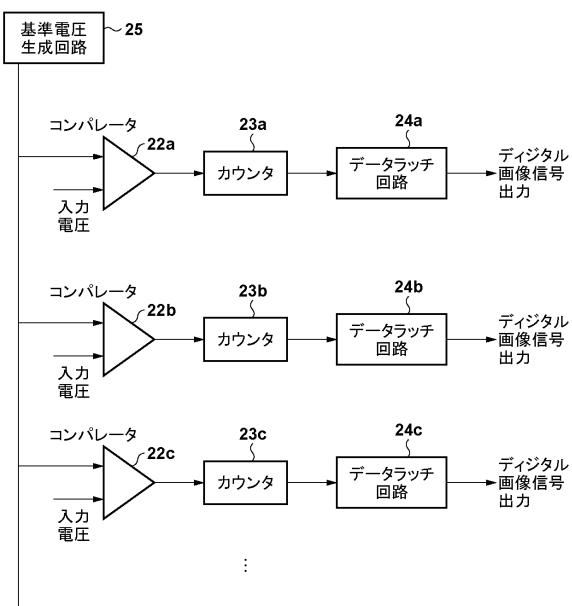

- 【図 4】変換回路部 20 の詳細を説明する図。

- 【図 5】変換回路部 20 の詳細を説明する図。

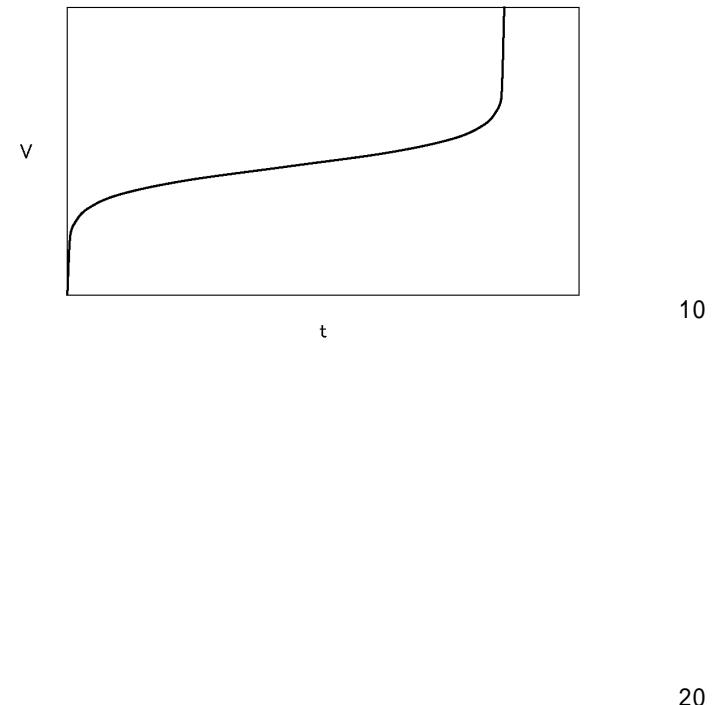

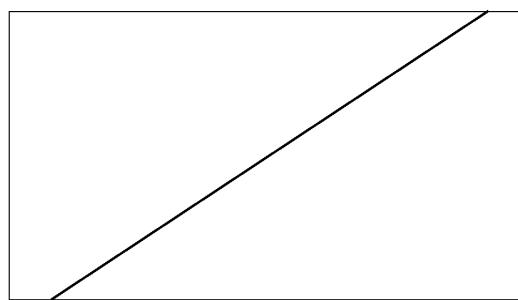

- 【図 6】基準電圧波形の電圧特性の一例を示す図。

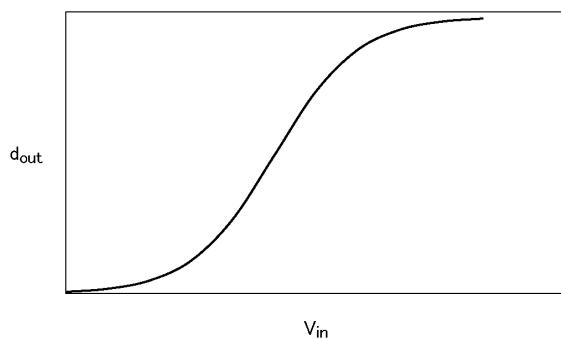

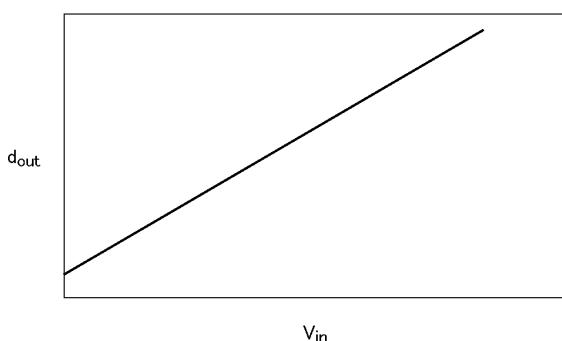

- 【図 7】A / D 変換回路 21a における入出力特性の一例を示す図。

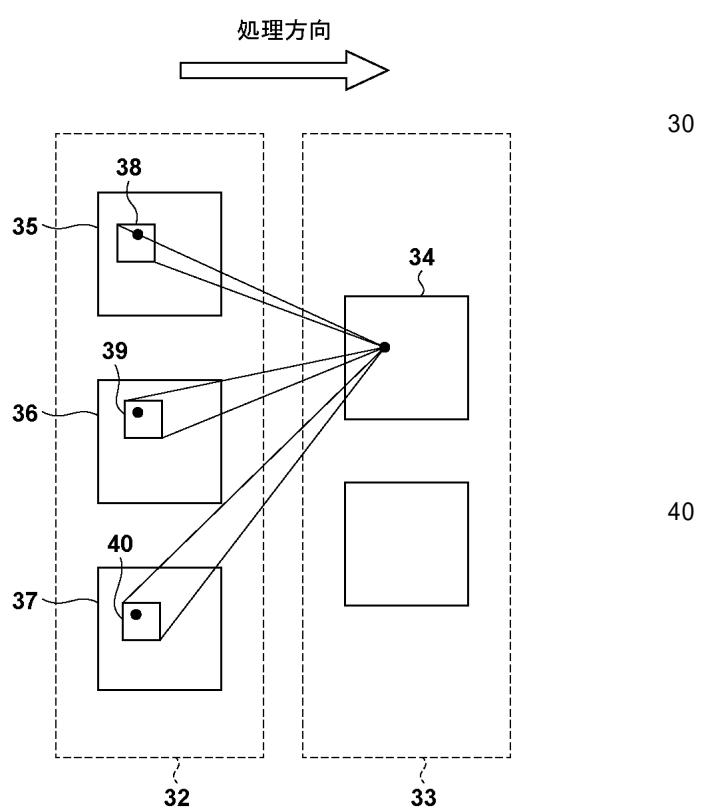

- 【図 8】CNN の畳み込み演算層で実行される演算処理の一例を示す図。

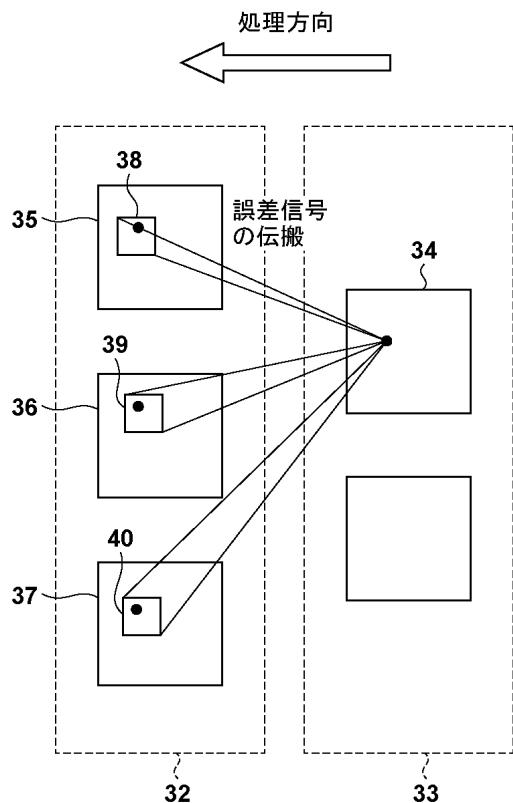

- 【図 9】バックプロパゲーション処理を説明する図。

- 【図 10】基準電圧波形の電圧特性の一例を示す図。

- 【図 11】基準電圧波形の電圧特性の一例を示す図。

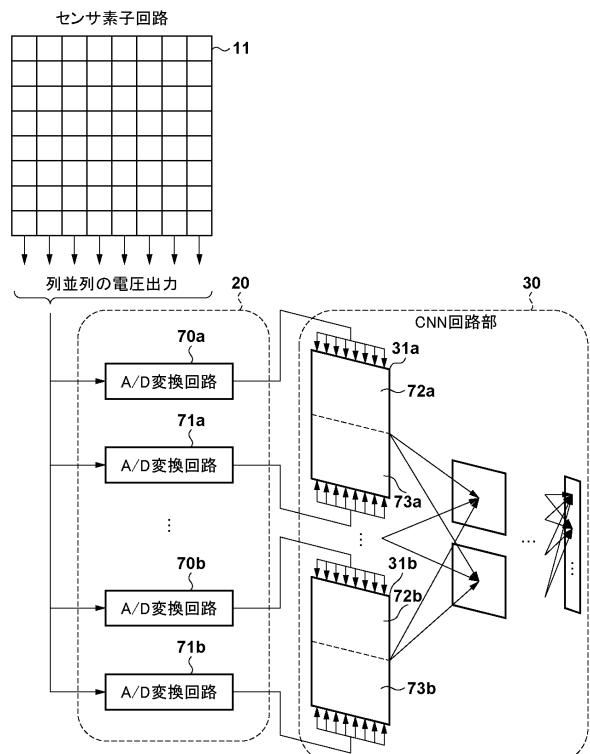

- 【図 12】変換回路部 20 の詳細を説明する図。

- 【図 13】認識装置の構成例を示す図。

- 【図 14】認識装置のハードウェア構成例を示すブロック図。

【発明を実施するための形態】

【0013】

以下、添付図面を参照して実施形態を詳しく説明する。尚、以下の実施形態は特許請求の範囲に係る発明を限定するものでない。実施形態には複数の特徴が記載されているが、これらの複数の特徴の全てが発明に必須のものとは限らず、また、複数の特徴は任意に組み合わせられてもよい。さらに、添付図面においては、同一若しくは同様の構成に同一の参考番号を付し、重複した説明は省略する。

【0014】

[第 1 の実施形態]

先ず、本実施形態に係る認識装置のハードウェア構成例について、図 1 のブロック図を用いて説明する。図 1 に示す如く、本実施形態に係る認識装置は、入力画像に対し、階層型畳み込みニューラルネットワーク演算回路を用いた 2 次元の畳み込み演算を行うことと、該入力画像から特定の物体を認識する認識処理を実現する。

【0015】

図 1 に示す如く、本実施形態に係る認識装置は、センサ回路部 10、変換回路部 20、RAM 102、CNN 回路部 30、ブリッジ 100、DMAC (Direct Memory Access Controller) 101 を有する。また、本実施形態に係る認識装置は、CPU 103、ROM 104、RAM 105 を有する。

【0016】

センサ回路部 10、変換回路部 20、CNN 回路部 30、RAM 102、DMAC 101 が画像バス 106 を介して互いに接続されており、CPU 103、ROM 104、RAM 105 が CPU バス 107 を介して互いに接続されている。また、ブリッジ 100 を介して画像バス 106 と CPU バス 107 との間のデータ転送が可能となっている。

【0017】

センサ回路部 10 は、光学系、CMOS (Complementary Metal Oxide Semiconductor) センサ等の光電変換デバイス、該光電変換デバイスを制御するドライバー回路、を有するセンサ部である。光学系を介して入光した光は光電変換デバイスにてアナログ画像信号 (アナログ画像データ) に変換され、該アナログ画像データは変換回路部 20 に対して出力される。

【0018】

変換回路部 20 は、A / D 変換回路及びフレームバッファを有する変換部である。センサ回路部 10 から出力されたアナログ画像データは A / D 変換回路にてディジタル画像データ (ディジタル画像信号) に変換され、該変換されたディジタル画像データはフレームバッファに格納される。センサ回路部 10 からフレーム単位でアナログ画像データが出力される場合、変換回路部 20 は、該フレーム単位のアナログ画像データをディジタル画像データに変換してフレームバッファに格納する。つまり、フレームバッファには、フレーム単位でディジタル画像データが格納されている。

10

20

30

40

50

**【 0 0 1 9 】**

CNN回路部30は、階層型畳み込みニューラルネットワーク（以下、CNNと称する）の演算処理を行う回路（階層型畳み込みニューラルネットワーク演算回路）である。CNN回路部30は、変換回路部20のフレームバッファに格納されているディジタル画像データをフレーム単位で読み出す。そしてCNN回路部30は、該読み出したディジタル画像データをCNNに入力して該CNNの演算処理を行うことで、該ディジタル画像データが表すフレーム画像から、認識対象となる物体を認識する。つまりCNN回路部30は認識部として機能する。RAM102は、CNN回路部30が各種の処理を行う際に用いる演算作業バッファとして使用される。DMAC101は、画像バス106上の変換回路部20、CNN回路部30、CPUバス107の間のデータ転送を司る。

10

**【 0 0 2 0 】**

CPU103は、ROM104からRAM105にロードしたコンピュータプログラムやデータを用いて認識装置全体の動作制御を行うと共に、認識装置が行うものとして後述する各処理を実行若しくは制御する。なお、CPU103は、ブリッジ100を介して画像バス106上のRAM102にアクセスすることも可能である。

**【 0 0 2 1 】**

ROM104には、各種のコンピュータプログラムやデータが格納されている。ROM104に格納されているコンピュータプログラムには、CPU103の動作を規定する命令を含むコンピュータプログラムが含まれている。また、ROM104に格納されているデータには、CNN回路部30の動作パラメータが含まれている。このように、ROM104には、認識装置が行うものとして後述する各処理を実現させるためのコンピュータプログラムやデータが格納されている。

20

**【 0 0 2 2 】**

RAM105は、ROM104からロードされたコンピュータプログラムやデータを格納するためのエリアや、CPU103が各種の処理を実行する際に用いるワークエリアを有する。このようにRAM105は、各種のエリアを適宜提供することができる。

**【 0 0 2 3 】**

次に、本実施形態に係る認識装置の動作について、図2のフローチャートに従って説明する。ステップS50では、CPU103は、物体の認識処理の開始に先立ち、各種の初期化処理を実行する。例えば、CPU103は、CNN回路部30の動作に必要なCNNの重み係数をROM104からRAM102に転送すると共に、CNN回路部30の動作、即ちCNNの構成を定義する為の各種レジスタ設定を行う。具体的には、CNN回路部30の制御部に存在する複数のレジスタに所定の値を設定する。同様に、変換回路部20等のレジスタに対しても動作に必要な値を書き込む。

30

**【 0 0 2 4 】**

ステップS51では、センサ回路部10は、光学系を介して入光した光を光電変換デバイスにてアナログ画像データに変換し、該変換したアナログ画像データを変換回路部20に対して出力する。

**【 0 0 2 5 】**

ステップS52では、変換回路部20は、センサ回路部10から出力されたアナログ画像データをA/D変換回路にてディジタル画像データに変換し、該ディジタル画像データをフレームバッファに格納する。変換回路部20は、1フレーム分のアナログ画像データをディジタル画像データに変換してフレームバッファに格納する処理が完了すると、完了信号を有効にする。

40

**【 0 0 2 6 】**

ステップS53およびステップS54の処理は、完了信号が有効になると実行される。ステップS53では、CNN回路部30は、フレームバッファに格納されている1フレーム分のディジタル画像データを読み出し、該読み出したディジタル画像データをCNNに入力して該CNNの各特徴面について演算処理（畳み込み演算処理）を行う。この畳み込み演算処理は、例えば図8に示す如く、特徴面34単位で行う。なお、畠み込み演算処理

50

の内容については後述する。

#### 【0027】

ステップS54では、CNN回路部30は、CNNにおける全ての特徴面について畳み込み演算処理を行ったか否かを判断する。この判断の結果、CNNにおける全ての特徴面について畳み込み演算処理を行った場合（図3の場合、最終出力面41の算出を終了した場合）には、処理はステップS55に進む。一方、CNNにおいて未だ畳み込み演算処理を行っていない特徴面が残っている場合には、処理はステップS53に進み、CNN回路部30は、未だ畳み込み演算処理を行っていない特徴面について畳み込み演算処理を行う。

#### 【0028】

ステップS55では、CNN回路部30は、CPU103に対して割り込み信号を出力する。ステップS56では、CPU103は、認識処理を終了するための条件が満たされたか否かを判断する。例えば、認識処理を終了する旨の指示がユーザ操作によって入力された場合や、フレームバッファに認識処理を行ったフレーム画像が残っていない場合には、上記の条件が満たされたと判断する。

10

#### 【0029】

このような判断の結果、認識処理を終了するための条件が満たされた場合には、図2のフローチャートに従った処理は終了する。一方、認識処理を終了するための条件が満たされていない場合には、処理はステップS51に進む。

#### 【0030】

次に、変換回路部20の詳細について、図3～5を用いて説明する。図3は、センサ回路部10が有する光電変換デバイスの一例としてのセンサ素子回路11の構成、変換回路部20に含まれるA/D変換回路21a～21c、CNN回路部30の構成、に関し、実行する処理と機能を説明するために模式的に示したものである。

20

#### 【0031】

センサ素子回路11は、フォトダイオードの2次元配列（センサ素子面）である。変換回路部20は、センサ素子回路11から列単位で並列に読み出した電圧をA/D変換して出力するべく、A/D変換回路21a～21cを有する。A/D変換回路21a～21cはそれぞれ、CNN回路部30にて実装されているCNNの入力特徴面31a～31cにデジタル画像データを供給するべく設けられている。A/D変換回路21a～21cのそれぞれの詳細な構成については図4を用いて後述する。

30

#### 【0032】

なお、CNN回路部30は、実際には半導体基板上の電子回路として構成されるが、図3では、実際の回路構成では無く、CNNによる畳み込み演算処理の処理内容を理解し易いように、実現する機能としてのCNNの構成を示している。

#### 【0033】

<ステップS60>

ステップS60における変換回路部20の動作について説明する。先ず、露光状態にあるセンサ素子回路11（センサ素子面）におけるそれぞれのフォトダイオードには、受光した光に応じた電荷が蓄積される。変換回路部20は、センサ素子回路11に蓄積されている電荷を電圧として読み出してA/D変換回路21a～21cのそれぞれに入力する。センサ素子回路11からの電圧の読み出しは列単位で並列に行われるものとする。

40

#### 【0034】

図3では、センサ素子回路11から列単位で読み出された電圧が、CNN回路部30における入力特徴面31a～31cのそれぞれについて設けられた、A/D変換回路21a～21cに入力される様子を模式的に示している。実際には、A/D変換回路は、フォトダイオードの2次元配列における列の数だけ設けられ、フォトダイオードの2次元配列における各列の電圧が、対応するA/D変換回路に入力される。また、CNN回路部30における入力特徴面の数もまた、フォトダイオードの2次元配列における列の数だけ設けられ、着目列に対応するA/D変換回路からの出力は、着目列に対応する入力特徴面に入力される。

50

**【 0 0 3 5 】**

A / D 変換回路 2 1 a ~ 2 1 c の構成例を図 4 に示す。図 4 は、変換回路部 2 0 の構成例を示すブロック図である。A / D 変換回路 2 1 a はコンパレータ 2 2 a、カウンタ 2 3 a、データラッチ回路 2 4 a を有する。A / D 変換回路 2 1 b はコンパレータ 2 2 b、カウンタ 2 3 b、データラッチ回路 2 4 b を有する。A / D 変換回路 2 1 c はコンパレータ 2 2 c、カウンタ 2 3 c、データラッチ回路 2 4 c を有する。以下では A / D 変換回路 2 1 a の動作について説明するが、同様の説明は A / D 変換回路 2 1 b および A / D 変換回路 2 1 c にも適用可能である。

**【 0 0 3 6 】**

コンパレータ 2 2 a には、A / D 変換回路 2 1 a に入力された電圧が入力電圧として入力される。また、コンパレータ 2 2 a には、基準電圧生成回路 2 5 が生成した基準電圧波形も入力される。

10

**【 0 0 3 7 】****< ステップ S 6 1 >**

次に、ステップ S 6 1 における変換回路部 2 0 の動作について説明する。コンパレータ 2 2 a は、入力電圧と、基準電圧波形と、を比較する。基準電圧波形は、例えば、図 6 および以降に示す式(1)のように時間的に単調増加する電圧特性を有している。

**【 0 0 3 8 】**

現時点で、入力電圧と基準電圧波形とで電圧値が等しくない場合はステップ S 6 2 を介してステップ S 6 1 に戻り、入力電圧と基準電圧波形とで電圧値が等しくなった時点でステップ S 6 2 を介してステップ S 6 3 に進む。コンパレータ 2 2 a は、入力電圧と基準電圧波形とで電圧値が等しくなった時点で出力パルス信号を反転させる。

20

**【 0 0 3 9 】****< ステップ S 6 3 >**

カウンタ 2 3 a は、基準電圧波形の開始タイミングから、クロック信号のパルス数をカウントした値(カウント値)を出力する。データラッチ回路 2 4 a は、コンパレータ 2 2 からの出力パルス信号が反転するタイミングで、カウンタ 2 3 から出力されるカウント値を保持する。これにより、入力電圧の電圧値がデジタル画像データとして変換される。然るにデータラッチ回路 2 4 a は、この変換したデジタル画像データをフレームバッファに保持しておき、所定の行数分のデジタル画像データが保持された時点で該所定の行数分のデジタル画像データを CNN 回路部 3 0 の入力特徴面 3 1 a に出力する。

30

**【 0 0 4 0 】**

なお、上記の説明における「所定の行数」は、CNN 回路部 3 0 における並列処理単位によって決定されるものであり、特定の値に限らない。本実施形態では一例として、センサ素子回路 1 1 の全面分(全行数分)のデジタル画像データがフレームバッファに格納された時点で、各行のデジタル画像データが CNN 回路部 3 0 におけるそれぞれの入力特徴面に入力されるものとする。

**【 0 0 4 1 】**

次に、A / D 変換回路 2 1 a の動作についてより詳細に説明する。上記の如く、A / D 変換回路 2 1 a は、基準電圧波形の波形特性に応じてアナログ画像データ(読み出された電圧)をデジタル画像データに変換する。ここで、本実施形態では、基準電圧波形は以下の式(1)(図 6)で示されるものとする。

40

**【 0 0 4 2 】****【 数 1 】**

$$v = -\frac{1}{\beta} \log \left| \frac{\alpha}{t} - 1 \right| + \gamma$$

• • • ( 1 )

10

#### 【 0 0 4 3 】

式(1)において、tは時間(カウンタ値に相当)を示し、vは基準電圧波形の電圧値を示す。パラメータ  $\alpha$ 、 $\beta$ 、 $\gamma$  は基準電圧波形を規定するパラメータであり、後述するように、CNNのパラメータを決定するための学習処理において算出され、図3のA/D変換回路ごとに異なる値を取り得る。なお、A/D変換回路21aにおける入出力特性は、式(1)の逆関数として、以下の式(2)(図7)で示される。

#### 【 0 0 4 4 】

#### 【 数 2 】

20

$$d_{out} = \frac{\alpha}{\left(1 + \exp\left(1 + (-\beta(v_{in} - \gamma))\right)\right)}$$

• • • ( 2 )

30

#### 【 0 0 4 5 】

式(2)において、 $v_{in}$ は入力アナログ電圧値を示し、 $d_{out}$ は出力ディジタル値を示す。続いて、基準電圧波形のパラメータ  $\alpha$ 、 $\beta$ 、 $\gamma$  およびCNNのパラメータを算出する学習処理に関して説明を行う。まず、CNNの畠み込み演算層で実行される演算処理を図8および式(3)に示す。

#### 【 0 0 4 6 】

#### 【 数 3 】

$$y_{ij(n)} = \sum_m \sum_{k=0}^{v-1} \sum_{l=0}^{h-1} w_{k,l(n,m)} x_{(i+k)(j+l(m))} + b_{(n)}$$

• • • ( 3 )

40

#### 【 0 0 4 7 】

式(3)において、xは入力データ、yは出力データ、wは畠み込みフィルタ、vは畠み込みフィルタの高さ、hは畠み込みフィルタの幅、mは前段層特徴面インデックス、n

50

は後段層特徴面インデックス、 $i$  は演算位置  $y$  座標、 $j$  は演算位置  $x$  座標を示す。また、 $k$  は畳み込みフィルタ  $y$  座標、 $l$  ( $t$ ) は畳み込みフィルタ  $x$  座標を示す。

#### 【0048】

CNNにおいて、図8の階層33の特徴面34を算出する場合、式(3)において入力データは図8に示した階層32の特徴面35~37となり、フィルタ38~40による畳み込み演算を画素単位で走査しながら繰り返す。本実施形態では説明を省略するが、一般的には畳み込み演算結果に対して非線形変換を実行する。なお、CNNの演算処理は、一般的に良く知られた手法であるため、これ以上の詳細な説明を省略する。

#### 【0049】

続いて本実施形態では、CNNのパラメータ  $w$ 、 $b$  および基準電圧波形のパラメータ<sup>10</sup>、 $\cdot$ 、 $\cdot$  を一般的な学習処理であるバックプロパゲーション処理により算出する。図9に示す如く、バックプロパゲーション処理においては、損失関数として定義される、CNNの出力と期待値との誤差を認識処理実行時とは逆方向に伝搬させることでパラメータを学習する。なお学習処理は、認識装置とは別個の装置において行われる。またその際には、認識結果に対する正解情報が付与された、学習処理に用いるための、変換回路に対する入力データ(所望の被写体を撮像したセンサ回路からのアナログ電圧値に対応するデータ)が用意されているものとする。なお、学習用のデータ生成方法としては、一般的なカメラで撮像された認識結果に対する正解情報を有する画像に対して、現像処理等の画像処理の逆変換を適用する手法が考えられる。または、カメラで撮像する際に、画像処理を適用したヒトが視認可能な画像と共に、センサ回路からの出力電圧値を外部に読み出すことで、それぞれが対応する画像セットを生成することが出来る。認識結果に対する正解情報はヒトが視認可能な画像を用いて設定することにより、認識装置で必要となる学習データを生成することが可能となる。

#### 【0050】

まずCNNのパラメータ  $w$ 、 $b$  は、バックプロパゲーション処理に基づいて、それぞれ以下の式(4)および(5)に基づいて更新される。なお、以降の式において、 $E$  は CNNにおける損失関数を示している。<sup>20</sup>

#### 【0051】

#### 【数4】

$$\frac{\partial E}{\partial w_{kl(n,m)}} = \sum_{i=0}^{V-v} \sum_{j=0}^{H-h} \frac{\partial E}{\partial y_{ij(n)}} x_{(i+k)(j+l)(m)} \\ \dots (4)$$

#### 【0052】

#### 【数5】

30

20

30

40

50

$$\frac{\partial E}{\partial b_{(n)}} = \sum_{i=0}^{V-v} \sum_{j=0}^{H-h} \frac{\partial E}{\partial y_{ij(n)}} \quad \dots \quad (5)$$

10

## 【0053】

損失関数としては、一般的なバックプロパゲーション手法と同様に、どのような関数を用いても良いが、本実施形態では一例として以下の式(6)に示す、交差エントロピー誤差を用いる。

## 【0054】

## 【数6】

$$E = - \sum_k t_k \log y_k$$

20

• • • (6)

30

## 【0055】

式(6)において、 $k$ は教師データのインデックス、 $t_k$ は教師データ、 $y_k$ はCNNの最終層の出力値（認識結果）を示す。また上式において、各階層から逆伝搬される誤差は、以下の式(7)に基づいて算出される。

## 【0056】

## 【数7】

$$\frac{\partial E}{\partial x_{ij(m)}} = \sum_n \sum_{k=0}^{v-1} \sum_{l=0}^{h-1} \frac{\partial E}{\partial y_{(i-k)(j-l)(n)}} w_{kl(n,m)}$$

40

• • • (7)

## 【0057】

一方、パラメータ $\theta$ 、 $w$ 、 $b$ は、バックプロパゲーション処理に基づいて、それぞれ以下の式(8)、式(9)、式(10)に基づいて更新される。

## 【0058】

## 【数8】

50

$$\frac{\partial E}{\partial \alpha_{(n)}} = \sum_{i=0}^{V-1} \sum_{j=0}^{H-1} \frac{\partial E}{\partial y_{ij(n)}} \frac{y_{ij(n)}}{\alpha_{(n)}}$$

• • • ( 8 )

【 0 0 5 9 】

【 数 9 】

$$\frac{\partial E}{\partial \beta_{(n)}} = \sum_{i=0}^{V-1} \sum_{j=0}^{H-1} \frac{\partial E}{\partial y_{ij(n)}} \alpha_{(n)}^2 y_{ij(n)} (\alpha_{(n)} - y_{ij(n)}) (x_{ij} - \gamma_{(n)})$$

• • • ( 9 )

【 0 0 6 0 】

【 数 10 】

$$\frac{\partial E}{\partial \gamma_{(n)}} = \sum_{i=0}^{V-1} \sum_{j=0}^{H-1} \frac{\partial E}{\partial y_{ij(n)}} \alpha_{(n)}^2 \beta_{(n)} y_{ij(n)} (\alpha_{(n)} - y_{ij(n)})$$

• • • ( 10 )

【 0 0 6 1 】

以上のバックプロパゲーション処理により、パラメータの更新を、前述した学習処理用の入力データに対して繰り返し実行することで、入力データに基づく、認識処理に適した CNN のパラメータ  $w$ 、 $b$  及び基準電圧波形のパラメータ  $\alpha$ 、 $\beta$ 、 $\gamma$  が算出される。

【 0 0 6 2 】

そして、算出された基準電圧波形のパラメータ  $\alpha$ 、 $\beta$ 、 $\gamma$  を用いて式 (1) に基づき基準電圧波形を事前に決定（取得）しておき、該基準電圧波形のデータ（波形データ）をルックアップテーブルの形式で ROM 104 に保持しておく。そして認識装置において認識処理を実行する際には基準電圧生成回路 25 が、ルックアップテーブル形式の波形データを元にして、時間的に変化するアナログ電圧波形を基準電圧波形（変換特性）として生成し、該生成した基準電圧波形をコンパレータに供給する。

【 0 0 6 3 】

また、基準電圧波形の生成方法としては、ROM 104 内にパラメータ  $\alpha$ 、 $\beta$ 、 $\gamma$  を保持しておき、基準電圧生成回路 25 がこれらのパラメータ  $\alpha$ 、 $\beta$ 、 $\gamma$  を用いて式 (1) に基づいて基準電圧波形を生成しても構わない。また CNN のパラメータ  $w$ 、 $b$  は ROM 1

04に保持され、認識処理実行時に随時、CNN回路部30に設定されて認識処理が実行される。

【0064】

以上説明したように、本実施形態では、CNNの特徴面毎に、異なる基準電圧波形に基づいてA/D変換されたディジタル画像データが入力されることになる。それぞれの基準電圧波形は、前述したように学習処理によって決定したものであり、認識処理に適した特性を有するものである。従って、本実施形態に係る認識装置は、センサ素子回路の出力に対してより認識に適した変換処理を実行することが可能となり、また、本来認識処理に対しては必須では無い現像処理等の画像処理に関わる回路を削減することが可能となる。

【0065】

<変形例 … 基準電圧波形の関数（線形関数）>

第1の実施形態では、基準電圧波形の波形特性として式(1)、(2)に示したものを使いたが、これらに限定されるものではない。例えば、以下の式(11)、(12)に示される波形特性を有する基準電圧波形を用いても構わないし、その他の波形特性を有する基準電圧波形を用いても構わない（それぞれの波形を図10および図11に示す）。

【0066】

【数11】

$$v = \frac{t - \beta}{\alpha} \quad (t \geq \beta)$$

… (11)

【0067】

【数12】

$$d_{out} = \alpha v_{in} + \beta$$

… (12)

【0068】

なお、式(11)、(12)で示される波形特性を有する基準電圧波形を用いる場合、そのパラメータ $\alpha$ 、 $\beta$ は、第1の実施形態と同様に、CNNの一般的な学習処理であるバックプロパゲーション処理により算出する。この場合、 $\alpha$ 、 $\beta$ はそれぞれ以下の式に基づいて更新される。

【0069】

【数13】

10

20

30

40

50

$$\frac{\partial E}{\partial \alpha_{(n)}} = \sum_{i=0}^{V-1} \sum_{j=0}^{H-1} \frac{\partial E}{\partial y_{ij(n)}} x_{ij(n)} \\ \dots (13)$$

【0070】

10

【数14】

$$\frac{\partial E}{\partial b_{(n)}} = \sum_{i=0}^{V-1} \sum_{j=0}^{H-1} \frac{\partial E}{\partial y_{ij(n)}} \\ \dots (14)$$

【0071】

20

このように、本変形例においても、第1の実施形態と同様の効果を奏することができる。

【0072】

## [ 第2の実施形態 ]

本実施形態を含む以下の各実施形態では、第1の実施形態との差分について説明し、以下で特に触れない限りは、第1の実施形態と同様であるものとする。図12は、センサ素子回路11の構成と、変換回路部20に含まれるA/D変換回路70a、70b、71a、71bと、CNN回路部30の構成と、に関し、実行する処理と機能を説明するために模式的に示したものである。

【0073】

30

入力特徴面31aを規定行数を単位に2つのブロック（上側のブロックは入力特徴面72a、下側のブロックは入力特徴面73a）に分割した場合において、入力特徴面72aについてはA/D変換回路70aが設けられている。また、入力特徴面73aについてはA/D変換回路71aが設けられている。

【0074】

同様に、入力特徴面31bを規定行数を単位に2つのブロック（上側のブロックは入力特徴面72b、下側のブロックは入力特徴面73b）に分割した場合において、入力特徴面72bについてはA/D変換回路70bが設けられている。また、入力特徴面73bについてはA/D変換回路71bが設けられている。

【0075】

40

このように、本実施形態では第1の実施形態と同様に、CNN回路部30における入力特徴面は、フォトダイオードの2次元配列における列の数だけ設けられているが、該入力特徴面は規定行数を単位に2つのブロックに分割されている。そして変換回路部20が有するA/D変換回路は、該ブロックごとに設けられている。

【0076】

よって、図12の構成の場合、A/D変換回路70a、70b、71a、71bのそれぞれ独立に、基準電圧波形の波形特性を設定することが可能である。そして、センサ素子回路11において、入力特徴面31aに対応する列の上側のブロックに対応する行の電圧はA/D変換回路70aに入力され、該列の下側のブロックに対応する行の電圧はA/D変換回路71aに入力される。そしてA/D変換回路70aからの出力は入力特徴面7

50

2 a に対して出力され、A / D 変換回路 7 1 a からの出力は入力特徴面 7 3 a に対して出力される。同様に、センサ素子回路 1 1において、入力特徴面 3 1 b に対応する列の上側のブロックに対応する行の電圧は A / D 変換回路 7 0 b に入力され、該列の下側のブロックに対応する行の電圧は A / D 変換回路 7 1 b に入力される。そして A / D 変換回路 7 0 b からの出力は入力特徴面 7 2 b に対して出力され、A / D 変換回路 7 1 b からの出力は入力特徴面 7 3 b に対して出力される。なお、ブロックごとの波形特性のパラメータのバックプロパゲーションによる学習処理については、第 1 の実施形態と同様である。

#### 【 0 0 7 7 】

このように、本実施形態によれば、センサ素子回路 1 1 によって撮像される領域において、それぞれのブロックにおける撮像環境が大きく異なる場合（例えば、画面上部と下部で明るさが大きく異なる場合）であっても、入力特徴面のブロックごとに A / D 変換回路の基準電圧波形の波形特性を学習するので、それぞれの撮像環境に適した波形特性を得ることが可能となる。これにより、センサ素子回路 1 1 によって撮像される領域ごとに認識に適した変換処理を実行することが可能となる。

10

#### 【 0 0 7 8 】

なお、本実施形態では、1つの入力特徴面を2つのブロックに分割する例について説明した。しかし、入力特徴面の分割数は2に限らず、3以上であっても良い。また、A / D 変換回路は、前述した複数行のブロックごとに独立に設けることに限らず、どのような単位で設けても構わない。例えば、センサ素子回路 1 1 の画素回路ごとに A / D 変換回路を設けても良いし、所定の画素回路領域ごとに A / D 変換回路を設けても良い。このよう 20 に、A / D 変換における基準電圧波形の波形特性を認識に関わる学習処理によって決定することができれば、A / D 変換回路はどのような単位で設けても良い。

20

#### 【 0 0 7 9 】

これにより、独立に設けられる A / D 変換回路に対応するセンサ素子回路 1 1 上の領域がどのような単位の領域であるのかに関わらず、領域ごとに認識に適した変換処理を実行することが可能となる。

#### 【 0 0 8 0 】

また、A / D 変換回路を独立に複数設けることに限らず、同一の A / D 変換回路を時分割に複数回使用することで、異なる基準電圧波形の波形特性パラメータによる変換を実行するものであっても良い。この場合は、例えば、第 1 の実施形態で説明したルックアップテーブルに波形データを複数用意しておき、変換処理毎に異なる波形データに対応した基準電圧波形を基準電圧生成回路 2 5 にて生成して A / D 変換回路に供給する。これにより、A / D 変換回路を独立に複数設ける場合と同様に、センサ素子回路 1 1 によって撮像される領域ごとに認識に適した変換処理を実行することが可能となる。

30

#### 【 0 0 8 1 】

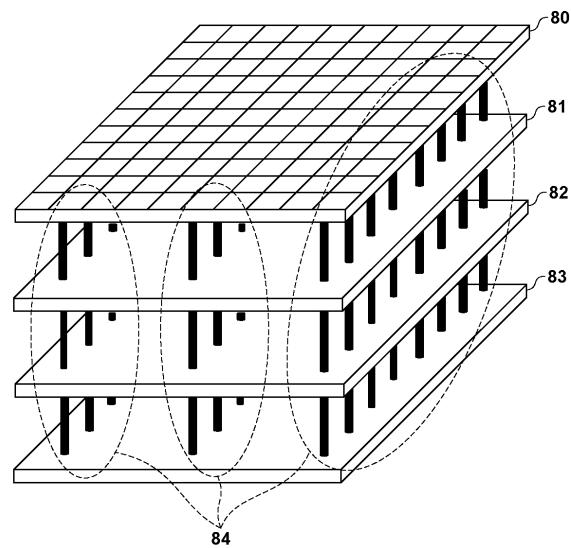

##### [ 第 3 の実施形態 ]

本実施形態に係る認識装置は、図 1 3 に模式的に示すように積層された半導体基板に構成されており、その他の構成および処理内容は第 1 の実施形態と同様である。本実施形態に係る認識装置は、図 1 3 に示すように3次元的に積層された半導体基板として構成されている。認識装置を構成するそれぞれの回路については、図 1 3 に示す如く、階層 8 0 にセンサ素子回路 1 1 が構成され、階層 8 1 ~ 8 3 のそれには、変換回路部 2 0 、 C N N 回路部 3 0 が構成されている。階層 8 1 ~ 8 3 の各階層に構成された C N N 回路部 3 0 は、それぞれ異なる入力特徴面に相当する（例えば、図 3 の3種類の入力特徴面）。

40

#### 【 0 0 8 2 】

センサ素子回路 1 1 から出力される電圧は、階層ごとに構成された変換回路部 2 0 の A / D 変換回路に並列に入力される。各階層間の信号の伝達は、T S V (シリコン貫通電極) 8 4 (図 1 3 における点線枠内) を介して行われる。A / D 変換回路ごとに、学習処理により算出した波形特性に基づく基準電圧波形を用いて A / D 変換回路を実行することは上記の各実施形態で説明した内容と同一である。

#### 【 0 0 8 3 】

50

このように、本実施形態によれば、認識装置を構成する変換回路部 20 および CNN 回路部 30 が積層された半導体基板に構成されるため、並列処理を実現しつつ 2 次元的な回路面積を削減することが可能となる。

#### 【0084】

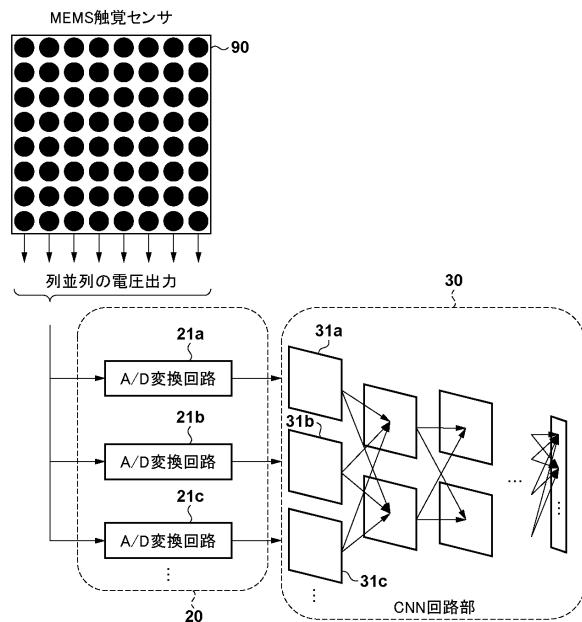

##### [第4の実施形態]

本実施形態に係る認識装置は、図 14 に示す如く、センサ回路部 10 がセンサ素子回路 11 の代わりに MEMS 觸覚センサ 90 を有する。本実施形態では、センサ素子回路 11 の列ごとの電圧が、該列に対応する A/D 変換回路に入力される代わりに、MEMS 觸覚センサ 90 の列ごとの電圧（アナログ信号）が、該列に対応する A/D 変換回路に入力される。そして、それぞれの A/D 変換回路において、列ごとに異なる基準電圧波形に基づく A/D 変換が行われる。そして CNN 回路部 30 は、それぞれの A/D 変換回路からの出力に基づいて、物体の形状を認識する。なお、上記の説明において「列ごと」の代わりに第 2 の実施形態のように「列を分割したブロックごと」であっても良い。

#### 【0085】

なお、列ごと若しくはブロックごとの波形特性のパラメータのバックプロパゲーションによる学習処理については、第 1 の実施形態と同様である。よって本実施形態では、MEMS 觸覚センサ 90 の出力に対してより認識に適した変換処理を実行することが可能となる。

#### 【0086】

なお、センサ回路部 10 が有するセンサは、センサ素子回路 11 等の光電変換デバイスや MEMS 觸覚センサ 90 に限らず、A/D 変換処理を伴うセンサであれば、その他の種類のセンサであっても良い。その他の種類のセンサを使用する場合であっても、A/D 変換処理における波形特性を学習処理によって決定することは、上記の実施形態にて説明したとおりである。

#### 【0087】

また、上記の各実施形態では、センサ回路部 10 が有するセンサ（上記のセンサ素子回路 11 や MEMS 觸覚センサ 90 等）における列の数と A/D 変換回路の数とが同じであるものとして説明したが、同じでなくても良い。例えば、1 つの A/D 変換回路で複数の列の電圧を変換するようにしても良い。

#### 【0088】

なお、以上説明した各実施形態や変形例の一部若しくは全部を適宜組み合わせて使用しても構わない。また、以上説明した各実施形態や変形例の一部若しくは全部を選択的に使用しても構わない。

#### 【0089】

##### （他の実施形態）

本発明は、上述の実施形態の 1 以上の機能を実現するプログラムを、ネットワーク又は記憶媒体を介してシステム又は装置に供給し、そのシステム又は装置のコンピュータにおける 1 つ以上のプロセッサがプログラムを読み出し実行する処理でも実現可能である。また、1 以上の機能を実現する回路（例えば、ASIC）によっても実現可能である。

#### 【0090】

発明は上記実施形態に制限されるものではなく、発明の精神及び範囲から離脱することなく、様々な変更及び変形が可能である。従って、発明の範囲を公にするために請求項を添付する。

#### 【符号の説明】

#### 【0091】

10 : センサ回路部 20 : 変換回路部 30 : CNN 回路部 100 : ブリッジ

101 : DMAC 102 : RAM 103 : CPU 104 : ROM 105 :

RAM 106 : 画像バス 107 : CPUバス

10

20

30

40

50

【図面】

【図 1】

【図 2】

10

20

30

40

【図 3】

【図 4】

50

【図 5】

【図 6】

【図 7】

【図 8】

【図 9】

【図 10】

10

20

【図 11】

【図 12】

30

40

50

【図 1 3】

【図 1 4】

10

20

30

40

50

---

フロントページの続き

- (56)参考文献      特開2019-004358 (JP, A)

特開2013-229852 (JP, A)

国際公開第2011/045835 (WO, A1)

特開2011-229102 (JP, A)

- (58)調査した分野 (Int.Cl., DB名)

H04N 25/00 - 25/79

G06T 7/00