(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4949231号

(P4949231)

(45) 発行日 平成24年6月6日(2012.6.6)

(24) 登録日 平成24年3月16日(2012.3.16)

(51) Int.Cl.

F 1

G06F 9/46 (2006.01)

G06F 9/38 (2006.01)G06F 9/46 410

G06F 9/38 370X

請求項の数 12 (全 38 頁)

(21) 出願番号 特願2007-506565 (P2007-506565)

(86) (22) 出願日 平成17年3月31日 (2005.3.31)

(65) 公表番号 特表2007-531167 (P2007-531167A)

(43) 公表日 平成19年11月1日 (2007.11.1)

(86) 國際出願番号 PCT/US2005/010923

(87) 國際公開番号 WO2005/098624

(87) 國際公開日 平成17年10月20日 (2005.10.20)

審査請求日 平成18年9月28日 (2006.9.28)

(31) 優先権主張番号 10/816,103

(32) 優先日 平成16年3月31日 (2004.3.31)

(33) 優先権主張国 米国(US)

前置審査

(73) 特許権者 593096712

インテル コーポレイション

アメリカ合衆国 95052 カリフォルニア州 サンタクララ ミッション カレッジ ブールバード 2200

(74) 代理人 100070150

弁理士 伊東 忠彦

(74) 代理人 100091214

弁理士 大貫 進介

(74) 代理人 100107766

弁理士 伊東 忠重

(72) 発明者 グロショウスキ, エドワード, ティー

アメリカ合衆国 95118 カリフォルニア州 サンノゼ イエール ドライヴ

5565

最終頁に続く

(54) 【発明の名称】 ユーザーレベルのマルチスレッドを提供する方法およびシステム

## (57) 【特許請求の範囲】

## 【請求項 1】

第一のオペレーティング・システム(OS)生成スレッドを実行する段階であって、ここで、前記第一のOS生成スレッドは第一のシステム状態に関連付けられている、オペレーティング・システムによって生成されたスレッドである、段階と、

非特権ユーザーレベルプログラミング命令に遭遇する段階と、

非特権レベルプログラミング命令に反応して、第一のアプリケーション状態の第一の専有部分に関連付けられた第一の共有リソース・スレッド(シュレッド)を生成する段階であって、前記第一のシュレッドは、前記第一のアプリケーション状態の共有部分および前記第一のシステム状態を少なくとも第二のシュレッドと共有し、前記非特権レベルプログラミング命令は、OSの介入なしにハードウェアにおいてシュレッドを生成するためにハードウェアによって認識可能な命令セットアーキテクチャ(ISA)に含まれるものである、段階と、

前記ユーザーレベルプログラミング命令に反応して、前記第一のシュレッドを少なくとも前記第二のシュレッドと並行して実行する段階と、

前記第一のシュレッドと前記第二のシュレッドとの間で、前記第一のシュレッドおよび前記第二のシュレッドによって更新されることができるよう適応されている一つまたは複数の共有レジスタを介して通信する段階とを含み、前記一つまたは複数の共有レジスタは、前記第一のアプリケーション状態の共有部分および前記第一のシステム状態を共有するシュレッドの専有である、方法。

## 【請求項 2】

前記第一のアプリケーション状態の前記第一の専有部分が、汎用レジスタ、浮動小数点レジスタ、MMXレジスタ、セグメント・レジスタ、フラグ・レジスタ、命令ポインタ、制御および状態レジスタ、SSEレジスタおよびMXCSRレジスタを含む複数のレジスタのうちの少なくとも一つと関連付けられていることを特徴とする、請求項1記載の方法。

## 【請求項 3】

前記第一のシュレッドおよび前記第二のシュレッドが、現在の特権レベルを共有し、共通のアドレス変換を共有することを特徴とする、請求項1記載の方法。

## 【請求項 4】

シュレッド破棄動作をエンコードする非特権ユーザーレベルプログラミング命令を受け取ることをさらに含むことを特徴とする、請求項1記載の方法。 10

## 【請求項 5】

前記通信がユーザーレベルのシュレッド信号伝送命令を介して実行されることを特徴とする、請求項1記載の方法。

## 【請求項 6】

ユーザーレベルのプログラミング命令に反応して、オペレーティング・システムの介入なしに前記第一のシュレッドおよび前記第二のシュレッドをスケジューリングすることさらに含むことを特徴とする、請求項1記載の方法。

## 【請求項 7】

コンテキスト切り換え要求の受領に反応して、前記一つまたは複数のシュレッドに対応する一つまたは複数の状態を保存する、ことをさらに含むことを特徴とする、請求項1記載の方法。 20

## 【請求項 8】

オペレーティング・システムの介入なしに、ユーザーレベルの例外ハンドラコードにより、前記第一のシュレッドの実行の間に発生した例外を扱う、ことをさらに含むことを特徴とする、請求項1記載の方法。

## 【請求項 9】

ある命令セットアーキテクチャ(ISA)を実装するマイクロプロセッサであって、前記マイクロプロセッサは複数のOS生成スレッドを実行し、前記マイクロプロセッサはまた、前記複数のOS生成スレッドのうちのあるOS生成スレッドに関連付けられた複数の共有リソース・スレッド(シュレッド)を並行して実行し、前記複数のシュレッドのそれぞれは前記OS生成スレッド内のある専有状態および前記OS生成スレッドの共有状態に関連付けられており、前記シュレッドのそれぞれは、前記ISAのアプリケーション・プログラム命令に反応して前記マイクロプロセッサのハードウェアを利用して生成され、前記OS生成スレッドの共有状態の一部であるレジスタが、前記複数のシュレッドによって直接更新可能であるよう適応されており、それにより前記複数のシュレッドの間の通信を許容するとともに、前記OS生成スレッドの共有状態に関連付けられていないスレッドによってはアクセス不可能でない、マイクロプロセッサと。 30

ユーザーレベルのマルチスレッド動作を許容するための、前記ISAの一つまたは複数の命令を記憶するメモリとを有することを特徴とする、

システム。 40

## 【請求項 10】

前記一つまたは複数の命令が、オペレーティング・システムの介入なしにシュレッドを生成する命令を含むことを特徴とする、請求項9記載のシステム。

## 【請求項 11】

前記一つまたは複数の命令が、オペレーティング・システムの介入なしにシュレッドを破棄する命令を含むことを特徴とする、請求項9記載のシステム。

## 【請求項 12】

前記ユーザーレベルのマルチスレッド動作が、同一のスレッドに関連付けられた二つ以上のシュレッドの並行的な実行を含むことを特徴とする、請求項9記載のシステム。 50

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明のここでの諸実施形態はコンピュータシステムの分野に関する。特に、ここでの諸実施形態はユーザーレベルのマルチスレッドを提供するための方法およびシステムに関する。

**【背景技術】****【0002】**

マルチスレッドは、プログラムまたはOS(オペレーティングシステム)が命令のシーケンスを一時に二つ以上実行する機能である。各ユーザー(ここではユーザーは別のプログラムでもよい)からのプログラムまたはシステムサービスの要求は、別個の素性をもつスレッドとして追跡される。プログラムはそのスレッドに対する初期要求のために動作し、他の要求によって中断されるので、そのスレッドのための作業の状態は、その作業が完了するまで追跡される。

**【0003】**

コンピュータ処理の種別には、単一命令ストリーム・單一データストリームが含まれるが、これは命令の単一のストリームを含む従来のシリアル式フォンノイマンコンピュータである。第二の処理種別は単一命令ストリーム・多重データストリーム(SIMD: single instruction stream, multiple data streams)処理である。この処理方式には、多重算術論理プロセッサおよび单一制御プロセッサが含まれる。算術論理プロセッサのそれぞれがデータに対して演算をロックステップで実行し、制御プロセッサによって同期される。第三の種別は多重命令ストリーム・單一データストリーム(MISD: multiple instruction streams, single data stream)処理であるが、これは同じデータストリームの流れを異なる命令ストリームを実行する諸プロセッサの線形配列を通じて処理することに関わる。第四の処理種別は、多重命令ストリーム・多重データストリーム(MIMD: multiple instruction streams, multiple data streams)処理であり、これは複数のプロセッサを使用し、そのそれぞれが該それぞれのプロセッサに供給されたデータストリームを処理するための独自の命令ストリームを実行する。MIMDプロセッサはいくつかの命令処理ユニット、複数の命令シーケンサ、よっていくつかのデータストリームを有しする。

**【発明の開示】****【発明が解決しようとする課題】****【0004】**

今日のマルチスレッド・マイクロプロセッサによって採用されているプログラミング・モデルは、伝統的な共有メモリ・マルチプロセッサと同じである：複数のスレッドがあたかも独立のCPUで走るかのようにプログラムされる。スレッド間の通信はメインメモリを通じて実行され、スレッド生成/破棄/スケジューリングはOSによって実行される。マルチスレッドはこれまで、プログラマーが直接スレッドにアクセスできるような、アーキテクチャ的に目に見える仕方では供給されていなかった。

**【0005】**

本発明のここでの諸実施形態は、以下の詳細な記述を図面とともに参照することからより完全に理解され、認識されるであろう。

**【課題を解決するための手段】****【0006】**

ユーザーレベルのマルチスレッドを提供する方法およびシステムが開示される。本技法に基づく方法は、命令セットアーキテクチャ(ISA: instruction set architecture)を介して一つまたは複数の共有リソース・スレッド(shared resource thread)(シュレッド[shred])を実行するためのプログラミング命令を受け取ることを含む。一つまたは複数の命令ポインタがISAを介して構成設定され、前記一つまたは複数のシュレッドがマイクロプロセッサにより同時的に実行される。ここで、マイクロプロセッサは複数の

10

20

30

40

50

命令シーケンサを含んでいる。

【発明を実施するための最良の形態】

【0007】

以下の記述では、説明の目的で個別的な述語が述べられる。しかし、こうした個別的な詳細が必須でないことは当業者には明らかであろう。以下の詳細な記述のいくつかの部分はアルゴリズムおよびコンピュータメモリ内のデータビットに対する演算の記号表現を用いて呈示されている。これらのアルゴリズム的記述および表現は、データ処理分野の当業者が自らの仕事の内容を他の当業者に最も効率的に伝達するために使っている手段である。アルゴリズムとはここでは、そして一般にも、所望の結果に導く一連の自己完結的な処理の系列であると考えられる。前記処理は物理量の物理的な操作を要求するものである。必須ではないが通例、こうした量は、保存、転送、組み合わせおよびその他の操作ができる電気信号または磁気信号の形をとる。時には主として慣用上の理由のため、これらの信号をビット、値、要素、記号、文字、項、数などと称することが便利であることがわかっている。

10

【0008】

しかし、これらの、そして同様の用語はすべて適切な物理量と関連しており、単にそれらの量に適用される便利なラベルにすぎないことを留意すべきである。以下の議論から明らかのように、特別に断らない限り、本記載を通じて、「処理」または「計算」または「計数」または「決定」または「表示」などといった用語を用いた議論は、コンピュータシステムのレジスタおよびメモリ内の物理的な（電子的な）量として表現されているデータを操作し、コンピュータシステムメモリまたはレジスタまたはその他のそのような情報記憶、伝送もしくは表示装置内の物理的な量として同様に表現される他のデータに変換するコンピュータシステムまたは同様の電子計算装置の動作およびプロセスを言っていることが了解される。

20

【0009】

本発明の諸実施形態はまた、この動作を実行するための装置にも関する。この装置は必要とされる目的のために特別に構築されたものでもよいし、あるいは汎用コンピュータであって該コンピュータ内に保存されるコンピュータプログラムによって選択的に活性化もしくは再構成設定されるのでもよい。そのようなコンピュータプログラムはコンピュータ可読記憶媒体に保存されうる。そのような媒体としては、これに限定されるものではないが、フロッピー（登録商標）ディスク、光ディスク、CD-ROM、光磁気ディスクを含む任意の種類のディスク、読み出し専用メモリ（ROM）、ランダムアクセスメモリ（RAM）、EPROM、EEPROM、磁気もしくは光カードまたは電子的な命令を保存するのに好適な任意の種類の媒体であってそれぞれコンピュータシステムバスに結合されているものがある。

30

【0010】

ここに呈示される動作および表示はいかなる特定のコンピュータまたはその他の装置に本的に関係しているものでもない。さまざまな汎用システムがこの思想に従ったプログラムとともに使用されうるし、あるいは必要とされる動作を実行するためにより特化した装置を構築することが便利であると判明することもありうる。多様なこれらのシステムのための必要とされる構造は以下の記述から明らかとなろう。さらに、本発明の実施形態はいかなる特定のプログラミング言語との関連で記載されているのでもない。ここに記載される本発明の諸実施形態の思想を実現するためには多様なプログラミング言語が使用されうることは理解されるであろう。

40

【0011】

この明細書を通じて使用される「ユーザー」は、アプリケーション・プログラム、非特権コードおよび同様なソフトウェアといったユーザー・レベル・ソフトウェアのことを述べている。ユーザー・レベル・ソフトウェアはOSまたは同様の特権ソフトウェアからは区別される。本発明のある実施形態によれば、以下の記述は上述したMIMDプロセッサに適用される。

【0012】

50

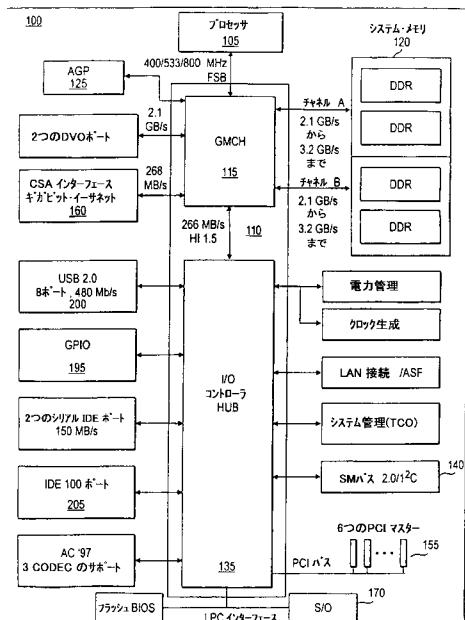

図1は、本発明のある実施形態に基づく、本方法および装置を利用する例示的なコンピュータシステム100のブロック図を示している。コンピュータシステムはプロセッサ105を含む。チップセット110がシステム100にメモリおよびI/O機能を提供する。より具体的には、チップセット110はグラフィックおよびメモリ・コントローラ・ハブ(GMCH: Graphics and Memory Controller Hub)115を含む。GMCH115は、プロセッサ105と通信するホストコントローラとしてはたらき、さらにメインメモリ120のためのコントローラとしてはたらく。本発明のある実施形態によれば、プロセッサ105はマルチスレッドのユーザーレベルへの拡張を可能にする。GMCH115はまた、それに結合されている先進グラフィックポート(AGP: Advanced Graphics Port)コントローラ125へのインターフェースをも提供する。チップセット110はさらに、数多くのI/O機能を実行するI/Oコントローラ・ハブ(ICH: I/O Controller Hub)を含む。ICH135はシステム管理バス(SMバス: System Management Bus)140に結合されている。

10

#### 【0013】

ICH135は、周辺コンポーネント相互接続(PCI: Peripheral Component Interconnect)バス155に結合されている。スーパーI/O(S/0: super I/O)コントローラ170がICH135に結合されて、キーボードおよびマウス175のような入力装置への接続性を提供する。汎用I/O(GPIO: general-purpose I/O)バス195がICH135に結合されている。USBポート200が図のようにICH135に結合されている。プリンタ、スキャナ、ジョイスティックなどのようなUSBデバイスはこのバス上でシステム構成に追加されることができる。IDEドライブ210をコンピュータシステムに接続するために統合ドライブエレクトロニクス(IDE: integrated drive electronics)バス205がICH135に結合されている。論理的にはICH135は、単一の物理コンポーネント内の複数PCIデバイスのように見える。

20

#### 【0014】

プロセッサ105には命令セットアーキテクチャが含まれている。命令セットアーキテクチャ(ISA: instruction set architecture)はプロセッサ105のようなマイクロプロセッサの抽象モデルで、状態要素(レジスタ)およびそれらの状態要素を動作させる命令からなる。命令セットアーキテクチャは、マイクロプロセッサの振る舞いの抽象的な仕様を提供することによって、プログラマーおよびマイクロプロセッサ設計者の両方に対して、ソフトウェアとハードウェアの間の境界のはたらきをする。

30

#### 【0015】

シリコンチップ上で利用可能なトランジスタ数の向上は、汎用マイクロプロセッサへのマルチスレッドの導入を可能にした。マルチスレッドは2つの異なる仕方で実装されうる:チップレベル・マルチプロセッサ(CMP: chip-level multiprocessor)および同時マルチスレッド・プロセッサ(SMT: simultaneous multithreaded processor)である。このどちらもプロセッサ105として使用されうる。

#### 【0016】

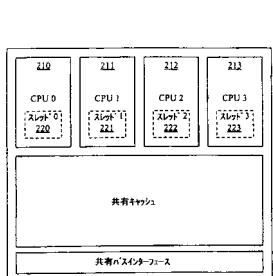

図2は、本発明のある実施形態に基づく、例示的なチップレベル・マルチプロセッサを示している。プロセッサ200のようなチップレベル・マルチプロセッサにおいては、複数のCPUコア210～213が単一のシリコンチップ200に集積されている。CPUコア210～213のそれぞれは独立した実行スレッド220～223を実行できるが、一部のリソース(キャッシュなど)がCPUコア210～213のうちの二つ以上によって共有されていてもよい。

40

#### 【0017】

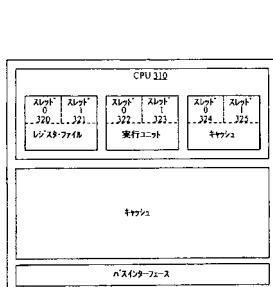

図3は、本発明のある実施形態に基づく、例示的な同時マルチスレッド・プロセッサ300を示している。プロセッサ105はプロセッサ300のような同時マルチスレッド・プロセッサであることができる。同時マルチスレッド・プロセッサ300においては、単一のCPUコア310が、複数の実行スレッドを実行できる。CPUコア310は、極度に細かい粒度でCPUリソースを共有する(しばしば各リソースでどのスレッドを処理するかをク

50

ロックごとに決定する)ことによって、ソフトウェアには二つ以上のプロセッサのように見える。

#### 【0018】

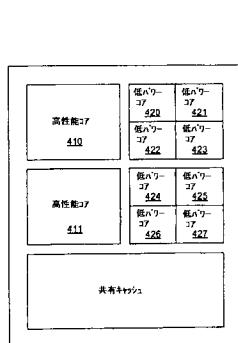

図4は、本発明のある実施形態に基づく、例示的な非対称マルチプロセッサ400を示している。プロセッサ105はマルチプロセッサ400のような非対称マルチプロセッサであることができる。CPUコア410～427が異なるマイクロアーキテクチャを有するがISAは同じであるようなチップレベル・マルチプロセッサ400を構築することが可能である。たとえば、少数の高性能CPUコア410～411が多数の低パワーCPUコア420～427と一緒に集積されてもよい。この種の設計は、高いスカラ-性能とともに高い総スループットを実現できる。2つの種類のCPUコアはソフトウェアには、通常の共有メモリ・スレッドとして、あるいはシェレッドとして、あるいは両者の何らかの組み合わせとして見える。命令セットアーキテクチャ(ISA)はプロセッサ105のようなマイクロプロセッサの抽象モデルであり、状態要素(レジスタ)およびそれらの状態要素に作用する命令からなる。ISAはマイクロプロセッサの振る舞いの抽象的な仕様を提供することによって、プログラマーおよびマイクロプロセッサ設計者の両方に対して、ソフトウェアとハードウェアの間の境界のはたらきをする。本プログラミング・モデルは、アプリケーション・プログラムが、直接的に複数の非対称CPUコアを制御することを可能にする。

10

#### 【0019】

##### 共有メモリ・プログラミング・モデル

20

従来のマルチスレッド・マイクロプロセッサは、従来の共有メモリ・マルチプロセッサ・システムと同じプログラミング・モデルを採用している。プログラミング・モデルは次のとおりである。マイクロプロセッサがOSに複数の実行スレッドを提供する。OSはこれらのスレッドを使って複数のアプリケーション(「プロセス」)を並行して走らせる、および/または単一のアプリケーションからの複数のスレッド(「マルチスレッド」)を並行して走らせる。いずれの場合にも、複数のスレッドはソフトウェアには独立したCPUのように見える。メインメモリはすべてのスレッドによって共有され、スレッド間の通信はメインメモリを通じて実行される。CPU内のハードウェアリソースも共有されうるが、共有はマイクロアーキテクチャによりソフトウェアからは隠されている。

#### 【0020】

30

伝統的な共有メモリ・マイクロプロセッサのプログラミング・モデルは広く理解され、多くのOSおよびアプリケーション・プログラムによってサポートされているものの、そのモデルはいくつかの不都合な点がある。それは:

- 1) スレッド間の通信がメインメモリを介して実行され、よって著しく遅い。キャッシングによって遅延の一部を軽減しうるが、共有を容易にするためにしばしばキャッシングのあるCPUコアから別のCPUコアに渡す必要がある。

- 2) スレッド間の同期がメモリベースのセマフォを使って実行され、よって著しく遅い。

- 3) スレッドの生成、破棄、サスPENDおよび再開がOSの介入を必要とし、よって著しく遅い。

4) CPUマルチスレッド機能の改良が上述したメモリ遅延およびOS遅延によって薄められてしまうため、マイクロプロセッサ発売元が最も効率的なマルチスレッド機能を提供できない。

40

#### 【0021】

##### マルチスレッド・アーキテクチャ拡張

従来システムに関する上に述べた理由のため、本方法およびシステムは、プロセッサのアーキテクチャを拡張して、マルチスレッド・アーキテクチャ拡張を通じてアーキテクチャ的に目に見えるマルチスレッド機能を含めるようにする。複数の同時的な実行スレッド、複数の命令ポインタ、単一の処理要素内のある種のアプリケーション状態(レジスタ)の複数のコピーが提供される。複数の実行スレッドは、既存の共有メモリ・スレッドとは

50

区別できるものであり、シュレッド (shred) すなわち共有リソース・スレッド (shared resource thread) と称される。

【0022】

本マルチスレッド・アーキテクチャ拡張 (multithreading architecture extensions) (その例は以下ではMAXと称される) は、既存のアーキテクチャ機能を含み、加えて複数の同時シュレッドをサポートすることになる。各シュレッドは独自の命令ポインタ、一般レジスタ、FPレジスタ、分枝レジスタ、述語レジスタおよびある種のアプリケーションレジスタを有している。シュレッドを生成および破棄するために非特権命令が生成される。シュレッド間の通信は、共有メモリに加えて共有レジスタを通じて実行される。本マルチスレッド・アーキテクチャ拡張は共有レジスタへの原子的なアクセスを保証するため、セマフォの必要性は低下する。さらに、本マルチスレッド・アーキテクチャ拡張は、インテル (登録商標) による 32 ビットアーキテクチャのような 32 ビットアーキテクチャと、やはりインテル (登録商標) による 64 ビットアーキテクチャのような 64 ビットアーキテクチャと、あるいは 16 ビットアーキテクチャとさえも使用できる。

10

【0023】

本発明のある実施形態に基づく、従来の共有メモリ・マルチプロセッサ・スレッドとシュレッドとの比較を次の表に示す。

【0024】

表 1

【0025】

【表 1】

20

| 動作     | 共有メモリ・マルチプロセッサ・スレッド | マルチスレッド・アーキテクチャ拡張                 |

|--------|---------------------|-----------------------------------|

| 生成、破棄  | OS コール              | 非特権命令                             |

| 通信     | 共有のメモリ              | 共有のレジスタおよびメモリ                     |

| 同期     | メモリ・セマフォ            | レジスタおよびメモリ・セマフォ。共有レジスタが原子的な更新を保証。 |

| システム状態 | 各スレッドに特有なシステム状態     | 全シュレッドで共有のシステム状態                  |

30

【0026】

本マルチスレッド・アーキテクチャ拡張が従来のアーキテクチャ拡張とは根本的に異なることに気づかれるであろう。従来のアーキテクチャ拡張がより多くの命令およびより多くのレジスタ (状態) を提供していたのに対し、マルチスレッド・アーキテクチャ拡張はより多くの実行単位を提供する。

【0027】

40

アプリケーションおよびシステム状態

プログラマーに見えるCPU状態は、2つの範疇に分けられる：アプリケーション状態およびシステム状態である。アプリケーション状態はアプリケーション・プログラムとOSの両方によって使用され、制御される一方、システム状態はOSによってのみ制御される。

【0028】

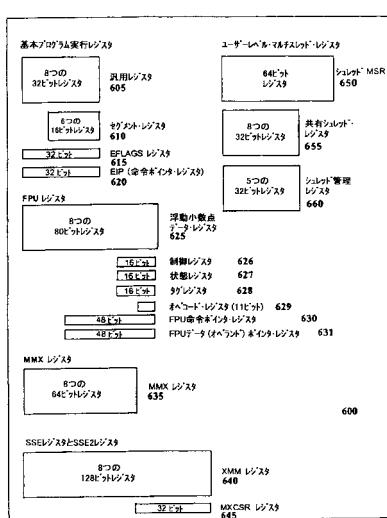

図 5 は、本発明のある実施形態に基づく、ユーザーレベルのマルチスレッドを提供するための例示的な実行環境を示す。実行環境 600 に含まれるレジスタのアプリケーション状態は次の表のようにまとめられる。

【0029】

表 2

50

【0030】

【表2】

| 32ビットアーキテクチャの<br>アプリケーション状態 | 名称                                                                            | 幅                                                       |

|-----------------------------|-------------------------------------------------------------------------------|---------------------------------------------------------|

| 汎用レジスタ<br>605               | EAX, EBX, ECX, EDX, EBP,<br>ESI, DEI, ESP                                     | 32ビット                                                   |

| 浮動小数点レジスタ<br>625            | ST0-7                                                                         | 80ビット                                                   |

| セグメントレジスタ<br>610            | CS, DS, ES, FS, GS, SS                                                        | 16ビット                                                   |

| フラグ・レジスタ<br>615             | EFLAGS                                                                        | 32ビット、あるビットは<br>アプリケーション                                |

| 命令ポインタ<br>620               | EIP                                                                           | 32ビット                                                   |

| FP制御および状態レジスタ<br>626～631    | CW 626,<br>SW 627,<br>TW 628,<br>FPオペコード 629,<br>命令ポインタ 630,<br>オペランドポインタ 631 | 16ビット,<br>16ビット,<br>16ビット,<br>11ビット,<br>48ビット,<br>48ビット |

| MMX レジスタ<br>635             | MM0-7                                                                         | 64ビット、<br>エイリアス ST0-7                                   |

| SSE レジスタ<br>640             | XMM0-7                                                                        | 128ビット                                                  |

| MXCSR レジスタ<br>645           | MXCSR                                                                         | 32ビット                                                   |

10

20

【0031】

ユーザーレベル・マルチスレッド・レジスタ 650～665 は、以下に、より詳細に述べる。

30

【0032】

32ビットアーキテクチャシステム状態は次のようにまとめられる。

【0033】

表3

【0034】

【表3】

| 32ビットアーキテクチャの<br>アプリケーション状態 | 名称              | 幅                                                                                                   |

|-----------------------------|-----------------|-----------------------------------------------------------------------------------------------------|

| 制御レジスタ<br>626               | CR0-CR4         | 32ビット                                                                                               |

| フラグ・レジスタ<br>615             | サブセット<br>EFLAGS | 32ビット、サブセット                                                                                         |

| メモリ管理レジスタ                   | GDTR, IDTR      | 48ビット                                                                                               |

| ローカル記述子表レジスタ、<br>タスクレジスタ    | LDTR, TR        | 16ビット                                                                                               |

| デバッグ・レジスタ                   | DR0-DR7         | 32ビット                                                                                               |

| モデル固有レジスタ<br>650            | MSR0-MSRN       | 64ビット<br>タイムスタンプカウンタ、APIC、機械チェック、メモリタイプ範囲レジスタ<br>(memory type range registers)、パフォーマンス監視のためのレジスタを含む |

| 共有レジスタ<br>655               | SH0-SH7         | 32ビット                                                                                               |

| シュレッド制御レジスタ<br>660          | SC0-SC4         | 32ビット                                                                                               |

10

20

各シュレッドについて、アプリケーション状態は2つの範疇に分けられる：シュレッド毎アプリケーション状態および共有アプリケーション状態である。ここで述べるMAXプログラミング・モデルはシュレッド毎アプリケーション状態の特有なインスタンスを提供する一方、共有アプリケーション状態は複数のシュレッドの間で共有される。システム状態のコピーは一つしかなく、所与のスレッドに対応するすべてのシュレッドが同じシステム状態を共有する。アプリケーションおよび状態の近似的な分割は次の表に呈示されている。

【0035】

表4

【0036】

【表4】

30

| 状態                        | タイプ                         |

|---------------------------|-----------------------------|

| 汎用レジスタ (プログラム可能なサブセット)    | シュレッド毎の占有状態                 |

| 浮動小数点レジスタ (プログラム可能なサブセット) |                             |

| SSE レジスタ (プログラム可能なサブセット)  |                             |

| 命令ポインタフラグ (アプリケーションサブセット) |                             |

| 汎用レジスタ (プログラム可能なサブセット)    | 複数のシュレッドの間で共有され、各スレッドにとって占有 |

| 浮動小数点レジスタ (プログラム可能なサブセット) |                             |

| SSE レジスタ (プログラム可能なサブセット)  |                             |

| 共有レジスタ (新)                |                             |

| フラグ (システムサブセット)           |                             |

| メモリ管理レジスタ                 |                             |

| アドレス変換 (TLB)              |                             |

| 現在特権レベル                   |                             |

| 制御レジスタ                    |                             |

| メインメモリ                    | 複数のスレッドの間で共有                |

40

50

## 【0037】

本マルチスレッド・アーキテクチャ拡張は、ほとんどのアプリケーション状態のプログラム可能な共有(sharing)または専有(privacy)を提供し、ソフトウェアが最良の分割を選択できる。プログラムはビットベクトルによって行われ、個々のレジスタが共有または専有のいずれかとして選択されることがある。ハードウェアの名称変更手段が、ビットベクトルによって指定される共有プールまたは専有プールのいずれかからレジスタを割り当てることができる。

## 【0038】

MAXの全体としての記憶要求は従来の同時マルチスレッド・プロセッサおよびチップレベル・マルチプロセッサより少ない。伝統的な共有メモリ・マルチプロセッサ・プログラミング・モデルを実装する同時マルチスレッド・プロセッサまたはチップレベル・マルチプロセッサではアプリケーションおよびシステム状態全体が複製される必要があるのに対し、MAXではシユレッド毎の専有アプリケーション状態だけが複製される。

10

## 【0039】

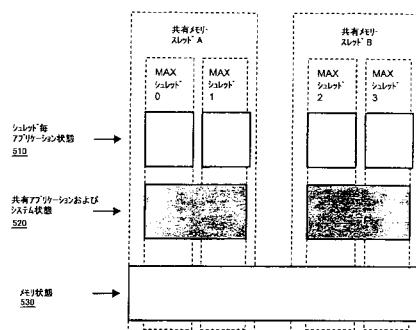

## シユレッド／スレッド階層

各共有メモリ・スレッドは複数のシユレッドからなる。シユレッドと共有メモリ・スレッドは2レベルの階層をなす。別の実施形態では、3レベルの階層が共有メモリMAXプロセッサのクラスタから構築できる。クラスタはメッセージ渡しを使って通信する。OSがスレッドのスケジューリングを扱い、一方、アプリケーション・プログラムがシユレッドのスケジューリングを扱う。任意の所与のシユレッドから見た他のシユレッドがローカルまたはリモートであるという意味において、シユレッドは非一様である。シユレッド毎アプリケーション状態は各シユレッドについて複製される。共有アプリケーションおよびシステム状態はローカルなシユレッドに共通であり、各共有メモリ・スレッドについて複製される。メモリ状態は一つのコピーのみを有する。

20

## 【0040】

図6は、本発明のある実施形態に基づく、シユレッドと共有メモリ・スレッドとの例示的な関係を示している。シユレッド毎アプリケーション状態510は各シユレッドについて複製される。共有アプリケーションおよびシステム状態520はローカルなシユレッドに共通であり、各共有メモリ・スレッドについて複製される。メモリ状態530は一つのコピーのみを有する。

30

## 【0041】

MAXプログラミング・モデルではシステム状態520が複数のシユレッドの間で共有されるため、該複数のシユレッドは同じプロセスに属する。本マルチスレッド・アーキテクチャ拡張は、マルチスレッド・アプリケーション、ライブラリおよび仮想マシンによって使用されることが意図されている。MAXプログラミング・モデルはこの種のソフトウェアに、そのシユレッドに対する先例のない度合いの制御および共有メモリでは実現できないパフォーマンス潜在力を与える。

## 【0042】

シユレッドはみな同じ特権レベルで走り、同じアドレス変換を共有するので、シユレッド間では保護確認は必要とされない。よって、伝統的な保護機構はシユレッド間通信の間には回避しうる。

40

## 【0043】

共有システム状態のため、同じスレッド上で異なるプロセスを走らせるためにMAXプログラミング・モデルを使うことはできない。このため、MAXプログラミング・モデルおよび従来の共有メモリ・プログラミング・モデルは同じシステム内で共存する。

## 【0044】

所与のCPUは有限個の物理シユレッドを提供するため、ソフトウェアは利用可能なシユレッド数を、ハードウェアスレッドの可視化と同様の仕方で可視化する。可視化の結果は、有限個の、並行して走っている物理シユレッドとともに潜在的には限りない数の仮想シユレッドを与える。

50

## 【0045】

## システムコール

OSコールは、アプリケーション・プログラムからOSに制御を移し、コンテキスト切り換えを実行することにより、従来式の仕方で処理されてもよい。MAXアーキテクチャでは、一つの主要な相違は、どのシェレッドでOSをコールしても、所与のシェレッドに関連するすべてのシェレッドの実行がサスペンドされるということである。同じシェレッドに属するすべてのシェレッドの状態を保存し、復元するのはOSの責任である。

## 【0046】

追加的な状態のため、コンテキスト切り換えのオーバーヘッドが増大する。コンテキスト切り換えのメモリ・フットプリントはシェレッド数に比例して増える。しかし、コンテキスト切り換え時間はあまり増加しない。各シェレッドが、他のシェレッドと並列に自分の状態を保存／復元するからである。コンテキスト切り換え機構は、複数のシーケンサを使った並列的な、状態の保存／復元を可能にする。OSそのものは複数のシェレッドを使用する。

## 【0047】

OSをコールするコストが増大するため、OSによって実行されていたある種の機能性はアプリケーション・プログラムに移行される。この機能性には、シェレッド維持およびある種の例外および割り込みの処理が含まれる。

## 【0048】

システムコールを実行するための代替的な実施形態は、コンテキスト切り換えが高価になりつつある一方、シェレッドが安価になりつつあるという観察に基づいている。この実施形態では、あるシェレッドがOSを走らせるのに専用とされ、第二のシェレッドがアプリケーション・プログラムを走らせるのに専用とされる。アプリケーション・プログラムのシェレッドがシステムコールを実行すると、それはOSシェレッドに（共有メモリを介して）メッセージを送り、応答メッセージを待つ。このようにして、メッセージ交換・待機機構が、従来式の制御移行・コンテキスト切り換え機構に取って代わる。どのシェレッドのアドレス変換も変更は必要とされない。恩恵は、あるシェレッドによってOSに送られたメッセージがローカルな他のシェレッドを乱さないということである。

## 【0049】

## 例外

従来のアーキテクチャでは、例外はアプリケーション・プログラムの実行をサスペンドし、OSの例外ハンドラを呼び出す。MAXプログラミング・モデルのもとでは、この振る舞いは望ましくない。あるシェレッドをサスペンドしてOSを呼び出すことは、（所与のシェレッドに関連する）あらゆるシェレッドもサスペンドしてしまうからである。

## 【0050】

この問題を解決するため、多くのタイプの例外を手当てる最初の機会をアプリケーション・プログラムに与える、新しいユーザーレベルの例外機構を導入する。ユーザーレベルの例外機構は、既存の例外タイプのいくつかが究極的にはアプリケーションそのものによって手当されているとの観察に基づいている。

## 【0051】

ユーザーレベルの例外機構のためには、例外がどう報告されるかが、例外がどう手当されるかから区別される。例外は次のように3つの範疇に分けられる。

1. アプリケーション・プログラムに報告され、アプリケーション・プログラムによって手当される例外。たとえば、0による除算例外はその例外を引き起こしたアプリケーションに報告され、手当てもそのアプリケーションによってなされる。OSの関与は必要でもないし、望ましくもない。

2. アプリケーション・プログラムに報告され、その後、アプリケーション・プログラムが手当るためにOSをコールする必要のある例外。アプリケーションによって起こされる

10

20

30

40

50

ページフォールトはアプリケーションに報告されてもよいが、ページ内でスワップするためにはアプリケーション・プログラムはOSをコールする必要がある。

3. OSに報告され、OSによって手当てされる必要のある例外。セキュリティ上の理由で、ハードウェア割り込みはOSに報告される必要がある。システムコール（ソフトウェア割り込み）は明らかにOSに報告される必要がある。

【0052】

次の表は、上記の3つの各範疇の例外を示している。「キャッシュミスに際しての読み込み例外」および「微細粒度タイマー」の例外タイプは、本発明のある実施形態に関係した例外タイプとして与えられている。

【0053】

表5

【0054】

【表5】

| 例外タイプ                    | 報告先      | 手当て主体    |

|--------------------------|----------|----------|

| 0による除算、オーバーフロー、バインド、FP例外 | アプリケーション | アプリケーション |

| アライメント確認                 | アプリケーション | アプリケーション |

| 無効なオペコード                 | アプリケーション | アプリケーション |

| キャッシュミスに際しての読み込み例外       | アプリケーション | アプリケーション |

| 微細粒度のタイマー                | アプリケーション | アプリケーション |

| スタックセグメントフォールト           | アプリケーション | システム     |

| 一般保護                     | アプリケーション | システム     |

| ページフォールト                 | アプリケーション | システム     |

| 二重フォールト                  | アプリケーション | システム     |

| デバイス利用不能                 | アプリケーション | システム     |

| ハードウェア割り込み               | システム     | システム     |

| マスク不能割り込み                | システム     | システム     |

| ソフトウェア割り込み(INTn)         | システム     | システム     |

10

20

30

【0055】

アプリケーション・プログラムに報告された例外は、選択的にアプリケーション内で処理され、あるいは処理のためにOSに渡される。後者の場合、アプリケーション・プログラムは例外（ページフォールトのような）に応答してOSに手当てを明示的に要求するシステムコールを実行する。これは、暗黙のうちにOSがアプリケーションに代わってそのような手当てを実行する伝統的なアプローチとは対照的である。ネストされた例外を避けるため、例外をOSに中継するアプリケーション・コードはそれ自身が追加的な例外を招くことはないという特別な規定が設けられる。ユーザーレベルの例外機構は、影のレジスタセットにおけるCPUレジスタの最少数およびプロセッサ・ベクトルを固定位置に保存する。

40

【0056】

仮想マシン

仮想マシンとマルチスレッド・アーキテクチャ拡張のここでの諸実施形態とは、互いに制約を課す。仮想マシンは、ソフトウェアが仮想化されているリソースにアクセスしようとするときには常に例外を発生させ、例外処理はシェレッドに対して著しいパフォーマンス上の影響をもつ。

【0057】

仮想マシンでは、特権命令の実行または特権プロセッサ状態へのアクセスが例外を発生

50

させる。例外は仮想マシン・モニタに報告される（そしてそれによって手当てされる）必要がある。MAXでは、OS（および仮想マシン・モニタ）によって手当てされる例外は、所与のスレッドに関連するあらゆるシュレッドをサスPENDさせる。仮想マシン・モニタは複数のシュレッドの存在を理解する。仮想マシンのアーキテクチャは、非特権命令およびプロセッサ・リソースについて発生される例外の数を最小化する。

#### 【 0 0 5 8 】

##### デッドロック

MAXアーキテクチャではシュレッドがローカルな他のシュレッドによってサスPENDされることができるので、デッドロック回避が複雑になる。アプリケーション・ソフトウェアは、一つのシュレッドがOSに手当てされる例外またはシステムコールを被っても、ローカルなすべてのシュレッドをサスPENDしてしまうデッドロックが生じないことを保証する。

10

#### 【 0 0 5 9 】

ローカルな（シュレッド間の）通信および同期は、リモートの（スレッド間の）通信および同期とは区別される。ローカルな通信は、共有レジスタ 655（図5に示してある）または共有メモリのいずれかを使って実行される。リモートの通信は共有メモリを使って実行される。ローカルなデータ同期は原子的なレジスタ更新、レジスタ・セマフォまたはメモリ・セマフォを使って実行される。リモートのデータ同期はメモリ・セマフォを使って実行される。

20

#### 【 0 0 6 0 】

ローカルおよびリモートのシュレッド制御（生成、破棄）はいずれもMAX命令を使って実行される。シュレッド制御は、`wait()`または`yield()`のためにOSをコールすることはしない。それは所与のスレッド上のあらゆるシュレッドをサスPENDするという意図しない効果を有しうるからである。スレッド維持のために使われるOSコールは、ユーザーレベルのシュレッド・ライブラリへのコールで置き換えられる。シュレッド・ライブラリは今度は、必要に応じてスレッドを生成および破棄するためにOSをコールする。

#### 【 0 0 6 1 】

##### シュレッドとファイバ

30

シュレッドは、従来のOSで実装されるファイバとは異なる。相違は次の表にまとめられている。

#### 【 0 0 6 2 】

##### 表 6

#### 【 0 0 6 3 】

【表6】

| 特性       | ファイバ                                                 | シュレッド                                                                 |

|----------|------------------------------------------------------|-----------------------------------------------------------------------|

| 生成       | 一つのスレッドが複数のファイバを生成しうる                                | 一つのスレッドが複数のシュレッドを生成しうる                                                |

| 同時並行     | 一つのスレッドはどの時点でも一つのファイバを走らせられる                         | 一つのスレッドは複数のシュレッドを同時に走らせられる                                            |

| スケジューリング | ファイバのスケジューリングは、協力的マルチタスク機構を使ってソフトウェアにより行われる          | シュレッドのスケジューリングは、同時マルチスレッドまたはチップレベル・マルチプロセシングを使ってハードウェアにより行われる         |

| 状態       | 各ファイバは独自の占有アプリケーション状態をもつ                             | 各シュレッドは独自の占有アプリケーション状態をもつ                                             |

| 状態保存     | 現在走っているファイバの状態がレジスタに保存される。アクティブでないファイバの状態はメモリに保存される。 | 現在走っている物理的シュレッドの状態のそれぞれがオンチップレジスタに保存される。アクティブでない仮想シュレッドの状態はメモリに保存される。 |

| 状態管理     | OSが現在走っているファイバの状態をコンテキスト切り換えに際して保存／復元する              | OSがあらゆるシュレッドのアプリケーション状態をコンテキスト切り換えに際して保存／復元する                         |

10

20

## 【0064】

## ハードウェア実装

マルチスレッド・アーキテクチャ拡張をサポートするマイクロプロセッサの実装は、チップレベル・マルチプロセッサ (CMP: chip-level multiprocessor) および同時マルチスレッド・プロセッサ (SMT: simultaneous multithreaded processor) の形をとることができ。従来のCMPおよびSMTプロセッサは、CPUリソースの共有をソフトウェアから隠そうとしている。これに対し、マルチスレッド・アーキテクチャ拡張のここでの諸実施形態を実装されたときには、プロセッサは共有をアーキテクチャの一部としてさらけ出す。

30

## 【0065】

MAXプロセッサをチップレベル・マルチプロセッサとして実装するため、システム状態の複数のコピーをCPUコアどうしの間で同期状態に保つために、ブロードキャスト機構が使われる。共有されるアプリケーションおよびシステム状態のために高速通信バスが導入される。オンチップ通信はオフチップのメモリに比べて高速なため、これらの通信バスはMAXプロセッサに、共有メモリ・マルチプロセッサに対するパフォーマンス上の優位性を与える。

40

## 【0066】

MAXプロセッサを同時マルチスレッド・プロセッサとして実装することは、ハードウェアがすでに必要なリソース共有を提供しているので可能である。MAXの実装を、マルチスレッドの32ビットプロセッサ上でほとんど完全にマイクロコードで行うことも可能である。

## 【0067】

ある実施形態によれば、本方法およびシステムは、複数のシュレッドの間でシステムコールおよび例外 (OSに報告されるもの) の優先順位付けを可能にする。それにより、いかなる時点においても、一つのシュレッドの要求だけが手当てされる。システム状態は一時には一つのOSサービス要求しか扱えないので、優先順位付けおよび一つの要求の選択は必

50

要である。たとえば、シュレッド 1 およびシュレッド 2 が同時にシステムコールを行うとする。優先順位付け手段が、シュレッド 1 のシステムコールだけが実行されたがシュレッド 2 のシステムコールはまだ実行が始まっていることを保証する。公正さへの配慮のため、優先順位付け手段はラウンドロビン選択アルゴリズムを採用するが、他の選択アルゴリズムを使ってもよい。

#### 【 0 0 6 8 】

##### スケーラビリティ

MAXプログラミング・モデルのスケーラビリティは次によって決定される。

- 1 ) コンテキスト切り換えに際して保存 / 復元するのが実行可能である状態の量 10

- 2 ) コンテキスト切り換えの間に所与のスレッドに関連するあらゆるシュレッドをサスペンドすることから帰結する、並列度の減少

- 3 ) シュレッド間通信

シュレッド数が増加するにつれ、コンテキスト切り換えに際して保存 / 復元される必要のある状態の量が増加し、全シュレッドをサスペンドする結果として失われる潜在的な並列度が増加する。これら 2 つの因子が実際的なシュレッド数を制限することになる。

#### 【 0 0 6 9 】

シュレッド間通信もスケーラビリティを制限する。該通信はオンチップリソースを使って実行されるからである。対照的に、伝統的な共有メモリ・マルチプロセッサ・モデルのスケーラビリティはオフチップ通信によって制限される。 20

#### 【 0 0 7 0 】

##### 共有分類

次の表には、シュレッドのアーキテクチャ、実装およびソフトウェア使用におけるさまざまな自由度での分類が呈示されている。

#### 【 0 0 7 1 】

##### 表 7

#### 【 0 0 7 2 】

【表7】

| 属性                    | オプション1                                | オプション2                                                    | オプション3                               |

|-----------------------|---------------------------------------|-----------------------------------------------------------|--------------------------------------|

| 命令セット<br>アーキテクチャ      | 均一……全シュレッドが同じ命令セットアーキテクチャを実装          | 不均一……諸シュレッドが異なる命令セットアーキテクチャを実装                            |                                      |

| マイクロ<br>アーキテクチャ<br>実装 | 対称的……全シュレッドが同じハードウェア・マイクロアーキテクチャで走る   | 非対称的……諸シュレッドが異なるハードウェア・マイクロアーキテクチャで走る                     |                                      |

| アプリケーション<br>並列度       | シーケンシャル……従来式の逐次コード                    | パラレル……並列化されたコード                                           |                                      |

| シュレッド生成               | プログラマーが生成……シュレッドはプログラマーによって明示的に生成される  | コンパイル……シュレッドはコンパイラによって自動的に生成される                           | 固定機能……シュレッドはガーベッジ・コレクションのような特定の機能の専用 |

| アーキテクチャの<br>正しさ       | アーキテクチャ上……全シュレッドがプログラムのアーキテクチャの正しさに貢献 | ヒント……いくつかのシュレッドはアーキテクチャ上の正しさに貢献するが、他のシュレッドはパフォーマンスにのみ貢献する |                                      |

| 入出力                   | 計算。シュレッドは計算のみを行う。                     | I/O。シュレッドは計算に加えて入出力も行う。                                   |                                      |

10

20

30

## 【0073】

MAXアーキテクチャの2つの異なる種類が区別される：均一と不均一である。均一シュレッドは、すべてのシュレッドが同じ命令セットを実行するという点で均一マルチプロセッサと同様である。不均一マルチプロセッサと同様の仕方で、不均一シュレッドも可能である。たとえば、不均一シュレッドは：

- ・32ビットプロセッサとネットワークプロセッサ、

- ・32ビットプロセッサと64ビットプロセッサ、

- の間で構築されうる。

## 【0074】

同様に、根底にあるマイクロアーキテクチャは対称的または非対称的のどちらでもあります。後者の場合の例としては、若干の大規模な高性能CPUコアと多数の小型低パワーCPUコアを含む、図4に示したようなチップレベル・マルチプロセッサがある。

## 【0075】

## 用途モデル

次の表は、本マルチスレッド・アーキテクチャ拡張の諸実施形態のためのいくつかの用途モデルをまとめている。

40

## 【0076】

## 表8

## 【0077】

【表 8】

| 用途モデル                  | 分類                                          | 説明                                                                                 | 効果                                  |

|------------------------|---------------------------------------------|------------------------------------------------------------------------------------|-------------------------------------|

| プリフェッч                 | 均一 ISA、シーケンシャルコード、コンパイラ生成、ヒント、計算            | ヘルパー・スレッドがメイン・スレッドに先立ってメモリ位置をプリフェッчする。ヘルパー・スレッドはコンパイラによって生成される。                    | キャッシュミスでかなりの時間が使われるスカラーコードを高速化      |

| 従来式スレッドの置き換え           | 均一 ISA、パラレルコード、プログラマー生成、アーキテクチャ上、計算         | 従来式の共有メモリ・スレッドの代わりにシェレッドが使われる。OSではなくライブラリがスレッドサービスを提供する。                           | スレッドのあるコードを高速化。スレッド・プリミティブは数桁速くなる。  |

| コンパイラのための専用実行リソース      | 均一 ISA、シーケンシャルコード、コンパイラ生成、アーキテクチャ上、計算       | コンパイラがスカラーソースコードから複数のシェレッドを生成する。                                                   | コンパイラがシェレッドに対する直接的な制御を有する。          |

| 管理されたランタイム環境のための専用スレッド | 均一 ISA、固定機能、アーキテクチャ上、計算                     | シェレッドは管理されたランタイム機能専用とされる。たとえば、ジャストインタイム翻訳およびガーベッジ・コレクションは専用シェレッドを使って実行される。         | 翻訳およびガーベッジ・コレクションのシェレッドが本質的に無償になる。  |

| 並列プログラミング言語            | 均一 ISA、パラレルコード、プログラマー生成、アーキテクチャ上、計算         | 複数のシェレッドにコンパイルされる並列コードをプログラマーが作成。                                                  | スレッド・プリミティブが命令として使われるのに十分な速さになる。    |

| 統合された I/O 機能をもつ CPU    | 不均一 ISA、パラレルコード、プログラマー生成、アーキテクチャ上、入出力       | I/O 機能がアプリケーション・プログラムによって直接実行される。たとえば、グラフィックおよびネットワーク処理。                           | I/O 機能を CPU アーキテクチャに直接統合することを可能にする。 |

| 同時マルチ ISA の CPU        | 不均一 ISA、非対称マイクロアーキテクチャ、プログラマー生成、アーキテクチャ上、計算 | 単一の CPU が複数の ISA、たとえば 32 ビットアーキテクチャと 64 ビットアーキテクチャを実装。各 ISA はプログラマーにはシェレッドとして利用可能。 | 興味深い可能性はあるが、有用ではないかもしだれない。          |

| 非対称コアマルチプロセッサ          | 均一 ISA、非対称マイクロアーキテクチャ、アーキテクチャ上、計算           | CMP が複数のコア、たとえば高性能および低パワーのコア混合を実装する。                                               | 良好なスカラーおよびスループット性能を実現。              |

【0078】

プリフェッч

プリフェッч用途モデルでは、メイン・スレッドは一つまたは複数のヘルパー・スレッ

ドを生み、それがメインメモリからキャッシュラインをプリフェッチするのに使われる。ヘルパー・スレッドが生み出されるのは、メイン・スレッドでのキャッシュミスに応答してである。メインメモリへのアクセスは完了するのに数百から1000CPUクロックを必要とするので、キャッシュミスになった読み込みを失敗としてメインメモリに進むためのアーキテクチャ上の備えがされていない限り、スカラーコードの実行はメインメモリアクセスの間事実上停止することになる。

#### 【 0 0 7 9 】

##### 従来式スレッドの置き換え

シュレッドは、従来式スレッドの高性能な置き換えとして、マルチスレッド・アプリケーションによって使われることがありうる。ユーザー・レベルのソフトウェア・ライブラリが、以前にOSによって実行されたシュレッド管理機能（生成、破棄など）を実行するためには提供される。ライブラリは追加的なスレッドを要求するために、必要に応じてOSをコールするほか、シュレッド命令を使用する。ソフトウェア・ライブラリのコールは、コンテキスト切り換えが必要ないためOSコールよりもずっと高速である。

10

#### 【 0 0 8 0 】

##### コンパイラのための専用実行リソース

コンパイラは、レジスタのようなほかのプロセッサ・リソースを使用するのと同じ仕方でシュレッドを使ってもよい。たとえば、コンパイラはプロセッサを8つの整数レジスタ、8つの浮動小数点レジスタ、8つのSSEレジスタおよび4つのシュレッドをもつものと見ることができる。シュレッドをリソースとして扱うことにより、コンパイラは、レジスタ割り当てと類似の仕方でシュレッドを割り当てる。レジスタと同様、アプリケーション・プログラムがハードウェアが提供するよりも多くの仮想シュレッドを要求する場合にシュレッドを補助記憶に散布／充填するための何らかの機構が必要である。従来のアーキテクチャでは、制御の流れは一つしかないので、通常プロセッサ・リソースとは見なされない。

20

#### 【 0 0 8 1 】

##### 管理されたランタイム環境のための専用スレッド

30

管理されたランタイム環境では、シュレッドはガーベッジ・コレクション、ジャストインタイム（just-in-time）コンパイルおよびプロファイリングのような機能の専用とされる。シュレッドはそのような機能を本質的に「無償で」実行する。シュレッドは命令セットアーキテクチャ（ISA）の一部として提供されているからである。ISAは、プロセッサのうち、プログラマーまたはコンパイラ作者に見える部分である。ISAはソフトウェアおよびハードウェアの間の境界のはたらきをする。

#### 【 0 0 8 2 】

##### 並列プログラミング言語

MAXは並列プログラミング言語およびハードウェア記述言語を直接サポートする。たとえば、iHDLまたはVerilogコンパイラは、ソースコードが明示的に並列であるため、直接的に複数シュレッドのためのコードを生成する。

40

#### 【 0 0 8 3 】

チップレベル・マルチプロセッサによって可能となったスレッドの増殖はマルチスレッドのための言語サポートにつながる。そのようなサポートはOSおよびランタイム・ライブラリのコールを通じて提供される。マルチスレッドのための言語サポートはメインストリームの汎用プログラミング言語に移行される。

#### 【 0 0 8 4 】

##### 統合されたI/O機能をもつCPU

50

シュレッドはネットワーク・コプロセッサのようなI/O機能を実装するために使われる。シュレッドとして実装されるネットワーク・コプロセッサの一つの重要な相違点は、I/Oデバイスとしてではなく、CPUの一部として見えるということである。

#### 【0085】

従来システムでは、アプリケーション・プログラムが入出力を要求するとき、アプリケーション・プログラムはAPI (application program interface [ アプリケーション・プログラム・インターフェース ] ) を使ってOSをコールする。OSは今度はデバイスドライバをコールして、そのデバイスドライバが要求をI/Oデバイスに送る。OSは複数のアプリケーション・プログラムからのI/O要求を待ち行列化またはシリアル化し、I/Oデバイスが一時には一つの（あるいは有限個の）要求のみを処理することを保証する役目を負う。これは、CPU状態が複数のアプリケーションの間で時間多重化されるのに対してI/Oデバイスの状態がシステムにとってグローバルであるため、必要なことである。

#### 【0086】

不均一シュレッドとして実装されるI/Oデバイスでは、I/Oデバイスの状態はCPUのアプリケーション状態の拡張として扱われる。アプリケーション・プログラムは、CPUのアプリケーション状態およびI/Oデバイス状態の両方を直接制御する。アプリケーション状態およびI/O状態の両方がコンテキスト切り換えに際してはOSによって保存／復元される。I/Oデバイスは、その状態がいくつかのアプリケーションの間で悪影響なしに時間多重化されることができるよう構成される。

10

20

#### 【0087】

##### 同時マルチISAのCPU

64ビットアーキテクチャが、32ビットアーキテクチャ・アプリケーション・アーキテクチャならびに新しい64ビット命令セットを「シームレス」として知られる機構を通じて含むよう定義される。32ビットアーキテクチャの命令セットとの両立により、64ビットアーキテクチャのプロセッサは新しい64ビットアーキテクチャのアプリケーションのほか既存の32ビットアーキテクチャのアプリケーションも走らせることができる。

#### 【0088】

現行の定義のもとでは、64ビットアーキテクチャのCPUは、どの時点でも、64ビットアーキテクチャのスレッドまたは32ビットアーキテクチャのスレッドのいずれかを走らせる。2つのISAの間の切り換えは、64ビットアーキテクチャbr.ia ( 32ビットアーキテクチャへの分岐 ) および32ビットアーキテクチャjmpc ( 64ビットアーキテクチャへのジャンプ ) を介して達成される。32ビットアーキテクチャのレジスタは64ビットアーキテクチャのレジスタにマッピングされるので、状態のコピーは一つしか必要とされない。

30

#### 【0089】

いかなる時点においても二つ以上の命令セットアーキテクチャが走っているマルチISAのCPUを創り出すことが可能である。これは、64ビットアーキテクチャISAのためのシュレッドと32ビットアーキテクチャISAのための第二のシュレッドを使うことによって達成しうる。均一シュレッドの場合のように、64ビットアーキテクチャのシュレッドと32ビットアーキテクチャのシュレッドの両方のために相異なるアプリケーション状態を提供する必要がある。64ビットアーキテクチャのシュレッドと32ビットアーキテクチャのシュレッドは同時に走る。

40

#### 【0090】

上記のマルチスレッド・アーキテクチャ拡張を通じたユーザー・レベルのマルチスレッドを提供するための本方法およびシステムの諸特徴を述べたので、以下では32ビットシステムのための実施形態を提供する。

#### 【0091】

##### 32ビットアーキテクチャの実施形態

50

IA-32アーキテクチャを参照しつつ記述しているが、ここに記載される方法およびシステムはIA-64アーキテクチャのような他のアーキテクチャにも適用されうることを読者は理解する。さらに、読者は、本発明のある実施形態に基づく例示的な実行環境を理解するために図5に戻るよう指示される。IA-32にユーザーレベルのマルチスレッド機能をもたらすために、いくつかのレジスタ650～660とともに、少数の命令が、IA-32のISAに追加される。

#### 【0092】

マルチスレッド・アーキテクチャ拡張は次の諸状態からなる：

- ・拡張を有効／無効にするためにOSまたはBIOSによって使われるモデル固有レジスタ650 (MAX\_SHRED\_ENABLE) 10

- ・プロセッサが拡張を実装しているかどうかと利用可能な物理シュレッド数とを示す、CPUID拡張機能情報の3ビット

- ・各シュレッドが独自に専有アプリケーション状態のコピーを有するようにする、アプリケーション状態 (EAX, EBXなど) のほとんどの複製

- ・シュレッド間の通信および同期のために使われうる、共有レジスタSH0-SH7 655の組

- ・シュレッド管理のために使われる制御レジスタSC0-SC4 660の組

#### 【0093】

このマルチスレッド・アーキテクチャ拡張は次の命令を有する。

- ・シュレッドの生成／破棄 : forkshred、haltshred、killshred、joinshred、getshred 20

- ・通信 : 共有レジスタ655への／からの移動 (mov) 、共有レジスタ655への／からの同期移動

- ・同期 (セマフォ) : cmpxshgsh、xaddsh、xchgsh

- ・信号伝送 : signalshred

- ・マルチシュレッドモード (multi-shredded mode) への／からの遷移 : entermsm、exitmsm

- ・状態管理 : shsave、shrestore

- ・雑 : シュレッド制御レジスタへの／からの移動

#### 【0094】

さらに、IA-32機構には以下の機能が設けられる。

- ・IA-32例外機構は、例外に際して（あてはまる場合には）マルチシュレッドモードを終了して全シュレッド状態を保存する

- ・IA-32のIRET命令は（あてはまる場合には）全シュレッド状態を復元してマルチシュレッドモードに戻る

- ・ユーザーレベルの例外機構が導入されている。

#### 【0095】

##### 構成設定

モデル固有レジスタ (MSR: model specific register) 650 はマルチスレッド・アーキテクチャ拡張を可能にするために使われる。MSRは下記に記述される。

#### 【0096】

表9

#### 【0097】

【表 9】

| レジスタ<br>アドレス<br>(十六進) | レジスタ<br>アドレス<br>(十進) | レジスタ名フィールド<br>およびフラグ | 共有<br>／<br>特有 | ビットの説明                                                                                       |

|-----------------------|----------------------|----------------------|---------------|----------------------------------------------------------------------------------------------|

| 1F0H                  | 496                  | MAX_SHRED_ENABLE     | 共有            | ビット0がマルチスレッド・アーキテクチャ拡張を有効にする。リセット時に0に初期化される。OSまたはBIOSがこのレジスタに1を書き込むことによって明示的にMAXを有効にする必要がある。 |

10

## 【0098】

シュレッドMSR 650のようなモデル固有レジスタは、特権レベル0でのみ書き込みおよび読み出しが行われる。マルチスレッド・アーキテクチャ拡張が有効にされていなければ、旧来のコードの実行はシュレッド番号0に制限される。

## 【0099】

表10

## 【0100】

## 【表10】

20

| 初期のEAXの値 | プロセッサについて与えられる情報                                                                                                                                                                                                     |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1H       | <p>EAXバージョン情報 (型、ファミリー、モデル、ステッピングID)<br/>EBX<br/>ビット7-0: ブランド指数<br/>ビット15-8: CLFLUSH ラインサイズ (値8=キャッシュライン<br/>サイズはバイト単位)<br/>ビット23-16: 物理プロセッサあたりの論理プロセッサ数<br/>ビット31-24: ローカルなAPIC ID<br/>ECX 拡張機能情報<br/>EDX 機能情報</p> |

30

## 【0101】

CPUID

IA-32のCPUID命令は、設けられている物理スレッド数の計数とともに、プロセッサがマルチスレッド・アーキテクチャ拡張をサポートしていることの指標を返すよう修正される。これはECXにおいて返される拡張機能情報に3ビット(NSHRED)を追加することによってなされる。CPUID命令によって返される情報は次の表に与えられている。

## 【0102】

表11

## 【0103】

40

## 【表 1 1】

| 初期の EAX の値 | プロセッサについて与えられる情報                                                                                                                                                                                              |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1H         | EAX バージョン情報 (型、ファミリー、モデル、ステッピング ID)<br>EBX<br>ビット 7-0: ブランド指数<br>ビット 15-8: CLFLUSH ラインサイズ (値 8=キャッシュライン<br>サイズはバイト単位)<br>ビット 23-16: 物理プロセッサあたりの論理プロセッサ数<br>ビット 31-24: ローカルな APIC ID<br>ECX 拡張機能情報<br>EDX 機能情報 |

10

## 【0 1 0 4】

表 1 2

## 【0 1 0 5】

## 【表 1 2】

| ビット番号 | 二一モニック | 説明                                                                                                                                                                                              |

|-------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18:16 | NSHRED | ハードウェアによってサポートされる物理シュレッド数を示す<br>3 ビット<br>000: 1 シュレッド/スレッド<br>001: 2 シュレッド/スレッド<br>010: 4 シュレッド/スレッド<br>011: 8 シュレッド/スレッド<br>100: 16 シュレッド/スレッド<br>101: 32 シュレッド/スレッド<br>110: リザーブ<br>111: リザーブ |

20

## 【0 1 0 6】

30

マルチスレッド・アーキテクチャ拡張が (MAX\_SHRED\_ENABLE MSRを通じて) 有効にされていない場合、拡張機能情報はNSHREDについては000を返す。

## 【0 1 0 7】

## アーキテクチャ状態

マルチスレッド・アーキテクチャ拡張は、全状態を 3 つの範疇のうちの一つに置く。

- 各シュレッドの専有

- ローカルなシュレッドの間で共有

- 全シュレッドの間で共有

IA-32状態の前記範疇のそれぞれの内訳は上掲の表 2 に示されている。シュレッドの専有という状態は、シュレッドごとに一回繰り返される。シュレッドの専有という状態は、各シュレッドにとっての完全な専有である。特に、アーキテクチャは、よそのシュレッドからあるシュレッドの専有レジスタの読み出しや書き込みを個々に行ういかなる命令も提供しない。アーキテクチャが提供するshssaveおよびshrestore命令は、全シュレッドの専有状態のメモリへの読み出しおよび書き込みを集合的に行うためのものであるが、これらの命令は单一シュレッドモードにおいてしか実行されない。シュレッドの共有状態は上掲の表 3 に示されている。

40

## 【0 1 0 8】

共有レジスタの組SH0-SH7 6 5 5 は、シュレッド間の通信および同期のために使われる。これらのレジスタ 6 5 5 は共有レジスタへのMOV命令および共有レジスタからのMOV命

50

令を通じて書き込みおよび読み出しが行われる。SH0-SH7レジスタ 655 は 32 ビットの整数値を保存する。ある実施形態によれば、80 ビットの浮動小数点 625 および 128 ビットの SSE データ 640 がメインメモリを通じて共有される。

【0109】

シュレッド制御レジスタの組 SC0-SC4 660 が提供される。これらのレジスタは次のように定義される。

【0110】

表 13

【0111】

【表 13】

10

| レジスタ | 名称                  | 説明                                                                                                                                                                                                       |

|------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SC0  | シュレッド実行レジスタ         | SC0 はシュレッドごとに 1 ビットをもつビットベクトルを含む。ビット 0 がシュレッド 0 に、ビット 1 がシュレッド 1 に、などと対応する。各ビットは、対応するシュレッドが現在走っているか停止しているかを示す。マルチスレッド・アーキテクチャ拡張が MAX_SHRED_ENABLE MSR を通じて無効にされているときは、SC0 はシュレッド 0 のみが有効であることを示す値 1 を含む。 |

| SC1  | シュレッド実行割り込みレジスタ     | マルチシュレッドから單一シュレッドモードに遷移する際に SC0 の内容が SC1 にコピーされ、單一シュレッドからマルチシュレッドモードに遷移する際に SC1 の内容が SC0 にコピーされる。                                                                                                        |

| SC2  | シュレッド状態保存／復元ポインタ    | SC2 はメモリ中でのシュレッド状態保存／復元領域をポイントする。このメモリ領域は、コンテキスト切り換えの際にすべての走っているシュレッドの状態を保存および復元するために使われる。                                                                                                               |

| SC3  | 共有レジスタ空き／充満ビット      | SC3 は共有レジスタのための空き／充満のビットを含む。ビット 0 は sh0 に、ビット 1 は sh1 に、などと対応する。                                                                                                                                         |

| SC4  | ユーザーレベル割り込み表ベースアドレス | SC4 はユーザーレベルの割り込み表のためのベースアドレスをポイントする。                                                                                                                                                                    |

20

30

【0112】

表 14

【0113】

【表 1 4】

| ビット   | 型    | 複製 | 二モニック | 説明                                       |

|-------|------|----|-------|------------------------------------------|

| 0     | 状態   | Y  | CF    | 桁上げフラグ (Carry flag)                      |

| 2     | 状態   | Y  | PF    | parity フラグ (Parity flag)                 |

| 4     | 状態   | Y  | AF    | 補助桁上げフラグ (Auxiliary carry flag)          |

| 6     | 状態   | Y  | ZF    | 零フラグ (Zero flag)                         |

| 7     | 状態   | Y  | SF    | 符号フラグ (Sign flag)                        |

| 8     | システム | Y  | TF    | トラップフラグ (Trap flag)                      |

| 9     | システム | N  | IE    | 割り込み有効フラグ (Interrupt enable flag)        |

| 10    | 制御   | Y  | DF    | 方向フラグ (Direction flag)                   |

| 11    | 状態   | Y  | OF    | オーバーフローフラグ (Overflow flag)               |

| 13:12 | システム | N  | IOPL  | 入出力特権フラグ (IO privilege flag)             |

| 14    | システム | N  | NT    | ネストされたタスク (Nested task)                  |

| 16    | システム | N  | RF    | 再開フラグ (Resume flag)                      |

| 17    | システム | N  | VM    | 仮想 86 モード (Virtual 86 mode)              |

| 18    | システム | N  | AC    | アライメント確認 (Alignment check)               |

| 19    | システム | N  | VIF   | 仮想割り込みフラグ (Virtual interrupt flag)       |

| 20    | システム | N  | VIP   | 仮想割り込みペンドィング (Virtual interrupt pending) |

| 21    | システム | N  | ID    | ID フラグ (ID flag)                         |

10

20

## 【0114】

Yと記されたフラグはシュレッドごとに複製される。Nと記されたフラグは全シュレッドによって共有される単一のコピーを有する。

## 【0115】

32ビットのEFLAGSレジスタ615は一群の状態フラグ、一つの制御フラグおよび一群のシステムフラグを含んでいる。プロセッサ105の初期化 (RESETピンまたはINITピンをアサートすることによる)直後のEFLAGSレジスタ615は00000002Hである。このレジスタ615のビット1, 3, 5, 15および22から31まではリザーブされており、ソフトウェアはこれらのビットのいずれの状態も使ったり依存したりするべきではない。

30

## 【0116】

EFLAGSレジスタ615におけるフラグのいくつかは、専用の命令を使って直接修正できる。レジスタ全体を直接調査または修正できるようにするための命令はない。しかし、次の諸命令は、一群のフラグをプロシージャ・スタックまたはEAXレジスタへ、そしてそれから移動させるのに使うことができる: LAHF, SAHF, PUSHF, PUSHFD, POPFおよびPOPFD。EFLAGSレジスタ615の内容がプロシージャ・スタックまたはEAXレジスタに転送されたのち、フラグは、プロセッサのビット操作命令 (BT, BTS, BTR, BTC) を使って調査および修正できる。

## 【0117】

40

タスクをサスPENDするとき (プロセッサのマルチタスク機能を使って)、プロセッサは自動的に、EFLAGSレジスタ615の状態を、サスPENDされるタスクのためのタスク状態セグメント (TSS: task state segment) に保存する。プロセッサは、自らを新しいタスクにバインドするとき、EFLAGSレジスタ615に新しいタスクのTSSからデータをロードする。

## 【0118】

割り込みまたは例外ハンドラ・プロシージャへのコールが行われるとき、プロセッサは自動的に、EFLAGSレジスタ615の状態をプロシージャ・スタックに保存する。割り込みまたは例外がタスク切り替えを用いて扱われるときは、EFLAGSレジスタ615の状態はサスPENDされるタスクのためのTSSに保存される。

50

## 【0119】

シュレッド生成 / 破棄

シュレッドはforkshred命令を使って生成されうる。書式は次のとおり。

## 【0120】

forkshred imm16, 目標IP

forkshred r16, 目標IP

2つの形が与えられている。一方はシュレッド番号を即値オペランド(immediate operand)としてもち、第二のものはシュレッド番号をレジスタオペランド(register operand)としてもつ。いずれの形についても、目標IPは即値オペランドとして指定され、その値は現在のIPではなく、コードセグメントの先頭(名目上0)を基準とする。

## 【0121】

forkshred imm16, 目標IPというエンコードは、長距離ジャンプ(far jump)命令と同様で、シュレッド番号が16ビットのセレクタの代わりに、目標IPが16/32ビットオフセットの代わりになっている。

## 【0122】

forkshred命令は適切な実行ビットをSC0に設定し、指定されたアドレスで実行を開始する。ユニックスのfork()システムコールとは異なり、forkshred命令は親シュレッドの状態をコピーしない。新しいシュレッドの実行は、他のすべての専有レジスタの現在の値とともに更新されたEIPを用いて開始される。新しいシュレッドがそのスタックをESPをロードすることによって初期化し、はいってくるパラメータを共有レジスタまたはメモリから取得するべきことが期待されている。forkshred命令は自動的にパラメータを渡すことはしない。

## 【0123】

目標シュレッドがすでに走っている場合、forkshredは#SNA(シュレッド利用不能)例外を発生させる。これはのちに述べるようにユーザーレベルの例外である。ソフトウェアは、すでに走っているシュレッドを開始させようとしないことを保証するか、あるいは代替的に、既存のシュレッドを停止させる#SNAハンドラを提供して改めてforkshredの実行に戻る。シュレッド番号がハードウェアによってサポートされる最大シュレッド数より大きい場合には、#GP(0)例外が発生する。

## 【0124】

現在のシュレッドの実行を終了させるためには、haltshred命令が使われる。haltshredはSC0における現在のシュレッドの実行ビットをクリアし、現在のシュレッドの実行を終わらせる。シュレッドの専有状態は停止中でさえも保持される。あるシュレッドが別のシュレッドの専有状態にアクセスするいかなる機構も存在しないので、停止したシュレッドの専有状態は見ることができない。しかし、その状態は持続し、そのシュレッドがforkshredを通じて再び実行を開始したときに見えるようになる。

## 【0125】

別のシュレッドの実行を途中で打ち切るためには、killshred命令が導入される。書式は次のとおり。

## 【0126】

killshred imm16

killshred r16

## 【0127】

ある実施形態によれば、シュレッド番号は16ビットのレジスタまたは即値オペランドである。killshredはSC0における指定されたシュレッドの実行ビットをクリアして、そのシュレッドの実行を打ち切る。停止中、そのシュレッドの専有状態は保持される。

## 【0128】

目標シュレッドが走っていない場合には、killshredは黙って無視される。この振る舞いは、killshredと通常に終了するシュレッドとの間の競合を避けるために必要である。

10

20

30

40

50

killshredを実行したのち、ソフトウェアは、目標シュレッドがもはや走っていないことを保証される。シュレッドはhaltshredを実行する代わりに自らを打ち切る(kill)こともできる。シュレッド番号がハードウェアによってサポートされる最大シュレッド数より大きい場合には、#GP(0)例外が発生する。

## 【0129】

指定されたシュレッドが終了する(SC0ビットがクリアされることで示される)まで待つため、joinshred命令が導入される。書式は次の通り。

## 【0130】

```

joinshred imm16

joinshred r16

```

10

## 【0131】

目標シュレッドが走っていないければ、joinshredはすぐに戻る。この振る舞いが、joinshredと通常に終了するシュレッドとの間の競合を避ける。joinshredを実行したのち、ソフトウェアは、目標シュレッドがもはや走っていないことを保証される。シュレッドがjoinshredを自らに行うことも許される(役には立たないが)。シュレッド番号がハードウェアによってサポートされる最大シュレッド数より大きい場合には、#GP(0)例外が発生する。joinshred命令は自動的に戻り値を渡しはしない。

## 【0132】

シュレッドが自らのシュレッド番号を決定できるようにするため、getshred命令が導入される。書式は次のとおり。

20

## 【0133】

```

getshred r32

```

## 【0134】

getshredは現在のシュレッドの番号を返す。getshredは、シュレッド番号によって指定されるメモリ配列にアクセスするために使われる。getshred zeroは目的レジスタの全ビットに書き込むために16ビットシュレッド番号を拡張する。

30

## 【0135】

全シュレッド生成/破棄命令のためには、シュレッド番号はレジスタオペランドまたは即値オペランドのどちらで指定されてもよい。即値形の実行のほうがレジスタ形の実行よりも高速であることが期待される。シュレッド番号が実行時ではなくデコード時において得られるであろうからである。即値形では、コンパイラがシュレッド番号を割り当てる。レジスタ形ではランタイムの割り当てが使用される。

## 【0136】

次の表はシュレッドの生成/破棄命令のまとめを呈示している。

## 【0137】

表15

## 【0138】

## 【表15】

| 命令                    | 説明                     |

|-----------------------|------------------------|

| forkshred imm16, 目標IP | 指定されたアドレスでシュレッド実行を開始する |

| forkshred r16, 目標IP   |                        |

| haltshred             | 現在のシュレッドを終了させる         |

| killshred imm16       | 指定されたシュレッドを終了させる       |

| killshred r16         |                        |

| joinshred imm16       | 指定されたシュレッドが終了するまで待つ    |

| joinshred r16         |                        |

| getshred r32          | 現在のシュレッドの番号を返す         |

40

## 【0139】

50

forkshred、haltshred、killshred、joinshred、getshred命令はいかなる特権レベルで実行されてもよい。既存のIA-32のhlt命令が特権命令であるのに対して、haltshredは非特権命令である。

#### 【0140】

killshredまたはhaltshredの実行の結果走っているシュレッドが0個になる可能性がある。この状態(SC0に0)は既存のIA-32の停止状態とは異なる。SC0は認められている状態である。ただし、ユーザーレベルのタイマー割り込みが生成されるまで有用ではない。

#### 【0141】

##### 通信

10

シュレッドは互いとの通信を、既存の共有メモリを通じて、およびその目的のために特別に導入されたレジスタの組を通じて行う。共有レジスタSH0-SH7 655は同じスレッドに属するすべてのローカルシュレッドによってアクセス可能である。SH0-SH7レジスタ655は、はいってくるパラメータをシュレッドに渡し、シュレッドからの戻り値を通信し、セマフォ動作を実行するために使われる。各目的のために特定の共有レジスタ655はソフトウェアの慣例によって割り当てられる。

#### 【0142】

各共有レジスタ655は対応する空き/充满ビットをSC3に有している。共有レジスタ655に書き込みおよび読み出しをするためには、共有レジスタ655にMOV、および共有レジスタ655からMOVの命令が使われる。これらは次のようにまとめられる。

20

#### 【0143】

```

mov r32,sh0-sh7

mov sh0-sh7,r32

```

#### 【0144】

命令のエンコードは既存の制御レジスタ660への/からのMOV、およびデバッグ・レジスタへの/からのMOVの命令と同様である。共有レジスタへの/からのMOV命令はいかなる特権レベルで実行されてもよい。これらの命令は、ソフトウェアが追加的な命令を使って同期を明示的に実行することを想定している。共有レジスタへの/からのmovは、SC3の空き/充满ビットの状態を調べることも、修正することもしない。

30

#### 【0145】

共有レジスタ655へのMOV、および共有レジスタ655からのMOVの遅延は、共有メモリへのロードおよび保存の遅延より低いことが期待される。ハードウェア実装は、共有レジスタ655を見込みで読んで、他のシュレッド書き込みをせんさくすることがありそうである。ハードウェアは、共有レジスタ655に書き込むときには、強い順序付けの等価物を保証しなければならない。代替的な実施形態では、共有レジスタ655にアクセスするためにバリア命令が生成されることがある。

#### 【0146】

あるアーキテクチャ特徴により、共有レジスタの順序付けとメモリの順序付けは互いから別個のものに保たれる。よって、あるシュレッドが共有レジスタ655に書き込み、次いでメモリ120に書き込む場合、共有レジスタ655の内容が共有メモリ内容より先に見える保証はない。この定義の理由は、不必要的メモリバリアを創り出すことなく、共有レジスタ655におけるループカウンタの高速アクセス/更新を可能にすることである。ソフトウェアが共有レジスタ655とメモリの両方にバリアを要求する場合、ソフトウェアは共有レジスタ・セマフォをメモリ・セマフォとともに両方実行する。メモリ・セマフォはバリアとしてはたらくことのほかは冗長である。

40

#### 【0147】

同期のほかに迅速な通信を提供するため、共有レジスタへの/からの同期mov命令が使われる。これらの命令は次のようにまとめられる。

#### 【0148】

```

syncmov r32,sh0-sh7

```

50

syncmov sh0-sh7, r32

【0149】

命令エンコードは、既存の制御レジスタ660への／からのMOV、およびデバッグ・レジスタへの／からのMOVの命令とパラレルである。共有レジスタ655への同期movは、共有レジスタ655への書き込みの前に空き／充満ビットが空きを示すまで待つということのほかは、その非同期の対応物と同様である。共有レジスタ655への書き込み後、空き／充満ビットは充満に設定される。共有レジスタ655からの同期movは、共有レジスタ655から読む前に空き／充満ビットが充満を示すまで待つということのほかは、その非同期の対応物と同様である。共有レジスタ655から読んだのち、空き／充満ビットはクリアされて空きにされる。

10

【0150】

空き／充満ビットは、下記に述べるようにSC3への移動を用いて初期化されうる。共有レジスタへの／からの同期MOV命令はいかなる特権レベルで実行されてもよい。共有レジスタ通信命令は次のようにまとめられる。

【0151】

表16

【0152】

【表16】

| 命令                   | 説明            |

|----------------------|---------------|

| mov r32, sh0-sh7     | 共有レジスタからの移動   |

| mov sh0-sh7, r32     | 共有レジスタへの移動    |

| syncmov r32, sh0-sh7 | 共有レジスタからの同期移動 |

| syncmov sh0-sh7, r32 | 共有レジスタへの同期移動  |

20

【0153】

同期

一組の同期プリミティブが共有レジスタ655に作用する。同期プリミティブは、メモリでなく共有レジスタ655に作用するということのほかは、既存のセマフォ命令と同様である。命令は次の通り。

30

【0154】

表17

【0155】

【表17】

| 命令                     | 説明                                                                                       |

|------------------------|------------------------------------------------------------------------------------------|

| cmpxchgsh sh0-sh7, r32 | 共有レジスタを r32 と比較。等しければ ZF がセットされて r32 が共有レジスタにロードされる。等しくなければ ZF をクリアして共有レジスタを EAX にロードする。 |

| xaddsh sh0-sh7, r32    | 共有レジスタを r32 と交換。次いで r32 を共有レジスタに加える。この命令は、原子的な動作を可能にするために LOCK プレフィックスとともに使われうる。         |

| xchchgsh sh0-sh7, r32  | 共有レジスタを r32 と交換。この命令は常に原子的である。                                                           |

40

50

## 【0156】

同期プリミティブはいかなる特権レベルでも実行される。これらの命令は、SC3の空き / 充満ビットの状態を調べることも、修正することもしない。

## 【0157】

マルチシュレッドモードの開始 / 終了

MAXアーキテクチャはマルチシュレッドモードと単一シュレッドモードの間の切り換えをする機構を提供する。単一シュレッドモードは、プロセッサが、一つを除いたすべてのシュレッドの実行を停止することによって秩序だった仕方でコンテキスト切り換えを実行できるようにする。SC0は現在の動作モードを次のように示す：

10

- ・どのビット位置であれちょうど一つの1を含むSC0は単一シュレッドモードを含意する。

- ・どのビット位置であれ一つの1という以外のパターンを含むSC0はマルチシュレッドモードを表す。

## 【0158】

コンテキスト切り換えを実行するためには次のことが必要である：

1) 単一シュレッドモードに切り換えることによって一つを除いたすべてのシュレッドをサスPENDする。

2) シュレッド状態を保存する。

3) 新しいシュレッド状態をロードする。

4) マルチシュレッドモードに切り換えることによってすべてのシュレッドの実行を再開する。

20

## 【0159】

マルチシュレッドモード (multi-shredded mode) および単一シュレッドモードに切り換えるためには、それぞれentermsmおよびexitmsmが使われる。entermsmはマルチシュレッドモードにはいるために使われる。この命令の実行に先立って、全シュレッドの状態がロードされる必要がある。entermsmはSC1の新しいシュレッド実行ベクトルをSC0にコピーする。entermsmは次いで指定された諸シュレッドを開始させる。

## 【0160】

entermsmの実行後、SC1の内容が全く追加的なシュレッドの実行をもたらさないことも可能である。この場合、プロセッサは単一シュレッドモードに留まる。entermsmを実行した結果として、entermsmが実行されたシュレッドがもはや走っていなくなることも可能である。マルチシュレッドモードを終了するにはexitmsmが使われる。exitmsmはSC0の現在のシュレッド実行ベクトルをSC1にコピーする。exitmsmを実行するシュレッドに対応するもの以外のすべてのSC0実行ビットはクリアされる。exitmsmを実行するシュレッド以外のすべてのシュレッドは停止される。これらの動作は原子的なシーケンスで実行される。SC0状態は単一シュレッドモードを示す。entermsmおよびexitmsmはいかなる特権レベルで実行されてもよい。

30

## 【0161】

状態管理

命令 (shsaveおよびshrestore) は、集合的なシュレッド状態をそれぞれ保存および復元するため、すなわち全シュレッドの専有状態の内容をメモリに書き込むため、および全シュレッドの専有状態をメモリから読み出すために使われる。書式は次のとおり。

40

## 【0162】

shsave m16384

shrestore m16384

## 【0163】

メモリ保存領域のアドレスは、命令中の偏位によって指定される。アドレスは16バイトの境界に整列させられる。メモリ保存領域は将来の拡張を許容するため、16キロバイトである。メモリ保存領域は、既存のFXSAVE / FXRESTOR書式を整数レジスタを追加すること

50

によって拡張する。各シュレッドのためのメモリ保存領域は次のように定義される。

【0164】

表18

【0165】

【表18】

| オフセット   | レジスタ                                   |

|---------|----------------------------------------|

| 0-1     | FCW                                    |

| 2-3     | FSW                                    |

| 4-5     | FTW                                    |

| 6-7     | FOP                                    |

| 8-11    | FIP                                    |

| 12-13   | CS                                     |

| 14-15   | リザーブ                                   |

| 16-19   | FPU DP                                 |

| 20-21   | DS                                     |

| 22-23   | リザーブ                                   |

| 24-27   | MXCSR                                  |

| 28-31   | MXCSR MASK                             |

| 32-159  | ST0-ST7                                |

| 160-287 | XMM0-XMM7                              |

| 288-351 | EAX, EBX, ECX, EDX, ESI, EDI, EBP, ESP |

| 352-359 | ES, FS, GS, SS                         |

| 360-367 | EIP                                    |

| 368-371 | EFLAGS                                 |

10

20

【0166】

全シュレッドの内容は次式で与えられるアドレスに保存 / 復元される :

アドレス =  $512 \times (\text{シュレッド番号}) + (\text{ベースアドレス})$

メモリ保存領域は現在走っているシュレッドのEIPおよびESPを含む。shsaveは現在のEIPおよびESPをメモリに書き込む。分岐を避けるため、shrestore命令は現在のシュレッドのEIPやESPを上書きすることはしない。shrestore関数は、IRETの一部として実行されたとき、現在のシュレッドのEIPおよびESPを上書きする。

30

【0167】

shsaveおよびshrestoreはいかなる特権レベルで実行されてもよいが、单一シュレッドモードにあるときのみである。マルチシュレッドモードにあるときにshsaveまたはshrestoreが試みられると、#GP(0)例外が発生する。実装では、shsave / shrestoreの保存 / ロード動作を実行するために利用可能な全ハードウェアリソースを自由に使用できる。

【0168】

shrestoreは無条件に、全シュレッドの状態をメモリからロードする。この振る舞いは、シュレッドの専有状態が一つのタスクから次のタスクへ漏れないことを保証するために必要である。shsaveは、無条件にまたは条件付きで、全シュレッドの状態をメモリに保存する。ある実装では、専有状態が修正されなかった場合にshsaveの保存動作の一部または全部をスキップするよう非アーキテクチャ的可視のダーティー・ビット (dirty bits) を維持しうる。

40

【0169】

shsaveおよびshrestore命令はシュレッドの専有状態のみを保存および復元する。共有レジスタ655を保存および復元することはOSの責任である。

【0170】

シュレッド制御レジスタ660への / からの移動

50

シュレッド制御レジスタSC0-SC4 660に書き込み、そこから読み出すための命令が提供されている。それは次のようにまとめられる。

【0171】

```

mov r32,sc-sc4

mov sc0-sc4,r32

```

命令エンコードは既存の制御レジスタ660へのノからのMOV、およびデバッグ・レジスタへのノからのMOVの命令と同様である。シュレッド制御レジスタへのノからのMOV命令はいかなる特権レベルで実行されてもよい。悪意のあるアプリケーション・プログラムがシュレッド制御レジスタに書き込むことによって自分以外の何らかのプロセスに影響できないことを保証するための安全措置が設けられる。

10

【0172】

アプリケーション・プログラムは、SC0の内容を直接操作するのではなく、forkshredおよびjoinshredを使う。exitmsmはマルチシュレッドモードから単一シュレッドモードへの遷移を原子的な仕方で行う。現在のシュレッド実行状態を読むためにSC0からのmovを使い、次いでシュレッド実行状態を書き込むためにSC0へのmovを使うことのでは、シュレッド実行状態が読み出しと書き込みの間で変化しうるので、所望の結果が得られないである。

【0173】

OS例外

20

MAXは、IA-32例外機構のためにいくつかの関わりを有する。まず、ユーザーレベルの例外機構により、いくつかの型の例外がそれを発生させたシュレッドに直接報告されることが可能になる。この機構については後述する。

【0174】

次に、IA-32例外機構は、コンテキスト切り換えを必要とする例外が存在する場合に複数のシュレッドを適正に処理するよう修正される。従来のIA-32例外機構に関する一つの問題は、ちょうど一つの実行中スレッドのためにCS、EIP、SS、ESP、EFLAGSを自動的に保存および復元するよう定義されているということである。

【0175】

既存のIA-32例外機構は、entermsm、exitmsm、shsave、shrestore命令の機能性を含むよう拡張される。コンテキスト切り換えを必要とする割り込みまたは例外が発生させられると、例外機構は次のことをする：

30

1) exitmsmを実行することによりマルチシュレッドモードを終了する。exitmsmは、その割り込みまたは例外を引き起こしているもの以外のすべてのシュレッドを停止させる。OSはその割り込みまたは例外を引き起こしたシュレッドを使ってはいられる。

2) SC2によって与えられる開始アドレスでshsaveを実行することにより、全シュレッドの現在の状態をメモリに保存する。

3) 現在定義されているようなIA-32コンテキスト切り換えを実行する。

【0176】

マルチシュレッドプログラムに戻るために、修正されたIRET命令は次のことを実行する：

40

1) 現在定義されているようなIA-32コンテキスト切り換えを実行する。

2) SC2によって与えられる開始アドレスでshrestoreを実行することにより、全シュレッドの現在の状態をメモリから復元する。これはIA-32コンテキスト切り換えにおいて保存されたEIPおよびESPを上書きする。

3) entermsmを実行することによりマルチシュレッドモードにはいる。SC1の状態によつては、entermsmの実行は、プロセッサをして単一シュレッドモードに留まらせることもある。

【0177】

OSは、IRETを実行するのに先立って、メモリ中にシュレッド状態の保存／復元領域を設

50

定してそのアドレスをSC2にロードするよう要求される。OSはまた、SC1、SC3、SC4の状態を保存／復元することも要求される。

#### 【0178】

複数のシュレッドがOSのサービスを必要とする例外に同時に遭遇する可能性がある。MAXアーキテクチャは一時には一つのOS例外しか報告できないので、ハードウェアは複数のシュレッドにわたるOS例外を優先順位付けし、ちょうど一つを報告して、他のすべてのシュレッドの状態を例外を発生させた命令がまだ実行されていない時点に設定する必要がある。

#### 【0179】

##### ユーザーレベルの例外

MAXは、ある型の例外が完全にアプリケーション・プログラム内で処理されることを可能にする、ユーザーレベルの例外機構を導入する。いかなるOS関与、特権レベル遷移あるいはコンテキスト切り換えも必要でない。

#### 【0180】

ユーザーレベルの例外が生起すると、次の未実行命令のEIPがスタックにプッシュされ、プロセッサは指定されたハンドラに差し向けられる。ユーザーレベルの例外ハンドラはそのタスクを実行し、次いで既存のRET命令を介して戻る。ある実施形態によれば、ユーザーレベルの例外をマスクするためにいかなる機構も設けられない。アプリケーションがユーザーレベルの例外を発生させるのは、該アプリケーションがそれを手当てる用意があるときのみであると想定されるからである。

#### 【0181】

最初の二つのユーザーレベル例外を生成するために、2つの命令が提供される：signalshredおよびforkshredである。これらについて以下の節で述べる。

#### 【0182】

##### 信号伝送

signalshred命令は、指定されたシュレッドに信号を送るために使用される。書式は次のとおり。

#### 【0183】

signalshred imm16, 目標IP

signalshred r16, 目標IP

目標シュレッドはレジスタオペランドまたは即値オペランドとして指定されうる。signalshred imm16, 目標IPという命令のエンコードは、既存の長距離ジャンプ命令と同様で、シュレッド番号が16ビットのセレクタの代わりに、目標IPが16/32ビットオフセットの代わりになっている。長距離ジャンプの場合と同様、signalshredの目標IPは、現在のIPを基準にするのではなく、コードセグメントの先頭（名目上0）を基準として指定される。

#### 【0184】

signalshredに応答して、目標シュレッドは、次の未実行命令のEIPをスタックにプッシュし、指定されたアドレスに差し向けられる。シュレッドは自分に信号を送ってもよく、その場合、効果は近距離コール（near call）命令を実行するのと同じである。目標シュレッドが走っていない場合には、signalshredは黙って無視される。シュレッド番号がハードウェアによってサポートされる最大シュレッド数より大きい場合には、#GP(0)例外が発生する。

#### 【0185】

signalshred命令はいかなる特権レベルで実行されてもよい。signalshred命令は目標シュレッドにパラメータを自動的に渡すことはしない。signalshredをブロックするためのいかなる機構も設けられていない。よって、ソフトウェアは、signalshredを発する前にブロック機構を実装するか、あるいはネスト可能なsignalshredハンドラを設けるかする

10

20

30

40

50

必要がありうる。

### 【 0 1 8 6 】

シュレッド利用不能 ( SNA: Shred Not Available )

forkshredは、プログラムがすでに走っているシュレッドを開始させようとした場合には#SNA例外を発生させる。ソフトウェアの#SNAハンドラは既存のシュレッドに対してkill shredを実行して、forkshred命令に戻りうる。

### 【 0 1 8 7 】

#SNA例外は、forkshred命令のEIPをスタックにプッシュし、SC4+0によって与えられるアドレスに差し向けることによって処理される。SC4+0のところにあるコードは実際のハンドラに分岐すべきである。例外ベクトルはSC4+16、SC4+32などに置かれる。ソフトウェアは、256とおりの可能なユーザーレベル例外をカバーするためにSC4+4095までのメモリをリザーブしている。メモリ / SC4機構内の割り込み表は、のちの時刻においてよりクリーンな機構で置き換えられる。

10

### 【 0 1 8 8 】

サスPEND / 再開とシュレッド可視化

マルチスレッド・アーキテクチャ拡張は、ユーザーレベルのソフトウェアが以下のようない命令を使ってシュレッドをサスPENDまたは再開することを許容する。シュレッドをサスPENDするための命令：

20

- 1 ) メモリ中のシュレッド状態保存領域を初期化する。これは、サスPEND動作のためにアプリケーション・プログラムによって設定されたメモリ領域であって、SC2とポイントされるコンテキスト切り換えシュレッド状態領域とは異なる。

- 2 ) サスPEND・ハンドラをポイントするシュレッドに信号を送る。これはsignalshred 目標シュレッド、 サスPEND・ハンドラIP を通じて行われる。

- 3 ) サスPEND・ハンドラが既存のmov, pusha, fxsave命令を使ってそのシュレッドの専有状態をメモリに保存する。

- 4 ) サスPEND・ハンドラがhaltshredを実行する。

- 5 ) オリジナルコードがjoinshredを実行してシュレッドが停止するまで待つ。

### 【 0 1 8 9 】

30

サスPEND動作の時点ではシュレッドがすでに停止されているかもしれないことが可能である。この場合、signalshredは無視され、サスPEND・ハンドラは呼び出されることはなく、joinshredが待つこともない。メモリ中のシュレッド状態保存領域はその初期値を保持するが、該初期値はすぐにhaltshredを実行するダミーシュレッドをポイントする必要がある。シュレッドを再開するには、逆の動作が実行される。

- 1 ) 再開ハンドラをポイントするシュレッドをフォークする。これは、forkshred 目標シュレッド、 再開ハンドラIP を通じて行われる。

- 2 ) 再開ハンドラが既存のmov, popa, fxrestor命令を使ってシュレッドの専有状態をメモリから復元する。

- 3 ) 再開ハンドラが既存のRET命令を通じてシュレッドに復帰する。

40

### 【 0 1 9 0 】

再開先のスレッドがすでに停止されているときには、再開ハンドラは、すぐにhaltshredを実行するダミーシュレッドにRETする。サスPEND / 再開機能は、シュレッド可視化の可能性を開く。forkshredを実行する前に、ソフトウェアは同じシュレッド番号をもつ既存のシュレッドをサスPENDすることを選ぶことができる。joinshredを実行したのちに、ソフトウェアは同じシュレッド番号をもつ既存のシュレッドを再開することを選ぶことができる。サスPEND / 再開シーケンスは再入可能ではないので、いかなる所与の時刻にもいかなる所与のシュレッドについても実行されているサスPEND / 再開が一つだけであることを保証するための、ソフトウェアの決定的なセクションが必要である。これらの機構を使って、アプリケーション・プログラムが独自のプリエンプティブなシュレッド・ス

50

ケジューラを生成することが可能である。

【0191】

MAXの代替的な実施形態では、最初の利用可能なシュレッドを使ってフォークするための命令が存在する (allocforkshred r32)。ここでr32は割り当てられたシュレッド番号を用いて書かれる (forkshredではr32はフォークすべきシュレッド番号を指定する)。allocforkshredは、利用可能なハードウェア・シュレッドがあるかどうかを示すフラグをも返す。

【0192】

別の実施形態では、waitshred命令が、共有レジスタを使った待機同期を提供する (waitshred sh0-sh7, imm)。wait命令は待機機能を命令として提供する。この命令がなければ、次のようなループを使う必要がある。

【0193】

```

loop: mov eax, sh0

and eax, mask

jz loop

```

別の実施形態では、joinshredは、複数のシュレッド上で待機するためのビットマスクを与えられる。ビットマスクがなければ、joinshredは一つのシュレッドが終了するのを待ち、複数のシュレッド上で待機するためには複数のjoinshredが必要とされる。

【0194】

ある代替的な実施形態では、killshredは使用されない。signalshredとそれに続くjoinshredがkillshredの代わりに使用されうる。signalshredハンドラはhaltshred命令からなる。

【0195】

さらに別の実施形態では、forkshredとsignalshredを組み合わせることが可能である。forkshredとsignalshredは、シュレッドが現在走っているか停止しているかに関する振る舞いでしか違わない。signalshredが停止されているシュレッドを開始させることを許容されれば、signalshredは可能性としてはforkshredの代わりになることができる。

【0196】

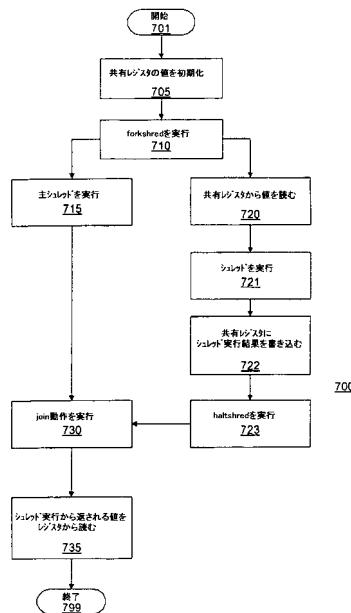

図7は、本発明のある実施形態に基づく、ユーザーレベルのマルチスレッドの例示的なプロセスの流れ図である。次に述べるプロセスはアプリケーションまたはソフトウェア・プログラムによって開始されたと想定されている。次に述べるプロセスはいかなる特定のプログラムとの関連でもなく、上記の命令およびアーキテクチャによって達成されるユーザーレベルのマルチスレッドの一つの実施形態として記述される。さらに、次に述べるプロセスは、16ビット、32ビット、64ビット、128ビットあるいはそれ以上のいずれのアーキテクチャであろうと、マルチプロセッサのようなマイクロプロセッサのISAとの関連で実行される。マルチプロセッサ(プロセッサ105のような)は、共有レジスタ、たとえば上掲の表3のレジスタの値を初期化する(処理ブロック705)。プロセッサ105はシュレッドを生成するforkshred命令を実行する(処理ブロック710)。複数の並行動作がプロセッサ105によって実行される。主(親)シュレッドがプロセッサ105によって実行される(処理ブロック715)。joinshred動作が実行されて、新しい目標シュレッドが実行を完了するのを待つ(処理ブロック730)。その間、新しい目標シュレッドはそのスタックを初期化し、はいってくるパラメータを共有レジスタおよび/またはメモリから取得し(処理ブロック720)、実行する(処理ブロック721)。現在の目標シュレッドの実行はhaltshred命令を使って終了される(処理ブロック723)。プロセッサ105は、実行結果を、シュレッドの実行結果が保存されているレジスタからプログラムまたはアプリケーションに返す(処理ブロック735)。ひとたびすべての実行されたデータが返されたら、プロセスは完了する(終了ブロック799)。

【0197】

ユーザーレベルのマルチスレッドを提供するための方法およびシステムが開示されている。本発明のここでの諸実施形態は、特定の例およびサブシステムに関連して述べられて

10

20

30

40

50

きたが、当業者には、本発明のここでの諸実施形態がそれらの特定の例またはサブシステムに限定されるものではなく、他の実施形態にも広がることは明らかであろう。本発明のここでの諸実施形態は、付属の請求項において規定される、これらの他の諸実施形態のすべてを含むものである。

【図面の簡単な説明】

【0198】

【図1】本発明のある実施形態に基づく、本方法および装置を利用する例示的なコンピュータシステムのブロック図である。

【図2】本発明のある実施形態に基づく、例示的なチップレベルのマイクロプロセッサを示す図である。 10

【図3】本発明のある実施形態に基づく、例示的な同時マルチスレッド・プロセッサを示す図である。

【図4】本発明のある実施形態に基づく、例示的な非対称マルチプロセッサを示す図である。

【図5】本発明のある実施形態に基づく、ユーザーレベルのマルチスレッド機能を提供するための例示的な実行環境を示す図である。

【図6】本発明のある実施形態に基づく、シュレッドと共有メモリ・スレッドとの間の例示的な関係を示す図である。

【図7】本発明のある実施形態に基づく、ユーザーレベルのマルチスレッド機能の例示的なプロセスの流れ図である。 20

【符号の説明】

【0199】

701 開始

705 共有レジスタの値を初期化

710 forkshredを実行

715 主シュレッドを実行

720 共有レジスタから値を読む

721 シュレッドを実行

722 共有レジスタにシュレッド実行結果を書き込む

30

723 haltshredを実行

730 join動作を実行

735 シュレッド実行から返される値をレジスタから読む

799 終了

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

## フロントページの続き

(72)発明者 ワン , ホン

アメリカ合衆国 94538 カリフォルニア州 フリモント サンデール ドライヴ 3987

7 105号

(72)発明者 シエン , ジョン , ピー

アメリカ合衆国 95121 カリフォルニア州 サンノゼ クウェイル ブラフ ブレイス 2

303

(72)発明者 ワン , ペリー , エイチ

アメリカ合衆国 95133 カリフォルニア州 サンノゼ キペラッシュ ドライヴ 2907

(72)発明者 コリンズ , ジャミソン , ディー

アメリカ合衆国 95032 カリフォルニア州 ロス ガトス オールド アドビー ウェイ

134

(72)発明者 ヘルド , ジェイムズ , ピー

アメリカ合衆国 97229 オレゴン州 ポートランド ノースウェスト 175ス ブレイス

3891

(72)発明者 クンドウ , パルサ

アメリカ合衆国 94303 カリフォルニア州 パロ アルト エッジウッド ドライヴ 19

06

(72)発明者 レヴィアザン , ラヤ

イスラエル国 56528 サヴィヨン マガル ストリート 10

(72)発明者 ガイ , テイン - フーク

アメリカ合衆国 95129 カリフォルニア州 サンノゼ オーク パーク アヴェニュー 5

544

審査官 漆原 孝治

(56)参考文献 特開2000-207233 (JP, A)

米国特許第05485626 (US, A)

笹田 耕一 , マルチスレッドアーキテクチャにおけるスレッドライブラリの実装と評価 , 先進的計算基盤システムシンポジウム SACSIS 2003 論文集 Symposium on Advanced Computing Systems and Infrastructures , 社団法人情報処理学会 , 2003年 5月28日 , 第2003巻 , 第9号 , p13-20

河原 章二 , Simultaneous Multithread (SMT)アーキテクチャの実現方式 , 情報処理学会論文誌 IPSJ Journal , 社団法人情報処理学会 , 2002年 4月15日 , 第43巻 , 第4号 , p829-843

REDSTONE, J., et al., Mini-threads: Increasing TLP on Small-Scale SMP Processors , High-Performance Computer Architecture, 2003. HPCA-9 2003. Proceedings. The Ninth International Symposium on , IEEE , 2003年 2月12日 , pp. 19 - 30

佐藤未来子、外6名 , マルチスレッドアーキテクチャ向けOS「Future」におけるプロセス管理 , コンピュータシステム・シンポジウム論文集 , 日本 , 社団法人情報処理学会 , 2003年12月11日 , Vol. 2001, No. 20 , pp. 61 - 70

HANKINS, R. A. et al. , Multiple Instruction Stream Processor , Proceedings of the 33rd annual international symposium on Computer Architecture , IEEE , 2006年 6月21日

(58)調査した分野(Int.Cl. , DB名)

G06F 9/46

G06F 9/38