(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5859444号

(P5859444)

(45) 発行日 平成28年2月10日(2016.2.10)

(24) 登録日 平成27年12月25日(2015.12.25)

|                      |            |

|----------------------|------------|

| (51) Int.Cl.         | F 1        |

| HO3F 3/24 (2006.01)  | HO3F 3/24  |

| HO3F 1/02 (2006.01)  | HO3F 1/02  |

| HO3F 3/68 (2006.01)  | HO3F 3/68  |

| HO4L 27/36 (2006.01) | HO4L 27/00 |

請求項の数 4 (全 34 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2012-535829 (P2012-535829)  |

| (86) (22) 出願日 | 平成22年10月28日 (2010.10.28)      |

| (65) 公表番号     | 特表2013-510454 (P2013-510454A) |

| (43) 公表日      | 平成25年3月21日 (2013.3.21)        |

| (86) 国際出願番号   | PCT/EP2010/066365             |

| (87) 国際公開番号   | W02011/054727                 |

| (87) 国際公開日    | 平成23年5月12日 (2011.5.12)        |

| 審査請求日         | 平成25年10月15日 (2013.10.15)      |

| (31) 優先権主張番号  | 12/611,677                    |

| (32) 優先日      | 平成21年11月3日 (2009.11.3)        |

| (33) 優先権主張国   | 米国(US)                        |

|           |                                                                                    |

|-----------|------------------------------------------------------------------------------------|

| (73) 特許権者 | 598036300<br>テレフォンアクチーボラゲット エル エ<br>ム エリクソン (パブル)<br>スウェーデン国 ストックホルム エスー<br>164 83 |

| (74) 代理人  | 100076428<br>弁理士 大塚 康徳                                                             |

| (74) 代理人  | 100112508<br>弁理士 高柳 司郎                                                             |

| (74) 代理人  | 100115071<br>弁理士 大塚 康弘                                                             |

| (74) 代理人  | 100116894<br>弁理士 木村 秀二                                                             |

| (74) 代理人  | 100130409<br>弁理士 下山 治                                                              |

最終頁に続く

(54) 【発明の名称】無線通信用デジタルアフィン変換変調電力増幅器

## (57) 【特許請求の範囲】

## 【請求項 1】

無線通信システムにおいて、デジタルアフィン変換変調電力増幅器により送信するため

に信号を変調する方法であって、

2つ以上の成分で送信される信号を提供する工程と、

前記信号の成分をm個の放射状のセクタを含むアフィンベクトル空間にマッピングする

工程であって、mは正の整数であり、前記セクタの境界が所定の境界角度に対応し、それ

により前記信号が前記所定の境界角度に沿って存在するベクトルの和として記述される

工程と、

複数の増幅器セル内において、各々が前記所定の境界角度のうちの1つに対応する位相

を有するクロック信号を増幅する、少なくとも2つの増幅器ユニットの出力を合計する工

程と、

対応する前記所定の境界角度を有するベクトルの大きさに基づいて各増幅器セル内の増

幅器ユニットを選択的にイネーブルする工程とを備えることを特徴とする方法。

## 【請求項 2】

送信される前記信号は、同相成分(I)と直交位相成分(Q)で提供されることを特徴

とする請求項1に記載の方法。

## 【請求項 3】

前記ベクトルの大きさに基づいて各増幅器セル内の増幅器ユニットを選択的にイネーブ

ルする工程は、

10

20

各大きさを符号に変換する工程と、

前記符号化された大きさの値の対応するビットの値に基づいて各増幅器セルの1つの増幅器ユニットをイネーブルする工程とを含むことを特徴とする請求項1に記載の方法。

【請求項4】

セクタ内の信号の動きを追跡する工程と、

2つの隣接セクタのうち前記信号の移動先であるセクタを予測する工程と、

現在のセクタと共有されない前記予測されたセクタの境界角度に対応する位相を有するクロック信号を前記複数の増幅器セル内のディスエーブルされた増幅器ユニットに供給する工程と、

前記信号が前記予測されたセクタに入った時には、

10

前記増幅器ユニットを選択的にイネーブルする工程と、

前記予測されたセクタと共有されない前記境界角度と関連付けられた位相を有するクロック信号によりクロック制御される増幅器ユニットを無効にする工程とを更に備えることを特徴とする請求項1に記載の方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、一般に、無線通信に関し、特に、送信機用デジタルアフィン変換変調電力増幅器に関する。

【背景技術】

20

【0002】

移動通信システムは、今日の生活では必要不可欠なものである。サイズの縮小と機能及び能力の増大とが移動通信デバイス（例えば、無線電話）の現在の傾向である。双方の傾向は、縮小するサイズと、電子機器、特にデジタル電子機器の高集積化により進んでいる。CMOS技術がより小さい機能サイズ及び高集積化に移行するにつれて、CMOS電子機器は、特に利用面積の増加、省電力化、高速化及び低価格化の恩恵を受けるようになっている。

【0003】

一方、多くがアナログのままである無線周波数（RF）回路は、そのような劇的な改善がされていない。デジタル回路の小型化が続く一方、アナログ回路が使用する移動通信デバイスの回路面積及び電力の割合はこれまでにもなく増加し続けている。

30

【0004】

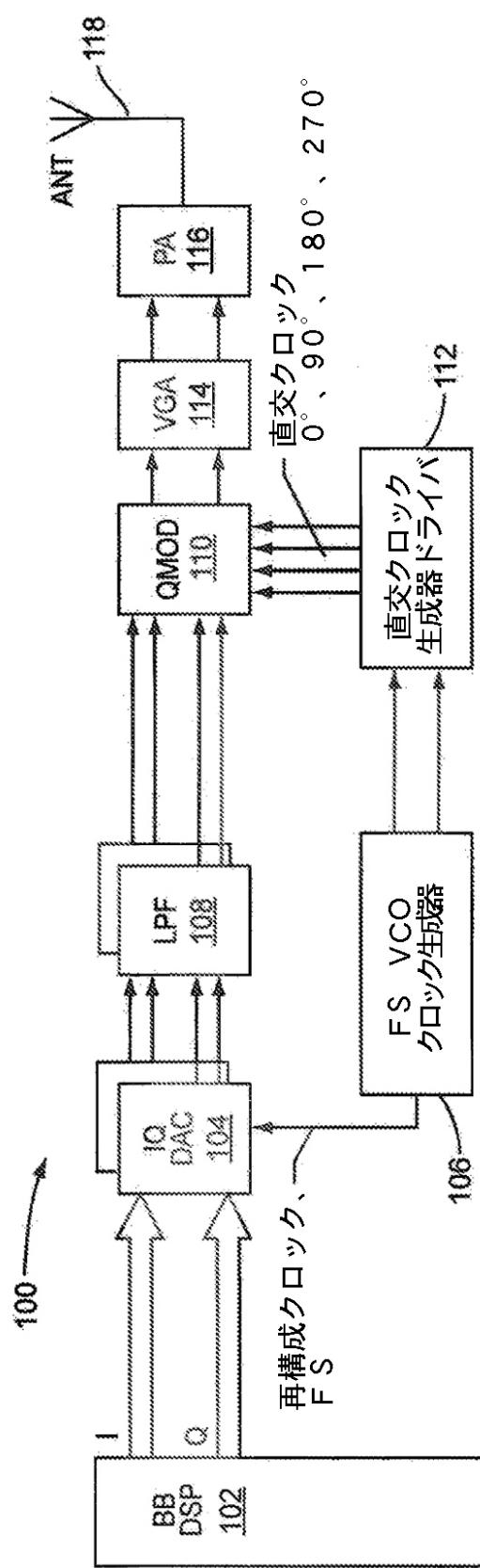

RF送信機の設計に関しては、図20に示す従来の直交送信機アーキテクチャが有力なデザインのままである。送信機100は、送信される信号の同相成分（I）及び直交成分（Q）を生成する信号プロセッサ102を含む。デジタル-アナログ変換器104は、クロック生成器回路106により提供される再構成クロック $f_r$ を使用してデジタル信号をアナログ信号に変換する。ローパスフィルタ108は、再構成フィルタのような役割を果たし、アナログ信号帯域幅を限定する。信号は、クロックドライバ回路112により提供される搬送周波数 $f_{tx}$ の直交クロックを使用して直交変調器110により変調される。可変利得増幅器114は変調信号を増幅し、電力増幅器116は、アンテナ118に接続された送信機の出力において十分な電力レベルまで信号レベルを高める。

40

【0005】

送信機100のチェーンに沿う構成要素の非線形性により、近接する受信機又は自身の受信機にさえスプリアス放射及び干渉を招く望ましくない周波数成分である高調波歪み及び相互変調積が発生する可能性がある。これを回避するために、LPF108、直交変調器110及びVGA114に要求される線形性は非常に高いため、これら構成要素の設計はより困難になり、コストも増加する。一方、これらアナログ構成要素は一般にA級動作しているため、高い線形性は一般に高い消費電力を意味する。

【0006】

従来の直交変調送信機100は、いくつかの点において欠陥がある。フリッカ雑音を最

50

小限にするフィルタコンデンサ及び大きなトランジスタ等の能動構成要素及び受動構成要素は、大きなシリコン面積を占め、その面積はC M O S技術の移行により劇的には縮小しない。更にアナログ設計は、処理の変更や温度及び供給電圧の変更等の影響を受けやすいため、環境の影響をより受けやすく、例えば、種々の要のプロセスに対処する際に設計するのがより困難になる。また、デバイスの整合性は、ミクロンサイズよりはるかに小さいサイズのC M O Sにとって問題である。最後に、より適切な線形性及びより低い雑音が要求されるため、消費電力はより高くなり、高電力になる。

#### 【 0 0 0 7 】

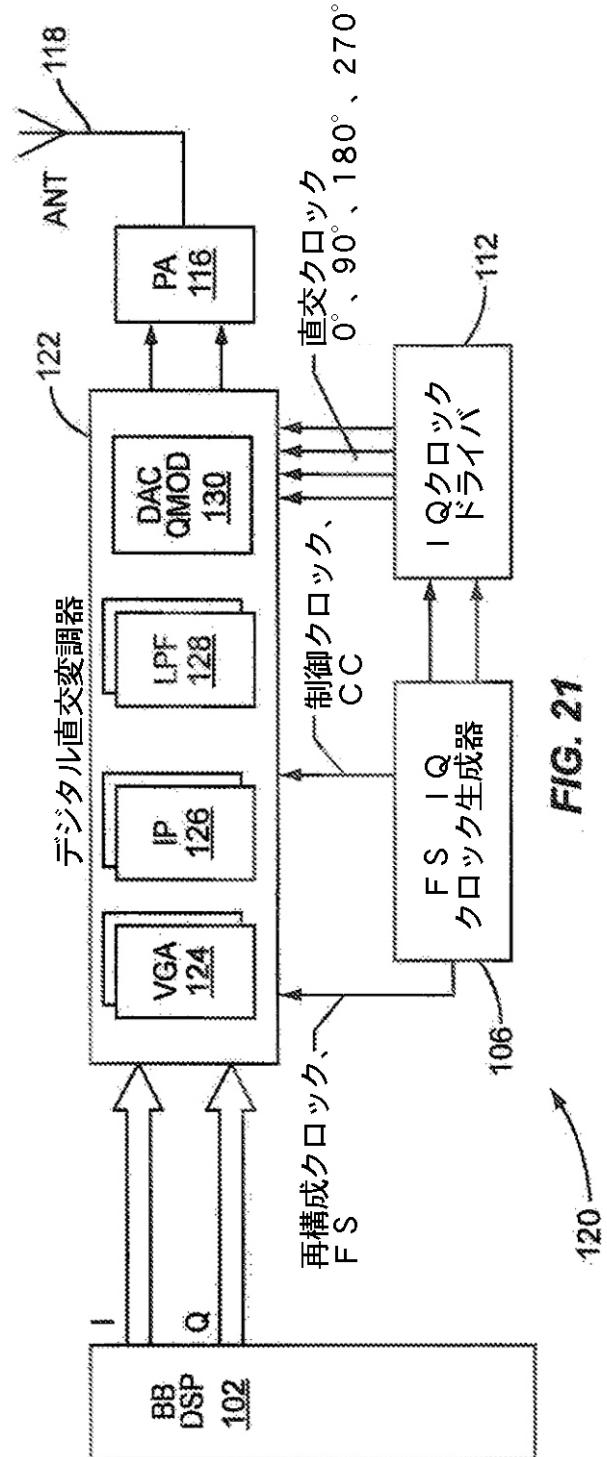

設計労力を緩和し且つ使用面積及び消費電力を減少するために、図21に示す統合デジタル直交変調送信機120が非特許文献1において、ヘ(He)により提案されている。

送信機120は、多くの構成要素を単一のデジタルブロックに結合するデジタル直交変調器122を特徴とする。VGA124は、変調動作により送信機チェーン利得をデジタル的に設定する。ベースバンド信号の元のサンプル比はデジタル-RF変換段DAC/QM0D、すなわち搬送波クロック周波数前後で変調スプリアススペクトルを生成する直交変調器130にとって十分ではない可能性があるため、直交変調器122は信号をオーバサンプリングし、内挿補間回路126を使用して必要な帯域幅を達成する。ローパスフィルタ128は高周波数高調波を除去し、組み合わせDAC/直交変調器130はRF直交変調信号を生成する。クロック生成器106及びクロックドライバ112は搬送波クロック信号を提供し、それら信号は、デジタルベースバンド信号により変調され、変調RF信号に変換される。デジタルベースバンド信号はそれらに相当するアナログ信号より小さい歪みを有するため、線形性は向上する。更に、大きなコンデンサを除去したために、使用面積はアナログ構成要素より小さい。

#### 【 0 0 0 8 】

図20の従来の設計100のいくつかの欠点に対処する一方で、図21の集積デジタル直交変調送信機120はいくつかの欠点がある。面積の効率は送信機100より良いが、電力増幅器116は独立した回路として残る。パッド及び相互接続を含む独立した変調器122及び電力増幅器116の必要性は、重複する領域を意味する。更に、変調器122の出力において通常50のインピーダンスを駆動する必要があるため、消費電力はその出力においてより高い。変調器122及び電力増幅器116は、消費電力が一定であるA級で通常動作しているため、変調器122及び電力増幅器116における電力効率はより低い。従って、設計120は低出力電力レベルにおいて非常に低い電力効率を有する。更に電力増幅器116における非線形歪みは補償するのが困難であり、他の無線周波数で干渉を発生する。最後にシステムインテグレーションは最適化されないため、送信機のコストは増加する。

#### 【 0 0 0 9 】

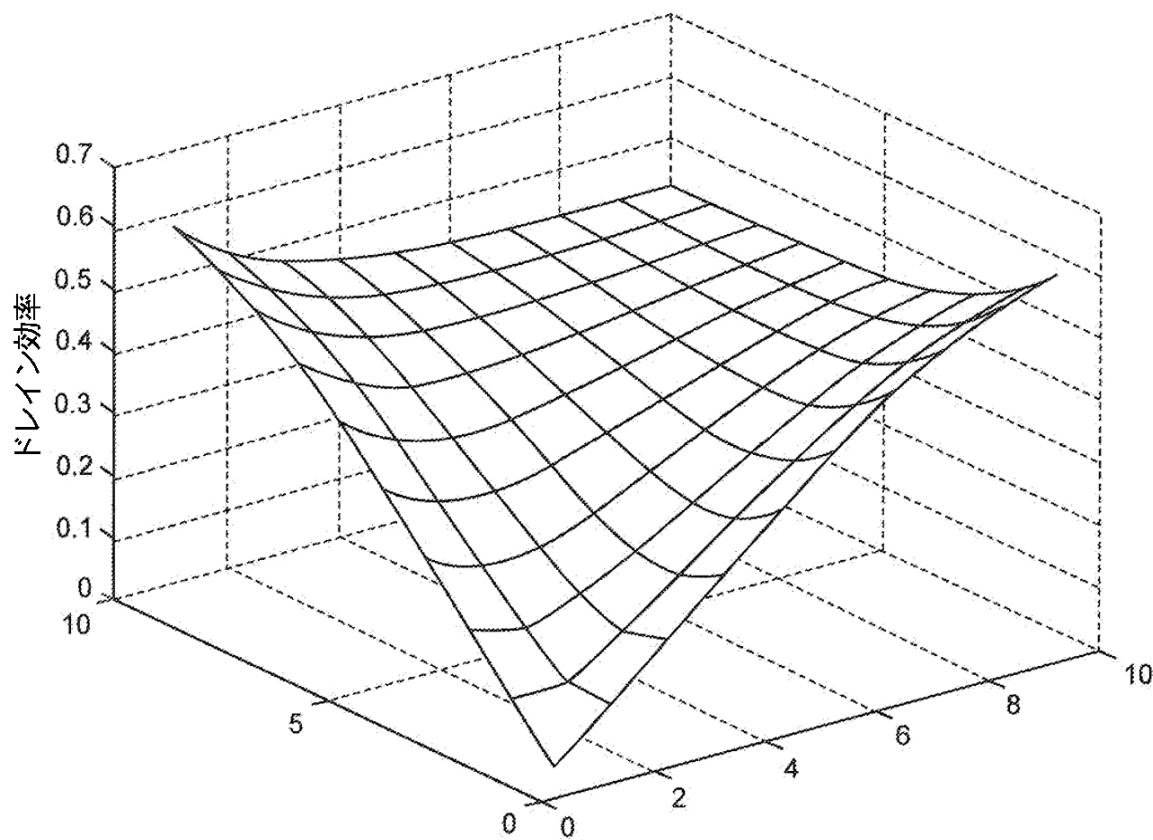

送信機100、120の構成要素の集積化のレベル又は構成に関わらず、直交変調はいくつかの基本的な欠陥がある。直交変調において、ベースバンドプロセッサが通常I信号及びQ信号を生成するため、直交信号成分I及びQは非常に単純で簡単な変調において使用される。更に、Iチャネル及びQチャネルは、受信機の帯域における干渉及び妨害を低減するようにバランスがとられる。しかし、電力増幅器116における残る課題は、Iチャネル出力及びQチャネル出力が組み合わされる時の効率の低下である。ウィルキンソン電力結合器を使用すると、効率は3dB低下し、誘導負荷電力結合器を使用すると、I及びQの双方が導通する時にドレイン効率は低下する。図22は、Iの振幅がQの振幅と等しい場合に効率が最も低下すること、すなわちIチャネル及びQチャネルが互いに最も負荷をかける場合に45°の方向に効率が低下することを示すシミュレーション結果を示す。

#### 【 0 0 1 0 】

直交変調に対する既知の代替の変調は極性変調である。極性変調において、振幅信号mは次の通りである。即ち、

$$m = (I^2 + Q^2)$$

10

20

30

40

50

である。ここで、 $m = 0$  である。位相又は角度信号は次の通りである。即ち、

$$\phi = \arctan(Q / I)$$

である。ここで、 $0 \leq \phi \leq \pi/2$  である。角度  $\phi$  における正弦関数は次の通りである。即ち

$$\sin(\phi) = Q / m, \cos(\phi) = I / m$$

である。

**【先行技術文献】**

**【非特許文献】**

**【0011】**

**【非特許文献1】** 直接直交電圧変調を用いた45ナノメータ低電力SAWレスWCDMA 10 送信変調器 (45 nm Low-power SAW-less WCDMA transmit Modulator Using Direct Quadrature Voltage Modulation)、ISSCC、サンフランシスコ、USA, 2009年2月

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0012】**

極性変調では、振幅及び位相変調パスが異なり、互いに負荷をかけないため、約45°の同様の効率の低下は起きない。しかし、2つのパスの差分により、それらを整合するのが困難となり、異なる群遅延を招く。これは、例えば信号振幅に対する歪みの比であるエラーベクトル振幅 (EVM) により測定されるような歪みを発生する。更にデカルト座標 (I, Q) から極座標 (振幅, 位相) への変換において大きな帯域幅の拡張 (例えば、約5倍～9倍) がある。変換は非線形であり、信号が歪みを低減するのに大きな帯域幅を必要とするゼロの振幅に近くなると鋭角になる。このため、極性変調はWCDMA等の広帯域の応用例に適さない。

**【0013】**

極性変調の効率が一定である状態で直交変調の一定の群遅延及び低帯域幅を示し、更には全てのデジタル実施形がCMOS技術の進化である速度及び電力の利点を利用できるようになる変調技術は、通信信号送信の最新技術における大きな進歩を表す。

**【課題を解決するための手段】**

**【0014】**

ここで開示され且つ特許が請求される1つ以上の実施例によると、アフィン変換はI成分及びQ成分で表される送信される通信信号に適用される。アフィン変換は、I, Qデカルト座標空間を所定の境界角度で規定される複数のm個の放射状のセクタに分割する。あるセクタ内に入る信号は、各々がセクタの境界角度に沿って存在する2つの放射状ベクトルのベクトル和として表される。

**【0015】**

デジタルアフィン変換変調器及び電力増幅器は、アナログ増幅器なしで送信する信号をデジタル方式で準備する。変調器は、信号に対してアフィン変換を実行する。電力増幅器は、各々が少なくとも2つの増幅器ユニットを含む複数の増幅器セルを含む。所定の信号に対して、各増幅器ユニットは信号のアフィン変換済みセクタの1つの境界角度に対応する位相を有するクロック信号を選択的に増幅する。位相クロック信号を受信する複数の増幅器セルの部分集合は、アフィン変換空間における信号を記述する関連するベクトルの大きさに基づいてインエーブルされる。一実施例において、大きさは2進数から1進数符号 (サーモメータコード) に変換され、各1進数符号化 (サーモメータコード化) ビットは、各増幅器セルの関連する増幅器ユニットを選択的にインエーブルする。増幅器セルの出力は、デジタル電力増幅器出力を形成するために結合される。一実施例において、増幅器セルは、出力インピーダンスの変動を防止するインピーダンス整合回路とディスエーブルされた増幅器ユニットとの内の少なくとも1つにおけるRF漏洩を防止する遮断回路を含む。増幅器ユニットは、トランジスタのシングルエンド又は差動構成として構築される。

**【0016】**

一実施例において、信号がアフィン変換セクタ境界を越えた時に迅速なスイッチングを

10

20

30

40

50

可能にするために、信号の動きが予測される。増幅器セル毎のディスエーブルされた第3の増幅器ユニットは、現在のセクタにより共有されない予測されたセクタの境界角度に対応する位相を有するクロック信号を受信する。信号が予測されたアフィン変換セクタに入ると、第3の増幅器ユニットは、アフィン変換空間の関連するベクトルの大きさに基づいて選択的にイネーブルされる。この時、新しい（予測された）セクタにより共有されない前のセクタの境界角度と関連付けられた増幅器ユニットはディスエーブルされる。これにより、信号がアフィン変換セクタ間を迅速に移動する時のスイッチング速度及び帯域幅が向上する。

【図面の簡単な説明】

【0017】

10

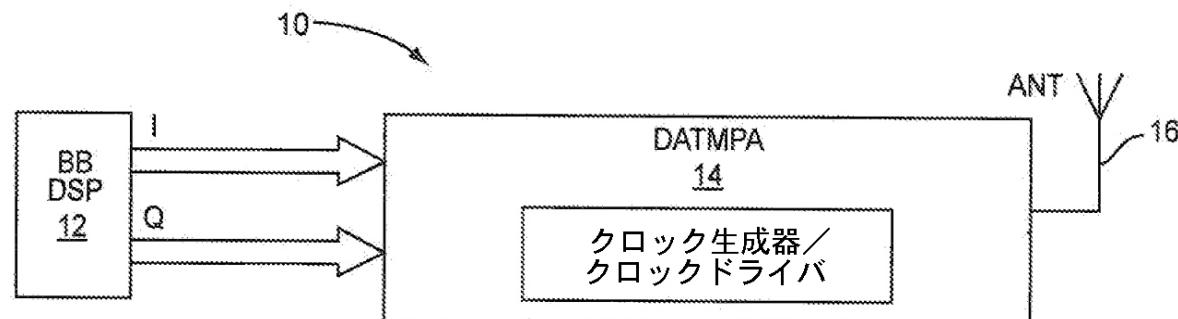

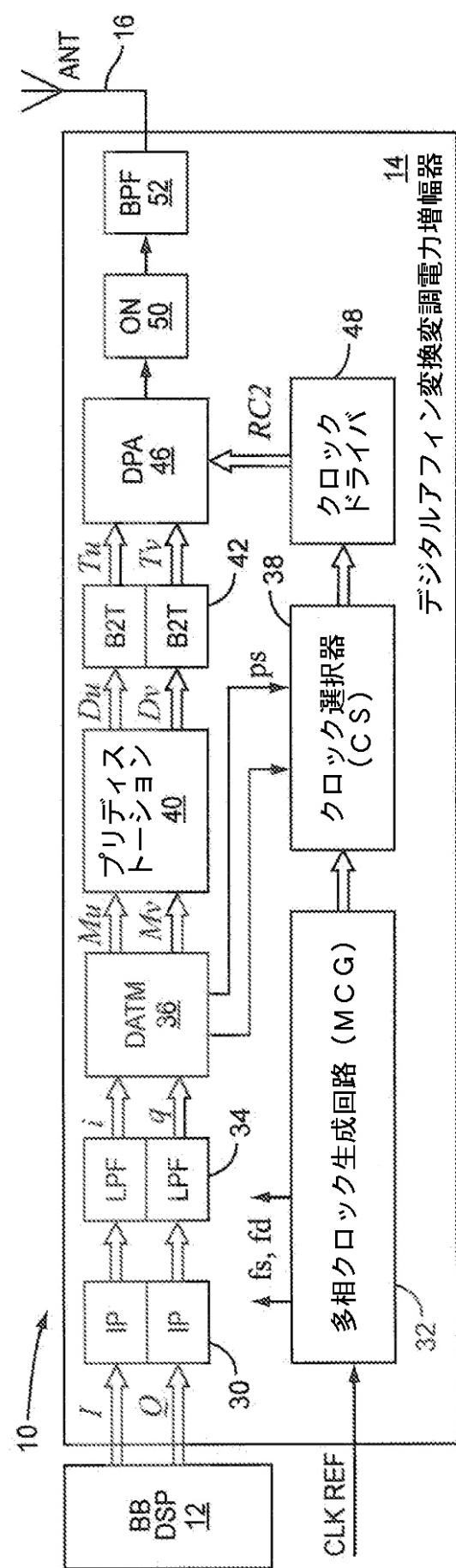

【図1】デジタルアフィン変換変調送信機（DATAM）を示す機能ブロック図である。

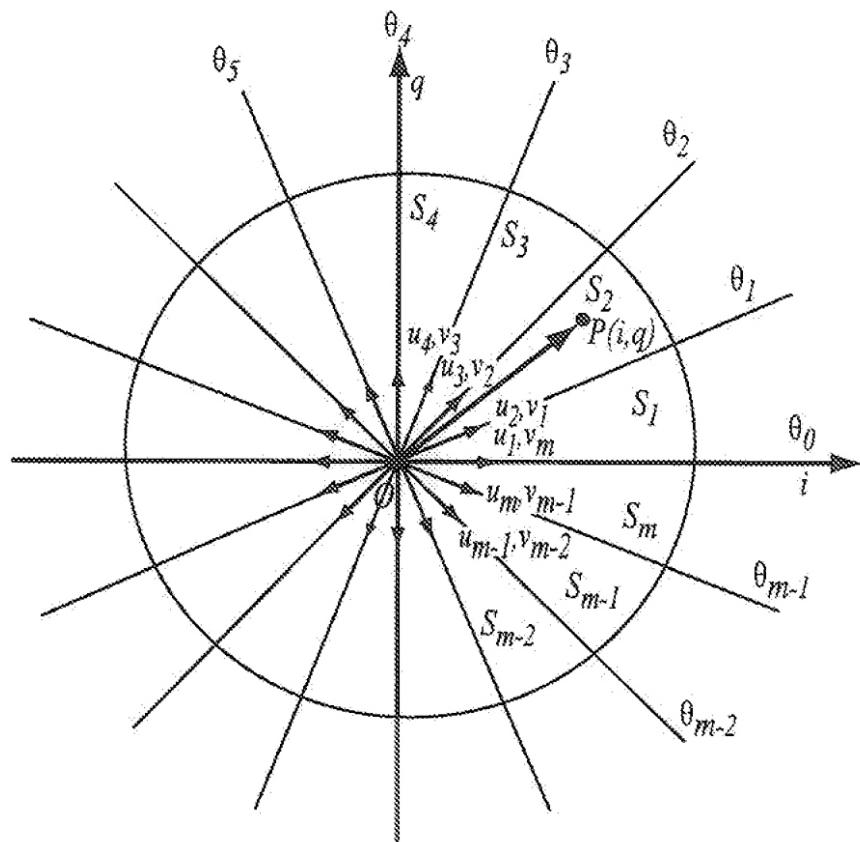

【図2】アフィン変換セクタを示す極座標グラフである。

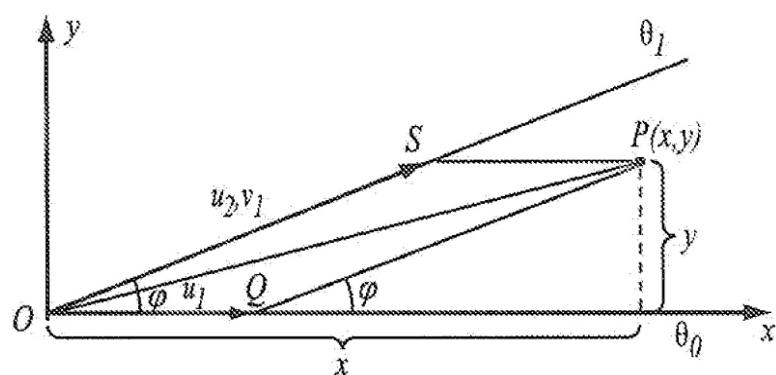

【図3】ベクトルの加算を示す図である。

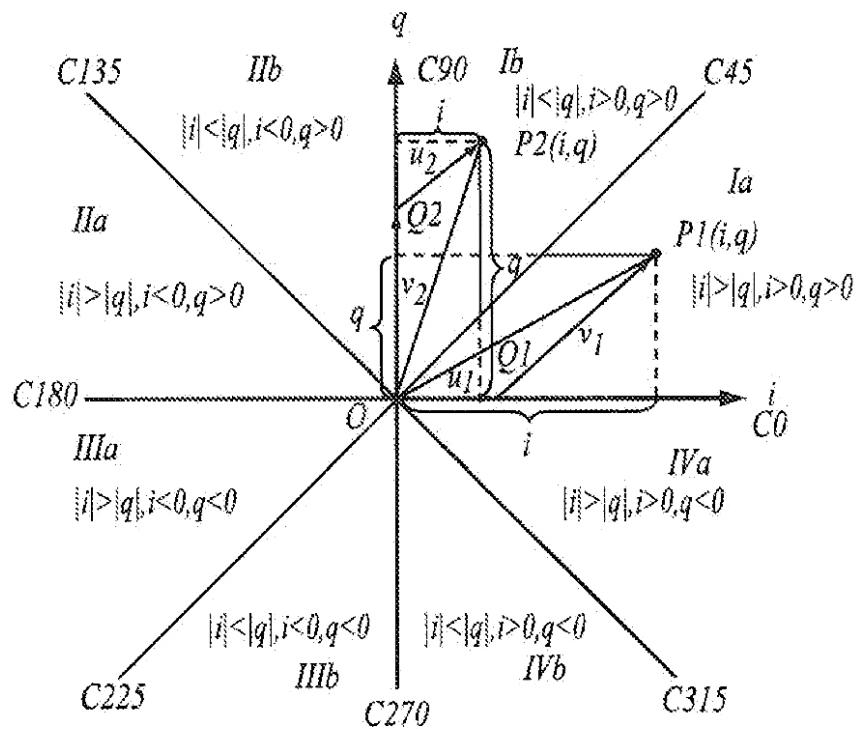

【図4】第1象限における2つの信号のベクトル和を示す極座標グラフである。

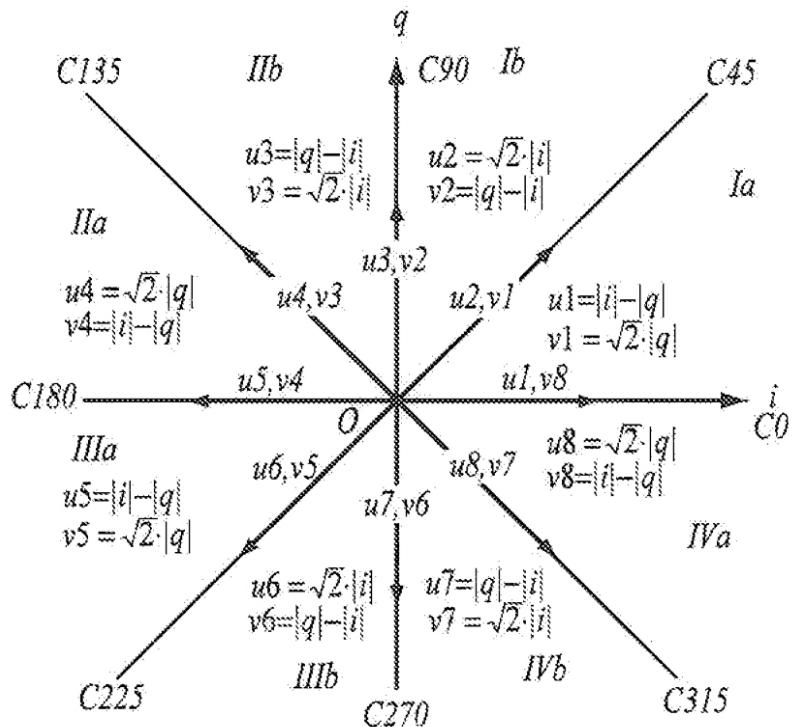

【図5】8セクタアフィン変換系に対するセクタ境界及び式を示す極座標グラフである。

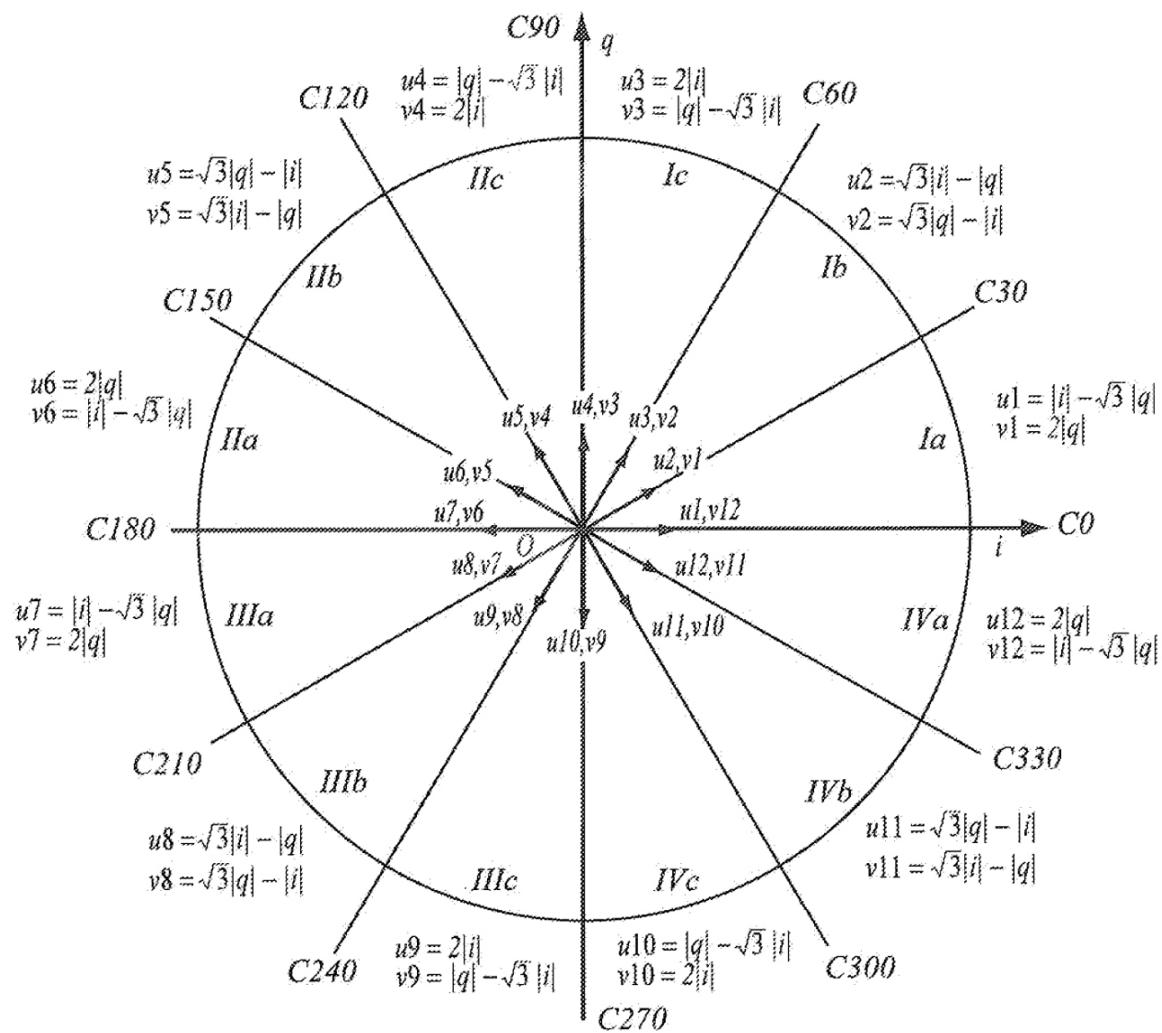

【図6】12セクタアフィン変換系に対するセクタ境界及び式を示す極座標グラフである。

【図7】コールドスイッチDATAMを示す機能ブロック図である。

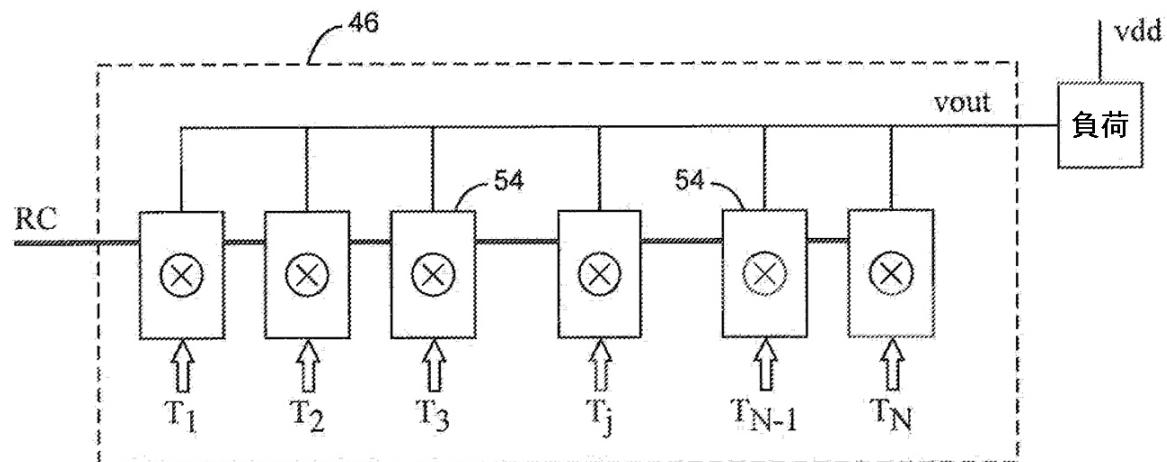

【図8】DATAMに対するシングルエンドデジタル電力増幅器を示す機能ブロック図である。

20

【図9】DATAMに対する差動デジタル電力増幅器を示す機能ブロック図である。

【図10】DATAMに対するコールドスイッチ差動デジタル電力増幅器の増幅器ユニットを示す機能回路図である。

【図11】セクタ境界及びセクタ間の信号の動きを示す極座標グラフである。

【図12】ホットスイッチDATAMを示す機能ブロック図である。

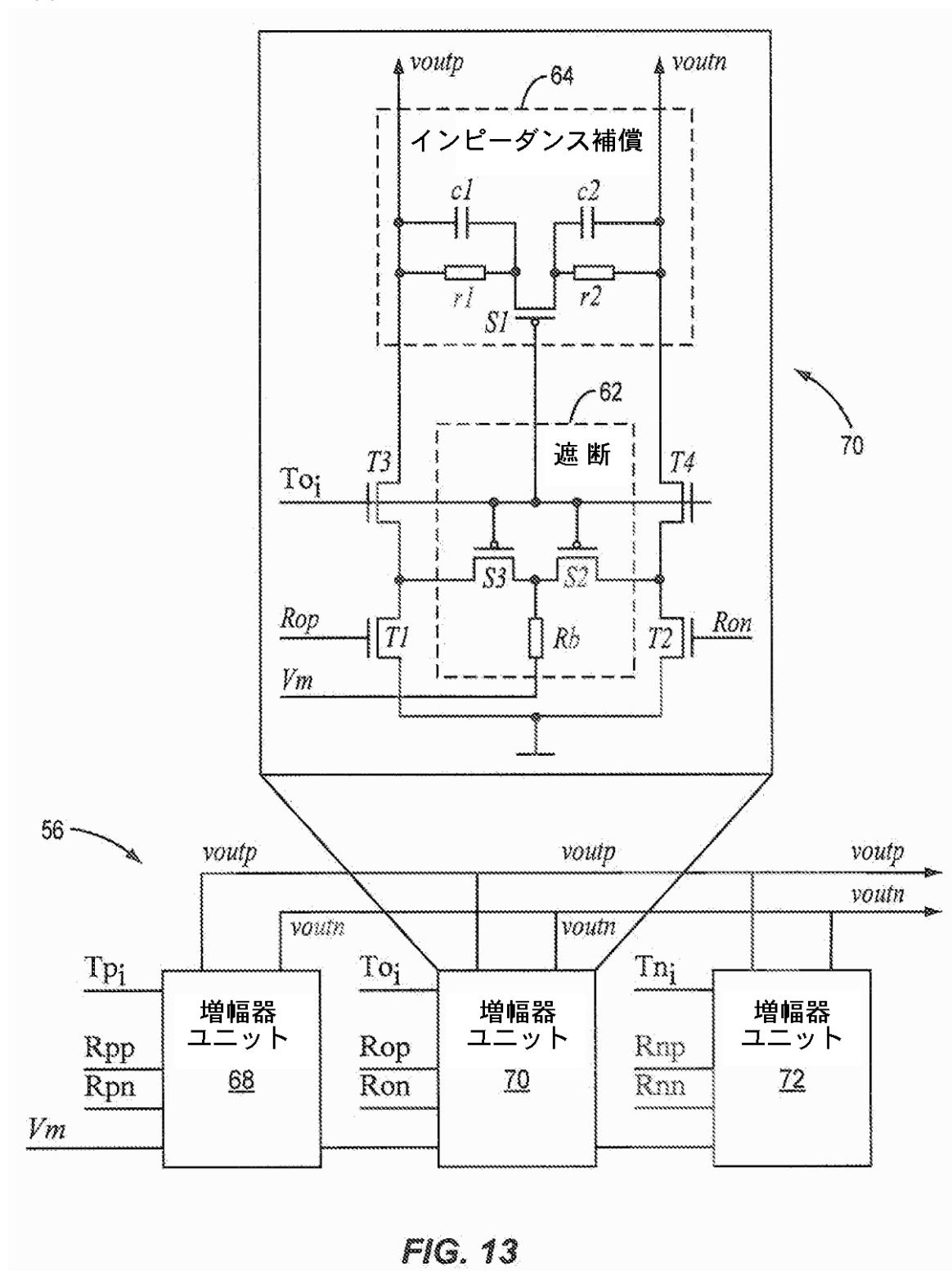

【図13】DATAMに対するホットスイッチ差動デジタル電力増幅器の増幅器ユニットを示す機能回路図である。

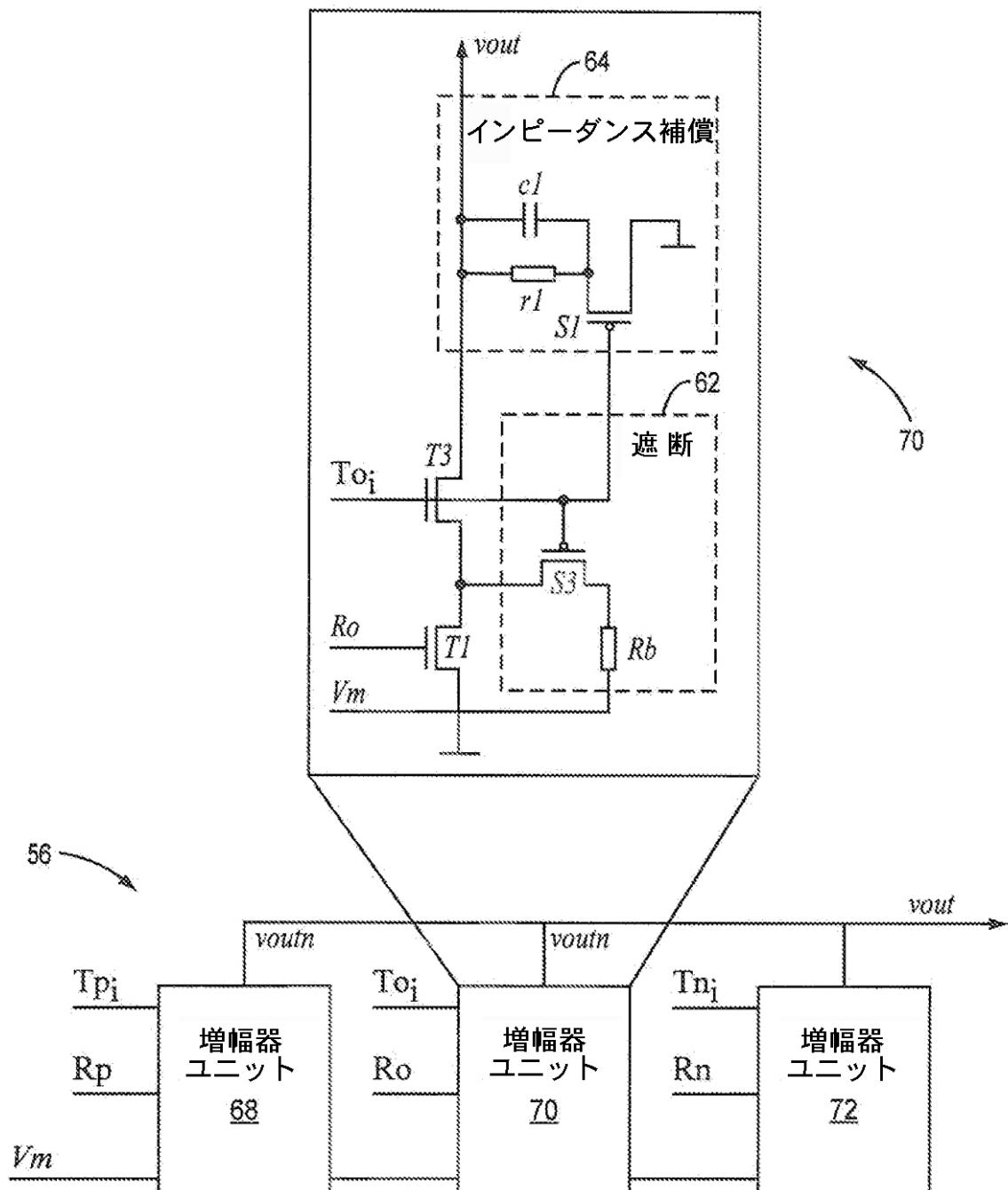

【図14】DATAMに対するホットスイッチシングルエンドデジタル電力増幅器の増幅器ユニットを示す機能回路図である。

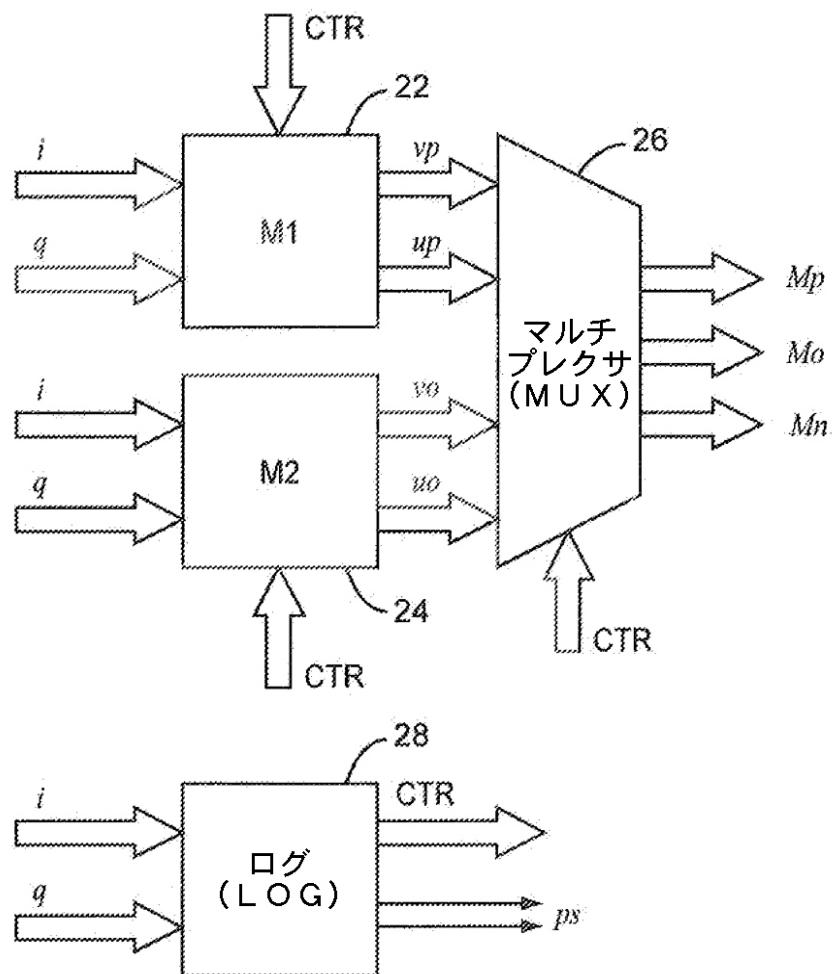

【図15】アフィン変換変調を実現する回路を示す機能ブロック図である。

30

【図16】セクタをまたがる信号の動きを示すグラフである。

【図17】信号がセクタを移動する時の信号の追跡及びベクトルの加算を示す図である。

【図18】角度だけ離間した一定の大きさの2つのベクトルを示すグラフである。

【図19】DATAMの電力効率及び電流を示すグラフである。

【図20】従来の直交変調送信機を示す機能ブロック図である。

【図21】統合デジタル直交変調器を特徴とする従来の直交変調送信機を示す機能ブロック図である。

【図22】I記号成分及びQ記号成分が等しくなるにつれて図20又は図21の送信機の効率が低下することを示すグラフである。

【発明を実施するための形態】

【0018】

40

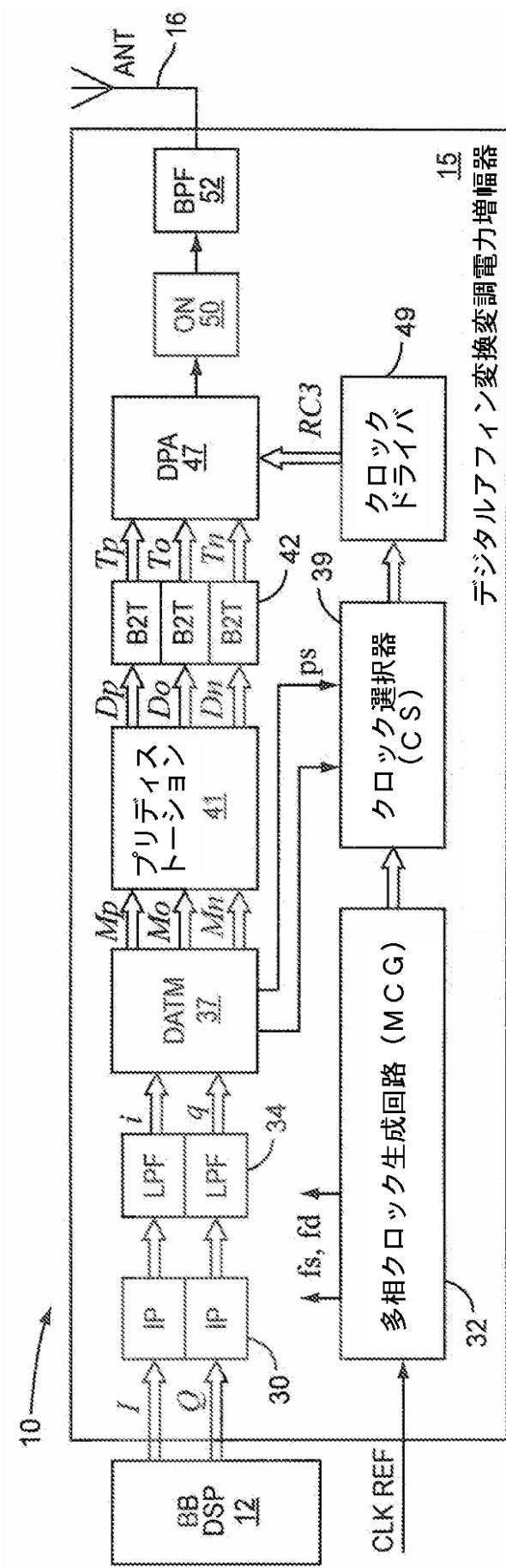

図1は、デジタルアフィン変換変調（DATAM）送信機10を示す。DATAM送信機10は、送信される信号の同相成分（I）及び直交成分（Q）を生成するベースバンドデジタル信号プロセッサ（BBDSP）12を含む。これらのデジタル2進値は、デジタル-アナログ変換器、ローパスフィルタ、可変利得増幅器、変調器及び電力増幅器の機能を1つのデジタルブロックに結合する統合デジタルアフィン変換変調電力増幅器（DATMPA）14により受信される。更に、DATMPA14は、クロック生成器及びクロックドライバ回路を含む。DATMPA14は、デジタル領域においてアフィン変換変調方式を使用してBBDSP12からのデジタル信号を変調し、デジタル電力増幅器において変調した信号を増幅する。DATMPA14は、送信するために増幅した信号をアンテナ16

50

に提供する。

【0019】

DATMは、変調器においてよく整合されたパスをイネーブルし、一定の群遅延を可能にする。それらパスは、雑音及び干渉を低減するための差動回路による実現に非常に適している。変調パスは、振幅及び位相に関連するため、I成分及びQ成分が45°に近づく時に低効率にならない。しかし、極座標へのI/Q変換に必要な非常に広い帯域幅は回避される。デジタル領域において変調及び電力増幅の双方を実現することにより、システムは、CMOS技術の進歩を利用してシリコン面積及び消費電力を低減し、高速化し、且つ非常に高い集積度を実現する。

【0020】

10

アフィン変換について最初に説明し、その後、DATM送信機10のいくつかの実施例を開示する。信号が移動する時のスイッチング速度が考慮され、迅速なスイッチングのために最適化されたDATM送信機10の実施例を開示する。シミュレーション結果は、アフィン変換パラメータの関数としてDATMPAの効率を示す。

【0021】

2つのベクトル空間の間のアフィン変換は、以下の式を使用してデカルト座標*i*, *q*を, vのアフィンベクトル空間にマッピングする行列Aにより与えられる非退化(full rank)線形変換として規定される。

【0022】

20

$$\begin{bmatrix} u \\ v \end{bmatrix} = \begin{bmatrix} a_{11}, a_{12} \\ a_{21}, a_{22} \end{bmatrix} \begin{bmatrix} i \\ q \end{bmatrix} + \begin{bmatrix} c_1 \\ c_2 \end{bmatrix}$$

(1)

【0023】

所望のアフィン変換は、*i*及び*q*空間の原点をアフィン空間の原点にマッピングすべきである。従って、平行移動係数*c*<sub>1</sub>及び*c*<sub>2</sub>はゼロに設定される。マッピング後、行列Aが直交行列でない限り、直交性は失われる。DATMにおいて、通常、非直交基底が使用される。*c*<sub>1</sub>及び*c*<sub>2</sub>の双方がゼロであるため、変換は実際には線形変換であり、アフィン変換の部分集合である。線形増幅又は線形変調と非線形増幅又は非線形変調とを混同しないようにするために、ここではアフィン変換という用語を用いる。

30

【0024】

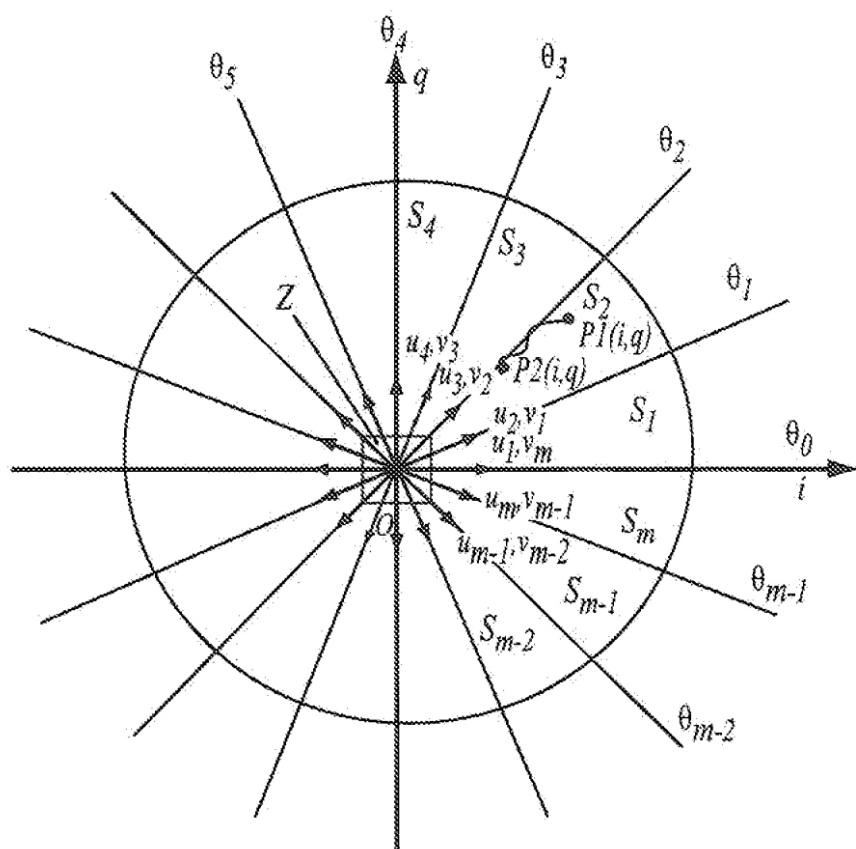

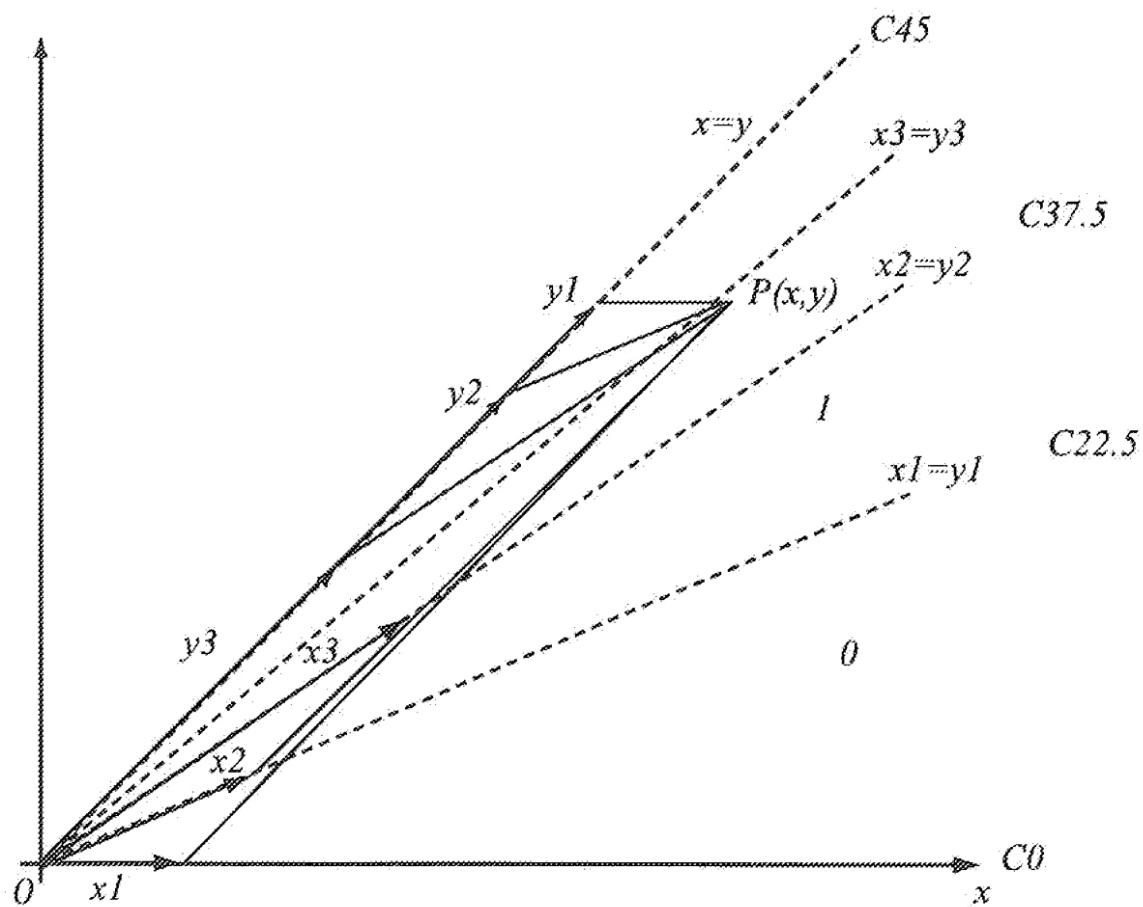

アフィン変換において、*i*及び*q*平面のサイクル領域は、図2に示すように複数の所定の境界角度 = { $\alpha_0, \alpha_1, \alpha_2, \dots, \alpha_{m-2}, \alpha_{m-1}$ }によりm個の同等なセクタS<sub>1</sub>、S<sub>2</sub>、…、S<sub>m-1</sub>、S<sub>m</sub>に分割される。ここで、mは整数であり、角度 $\alpha$ はデジタルクロック信号の位相を変動させることにより容易に実現されるように選択される。

30

【0025】

原点から、例えば、図2においてS<sub>2</sub>であるセクタに配置された点P(*i*, *q*)へのベクトルOPにより表されるI成分及びQ成分で出力される信号は、ベクトル基底であるセクタの2つの境界角度、例えば、図2の $\alpha_1$ ,  $\alpha_2$ を使用して線形行列により部分空間にマッピングされる。これらの境界角度は連続したクロック位相に対応する。ベクトルOPは、部分空間S<sub>2</sub>において以下のベクトル和により表される。即ち、

40

$$\begin{aligned} U(\alpha_1, \alpha_2) &= S_2 \\ S(u_2, v_2) &= A_2(p(i, q)) \\ &= b_1 C_1 + b_2 C_2 \quad (2) \end{aligned}$$

である。ここで、*b*<sub>1</sub>と*b*<sub>2</sub>はゼロ以上の大きさであり、*C*<sub>1</sub>及び*C*<sub>2</sub>はそれぞれ、 $\alpha_1$ 、 $\alpha_2$ の位相/角度を有するベクトルである。

【0026】

一般に、原点からセクタjに配置された点P(*i*, *q*)へのベクトルOPにより表され

50

る I 成分及び Q 成分で出力される信号に対して、部分空間  $S_j$  におけるアフィン変換は次の通りである。即ち、

$$\begin{aligned} U(j-1, j) &= S_j \\ S(u_j, v_j) &= A_j(p(i, q)) \\ &= b_{j-1}C_{j-1} + b_jC_j \quad (3) \end{aligned}$$

である。ここで、 $b_j$  はゼロ以上の大きさであり、 $C_j$  は  $j$  の位相 / 角度を有するベクトルであり、 $j = 0, 1, 2, \dots, m-1$  である。

#### 【0027】

$m$  個の異なるセクタに対して、I / Q 空間の信号の軌道に従って I / Q 信号出力（すなわち、I 及び Q 座標で表される連続した信号）を  $m$  個のアフィン線形空間に変換する  $m$  個の異なる線形マッピング  $A = \{A_1, A_2, \dots, A_{m-2}, A_{m-1}, A_m\}$  が存在する。アフィン線形空間  $S_j$  は、境界角度  $\theta_j$  に対応する 2 つのベクトル基底  $u_j$  及び  $v_j$  を有するアフィン変換  $A_j$  により作成される。境界角度  $\theta_j$  は、回路の実現を容易にするために正のみであると仮定される。当然、負のベース / 境界角度も可能である。

#### 【0028】

アフィン変換  $A_j$  は、2 つのベクトル成分が組み合わされた時にアフィン変換がセクタの全ての境界において元の I / Q 信号と同一の軌道を維持し且つマッピングされた信号の連続性を保証するように最適に選択されるべきである。これらの条件が満たされた場合、マッピングはいかなる歪みも発生させない。

#### 【0029】

図 3 は、第 1 のセクタに対するアフィン変換を示す。ベクトル  $OP$  は、2 つのベクトル  $OS$  及び  $OQ$  の和で置換される。2 つのベクトルの各々は、境界角度  $\theta_0$  及び  $\theta_1$  と同一方向を有する。アフィン変換は、以下のように表される。即ち、

$$\begin{aligned} u_1 &= SP = OQ = x - \{y / \tan(\theta)\} \\ v_1 &= OS = QP = y / \sin(\theta) \quad (4) \end{aligned}$$

である。

#### 【0030】

あるいは、式 (4) は以下のように行列形式で表されてもよい。

#### 【0031】

$$\begin{bmatrix} u_1 \\ v_1 \end{bmatrix} = \begin{bmatrix} 1, & \frac{-1}{\tan(\theta)} \\ 0, & \frac{1}{\sin(\theta)} \end{bmatrix} \begin{bmatrix} x \\ y \end{bmatrix} = A_1 \begin{bmatrix} x \\ y \end{bmatrix} \quad (5)$$

#### 【0032】

他のセクタ、例えばセクタ  $k$ 、 $k = 1, \dots, m-1, m$  に対して、以下の回転演算子  $R_k$  が使用される。

#### 【0033】

$$R_k = \begin{bmatrix} \cos(k-1)\phi, & \sin(k-1)\phi \\ -\sin(k-1)\phi, & \cos(k-1)\phi \end{bmatrix} \quad (6)$$

#### 【0034】

これを使用して  $i$  及び  $q$  を第 1 の  $x$  及び  $y$  空間にマッピングし、その後、アフィン変換が行われ、 $x$  及び  $y$  空間をアフィン空間にマッピングする。それ故に、その変換は  $A_1$  と

10

20

30

40

50

回転行列  $R_k$  との積として次のように書ける。

【0035】

$$\begin{bmatrix} u_k \\ v_k \end{bmatrix} = A_1 \begin{bmatrix} x \\ y \end{bmatrix} = A_1 R_k \begin{bmatrix} i \\ q \end{bmatrix} = A_k \begin{bmatrix} i \\ q \end{bmatrix} = \begin{bmatrix} 1, & \frac{-1}{\tan(\phi)} \\ 0, & \frac{1}{\sin(\phi)} \end{bmatrix} \begin{bmatrix} \cos((k-1)\varphi), & \sin((k-1)\varphi) \\ -\sin((k-1)\varphi), & \cos((k-1)\varphi) \end{bmatrix} \begin{bmatrix} i \\ q \end{bmatrix} \quad (7)$$

【0036】

ここで、 $A_k$  は、セクタ  $k$  を  $s_k$  及び  $s_{k+1}$  の境界角度を有するアフィン空間にマッピングする変換である。

【0037】

当然、 $i$  成分及び  $q$  成分は、符号部分と値部分とに分離され、信号は第1象限へと回転される。アフィン変換は、第1象限において実行され、適切な境界角度が判定される。このように、信号  $u_k$  及び  $v_k$  は正となる。

【0038】

2つの連続したセクタ  $s_k$  及び  $s_{k+1}$  に対して、 $v_k = u_{k+1}$  であることが図2又は式(5)から分かり、これはマッピングされた部分空間における信号表現の連続性を維持するのに必要である。換言すると、2つの連続したセクタは異なるアフィン変換を使用するが、境界において2つの変換は連続的に結び付けられる。

【0039】

セクタ数及び従って境界角度(又はクロック位相)の数である整数パラメータ  $m$  は、電力効率に影響を及ぼす。極性変調方法の限界まで、 $m$  が無限大に近づくにつれて、 $m$  が大きい程、電力効率は高くなる。直交変調は、 $m = 4$  の場合に特殊な例と考えられ、境界角度は I、Q 軸である。実際には、 $m$  の値は 6、8、12、16、24、32 等として選択される。以下に説明するように、 $m$  の値が大きい程、電力増幅器の非線形性を解除するのに採用されるプリディストーションルックアップテーブルのサイズは縮小される。 $u$  及び  $v$  は、図3に示す  $u_1$  及び  $v_1$  のように間の角度が  $\frac{2\pi}{m}$  である2つのベクトルであると仮定する。OPの振幅、すなわちベクトル  $u$  及び  $v$  の和は以下の通りである。

【0040】

$$|OP| = \sqrt{|u|^2 + |v|^2 + 2|u||v|\cos(\varphi)} = \sqrt{|u|^2 + |v|^2 + 2|u||v|\cos\left(\frac{2\pi}{m}\right)} \quad (8)$$

【0041】

$m$  が増加すると、 $|OP|$  は減少する。 $|OP|$  が非常に小さい場合、電力増幅器の非線形性を解除するために1Dプリディストーションテーブルを使用できる。

【0042】

本発明の好適な一実施例において、 $m = 4 * I$  である。 $I$  は正の整数である。 $m = 4 * I$  である場合、第1象限におけるアフィン変換行列の成分は他の象限に現れ、これにより、デジタル変調器がアフィン変換された信号を実現する時のハードウェアの複雑さを低減する。

【0043】

図4に示す一実施例において、 $m = 8$  であり、セクタ(及びデジタル実施形に対する8位相クロック)を規定するための8つの境界角度に対応する。セクタの境界位相は、C0、C45、C90、C135、C180、C225、C270 及び C315 である。これらの位相角は、 $i$  及び  $q$  平面を8つのセクタ Ia、Ib、IIa、IIb、IIIa、IIIb、IVa 及び IVb に分割する。これらは、 $i$  及び  $q$  信号の符号及び絶対値の比較から容易に取得される。

10

20

30

40

50

## 【0044】

セクタ I a の点  $P_1 (i, q)$  に対して、アフィン変換は、 $0^\circ$  及び  $45^\circ$  のクロック位相に対応する 2 つの境界角度  $C_0$  及び  $C_{45}$  に基づいてその点をアフィン空間  $U_1$  にマッピングする。ベクトル  $OP_1$  は 2 つのベクトル  $OQ_1$  及び  $Q_1P_1$  の和として表される。 $OQ_1$  は  $i$  軸と同一方向を有し、 $Q_1P_1$  は時計方向に  $45^\circ$  回転された  $q$  軸である。以下のことが図 4 から容易に分かる。即ち、

$$OQ_1 = u_1 = i - q$$

$$Q_1P_1 = v_1 = 2q$$

である。ここで、 $u_1$  及び  $v_1$  は、セクタを規定する境界角度に沿って存在する第 1 のアフィンセクタにおけるベクトルである。

10

## 【0045】

同様に、セクタ I b に存在する点  $P_2 (i, q)$  に対して、アフィン変換は、 $45^\circ$  及び  $90^\circ$  のクロック位相に対応する 2 つの境界角度  $C_{45}$  及び  $C_{90}$  に基づいてその点をアフィン空間  $U_2$  にマッピングする。ベクトル  $OP_2$  は、2 つのベクトル  $OQ_2$  及び  $Q_2P_2$  の和として表される。 $OQ_2$  は  $q$  軸と同一方向を有し、 $Q_2P_2$  は反時計方向に  $45^\circ$  回転された  $i$  軸である。以下のことが図 4 から容易に分かる。即ち、

$$Q_2P_2 = u_2 = 2i$$

$$OQ_2 = v_2 = q - i$$

である。

20

## 【0046】

残りのマッピングは同様に判定される。図 5 のグラフは、全てのマッピングを示し、8 つのセクタのアフィン変換を表す。6 桁で表されるアフィン変換行列の成分は、変数  $i$  及び  $q$  に対する絶対値を使用して表 1 に一覧表示される。

## 【0047】

表 1 :  $m = 8$  の場合のアフィン変換行列の成分

| 8 セクタの行列 $A_k$ |          |          |          |          |

|----------------|----------|----------|----------|----------|

|                | $a_{11}$ | $a_{12}$ | $a_{21}$ | $a_{22}$ |

| $k = 1$        | 1.00000  | -1.00000 | 0.00000  | 1.41421  |

| $k = 2$        | 1.41421  | 0.00000  | -1.00000 | 1.00000  |

| $k = 3$        | -1.00000 | 1.00000  | 1.41421  | 0.00000  |

| $k = 4$        | 0.00000  | 1.41421  | 1.00000  | -1.00000 |

| $k = 5$        | 1.00000  | -1.00000 | 0.00000  | 1.41421  |

| $k = 6$        | 1.41421  | 0.00000  | -1.00000 | 1.00000  |

| $k = 7$        | -1.00000 | 1.00000  | 1.41421  | 0.00000  |

| $k = 8$        | 0.00000  | 1.41421  | 1.00000  | -1.00000 |

30

## 【0048】

図 6 は、同様に判定される  $m = 12$  の場合のアフィン変換のマッピングを示す。変数  $i$  及び  $q$  に対する絶対値を使用するアフィン変換行列の成分は表 2 に一覧表示される。

40

## 【0049】

表 2 :  $m = 1, 2$  の場合のアフィン変換行列の成分

| 1 2 セクタの行列 $A_k$ |          |          |          |          |

|------------------|----------|----------|----------|----------|

|                  | $a_{11}$ | $a_{12}$ | $a_{21}$ | $a_{22}$ |

| $k = 1$          | 1.00000  | -1.73205 | 0.00000  | 2.00000  |

| $k = 2$          | 1.73205  | -1.00000 | -1.00000 | 1.73205  |

| $k = 3$          | 2.00000  | 0.00000  | -1.73205 | 1.00000  |

| $k = 4$          | -1.73205 | 1.00000  | 2.00000  | 0.00000  |

| $k = 5$          | -1.00000 | 1.73205  | 1.73205  | -1.00000 |

| $k = 6$          | 0.00000  | 2.00000  | 1.00000  | -1.73205 |

| $k = 7$          | 1.00000  | -1.73205 | 0.00000  | 2.00000  |

| $k = 8$          | 1.73205  | -1.00000 | -1.00000 | 1.73205  |

| $k = 9$          | 2.00000  | 0.00000  | -1.73205 | 1.00000  |

| $k = 10$         | -1.73205 | 1.00000  | 2.00000  | 0.00000  |

| $k = 11$         | -1.00000 | 1.73205  | 1.73205  | -1.00000 |

| $k = 12$         | 0.00000  | 2.00000  | 1.00000  | -1.73205 |

## 【 0 0 5 0 】

アフィン変換式の展開及びアフィン変換行列の成分は、より大きい値  $m$  に対しても同様に導出される。

## 【 0 0 5 1 】

一般に各々がアフィン変換セクタを規定する境界角度の 1 つの角度と異なる大きさとを有する 2 つのベクトルの和としてアフィン変換された信号を表すことにより、アナログ増幅器なしで送信アンテナに R F 信号を直接提供できるようにデジタルアフィン変換変調器及び / 又はデジタル電力増幅器を実現することが可能になる。

## 【 0 0 5 2 】

図 7 は、送信機 10 の一実施例を示す。送信機は、ベースバンドデジタル信号プロセッサ 12 と、デジタルアフィン変換変調電力増幅器 ( D A T M P A ) 14 と、アンテナ 16 とを含む。B B D S P 12 は、I 成分及び Q 成分として表されるデジタル変調信号 ( デジタルベースバンド信号 ) を生成する。I 信号成分及び Q 信号成分は、D A T M P A 14 の並列チェーンにおいて受信され且つ処理される。以下に説明する理由のために、D A T M P A 14 のこの実施例は、「コールドスイッチ」設計と呼ばれる。信号処理チェーンは、チャネル毎に補間器 30 及びローパスフィルタ 34 と、デジタルアフィン変換変調器 ( D A T M ) 36 と、プリディストーションモジュール 40 と、2 進数 - 1 進数符号化 ( binary to thermometer coding ) 変換モジュール 42 と、デジタル電力増幅器 46 と、出力ネットワーク 50 と、バンドパスフィルタ 52 を含む。

## 【 0 0 5 3 】

内挿補間器 30 は、ベースバンドデジタル信号をオーバサンプリングし、デジタルローパスフィルタ 34 は、サンプリングが原因となるバンド外のスプリアス成分を除去する。I P 30 及び L P F 34 は、多相クロック生成回路 32 から適切なクロック信号を受信する。

## 【 0 0 5 4 】

サンプリング及びフィルタリングされた  $i$  及び  $q$  信号は、デジタルアフィン変換変調器 ( D A T M ) 36 に渡され、D A T M 36 は、上述したように信号をアフィン変換空間に変換する。アフィン変換空間は、各々がアフィン変換セクタの境界角度に対応する方向及び大きさを有する 2 つのベクトルを含む。D A T M 36 は、それら 2 つのベクトルの大きさをデジタル値  $M_u$  及び  $M_v$  として出力する。D A T M 36 は、対応するベクトル方向情報 ( 位相制御信号  $p, s$  ) をクロック選択器回路 38 に更に出力する。

## 【 0 0 5 5 】

10

20

30

40

50

クロック選択器回路38は、DATM36が信号をマッピングするセクタの境界角度に対応する位相を有するクロック信号を選択する。任意の位相シフトを有するあらゆるクロックが以下の式により生成される。即ち、

$$\begin{aligned} \sin(t + \phi) &= \sin(t) \cos(\phi) \\ &\quad + \cos(t) \sin(\phi) \end{aligned} \quad (9)$$

である。

#### 【0056】

即ち、 $\cos(\phi)$  及び  $\sin(\phi)$  の固定の重み又はプログラム可能な因子を有する直交クロックの和である。一実施例において、多相クロック生成回路32は、いくつかのクロック位相（例えば、アフィン変換セクタを規定する全ての境界角度に対応する）を作成する。クロック選択器回路38は、DATM36から生成される位相制御信号psに基づいて多相クロック生成回路32の出力から必要とされるクロック信号を選択し、選択された位相クロック信号はクロックドライバモジュール48に送出され、クロックドライバモジュール48はそれら信号をデジタル増幅器46に提供する。

#### 【0057】

プリディストーションモジュール40は、下流側のデジタル電力増幅器46により発生された特定の非線形歪みを補償する大きさ信号Mu及びMvに補正を適用し、プリディストーションされたアフィン変換ベクトルDu及びDvを出力する。一実施例において、プリディストーションユニット40はルックアップテーブルを使用することにより動作する。

#### 【0058】

プリディストーションされたアフィン変換ベクトルDu及びDvは、2進数-1進数符号化 (binary to thermometer coding) 変換モジュール42において1進数符号（サーモメータコード）に変換され、モジュール42は値Tu及びTvを出力する。従来技術において既知であるように、値xのnビット表現のサーモメータコードは2^nビットを含む値である。x番目のビットまでの全ての下位ビット位置は1であり、x番目のビットより上のビット位置は0である。

#### 【0059】

デジタル電力増幅器46は、対応するアフィン変換セクタの境界角度に沿って位置合わせされたベクトルの大きさに従って選択された位相クロック信号を増幅し、これは結果としてそのセクタ内の信号になる。デジタル電力増幅器46の構造及び動作については、ここで更に詳細に説明する。

#### 【0060】

デジタル方式で増幅されたRF信号は、出力整合ネットワーク50によりインピーダンス整合される。バンドパスフィルタ52は、送信機10の帯域外のスプリアス信号成分を除去する。フィルタリングされたRF出力信号は、送信するためにアンテナ16に結合される。

#### 【0061】

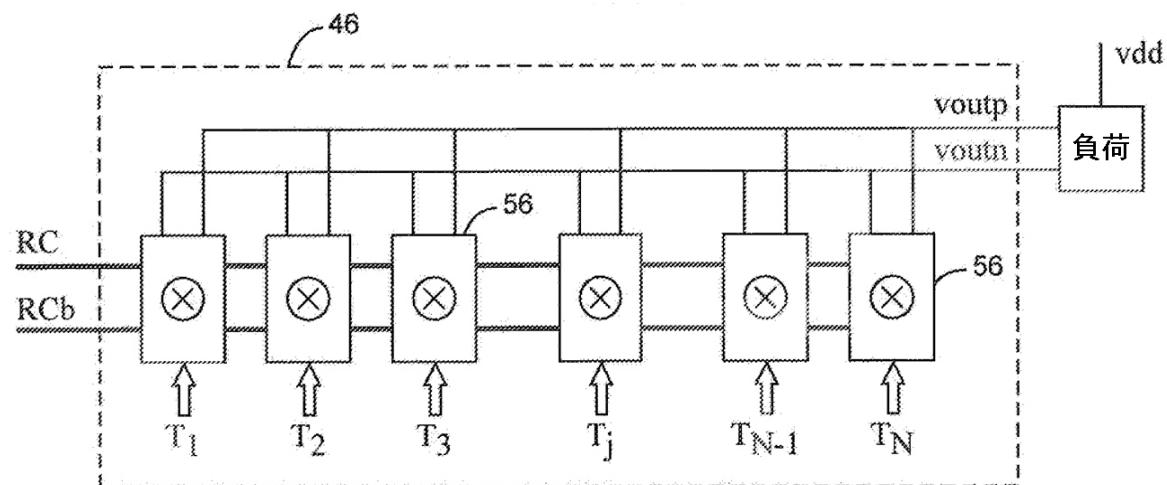

図8は、シングルエンド設計で実現され、N個の並列増幅器セル54を含むデジタル電力増幅器46の構造を示す。図9は、N個の並列差動増幅器セル56を含む差動設計又はバランス設計の増幅器46を示す。いずれの場合においても、各セル54、56は、入力ベクトル $T_j$ 、 $j = 1, 2, \dots, N$ の対応するビットとクロック信号入力ベクトルRCとを受信する。図9の差動設計のセル56は、相補クロック信号ベクトルRCbも受信する。 $T_j$ は、各増幅器セル54、56に対してビット $[Tu_i, Tv_i]$ を含むサーモメータコード化データバスである。同様に、クロック信号入力ベクトルRCは、2つの位相クロック信号Ru及びRvを含む。増幅器セル54、56の出力は接続され、負荷に印加される。

#### 【0062】

N個の並列増幅器セル54、56の出力を合計することにより、以下のように表される乗算演算が実現される。

10

20

30

40

50

## 【0063】

$$Yse = Tx \cdot Rz = \sum_{k=1}^N (Tx_k \cdot Rz) \quad \text{シングルエンドの場合}$$

$$\begin{aligned} Ydiff &= Tx \cdot Rzp - Tx \cdot Rzn \\ &= \sum_{k=1}^N (T_k \cdot Rzp - T_k \cdot Rzn) \quad \text{差動の場合} \end{aligned} \quad (10)$$

## 【0064】

10

ここで、 $Tx$  はアフィン変換ベクトルの大きさから導出される変調信号であり、 $Rz$  は位相クロック信号 ( $Ru$ 、 $Rv$ ) である。 $Rzp$  及び  $Rzn$  は、差動位相クロック信号である。このように、乗算演算子は、論理演算子 AND の複数の重み付き分岐を合計することにより実現される。この加算演算は、線形負荷において重み付き分岐の電流を結合することにより実現される。

## 【0065】

これは、以下のような演算を行う変調器に適用される。

## 【0066】

$$Ose = Tu \cdot Ru + Tv \cdot Rv = \sum_{k=1}^N (Tu_k \cdot Ru + Tv_k \cdot Rv) \quad \text{シングルエンドの場合}$$

20

$$\begin{aligned} Odif &= Tu \cdot Rup - Tu \cdot Run + Tv \cdot Rvp - Tv \cdot Rvn \\ &= \sum_{k=1}^N (Tu_k \cdot Rup - Tu_k \cdot Run + Tv_k \cdot Rvp - Tv_k \cdot Rvn) \quad \text{差動の場合} \end{aligned} \quad (11)$$

## 【0067】

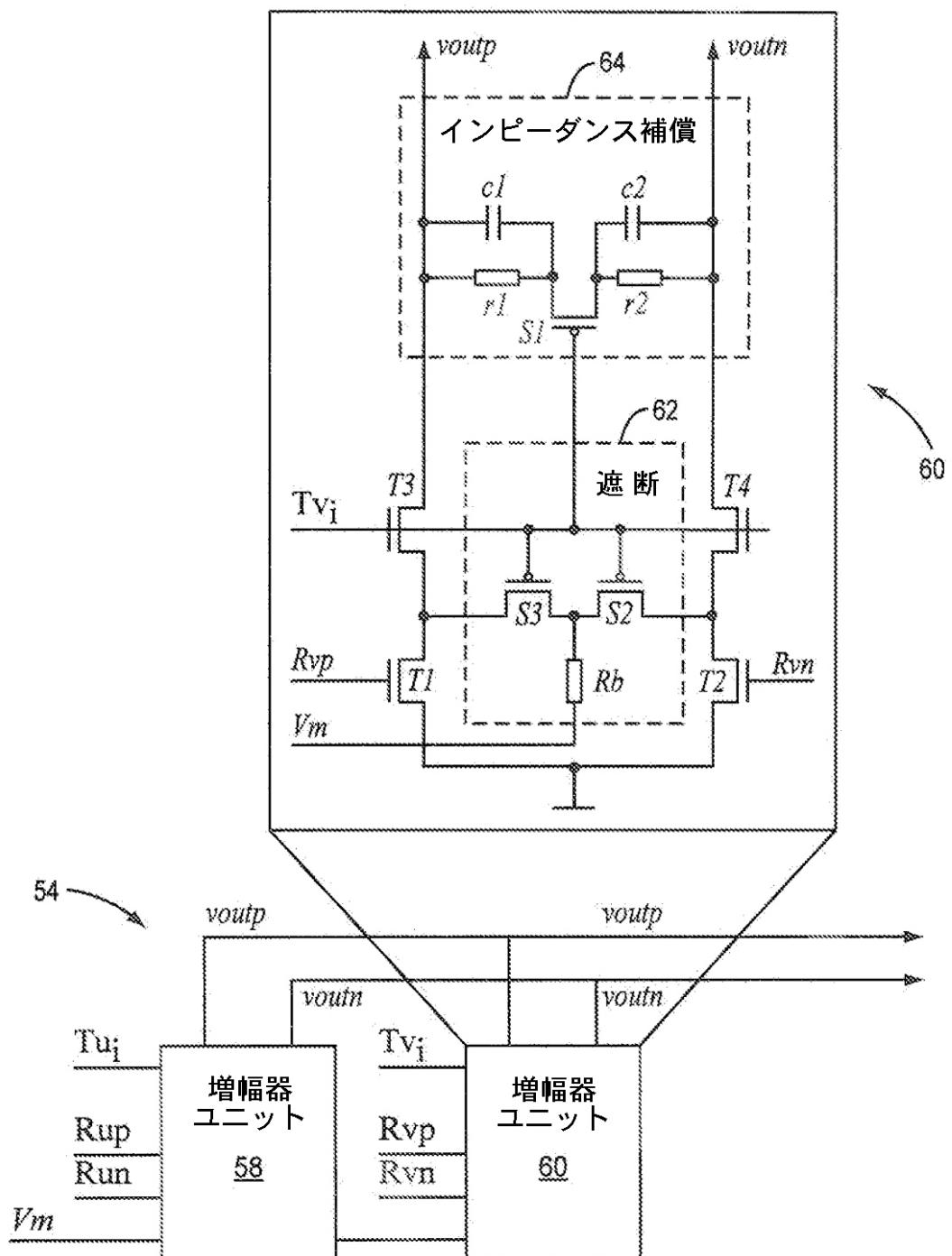

図 10 は、差動の場合の式 (11) の括弧内に表された演算の一実施形を示す。図 10 は、2つの増幅器ユニット 58、60 を含む单一の増幅器セル 56 を示す。第 1 の増幅器ユニット 58 は、変調信号  $Tu$  の  $i$  番目のビット (アフィン変換空間の境界角度  $u$  に沿うベクトルの大きさから導出される) と、境界角度  $u$  に対応する位相を有する差動クロック信号  $Rup$ 、 $Run$  とを受信する。第 2 の増幅器ユニット 60 は、変調信号  $Tv$  の  $i$  番目のビットと、境界角度  $v$  に沿うベクトルに対応する差動クロック信号  $Rvp$ 、 $Rvn$  とを受信する。

30

## 【0068】

増幅器ユニット 60 の機能回路図を図 10 に示す。トランジスタ  $T1$  及び  $T2$  は、相補クロック信号  $Rvp$ 、 $Rvn$  に接続され、トランジスタ  $T3$  及び  $T4$  は、デジタル論理  $Tv_i$  により制御され、式 (11) の演算を行う。 $voutp$  及び  $voutn$  は出力ノードである。共通ソース構成のトランジスタ  $T1$  及び  $T2$  は、高周波相互コンダクタンス  $gm$  を提供し、共通ゲート構成のトランジスタ  $T3$  及び  $T4$  は高圧出力を提供する。通常、 $T3$  及び  $T4$  は、高い絶縁破壊電圧を達成するために厚膜酸化物 LDMOS トランジスタにより構築され、それらは共通ゲート構成で動作しているため、カットオフ周波数は非常に高い。この共通ソース及び共通ゲート構造は、電力増幅器 46 の段階に対しても適切なものである。差動出力は、以下の 2 つの利点を提供する。第 1 に、シングルエンド出力の 2 倍の出力振幅を有し、第 2 に、全ての偶数次高調波及び相互変調積が除去され、スプリアス放射を低減する。

40

## 【0069】

いくつかの実施例において、 $T1$  ~  $T4$  で実現される 2 つの RF トランジスタ分岐に加えて、増幅器ユニット 60 は、インピーダンス補償回路 64 及び遮断回路 62 のうちのいずれか一方又は双方を含む。スイッチングトランジスタ  $T1$  ~  $T4$  は、出力インピーダン

50

スを変更し、トランジスタが全ての増幅器セル 5 4、5 6 でスイッチオン／オフされる（ $T$  の値に基づいて）際にに基づく位相変更の原因となるだろう。インピーダンス補償回路 6 4 の PMOS トランジスタ  $S_1$  は、 $T v_i$  信号がローレベルの時に導通する。 $S_1$  の導通により、イネーブル状態及びディスエーブル状態の双方においてセル出力インピーダンスは変更されない。

#### 【0070】

遮断回路 6 2 は、クロック漏洩を除去する。 $T v_i$  がローレベルの時、 $T_3$  及び  $R_4$  はオフである。しかし、RF 信号は結合して  $T_3$  及び  $T_4$  を通り、漏洩として  $v_{outn}$ 、 $v_{outp}$  に到達する。遮断回路 6 2 内において、PMOS トランジスタ  $S_2$  及び  $S_3$  は、増幅器ユニット 6 0 がディスエーブルされた時に導通する。これにより、RF トランジスタ  $T_1$  及び  $T_2$  のドレインのフローティングノードをバイアス電圧  $V_m$  に接続し、弱い DC 電流漏洩をドレインに提供し、イネーブルされた時に動作電圧の近くで特定の電圧電位を維持する。この構成は、トランジスタがイネーブルからディスエーブルに及びディスエーブルからイネーブルに遷移する間の充電及び放電によるスイッチング妨害を低減する。当然、他の実施例において、スイッチデバイス  $S_1 \sim S_3$  は、NMOS トランジスタにより置換可能であり、逆論理により駆動可能である。また、他の共通ゲート構成の NMOS トランジスタは、NMOS トランジスタ  $T_3$  のドレインと出力ノード  $v_{outp}$  との間及び NMOS トランジスタ  $T_4$  と出力ノード  $v_{outn}$  との間に挿入可能であり、 $T_3$  及び  $T_4$  に対する絶縁破壊に関する要求を緩和する。

#### 【0071】

図 1 1 は、I / Q 信号軌道、すなわち I 及び Q 成分形式で BBDSP12 により生成される一連のデジタルベースバンド信号が P1 から P2 に移動し、境界角度を行ったり来たりする例を示す。図示する例において、境界角度は 45° である。 $S_2$  は、デジタル電力増幅器 4 6 の増幅器セル 5 4、5 6 に供給される 1 つのクロック位相として選択される必要があることが明らかである。しかし、他のクロック位相は、信号がセクタ  $S_3$  にあるか又は  $S_2$  にあるかに依存して場合によっては  $S_3$  であるか又は  $S_1$  であるべきである。高速に 1 つのアフィン変換を使用することは、信号が異なる（隣接する）アフィン変換セクタにマッピングされる時に、クロック選択器回路 3 8 が DATM36 に応答してクロック位相をスイッチングするのに十分な程速くないという実施時におけるタイミングの問題がある。

#### 【0072】

図 1 2 は、「ホットスイッチ」DATMPA15 を含む送信機 1 0 の一実施例を示す。図 7 のコールドスイッチの実施例に対応する回路モジュールは同様に機能し、同一の番号が付される。ホットスイッチの実施例において、DATM37、プリディストーションモジュール 4 1 及びデジタル電力増幅器 4 7 は、2 つではなく 3 つの並列デジタル処理バスを有する。クロック選択器 3 9 及びクロックドライバモジュール 4 9 は、それぞれ 3 つのクロック位相を選択し且つ駆動する。2 進数 - 1 進数符号化 (binary to thermometer coding) 変換モジュール 4 2 は、上述したように機能する。しかし、ホットスイッチ DATMPA15においてそのモジュールは 3 つ存在する。

#### 【0073】

ホットスイッチ DATM37 は、信号をデジタルアフィン変換空間にマッピングし、アフィン変換セクタ境界に沿って存在するベクトルの大きさ及び角度を出力し、結果として上述したように信号になる。更に DATM37 は、アフィン変換空間における信号の軌道を予測し、第 3 のベクトルの大きさ及び角度を算出して出力する。第 3 のベクトルは、現在のセクタの境界でない予測された（隣接する）セクタの境界角度に沿って存在する。例えば図 1 1 を参照すると、信号  $S_2$  の辺りで、DATM37 は境界角度  $S_1$  及び  $S_2$  に沿ってベクトルを出力する。更に DATM37 は、信号がアフィン変換セクタ  $S_3$  に移動する可能性があると予測するため、境界角度  $S_2$  に沿って存在する第 3 のベクトルを出力する。

#### 【0074】

10

20

30

40

50

図13は、ホットスイッチデジタル電力増幅器47の増幅器セル56を示す。増幅器セル56は、3つの差動増幅器ユニット68、70、72を含み、各差動増幅器ユニットは、各ベクトルのサーモメータコード化の量の*i*番目のビットと、対応する位相クロック信号とを受信する。所定の時間において、予測されたアフィン変換セクタの「他の」境界角度に対応する3つの増幅器ユニット68、70、72のうちの1つは、デジタル電力増幅器47の全ての増幅器セル56にわたりディスエーブルされる（即ち、 $T_j$ 値は全て0である）。その一方で、他の2つの増幅器ユニット68、70、72は、コールドスイッチの実施例に関して上述したように各 $T_j$ 値に基づいて選択的にイネーブルされる。信号が隣接するアフィン変換セクタに入ると、ディスエーブルされた増幅器ユニット68、70、72はアクティブになり、他の2つのうちの一方（前のセクタの「他の」境界角度に対応する）がデジタル電力増幅器47の全ての増幅器セル56にわたりディスエーブルされる。このように、デジタル電力増幅器47は、信号がアフィン変換セクタ間を移動した時に境界角度間で迅速にスイッチングできる。図13は、上述したように機能する増幅器ユニット70（全ての増幅器ユニット68、70、72を表す）のトランジスタ回路の一実施例を示す。

#### 【0075】

図14は、3つのシングルエンド増幅器ユニット68、70、72を含むホットスイッチデジタル電力増幅器47の増幅器セル54を示す。尚、コールドスイッチデジタル電力増幅器46の増幅器セル54は、同一のトランジスタ構造を有するが、増幅器ユニット68、70、72のうち2つのみを含む。

#### 【0076】

図15は、ホットスイッチDATM37に対する例示的な機能構造を示す。DATM37は、2つの行列演算子M1 22及びM2 24と、マルチプレクサ26と、制御信号CTR及びクロック位相選択信号psを生成するデジタル論理ブロック28とを含む。

#### 【0077】

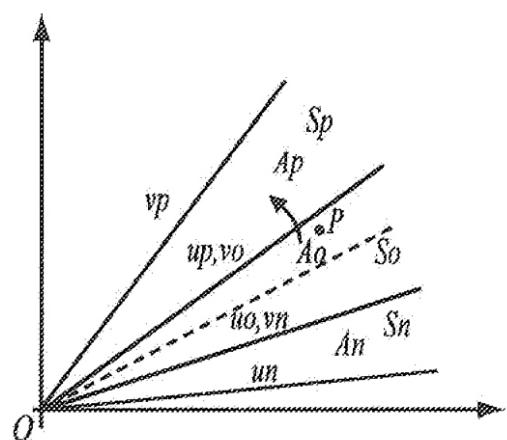

図16は、出力uo及びvoを作成するアフィン変換Aoに対応するセクタS0に現在配置されている信号P(i, q)を示す。アフィン変換Aoは、行列演算子M1 22に割り当てられる。出力ベクトルuo及びvoの振幅を比較して、 $|v_0| > |u_0|$ である場合、M2は演算パラメータとしてアフィン変換Apをロードする。それ以外の場合、M2はAnをロードする。従って、Aoは現在アクティブなアフィン変換であり、Apはホットスイッチされる準備がされた別のアフィン変換である。信号が実際にセクタSpに入る場合、M2 = Apであり、M1はホットスイッチされる準備がされた別のアフィン変換のために解放される。

#### 【0078】

現在の入力信号i(t)及びq(t)と次の入力信号i(t+1)及びq(t+1)に基づいて、ログモジュール28は、行列パラメータの更新のための必要とされる全ての制御信号CTRと、クロック位相信号の更新のための位相選択信号psとを提供する。

#### 【0079】

対数（ログ）モジュール28の一実施例において、アルゴリズムは、所定の信号のセクタ番号を判定する。ここで、セクタ数は $m = 2^b$ であり、bは整数である。アルゴリズムは、現在の成分を半分のセクタに投影する演算の有限数の繰り返しを使用し、2進値のbビットを割り当てる。アルゴリズムについては、図17を参照して説明する。図17において、記号CXは、X°の位相オフセットを有するクロックを示す。

#### 【0080】

$m = 64$ と仮定すると、 $b = 6$ である。所定の点P(x, y)は第1象限に配置され、最初の2ビットは値0, 0を割り当てられる。座標x及びyは比較される。ここでは $x < y$ であるため、次のビットは値0を割り当てられ、P(x, y)はクロック位相C45とC0との間に投影され、x1及びy1が結果として得られる。 $y_1 > x_1$ であるため、次のビットは値0を割り当てられ、P(x, y)はクロック位相C45とC22.5との間に投影され、x2及びy2が結果として得られる。 $y_2 > x_2$ であるため、次のビットは

値 1 を割り当てられ、 $P(x, y)$  はクロック位相 C 45 と C 37.5 との間に投影され、 $x < 3$  及び  $y < 3$  が結果として得られる。 $x < 3 < y < 3$  であるため、次のビットは値 1 が割り当てられ、アルゴリズムは終了する。従って、セクタ番号は 2 進数形式で (000110) であることが分かる。

#### 【0081】

第 1 象限に配置された所定の点  $P(x, y)$  に対するセクタ番号を判定する別の方法は  $y / x$  の比を算出することであり、以下の通りである。即ち、

もし  $\tan\{(k-1)\} < y / x < \tan\{(k-1)\}$  であれば、

セクタ( $y / x$ ) =  $k$ 、であり、又は

もし  $\tan\{(k-1)\} \cdot x < y < \tan\{(k-1)\} \cdot x$  であれば、

セクタ( $y / x$ ) =  $k$  (12)

である。

#### 【0082】

その時、 $P(x, y)$  は  $k$  番目のセクタに入る。ここで、 $0 \leq k \leq I-1$ 、且つ  $I = m / 4$  である。一般に、象限  $K$  に存在する所定の点  $P(x, y)$  に対して、セクタ番号  $k_s$  は以下の式により見つけられる。即ち、

$K = 1$  の場合、

もし  $\tan\{(k-1)\} \cdot x < y < \tan\{(k-1)\} \cdot x$  であれば、

セクタ( $y / x$ ) =  $k$  であり、

$K = 2$  の場合、

もし  $\tan\{(k-1)\} \cdot y < |x| < \tan\{(k-1)\} \cdot y$  であれば、

セクタ( $|x| / y$ ) =  $k$  であり、

$K = 3$  の場合、

もし  $\tan\{(k-1)\} \cdot |x| < |y| < \tan\{(k-1)\} \cdot |x|$  であれば、

セクタ( $|y| / |x|$ ) =  $k$  であり、

$K = 4$  の場合、

もし  $\tan\{(k-1)\} \cdot |y| < x < \tan\{(k-1)\} \cdot |y|$  であれば

セクタ( $x / |y|$ ) =  $k$  であり、

最終的には、 $k_s = (K-1) \cdot I + k$  (13)

である。

#### 【0083】

即ち、入力変数  $x$  及び  $y$  の絶対値をとり、それらを変数の符号から判断される場所に従って入れ替える。その後、 $I$  の比較を行い、セクタ番号をカウントする。比較は、高速化するために並列構造で実現される。

#### 【0084】

再び、図 11 に戻ると、原点に近い信号に対して、全てのセクタは近接しつつも離間され、小さな信号の動きでもセクタ境界の横断を迅速にトリガすることになり、これは D A T M P A 14、15 における高速スイッチングを意味する。回路に対する速度要求を軽減するために、正方形の  $Z$  領域等の原点を範囲に含む領域が規定される。一般に  $Z$  領域は、その境界が容易に判定できる限り、どのような形状をとることもできる。 $Z$  領域内では  $m$  は  $M_S$  となり、 $X$  領域外では  $m$  は  $M_L$  となる。ここで、 $M_L > M_S$  であり、 $M_L$  及び  $M_S$  は正の整数である。 $M_S = 4$  である場合、領域  $Z$  は  $z$  正方形となり、この場合、直交変調は  $Z$  領域内で適用され、アフィン変換は  $Z$  領域外で適用される。一般に、 $M_S$  は他のいかなる整数値もとることができる。

#### 【0085】

$z$  正方形領域は、非常に単純な境界を有するため、以下が得られる。即ち、

( $|i| < z$  且つ  $|q| < z$ ) の場合、

$P(i, q) = Z$  であり、

10

20

30

40

50

上記以外の場合、

P ( i , q ) S

( 1 4 )

である。

【 0 0 8 6 】

ここで、z は正方形の Z 領域の境界を規定する小さな正数であり、S は Z を除く ( i , q ) 平面全体の領域である。従って、領域 Z 内において、マッピングは以下の通りである。

【 0 0 8 7 】

$$\begin{bmatrix} uz \\ vz \end{bmatrix} = \begin{bmatrix} 1, & 0 \\ 0, & 1 \end{bmatrix} \begin{bmatrix} i \\ q \end{bmatrix}$$

10

( 1 5 )

【 0 0 8 8 】

Z 外では、式 ( 7 ) で規定されたアフィン変換が適用される。

【 0 0 8 9 】

一実施例において、領域 Z は 2 つ以上の領域に更に分割され、信号は種々の数のセクタにマッピングされる。一例として、領域 Z は原点に近くなる程セクタ数が徐々に少なくなる階層構造を仮定する。当業者であれば、本発明の教示を仮定すると所定のあらゆる実施形に対してセクタ数や移行を配置する原点からの距離を容易に判定できる。

20

【 0 0 9 0 】

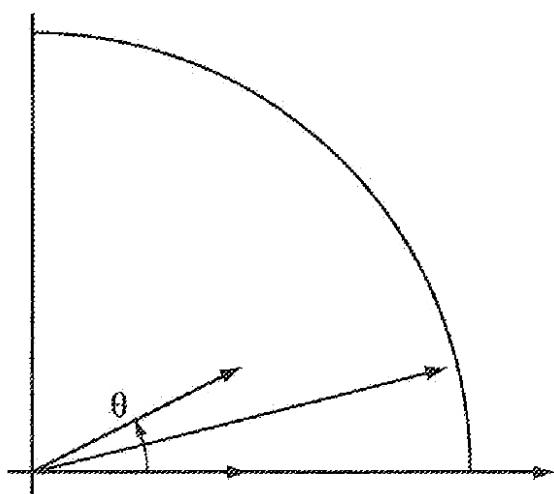

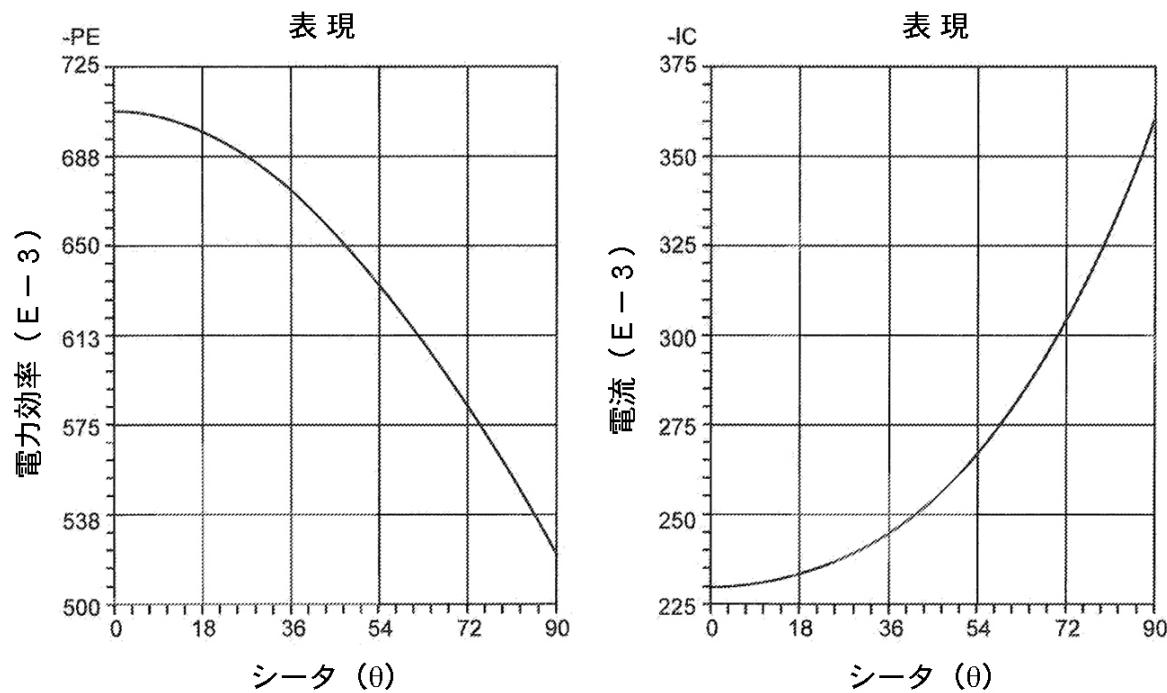

D A T M P A 1 4 、 1 5 の電力及び効率について、図 1 8 を参照して考察する。同一の振幅を有し且つ間に角度  $\theta$  を有する 2 つのベクトルが合計されると仮定する。結合ベクトルの振幅は一定に維持されるが、その一方で、角度  $\theta$  は 0 から 90° まで変更される。角度信号  $\theta$  の関数としてデジタル電力増幅器 4 6 の電力効率を例示するために、それら信号に基づいてシミュレーションを行った。

【 0 0 9 1 】

シミュレーション結果を図 1 9 の第 1 のグラフに示す。角度  $\theta$  の関数である消費電流を第 2 のグラフに示す。これらのグラフが示すように、角度  $\theta$  が小さい程、電力効率は高い。角度  $\theta$  が 0 である場合、D A T M P A 1 4 、 1 5 は、極性変調と同一の電力効率を達成する。角度  $\theta$  が 90° である場合、D A T M P A 1 4 、 1 5 は、直交変調と同一の電力効率を達成する。角度  $\theta = 360 / m$  であるため、m が増加すると、 $\theta$  は減少する。m が十分に大きい時に飽和状態となり、更なる向上は僅かである。

30

【 0 0 9 2 】

ユニークな利点がアフィン変換変調のデジタル実施系から得られるが、アナログ変調器でも実現可能である。アナログアフィン変換変調器において、ギルバートセル等のいくつかの異なる混合器セルは並列に接続可能である。

【 0 0 9 3 】

40

ベースバンド入力信号を直交デカルト信号として説明したが、2 つ以上の成分を含む他の信号形式がアフィン空間に都合よくマッピングされても良く、これにより、ここで説明されるデジタルアフィン変換変調電力増幅器の実現が可能になる。一例として、ベースバンド入力信号は極座標形式であってもよい。

【 0 0 9 4 】

図 1 、図 7 及び図 1 2 は、アンテナ 1 6 を直接駆動するものとして D A T M P A 1 4 、 1 5 を示す。しかし、本発明はこれに限定されるものではない。一実施例において、D A T A M 1 4 、 1 5 は、従来の電力増幅器に対して変調された搬送波信号を生成してもよい。例えば D A T A M 1 4 、 1 5 はトランシーバ A S I C に統合され、独立した電力増幅器を駆動する送信信号を生成してもよい。更にフィルタ、スイッチ及びデュプレクサ等の従

50

來の整合構成要素は、DATMPA 14、15の出力と物理アンテナ16との間に介在してもよいことが当業者には容易に理解されるだろう。

【0095】

アフィン変換変調とそれを実現するデジタルアフィン変換変調電力増幅器(DATMPA)14、15とは、従来技術より有利な点をいくつか提供する。DATMPA 14、15は、直交変調器にわたり増加した電力効率を示し、極性変調の電力効率に近づく。しかし、DATMPA 14、15は、帯域幅の拡張及び群遅延の不整合等の極性変調における有害な問題を回避する。デジタル電力増幅器46、47のインピーダンス補償回路64は、関連する増幅器ユニット58、60、68、70、72がイネーブルされるかディスエーブルされるかに関係なく一定の出力インピーダンスを維持する。これにより、通常、スイッチングされた電力増幅器アレイに関連する位相シフトの問題をなくし、電力増幅器46、47の出力における振幅の非線形性を低減する。

【0096】

更にイネーブル状態とディスエーブル状態との間で増幅器ユニット58、60、68、70、72をスイッチングする影響により、電力増幅器46、47の出力の過渡挙動が減少する。また、プリディストーションモジュール40、41は、電力増幅器46、47における非線形性を補償する。一実施例において、プリディストーションは、ルックアップテーブルを介してデジタル領域において達成される。当然、本発明は、本発明の主な特徴から逸脱することなく、ここで特に示した方法以外の方法で実施されてもよい。本発明の実施例は、全ての点において例示的なものであると考えられ、限定的なものではない。添付の請求の範囲の意味及び同等の範囲内で行われる全ての変更は、請求の範囲内に含まれることが意図されている。

【図1】

FIG. 1

【図2】

FIG. 2

【図3】

FIG. 3

【図4】

FIG. 4

【図5】

FIG. 5

【図6】

FIG. 6

【図7】

FIG. 7

【図8】

FIG. 8

【図9】

FIG. 9

【図10】

FIG. 10

【図 11】

FIG. 11

【図 12】

FIG. 12

【図13】

FIG. 13

【図14】

FIG. 14

【図15】

FIG. 15

【図16】

FIG. 16

【図17】

FIG. 17

【図18】

FIG. 18

【図 19】

FIG. 19

【図20】

FIG. 20

【図21】

FIG. 21

【図22】

FIG. 22

---

フロントページの続き

(72)発明者 ム, フエンハオ

スウェーデン国 ヤーロプ エス-24563, スメルブロンメフ. 17

(72)発明者 マチソン, スヴェン

スウェーデン国 ピヤレド エス-237 36, エスタンヴェグ 3

審査官 白井 孝治

(56)参考文献 特開2010-011142(JP,A)

(58)調査した分野(Int.Cl., DB名)

H03F 1/00 ~ 3/72

H04L 27/00

H04L 27/36