# (19) World Intellectual Property Organization

International Bureau

# . I TERRE BUILDER IN BERNE HER BERN BEINE BUIL IN DER HER BERNE HERE HERE BUILD BEINE BERNE HERE HERE HER

# (43) International Publication Date 28 September 2006 (28.09.2006)

ion Date 9.2006)

# (10) International Publication Number WO 2006/102180 A2

(51) International Patent Classification: *B28B 19/00* (2006.01) *C23C 18/34* (2006.01)

(21) International Application Number:

PCT/US2006/009918

(22) International Filing Date: 20 March 2006 (20.03.2006)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

| 60/663,493 | 18 March 2005 (18.03.2005)    | US |

|------------|-------------------------------|----|

| 60/683,599 | 23 May 2005 (23.05.2005)      | US |

| 60/703,538 | 29 July 2005 (29.07.2005)     | US |

| 60/703,633 | 29 July 2005 (29.07.2005)     | US |

| 60/709,564 | 19 August 2005 (19.08.2005)   | US |

| 60/754,230 | 27 December 2005 (27.12.2005) | US |

|            |                               |    |

(71) Applicant (for all designated States except US): AP-PLIED MATERIALS, INC. [US/US]; 3050 Bowers Avenue, Santa Clara, CA 95054 (US).

(72) Inventors; and

(75) Inventors/Applicants (for US only): WEIDMAN, Timothy W. [US/US]; 776 Henderson Avenue, Sunnyvale, CA 94086 (US). WIJEKOON, Kapila P. [US/US]; 438 East Charleston Road, Palo Alto, CA 94306 (US). ZHU, Zhize [CN/US]; 10282 Terry Way, Apt. #3, Cupertino, CA 95014 (US). GELATOS, Avgerinos V. (Jerry) [US/US]; 2651 Eaton Avenue, Redwood City, CA 94062 (US). KHANDELWAL, Amit [IN/US]; 3770 Flora Vista Ave., #2102, Santa Clara, CA 95051 (US). SHANMUGASUNDRAM, Arulkumar [IN/US]; 428 Madera Avenue #10, Sunnyvale, CA 94086 (US). YANG, Michael X. [US/US]; 793 Cereza Drive, Palo Alto, CA 94306 (US). WANG, Yaxin [US/US]; 44224 Ibero Way, Fremont, CA 94539 (US). MEI, Fang [CN/US]; 975 Laguna Circle, Foster City, CA 94404 (US). MOGHADAM, Farhad K. [US/US]; 276

Old Adobe Road, Los Gatos, CA 95030 (US). **STEWART, Michael P.** [US/US]; 392 N. Rengstorff Ave., Apt. 2, Mountain View, CA 94043 (US). **KRISHNA, Nety M.** [IN/US]; 1345 Floyd Avenue, Sunnyvale, CA 94087 (US). **KONECNI, Anthony** [US/US]; 12891 Andys Gulch Road, Boise, ID 83714 (US). **GANDIKOTA, Srinivas** [US/US]; 2727 Monroe Street, Santa Clara, CA 95054 (US).

- (74) Agents: PATTERSON, B. Todd et al.; PATTERSON & SHERIDAN, L.L.P., 3040 Post Oak Blvd., Suite 1500, Houston, Texas 77056-6582 (US).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, LY, MA, MD, MG, MK, MN, MW, MX, MZ, NA, NG, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RU, SC, SD, SE, SG, SK, SL, SM, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, YU, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HU, IE, IS, IT, LT, LU, LV, MC, NL, PL, PT, RO, SE, SI, SK, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### **Published:**

without international search report and to be republished upon receipt of that report

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

(54) Title: CONTACT METALLIZATION METHODS AND PROCESSES

(57) Abstract: Embodiments of the invention generally provide methods of filling contact level features formed in a semiconductor device by depositing a barrier layer over the contact and then filing the contact using an PVD, CVD, ALD, electrochemical plating and/or electroless deposition processes. In one embodiment, the barrier layer contains catalytically active surface that allows the electroless deposition of a metal on the surface. In one aspect, the electrolessly deposited metal is copper or a copper alloy. In one embodiment, a method for depositing a material on a substrate includes positioning a substrate within a process chamber, exposing the substrate to at least one pretreatment step and filling the contact by an electroless deposition process. Embodiments of the invention provide a simplified method of filling contact level features formed in a semiconductor device, which include novel methods

of forming a contact level feature that contains a silicide interface and a tungsten CVD deposited layer.

## CONTACT METALLIZATION METHODS AND PROCESSES

## **BACKGROUND OF THE INVENTION**

#### Field of the Invention

[0001] Embodiments of the invention generally relate to methods for depositing materials on a substrate, and more specifically to methods for filling apertures within a contact formed on a substrate.

# **Description of the Related Art**

[0002] Multilevel, 45 nm node metallization is one of the key technologies for the next generation of very large scale integration (VLSI). The multilevel interconnects that lie at the heart of this technology possess features with small CD's and high aspect ratios including contacts, vias, lines and other apertures. Reliable formation of these features is very important for the success of VLSI and the continued effort to increase quality and circuit density on individual substrates. Therefore, there is a great amount of ongoing effort being directed to the formation of void-free features with low contact resistance for the 45 nm node and nodes below.

Tungsten is a choice metal for filling VLSI features, such as sub-micron contact on a substrate. Conventional "contacts" are formed by depositing a conductive interconnect material, such as tungsten into an aperture (e.g., via) on the surface of insulating material disposed between two spaced-apart conductive layers. The aspect ratio of such an opening may inhibit deposition of a conformal conductive interconnect material to fill an aperture. Although tungsten is a popular interconnect material, vapor deposition processes for depositing tungsten commonly suffer from void or a seam type defect creation within the contact plug, as illustrated in Figure 1C. Also, tungsten is has a relatively high resistivity, which will result in a high circuit resistance formed using the tungsten containing contact.

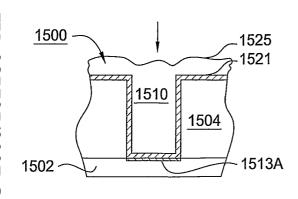

[0004] Figure 1A depicts a schematic cross-sectional view of an integrated circuit device on substrate 100 containing a via or aperture 105 formed in dielectric layer 104 to expose contact layer 102. During a vapor deposition process that may include chemical vapor deposition (CVD) or atomic layer deposition (ALD), a tungsten layer 106 is deposited on dielectric layer 104 and within aperture 105 including on contact layer 102 and the sidewalls of dielectric layer 104 to form plug

103, as illustrated in Figure 1B. Near the opening 107 of plug 103, tungsten layer 106 may pinch off, depicted in Figure 1C, so that plug 103 maintains a seam or a void 108 therein. During a subsequent chemical mechanical polishing (CMP) process that removes a portion of tungsten layer 106 and dielectric layer 104 from the surface of substrate 100, void 108 may be breached or exposed to form gap 110 within plug 103, as illustrated in Figure 1D. Figure 1E depicts conductive layer 112 (e.g., copper) deposited on substrate 100 forming void 114 by enclosing gap 110. Substrate 100 may contain additional layers of material depending on the overall architecture of the electronic device. For example, dielectric layer 104 may be covered by a barrier layer (not shown) thereon prior to the deposition of conductive layer 112 and/or conductive layer 112 may also contain a barrier layer (not shown) thereon prior to the deposition of layer 120.

Defects, such as a seam or a void 114, may cause a series of problems [0005] during the fabrication of electronic devices depicted herein. The resistance to current flow through the plug 103 is impaired due to the lack of tungsten material in However, a more serious obstacle during fabrication is the the void 114. displacement of voids from one layer to the next. For example, subsequent fabrication processes of substrate 100 may include the deposition of layer 120 (e.g., dielectric layer) on conductive layer 112. During subsequent thermal processing, such as an annealing process, the material 116 from conductive layer 112 may diffuse into void 114 and form a void 118 within conductive layer 112. As illustrated in Figure 1F, material 116 may not diffuse completely to the bottom of void 114. The defect formed in the conductive layer 112, such as void 118, will increase the resistance of the circuit containing the defect and thus affect device performance. Ultimately, the defects in the conductive layer 112 can affect the device yield of the fabricated substrate. Therefore, there is a need for a method of reliably forming a plug 103 that does not have a seam or void type defect.

[0006] Also, one limitation of device performance, or device speed, is related to the resistance of the circuit formed in the semiconductor device. If the geometry of the device(s) remain the same (e.g., trace length, contact feature aspect ratio) the main factor that effects the resistance of a formed circuit is the resistivity of the materials used to form the device. The lower the resistivity, the better one material will perform versus another material. For example, the resistivity of pure tungsten is

about 3.3 times higher than the resistivity of pure copper and thus a copper containing device would be faster than a comparable circuit made using tungsten. This among other reasons is often why copper interconnects are formed on integration levels M1 and above. In general, the term metal layer 1, or M1 layer, is generally intended to describe an interconnect layer (*e.g.*, conductive layer 112) formed over the contact level layer, such as a tungsten plug (*e.g.*, plug 103) that is formed during the contact layer formation process. Tungsten is commonly used at the contact level features due to it ability to fill features using CVD processes and it will not rapidly diffuse into silicon and adjacent oxide layers.

[0007] Reliably producing nanometer-sized features is one of the key technologies for the next generation of very large scale integration (VLSI) and ultra large scale integration (ULSI) of semiconductor devices. However, as the fringes of circuit technology are pressed, the shrinking dimensions of interconnects in VLSI and ULSI technology have placed additional demands on the processing capabilities. The multilevel interconnects that lie at the heart of this technology require precise processing of the contact level features (e.g., contacts, vias and other interconnects). Reliable formation of these interconnects is very important to VLSI and ULSI success and to the continued effort to increase circuit density and quality of individual substrates.

[0008] Copper has become the metals of choice for nanometer-sized interconnect technology used in the metal layers M1 and above because copper has a lower electrical resistivity than most commonly used metals (e.g., aluminum) and a higher current carrying capacity. These characteristics are important for supporting the higher current densities experienced at high levels of integration and increased device speed. Further, copper has a good thermal conductivity and is available in a highly pure state. Unfortunately, the use of copper at the contact level of a device has a number of drawbacks which include that it rapidly diffuses through silicon and dielectric materials, it has a relatively low melting point which can limit the maximum allowable silicidation formation temperature.

[0009] Contact level metallization processes require the formation of a silicide at the doped silicon source or drain interface to reduce the contact resistance and thus improve the speed of the formed device(s). Typically, conventional contact level metallization process(es) require the time consuming and complex process steps of

depositing a metal layer that will form a silicide at the doped silicon interface (*e.g.*, source or drain interface), removing the excess metal layer from the "field" (*e.g.*, top surface of the substrate in which the features are formed) by use of a chemical mechanical polishing (CMP) type process, performing a high temperature anneal process to form a metal silicide layer, depositing a liner/barrier layer (*e.g.*, titanium nitride (TiN), titanium (Ti), tantalum (Ta), tantalum nitride (TaN)) over the formed metal/metal silicide layer, and then filling the contact feature formed in the dielectric layer with tungsten (W) using a tungsten hexafluoride (WF<sub>6</sub>) chemical vapor deposition (CVD) process. Since the contact level metallization process is relatively complex and requires a number of process steps, the chance of misprocessing the substrate or the chance that contamination will affect the device yield is very high.

[0010] Therefore, there exists a need for an improved contact level device that is void free, that has a low electrical resistance, that has good electromigration performance, that is reliable, and that can be reliably formed. Also, there is a need for a less time consuming and less complex method of forming a contact level interconnect that has a silicide formed at the doped silicon interface.

# **SUMMARY OF THE INVENTION**

[0011] The present invention generally provide a method for depositing a material on a contact level feature formed on a substrate, comprising providing a substrate that has one or more contact level features that have an exposed silicide layer formed on a silicon containing region, depositing a barrier layer over the surface of the exposed silicide layer, wherein the depositing the barrier layer comprises depositing a first metal layer on the exposed silicide layer, and depositing a second metal layer over the first metal layer, wherein the second metal layer contains a metal selected from a group consisting of ruthenium (Ru), cobalt (Co), nickel (Ni), rhodium (Rh), iridium (Ir), palladium (Pd) and platinum (Pt), and filling the contact level feature with a metal containing layer.

[0012] Embodiments of the invention further provide a material on a contact level feature formed on a substrate, comprising providing a substrate that has one or more contact level features that have an exposed silicide layer formed on a doped silicon containing region, depositing a barrier layer over the surface of the exposed silicide layer, wherein the depositing the barrier layer comprises depositing a first metal layer on the exposed silicide layer, and depositing a second metal layer over

the first metal layer, wherein the second metal layer contains a metal selected from a group consisting of ruthenium (Ru), cobalt (Co), nickel (Ni), rhodium (Rh), iridium (Ir), palladium (Pd) and platinum (Pt), electrolessly depositing a first copper containing layer on the barrier layer, and depositing a second copper containing layer on the first copper containing layer to fill the one or more contact level features.

[0013] Embodiments of the invention further provide a method for depositing a material on a contact level feature formed on a substrate, comprising depositing a barrier layer over the surfaces of one or more contact level features formed on the substrate, and electrolessly depositing a copper containing layer on the barrier layer using a metal layer electroless deposition solution, wherein the metal layer electroless deposition solution comprises EDTA and copper ions at a concentration ratio of less than about 6:1.

Embodiments of the invention further provide a method for depositing a material on a contact level feature formed on a substrate, comprising electrolessly depositing a first metal containing layer on a doped silicon region on a surface of a substrate, forming a contact level interconnect feature, wherein the process of forming the contact level interconnect comprises depositing a dielectric layer over a surface of the substrate and the first metal containing layer, and forming one or more contact level features in the dielectric layer using conventional semiconductor processing methods, wherein the first metal containing layer is exposed at the bottom of one or more of the contact level features, depositing a barrier layer over the surface of the first metal layer, wherein the depositing the barrier layer comprises depositing a second metal layer over the first metal layer, wherein the second metal layer contains a metal selected from a group consisting of ruthenium (Ru), cobalt (Co), nickel (Ni), rhodium (Rh), iridium (Ir), palladium (Pd) and platinum (Pt); and electrolessly depositing a copper containing layer on the barrier layer.

[0015] Embodiments of the invention further provide a method for depositing a material on a contact level feature formed on a substrate, comprising providing a substrate that has one or more contact level features that have an exposed doped silicon containing region, depositing a first metal layer on the doped silicon containing region, depositing a barrier layer over the surface of the first metal layer, wherein the depositing the barrier layer comprises depositing a second layer over

the first layer, wherein the second layer comprises ruthenium and tantalum, and filling the contact level feature with a metal containing layer.

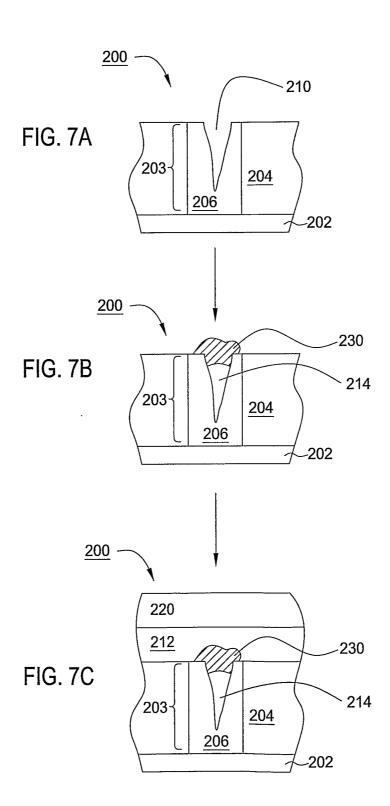

[0016] Embodiments of the invention further provide a method of forming an electrical contact on a silicon substrate, comprising providing a substrate containing an exposed tungsten-containing contact plug exposed that has an exposed gap formed therein, exposing the substrate to a pretreatment process, wherein the pretreatment process is adapted to remove an oxide layer from a surface of the exposed tungsten-containing contact plug, filling the exposed gap with a fill material. [0017] Embodiments of the invention further provide a method of forming an electrical contact on a silicon substrate, comprising providing a silicon substrate having a first dielectric layer which is disposed on a surface of the silicon substrate and a first aperture formed in the first dielectric layer, wherein a doped silicon containing region of the silicon substrate is exposed at the bottom of the first aperture, filling the first aperture formed in the first dielectric layer with a tungsten containing layer, wherein the tungsten containing layer is in electrical communication with the doped silicon containing region, removing an amount of the tungsten containing layer disposed on the first dielectric layer, wherein a gap formed in the tungsten containing layer during the step of filling the first aperture is exposed, and depositing a material on the surface of the silicon substrate to substantially cover the gap formed in the tungsten containing layer.

[0018] Embodiments of the invention further provide a method of forming an electrical contact on a silicon substrate, comprising providing a substrate containing first dielectric layer that contains at least one tungsten-containing contact plug that has an exposed surface, forming a second dielectric layer over the first dielectric layer and the tungsten-containing contact plug, forming a second aperture in the second dielectric layer that is in communication with the exposed surface of the tungsten-containing contact plug, and selectively filling the second aperture with a fill material.

[0019] Embodiments of the invention further provide a method for depositing a material on a substrate, comprising positioning a silicon containing substrate that has one or more contact level features that have an exposed doped silicon containing region, pretreating the exposed doped silicon containing region, wherein the pretreating process is adapted to remove an oxide layer from the exposed doped

silicon containing region, depositing a metal containing layer over a surface of the exposed doped silicon containing regions, and depositing a tungsten layer over the metal containing layer at a temperature between about 300 °C and about 400 °C, wherein during the tungsten layer deposition process a metal silicide is formed.

[0020] Embodiments of the invention further provide a method for depositing a material on a substrate, comprising positioning a silicon containing substrate that has one or more contact level features that have an exposed doped silicon containing region, pretreating the exposed doped silicon containing region, wherein the pretreating process is adapted to remove an oxide layer from the exposed doped silicon containing region, depositing a nickel containing layer over the bottom surface of the one or more contact level features, forming a nickel silicide layer by exposing the deposited nickel containing layer and silicon containing substrate to temperatures greater the 250 °C, depositing a cobalt containing layer over the nickel silicide layer, and depositing a tungsten layer on the cobalt containing layer.

[0021] Embodiments of the invention further provide a method for depositing a material on a substrate, comprising providing a substrate that has one or more contact level features that have an exposed doped silicon containing region, selectively depositing a metal containing layer over a surface of the exposed doped silicon containing regions, and depositing a tungsten layer on the metal layer at a temperature between about 300 °C and about 400 °C, wherein during the process of depositing tungsten layer a metal silicide is formed at the surface of the exposed doped silicon containing region.

[0022] Embodiments of the invention further provide a method of forming an interconnect on a silicon substrate, comprising providing a substrate having an aperture formed in a dielectric layer disposed on a surface of the substrate, wherein the aperture is in communication with an exposed surface of a tungsten-containing contact plug, dispensing a clean solution on an the exposed surface of the tungsten-containing contact plug, wherein the clean solution comprises hydrogen fluoride, disposing a preparation solution on the exposed surface of the tungsten-containing contact plug, wherein the preparation solution comprises a tungstate source, depositing a initiation layer on the exposed surface of the tungsten-containing contact plug using an activation solution, activating the initiation layer using a rinse activation solution, and selectively filling the second aperture with a fill material.

# BRIEF DESCRIPTION OF THE DRAWINGS

[0023] So that the manner in which the above recited features of the invention are attained and can be understood in detail, a more particular description of the invention, briefly summarized above, may be had by reference to the embodiments thereof which are illustrated in the appended drawings. It is to be noted, however, that the appended drawings illustrate only typical embodiments of this invention and are therefore not to be considered limiting of its scope, for the invention may admit to other equally effective embodiments.

[0024] Figures 1A-1F illustrate schematic cross-sectional views of an integrated circuit formed by a process described in the art;

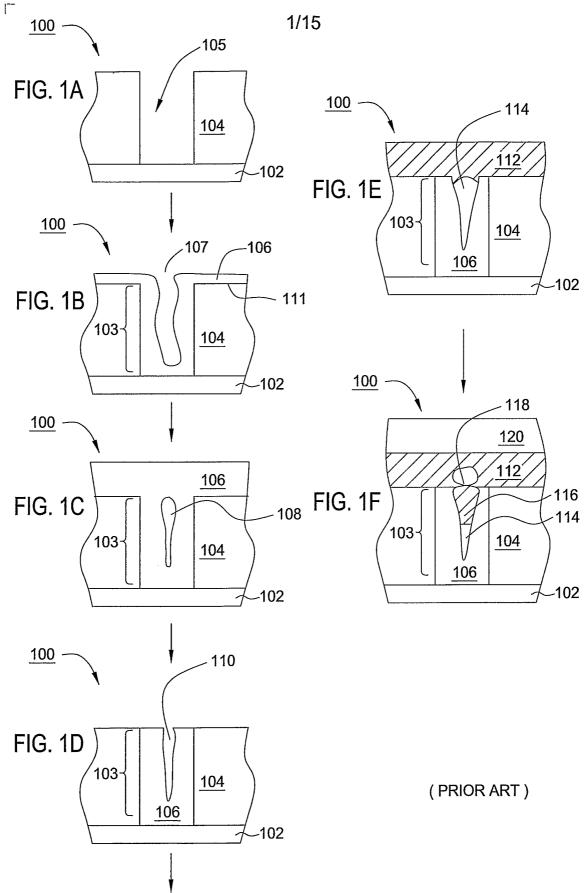

[0025] Figures 2A-2G illustrate schematic cross-sectional views of an contact level feature formed by a process described within an embodiment herein;

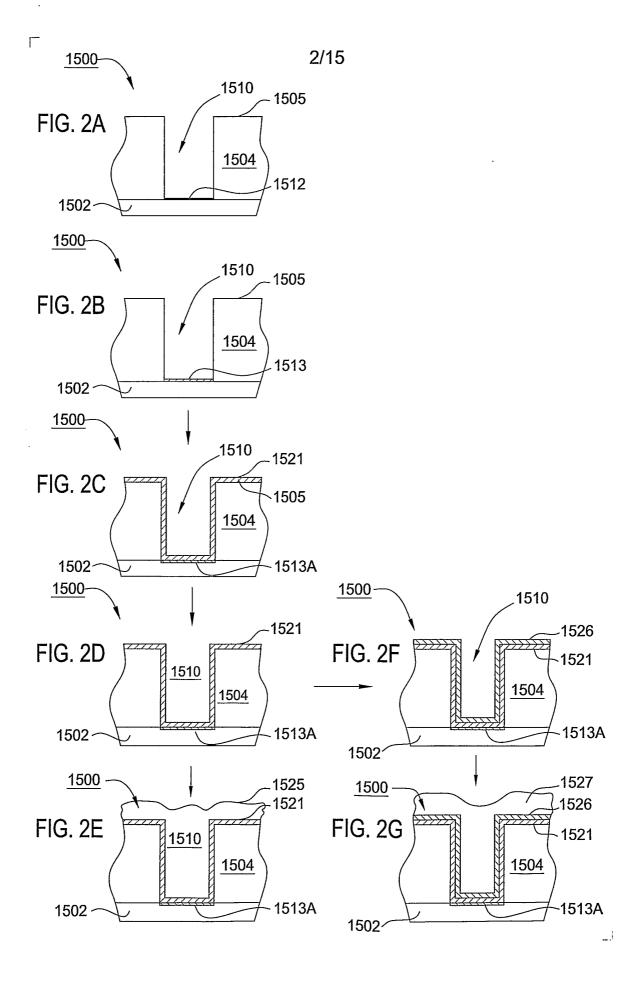

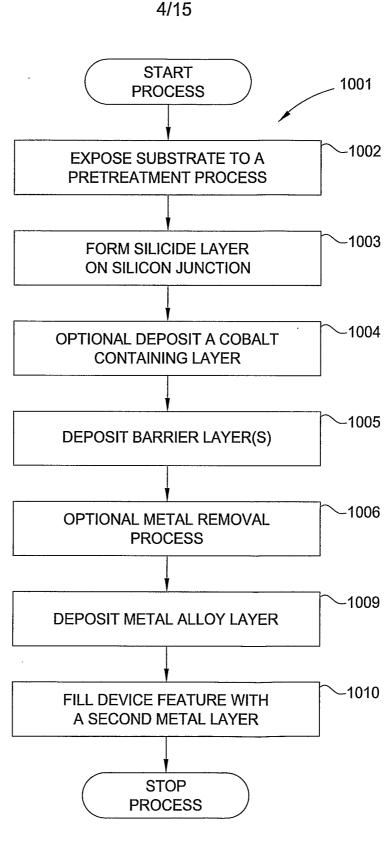

[0026] Figure 3 is a flow chart depicting an deposition process as described within an embodiment herein;

[0027] Figure 4 is a flow chart depicting a deposition process as described within an embodiment herein.

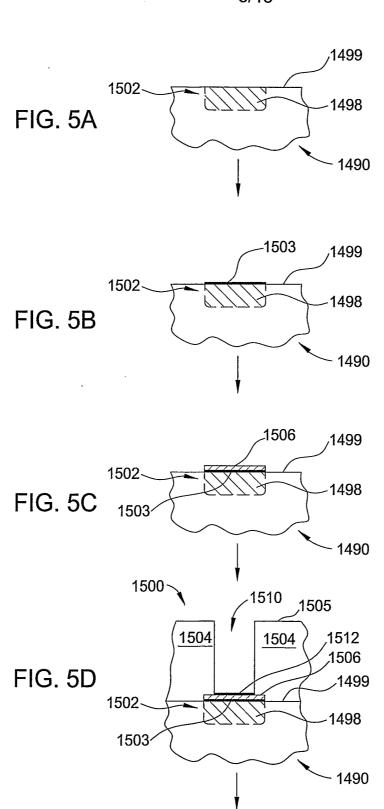

[0028] Figures 5A-5D illustrate schematic cross-sectional views of an contact level feature formed by a process described within an embodiment herein;

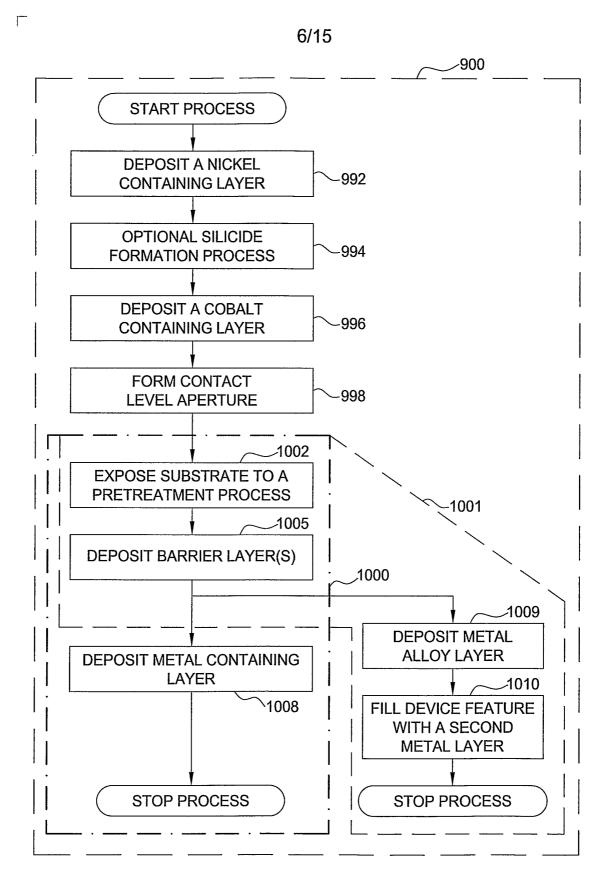

[0029] Figure 6 is a flow chart depicting a deposition process as described within an embodiment herein;

[0030] Figures 7A-7C illustrate schematic cross-sectional views of an integrated circuit formed by a process to cap a defect within a contact plug described within an embodiment herein;

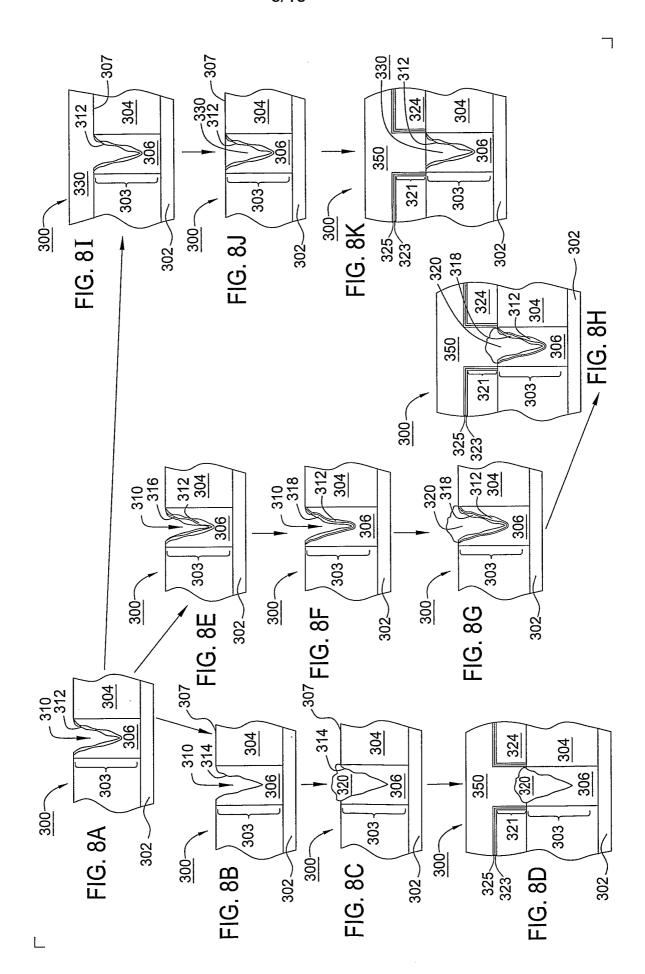

[0031] Figures 8A-8K illustrate schematic cross-sectional views of an integrated circuits formed by processes to fill defects within contact plugs described within embodiments herein;

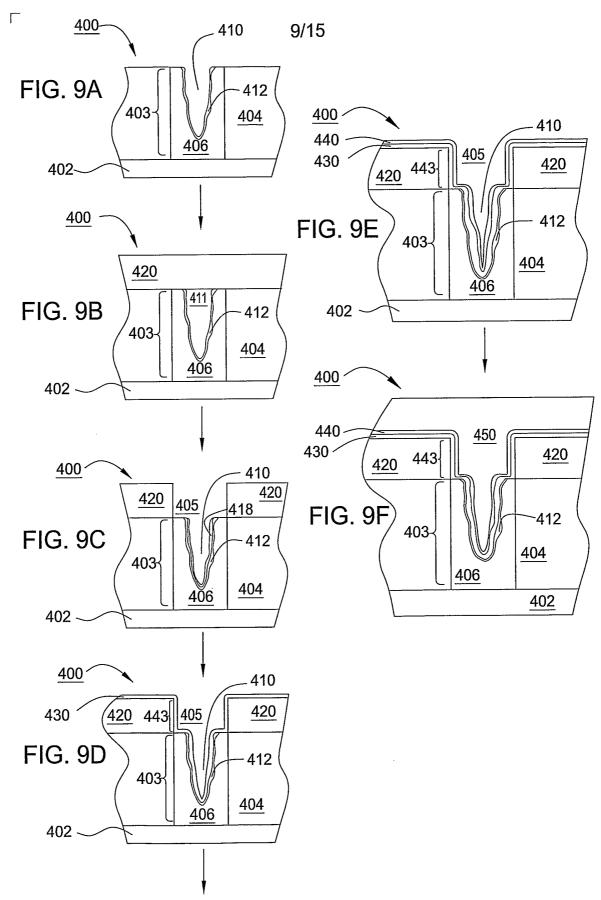

[0032] Figures 9A-9F illustrate schematic cross-sectional views of an integrated circuit formed by another process to fill a defect within a contact plug described within an embodiment herein;

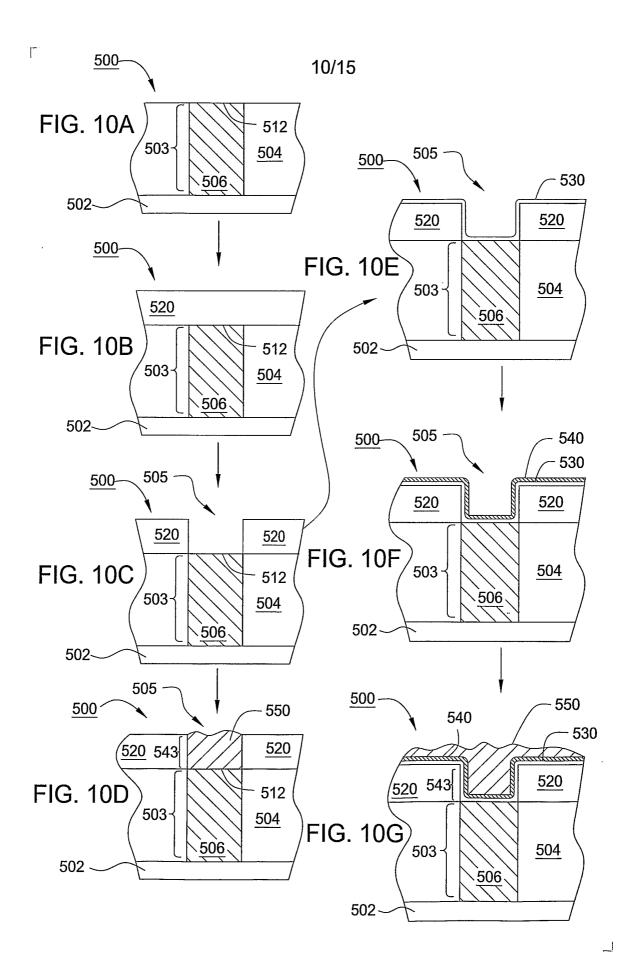

[0033] Figures 10A-10G illustrate schematic cross-sectional views of a method of forming an interconnect layer on a contact plug that is described within an embodiment herein;

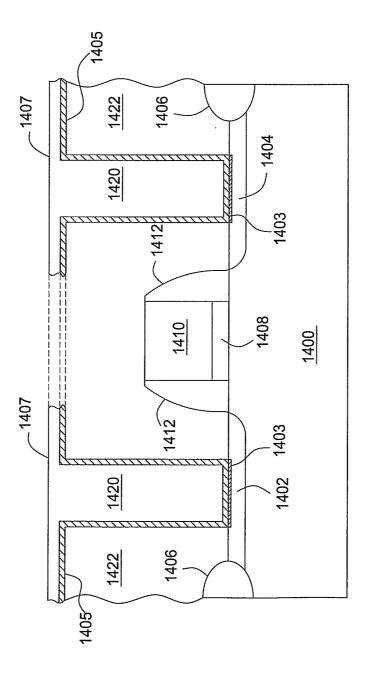

[0034] Figure 11 illustrate schematic cross-sectional view of a MOS type integrated circuit formed by a process described in the art;

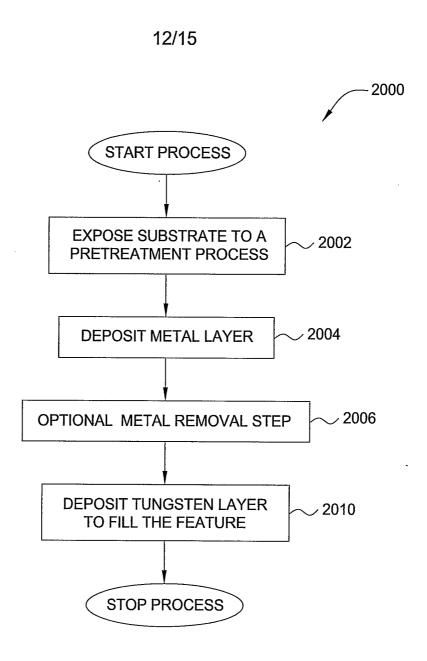

[0035] Figure 12 illustrates a flow chart depicting an electroless deposition process as described within an embodiment herein;

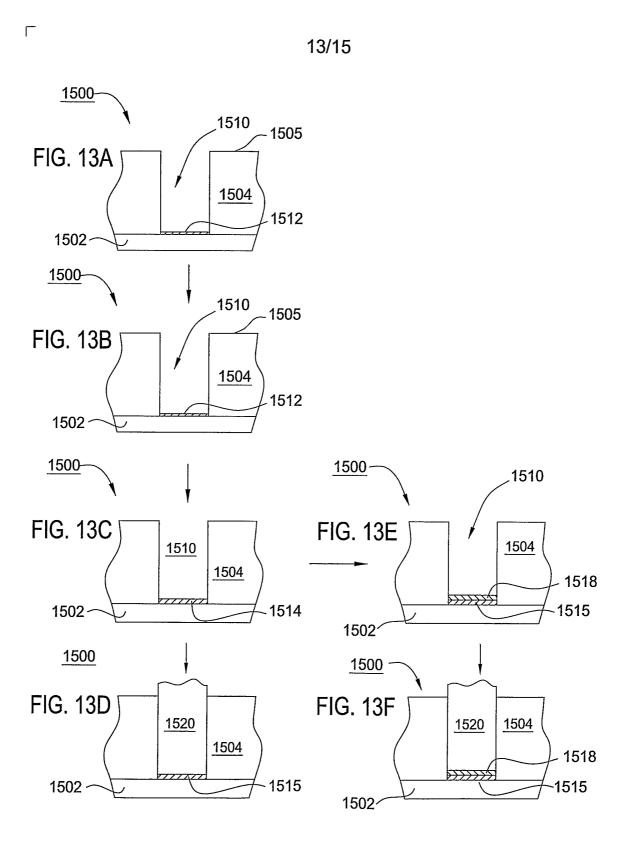

[0036] Figure 13A-G illustrate schematic cross-sectional views of an integrated circuit formed by a process to cap a defect within a contact plug described within an embodiment herein;

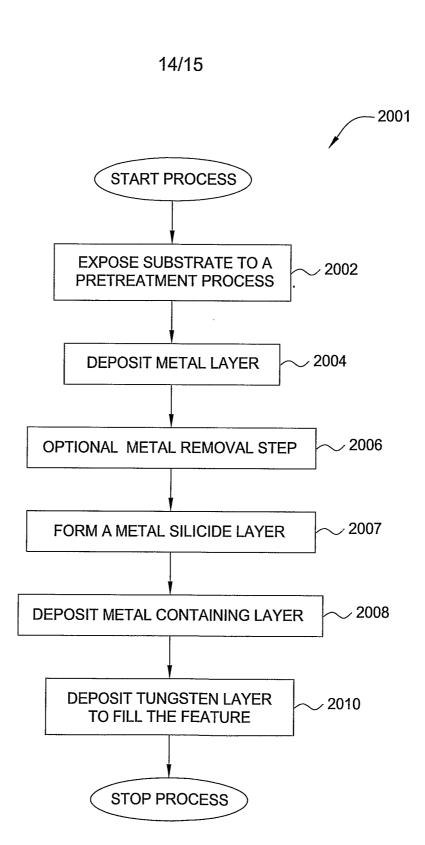

[0037] Figure 14 illustrates a flow chart depicting an electroless deposition process as described within an embodiment herein;

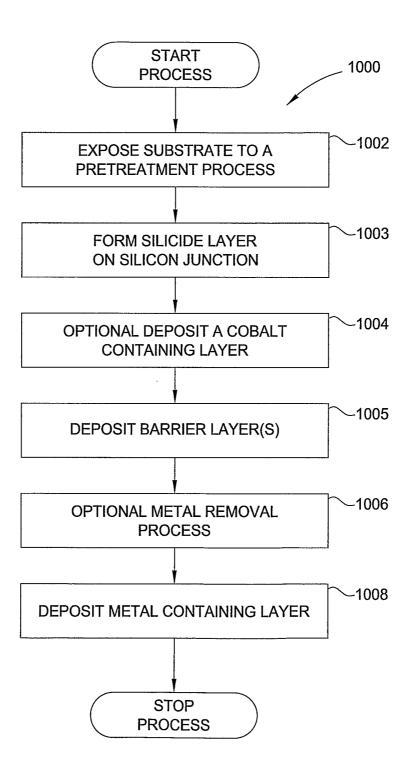

[0038] Figure 15 is a flow chart depicting a pretreatment process as described within an embodiment herein.

# DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENT

Embodiments of the invention generally provide methods of filling contact [0039] level features formed in a semiconductor device by depositing a barrier layer over the contact feature and then filing the layer using an PVD, CVD, ALD, electrochemical plating process (ECP) and/or electroless deposition processes. The term "barrier layer" as used herein is generally intended describe a single layer, or two or more layers, that act as an adhesion layer and a diffusion barrier for the subsequently deposited metal layer(s). In one embodiment, the barrier layer has a catalytically active surface that will allow the electroless deposition of a metal on the barrier layer. In one aspect, the electrolessly deposited metal is copper or a copper alloy. Copper alloys may be useful to improve the device speed and performance, help prevent electromigration or stress migration degradation during subsequent processing, improve the manufacturing device yield and device lifetime due to electromigration or stress migration limitations of copper or allow the deposited materials to diffuse to unwanted areas in the formed device. In one embodiment, a portion of the barrier layer is purposely allowed to react with traces of residual oxide at the silicon junction of the contact level feature to form a low resistance connection

(e.g., silicide formation). One embodiment includes a method of filling a contact level feature with a copper alloy by use of an electroless deposition process. In another embodiment, a copper alloy is used to from a thin conductive copper layer that is used to subsequently fill features with a copper containing material by use of an electrochemical plating process (ECP), PVD, CVD, and/or ALD deposition process.

# **Electroless Fill Contact Formation Process**

The first novel method, illustrated in Figure 3, is a series of method steps 1000 that are used to fill a contact level feature. Figure 2A illustrates a cross-sectional view of substrate 1500 having a contact level aperture 1510 formed into dielectric layer 1504. The dielectric layer 1504 contains an insulating material that includes silicon dioxide, silicon nitride, SOI, silicon oxynitride and/or carbon-doped silicon oxides, such as SiO<sub>x</sub>C<sub>y</sub>, for example, BLACK DIAMOND™ low-k dielectric, available from Applied Materials, Inc., located in Santa Clara, California. Contact level aperture 1510 may be formed in dielectric layer 1504 using conventional lithography and etching techniques to expose the silicon junction 1502, such as a MOS type source or drain interface. Silicon junction 1502 is generally a doped silicon region formed in a silicon substrate, such as a n+ or p+ doped silicon region.

[0041] An oxide surface 1512 is usually formed at the silicon junction 1502 during previous etching and ashing processes used to form contact level aperture 1510. Oxide surface 1512 may be a continuous layer or a discontinuous layer across the surface of silicon junction 1502 and include a surface terminated with oxygen, hydrogen, hydroxides, a metal or combinations thereof. In examples wherein silicon junction 1502 contains a single crystal or polycrystalline silicon substrate the oxide surface 1512 is usually a silicon oxide surface. Also, where the silicon junction 1502 contains a doped layer and/or metal silicide formed on the surface, the oxide surface 1512 will generally contain metal oxides and silicon oxides present at the surface.

[0042] The first step of the method steps 1000 includes an optional pretreatment process step 1002, to remove the oxide layer so subsequent processes can be preformed on the surface of the silicon junction 1502. In this process step the substrate 1500 is exposed to a pretreatment process to form a treated surface (not shown) on the silicon junction 1502, which is substantially free of oxide surface

1512. The various processes that may be used to perform the pretreatment process step 1002 on the surface of the silicon junction 1502 include, but are not limited to wet-clean processes and plasma cleaning processes. Examples of various wet-clean processes that may be used to remove oxide surface 1512 are further described in the US Provisional Applications Serial No. 60/709,564 [APPM 9916.L05], filed 8/19/2005, US Provisional Applications Serial No. 60/703,538 [APPM 9916.L03], filed 7/29/2005, and US Provisional Applications Serial No. 60/663,493 [APPM 9916L], filed 3/18/2005, which are all incorporated by reference herein in their entirety. A plasma cleaning processes may be performed using a vacuum preclean chamber, such as a Siconi Preclean chamber available from Applied Materials Inc. of Santa Clara, California.

The second step includes a silicide layer formation step 1003 that is used [0043] to form a metal layer 1513 over the silicon junction 1502. In general the metal layer 1513 contains a metal that forms a silicide (e.g., element 1513A in Figures 2C-2G) with the silicon material contained in the silicon junction 1502 during subsequent thermal processing steps. In general the deposited metal layer 1513 may contain one or more of the following elements nickel (Ni), titanium (Ti), tantalum (Ta), cobalt (Co), molybdenum (Mo) or tungsten (W). The metal layer 1513 may be selectively or non-selectively deposited using a conventional ALD or CVD deposition process. Also, the metal layer 1513 may be non-selectively deposited using a conventional PVD deposition process. Preferably, the metal layer 1513 is deposited using an electroless deposition process, such as the processes described in United States Provisional Patent Application Serial number 60/703,538, filed 7/29/2005 [APPM 9916L03] and United States Provisional Patent Application Serial number 60/731,624, filed 10/28/2005 [APPM 10659L], which are herein incorporated by reference. In one embodiment, the metal layer 1513 is a nickel layer containing layer that has been deposited using an electroless deposition process. In one aspect, the metal layer 1513 when deposited is between about 5 and about 100 angstroms (Å) thick. Preferably, the metal layer 1513 is from about 10 Å to about 50 Å thick, and more preferably, from about 10 Å to about 30 Å. In one aspect, to achieve a contact resistance of 45 ohms at 50 nm plug with 5:1 aspect ratio a metal layer 1513 having a resistivity less than about 35 microohm-cm, and preferably less than about 10 microohm-cm, and more preferably less than about 5 microohm-cm.

In one aspect of the method steps 1000 (not shown in Figures 2A-2G or [0044] Figure 3), the metal silicide layer 1513A is formed at the silicon junction 1502 by use of a thermal process, such as a conventional anneal or RTP process, prior to performing the subsequent method steps. Generally, the silicide formation process step is performed in a vacuum or inert environment to prevent the oxidation or damage to the surface of the metal silicide layer 1513A and contact level aperture 1510 surfaces. Typically, the metal silicide layer 1513A formed at the silicon junction 1502 is a nickel silicide, cobalt silicide, titanium silicide, molybdenum silicide, tungsten silicide, tantalum silicide, or other common metal silicides. In one aspect, where a nickel silicide layer is to be formed at the silicon junction 1502 the substrate may be heated to a temperature between about 300 °C and about 450 °C for a period of time that allows a silicide layer of a desired thickness and resistance to be formed. The silicide formation process step is used to reduce the contact resistance between the metal layers deposited in the contact level aperture 1510 and the silicon junction 1502.

In one embodiment of the method steps 1000 (not shown in Figure 3), an optional cleaning process is performed on the surface of the formed metal silicide layer 1513A, or metal layer 1513, using a very dilute solution of hydrofluoric acid (HF) (*e.g.*, 100:1 ratio of DI Water:HF) prior to depositing barrier layer 1521. The optional cleaning process step may be used to remove any surface oxides formed on the exposed surfaces of the metal silicide layer 1513A or metal layer 1513. The removal of these oxides can help reduce the contact resistance of the formed structure.

[0046] In one embodiment, a thin layer cobalt containing layer (step 1004 in Figure 3) may be deposited over the metal silicide layer 1513A to inhibit the diffusion of the metal layer component(s) into the subsequently deposited layers or other contact level aperture 1510 elements. In one aspect, step 1004 is completed before the silicide layer formation step 1003 and thus is deposited directly on the metal layer 1513. In general the cobalt containing layer (not shown) is a binary alloy or ternary alloy, such as cobalt boride (CoB), cobalt phosphide (CoP), cobalt tungsten phosphide (CoWP), cobalt tungsten boride (CoWB), cobalt molybdenum phosphide (CoMoP), cobalt molybdenum boride (CoMoB), cobalt rhenium boride (CoReB), cobalt rhenium phosphide (CoReP), derivatives thereof, or combinations thereof. In

one aspect, the cobalt containing layer (not shown) is between about 5 and about 100 angstroms (Å) thick. Preferably, the cobalt containing layer is from about 5 Å to about 50 Å thick, and more preferably, from about 10 Å to about 30 Å. Preferably, the cobalt containing layer is deposited using an electroless deposition process, such as the processes described in United States Patent Application serial number 11/040,962, filed 1/22/2005 [APPM 8926] and United States Patent Application serial number 10/967,644, filed 10/18/2004 [APPM 8660.02], which are herein incorporated by reference..

The third step includes a barrier layer deposition step 1005 that is used to form a barrier layer 1521 over the metal silicide layer 1513A. While the discussion below describes the deposition of the barrier layer 1521 over the metal silicide layer 1513A, this is not intended to be limiting as to processing sequence described herein since the thermal processes used to form the metal silicide layer 1513A may be performed after the barrier layer 1521 or other subsequent layers are formed. In general the barrier layer 1521 contains one or more layers of material that act as an adhesion layer and a diffusion barrier for the subsequently deposited metal layer 1525. In one aspect, the barrier layer 1521 is between about 5 and about 100 angstroms (Å) thick. Preferably, the barrier layer 1521 is from about 10 Å to about 50 Å thick, and more preferably, from about 10 Å to about 30 Å. In one embodiment, a portion of the barrier layer 1521 is selected so that it will react with traces of residual oxide at the silicon junction 1502 to further provide a low resistance connection to the metal silicide layer 1513A.

In one aspect, the exposed surface of the barrier layer 1521 may have a catalytically active surface for the subsequently deposited metal layers (*e.g.*, metal layer 1525) using an electroless deposition process. For example, in some embodiments, it may be desirable to form a barrier layer 1521 that has an exposed surface layer that contains a group VIII metal, such as ruthenium (Ru), cobalt (Co), nickel (Ni), rhodium (Rh), iridium (Ir), palladium (Pd) or platinum (Pt) to serve as a catalytically active initiation and adhesion layer for the subsequently deposited metal layer 1525 (*e.g.*, copper (Cu)).

[0049] The barrier layer 1521 may also contain one or more layers that contain titanium (Ti), titanium nitride (TiN), tantalum (Ta), tantalum nitride (TaN), tungsten (W), molybdenum (Mo), tungsten nitride (WN), tungsten carbon nitride (WCN),

molybdenum carbon nitride (MoCN), tantalum carbon nitride (TaCN), titanium silicon nitride (TiSiN), or any other combinations thereof. The barrier layer deposition step 1005 may be performed by use of conventional PVD, CVD, plasma enhanced CVD (PECVD), ALD, plasma enhanced ALD (PEALD). In one aspect, a non-selective deposition process is used, such as a PVD, non-selective CVD, non-selective plasma enhanced CVD, non-selective ALD, and/or non-selective plasma enhanced ALD process(es). Examples of an exemplary CVD and ALD type deposition processes and hardware configuration are further described in the commonly assigned United States Patent Application number 6,951,804, the commonly assigned United States Patent Publication number 20030108674 [APPM 6043], the commonly assigned United States Patent Publication number 20050106865 [APPM 6303.P3], and the commonly assigned United States Patent Application publication number 20030049931 [APPM 5350], which are all herein incorporated by reference.

In one aspect, the barrier layer 1521 is deposited in the barrier deposition [0050] step 1005 by use of a PVD deposition process that is used to deposit a layer that contains two or more elements, such as a ruthenium and tantalum alloy. Ruthenium and Tantalum alloys are useful, since it they have the combined benefits of blocking copper diffusion as effectively as conventional tantalum barrier layers and providing a suitable surface for direct electroless and/or electrochemical plating of a copper seed layer thereon. In general Ru-Ta alloys do not suffer from the same adhesion problems as found with conventional Ta and TaN barrier layers. Therefore, in one aspect of the invention, the barrier layer 1521 contains a Ru-Ta alloy that contains between about 70 atomic % and about 95 atomic % ruthenium and the balance tantalum. In another aspect, the barrier layer 1521 preferably contains a Ru-Ta alloy that contains between about 70 atomic % and about 90 atomic % ruthenium and the balance tantalum. In yet another aspect, the barrier layer 1521 more preferably contains a Ru-Ta alloy that contains between about 80 atomic % and about 90 atomic % ruthenium and the balance tantalum. In one aspect, it may be desirable to select a Ru-Ta alloy that does not contain regions of pure tantalum on the surface. In one aspect, a PVD type deposition process is used to deposit a barrier layer 1521 that contains the Ru-Ta alloy containing about 90 atomic % ruthenium and the balance tantalum (e.g., 0.9Ru:0.1Ta).

In one embodiment, a selective deposition process may be used, such as [0051] electroless, selective CVD, selective PECVD, selective ALD, and/or selective PEALD, to form a barrier layer 1521 that may only cover the exposed area(s) of the metal silicide layer 1513A. Also, one or more of the layers in the barrier layer 1521 may be selectively deposited by use of an electroless deposition process. The electroless deposition process may be used to form a layer that contains a binary alloy or ternary alloy, such as cobalt boride (CoB), cobalt phosphide (CoP), nickel boride (NiB), nickel phosphide (NiP), cobalt tungsten phosphide (CoWP), cobalt tungsten boride (CoWB), nickel tungsten phosphide (NiWP), nickel tungsten boride (NiWB), cobalt molybdenum phosphide (CoMoP), cobalt molybdenum boride (CoMoB), nickel molybdenum phosphide (NiMoB), nickel molybdenum phosphide (NiMoP), nickel rhenium phosphide (NiReP), nickel rhenium boride (NiReB), cobalt rhenium boride (CoReB), cobalt rhenium phosphide (CoReP), derivatives thereof, or combinations thereof. The film composition of the binary or ternary alloys can be preferably designed to have a resistivity in the range of about 1 to about 200 microohm-cm.

[0052] In one aspect, a nickel containing barrier layer 1521 is formed by performing two or more process steps which may include depositing a self-assembled-monolayer (SAM) material on to the surface of the substrate 1500 (e.g., covers field region 1505 and in the contact level aperture 1510) and then electrolessly depositing a nickel layer onto the deposited SAM layer. Examples of a prototypical SAM materials include, but are not limited to aminopropyltriethoxy silane (APTES) that may be deposited using a vapor phase deposition process. In one aspect, it may be desirable to perform a hydrogen and/or water containing plasma treatment process to the metal silicide layer 1513A, field region 1505 and contact level aperture 1510 prior to depositing the SAM layer to form a silanol (e.g., Si-OH) surface to promote the adhesion of the SAM layer. In one aspect, the hydrogen and/or water containing plasma treatment is used to perform the photoresist stripping process.

[0053] In another aspect, the barrier layer 1521 contains a multilayer stack of materials that are deposited on the field region 1505 and in the contact level aperture 1510. Examples of multilayer stacks that may be used to form a barrier layer 1521 that has desirable diffusion barrier and contact resistance properties

include, but are not limited to layers containing Ti/TiN/Ru, Ti/TiN/Co, Ti/TiN/Ni, Ti/Ru, Ta/Ru, TaN/Ru, Ni/Co, Ti/TiN/W/Ni, and Ti/TiN/W/Co. The nomenclature used herein to define a multilayer stack is intended to describe a barrier layer 1521 that contains discrete layers that may be arranged in a any desired order (e.g., Ni/Co = Ni on Co or Co on Ni) as long as the final exposed surface of the barrier layer 1521 is catalytically active to enable a subsequent electroless deposition process or can be readily rendered catalytically active by performing a activation process (e.g., palladium activation). For example, a Ti/TiN/Ru stack contains three layers, which are a titanium (Ti) containing layer, a titanium nitride (TiN) containing layer, and a ruthenium (Ru) containing layer (e.g., pure Ru, 0.9Ru:0.1Ta, etc.), that may be arranged so that the Ti containing layer is deposited on the metal silicide layer 1513A and then the TiN containing layer is deposited on the Ti layer and then the Ru containing layer is deposited over both layers. The multilayer stacks that may be used to form a barrier layer 1521 may be deposited by use of one or more conventional deposition techniques, such as PVD, CVD, PECVD, ALD, PEALD, ECP, or electroless deposition processes.

[0054] In yet another aspect, the barrier layer 1521 may contain a multilayer stack of metals, such as, Ti, TiN, Ti/TiN/W, Ti/TiN, Ti/W, Ta/TaN/W, Ta/W, Ni/W, and Co/W that have an additional catalytic layer deposited on the top surface so that an electroless layer can be deposited thereon. A typical catalytic layer that is deposited on these multilayer stacks may be a ruthenium (Ru), cobalt (Co), nickel (Ni), rhodium (Rh), iridium (Ir), palladium (Pd) or platinum (Pt) containing layer. The multilayer stacks that may be used to form a barrier layer 1521 may be deposited by use of one or more conventional deposition techniques, such as PVD, CVD, PECVD, ALD, PEALD, ECP, or electroless deposition processes.

[0055] In one embodiment, it may be desirable to deposit a single layer type barrier layer 1521 that contains a material, such as titanium, palladium, platinum or ruthenium prior to electrolessly depositing the subsequent metal layer(s) (*e.g.*, metal layer 1525). In one example, the titanium (Ti) is deposited using a two step process that contains a preclean process step (*e.g.*, performed in a Siconi, Preclean II or Preclean XT chambers available from Applied Materials, Inc. of Santa Clara, California) and then PVD titanium deposition step using a Endura™ RTM PVD chamber, which are both available from Applied Materials, Inc. of Santa Clara,

California. In another example, a ruthenium (Ru) and tantalum (Ta) alloy layer (*e.g.*, 0.9Ru:0.1Ta) is deposited using a two step process that contains a preclean process step (*e.g.*, Siconi) and then PVD ruthenium and tantalum alloy deposition step using a Endura<sup>TM</sup> RTM PVD chamber. In another example, a ruthenium (Ru) layer is deposited using a CVD, ALD or PEALD processes. In another example, the ruthenium layer is deposited by use of an electroless displacement plating process using a ruthenium chloride solution. In another example, a palladium (Pd) layer is deposited using either an ALD, PEALD, CVD, or PECVD process or by use of an electroless displacement plating process. The thickness and the choice of the type of material that may be used depends on the types subsequent processes performed on the formed device (*e.g.*, thermal cycling) and the barrier properties of the material or the stack formed using the material.

[0056] In one embodiment, an optional metal removal step 1006 may be added to the method steps 1000 to remove any deposited barrier layer 1521 from the field region 1505 (Figures 2A-B) by use of a wet clean process, CMP process, electrochemical process or other comparable material removal processes. A CMP process may be performed using a Reflexion<sup>TM</sup> CMP system available from Applied Materials Inc. of Santa Clara, California.

[0057] In the deposit a metal alloy layer step 1008, a metal layer 1525 is deposited so that it fills the contact level aperture 1510. In one aspect, this process is performed using an electroless deposition process. In general the contact level aperture 1510 can be filled with a metal, such as copper (Cu), nickel (Ni), cobalt (Co), ruthenium (Ru), tungsten (W) or combinations thereof. In one embodiment, the metal layer 1525 is formed by use of a metal layer electroless deposition solution (discussed below) that contains only a copper ion source and a reducing agent that allows the deposition of copper.

In another embodiment, metal layer 1525 is formed by use of metal layer electroless deposition solution (discussed below) that contains two or more metal ion sources and a reducing agent that allows the co-deposition of two or more metals. In one aspect, one of the metals ions is a copper ion and the other metal ion(s) are a metal selected from a group consisting of aluminum (AI), indium (In), molybdenum (Mo), tungsten (W), manganese (Mn), cobalt (Co), tin (Sn), nickel (Ni), magnesium (Mg), rhenium (Rh), beryllium (Be), phosphorus (P), boron (B), gallium

(Ga), or ruthenium (Ru). In one aspect, a metal alloying element that is more electropositive than copper may be beneficial to improve the oxidation resistance and corrosion resistance of the deposited film. The addition of the alloying element will also generally improve the stability of the formed device by reducing the ability of some of the elements in deposited layer to rapidly diffuse into silicon or the silicon oxides. Examples of various chemistries that may be used to form the metal layer 1525 are further described below. In this configuration the electrical resistance of the electrical connection formed using method steps 1000 will be reduced, since a significant part, or volume, of the contact level aperture 1510 will contain predominantly copper, or a copper containing alloy, that has a resistivity lower than a conventional tungsten plug. The use of a metal layer 1525 is advantageous since by the selection of a desirable elements, such as a copper aluminum alloy, copper indium alloy, copper manganese alloy, a copper tungsten alloy, or a copper molybdenum alloy, to name just a few, the resistance of the formed connection will be reduced versus a conventional tungsten plug, and the metal alloy will have better electromigration performance than pure copper and/or diffusion resistance. It should be noted that the term "alloy" as used herein is not intended to be limited to the case of where one element forms a bond or compound with another element, and is intended to generally describe a film that contains a percentage of two or more elements. In one example, one of the elements may be positioned in an interstitial site or be deposited on the grain boundaries of a formed crystalline or amorphous structure containing a second element (e.g., Cu), rather than form a compound containing two or more elements. Further, in one aspect of the invention, due to the addition of the alloying element to copper, the copper atoms in the formed copper containing layer become less mobile thus reducing, or possibly eliminating the need for the barrier layer 1521. Thus, in some cases by adding an alloying element to a metal, such as copper will tend prevent or inhibit the metal from diffusing into unwanted areas of the formed device. In one aspect, it may be desirable to have the second metal ion source (i.e., metal ion other than copper ions) in the metal layer electroless deposition solution because the second ion is better suited to form an adhesion promoting interface between the barrier layer 1521 and the growing alloy layer (i.e., element 1525 and 1526).

[0059] In another embodiment of the deposit a metal alloy layer step 1008, the metal layer 1525 is formed using a metal layer electroless deposition solution that contains one or more metal ion sources and a reducing agent that allows the codeposition of two or more metals. In one aspect, one of the metals ions is a cobalt or nickel based alloy can be deposited on top of these materials by electroless process. For example, the cobalt or nickel based alloys may be a binary alloy or ternary alloy, such as cobalt boride (CoB), cobalt phosphide (CoP), nickel boride (NiB), nickel phosphide (NiP), cobalt tungsten phosphide (CoWP), cobalt tungsten boride (CoWB), nickel tungsten phosphide (NiWP), nickel tungsten boride (NiWB), cobalt molybdenum phosphide (CoMoP), cobalt molybdenum boride (CoMoB), nickel molybdenum phosphide (NiMoP), nickel molybdenum boride (NiMoB), nickel rhenium phosphide (NiReP), nickel rhenium boride (NiReB), cobalt rhenium boride (CoReB), cobalt rhenium phosphide (CoReP), derivatives thereof, or combinations thereof. The selection of materials used to form the metal layer 1525 is influenced by the resistivity of the films deposited. In one aspect, all the deposited films are pure metals and thus their resistivity is less than about 10 microohms-cm, and more preferably less than about 5 microohms-cm. In another aspect, a stack of discrete metal layers having different thickness may be used to form a device that has good diffusion barrier properties as well as lower overall contact resistance of the device.

## **Second Contact Fill Formation Process**

[0060] Another novel method of filling a contact level feature is illustrated in Figures 2A-2D, 2F-2G and 4. Figure 4 illustrates is a series of method steps 1001 that are used to fill a contact level feature. The steps 1002-1006 in the method steps 1001 are generally the same as the method steps 1000 and thus are not recited below. The method steps 1001 differ from the method steps 1000, described above, due to the variation of only depositing a thin metal layer 1526 (step 1009 in Figure 4) and then filling the contact level aperture 1510 with a second metal layer 1527 (step 1010 in Figure 4).

[0061] In one embodiment of the method steps 1001, after performing steps 1002-1006, the step 1009 is performed to deposit a thin metal layer 1526 on the field region 1505 and in the contact level aperture 1510. Step 1009 is similar to step 1008 described above in conjunction with Figure 3, except that the thin metal layer 1526 is formed rather than filling the contact level aperture 1510. Therefore, as

noted above the metal layer 1526 will contain one or more metal elements that are deposited using an electroless deposition process that utilizes the metal layer electroless deposition solution (discussed below). The use of an electroless deposition process may be especially useful due to the deposition of a conformal coating having a uniform thickness formed over the contact level aperture 1510. In one aspect, electrolessly deposited films are preferred, since they generally do not contain the amount of carbon that CVD and ALD deposited films contain from the incorporation of the CVD or ALD precursor materials in the deposited film. The incorporation of carbon in the deposited film will affect the resistivity and adhesion of the deposited layer to prior or subsequently deposited layers. Electrolessly deposited films may also be favored over PVD deposited films, because a thin or discontinuous PVD deposited layer will be formed in typical ≤45nm type features due to the fact that it is a line-of-sight type deposition process. deposition processes are also useful to form metal layers that have two or more metal components contained therein. In one aspect, it may be desirable to varying composition of the electrolessly deposited layer that contains two or more metal components. An exemplary process and hardware that may be used to form a metal layer having a varying composition is described in the commonly assigned United States Patent Application Serial No. 11/040,962 [APPM 8926], filed 1/22/2005, which is incorporated by reference herein in its entirety.

[0062] In one aspect, the thin metal layer 1526 is thick enough to reduce the terminal effect of the subsequently deposited second metal layer 1527 by use of an electrochemical plating process (ECP). In another aspect, the thin metal layer 1526 is thick enough to reduce or inhibit the diffusion of the material in the subsequently deposited second metal layer 1527 into the silicon junction 1520, or adjacent devices elements, and prevent diffusion of silicon in the silicon junction 1520 from diffusing into the second metal layer 1527. In one aspect, the thin metal layer 1526 is deposited to a thickness between about 10 Å and about 100 Å. In general, ECP deposition processes have advantages over CVD, ALD and PVD type processes, since the selection of the electrolyte components (e.g., additives, acid concentration) and various process recipe parameters (e.g., current density) apertures of varying sizes can be filled without forming voids or gaps in the deposited layer or incorporating carbon in the deposited film. Examples of exemplary electrochemical

deposition processes and hardware configuration are further described in the commonly assigned United States Patent Application number 6,596,151, and the commonly assigned copending United States Patent Application serial number 10/854,006, filed 5/25/2004 [APPM 7669.P4] and United States Patent Application serial number 10/616,284, filed 7/28/2003 [APPM 7669], which are all herein incorporated by reference.

In step 1010, a second metal layer 1527 is deposited on the thin metal layer 1526 to fill the contact level aperture 1510. In one embodiment, the second metal layer 1527 may be a metal alloy that contains one or more elements, such as copper (Cu), aluminum (Al), indium (In), molybdenum (Mo), tungsten (W), manganese (Mn), cobalt (Co), rhenium (Rh), ruthenium (Ru), or combinations thereof. In another embodiment, the second metal layer 1527 is a pure copper (Cu) layer. The second metal layer 1527 may be deposited by any conventional deposition technique, such as PVD, CVD, PECVD, ALD, PEALD, ECP, or electroless deposition processes. In general, the material from which the second metal layer 1527 is formed is selected so that it has a high electrical conductivity to reduce the overall resistance of the circuit formed using the contact level aperture 1510.

[0064] The formed device feature using the method steps 1001 may be advantageous since it combines the use of a thin metal layer 1526 and high conductivity second metal layer 1527 to form a device feature that has a lower resistivity than conventional tungsten deposited materials, while also inhibiting the diffusion of the second metal layer 1527 to unwanted regions of the device due to the barrier-like properties of the thin metal layer 1526.

# **Third Contact Fill Formation Process**

[0065] Another novel method of filling a contact level feature is illustrated in Figures 5A-5F and 6. Figure 6 illustrates is a series of method steps 900 that are used to fill a contact level feature (*e.g.*, contact level aperture 1510) using the methods described in methods steps 1000 or 1001, plus some additional preprocessing steps 992-998. The steps 1002, 1005, 1008, 1009 and 1010 in the method step 900 are generally the same as the steps contained in the method steps 1000 or 1001 and thus are not recited below. One will note that the silicide layer

formation step 1003, the optional deposit a cobalt containing layer step 1004, and the optional metal removal step 1006 found in method steps 1000 and 1001 have been removed, since they are performed at different stages of the process sequence or they are may not be required. Figure 5A illustrates a silicon junction 1502 formed on a substrate 1490, wherein the silicon junction 1502 generally contains a doped silicon region 1498 that has an exposed surface 1499 on which the subsequent process steps will be performed.

Referring to Figures 5B and 6, in the deposit a metal containing layer step 992, or the first step of the method steps 900, a metal containing layer 1503 is deposited on the doped silicon region 1498 of the substrate 1490. In one embodiment, the metal containing layer 1503 is deposited using an electroless deposition process. For example, an electroless deposition process may be used to deposit a nickel containing layer on the doped silicon region 1498. An exemplary electroless nickel deposition process is further described in the commonly assigned US Provisional Patent Application Serial No. 60/703,633 [9916.L04], filed 7/29/2005, the commonly assigned US Provisional Patent Application Serial No. 60/703,538 [9916.L03], filed 7/29/2005, the commonly assigned US Provisional Applications Serial No. 60/709,564 [9916.L05], filed 8/19/2005, and the commonly assigned US Provisional Patent Application Serial No. 60/663,493 [9916L], filed 3/18/2005, which are all incorporated by reference herein in their entirety.

[0067] Referring to Figures 5D and 6, in the form the contact level aperture step 998 a contact level aperture 1510 is formed over the metal containing layer 1503 and the optional cobalt containing layer 1506 using conventional dielectric deposition, lithography and etching techniques. After step 998 is completed then the barrier deposition step 1002 can performed following the methods described in Figures 3 or 4.

## **Example - Nickel Electroless Chemistry**

[0068] In one example, an electroless solution contains: nickel sulfate with a concentration of about 60 mM; dimethylaminoborane (DMAB) in a concentration of about 14 mM; citric acid in a concentration of about 60 mM; diethanolamine (DEA) in a concentration of between about 33 mM and about 115 mM; glycine in a concentration between about 5 mM to about 50 mM; boric acid in a concentration

between about 5 mM and about 10 mM; lactic acid in a concentration of about 120 mM; tetramethyl ammonium hydroxide (TMAH) in a concentration to adjust the electroless solution to a have pH value in a range from about 8 to about 11, preferably from about 9 to about 10, and more preferably from about 9.2 to about 9.6, such as about 9.4. The electroless deposition process may be conducted at a temperature in a range from about 35°C to about 120°C, preferably from about 80°C to about 85°C. The water may be degassed, preheated and/or deionized water. Degassing the water reduces the oxygen concentration of the subsequently formed electroless solution. An electroless solution with a low oxygen concentration (*e.g.*, less than about 100 ppm) may be used during the deposition process. Preheated water allows forming the electroless solution at a predetermined temperature just below the temperature used to initiate the deposition process, thereby shortening the process time.

Referring to Figure 6, next an optional silicide formation process step 994, is used to reduce the contact resistance between the metal containing layer 1503 deposited on the surface 1499 of the doped silicon region 1498 by causing the deposited metal containing layer 1503 to form a nickel silicide (Ni<sub>x</sub>Si<sub>y</sub>). The metal containing layer 1503 formed in step 992 should have a sufficient thickness to form a good electrical contact (*e.g.*, ohmic contact) between the subsequently deposited layers (*e.g.*, barrier layer 1521) and the doped silicon region 1498 in the silicon junction 1502. Typical silicide formation processes include heating a substrate 1490 to a temperature that will cause the nickel in the metal containing layer 1503 to form a nickel silicide. Generally, the silicide formation process step 994 is performed in a vacuum or inert environment to prevent the oxidation of the surface of the metal containing layer 1503.

[0070] Referring to Figures 5C and 6, in the optional deposit a cobalt containing layer step 996, a cobalt containing layer 1506 is deposited on the metal containing layer 1503. In one embodiment, step 996 is used to form a cobalt alloy layer, such as CoB, CoP, CoWP, CoWB, CoMoP, CoMoB, CoReB, or CoReP using electroless deposition techniques further described in the copending US Provisional Patent Application Serial No. 60/703,538 [APPM 9916.L03], filed 7/29/2005, the copending US Patent Application Serial No. 11/040,962 [APPM 8926], filed 1/22/2005, the copending US Patent Application Serial No. 10/967,644 [APPM 8660], filed

10/15/04, and the copending US Patent Application Serial No. 10/967,919 [APPM 8660.02], filed 10/18/2004, which are all incorporated by reference herein in their entirety. The addition of the cobalt containing layer 1506 layer over the metal containing layer 1503 will help to isolate the nickel silicide layer formed during step 994 from being attacked during the subsequent deposition dielectric etch step(s) (*e.g.*, step 998).

# **Examples - Cobalt Electroless Chemistries**

In one aspect, an electroless solution for depositing cobalt boride contains: cobalt ions (Co<sup>2+</sup>) with a concentration in a range from about 1 mM to about 100 mM, preferably from about 5 mM to about 50 mM, and more preferably from about 10 mM to about 20 mM, such as about 15 mM; DMAB with a concentration in a range from about 1 mM to about 200 mM, preferably from about 10 mM to about 100 mM, and more preferably from about 30 mM to about 50 mM, such as about 40 mM; citric acid or citrate salt with a citrate concentration in a range from about 5 mM to about 500 mM, preferably from about 30 mM to about 300 mM, and more preferably from about 50 mM to about 150 mM, such as about 100 mM; and an optional pH adjusting agent (e.g., TMAH) with a concentration to adjust the electroless solution to a have pH value in a range from about 8 to about 11, preferably from about 8 to about 10, and more preferably from about 8.5 to about 9.5, such as about 8.9. The electroless deposition process to deposit cobalt boride may be conducted at a temperature within a range from about 35°C to about 100°C, preferably from about 60°C to about 80°C, and more preferably from about 65°C to about 75°C, such as about 70°C.

[0072] In one aspect, an electroless solution for depositing metallic cobalt contains: cobalt ions (Co<sup>2+</sup>) with a concentration in a range from about 1 mM to about 100 mM, preferably from about 5 mM to about 50 mM, and more preferably from about 10 mM to about 20 mM, such as about 15 mM; hydrazine hydrate with a concentration in a range from about 100 mM to about 2 M, preferably from about 200 mM to about 1 M, and more preferably from about 300 mM to about 700 mM, such as about 500 mM; citric acid or citrate salt with a citrate concentration in a range from about 5 mM to about 200 mM, preferably from about 10 mM to about 100 mM, and more preferably from about 30 mM to about 70 mM, such as about 50 mM; and an optional pH adjusting agent (*e.g.*, TMAH) with a concentration to adjust the

electroless solution to a have pH value in a range from about 10 to about 14, preferably from about 11.5 to about 13, and more preferably from about 12.2 to about 12.8, such as about 12.5. In one example, a pH value is about 11.5 or higher, preferably, about 12.0 or higher, and more preferably, about 12.5 or higher. The electroless deposition process to deposit metallic cobalt may be conducted at a temperature within a range from about 35°C to about 100°C, preferably from about 60°C to about 90°C, and more preferably from about 70°C to about 80°C, such as about 75°C.

[0073] The "water" component used in any of the above examples may be degassed, preheated and/or deionized water. Degassing the water reduces the oxygen concentration of the subsequently formed electroless solution. An electroless solution with a low oxygen concentration (e.g., less than about 100 ppm) may be used during the deposition process. Preheated water allows forming the electroless solution at a predetermined temperature just below the temperature used to initiate the deposition process, thereby shortening the process time.

# Metal Layer Electroless Deposition Solution(s)

[0074] In one aspect, the metal layer electroless deposition solution, which is used to form the metal layer 1525 or thin metal layer 1526 generally contains two metal ion sources and reducing agent that is used to form a high conductivity metal alloy layer. In one embodiment, one of the metal ion sources is copper ion that is added to the metal layer deposition solution.

In one embodiment, the metal layer electroless deposition solution is an aqueous solution that may contain a copper source, a second metal ion source, a reductant, a complexing agent, and a pH adjusting agent. The copper ion source within the metal layer electroless deposition solution may have a concentration in a range from about 5 mM to about 100 mM, preferably from about 25 mM to about 75 mM. Copper sources provide copper ions (*e.g.*, Cu<sup>1+</sup> or Cu<sup>2+</sup>) dissolved within the electroless solution to be reduced out as the deposited copper-containing material. Useful copper sources include copper sulfate, copper chloride, copper acetate, copper phosphate, copper pyrophosphate, copper fluoroborate, copper formate, derivatives thereof, hydrates thereof or combinations thereof.

In one embodiment, the metal layer electroless deposition solution [0076] contains a copper ion source and a second ion source that is an aluminum ion source, to form a metal layer that contains predominantly copper and small amounts of aluminum. Sources of aluminum that can be added to the metal layer electroless deposition solution may be aluminum ammonium sulfate (AINH<sub>4</sub>(SO<sub>4</sub>)<sub>2</sub>•12H<sub>2</sub>O),  $(AIK(SO_4)_2 \cdot 12H_2O),$ aluminum sulfate potassium alum dodecahydrate hexadecahydrate (Al<sub>2</sub>(SO<sub>4</sub>)<sub>3</sub>•16H<sub>2</sub>O), derivatives thereof, or combinations thereof. In one embodiment, the metal layer electroless deposition solution contains about 7 grams/liter of a copper sulfate (CuSO<sub>4</sub>) and between about 0.5 grams/liter and about 6 grams/liter of aluminum ammonium sulfate. In another embodiment, the metal layer electroless deposition solution contains a copper ion source and a second ion source that is an indium ion source, to form a metal layer that contains predominantly copper and small amounts of indium. Typical sources of indium that can be added to the metal layer electroless deposition solution may be indium(III) sulfate hydrate (In<sub>2</sub>(SO<sub>4</sub>)<sub>3</sub>•xH<sub>2</sub>O) and Indium(III) nitrate hydrate (In(NO<sub>3</sub>)<sub>3</sub>•xH<sub>2</sub>O), derivatives thereof, or combinations thereof. In yet another embodiment, the metal layer electroless deposition solution contains a copper ion source and a second ion source that is a tungsten ion source, to form a metal layer that contains predominantly copper and small amounts of tungsten. The tungsten source may include various tungstate salts, such as ammonium tungstate ((NH<sub>4</sub>)<sub>2</sub>WO<sub>4</sub>), or other WO<sub>4</sub><sup>2-</sup> sources, derivatives thereof and/or combinations thereof. In yet another embodiment, the metal layer electroless deposition solution contains a copper ion source and a second ion source that is a molybdenum ion source, to form a metal layer that contains predominantly copper and small amounts of molybdenum. A typical molybdenum source is molybdenum sulfate. In yet another embodiment, the metal layer electroless deposition solution contains a copper ion source and a second ion source that is a magnesium ion source, to form a metal layer that contains predominantly copper and small amounts of magnesium. The magnesium sources may include magnesium sulfate, magnesium acetate tetrahydrate ((CH<sub>3</sub>COO)<sub>2</sub>Mg•4H<sub>2</sub>O), manganous sulfate, manganous acetate, manganous trifluoroacetate or other Mg<sup>2+</sup> sources, derivatives thereof, or combinations thereof. In yet another embodiment, the metal layer electroless deposition solution contains a copper ion source and a second ion source that is a beryllium ion source, to form a

metal layer that contains predominantly copper and small amounts of beryllium. The beryllium sources may include beryllium sulfate or other Be2+ sources, derivatives thereof, or combinations thereof. In yet another embodiment, the metal layer electroless deposition solution contains a copper ion source and a second ion source that is a titanium ion source, to form a metal layer that contains predominantly copper and small amounts of titanium. The titanium sources generally include ion sources that contain Ti<sup>3+</sup> and Ti<sup>2+</sup> complexes. In yet another embodiment, the metal layer electroless deposition solution contains a copper ion source and a second ion source that is a gallium ion source, to form a metal layer that contains predominantly copper and small amounts of gallium. The gallium sources may include gallium sulfate or other Ga1+, Ga2+, or Ga+3 sources. In yet another embodiment, the metal layer electroless deposition solution contains a copper ion source and a second ion source that is a boron ion source, to form a metal layer that contains predominantly copper and small amounts of boron. The tetramethylammonium boron sources may include dimethylaminoborane (DMAB). In yet another embodiment, the metal layer electroless deposition solution contains a copper ion source and a second ion source that is a phosphorous ion source, to form a metal layer that contains predominantly copper and small amounts of phosphorus. The phosphorus sources may include a hypophosphite salt such as tetramethylamonium hypophosphite or ammonium hypophosphite. In yet another embodiment, the metal layer electroless deposition solution contains a copper ion source and a second ion source that is a tin ion source, to form a metal layer that contains predominantly copper and small amounts of tin. The tin sources may include tin sulfate (SnSO<sub>4</sub>) or other Sn<sup>2+</sup> or Sn<sup>4+</sup>sources.

[0077] The reducing agent, or reductant, within the metal layer electroless deposition solution may have a concentration in a range from about 10 mM to about 2 M, preferably from about 20 mM to about 500 mM. Reductants provide electrons to induce chemical reduction of the metal ions that form and deposit the metal alloy, which in one embodiment is a copper-containing alloy material. Reductants may include organic reductants (*e.g.*, formaldehyde or glyoxylic acid), hydrazine, organic hydrazines (*e.g.*, methyl hydrazine), hypophosphite sources (*e.g.*, hypophosphorous acid (H<sub>3</sub>PO<sub>2</sub>), ammonium hypophosphite ((NH<sub>4</sub>)<sub>4-x</sub>H<sub>x</sub>PO<sub>2</sub>) and salts thereof),

borane sources (*e.g.*, dimethylamine borane complex ((CH<sub>3</sub>)<sub>2</sub>NH•BH<sub>3</sub>), DMAB), trimethylamine borane complex ((CH<sub>3</sub>)<sub>3</sub>N•BH<sub>3</sub>), TMAB), tert-butylamine borane complex (<sup>†</sup>BuNH<sub>2</sub>•BH<sub>3</sub>), tetrahydrofuran borane complex (THF•BH<sub>3</sub>), pyridine borane complex (C<sub>5</sub>H<sub>5</sub>N•BH<sub>3</sub>), ammonia borane complex (NH<sub>3</sub>•BH<sub>3</sub>), borane (BH<sub>3</sub>), diborane (B<sub>2</sub>H<sub>6</sub>), tetraethylammonium borohydride ((C<sub>2</sub>H<sub>5</sub>)<sub>4</sub>N(BH<sub>4</sub>)), derivatives thereof, complexes thereof or combinations thereof. In one embodiment, the metal layer electroless deposition solution contains glyoxylic acid in a range between about 5g/L and about 30g/L. In another embodiment, the formulation may also contain formate ion, generated as by the neutralization of formic acid or simply by the use of cupric formate at the copper precursor.

[0078] In one embodiment, it is desirable to form an electroless plating solution that is optimized to perform a single wafer puddle plating process. Single use electroless puddle plating processes have advantages over re-circulating electroless deposition processes, since the deposition rate can be made more aggressive (i.e., higher deposition rate) without the issue of particle growth in the electroless plating solution or wafer-to-wafer electrolyte solution variation due to bath depletion. To meet the current cost-of-ownership (CoO) requirements, much higher deposition rate are required when performing electroless deposition fill processes. One such chemistry that can be used to obtain high deposition rates is a formulation such as, the novel copper formulation described below.

Polymeric additives are generally added to the metal layer electroless [0079] deposition solution to suppress the metal deposition on the field region (e.g., item 1505 Figure 2C) by initially adsorbing onto underlying catalytic surfaces (e.g., barrier layer 1521) and therefore suppressing the rate of deposition. An exemplary polymeric additive, due to its size (e.g., molecular weight), will generally have a limited ability to diffuse into and thus inhibit the growth of the deposited film in the recess of the contact level aperture 1510, but will be able to suppress the growth of the deposited film on the field region. The polymeric additives may have a concentration in a range from about 0.5 parts-per-million (ppm) to 500 ppm. In one aspect, the polymeric additives generally include poly(4-ammonium styrenesulfonic acid), poly(acrylic acid-co-maleic acid), 4-vinylphenol-co-hydroxyethyl methacrylate, Poly(acrylic acid-co-acrylamide) potassium salt, Poly[2,6-bis(hydroxymethyl)-4methylphenol-co-4-hydroxybenzoic acid], Poly(acrylamide-co-

diallyldimethylammonium chloride), Poly(vinylpyridine), Poly(2-acrylamido-2-methyl-1-propanesulfonic acid), Poly(anilinesulfonic acid), Poly(4-vinylphenol), derivatives thereof, and/or combinations thereof.

[0080] In one embodiment, additives such as polyethylene glycol (PEG), polypropylene glycol (PPG), polypropylene-polypropylene copolymer (POCP), benzotriazole (BTA), dipyridyl, dimethyl dipyridyl, derivatives thereof or combinations thereof are added to metal layer electroless deposition solution. The additives, or "suppressors," can be added to the electroless deposition solution in a concentration in a range between about 20 ppb and about 600 ppm. In another aspect, a PEG type additive is added in a concentration range of about 0.05 to about 1 g/l.

In one aspect, one or more of the following chelators or complexing [0081] agents, may also be added to the metal layer electroless deposition solution which include: amino acids, carboxylic acids, dicarboxylic acids, polycarboxylic acids, amino acids, amines, diamines, polyamines, alkylamines, alkanolamines and alkoxyamines. The additional complexing agents may have a concentration in a range from about 10 mM to about 2 M, preferably from about 20 mM to about 300 mM. Complexing agents may include, but are not limited to citric acid, citrates, glycine. acid, malonic acid. maleic acid. lactic acid, glycolic ethylenediaminetetraacetic acid (EDTA), ethylenediamine (EDA), triethylene tetramine (TETA), diaminoethane, monoethanolamine, diethanolamine (DEA), triethanolamine (TEA), hydroxylamine hydrochloride, and ammonia, derivatives thereof, salts thereof or combinations thereof.

[0082] In one embodiment, the metal layer electroless deposition solution contains EDTA in a ratio relative to copper that is less than about 6:1 (*e.g.*, EDTA concentration to Cu concentration), and more preferably at a ratio of about 2:1. In one embodiment, the EDTA concentration in the metal layer electroless deposition solution is in a range between about 5 g/L and about 30 g/L, and the copper concentration is in a range between about 2g/L and about 12 g/L. The use of EDTA at the lower concentration will help to maintain a consistent deposition rate throughout a deposition process that uses a single use electroless puddle plating type process. Traditional, electroless copper electroless plating processes employ higher EDTA to copper concentrations to achieve much greater bath stability at the expense of deposition rate. These traditional electroless plating baths are harder to

use since their ability to modulate fill characteristics is significantly reduced due to the adsorption of additives on the exposed surface. The high concentration of EDTA when used in a single use electroless puddle plating processes will greatly affect the deposition rates near the end of the electroless process due to the EDTA concentration increase as the water evaporates from the puddle during processing, and also due to the drop in copper concentration as it is plated out in the contact level aperture 1510 and on the field region 1505. A single use electroless puddle plating processes may be advantageous, due to ability to use solutions that have improved deposition rates without the issue of particle growth in the electroless plating solution or wafer-to-wafer electrolyte solution variation due to bath depletion.