(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2009-158751

(P2009-158751A)

(43) 公開日 平成21年7月16日(2009.7.16)

(51) Int.Cl.

H01L 23/12 (2006.01)

F 1

H01L 23/12

テーマコード (参考)

501P

審査請求 未請求 請求項の数 16 O L (全 21 頁)

(21) 出願番号

特願2007-335819 (P2007-335819)

(22) 出願日

平成19年12月27日 (2007.12.27)

(71) 出願人 000001889

三洋電機株式会社

大阪府守口市京阪本通2丁目5番5号

100105924

弁理士 森下 賢樹

齋藤 浩一

大阪府守口市京阪本通2丁目5番5号 三

洋電機株式会社内

岡山 芳央

大阪府守口市京阪本通2丁目5番5号 三

洋電機株式会社内

高野 洋

大阪府守口市京阪本通2丁目5番5号 三

洋電機株式会社内

(54) 【発明の名称】 素子搭載用基板およびその製造方法、半導体モジュールおよびその製造方法、ならびに携帯機器

## (57) 【要約】

【課題】半導体モジュールをさらに小型化するとともに、製造工程数を減らす。

【解決手段】素子搭載用基板10は、絶縁樹脂層12と、絶縁樹脂層12の一方の主表面S1に設けられた配線層14と、配線層14と電気的に接続され、配線層14から絶縁樹脂層12側に突出する複数の突起電極16と、絶縁樹脂層12の他方の主表面S2の、複数の突起電極16のそれぞれに対応する位置に設けられた対向電極18と、を備える。突起電極16のうち、一部の突起電極16aの突出長さは、他の突起電極16bとこれに対応する対向電極18aとが容量結合し、突起電極16bとこれに対応する対向電極18bとが電気的に接続されている。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

絶縁樹脂層と、

前記絶縁樹脂層の一方の主表面に設けられた配線層と、

前記配線層と電気的に接続され、前記配線層から前記絶縁樹脂層側に突出している複数の突起電極と、

前記絶縁樹脂層の他方の主表面の、前記複数の突起電極のそれぞれに対応する位置に設けられ、前記突起電極の頂部面に対向する対向面を有する対向電極と、を備え、

前記複数の突起電極のうち、一部の突起電極の突出長さが、他の突起電極の突出長さよりも短く、当該一部の突起電極とこれに対応する対向電極とが容量結合し、前記他の突起電極とこれに対応する対向電極とが電気的に接続されていることを特徴とする素子搭載用基板。

**【請求項 2】**

前記対向電極の前記対向面と前記一部の突起電極の前記頂部面との間に、前記絶縁樹脂層よりも誘電率の大きい誘電膜層を有することを特徴とする請求項 1 に記載の素子搭載用基板。

**【請求項 3】**

前記絶縁樹脂層の他方の主表面に設けられた他の配線層を備え、

前記対向電極は、前記他の配線層の一部であることを特徴とする請求項 1 または 2 に記載の素子搭載用基板。

**【請求項 4】**

請求項 1 ないし 3 のいずれか 1 項に記載の素子搭載用基板と、

前記素子搭載用基板に搭載された半導体素子と、

を備えたことを特徴とする半導体モジュール。

**【請求項 5】**

請求項 1 または 2 に記載の素子搭載用基板と、

素子電極が設けられ、前記素子搭載用基板に搭載された半導体素子と、

を備え、

前記対向電極は、前記半導体素子の素子電極であることを特徴とする半導体モジュール。

。

**【請求項 6】**

請求項 4 または 5 に記載の半導体モジュールを搭載したことを特徴とする携帯機器。

**【請求項 7】**

複数の突起電極が突設された金属板を準備する工程と、

前記複数の突起電極のうち、一部の突起電極の突出長さを他の突起電極の突出長さよりも短くする突出長さ調節工程と、

前記突起電極が絶縁樹脂層側に向くようにして前記金属板を絶縁樹脂層の一方の主表面に配置するとともに前記他の突起電極を前記絶縁樹脂層の他方の主表面から露出させ、また、前記突起電極の頂部面に対向する対向面を有する対向電極を前記絶縁樹脂層の他方の主表面の、前記複数の突起電極のそれぞれに対応する位置に配置し、前記一部の突起電極とこれに対応する対向電極とを容量結合させ、前記他の突起電極とこれに対応する対向電極とを電気的に接続させる結合工程と、

前記金属板を選択的に除去して配線層を形成する工程と、

を含むことを特徴とする素子搭載用基板の製造方法。

**【請求項 8】**

前記対向電極の前記対向面と前記一部の突起電極の前記頂部面との間に、前記絶縁樹脂層よりも誘電率の大きい誘電膜層を設ける工程を含むことを特徴とする請求項 7 に記載の素子搭載用基板の製造方法。

**【請求項 9】**

前記絶縁樹脂層の他方の主表面に他の配線層を設ける工程を含み、

10

20

30

40

50

前記対向電極は、前記他の配線層の一部とすることを特徴とする請求項 7 または 8 に記載の素子搭載用基板の製造方法。

**【請求項 10】**

前記突出長さ調節工程において、

前記他の突起電極の頂部面に金属を被覆することで、前記一部の突起電極の突出長さを他の突起電極の突出長さよりも短くすることを特徴とする請求項 7 ないし 9 のいずれか 1 項に記載の素子搭載用基板の製造方法。

**【請求項 11】**

前記突出長さ調節工程において、

前記一部の突起電極の一部を除去することで、当該一部の突起電極の突出長さを前記他の突起電極の突出長さよりも短くすることを特徴とする請求項 7 ないし 9 のいずれか 1 項に記載の素子搭載用基板の製造方法。 10

**【請求項 12】**

請求項 7 ないし 11 のいずれか 1 項に記載の素子搭載用基板の製造方法により製造された素子搭載用基板に、半導体素子を搭載する工程を含むことを特徴とする半導体モジュールの製造方法。

**【請求項 13】**

複数の突起電極が突設された金属板を準備する工程と、

前記複数の突起電極のうち、一部の突起電極の突出長さを他の突起電極の突出長さよりも短くする突出長さ調節工程と、 20

前記突起電極が絶縁樹脂層側に向くようにして前記金属板を絶縁樹脂層の一方の主表面に配置するとともに前記他の突起電極を前記絶縁樹脂層の他方の主表面から露出させ、また、前記突起電極に対応する素子電極が設けられた半導体素子を前記絶縁樹脂層の他方の主表面に配置し、前記一部の突起電極とこれに対応する素子電極とを容量結合させ、前記他の突起電極とこれに対応する素子電極とを電気的に接続させる結合工程と、

前記金属板を選択的に除去して配線層を形成する工程と、

を含むことを特徴とする半導体モジュールの製造方法。

**【請求項 14】**

前記結合工程において、前記金属板および半導体素子を、前記絶縁樹脂層を介して圧着して、前記一部の突起電極とこれに対応する素子電極とを容量結合させ、前記他の突起電極とこれに対応する素子電極とを電気的に接続させることを特徴とする請求項 13 に記載の半導体モジュールの製造方法。 30

**【請求項 15】**

前記絶縁樹脂層は、加圧によって塑性流動を起こすことを特徴とする請求項 14 に記載の半導体モジュールの製造方法。

**【請求項 16】**

前記素子電極と前記一部の突起電極との間に、前記絶縁樹脂層よりも誘電率の大きい誘電膜層を設ける工程を含むことを特徴とする請求項 13 ないし 15 のいずれか 1 項に記載の半導体モジュールの製造方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、素子搭載用基板およびその製造方法、半導体モジュールおよびその製造方法、ならびに携帯機器に関する。 40

**【背景技術】**

**【0002】**

携帯電話、PDA、DVC、DSCといったポータブルエレクトロニクス機器の高機能化が加速するなか、こうした製品が市場で受け入れられるためには小型・軽量化が必須となっている。そのため、これらのエレクトロニクス機器に使用されるマルチチップモジュール（MCM）などの半導体モジュールに対しても小型化が求められている。これに対し

10

20

30

40

50

、基体上に形成された絶縁層によって、半導体チップなどの能動素子とキャパシタなどの受動素子とが被覆され、能動素子と受動素子とが絶縁層を介して絶縁層状の配線に接続されている半導体装置が提案されている（特許文献1参照）。

【特許文献1】特開2005-5548号公報

【発明の開示】

【発明が解決しようとする課題】

【0003】

しかしながら、特許文献1に記載の半導体装置では、キャパシタなどの受動素子を別個の部品としてシリコン基板に搭載しているため、半導体モジュールの小型化が抑制され、また製造工程数が多くなるという問題があった。

10

【0004】

本発明はこうした状況に鑑みてなされたものであり、その目的は、半導体モジュールをさらに小型化するとともに、製造工程数を減らす技術の提供にある。

【課題を解決するための手段】

【0005】

上記課題を解決するために、本発明のある態様は素子搭載用基板である。この素子搭載用基板は、絶縁性の樹脂で形成された絶縁樹脂層と、絶縁樹脂層の一方の主表面に設けられた配線層と、配線層と電気的に接続され、配線層から絶縁樹脂層側に突出している複数の突起電極と、絶縁樹脂層の他方の主表面の、複数の突起電極のそれぞれに対応する位置に設けられ、突起電極の頂部面に対向する対向面を有する対向電極と、を備え、複数の突起電極のうち、一部の突起電極の突出長さが、他の突起電極の突出長さよりも短く、当該一部の突起電極とこれに対応する対向電極とが容量結合し、他の突起電極とこれに対応する対向電極とが電気的に接続されている。

20

【0006】

この態様によれば、配線層に設けられた複数の突起電極のうち、一部の突起電極が対向電極と容量結合し、他の突起電極が電気的に接続される。このため、この素子搭載用基板に半導体素子を搭載して半導体モジュールを形成した場合に、半導体モジュールの小型化が可能となる。

【0007】

上記態様において、素子搭載用基板は、対向電極の対向面と一部の突起電極の頂部面との間に、絶縁樹脂層よりも誘電率の大きい誘電膜層を有するものであってもよい。

30

【0008】

上記態様において、絶縁樹脂層の他方の主表面に設けられた他の配線層を備え、対向電極は、他の配線層の一部であってもよい。

【0009】

本発明の他の態様は、半導体モジュールである。この半導体モジュールは、上述したいずれかの態様の素子搭載用基板と、素子搭載用基板に搭載された半導体素子と、を備える。

【0010】

本発明のさらに他の態様もまた、半導体モジュールである。この半導体モジュールは、上述したいずれかの態様の素子搭載用基板と、素子電極が設けられ、素子搭載用基板に搭載された半導体素子と、を備え、対向電極は、半導体素子の素子電極である。

40

【0011】

本発明のさらに他の態様は、携帯機器である。この携帯機器は、上述したいずれかの態様の半導体モジュールを搭載している。

【0012】

本発明のさらに他の態様は、素子搭載用基板の製造方法である。この素子搭載用基板の製造方法は、複数の突起電極が突設された金属板を準備する工程と、複数の突起電極のうち、一部の突起電極の突出長さを他の突起電極の突出長さよりも短くする突出長さ調節工程と、突起電極が絶縁樹脂層側に向くようにして金属板を絶縁樹脂層の一方の主表面に配

50

置するとともに他の突起電極を絶縁樹脂層の他方の主表面から露出させ、また、突起電極の頂部面に対向する対向面を有する対向電極を絶縁樹脂層の他方の主表面の、複数の突起電極のそれぞれに対応する位置に配置し、一部の突起電極とこれに対応する対向電極とを容量結合させ、他の突起電極とこれに対応する対向電極とを電気的に接続させる結合工程と、金属板を選択的に除去して配線層を形成する工程と、を含む。

#### 【0013】

この態様によれば、一部の突起電極を対向電極と容量結合させ、他の突起電極を電気的に接続しているため、この素子搭載用基板に半導体素子を搭載して半導体モジュールを形成した場合に、半導体モジュールの小型化が可能となる。また、突起電極と対向電極との電気的な接続による再配線形成と同時に、突起電極と対向電極とを容量結合させているため、製造工程数を減らすことができ、製造工程の簡略化、製造コストの削減を図ることができる。

10

#### 【0014】

上記態様において、対向電極の対向面と一部の突起電極の頂部面との間に、絶縁樹脂層よりも誘電率の大きい誘電膜層を設ける工程を含めてもよい。

#### 【0015】

上記態様において、絶縁樹脂層の他方の主表面に他の配線層を設ける工程を含み、対向電極は、他の配線層の一部としてもよい。

20

#### 【0016】

上記態様における突出長さ調節工程において、他の突起電極の頂部面に金属を被覆することで、一部の突起電極の突出長さを他の突起電極の突出長さよりも短くしてもよい。

#### 【0017】

上記態様における突出長さ調節工程において、一部の突起電極の一部を除去することで、当該一部の突起電極の突出長さを他の突起電極の突出長さよりも短くしてもよい。

#### 【0018】

本発明のさらに他の態様は、半導体モジュールの製造方法である。この半導体モジュールの製造方法は、上述したいずれかの態様の素子搭載用基板の製造方法により製造された素子搭載用基板に、半導体素子を搭載する工程を含む。

30

#### 【0019】

本発明のさらに他の態様もまた、半導体モジュールの製造方法である。この半導体モジュールの製造方法は、複数の突起電極が突設された金属板を準備する工程と、複数の突起電極のうち、一部の突起電極の突出長さを他の突起電極の突出長さよりも短くする突出長さ調節工程と、突起電極が絶縁樹脂層側に向くようにして金属板を絶縁樹脂層の一方の主表面に配置するとともに他の突起電極を絶縁樹脂層の他方の主表面から露出させ、また、突起電極に対応する素子電極が設けられた半導体素子を絶縁樹脂層の他方の主表面に配置し、一部の突起電極とこれに対応する素子電極とを容量結合させ、他の突起電極とこれに対応する素子電極とを電気的に接続させる結合工程と、金属板を選択的に除去して配線層を形成する工程と、を含む。

#### 【0020】

上記態様における結合工程において、金属板および半導体素子を、絶縁樹脂層を介して圧着して、一部の突起電極とこれに対応する素子電極とを容量結合させ、他の突起電極とこれに対応する素子電極とを電気的に接続させてもよい。

40

#### 【0021】

上記態様において、絶縁樹脂層は、加圧によって塑性流動を起こすものであってもよい。

#### 【0022】

上記態様において、素子電極と一部の突起電極との間に、絶縁樹脂層よりも誘電率の大きい誘電膜層を設ける工程を含めてもよい。

#### 【発明の効果】

#### 【0023】

50

本発明によれば、配線層に設けられた複数の突起電極のうち、一部の突起電極が対向電極と容量結合し、他の突起電極が電気的に接続されるため、半導体モジュールの小型化が可能となる。また、突起電極と対向電極との電気的な接続による再配線形成と同時に、突起電極と対向電極とを容量結合させているため、製造工程数を減らすことができる。

【発明を実施するための最良の形態】

【0024】

以下、本発明を好適な実施の形態をもとに図面を参照しながら説明する。各図面に示される同一または同等の構成要素、部材、処理には、同一の符号を付するものとし、適宜重複した説明は省略する。また、実施の形態は、発明を限定するものではなく例示であって、実施の形態に記述されるすべての特徴やその組み合わせは、必ずしも発明の本質的なものであるとは限らない。10

【0025】

(実施形態1)

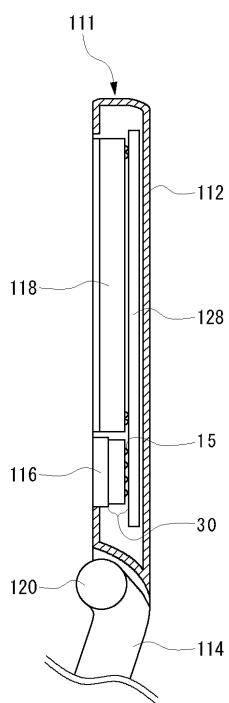

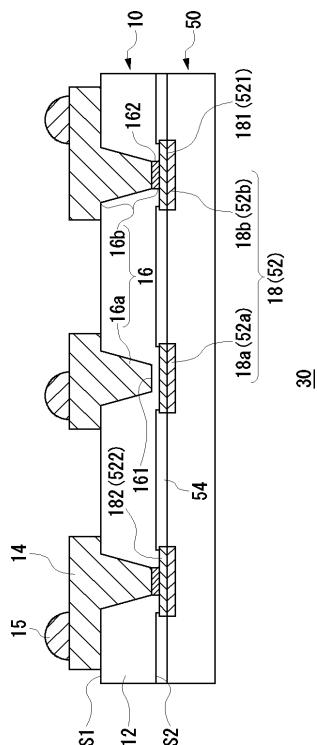

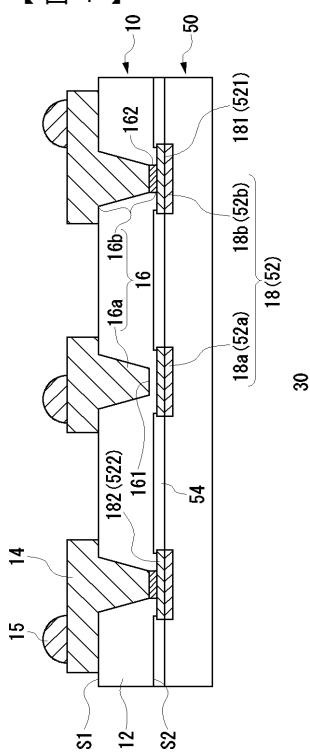

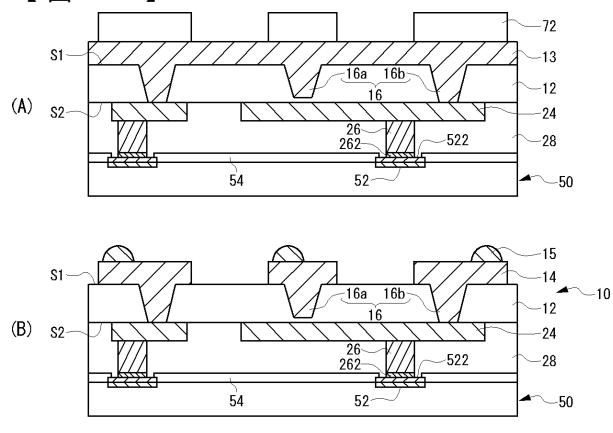

図1は、実施形態1に係る素子搭載用基板10およびこれを用いた半導体モジュール30の構成を示す概略断面図である。半導体モジュール30は、素子搭載用基板10およびこれに搭載された半導体素子50を備える。

【0026】

素子搭載用基板10は、絶縁性の樹脂で形成された絶縁樹脂層12と、絶縁樹脂層12の一方の主表面S1に設けられた配線層14と、配線層14と電気的に接続され、配線層14から絶縁樹脂層12側に突出している複数の突起電極16とを備える。また、素子搭載用基板10は、絶縁樹脂層12の他方の主表面S2の、複数の突起電極16のそれぞれに対応する位置に設けられ、突起電極16の頂部面161に対向する対向面181を有する対向電極18と、を備える。20

【0027】

絶縁樹脂層12は、絶縁性の樹脂からなり、たとえば加圧したときに塑性流動を引き起こす材料で形成されている。加圧したときに塑性流動を引き起こす材料としては、エポキシ系熱硬化型樹脂が挙げられる。絶縁樹脂層12に用いられるエポキシ系熱硬化型樹脂は、たとえば、温度160°C、圧力8 MPaの条件下で、粘度が1 kPa·sの特性を有する材料であればよい。また、このエポキシ系熱硬化型樹脂は、たとえば温度160°Cの条件下で、5~15 MPaで加圧した場合に、加圧しない場合と比較して、樹脂の粘度が約1/8に低下する。これに対して、熱硬化前のBステージのエポキシ樹脂は、ガラス転移温度Tg以下の条件下では、樹脂を加圧しない場合と同程度に、粘性がなく、加圧しても粘性は生じない。また、このエポキシ系熱硬化型樹脂は、約3~4の誘電率を有する誘電体である。30

【0028】

配線層14は、絶縁樹脂層12の一方の主表面S1に設けられており、導電材料、好ましくは圧延金属、さらには圧延銅により形成される。配線層14には、絶縁樹脂層12側に複数の突起電極16が突設されている。本実施例においては、配線層14と突起電極16とは一体的に形成されているが、特にこれに限定されない。絶縁樹脂層12と反対側の配線層14の主表面には、所定の位置にはんだバンプ15が形成されている。はんだバンプ15を形成する位置は、たとえば再配線で引き回した先の位置である。40

【0029】

突起電極16は、たとえば平面視で丸型であり、頂部に近づくにつれて径が細くなるように形成された側面を備えている。なお、突起電極16の形状は特に限定されず、たとえば、所定の径を有する円柱状であってもよい。また、平面視で四角形などの多角形であってもよい。ここで、複数の突起電極16のうち、一部の突起電極16aの配線層14からの突出長さ(高さ)は、他の突起電極16bの配線層14からの突出長さよりも短くなっている。

【0030】

すなわち、本実施形態においては、突起電極16bの頂部面161を被覆した金属層1

62と、配線層14から突出する部分とによって突起電極16bが構成されているため、突起電極16aの突出長さが突起電極16bの突出長さよりも短くなっている。金属層162は、たとえば、金(Au)などの金属を用いて電解めっき法あるいは無電解めっき法により形成された金属めっき層であるか、あるいは導電ペーストを用いて形成された導電ペースト層である。本実施形態では、金属層162は金(Au)およびニッケル(Ni)からなるNi/Auめっき層で構成されている。あるいは、一部の突起電極16aの頂部を、エッチングなどによって除去することで、突起電極16aの突出長さを他の突起電極16bの突出長さよりも短くすることもできる。

#### 【0031】

対向電極18は、銅(Cu)やアルミニウム(Al)などの金属からなる。対向電極18は、絶縁樹脂層12の他方の主表面S2の、複数の突起電極16のそれぞれに対応する位置に設けられている。突起電極16aは突起電極16bよりも突出長さが短いため、突起電極16aとこれに対応する対向電極18aとの間には絶縁樹脂層12が介在している。そのため、突起電極16aと対向電極18aとは容量結合し、キャパシタを構成する。一方、突起電極16aよりも突出長さの長い突起電極16bとこれに対応する対向電極18bとは、互いが接触して電気的に接続されている(オーミック接合)。なお、本実施形態では、対向電極18の対向面181にNi/Auの金属層182が設けられている。そのため突起電極16bと対向電極18bとは金-金接合し、突起電極16bと対向電極18bとの接続信頼性の向上が図られる。

#### 【0032】

ここで、本実施形態においては、対向電極18は、半導体素子50の素子電極52となっている。半導体素子50には、突起電極16a、16bのそれぞれに対応する素子電極52a、52bが設けられている。また、絶縁樹脂層12に接する側の半導体素子50の主表面には、素子電極52が開口するように設けられた保護層54が積層されている。半導体素子50の具体例としては、集積回路(IC)、大規模集積回路(LSI)などの半導体チップが挙げられる。保護層54の具体例としては、ポリイミド層が挙げられる。なお、本実施形態では、対向電極18が半導体素子50の素子電極52となっている構造を示すが、半導体素子50は、素子搭載用基板10の任意の位置に、ワイヤボンディングなどの任意の方法で実装されていてもよい。

#### 【0033】

またここで、本実施形態においては、絶縁樹脂層12が素子搭載用基板10と半導体素子50との間に設けられ、絶縁樹脂層12の一方の主表面S1に素子搭載用基板10が圧着し、他方の主表面S2に半導体素子50が圧着している。そして、突起電極16bが、絶縁樹脂層12を貫通して、対向電極18b、すなわち半導体素子50に設けられた素子電極52bと電気的に接続されている。絶縁樹脂層12は、加圧により塑性流動を起こす材料からなるため、素子搭載用基板10、絶縁樹脂層12および半導体素子50がこの順で加圧により一体化された状態において、突起電極16bと素子電極52bとの間に絶縁樹脂層12の残膜が介在することが抑制され、接続信頼性の向上が図られる。

#### 【0034】

(素子搭載用基板および半導体モジュールの製造方法)

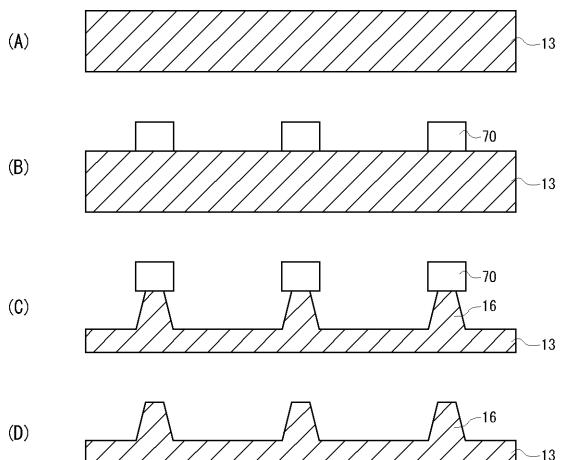

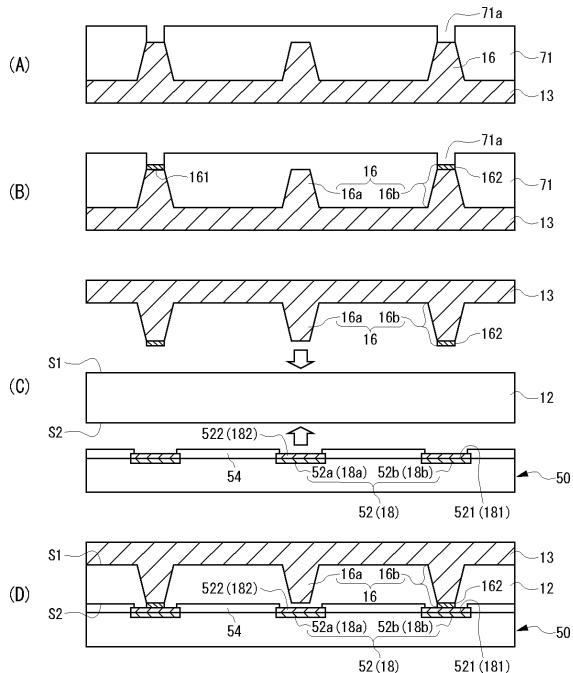

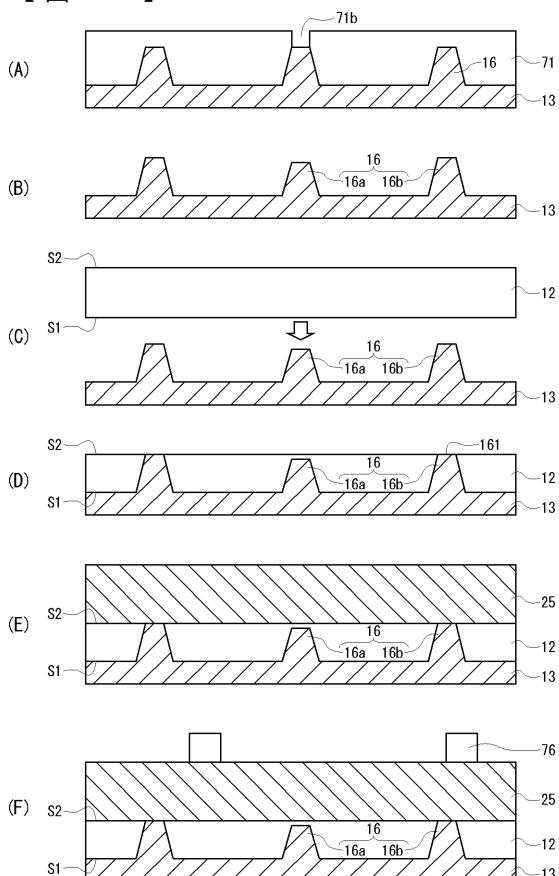

図2(A)～(D)は、突起電極16の形成方法を示す工程断面図である。

#### 【0035】

図2(A)に示すように、少なくとも、突起電極16の高さと配線層14の厚さとの和より大きい厚さを有する銅板13を用意する。

#### 【0036】

次に、図2(B)に示すように、リソグラフィ法により、突起電極16のパターンに合わせてレジスト70を選択的に形成する。

#### 【0037】

次に、図2(C)に示すように、レジスト70をマスクとして、銅板13に所定のパターンの突起電極16を形成する。

10

20

30

40

50

## 【0038】

次に、図2(D)に示すように、レジスト70を除去する。以上説明した工程により、突起電極16が形成される。

## 【0039】

本実施形態の突起電極16における基底部の径、先端部の径、高さは、たとえばそれぞれ、 $100\mu m$ 、 $50\mu m$ 、 $40\mu m$ である。

## 【0040】

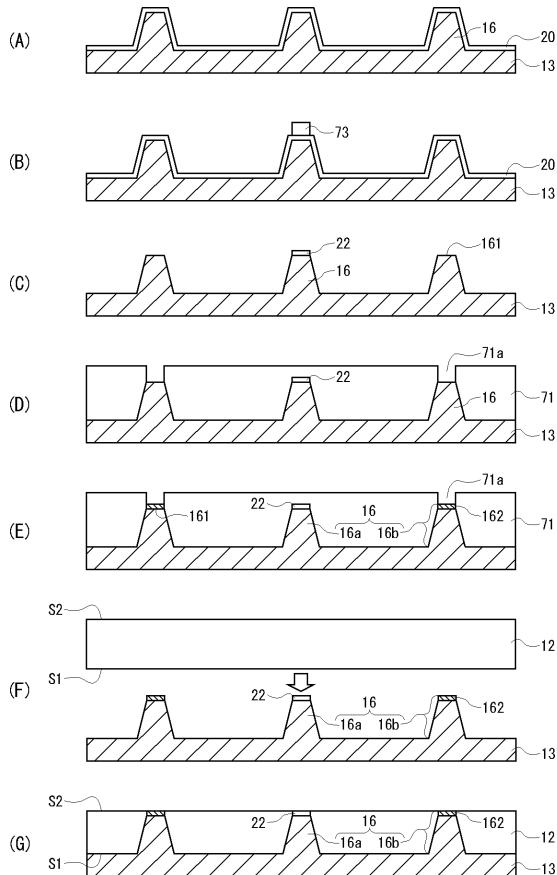

図3(A)～(D)および図4(A)～(C)は、突起電極16と、対向電極18あるいは素子電極52との結合方法を示す工程断面図である。

## 【0041】

図3(A)に示すように、複数の突起電極16が形成された側の銅板13の主表面に、リソグラフィ法により、レジスト71を積層して所定の突起電極16に対応する位置に開口部71aを設ける。

10

## 【0042】

次に、図3(B)に示すように、開口部71aにおいて露出している突起電極16の頂部面161に、金属層162を形成する。金属層162は、たとえば電解めっき法または無電解めっき法によりNi/Auの金属層として形成する。これにより金属層162が形成されない突起電極16aの銅板13からの突出長さを、金属層162を含む突起電極16bの銅板13からの突出長さよりも短くする。金属層162は、Ni層が突起電極16と接する側に、Au層が対向電極18と接する側となるように形成される。なお、金属層162の形成方法としては、特にこれに限定されず、たとえば金ペーストなどの導電性ペーストを用いて形成してもよい。金属層162の厚さは、たとえば約 $1.25\sim3.25\mu m$ であり、そのうちAu層の厚さが $0.25\mu m$ 、Ni層の厚さが $1\sim3\mu m$ である。

20

## 【0043】

次に、図3(C)に示すように、レジスト71を除去する。そして、突起電極16が絶縁樹脂層12側に向くようにして銅板13を絶縁樹脂層12の一方の主表面S1に配置する。また、突起電極16の頂部面161に対向する対向面181を有する対向電極18を絶縁樹脂層の他方の主表面S2の、突起電極16のそれぞれに対応する位置に配置する。絶縁樹脂層12の厚さは突起電極16bの高さ程度であり、約 $43\mu m$ である。対向電極18の対向面181には、突起電極16bと同様にして、Ni/Auの金属層182が形成されている。

30

## 【0044】

次に、図3(D)に示すように、突起電極16bを絶縁樹脂層12の他方の主表面S2から露出させて、突起電極16aとこれに対応する対向電極18aとを容量結合させ、突起電極16bとこれに対応する対向電極18bとを電気的に接続させる。突起電極16aは、金属層162の厚さ分だけ突起電極16bよりも突出長さが短いため、突起電極16bと対向電極18bとが当接した状態において、突起電極16aと対向電極18aとの間に、金属層162の厚さ分だけ絶縁樹脂層12が介在することとなる。これにより、突起電極16aと対向電極18aとを容量結合させ、受動素子としてのキャパシタを形成することができる。当該キャパシタは、絶縁樹脂層12の材料や、突起電極16aと対向電極18aとの間に介在する絶縁樹脂層12の厚さ、すなわち金属層162の厚さを調節することで、その容量を任意に変更することが可能である。また、突起電極16bの頂部面161と対向電極18bの対向面181には、それぞれNi/Auの金属層182、金属層182が形成されており、突起電極16bと対向電極18bとは金-金接合により電気的に接続される。そのため、突起電極16bと対向電極18bとの接続信頼性の向上が図られる。なお、突起電極16bと対向電極18bとには、金属層を設けなくてもよい。この場合、一部の突起電極16aの頂部をエッチングして、一部を除去することで、突起電極16aの突出長さを他の突起電極16bの突出長さよりも短くすることができる。また、突起電極16aの一部を除去する量を調節することで、キャパシタの容量を任意に変更することができる。

40

50

## 【0045】

また、本実施形態においては、絶縁樹脂層12の他方の主表面S2に突起電極16に対応する素子電極52が設けられた半導体素子50を配置している。この場合、素子電極52が対向電極18に相当する。そして、プレス装置を用いて、銅板13と半導体素子50とを、絶縁樹脂層12を介して圧着することにより、銅板13、絶縁樹脂層12および半導体素子50を一体化する。これにより、突起電極16aと素子電極52aとの容量結合および突起電極16bと素子電極52bとの電気的接続を行っている。プレス加工時の圧力および温度は、それぞれ約5Mpaおよび180である。プレス加工により、絶縁樹脂層12が塑性流動を起こし、突起電極16が絶縁樹脂層12を貫通し、突起電極16bの金属層162と素子電極52bの金属層522とが圧着して、突起電極16bと素子電極52bとが電気的に接続される。突起電極16は、その全体的な形状が先端に近づくにつれて細くなるような形状であるため、突起電極16が絶縁樹脂層12をスムースに貫通する。

10

## 【0046】

次に、図4(A)に示すように、リソグラフィ法により、配線層14のパターンに合わせてレジスト72を選択的に形成する。具体的には、ラミネーター装置を用いて銅板13に所定膜厚のレジスト膜を貼り付け、配線層14のパターンを有するフォトマスクを用いて露光した後、Na<sub>2</sub>CO<sub>3</sub>溶液を用いて現像し、未露光領域のレジストを除去することによって、銅板13の上にレジスト72が選択的に形成される。なお、レジストとの密着性向上のために、レジスト膜のラミネート前に、銅板13の表面に研磨、洗浄等の前処理を必要に応じて施すことが望ましい。また、レジスト72のラミネート前に、必要に応じて、銅板13の裏面側の全体をエッチングして、銅板13を配線層14の厚さに調整するようにしてもよい。

20

## 【0047】

次に、図4(B)に示すように、塩化第二鉄溶液を用いて、レジスト72をマスクとして銅板13をエッチングすることにより、所定の配線パターンを有する配線層14を形成する。そして、レジストをNaOH溶液などの剥離剤を用いて剥離する。本実施形態における配線層14の厚さは約15μmである。

30

## 【0048】

次に、図4(C)に示すように、配線層14の所定の位置にはんだバンプ15を形成する。はんだバンプ15を形成する位置は、たとえば再配線で引き回した先の位置である。

## 【0049】

以上説明した製造工程により、素子搭載用基板10が形成される。また、絶縁樹脂層12を介して半導体素子50を圧着し、対向電極18を素子電極52とした場合には、半導体モジュール30が得られる。

40

## 【0050】

以上説明したように、本実施形態では、配線層14に設けられた複数の突起電極16のうち、一部の突起電極16aが対向電極18aあるいは素子電極52aと容量結合し、他の突起電極16bが対向電極18bあるいは素子電極52bと電気的に接続される。そのため、受動素子であるキャパシタを別個の部品として素子搭載用基板10に搭載する必要がないため、半導体モジュール30の小型化が可能となる。また、配線層14に突設された突起電極16bと、対向電極18bあるいは素子電極52との電気的な接続による再配線形成と同時に、突起電極16aと、対向電極18aあるいは素子電極52aとを容量結合させてキャパシタを形成している。そのため、キャパシタを別個の部品として素子搭載用基板10に搭載する場合と比べて、製造工程数を減らすことができ、製造工程の簡略化、製造コストの削減を図ることができる。さらに、絶縁樹脂層12内に挿入される突起電極16aと、対向電極18aあるいは素子電極52aとを容量結合させてキャパシタを形成しているため、電極間距離を小さくすることができる。そのため、キャパシタの容量を大きくすることができる。また、当該キャパシタは、絶縁樹脂層12の材料や、突起電極16aと対向電極18aとの間に介在する絶縁樹脂層12の厚さを調節することで、その

50

容量を任意に変更することが可能である。

【0051】

(実施形態2)

上述の実施形態1では、銅板13と、対向電極18あるいは半導体素子50との間に絶縁樹脂層12を挟持して加圧成形し、これらを一体化して素子搭載用基板10あるいは半導体モジュール30を形成したが、以下のようにして素子搭載用基板10あるいは半導体モジュール30を形成してもよい。以下、本実施形態について説明する。なお、突起電極16の形成方法については、実施形態1と同様である。また、実施形態1と同一の構成については同一の符号を付し、その説明は省略する。

【0052】

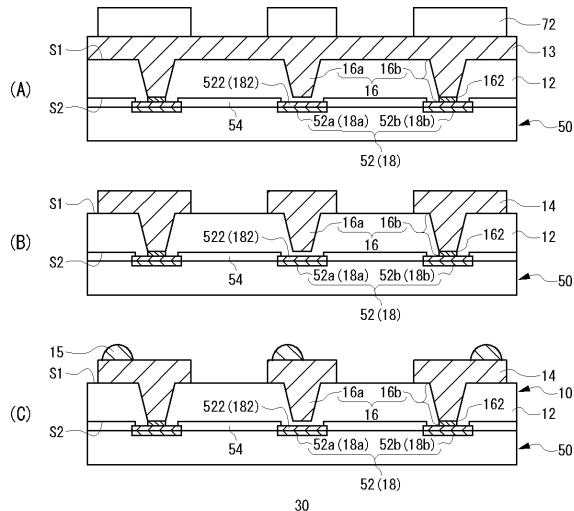

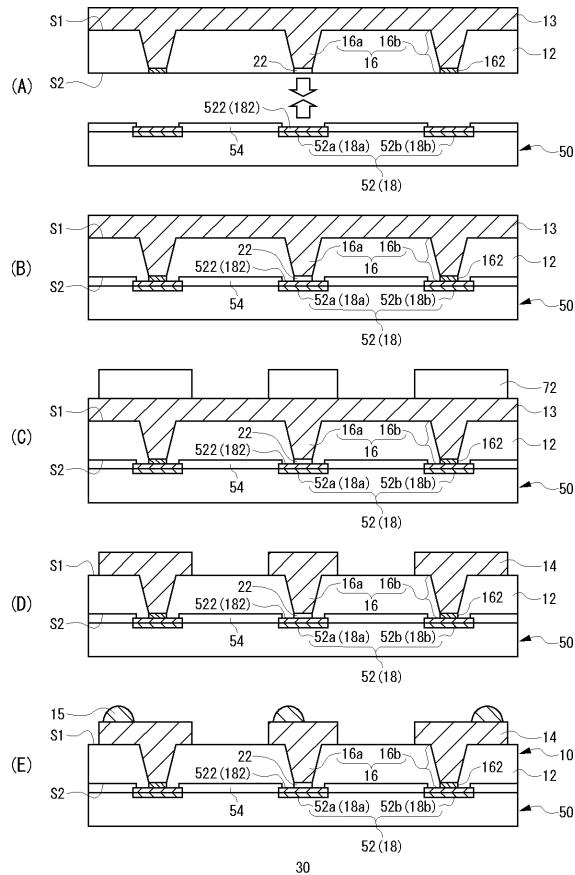

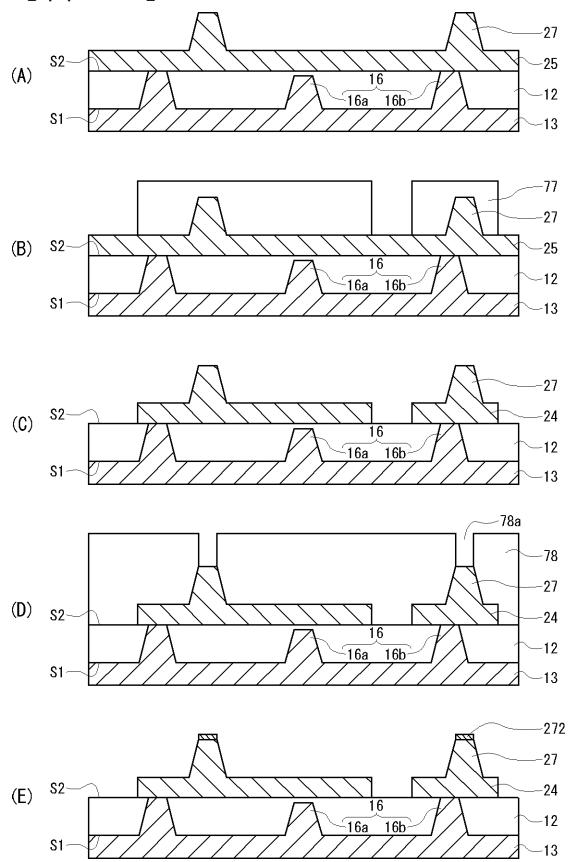

図5(A)～(F)および図6(A)～(C)は、突起電極16と、対向電極18あるいは素子電極52との結合方法を示す工程断面図である。

【0053】

図5(A)に示すように、複数の突起電極16が形成された側の銅板13の主表面に、リソグラフィ法により、レジスト71を積層して所定の突起電極16に対応する位置に開口部71aを設ける。

【0054】

次に、図5(B)に示すように、開口部71aにより露出している突起電極16の頂部面161に金属層162を形成する。これにより金属層162が形成されない突起電極16aの銅板13からの突出長さを、金属層162を含む突起電極16bの銅板13からの突出長さよりも短くする。

【0055】

次に、図5(C)に示すように、レジスト71を除去し、銅板13を絶縁樹脂層12の一方の主表面S1側に配置し、突起電極16が形成された側の銅板13の主表面に絶縁樹脂層12を圧着する。

【0056】

次に、図5(D)に示すように、銅板13に圧着した絶縁樹脂層12の他方の主表面S2側をエッチングして、突起電極16bの金属層162を露出させる。

【0057】

次に、図5(E)に示すように、半導体素子50を絶縁樹脂層12の他方の主表面S2側に配置して、絶縁樹脂層12に圧着した銅板13と半導体素子50とを圧着し、図5(F)に示すように銅板13、絶縁樹脂層12および半導体素子50を一体化する。これにより、突起電極16aと素子電極52aとの容量結合および突起電極16bと素子電極52bとの電気的接続を行う。

【0058】

次に、図6(A)に示すように、リソグラフィ法により、配線層14のパターンに合わせてレジスト72を選択的に形成する。

【0059】

次に、図6(B)に示すように、レジスト72をマスクとして銅板13をエッチングすることにより、所定の配線パターンを有する配線層14を形成する。そして、レジスト72を除去する。

【0060】

次に、図6(C)に示すように、配線層14の所定の位置にはんだバンプ15を形成する。

【0061】

以上説明した製造工程により、半導体モジュール30が形成される。なお、半導体素子50の代わりに対向電極18を用いてもよく、その場合には、上述の工程によって素子搭載用基板10が得られる。

【0062】

本実施形態によれば、実施形態1の上述の効果に加えて、さらに次のような効果が得ら

10

20

30

40

50

れる。すなわち、本実施形態においては、金属層 162 を露出させた後に対向電極 18 あるいは半導体素子 50 を絶縁樹脂層 12 に圧着している。そのため、突起電極 16 と、対向電極 18 あるいは素子電極 52 との正確な位置決めが可能となり、突起電極 16b と、対向電極 18b あるいは素子電極 52b との接続信頼性が向上する。これにより、素子搭載用基板 10 あるいは半導体モジュール 30 の信頼性の向上を図ることができる。

#### 【0063】

##### (実施形態 3)

上述の実施形態 1 および 2 の構成では、突起電極 16a と、対向電極 18a あるいは素子電極 52a との間に絶縁樹脂層 12 が介在しているが、本実施形態に示すように突起電極 16a と、対向電極 18a あるいは素子電極 52a との間に絶縁樹脂層 12 よりも誘電率の大きい誘電膜層を設けてよい。以下、本実施形態について説明する。なお、突起電極 16 の形成方法については、実施形態 1 と同様である。また、実施形態 1 あるいは 2 と同一の構成については同一の符号を付し、その説明は省略する。

#### 【0064】

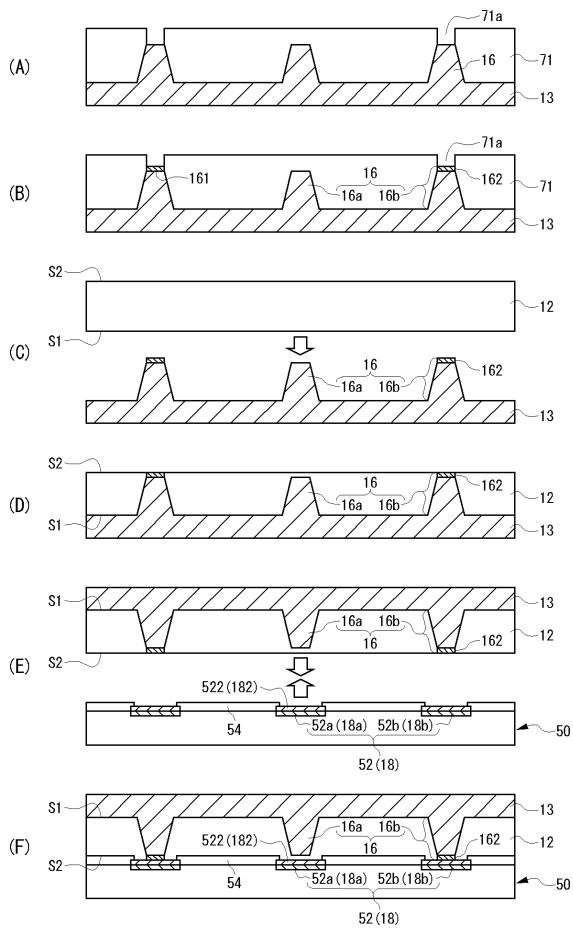

図 7 (A) ~ (G) および図 8 (A) ~ (E) は、突起電極 16 と、対向電極 18 あるいは素子電極 52 との結合方法を示す工程断面図である。

#### 【0065】

図 7 (A) に示すように、複数の突起電極 16 が形成された側の銅板 13 の主表面全体に、誘電膜 20 を成膜する。誘電膜 20 は、プラズマ CVD 法などにより、たとえば窒化シリコン (SiN) 膜として形成する。SiN 膜は、約 7 の誘電率を有する。

#### 【0066】

次に、図 7 (B) に示すように、リソグラフィ法により、誘電膜 20 上の所定の突起電極 16 に対応する位置に、レジスト 73 を積層する。

#### 【0067】

次に、図 7 (C) に示すように、レジスト 73 をマスクとして、誘電膜 20 をエッチングし、所定の突起電極 16 の頂部面 161 に、誘電膜層 22 を形成する。

#### 【0068】

次に、図 7 (D) に示すように、複数の突起電極 16 が形成された側の銅板 13 の主表面に、リソグラフィ法により、レジスト 71 を積層する。そして誘電膜層 22 を形成していない突起電極 16 に対応する位置に開口部 71a を設ける。

#### 【0069】

次に、図 7 (E) に示すように、開口部 71a において露出している突起電極 16 の頂部面 161 に、金属層 162 を形成する。これにより金属層 162 が形成されない突起電極 16a の銅板 13 からの突出長さを、金属層 162 を含む突起電極 16b の銅板 13 からの突出長さよりも短くする。

#### 【0070】

次に、図 7 (F) に示すように、レジスト 71 を除去した後、銅板 13 を絶縁樹脂層 12 の一方の主表面 S1 側に配置し、突起電極 16 が形成された側の銅板 13 の主表面に絶縁樹脂層 12 を圧着する。

#### 【0071】

次に、図 7 (G) に示すように、銅板 13 に圧着した絶縁樹脂層 12 の他方の主表面 S2 側をエッチングして、誘電膜層 22 および金属層 162 を露出させる。

#### 【0072】

次に、図 8 (A) に示すように、半導体素子 50 を絶縁樹脂層 12 の他方の主表面 S2 側に配置して、絶縁樹脂層 12 に圧着した銅板 13 と半導体素子 50 とを圧着し、図 8 (B) に示すように銅板 13、絶縁樹脂層 12 および半導体素子 50 を一体化する。これにより、突起電極 16a と素子電極 52a とを、誘電膜層 22 を介して容量結合させ、また突起電極 16b と素子電極 52b とを電気的に接続する。

#### 【0073】

次に、図 8 (C) に示すように、リソグラフィ法により、配線層 14 のパターンに合わ

せてレジスト 7 2 を選択的に形成する。

【0074】

次に、図 8 (D) に示すように、レジスト 7 2 をマスクとして銅板 1 3 をエッティングすることにより、所定の配線パターンを有する配線層 1 4 を形成する。そして、レジスト 7 2 を除去する。

【0075】

次に、図 8 (E) に示すように、配線層 1 4 の所定の位置にはんだバンプ 1 5 を形成する。

【0076】

以上説明した製造工程により、半導体モジュール 3 0 が形成される。なお、半導体素子 5 0 の代わりに対向電極 1 8 を用いてもよく、その場合には、上述の工程によって素子搭載用基板 1 0 が得られる。また、本実施形態では、実施形態 2 と同様に銅板 1 3 に絶縁樹脂層 1 2 を圧着した後に半導体素子 5 0 を圧着しているが、特にこれに限定されず、実施形態 1 と同様に銅板 1 3 と半導体素子 5 0 とを略同時に圧着してもよい。10

【0077】

本実施形態によれば、実施形態 1 および 2 の上述の効果に加えて、さらに次のような効果が得られる。すなわち、本実施形態においては、突起電極 1 6 a と、対向電極 1 8 a あるいは素子電極 5 2 a との間に絶縁樹脂層 1 2 よりも誘電率の大きい誘電膜層 2 2 を設けている。そして、誘電膜層 2 2 を介して突起電極 1 6 a と、対向電極 1 8 a あるいは素子電極 5 2 a を容量結合させている。そのため、突起電極 1 6 a と、対向電極 1 8 a あるいは素子電極 5 2 a とにより形成されるキャパシタの容量をさらに大きくすることができる。20

【0078】

(実施形態 4)

本実施形態は、対向電極 1 8 が、絶縁樹脂層 1 2 の他方の主表面 S 2 に設けられた他の配線層の一部である構成の例である。以下、本実施形態について説明する。なお、突起電極 1 6 の形成方法については、実施形態 1 と同様である。また、実施形態 1 ないし 3 と同一の構成については同一の符号を付し、その説明は省略する。

【0079】

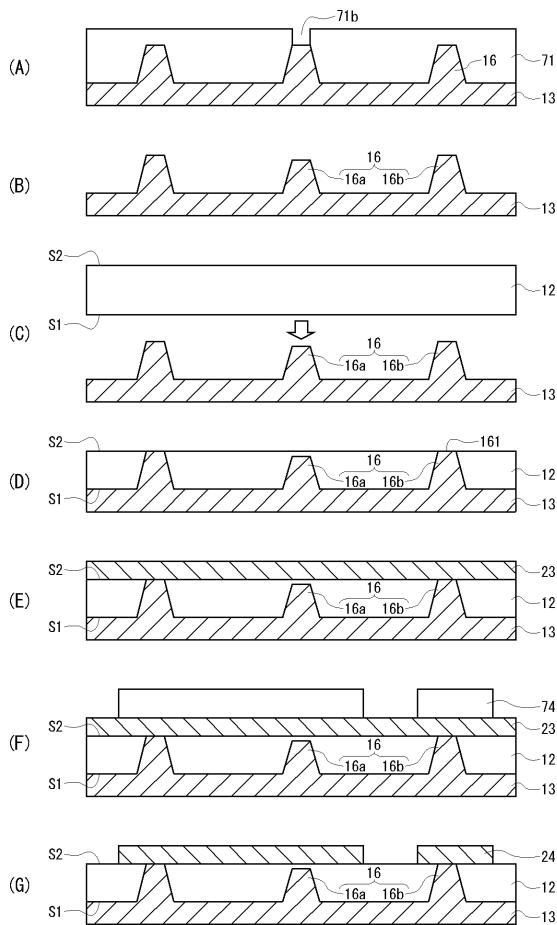

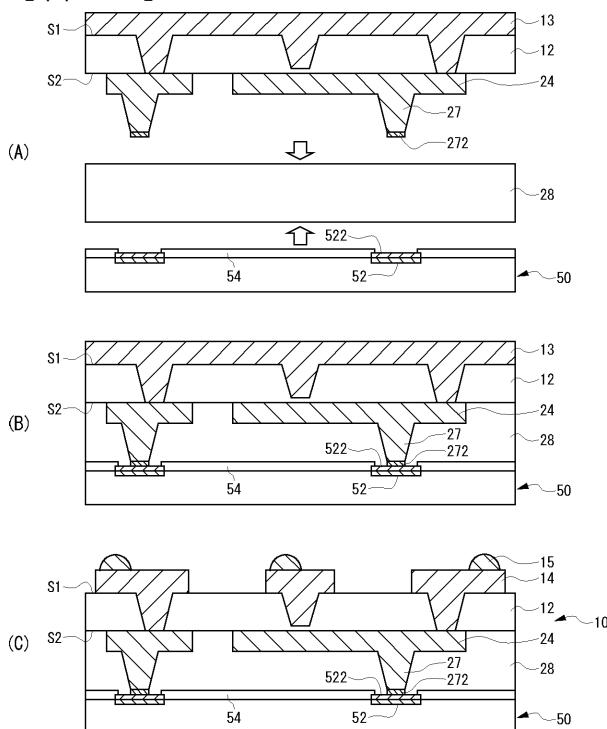

図 9 (A) ~ (G) 、図 10 (A) ~ (D) および図 11 (A) 、(B) は、突起電極 1 6 と対向電極 1 8 との結合方法を示す工程断面図である。30

【0080】

図 9 (A) に示すように、複数の突起電極 1 6 が形成された側の銅板 1 3 の主表面に、リソグラフィ法により、レジスト 7 1 を積層して所定の突起電極 1 6 に対応する位置に開口部 7 1 b を設ける。

【0081】

次に、図 9 (B) に示すように、レジスト 7 1 をマスクとして、開口部 7 1 b において露出している突起電極 1 6 の頂部をエッティングすることにより、突起電極 1 6 の一部を除去する。これにより一部が除去された突起電極 1 6 a の銅板 1 3 からの突出長さを、他の突起電極 1 6 b の銅板 1 3 からの突出長さよりも短くする。そして、レジスト 7 1 を除去する。40

【0082】

次に、図 9 (C) に示すように、銅板 1 3 を絶縁樹脂層 1 2 の一方の主表面 S 1 側に配置し、突起電極 1 6 が形成された側の銅板 1 3 の主表面に絶縁樹脂層 1 2 を圧着する。

【0083】

次に、図 9 (D) に示すように、銅板 1 3 に圧着した絶縁樹脂層 1 2 の他方の主表面 S 2 側をエッティングして、突起電極 1 6 b の頂部面 1 6 1 を露出させる。

【0084】

次に、図 9 (E) に示すように、絶縁樹脂層 1 2 の他方の主表面 S 2 側に銅板 2 3 を積層する。銅板 2 3 の積層は、たとえば電解めっき法あるいは無電解めっき法により行う。50

銅板 23 の厚さは、配線層 24 と略同一の厚さである。

【0085】

次に、図 9 (F) に示すように、絶縁樹脂層 12 と反対側の銅板 23 の主表面に、他の配線層である配線層 24 のパターンに合わせてレジスト 74 を選択的に形成する。

【0086】

次に、図 9 (G) に示すように、レジスト 74 をマスクとして銅板 23 をエッチングすることにより、所定の配線パターンを有する配線層 24 を形成する。その後、レジスト 74 を除去する。

【0087】

次に、図 10 (A) に示すように、絶縁樹脂層 12 と反対側の配線層 24 の主表面に、リソグラフィ法により、レジスト 75 を積層して配線層 24 に対応する所定位置に開口部 75a を設ける。

10

【0088】

次に、図 10 (B) に示すように、開口部 75a 内に電極 26 を形成する。電極 26 は、たとえば電解めっき法あるいは無電解めっき法により形成する。その後、電極 26 の頂部面 261 に金属層 262 を形成し、レジスト 75 を除去する。

【0089】

次に、図 10 (C) に示すように、半導体素子 50 を、絶縁樹脂層 12 と同一の材料からなる絶縁樹脂層 28 の一方の主表面側に配置し、銅板 13 を絶縁樹脂層 28 の他方の主表面側に配置する。そして銅板 13 と半導体素子 50 とを、絶縁樹脂層 28 を介して圧着することにより、図 10 (D) に示すように銅板 13、絶縁樹脂層 28 および半導体素子 50 を一体化する。

20

【0090】

次に、図 11 (A) に示すように、リソグラフィ法により、配線層 14 のパターンに合わせてレジスト 72 を選択的に形成する。

【0091】

次に、図 11 (B) に示すように、レジスト 72 をマスクとして銅板 13 をエッチングすることにより、所定の配線パターンを有する配線層 14 を形成する。そして、レジスト 72 を除去し、配線層 14 の所定の位置にはんだバンプ 15 を形成する。

30

【0092】

以上説明した製造工程により、半導体モジュール 30 が形成される。また、半導体素子 50 を圧着しない状態であれば、素子搭載用基板 10 が得られる。

【0093】

本実施形態では、配線層 14 に設けられた突起電極 16a と、絶縁樹脂層 12 の他方の主表面 S2 に設けられた配線層 24 との間で容量結合を形成している。すなわち、対向電極 18 が、絶縁樹脂層 12 の他方の主表面 S2 に設けられた配線層 24 の一部となっている。

【0094】

本実施形態によれば、実施形態 1 の上述の効果に加えて、さらに次のような効果が得られる。すなわち、本実施形態に示すように、突起電極 16a と配線層 24 との間にキャパシタを形成することができるため、キャパシタを一体的に形成した多層構造の素子搭載用基板 10 および半導体モジュール 30 を形成することができる。

40

【0095】

(実施形態 5)

本実施形態は、対向電極 18 が、絶縁樹脂層 12 の他方の主表面 S2 に設けられた他の配線層の一部である構成の例であるが、実施形態 4 と製造工程が異なる。以下、本実施形態について説明する。なお、突起電極 16 の形成方法については、実施形態 1 と同様である。また、実施形態 1 ないし 4 と同一の構成については同一の符号を付し、その説明は省略する。

【0096】

50

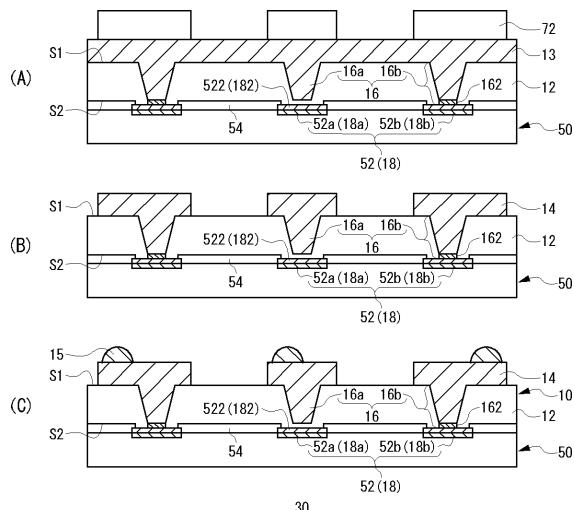

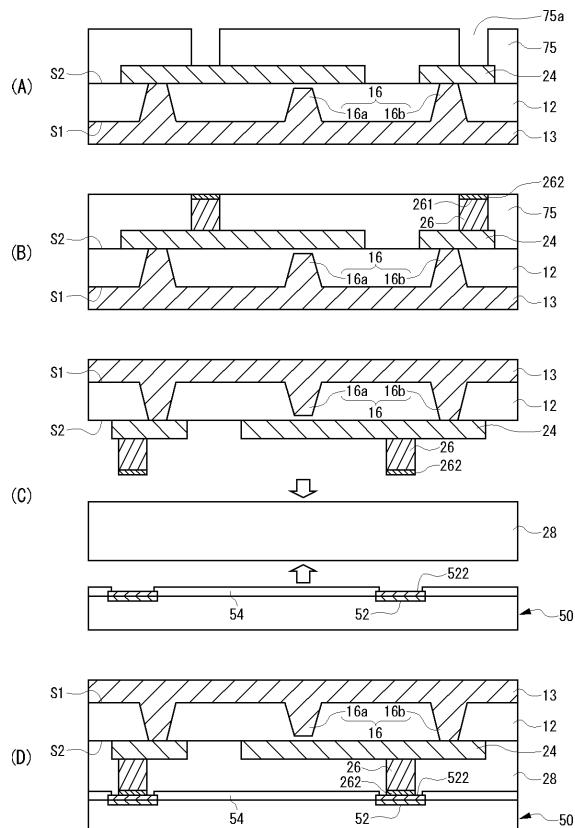

図12(A)～(F)、図13(A)～(E)および図14(A)～(C)は、突起電極16と対向電極18との結合方法を示す工程断面図である。

【0097】

図12(A)に示すように、複数の突起電極16が形成された側の銅板13の主表面に、リソグラフィ法により、レジスト71を積層して所定の突起電極16に対応する位置に開口部71bを設ける。

【0098】

次に、図12(B)に示すように、レジスト71をマスクとして、開口部71bにおいて露出している突起電極16の頂部をエッチングすることにより、突起電極16の一部を除去する。これにより一部が除去された突起電極16aの銅板13からの突出長さを、他の突起電極16bの銅板13からの突出長さよりも短くする。そして、レジスト71を除去する。

10

【0099】

次に、図12(C)に示すように、銅板13を絶縁樹脂層12の一方の主表面S1側に配置し、突起電極16が形成された側の銅板13の主表面に絶縁樹脂層12を圧着する。

【0100】

次に、図12(D)に示すように、銅板13に圧着した絶縁樹脂層12の他方の主表面S2側をエッチングして、突起電極16bの頂部面161を露出させる。

20

【0101】

次に、図12(E)に示すように、絶縁樹脂層12の他方の主表面S2側に銅板25を積層する。銅板25の積層は、たとえば電解めっき法あるいは無電解めっき法により行う。銅板25の厚さは、少なくとも、後述する電極27の高さと配線層24の厚さとの和より大きい厚さである。

【0102】

次に、図12(F)に示すように、リソグラフィ法により、電極27のパターンに合わせてレジスト76を選択的に形成する。

30

【0103】

次に、図13(A)に示すように、レジスト76をマスクとして、銅板25に所定のパターンの電極27を形成する。

【0104】

次に、図13(B)に示すように、絶縁樹脂層12と反対側の銅板25の主表面に、他の配線層である配線層24のパターンに合わせてレジスト77を選択的に形成する。

30

【0105】

次に、図13(C)に示すように、レジスト77をマスクとして銅板25をエッチングすることにより、所定の配線パターンを有する配線層24を形成する。その後、レジスト77を除去する。

40

【0106】

次に、図13(D)に示すように、絶縁樹脂層12と反対側の配線層24の主表面に、リソグラフィ法により、レジスト78を積層して電極27に対応する所定位置に開口部78aを設ける。

【0107】

次に、図13(E)に示すように、開口部78aにおいて露出している電極27の頂部面に、金属層272を形成し、レジスト78を除去する。

【0108】

次に、図14(A)に示すように、半導体素子50を、絶縁樹脂層12と同一の材料からなる絶縁樹脂層28の一方の主表面側に配置し、銅板13を絶縁樹脂層28の他方の主表面側に配置する。そして銅板13と半導体素子50とを、絶縁樹脂層28を介して圧着することにより、図14(B)に示すように銅板13、絶縁樹脂層28および半導体素子50を一体化する。

【0109】

50

次に、図14( C )に示すように、リソグラフィ法により、配線層14のパターンに合わせてレジスト( 図示せず )を選択的に形成し、銅板13をエッティングすることにより、所定の配線パターンを有する配線層14を形成する。そして、レジストを除去し、配線層14の所定の位置にはんだバンプ15を形成する。

#### 【 0 1 1 0 】

以上説明した製造工程により、半導体モジュール30が形成される。また、半導体素子50を圧着しない状態であれば、素子搭載用基板10が得られる。

#### 【 0 1 1 1 】

本実施形態では、配線層14に設けられた突起電極16aと、絶縁樹脂層12の他方の主表面S2に設けられた配線層24との間で容量結合を形成している。すなわち、対向電極18が、絶縁樹脂層12の他方の主表面S2に設けられた配線層の一部となっている。

10

#### 【 0 1 1 2 】

以上、本実施形態に示した方法によっても、キャパシタが一体的に形成された多層構造の素子搭載用基板10および半導体モジュール30を形成することができる。

#### 【 0 1 1 3 】

##### ( 実施形態6 )

本実施形態は、突起電極16の形成方法が実施形態1ないし5と異なる。以下、本実施形態について説明する。なお、突起電極16と対向電極18との結合方法については、実施形態1ないし5と同様である。また、実施形態1ないし5と同一の構成については同一の符号を付し、その説明は省略する。

20

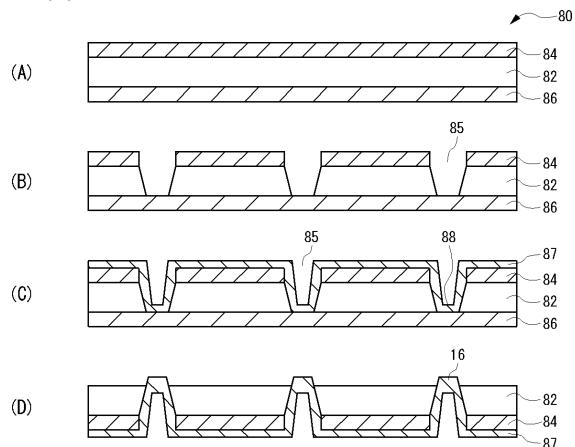

#### 【 0 1 1 4 】

図15( A )～( D )は、突起電極16の形成方法を示す工程断面図である。

#### 【 0 1 1 5 】

図15( A )に示すように、絶縁性の樹脂からなる樹脂層82と、樹脂層82の一方の主表面に形成された第1の金属層84と、他方の主表面側に形成された第2の金属層86とを有するコア基材80を用意する。第1の金属層84および第2の金属層86は、たとえば銅( Cu )などからなる。

20

#### 【 0 1 1 6 】

次に、図15( B )に示すように、たとえば第1の金属層84側からレーザを照射して、第2の金属層86が露出するまで第1の金属層84および樹脂層82の一部を除去し、開口部85を形成する。ここで、レーザ照射には、たとえば炭酸ガスレーザを用いることができる。開口部85は、突起電極16のパターンに合わせて形成する。

30

#### 【 0 1 1 7 】

次に、図15( C )に示すように、電解めっき法あるいは無電解めっき法などにより、開口部85の内面に、たとえば銅( Cu )などの金属をめっきして、金属めっき層87を形成する。これにより開口部85内部にピア導体88が形成され、ピア導体88を介して第1の金属層84と第2の金属層86とが導通される。また、第1の金属層84に金属めっき層87が積層された結果、第1の金属層84と金属めっき層87の合計の層厚が配線層の厚さ以上に調整される。

40

#### 【 0 1 1 8 】

次に、図15( D )に示すように、第2の金属層86と、樹脂層82の一部をエッティングにより除去する。これにより、樹脂層82に突起電極16が形成される。

#### 【 0 1 1 9 】

以上、本実施形態に示した方法によって形成された突起電極16を用いても、本発明の素子搭載用基板10および半導体モジュール30を形成することができる。

#### 【 0 1 2 0 】

##### ( 実施形態7 )

次に、本発明の半導体モジュールを備えた携帯機器について説明する。なお、携帯機器として携帯電話に搭載する例を示すが、たとえば、個人用携帯情報端末( PDA )、デジタルビデオカメラ( DVC )、及びデジタルスチルカメラ( DSC )といった電子機器で

50

あってもよい。

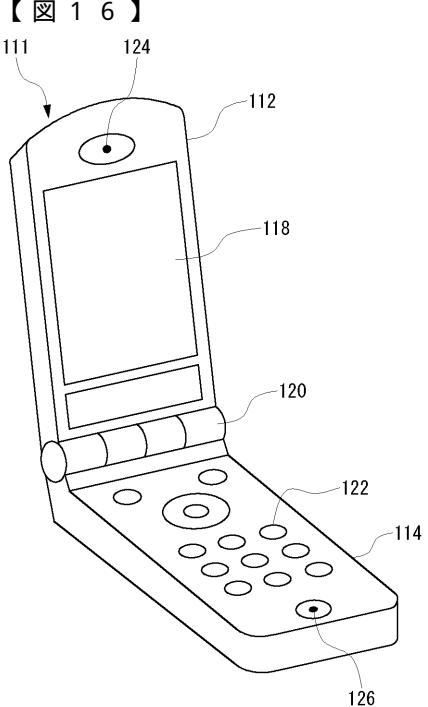

**【0121】**

図16は本発明の実施形態に係る半導体モジュール30を備えた携帯電話の構成を示す図である。携帯電話111は、第1の筐体112と第2の筐体114が可動部120によって連結される構造になっている。第1の筐体112と第2の筐体114は可動部120を軸として回動可能である。第1の筐体112には文字や画像等の情報を表示する表示部118やスピーカ部124が設けられている。第2の筐体114には操作用ボタンなどの操作部122やマイク部126が設けられている。なお、本発明の各実施形態に係る半導体モジュール30はこうした携帯電話111の内部に搭載されている。

**【0122】**

図17は図16に示した携帯電話の部分断面図（第1の筐体112の断面図）である。本発明の各実施形態に係る半導体モジュール30は、はんだバンプ15を介してプリント基板128に搭載され、こうしたプリント基板128を介して表示部118などと電気的に接続されている。また、半導体モジュール30の裏面側（はんだバンプ15とは反対側の面）には金属基板などの放熱基板116が設けられ、たとえば、半導体モジュール30から発生する熱を第1の筐体112内部に蓄もらすことなく、効率的に第1の筐体112の外部に放熱することができるようになっている。

**【0123】**

本発明の各実施形態に係る半導体モジュール30は、小型化が可能であり、また製造コストの削減ができるため、こうした半導体モジュール30を搭載した本実施形態に係る携帯機器についても、その小型化、製造コストの削減が可能となる。

**【0124】**

本発明は、上述の各実施形態に限定されるものではなく、当業者の知識に基づいて各種の設計変更等の変形を加えることも可能であり、そのような変形が加えられた実施形態も本発明の範囲に含まれうるものである。

**【0125】**

たとえば、上述の各実施形態では、素子搭載用基板の配線層は単層あるいは二層であったが、これに限定されず、配線層はさらに多層化したものであってもよい。また、配線層の最外面にはんだバンプが形成されているが、これに限定されない。たとえば、配線層にMOSトランジスタを接着し、MOSトランジスタのソース電極、ドレイン電極およびゲート電極を配線層に電気的に接続してもよい。

**【図面の簡単な説明】**

**【0126】**

【図1】実施形態1に係る素子搭載用基板および半導体モジュールの構成を示す概略断面図である。

【図2】突起電極の形成方法を示す工程断面図である。

【図3】突起電極と、対向電極あるいは素子電極との結合方法を示す工程断面図である。

【図4】突起電極と、対向電極あるいは素子電極との結合方法を示す工程断面図である。

【図5】実施形態2に係る突起電極と、対向電極あるいは素子電極との結合方法を示す工程断面図である。

【図6】突起電極と、対向電極あるいは素子電極との結合方法を示す工程断面図である。

【図7】実施形態3に係る突起電極と、対向電極あるいは素子電極との結合方法を示す工程断面図である。

【図8】突起電極と、対向電極あるいは素子電極との結合方法を示す工程断面図である。

【図9】実施形態4に係る突起電極と対向電極との結合方法を示す工程断面図である。

【図10】突起電極と対向電極との結合方法を示す工程断面図である。

【図11】突起電極と対向電極との結合方法を示す工程断面図である。

【図12】実施形態5に係る突起電極と対向電極との結合方法を示す工程断面図である。

【図13】突起電極と対向電極との結合方法を示す工程断面図である。

【図14】突起電極と対向電極との結合方法を示す工程断面図である。

10

20

30

40

50

【図15】実施形態6に係る突起電極の形成方法を示す工程断面図である。

【図16】実施形態7に係る半導体モジュールを備えた携帯電話の構成を示す図である。

【図17】携帯電話の部分断面図である。

【符号の説明】

【0127】

10 素子搭載用基板、12 絶縁樹脂層、14 配線層、15 はんだバンプ

、16、16a、16b 突起電極、18、18a、18b 対向電極、30 半

導体モジュール、50 半導体素子、52、52a、52b 素子電極、54 保

護層、162 金属層。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

30

【図9】

【図10】

【図 1 1】

30

【図 1 2】

【図 1 3】

【図 1 4】

30

【図 1 5】

【図 1 6】

【図 1 7】