(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5068444号

(P5068444)

(45) 発行日 平成24年11月7日(2012.11.7)

(24) 登録日 平成24年8月24日(2012.8.24)

(51) Int.Cl.

F 1

G06F 12/00 (2006.01)

G06F 12/06 (2006.01)G06F 12/00 564A

G06F 12/06 51OB

請求項の数 10 (全 15 頁)

(21) 出願番号 特願2005-310377 (P2005-310377)

(22) 出願日 平成17年10月25日 (2005.10.25)

(65) 公開番号 特開2006-127515 (P2006-127515A)

(43) 公開日 平成18年5月18日 (2006.5.18)

審査請求日 平成20年10月24日 (2008.10.24)

(31) 優先権主張番号 10-2004-0085381

(32) 優先日 平成16年10月25日 (2004.10.25)

(33) 優先権主張国 韓国 (KR)

(73) 特許権者 390019839

三星電子株式会社

Samsung Electronics

Co., Ltd.

大韓民国京畿道水原市靈通区三星路129

129, Samsung-ro, Yeongtong-gu, Suwon-si, Gyeonggi-do, Republic

of Korea

(74) 代理人 100064908

弁理士 志賀 正武

(74) 代理人 100089037

弁理士 渡邊 隆

(74) 代理人 100108453

弁理士 村山 靖彦

最終頁に続く

(54) 【発明の名称】メモリモジュール内でのインターフェースタイミングを制御するメモリシステム及びタイミング制御方法

## (57) 【特許請求の範囲】

## 【請求項1】

データを保存する複数のメモリ装置と、メモリ情報及びメモリ信号情報によって前記複数のメモリ装置と関連したインターフェースタイミングを制御するメモリモジュール制御部と、を備えるメモリモジュールと、

一つ以上の入力／出力装置と連結され、前記メモリモジュールから前記メモリ情報を受信するインターフェース制御部と、

前記インターフェース制御部から前記メモリ情報を受信し、前記メモリ情報及び前記メモリ信号情報を前記メモリモジュールに提供するメモリ制御部と、を備え、

前記メモリ情報は、メモリ初期化情報及び前記複数のメモリ装置のインターフェースタイミング情報を含むことを特徴とするメモリシステム。

10

## 【請求項2】

前記メモリモジュールは、

前記メモリ情報を保存し、前記メモリ情報を前記インターフェース制御部に提供するメモリ情報保存部をさらに備えることを特徴とする請求項1に記載のメモリシステム。

## 【請求項3】

前記メモリモジュール制御部は、

前記メモリ制御部から前記メモリ信号情報を受信する送受信部と、

前記メモリ制御部から提供された前記メモリ情報を検出するメモリ情報検出部と、

前記メモリ情報及び前記メモリ信号情報をを利用して、メモリ信号のタイミングを発生さ

20

せて制御するメモリ装置制御部と、

前記複数のメモリ装置と前記メモリモジュール制御部とを連結するメモリインターフェース部と、を備えることを特徴とする請求項 2 に記載のメモリシステム。

【請求項 4】

前記メモリ装置制御部は、

前記メモリ信号情報を利用して前記メモリ信号を発生させるメモリ信号発生部と、

前記メモリ情報と関連した前記メモリ信号のタイミングを制御するメモリ信号タイミング制御部と、

前記メモリ信号をバッファリングして、前記メモリ信号を前記メモリインターフェース部に提供するメモリ信号バッファ部と、を備えることを特徴とする請求項 3 に記載のメモリシステム。 10

【請求項 5】

前記メモリ信号タイミング制御部は、

前記インターフェースタイミング情報に応答してクロック信号のタイミングを制御するクロック信号タイミング制御部と、

前記インターフェースタイミング情報に応答して命令信号のタイミングを制御する命令信号タイミング制御部と、

前記インターフェースタイミング情報に応答してアドレス信号のタイミングを制御するアドレスタイミング制御部と、

前記インターフェースタイミング情報に応答してデータストローブ信号のタイミングを制御するデータストローブタイミング制御部と、を備えることを特徴とする請求項 4 に記載のメモリシステム。 20

【請求項 6】

前記インターフェースタイミング情報は、

クロック信号タイミング情報、命令信号タイミング情報、アドレス信号タイミング情報、及びデータストローブ信号タイミング情報を備えることを特徴とする請求項 5 に記載のメモリシステム。

【請求項 7】

前記メモリ信号バッファ部は、

前記クロック信号をバッファリングして、前記クロック信号を前記メモリインターフェース部に供給するクロック信号バッファ部と、

前記命令信号をバッファリングして、前記命令信号を前記メモリインターフェース部に供給する命令信号バッファ部と、

前記アドレス信号をバッファリングして、前記アドレス信号を前記メモリインターフェース部に供給するアドレスバッファ部と、

前記データストローブ信号をバッファリングして、前記データストローブ信号を前記メモリインターフェース部に供給するデータストローブバッファ部と、を備えることを特徴とする請求項 6 に記載のメモリシステム。 30

【請求項 8】

前記メモリモジュールは、

インターフェースタイミング情報を保存して、前記インターフェースタイミング情報を前記インターフェース制御部に提供する追加メモリ情報保存部をさらに備えることを特徴とする請求項 7 に記載のメモリシステム。 40

【請求項 9】

メモリ情報保存部及びメモリモジュール制御部を備えるメモリモジュールに装着された複数のメモリ装置と関連したインターフェースタイミングを制御する方法において、

メモリ制御部または前記メモリ情報保存部が、前記メモリ情報保存部に保存されたメモリ情報を前記メモリモジュール制御部に提供するステップと、

送受信部が、メモリ制御部により提供されたメモリ信号情報を受信するステップと、

メモリ装置制御部が、前記メモリ信号情報に応答してメモリ信号を発生させるステップ。 50

と、

前記メモリ装置制御部が、前記メモリ情報及び前記メモリ信号情報を利用して前記メモリ信号のタイミングを制御するステップであり、前記メモリ情報は、メモリ初期化情報及び前記複数のメモリ装置のインターフェースタイミング情報を含む、前記メモリ信号のタイミングを制御するステップと、

メモリインターフェース部が、前記メモリ信号を前記複数のメモリ装置に提供するステップと、を含み、

前記送受信部と前記メモリ装置制御部と前記メモリインターフェース部とは、前記メモリモジュール制御部に備えられていることを特徴とするタイミング制御方法。

【請求項 10】

10

前記メモリ制御部または前記メモリ情報保存部が、前記メモリ情報保存部に保存されたメモリ情報を前記メモリモジュール制御部に提供するステップは、

前記メモリ制御部または前記メモリ情報保存部が、追加メモリ情報保存部に保存されたインターフェースタイミング情報を前記メモリモジュール制御部に提供するステップをさらに含むことを特徴とする請求項 9 に記載のタイミング制御方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、複数のメモリ装置を備えるメモリモジュールを備えるメモリシステムに関する。さらに詳細に、本発明は、メモリ情報保存部にタイミング調節情報を保存することによってメモリ装置のインターフェースタイミングを調節できるメモリシステムに関する。

20

【背景技術】

【0002】

本発明は、特許文献 1 に対する優先権の利益を主張し、前記特許文献 1 に開示された内容全体は、本明細書内で参照として含まれる。

【0003】

コンピュータシステムの性能は向上し続けており、このような性能向上と共にメモリシステムの設計に当っても変化しつつある。現在大部分のメモリシステムは複数のメモリモジュールを備えており、現在大部分のメモリモジュールは複数のメモリ装置を備える。従来のメモリモジュールには、S I M M ( S i n g l e I n - l i n e M e m o r y M o d u l e ) 、 D I M M ( D u a l I n - l i n e M e m o r y M o d u l e ) 、 F B D I M M ( F u l l y B u f f e r e d D I M M ) などがある。

30

【0004】

S I M M は、D R A M ( D y n a m i c R a n d o m A c c e s s M e m o r y ) またはS D R A M ( S y n c h r o n o u s D y n a m i c R a n d o m A c c e s s M e m o r y ) のような一つ以上のR A M ( R a n d o m A c c e s s M e m o r y ) チップが装着される小さなP C B ( P r i n t e d C i r c u i t B o a r d ) である。また、S I M M は、コンピュータマザーボードとの連結に利用されるピンを備える。D I M M は普通 2 個のS I M M を備え、D I M M も小さなP C B 及びマザーボード連結ピンに付着される複数のR A M チップを備える。

40

【0005】

一般的なS I M M の 3 2 ビット幅のデータワードを記録 / 再生し、たびたび 7 2 ピンコネクタを備えるシステム内に使われることもある。D I M M は、6 4 ビット幅のデータを記録 / 再生し、1 6 8 ピンコネクタを備えるシステムに使われる。現在のS D R A M は 6 4 ビット幅のデータを記録 / 再生し、したがって、S D R A M は少なくとも 2 つのS I M M または一つのD I M M が必要である。

【0006】

一般的なD I M M は、D I M M 外部のメモリ制御部により制御される。例示的なシステムで、C P U に連結されたノースブリッジ ( N o r t h B r i d g e : N B ) がメモリ制御部の役割を行える。しかし、外部制御部の使用は、動作速度を減少させてD I M M の

50

性能を制限する。

#### 【0007】

FBDIMMは、このような問題点を解決するためのメモリモジュールである。FBDIMMは、メモリモジュール内に装着される制御部を備え、AMB (Advanced Memory Buffer) を備えることができるメモリモジュールの動作を制御するように適用される。

#### 【0008】

前述したように、複数のメモリ装置がメモリモジュール（特に、DIMM / FBDIMM）に使われ、複数のメモリモジュールがメモリシステムに使われるために、メモリシステム内のメモリモジュールに / からデータを適切に記録 / 再生するために、メモリモジュール及びメモリモジュール内のメモリ装置を初期化してタイミングを設定する必要がある。

10

#### 【0009】

従来には、メモリ初期化及びタイミング情報を含むメモリ情報は、メモリモジュールと関連したSPD (Serial Presence Detect) のようなメモリ情報保存部に保存される。メモリ制御部は、SPDに保存されたメモリ情報を収集して、メモリ制御部がメモリモジュールを初期化するかテストする場合、収集されたメモリ情報をを利用してメモリモジュールを初期化するか、タイミングを設定する。

SPDは、メモリモジュール及び / またはメモリ装置と関連した情報を保存し、メモリモジュール内に位置する。SPDに保存された情報は、メモリモジュール及び / またはメモリ装置の速度、電圧、ロー / カラムアドレス、リフラッシュレート、ACパラメータ（クロックサイクル時間t<sub>CC</sub>、CAS遅延時間t<sub>CL</sub>、RAS - CAS遅延時間t<sub>RCD</sub>、ローフリー次知時間t<sub>RP</sub>）、製作者など、メモリモジュールについての全般的な情報を含む。

20

#### 【0010】

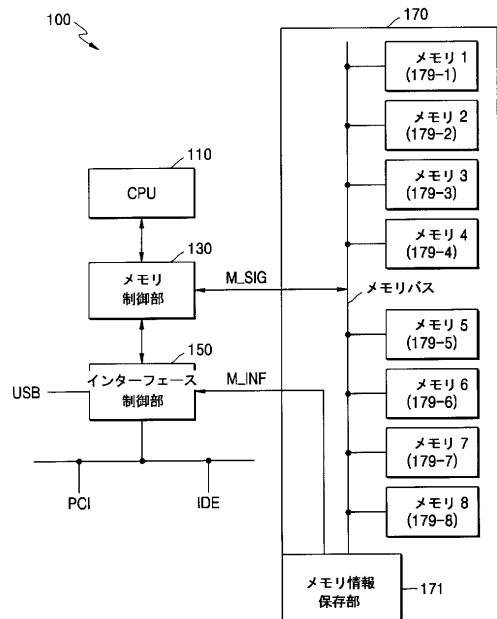

図1は、メモリモジュールを備える例示的なメモリシステムのロックダイアグラムである。

図1に図示されたメモリシステム100は、CPU 110、メモリ制御部130、インターフェース制御部150、及びメモリモジュール170を備える。インターフェース制御部150は、メモリモジュール170内のメモリ情報保存部171に保存されたメモリ情報M\_INFを読み出してメモリ制御部130に提供する。メモリ制御部130は、インターフェース制御部150から伝送されたメモリ情報M\_INFを内部のメモリタイミングレジスタに保存しておき、それを利用してメモリモジュール170を初期化してメモリモジュールのタイミングを設定する。その後、メモリ制御部130は、クロック信号CLK、命令信号CMD、アドレス信号ADD、データストローブ信号DQSなどを備えるメモリ信号M\_SIGをメモリ装置179-1ないし179-8に提供する。

30

#### 【0011】

コンピュータシステムで、メモリ制御部130は、CPUをメモリモジュールとAGP (Accelerated Graphics Port) 及びPCI (Peripheral Component Interconnect) バスに連結するNB内に具現でき、インターフェース制御部150は、IDE (Integrated Drive Electronics) バス、USB (Universal Serial BUS)、プラグアンドプレイ支援、キーボード / マウスコントローラ、電源管理などの機能を制御するサウスブリッジ (South Bridge : SB) 内に具現されることもある。

40

#### 【0012】

コンピュータシステムで具現される場合には、SBがメモリ情報保存部171からメモリ情報M\_INFを読み出した後、NBにインタラプトを要請すれば、NBは、インタラプト要請に応答して現在実行中の動作をしばらく中断してSBからメモリ情報M\_INFを受信し、それを内部のメモリタイミングレジスタに保存した後、中断された動作を再び行う。

50

**【0013】**

しかし、一般的なメモリシステム100では、外部のメモリ制御部130に保存されたメモリタイミング情報を利用してメモリモジュール170が初期化され、かつメモリタイミングが設定されるために、メモリモジュールの初期化に長時間がかかり、メモリ装置のインターフェースタイミングを調節し難い。

**【0014】**

多様なメモリ装置が開発される現在の勢いによって、メモリモジュールはセットアップタイム及びホールドタイムのようなインターフェースタイミングの相異なる多様なメモリ装置を使用せねばならない。したがって、メモリシステムの誤動作を防止するために、他のインターフェースタイミングを適切に制御する必要がある。

10

【特許文献1】韓国特許出願第10-2004-0085381号（2004年10月25日出願）

**【発明の開示】****【発明が解決しようとする課題】****【0015】**

前述したように、メモリモジュールの初期化に長時間がかかり、メモリ装置のインターフェースタイミングを調節し難いので、メモリシステムの誤動作を防止するために他のインターフェースタイミングを適切に制御する必要がある。

**【0016】**

前述した問題点を解決するために、本発明は、メモリ情報保存部にタイミング調節情報を保存することによって、メモリ装置のインターフェースタイミングを調節できるメモリシステムを提供する。

20

**【課題を解決するための手段】****【0017】**

本発明の実施形態によるメモリシステムは、データを保存する複数のメモリ装置と、メモリ情報及びメモリ信号情報によって前記複数のメモリ装置と関連したインターフェースタイミングを制御するメモリモジュール制御部と、を備えるメモリモジュールと、一つ以上の入力／出力（I/O）装置と連結され、前記メモリモジュールから前記メモリ情報を受信するインターフェース制御部と、前記インターフェース制御部から前記メモリ情報を受信し、前記メモリ情報及び前記メモリ信号情報を前記メモリモジュールに提供するメモリ制御部と、を備え、前記メモリ情報は、メモリ初期化情報及び前記複数のメモリ装置のインターフェースタイミング情報を含む。

30

**【0018】**

本発明の他の実施形態によるメモリシステムは、データを保存する複数のメモリ装置、メモリ情報を保存し、前記メモリ情報をメモリモジュール制御部に提供するメモリ情報保存部、及び前記メモリ情報及びメモリ信号情報によって前記複数のメモリ装置と関連されたインターフェースタイミングを制御するメモリモジュール制御部を備えるメモリモジュールと、前記メモリモジュールと一つ以上のI/O装置との連結を制御するインターフェース制御部と、前記メモリ信号情報を前記メモリモジュールに提供するメモリ制御部と、を備え、前記メモリ情報は、メモリ初期化情報及び前記複数のメモリ装置のインターフェースタイミング情報を含む。

40

**【0019】**

本発明の実施形態によるタイミング制御方法は、メモリ情報保存部及びメモリモジュール制御部を備えるメモリモジュールに装着された複数のメモリ装置と関連したインターフェースタイミングを制御し、前記メモリ情報保存部に保存されたメモリ情報をインターフェース制御部に提供するステップと、前記メモリ情報をメモリ制御部に提供するステップと、前記メモリ情報及びメモリ信号情報を前記メモリモジュール制御部に提供するステップと、前記メモリ信号情報に応答してメモリ信号を発生させるステップと、前記メモリ情報及び前記メモリ信号情報をを利用して前記メモリ信号のタイミングを制御するステップであり、前記メモリ情報は、メモリ初期化情報及び前記複数のメモリ装置のインターフェー

50

タイミング情報を含む、前記メモリ信号のタイミングを制御するステップと、前記メモリ信号を前記複数のメモリ装置に提供するステップと、を含む。

#### 【0020】

本発明の他の実施形態によるタイミング制御方法は、メモリ情報保存部及びメモリモジュール制御部を備えるメモリモジュールに装着された複数のメモリ装置と関連したインターフェースタイミングを制御し、前記メモリ情報保存部に保存されたメモリ情報を前記メモリモジュール制御部に提供するステップと、メモリ制御部により提供されたメモリ信号情報を受信するステップと、前記メモリ信号情報に応答してメモリ信号を発生させるステップと、前記メモリ情報及び前記メモリ信号情報を利用して前記メモリ信号のタイミングを制御するステップであり、前記メモリ情報は、メモリ初期化情報及び前記複数のメモリ装置のインターフェースタイミング情報を含む、前記メモリ信号のタイミングを制御するステップと、前記メモリ信号を前記複数のメモリ装置に提供するステップと、を含む。

10

#### 【発明の効果】

#### 【0021】

本発明の実施形態によるメモリシステム、メモリモジュール、及びメモリ装置のタイミング制御方法は、メモリインターフェースタイミング情報をを利用してメモリ信号のタイミングを調節し、メモリ装置のインターフェースタイミングを調節することによって相異なるインターフェースタイミング特性を持つメモリ装置についてもメモリの量産が可能である。

#### 【0022】

また、本発明の実施形態によるメモリシステム、メモリモジュール、及びメモリ装置のタイミング制御方法は、メモリ装置のインターフェースタイミングを調節して誤動作するメモリ装置のタイミングを調節することによって、メモリ装置のデバッグ作業などを容易に行える。

20

#### 【発明を実施するための最良の形態】

#### 【0023】

以下、本発明の例示的な実施形態は、図面を参照してさらに詳細に説明される。図面全体を通じて同じ参考番号は同じ部材を表す。

#### 【0024】

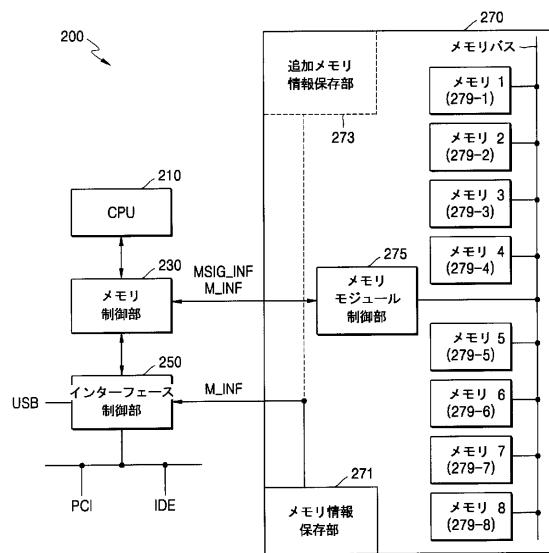

図2は、本発明の実施形態によるメモリシステム200のブロック図である。

30

メモリシステム200は、メモリモジュール270、メモリ制御部230、及びインターフェース制御部250を備える。インターフェース制御部250は、メモリモジュール270に保存されたメモリ情報M\_INFを受信してメモリ制御部230に提供する。メモリ制御部230は、メモリ情報M\_INF及びメモリ信号情報MSG\_INFをメモリモジュール270に伝送する。メモリ制御部230からメモリモジュール270にデータを提供する方式として、従来の並列方式の代わりにパケット形態のシリアル方式が利用される。

#### 【0025】

メモリ情報M\_INFは、メモリ初期化情報とクロック信号CLK、命令信号CMD、アドレス信号ADD、データストローブ信号DQSなどのタイミングを制御するためのメモリ装置のインターフェースタイミング情報を含む。

40

#### 【0026】

図1の従来技術と同様に、本発明のインターフェース制御部250及びメモリ制御部230は、コンピュータシステムでそれぞれSB及びNB内に具現されうる。この場合、SBは、メモリモジュール270からメモリ情報M\_INFを読み出した後、NBにメモリ情報M\_INFの提供のためのインタラプトを要請し、NBは、SBからのインタラプト要請に応答して実行中の作業を中断し、メモリ信号情報MSG\_INF及びメモリ情報M\_INFをメモリモジュール270に提供する。

#### 【0027】

メモリモジュール270はメモリ装置279-1ないし279-8、メモリモジュール

50

制御部 275、及びメモリ情報保存部 271を備え、追加メモリ情報保存部 273をさらに備えられる。

**【0028】**

メモリシステムで、メモリモジュール 270はDIMM、望ましくは、FBDIMMである。メモリ装置 279-1ないし 279-8 それぞれは、RAM、望ましくはSDRAMである。メモリ情報保存部 271及びメモリモジュール制御部 275は、それぞれ望ましくはSPD及びAMBである。しかし、本発明はそれに制限されるものではない。

**【0029】**

従来技術と違って、メモリ情報保存部 271は、従来のメモリ情報に追加してメモリ情報 M\_INF の一部として、メモリ装置 279-1ないし 279-8 のインターフェースタイミングを調節するためのインターフェースタイミング情報を保存する。

10

**【0030】**

インターフェースタイミング情報は、メモリ情報保存部 271の領域のうち従来のメモリ情報が保存された領域を除外したメモリ情報保存部 271の使われない領域に保存される。他の方法として、インターフェースタイミング情報のみを保存する追加メモリ情報保存部 273に保存されてもよい。

**【0031】**

メモリ情報 M\_INF は、インターフェース制御部 250 及びメモリ制御部 230 を通じてメモリモジュール制御部 275 に提供される。メモリモジュール制御部 275 は、伝送されたメモリ情報 M\_INF によって内部のメモリタイミングレジスタを設定してメモリモジュール 270 を初期化する。また、メモリモジュール制御部 275 は、伝送されたメモリ信号情報 M\_SIG\_INF を利用してメモリ信号 M\_SIG を発生させる。

20

**【0032】**

メモリ信号 M\_SIG が発生した後、メモリモジュール制御部 275 は、インターフェースタイミング情報をを利用してメモリモジュール内部の信号（メモリ信号 M\_SIG）タイミングを調節する。メモリモジュール制御部 275 で発生してタイミングが調節されたメモリ信号 M\_SIG は、並列にそれぞれのメモリ装置 279-1ないし 279-8 に提供される。

**【0033】**

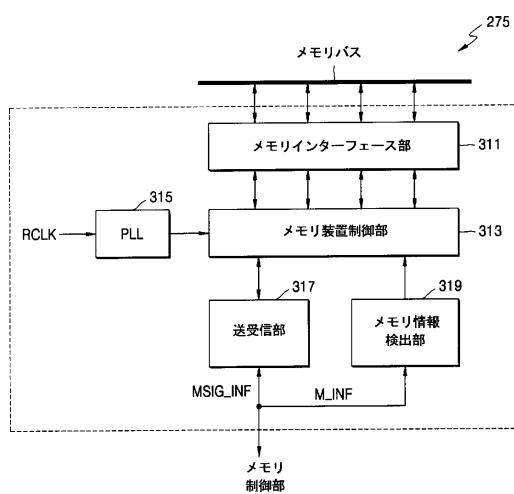

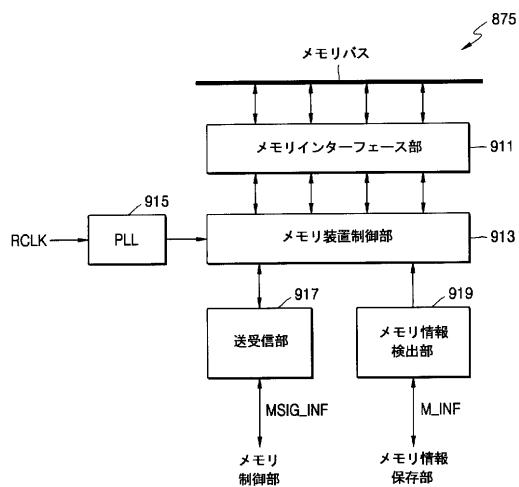

図 3 は、図 2 のメモリモジュール制御部を示すブロック図である。

30

メモリモジュール制御部 275 は、メモリインターフェース部 311、メモリ装置制御部 313、位相同期ループ（Phase Locked Loop：PLL）315、送受信部 317、及びメモリ情報検出部 319 を備える。

**【0034】**

送受信部 317 は、メモリ制御部 230 とメモリモジュール 270 との間に信号を送受信する。一方、メモリ制御部 230 とメモリモジュール 270 との間に送受信される信号は、メモリ情報 M\_INF だけでなく、クロック信号 CLK、命令信号 CMD、アドレス信号 ADD 及びデータストローブ信号 DQS などの信号を発生させるためのメモリ信号情報 M\_SIG\_INF など、メモリの記録 / 再生のためのあらゆる信号を含む。

**【0035】**

メモリ情報検出部 319 は、メモリ制御部 230 から受信された信号のうちメモリ情報 M\_INF を検出してメモリ装置制御部 313 に提供する。メモリ装置制御部 313 は、検出されたメモリ情報 M\_INF 及びメモリ制御部 230 から受信されたメモリ信号情報 M\_SIG\_INF に応答して、それぞれのメモリ装置 279-1ないし 279-8 に提供されるメモリ信号 M\_SIG を制御する。

40

**【0036】**

さらに具体的に、メモリ装置制御部 313 は、内部のメモリタイミングレジスタを設定してメモリ情報 M\_INF によってメモリモジュール 270 を初期化し、メモリ信号情報 M\_SIG\_INF に応答して記録動作または再生動作のためのメモリ信号 M\_SIG を発生させる。また、メモリ装置制御部 313 は、インターフェースタイミング情報を利用し

50

てメモリ信号M\_SIGのタイミングを調節する。

**【0037】**

メモリインターフェース部311は、メモリバスを通じてメモリモジュール制御部275とそれぞれのメモリ装置279-1ないし279-8との間にメモリ信号M\_SIGの通信を提供する。PLL315は、全体システムクロック信号RCLKを利用してメモリモジュールで使われるクロック信号CLKを発生させる。

**【0038】**

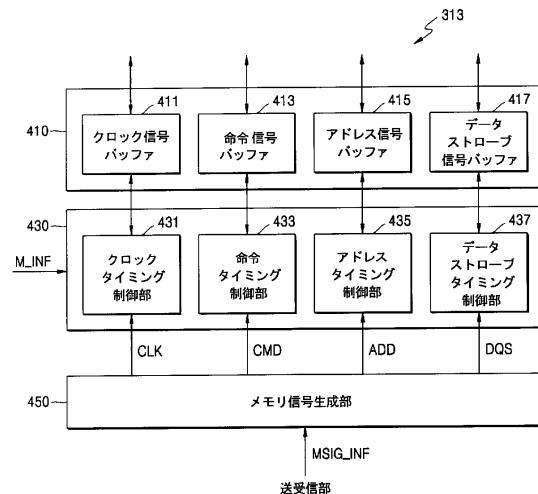

図4は、図3のメモリ装置制御部を示すブロック図である。

メモリ装置制御部313は、メモリ信号発生部450、メモリタイミング制御部430、及びメモリ信号バッファ部410を備える。メモリ信号情報SIG\_INFを利用してメモリ信号発生部450は、メモリ装置279-1ないし279-8に提供されるメモリ信号M\_SIGを発生させる。メモリ信号M\_SIGは、クロック信号CLK、命令信号CMD、アドレス信号ADD、データストローブ信号DQSを含む。

10

**【0039】**

メモリタイミング制御部430は、メモリ情報SIG\_INFを利用してメモリ信号M\_SIGのタイミングを制御する。メモリ信号バッファ部410は、メモリ信号M\_SIGをバッファリングし、メモリタイミング制御部430により提供されるタイミング制御器情報によってメモリ信号M\_SIGのタイミングを調節する。

**【0040】**

メモリタイミング制御部430は、クロック信号タイミング制御部431、命令信号タイミング制御部433、アドレスタイミング制御部435、及びデータストローブタイミング制御部437を備える。

20

**【0041】**

クロック信号タイミング制御部431は、メモリ情報SIG\_INFに含まれたクロック信号タイミング情報をを利用して、PLL315で発生したクロック信号CLKのタイミングを制御する。命令信号タイミング制御部433は、メモリ情報SIG\_INFに含まれた命令信号タイミング情報をを利用して命令信号CMDのタイミングを制御する。アドレスタイミング制御部435は、メモリ情報SIG\_INFに含まれたアドレス信号タイミング情報をを利用して、アドレス信号ADDのタイミングを制御する。データストローブタイミング制御部435は、メモリ情報SIG\_INFに含まれたデータストローブ信号タイミング情報をを利用して、データストローブ信号DQSのタイミングを制御する。

30

**【0042】**

メモリ信号バッファ部410は、クロック信号バッファ部411、命令信号バッファ部413、アドレスバッファ部415、及びデータストローブバッファ部417を備える。クロック信号バッファ部411は、クロック信号制御部431により提供されるクロックタイミング制御器情報によってクロック信号CLKのタイミングを制御して、クロック信号CLKをメモリインターフェース部311に提供する。

**【0043】**

命令信号バッファ部413は、命令信号制御部433により提供される命令タイミング制御器情報によって命令信号CMDのタイミングを制御して、命令信号CMDをメモリインターフェース部311に提供する。アドレス信号バッファ部415は、アドレス制御部435により提供されるアドレスタイミング制御器情報によってアドレス信号ADDのタイミングを制御して、アドレス信号ADDをメモリインターフェース部311に提供する。

40

**【0044】**

データストローブバッファ部417は、データストローブ制御部431により提供されるデータストローブタイミング情報によってデータストローブ信号DQSのタイミングを制御して、データストローブ信号DQSをメモリインターフェース部311に提供する。

**【0045】**

図5は、インターフェースタイミング情報の一例を示す図面である。

50

図5に図示されたインターフェースタイミング情報500は、メモリ情報保存部271に保存される。インターフェースタイミング情報は、クロック信号CLK、命令信号CMD、アドレス信号ADD、及びデータストローブ信号DQS(図示せず)のインターフェースタイミング情報を含む。

#### 【0046】

図5の実施形態で、クロック信号CLKのインターフェースタイミング情報はメモリ情報保存部271の126番目バイトに、命令信号CMDのインターフェースタイミング情報はメモリ情報保存部271の127番目バイトに、そして、アドレス信号ADDのインターフェースタイミング情報はメモリ情報保存部271の128番目バイトにそれぞれ保存される。しかし、インターフェースタイミング情報が保存される位置がそれに制限されるものではない。10

#### 【0047】

メモリ情報保存部271の126番目バイトに保存された値が“0F”である場合をデフォルト値として、クロック信号CLKのインターフェースタイミングが図5に図示された値によって調節される。例えば、メモリ情報保存部271の126番目バイトに保存された値が“0E”である場合、クロック信号CLKのインターフェースタイミングは+100ps(picosecond)ほど調節されて、クロック信号CLKが基準クロック信号に比べて100psほど先立つように調節される。

#### 【0048】

命令信号CMDのインターフェースタイミングも、メモリ情報保存部271の127番目バイトに保存される値が“0F”である場合をデフォルト値として調節される。例えば、保存された値が“10”である場合、命令信号CMDのインターフェースタイミングは-100psほど調節されて、命令信号CMDが基準命令信号に比べて100psほど遅れるように調節される。20

#### 【0049】

図5に示すように、アドレス信号ADDのインターフェースタイミングの調節のために保存された値が“0D”である場合、アドレス信号ADDは+200psほど調節されて、アドレス信号ADDが基準アドレス信号に比べて200psほど先立つように調節される。

#### 【0050】

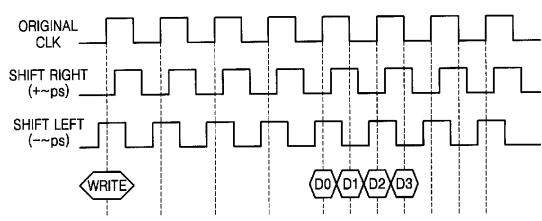

図6は、図5のインターフェースタイミング情報によって制御されるクロック信号のタイミングダイヤグラムである。

図6のタイミングダイヤグラムには、基準クロック信号ORIGINAL CLK、右側に遷移されたクロック信号SHIFT RIGHT、左側に遷移されたクロック信号SHIFT LEFT、及び記録命令WRITEとデータ信号D0ないしD3とが現れている。

メモリ保存装置271に保存された値が“0F”である場合を基準に(ORIGINAL CLK)クロック信号CLKのインターフェースタイミングが調節される。すなわち、“0F”より小さな値が保存された場合にクロック信号CLKは正の遷移量を持ち、クロック信号CLKは右側に遷移される(SHIFT RIGHT)。一方、“0F”より大きい値が保存された場合、クロック信号CLKは負の遷移量を持ち、クロック信号CLKは左側に遷移される(SHIFT LEFT)。40

#### 【0051】

図6で、命令信号である記録命令WRITE及びデータ信号D0ないしD3は、基準クロックORIGINAL CLKに同期されるように設定されている。しかし、命令信号及びデータ信号D0ないしD3は、メモリ装置279-1ないし279-8の初期化にかかる時間及び信号の遅延により基準クロックORIGINAL CLKとの同期が外れる場合が発生でき、このような場合、本発明によってクロック信号CLKのインターフェースタイミングを調節することによって、クロック信号CLKと同期できる。

#### 【0052】

10

20

30

40

50

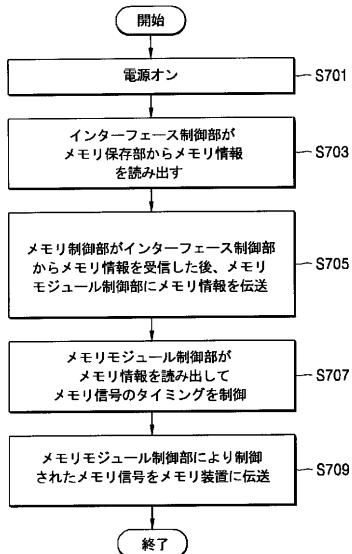

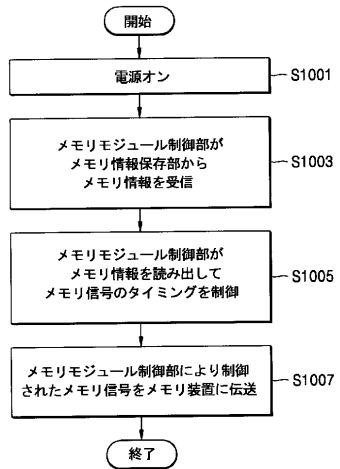

図7は、本発明の実施形態によるメモリモジュール内でのインターフェースタイミング制御方法を示すフロー チャートである。

図7を参照して、メモリ装置279-1ないし279-8に提供されるメモリ信号M\_SI Gのタイミングを調節する方法について詳述する。

#### 【0053】

一旦、電源がオンになれば(S701)、インターフェース制御部250は、メモリ情報保存部271に保存されたメモリ情報M\_INFを読み出した後(S703)、読み出されたメモリ情報M\_INFをメモリ制御部230に提供する。メモリ制御部230は、インターフェース制御部250からメモリ情報M\_INFを受信して、メモリ情報M\_INFをメモリモジュール制御部275に提供する(S705)。

10

#### 【0054】

メモリモジュール制御部275はメモリ情報M\_INFを読み出し、メモリ情報M\_INFを利用してメモリ信号M\_SI Gを発生させ、メモリ信号M\_SI Gのタイミングを制御する(S707)。メモリ制御部275は、メモリバスを通じてメモリ信号M\_SI Gをメモリ装置279-1ないし279-8に伝送する(S709)。

#### 【0055】

一方、メモリモジュール制御部275は、インターフェースタイミング情報をを利用してクロック信号CLK、命令信号CMD、アドレス信号ADD、及びデータストローブ信号DQSのインターフェースタイミングを制御する。

#### 【0056】

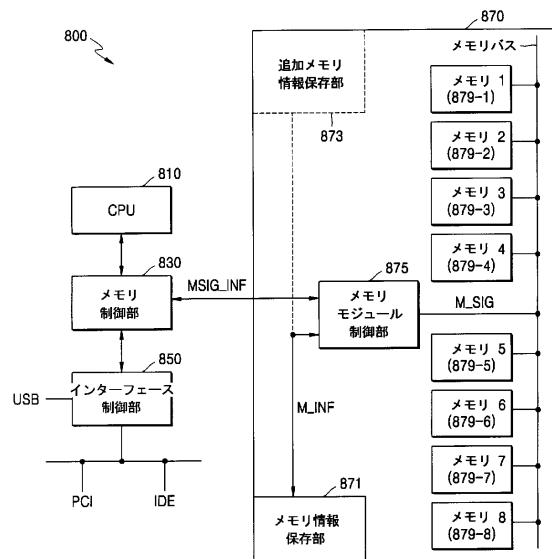

図8は、本発明のさらに他の実施形態によるメモリシステムを示すブロック図である。メモリシステム800は、メモリモジュール制御部875がメモリ情報保存部871からメモリ情報M\_INFを直接受信することを除いて、図2に図示されたメモリシステム200と同じ構成を持つ。本発明の他の実施形態で、メモリモジュール制御部875は、メモリ情報保存部871及び/または追加メモリ情報保存部873からメモリ情報M\_INFを直接受信する。

20

#### 【0057】

メモリ情報保存部871に保存されたメモリ情報M\_INFは、メモリモジュール制御部875がインターフェース制御部850及びメモリ制御部830を通じてメモリ情報保存部871からメモリ情報M\_INFを受信する過程なく、メモリモジュール制御部875に直接提供される。

30

#### 【0058】

図9は、図8のメモリモジュール制御部を示すブロック図である。

メモリモジュール制御部875は、メモリ情報検出部919がメモリ情報M\_INFをメモリ制御部830ではないメモリ情報保存部871から直接受信することを除いては、図2のメモリモジュール制御部275と構成が同一である。

#### 【0059】

したがって、メモリ情報M\_INFは、メモリインターフェース制御部850及びメモリ制御部830を通じてメモリモジュール制御部875に提供されるものではなく、メモリ情報保存部871からメモリモジュール制御部875に直接提供される。メモリ情報検出部919は、メモリ情報保存部871により提供されたメモリ情報M\_INFを検出し、メモリ情報M\_INFをメモリ装置制御部913に提供する。

40

#### 【0060】

一方、メモリ装置制御部913がメモリ情報M\_INFを利用してメモリ信号M\_SI Gのタイミングを制御する構成は、本発明の図2と同一であり、したがって、メモリ装置制御部913の構成も本発明の図3のメモリ装置制御部313の構成と同一である。

図10は、メモリ装置800内でのインターフェースタイミング制御方法を示すフロー チャートである。

#### 【0061】

電源がオンになれば(S1001)、メモリモジュール制御部875は、メモリ情報保

50

存部 871 からメモリ情報 M\_INF を受信する (S1003)。メモリモジュール制御部 875 は、メモリ情報 M\_INF を利用してメモリ信号 M\_SIG のタイミングを制御し (S1005)、メモリバスを通じてメモリ信号 M\_SIG をメモリ装置 879-1 ないし 879-8 に伝送する (S1007)。

#### 【0062】

図4を参照して前述したことと同じ方式で、メモリモジュール制御部 875 は、インターフェースタイミング情報をを利用してクロック信号 CLK、命令信号 CMD、アドレス信号 ADD、及びデータストローブ信号 DQS のインターフェースタイミングを制御する。

本発明は、図面に図示された一実施形態に基づいて説明されたが、これは例示的なものに過ぎず、当業者ならばこれより多様な変更及び均等な他の実施形態が可能であるという点を理解できるであろう。したがって、本発明の真の技術的保護範囲は、特許請求の範囲の技術的思想により決まらねばならない。

#### 【産業上の利用可能性】

#### 【0063】

本発明は、メモリシステムの関連技術分野に好適に用いられる。

#### 【図面の簡単な説明】

#### 【0064】

【図1】メモリモジュールを備える従来のメモリシステムを示すブロック図である。

【図2】本発明の実施形態によるメモリシステムを示すブロック図である。

【図3】図2のメモリモジュール制御部を示すブロック図である。

20

【図4】図3のメモリ装置制御部を示すブロック図である。

【図5】インターフェースタイミング情報の一例を示す図面である。

【図6】図5のインターフェースタイミング情報によって制御されるクロック信号のタイミングダイヤグラムである。

【図7】本発明の他の実施形態によるメモリモジュール内でのインターフェースタイミング制御方法を示すフローチャートである。

【図8】本発明のさらに他の実施形態によるメモリシステムを示すブロック図である。

【図9】図8のメモリモジュール制御部を示すブロック図である。

【図10】本発明のさらに他の実施形態によるメモリ装置内でのインターフェースタイミング制御方法を示すフローチャートである。

30

#### 【符号の説明】

#### 【0065】

200 メモリシステム

210 CPU

230 メモリ制御部

250 インターフェース制御部

270 メモリモジュール

271 メモリ情報保存部

273 追加メモリ情報保存部

275 メモリモジュール制御部

279-1 ~ 279-8 メモリ装置

40

【図1】

【図2】

【図3】

【図4】

【図5】

| SPD Byte #               | SPD Value | CLK Adjust |

|--------------------------|-----------|------------|

| 126 for CLK<br>(Example) | 0C        | +300 ps    |

|                          | 0D        | +200 ps    |

|                          | 0E        | +100 ps    |

|                          | 0F        | Default    |

|                          | 10        | -100 ps    |

|                          | 11        | -200 ps    |

|                          | 12        | -300 ps    |

| 127 for CMD<br>(Example) | 0C        | +300 ps    |

|                          | 0D        | +200 ps    |

|                          | 0E        | +100 ps    |

|                          | 0F        | Default    |

|                          | 10        | -100 ps    |

|                          | 11        | -200 ps    |

|                          | 12        | -300 ps    |

| 128 for ADD<br>(Example) | 0C        | +300 ps    |

|                          | 0D        | +200 ps    |

|                          | 0E        | +100 ps    |

|                          | 0F        | Default    |

|                          | 10        | -100 ps    |

|                          | 11        | -200 ps    |

|                          | 12        | -300 ps    |

【図6】

【図7】

【図8】

【図9】

【図10】

---

フロントページの続き

(74)代理人 100110364

弁理士 実広 信哉

(72)発明者 崔 熙柱

大韓民国京畿道水原市靈通區靈通洞 1047 - 1番地 清明マウル4團地建榮アパート423棟7

01號

(72)発明者 李 俊熙

大韓民国京畿道龍仁市豊徳川2洞213 - 1番地 三星5次アパート521棟103號

(72)発明者 金 東俊

大韓民国京畿道水原市靈通區靈通洞948 - 4番地 嶺谷マウル住公1團地アパート122棟19

04號

審査官 野田 佳邦

(56)参考文献 国際公開第2005/024832 (WO, A1)

特開2003-023349 (JP, A)

国際公開第2005/114669 (WO, A1)

(58)調査した分野(Int.Cl., DB名)

G 06 F 12 / 00 - 12 / 06