(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6303411号

(P6303411)

(45) 発行日 平成30年4月4日(2018.4.4)

(24) 登録日 平成30年3月16日(2018.3.16)

|                          |                |

|--------------------------|----------------|

| (51) Int.Cl.             | F 1            |

| GO 1 C 19/5776 (2012.01) | GO 1 C 19/5776 |

| GO 1 C 19/5614 (2012.01) | GO 1 C 19/5614 |

| HO 1 L 41/113 (2006.01)  | HO 1 L 41/113  |

| HO 1 L 41/04 (2006.01)   | HO 1 L 41/04   |

| HO 1 L 41/09 (2006.01)   | HO 1 L 41/09   |

請求項の数 13 (全 30 頁)

(21) 出願番号 特願2013-231343 (P2013-231343)

(22) 出願日 平成25年11月7日 (2013.11.7)

(65) 公開番号 特開2015-90353 (P2015-90353A)

(43) 公開日 平成27年5月11日 (2015.5.11)

審査請求日 平成28年11月4日 (2016.11.4)

(73) 特許権者 000002369

セイコーエプソン株式会社

東京都新宿区新宿四丁目1番6号

(74) 代理人 100104710

弁理士 竹腰 昇

(74) 代理人 100090479

弁理士 井上 一

(74) 代理人 100124682

弁理士 黒田 泰

(72) 発明者 牧 克彦

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

(72) 発明者 樋口 哲平

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

最終頁に続く

(54) 【発明の名称】検出装置、センサー、電子機器及び移動体

## (57) 【特許請求の範囲】

## 【請求項 1】

物理量トランスデューサーからのフィードバック信号を受けて、前記物理量トランスデューサーを駆動する駆動回路と、

前記物理量トランスデューサーからの検出信号を受けて、所望信号を検出する検出回路と、

電源電圧が入力される電源端子と、

前記電源端子からの前記電源電圧を降圧する電圧調整を行い、前記電圧調整により得られたレギュレート電源電圧を、動作電源電圧として前記駆動回路及び前記検出回路に供給するレギュレーター回路と、

前記電源電圧が供給され、前記駆動回路からの駆動信号を受けて、前記駆動信号の振幅を増加させた増幅駆動信号を前記物理量トランスデューサーに出力するバッファー回路と、

を含み、

前記バッファー回路は、

前記電源端子からの前記電源電圧を動作電源電圧として動作し、入力ノードである非反転入力端子に前記駆動回路からの前記駆動信号が入力され、出力ノードに前記増幅駆動信号を出力する演算増幅器と、

前記演算増幅器の前記出力ノードと、前記演算増幅器の反転入力端子に接続される接続ノードとの間に、直列に設けられる第1の抵抗素子及び第1のスイッチ素子と、

10

20

前記接続ノードと低電位側電源のノードとの間に直列に設けられる第2の抵抗素子及び第2のスイッチ素子と、

前記演算増幅器の前記出力ノードと前記入力ノードとの間に設けられる第3のスイッチ素子と、

を含み、

前記バッファー回路は、

第1のモードでは、前記第1のスイッチ素子及び前記第2のスイッチ素子がオンになり、前記第3のスイッチ素子がオフになることで、前記増幅駆動信号を前記物理量トランスデューサーに出力し、

第2のモードでは、前記第1のスイッチ素子及び前記第2のスイッチ素子がオフになり、前記第3のスイッチ素子がオンになることで、前記駆動回路からの前記駆動信号を前記物理量トランスデューサーに出力することを特徴とする検出装置。 10

**【請求項2】**

請求項1に記載の検出装置において、

前記物理量トランスデューサーは振動子であり、

前記振動子の発振の起動期間では、前記第1のモードに設定されて、前記バッファー回路からの前記増幅駆動信号を前記振動子に出力することを特徴とする検出装置。

**【請求項3】**

請求項2に記載の検出装置において、

前記起動期間が終了し、前記振動子が定常発振状態になった後で、前記第2のモードに設定されており、前記駆動回路からの前記駆動信号を前記振動子に出力していることを特徴とする検出装置。 20

**【請求項4】**

請求項1乃至3のいずれか一項に記載の検出装置において、

前記駆動回路及び前記検出回路は、第1の耐圧のトランジスターにより構成され、

前記バッファー回路は、前記第1の耐圧よりも高耐圧の第2の耐圧のトランジスターにより構成されることを特徴とする検出装置。

**【請求項5】**

物理量トランスデューサーからのフィードバック信号を受けて、前記物理量トランスデューサーを駆動する駆動回路と、 30

前記物理量トランスデューサーからの検出信号を受けて、所望信号を検出する検出回路と、

電源電圧が入力される電源端子と、

前記電源端子からの前記電源電圧を降圧する電圧調整を行い、前記電圧調整により得られたレギュレート電源電圧を、動作電源電圧として前記駆動回路及び前記検出回路に供給するレギュレーター回路と、

前記電源電圧が供給され、前記駆動回路からの駆動信号を受けて、前記駆動信号の振幅を増加させた増幅駆動信号を前記物理量トランスデューサーに出力するバッファー回路と、

を含み、 40

前記物理量トランスデューサーは振動子であり、

前記駆動回路は、

前記フィードバック信号を受けて、電流 - 電圧変換を行う電流 - 電圧変換回路と、

前記電流 - 電圧変換回路による電流 - 電圧変換後の入力電圧信号を増幅して、正弦波の前記駆動信号を出力する駆動信号出力回路と、

前記入力電圧信号に基づいて、前記駆動信号出力回路での前記駆動信号の増幅のゲインを制御するゲイン制御回路と、

を有し、

前記電流 - 電圧変換回路の電流 - 電圧変換用の抵抗をR Iとし、前記駆動信号出力回路と前記バッファー回路とによる駆動信号の増幅のゲインをKとし、前記振動子の基本波モ 50

ードでの等価直列抵抗をRとした場合に、前記ゲイン制御回路は、 $K \times R I = R$ となるよう<sub>に</sub>ゲイン制御を行うことを特徴とする検出装置。

【請求項 6】

請求項5に記載の検出装置において、

前記駆動信号出力回路は、

前記ゲイン制御回路からの制御電圧によってトランスコンダクタンスが設定されて、前記入力電圧信号を電流信号に変換するOTA (Operational Transconductance Amplifier)回路と、

前記OTA回路からの前記電流信号の電流 - 電圧変換を行い、前記駆動信号を出力する第2の電流 - 電圧変換回路と、

を有することを特徴とする検出装置。

10

【請求項 7】

請求項6に記載の検出装置において、

前記OTA回路は、

前記ゲイン制御回路からの前記制御電圧を制御電流に変換する電圧 - 電流変換回路と、

前記制御電流により設定されるバイアス電流がバイアス電流源に流れ、第1の差動入力端子にアナログ基準電圧が入力され、第2の差動入力端子に前記入力電圧信号が入力され、前記電流信号を前記第2の電流 - 電圧変換回路に出力する差動部と、

を有することを特徴とする検出装置。

【請求項 8】

請求項1乃至7のいずれか一項に記載の検出装置において、

第2の物理量トランスデューサーからの第2のフィードバック信号を受けて、前記第2の物理量トランスデューサーを駆動する第2の駆動回路と、

前記第2の物理量トランスデューサーからの第2の検出信号を受けて、所望信号を検出する第2の検出回路と、

前記電源端子からの前記電源電圧を降圧する電圧調整を行い、前記電圧調整により得られた第2のレギュレート電源電圧を前記第2の駆動回路及び前記第2の検出回路に供給する第2のレギュレーター回路と、

前記電源電圧が供給され、前記第2の駆動回路からの第2の駆動信号を受けて、前記第2の駆動信号の振幅を増加させた第2の増幅駆動信号を前記第2の物理量トランスデューサーに出力する第2のバッファー回路と、

を含むことを特徴とする検出装置。

20

【請求項 9】

請求項8に記載の検出装置において、

第1のモードでは、前記バッファー回路からの前記増幅駆動信号を前記物理量トランスデューサーに出力し、前記第2のバッファー回路からの前記第2の増幅駆動信号を前記第2の物理量トランスデューサーに出力し、

第2のモードでは、前記駆動回路からの前記駆動信号を前記物理量トランスデューサーに出力し、前記第2の駆動回路からの前記第2の駆動信号を前記第2の物理量トランスデューサーに出力することを特徴とする検出装置。

30

【請求項 10】

請求項8又は9に記載の検出装置において、

前記物理量トランスデューサーは、第1の軸回りでの回転角速度を検出するための振動子あり、

前記第2の物理量トランスデューサーは、第2の軸回りでの回転角速度を検出するための振動子であることを特徴とする検出装置。

40

【請求項 11】

請求項1乃至10のいずれか一項に記載の検出装置と、

前記物理量トランスデューサーと、

を含むことを特徴とするセンサー。

50

**【請求項 12】**

請求項 1 乃至 10 のいずれか一項に記載の検出装置を含むことを特徴とする電子機器。

**【請求項 13】**

請求項 1 乃至 10 のいずれか一項に記載の検出装置を含むことを特徴とする移動体。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、検出装置、センサー、電子機器及び移動体等に関する。

**【背景技術】****【0002】**

デジタルカメラ、スマートフォン等の電子機器や車、飛行機等の移動体には、外的な要因で変化する物理量を検出するためのジャイロセンサーが組み込まれている。このようなジャイロセンサーは、角速度等の物理量を検出し、いわゆる手振れ補正、姿勢制御、GPS自律航法などに用いられる。

**【0003】**

このようなジャイロセンサーの一つとして、水晶圧電振動ジャイロセンサーなどの振動ジャイロセンサーが知られている。振動ジャイロセンサーでは、回転によって発生するコリオリ力に対応した物理量を検出している。このような振動ジャイロセンサーの検出装置としては、例えば特許文献 1、2 に開示される従来技術が知られている。

**【先行技術文献】****【特許文献】****【0004】**

【特許文献 1】特開平 5 - 259738 号公報

【特許文献 2】特開 2008 - 99257 号公報

**【発明の概要】****【発明が解決しようとする課題】****【0005】**

特許文献 1 の従来技術では、第 1 の電源電圧を第 2 の電源電圧に昇圧する昇圧回路を設け、起動期間において、高い第 2 の電源電圧を動作電源電圧としてすることで、発振回路の起動時間の短縮化を図っている。しかしながら、この特許文献 1 の手法では、起動開始から、昇圧回路が高い第 2 の電源電圧を供給可能になるまでに時間がかかり、起動時間の短縮が不十分であるという課題がある。

**【0006】**

このような課題を解決するために、特許文献 2 の従来技術では、まず低い第 1 の電源電圧を動作電源電圧として検出装置を動作させ、次に第 1 の電源電圧から高い第 2 の電源電圧に切り替え、その後に低い第 1 の電源電圧に切り替える手法を採用している。

**【0007】**

しかしながら、特許文献 1、2 の従来技術では共に、検出装置の全体の動作電源電圧の切替により、起動時間の短縮化を図っている。このため、起動時間の短縮と検出性能の向上等とを両立して実現することが難しいという課題がある。

**【0008】**

本発明の幾つかの態様によれば、起動時間の短縮と検出性能の向上等とを両立して実現できる検出装置、センサー、電子機器及び移動体等を提供できる。

**【課題を解決するための手段】****【0009】**

本発明は、上述の課題の少なくとも一部を解決するためになされたものであり、以下の形態または態様として実現することが可能である。

**【0010】**

本発明の一態様は、物理量トランスデューサーからのフィードバック信号を受けて、前記物理量トランスデューサーを駆動する駆動回路と、前記物理量トランスデューサーから

10

20

30

40

50

の検出信号を受けて、所望信号を検出する検出回路と、電源電圧が入力される電源端子と、前記電源端子からの前記電源電圧を降圧する電圧調整を行い、前記電圧調整により得られたレギュレート電源電圧を、動作電源電圧として前記駆動回路及び前記検出回路に供給するレギュレーター回路と、前記電源電圧が供給され、前記駆動回路からの駆動信号を受けて、前記駆動信号の振幅を増加させた増幅駆動信号を前記物理量トランスデューサーに出力するバッファーレギュレーター回路とを含む検出装置に関するもの。

#### 【0011】

本発明の一態様では、レギュレーター回路が、電源端子からの電源電圧を降圧する電圧調整を行い、レギュレート電源電圧を駆動回路及び検出回路に供給する。駆動回路及び検出回路は、レギュレーター回路から供給されたレギュレート電源電圧を動作電源電圧として動作する。一方、バッファーレギュレーター回路には、電源端子からの電源電圧が供給されると共に駆動回路からの駆動信号が入力される。そしてバッファーレギュレーター回路は、駆動信号の振幅を増加させた増幅駆動信号を出力して物理量トランスデューサーを駆動する。このように、駆動回路及び検出回路を、レギュレーター回路により電圧調整されたレギュレート電源電圧により動作させれば、電源電圧変動による検出性能の低下等の事態を抑制でき、検出装置の検出性能の向上等を図れる。一方、バッファーレギュレーター回路については、レギュレート電源電圧ではなく電源電圧により動作させることで、駆動回路からの駆動信号の振幅を増加させた増幅駆動信号を物理量トランスデューサーに出力できるようになるため、起動時間の短縮と検出性能の向上等とを両立して実現することが可能になる。

#### 【0012】

また本発明の一態様では、第1のモードでは、前記バッファーレギュレーター回路からの前記増幅駆動信号を前記物理量トランスデューサーに出力し、第2のモードでは、前記駆動回路からの前記駆動信号を前記物理量トランスデューサーに出力してもよい。

#### 【0013】

このようにすれば、増幅駆動信号による駆動が必要な場合には第1のモードに設定して、通常の駆動信号による駆動の方が望ましい場合には第2のモードに設定できるようになり、利便性を向上できる。

#### 【0014】

また本発明の一態様では、前記物理量トランスデューサーは振動子であり、前記振動子の発振の起動期間では、前記第1のモードに設定されて、前記バッファーレギュレーター回路からの前記増幅駆動信号を前記振動子に出力してもよい。

#### 【0015】

このようにすれば、物理量トランスデューサーである振動子の発振の起動期間において増幅駆動信号による駆動が行われるため、発振の起動時間の短縮化を図れる。

#### 【0016】

また本発明の一態様では、前記起動期間の完了後に前記第2のモードに設定されて、前記駆動回路からの前記駆動信号を前記振動子に出力してもよい。

#### 【0017】

このようにすれば、起動期間の完了後の発振の定常状態では、増幅駆動信号ではなく駆動回路からの低振幅の駆動信号で振動子が駆動されるため、所望信号の検出性能の向上等を期待できるようになる。

#### 【0018】

また本発明の一態様では、前記バッファーレギュレーター回路は、非反転入力端子に前記駆動回路からの前記駆動信号が入力される演算増幅器と、前記演算増幅器の出力ノードと低電位側電源のノードとの間に直列に設けられる第1の抵抗素子及び第2の抵抗素子とを有し、前記第1の抵抗素子と前記第2の抵抗素子の接続ノードが前記演算増幅器の反転入力端子に接続されてもよい。

#### 【0019】

このようにすれば、駆動回路からの駆動信号の振幅を、第1、第2の抵抗素子の抵抗値により設定される増幅率で増幅できるようになる。

10

20

30

40

50

## 【0020】

また本発明の一態様では、前記駆動回路及び前記検出回路は、第1の耐圧のトランジスターにより構成され、前記バッファー回路は、前記第1の耐圧よりも高耐圧の第2の耐圧のトランジスターにより構成されてもよい。

## 【0021】

このように駆動回路及び検出回路を、低耐圧の第1の耐圧のトランジスターにより構成することで、低消費電力化等を図れるようになる。一方、バッファー回路を高耐圧の第2の耐圧のトランジスターにより構成することで、高振幅駆動によりトランジスターの故障・破壊等の不具合が発生するのを効果的に防止できる。

## 【0022】

また本発明の一態様では、前記物理量トランスデューサーは振動子であり、前記駆動回路は、前記フィードバック信号を受けて、電流・電圧変換を行う電流・電圧変換回路と、前記電流・電圧変換回路による電流・電圧変換後の入力電圧信号を増幅して、正弦波の前記駆動信号を出力する駆動信号出力回路と、前記駆動信号出力回路での前記駆動信号の増幅のゲインを制御するゲイン制御回路とを有し、前記電流・電圧変換回路の電流・電圧変換用の抵抗をR<sub>I</sub>とし、前記駆動信号出力回路と前記バッファー回路とによる駆動信号の増幅のゲインをKとし、前記振動子の基本波モードでの等価直列抵抗をRとした場合に、前記ゲイン制御回路は、 $K \times R_I = R$ となるようにゲイン制御を行ってもよい。

## 【0023】

このように、 $K \times R_I = R$ となるようにゲイン制御が行われることで、駆動回路側の負性抵抗を振動子の等価直列抵抗に応じた抵抗に設定できるようになる。これにより、正弦波の駆動信号による振動子の駆動が可能になり、検出装置の検出性能の向上等を図れる。

## 【0024】

また本発明の一態様では、前記駆動信号出力回路は、前記ゲイン制御回路からの制御電圧によってトランスコンダクタンスが設定されて、前記入力電圧信号を電流信号に変換するOTA (Operational Transconductance Amplifier)回路と、前記OTA回路からの前記電流信号の電流・電圧変換を行い、前記駆動信号を出力する第2の電流・電圧変換回路とを有してもよい。

## 【0025】

このようにすれば、制御電圧により設定されたトランスコンダクタンスで、入力電圧信号を電流信号に変換し、当該電流信号を電流・電圧変換した信号を駆動信号として生成できるようになる。

## 【0026】

また本発明の一態様では、前記OTA回路は、前記ゲイン制御回路からの前記制御電圧を制御電流に変換する電圧・電流変換回路と、前記制御電流により設定されるバイアス電流がバイアス電流源に流れ、第1の差動入力端子にアナログ基準電圧が入力され、第2の差動入力端子に前記入力電圧信号が入力され、前記電流信号を前記第2の電流・電圧変換回路に出力する差動部とを有してもよい。

## 【0027】

このようにすれば、制御電圧を制御電流に変換し、この制御電流に応じたバイアス電流を、差動部のバイアス電流源に流すことができる。これにより、制御電圧により設定されたトランスコンダクタンスで、入力電圧信号を電流信号に変換することが可能になる。

## 【0028】

また本発明の一態様では、第2の物理量トランスデューサーからの第2のフィードバック信号を受けて、前記第2の物理量トランスデューサーを駆動する第2の駆動回路と、前記第2の物理量トランスデューサーからの第2の検出信号を受けて、所望信号を検出する第2の検出回路と、前記電源端子からの前記電源電圧を降圧する電圧調整を行い、前記電圧調整により得られた第2のレギュレート電源電圧を前記第2の駆動回路及び前記第2の検出回路に供給する第2のレギュレーター回路と、前記電源電圧が供給され、前記第2の駆動回路からの第2の駆動信号を受けて、前記第2の駆動信号の振幅を増加させた第2の

10

20

30

40

50

増幅駆動信号を前記第2の物理量トランスデューサーに出力する第2のバッファー回路とを含んでもよい。

【0029】

このようにすれば、複数の物理量トランスデューサーについての駆動及び検出が可能になる。そして例えば物理量トランスデューサーの駆動、検出による電源電圧変動等の悪影響が、第2の物理量トランスデューサーの駆動、検出に及んだり、第2の物理量トランスデューサーの駆動、検出による電源電圧変動等の悪影響が、物理量トランスデューサーの駆動、検出に及ぶのを効果的に抑制できるようになる。

【0030】

また本発明の一態様では、第1のモードでは、前記バッファー回路からの前記増幅駆動信号を前記物理量トランスデューサーに出力し、前記第2のバッファー回路からの前記第2の増幅駆動信号を前記第2の物理量トランスデューサーに出力し、第2のモードでは、前記駆動回路からの前記駆動信号を前記物理量トランスデューサーに出力し、前記第2の駆動回路からの前記第2の駆動信号を前記第2の物理量トランスデューサーに出力してもよい。

10

【0031】

このようにすれば、複数の物理量トランスデューサーについての駆動及び検出を行う場合において、増幅駆動信号による駆動が必要な場合には第1のモードに設定して、通常の駆動信号による駆動の方が望ましい場合には第2のモードに設定できるようになり、利便性を向上できる。

20

【0032】

また本発明の一態様では、前記物理量トランスデューサーは、第1の軸回りでの回転角速度を検出するための振動子あり、前記第2の物理量トランスデューサーは、第2の軸回りでの回転角速度を検出するための振動子であってもよい。

【0033】

このようにすれば、複数の回転軸での回転角速度を検出する際の軸間干渉を効果的に低減できるようになる。

【0034】

また本発明の他の態様は、上記のいずれかに記載の検出装置と、前記物理量トランスデューサーとを含むことを特徴とするセンサーに関係する。

30

【0035】

また本発明の他の態様は、上記のいずれかに記載の検出装置を含む電子機器に関係する。

【0036】

また本発明の他の態様は、上記のいずれかに記載の検出装置を含む移動体に関係する。

【図面の簡単な説明】

【0037】

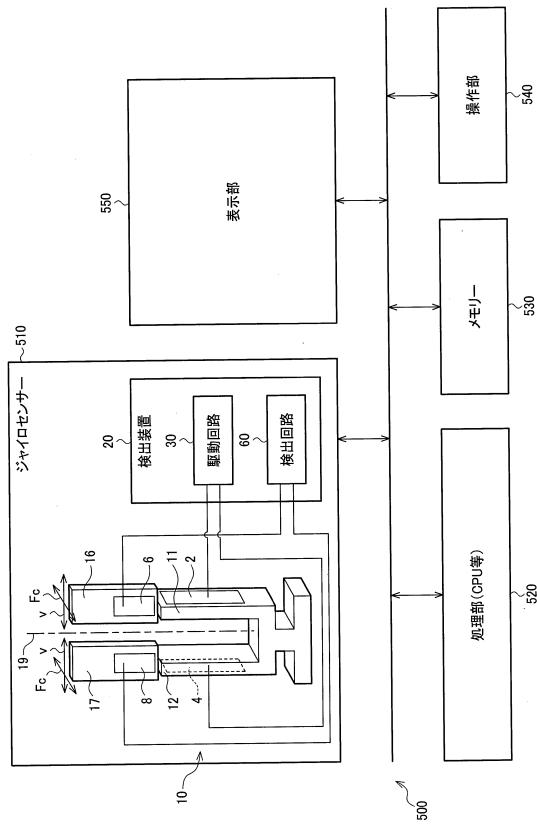

【図1】本実施形態の電子機器、ジャイロセンサーの構成例。

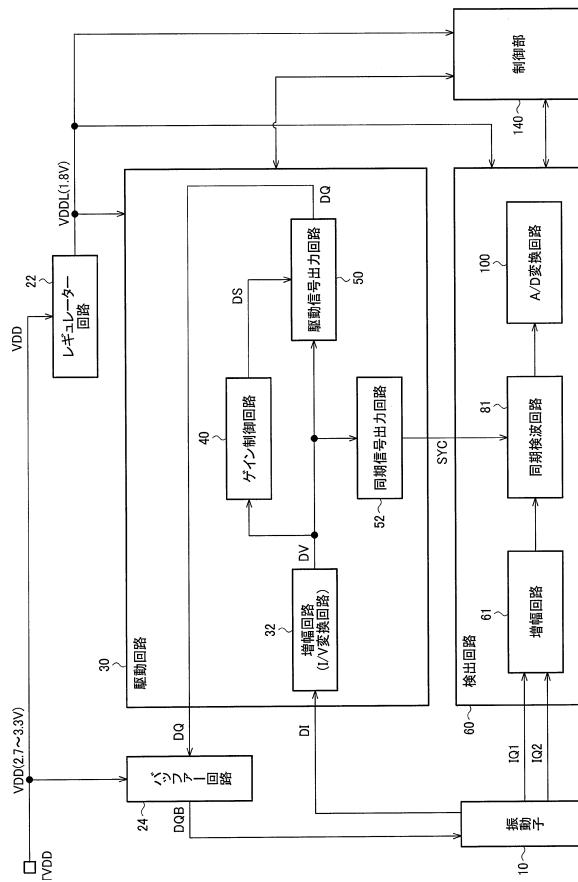

【図2】本実施形態の検出装置の構成例。

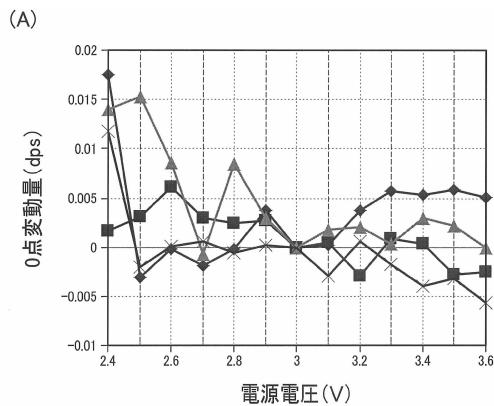

【図3】図3(A)は電源電圧VDDと0点変動量の関係を示す図であり、図3(B)は電源電圧と起動時間の関係を示す図。

40

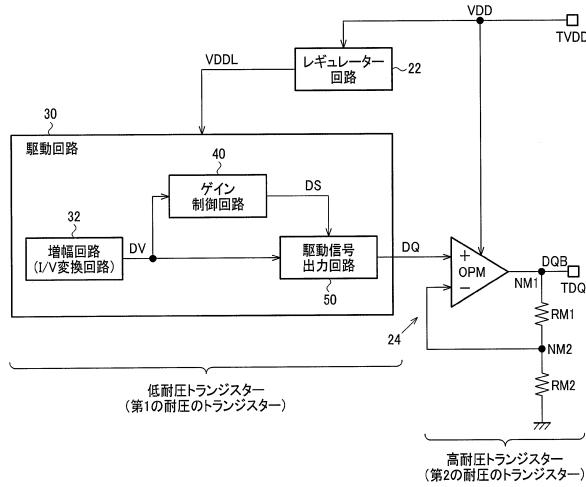

【図4】バッファー回路の第1の構成例。

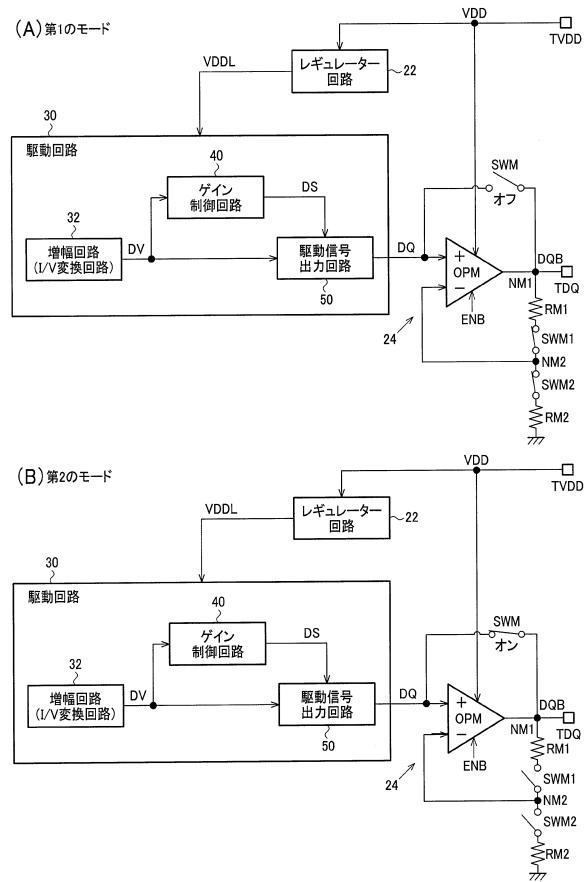

【図5】図5(A)、図5(B)はバッファー回路の第2の構成例。

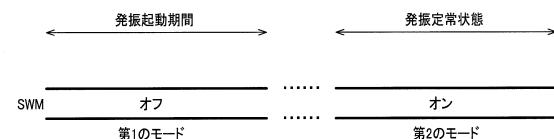

【図6】第1、第2のモードについての説明図。

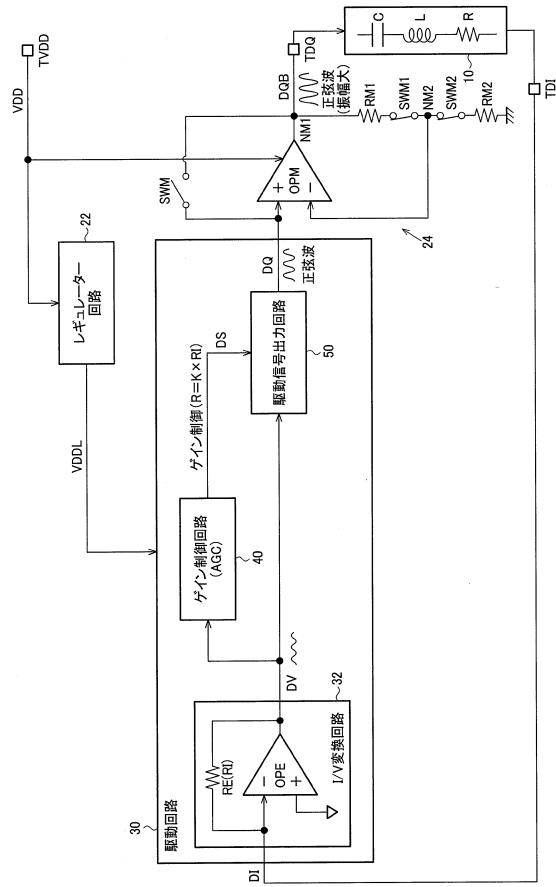

【図7】振動子を正弦波駆動で発振させる駆動回路の構成例。

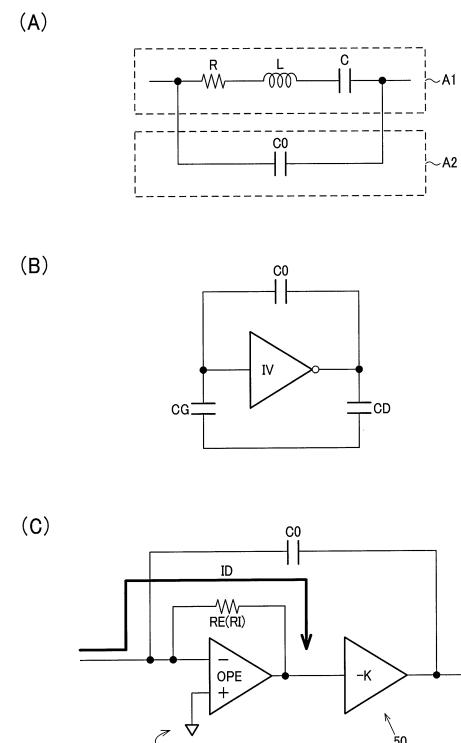

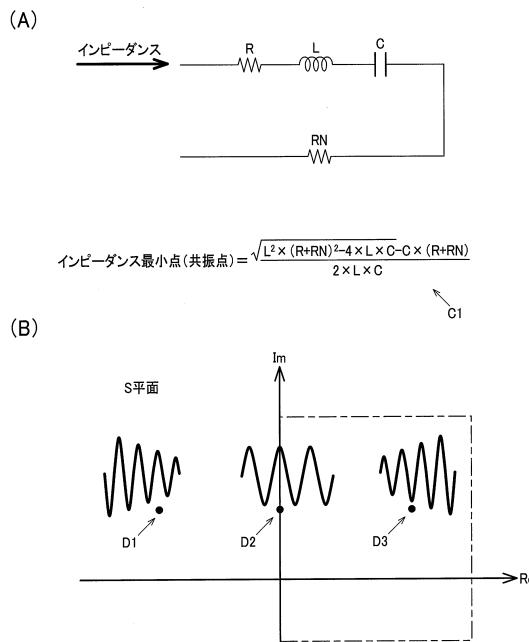

【図8】図8(A)～図8(C)は振動子の駆動回路の負性抵抗についての説明図。

【図9】図9(A)、図9(B)は振動子を正弦波駆動で発振させる手法の説明図。

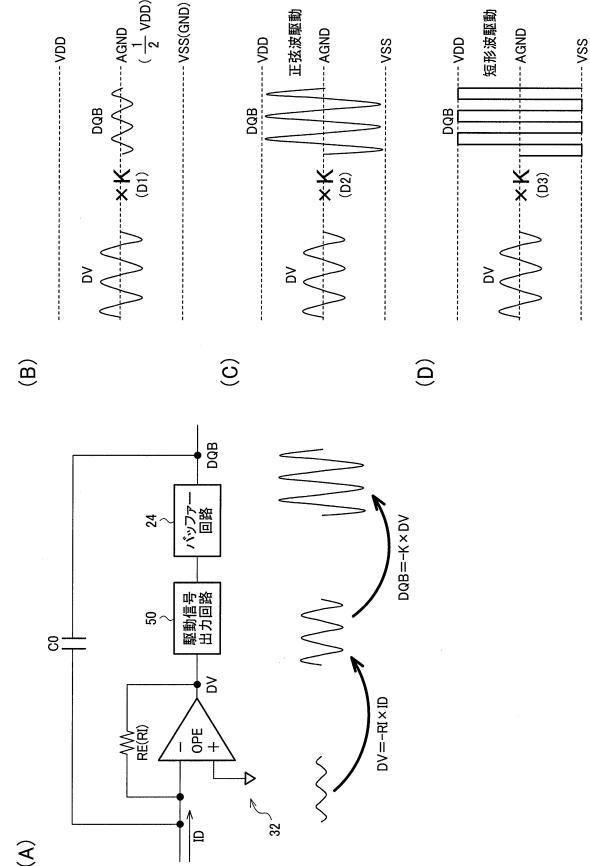

【図10】図10(A)～図10(D)も振動子を正弦波駆動で発振させる手法の説明図。

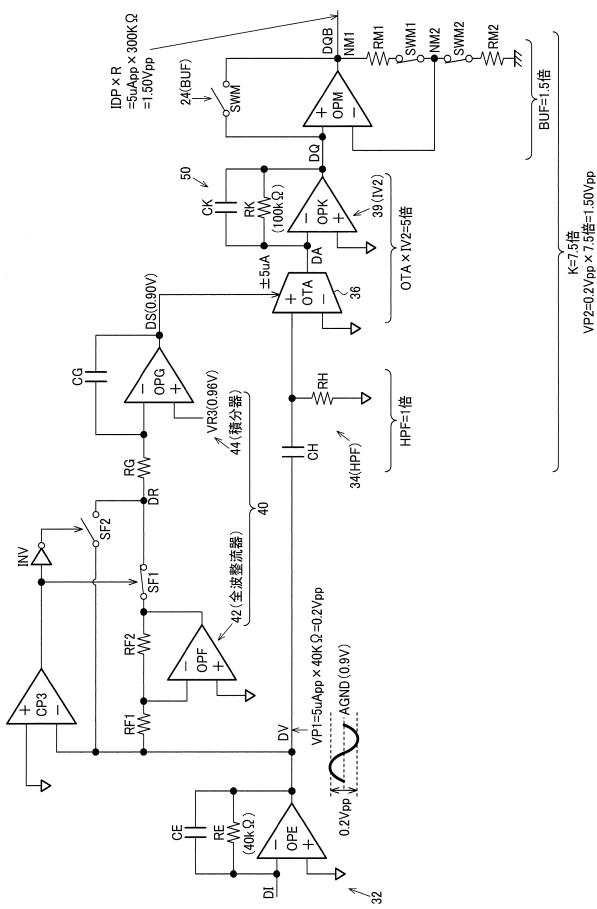

【図11】振動子を正弦波駆動で発振させる駆動回路の詳細な構成例。

50

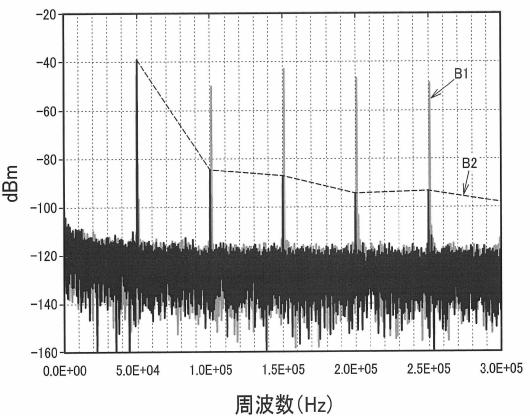

【図12】正弦波駆動による高調波成分の低減についての説明図。

【図13】OTA回路の詳細な構成例。

【図14】本実施形態の検出装置の他の構成例。

【図15】検出回路の構成例。

【図16】図16(A)、図16(B)は検出回路の他の構成例。

【図17】移動体の一具体例としての自動車の構成を概略的に示す概念図。

【発明を実施するための形態】

【0038】

以下、本発明の好適な実施の形態について詳細に説明する。なお以下に説明する本実施形態は特許請求の範囲に記載された本発明の内容を不当に限定するものではなく、本実施形態で説明される構成の全てが本発明の解決手段として必須であるとは限らない。例えば以下では、物理量トランスデューサーが圧電型の振動子(振動ジャイロ)であり、センサーがジャイロセンサーである場合を例にとり説明するが、本発明はこれに限定されない。例えばシリコン基板などから形成された静電容量検出方式の振動子(振動ジャイロ)や、角速度情報と等価な物理量や角速度情報以外の物理量を検出する物理量トランスデューサー、センサー等にも本発明は適用可能である。

10

【0039】

### 1. 電子機器、ジャイロセンサー

図1に本実施形態の検出装置20を含むジャイロセンサー510(広義にはセンサー)と、ジャイロセンサー510を含む電子機器500の構成例を示す。なお電子機器500、ジャイロセンサー510は図1の構成に限定されず、その構成要素の一部を省略したり、他の構成要素を追加するなどの種々の変形実施が可能である。また本実施形態の電子機器500としては、デジタルカメラ、ビデオカメラ、スマートフォン、携帯電話機、カーナビゲーションシステム、ロボット、ゲーム機、時計、健康器具、或いは携帯型情報端末等の種々の機器を想定できる。

20

【0040】

電子機器500はジャイロセンサー510と処理部520を含む。またメモリー530、操作部540、表示部550を含むことができる。処理部520(CPU、MPU等)はジャイロセンサー510等の制御や電子機器500の全体制御を行う。また処理部520は、ジャイロセンサー510により検出された角速度情報(広義には物理量)に基づいて処理を行う。例えば角速度情報に基づいて、手ぶれ補正、姿勢制御、GPS自律航法などのための処理を行う。メモリー530(ROM、RAM等)は、制御プログラムや各種データを記憶したり、ワーク領域やデータ格納領域として機能する。操作部540はユーザーが電子機器500を操作するためのものであり、表示部550は種々の情報をユーザーに表示する。

30

【0041】

ジャイロセンサー510(センサー)は振動子10、検出装置20を含む。図1の振動子10(広義には物理量トランスデューサー)は、水晶などの圧電材料の薄板から形成される音叉型の圧電振動子であり、駆動用振動子11、12と、検出用振動子16、17を有する。駆動用振動子11、12には駆動端子2、4が設けられ、検出用振動子16、17には検出端子6、8が設けられている。

40

【0042】

検出装置20が含む駆動回路30は、駆動信号(駆動電圧)を出力して振動子10を駆動する。そして振動子10からフィードバック信号を受け、これにより振動子10を励振させる。検出回路60は、駆動信号により駆動される振動子10から検出信号(検出電流、電荷)を受け、検出信号から、振動子10に印加された物理量に応じた所望信号(コリオリ力信号)を検出(抽出)する。

【0043】

具体的には、駆動回路30からの交流の駆動信号(駆動電圧)が駆動用振動子11の駆動端子2に印加される。すると逆電圧効果によって駆動用振動子11が振動を開始し、音

50

又振動により駆動用振動子 12 も振動を開始する。この時、駆動用振動子 12 の圧電効果によって発生する電流（電荷）が、駆動端子 4 からフィードバック信号として駆動回路 30 にフィードバックされる。これにより振動子 10 を含む発振ループが形成される。

【0044】

駆動用振動子 11、12 が振動すると、検出用振動子 16、17 が図 1 に示す方向で振動速度  $v$  で振動する。すると、検出用振動子 16、17 の圧電効果によって発生する電流（電荷）が、検出信号（第 1、第 2 の検出信号）として検出端子 6、8 から出力される。すると、検出回路 60 は、この振動子 10 からの検出信号を受け、コリオリ力に応じた信号である所望信号（所望波）を検出する。即ち、検出軸 19 を中心に振動子 10（ジャイロセンサー）が回転すると、振動速度  $v$  の振動方向と直交する方向にコリオリ力  $F_c$  が発生する。例えば検出軸 19 を中心に回転したときの角速度を  $\omega$  とし、振動子の質量を  $m$  とし、振動子の振動速度を  $v$  とすると、コリオリ力は  $F_c = 2m \cdot v \cdot \omega$  と表される。従って検出回路 60 が、コリオリ力に応じた信号である所望信号を検出することで、ジャイロセンサーの回転角速度  $\omega$  を求めることができる。そして求められた角速度  $\omega$  を用いることで、処理部 520 は、手振れ補正、姿勢制御、或いは GPS 自律航法等のための種々の処理を行うことができる。

【0045】

なお図 1 では、振動子 10 が音叉型である場合の例を示しているが、本実施形態の振動子 10 はこのような構造に限定されない。例えば T 字型やダブル T 字型等であってもよい。また振動子 10 の圧電材料は水晶以外であってもよい。

【0046】

2. 検出装置

図 2 に本実施形態の検出装置 20 の構成例を示す。検出装置 20 は、振動子 10（物理量トランスデューサー）からのフィードバック信号 DI を受けて、振動子 10 を駆動する駆動回路 30 と、振動子 10 からの検出信号 IQ1、IQ2 を受けて、所望信号を検出する検出回路 60 を含む。

【0047】

また検出装置 20（集積回路装置）は、電源電圧 VDD が入力される電源端子 TVDD と、レギュレーター回路 22 と、バッファ回路 24 を含む。

【0048】

電源端子 TVDD には、例えば外部から電源電圧 VDD が入力される。この電源電圧 VDD はレギュレーター回路 22 やバッファ回路 24 に供給される。電源端子 TVDD は例えば集積回路装置（IC チップ）におけるパッドである。

【0049】

レギュレーター回路 22 は、電源端子 TVDD から供給される電源電圧 VDD を降圧する電圧調整を行う。そして電圧調整により得られたレギュレート電源電圧 VDDL を、動作電源電圧として駆動回路 30 及び検出回路 60 に供給する。またレギュレーター回路 22 は、レギュレート電源電圧 VDDL を制御部 140 に供給する。例えば外部からの電源電圧 VDD として 2.7V ~ 3.3V の電圧が供給された場合に、レギュレーター回路 22 は、この電源電圧 VDD を降圧する電圧調整を行って、例えば 1.8V の一定電圧の電源電圧 VDDL を駆動回路 30、検出回路 60、制御部 140 に供給する。

【0050】

バッファ回路 24 には、電源電圧 VDD が供給される。この電源電圧 VDD はバッファ回路 24 の高電位側電源電圧として用いられる。そしてバッファ回路 24 は、駆動回路 30 からの駆動信号 DQ を受けて、駆動信号 DQ の振幅を増加させた高振幅の駆動信号（增幅駆動信号）DQB を振動子 10（物理量トランスデューサー）に出力する。例えば駆動信号 DQ の振幅を第 1 の振幅とした場合に、第 1 の振幅よりも大きい第 2 の振幅の駆動信号 DQB を振動子 10 に出力する。この場合に駆動信号 DQ、DQB は矩形波の信号であってもよいし、正弦波の信号であってもよい。

【0051】

10

20

30

40

50

駆動回路 3 0 は、振動子 1 0 からのフィードバック信号 D I が入力される増幅回路 3 2 と、自動ゲイン制御を行うゲイン制御回路 4 0 と、駆動信号 D Q を振動子 1 0 に出力する駆動信号出力回路 5 0 を含む。また同期信号 S Y C を検出回路 6 0 に出力する同期信号出力回路 5 2 を含む。なお、駆動回路 3 0 の構成は図 2 に限定されず、これらの構成要素の一部を省略したり、他の構成要素を追加するなどの種々の変形実施が可能である。

#### 【 0 0 5 2 】

増幅回路 3 2 ( I / V 変換回路 ) は、振動子 1 0 からのフィードバック信号 D I を増幅する。例えば振動子 1 0 からの電流の信号 D I を電圧の信号 D V に変換して出力する。この増幅回路 3 2 は、キャパシター、抵抗素子、演算増幅器などにより実現できる。

#### 【 0 0 5 3 】

駆動信号出力回路 5 0 は、増幅回路 3 2 による増幅後の信号 D V に基づいて、駆動信号 D Q を出力する。例えば駆動信号出力回路 5 0 が、矩形波 ( 又は正弦波 ) の駆動信号を出力する場合には、駆動信号出力回路 5 0 はコンパレーター等により実現できる。

#### 【 0 0 5 4 】

ゲイン制御回路 4 0 ( A G C ) は、駆動信号出力回路 5 0 に制御電圧 D S を出力して、駆動信号 D Q の振幅を制御する。具体的には、ゲイン制御回路 4 0 は、信号 D V を監視して、発振ループのゲインを制御する。例えば駆動回路 3 0 では、ジャイロセンサーの感度を一定に保つために、振動子 1 0 ( 駆動用振動子 ) に供給する駆動電圧の振幅を一定に保つ必要がある。このため、駆動振動系の発振ループ内に、ゲインを自動調整するためのゲイン制御回路 4 0 が設けられる。ゲイン制御回路 4 0 は、振動子 1 0 からのフィードバック信号 D I の振幅 ( 振動子の振動速度 v ) が一定になるように、ゲインを可変に自動調整する。

#### 【 0 0 5 5 】

同期信号出力回路 5 2 は、増幅回路 3 2 による増幅後の信号 D V を受け、同期信号 S Y C ( 参照信号 ) を検出回路 6 0 に出力する。この同期信号出力回路 5 2 は、正弦波 ( 交流 ) の信号 D V の 2 値化処理を行って矩形波の同期信号 S Y C を生成するコンパレーターや、同期信号 S Y C の位相調整を行う位相調整回路 ( 移相器 ) などにより実現できる。

#### 【 0 0 5 6 】

検出回路 6 0 は、増幅回路 6 1 、同期検波回路 8 1 、 A / D 変換回路 1 0 0 を含む。増幅回路 6 1 は、振動子 1 0 からの第 1 、第 2 の検出信号 I Q 1 、 I Q 2 を受けて、信号増幅や電荷 - 電圧変換を行う。同期検波回路 8 1 は、駆動回路 3 0 からの同期信号 S Y C に基づいて同期検波を行う。 A / D 変換回路 1 0 0 は、同期検波後の信号の A / D 変換を行う。なお検出回路 6 0 の構成としては、後述するように種々の方式の構成を採用することができる。これらについては後に詳述する。

#### 【 0 0 5 7 】

検出装置 2 0 は、制御部 1 4 0 を更に含むことができる。制御部 1 4 0 は、検出装置 2 0 の制御処理を行う。この制御部 1 4 0 は、ロジック回路 ( ゲートアレイ等 ) やプロセッサー等により実現できる。検出装置 2 0 での各種のスイッチ制御やモード設定等はこの制御部 1 4 0 により行われる。

#### 【 0 0 5 8 】

##### 3 . バッファー回路を用いた高振幅駆動

本実施形態では、図 2 に示すように、外部からの電源電圧 V D D を降圧する電圧調整を、レギュレーター回路 2 2 により行い、電圧調整されたレギュレート電源電圧 V D D L を駆動回路 3 0 や検出回路 6 0 に供給している。そして駆動回路 3 0 や検出回路 6 0 は、このレギュレート電源電圧 V D D L を動作電源電圧として動作する。

#### 【 0 0 5 9 】

このように、一定電圧になるように調整されたレギュレート電源電圧 V D D L を生成し、このレギュレート電源電圧 V D D L を用いて駆動回路 3 0 、検出回路 6 0 を動作させれば、検出性能の向上等を実現できる。

#### 【 0 0 6 0 】

10

20

30

40

50

即ち、従来のように外部からの電源電圧 VDD により駆動回路 30、検出回路 60 を動作させる構成では、電源電圧 VDD に電圧変動があった場合に、この電圧変動が原因で、例えばジャイロの 0 点変動等が生じるおそれがある。

#### 【0061】

この点、本実施形態では、電源電圧 VDD を動作電源電圧として、駆動回路 30、検出回路 60 を動作させるのではなく、レギュレーター回路 22 により生成されたレギュレート電源電圧 VDDL を動作電源電圧として、駆動回路 30、検出回路 60 を動作させている。このようにすれば、電源電圧 VDD に電圧変動があった場合にも、この電圧変動がレギュレーター回路 22 により吸収されるため、駆動回路 30、検出回路 60 に VDD の電圧変動が伝達されるのを抑制できる。

10

#### 【0062】

即ち、本実施形態のレギュレーター回路 22 を用いれば、例えば電源電圧 VDD が 2.7 V ~ 3.3 V の範囲内において変動した場合にも、レギュレート電源電圧 VDDL の電圧変動を例えば 1 mV 以下（例えば 0.3 mV 以下）に抑えることができる。また温度変化があった場合にも、レギュレート電源電圧 VDDL の変動を例えば ± 数十 mV 以下（例えば ± 30 mV 以下）に抑えることができる。従って、電源電圧 VDD の変動がある場合にも、レギュレーター電圧 VDDL の変動については最小限に抑えることができるため、電源電圧 VDD の変動が原因で 0 点（ジャイロの静止状態時の出力）が変動して、検出性能が悪化してしまう事態を抑制できる。

#### 【0063】

20

例えば図 3 (A) は、本実施形態のようにレギュレーター回路 22 を用いた場合における、電源電圧 VDD と 0 点変動量の関係（サンプル数 4 個）を示す図である。図 3 (A) に示すように本実施形態では、例えば電源電圧 VDD が 2.7 V ~ 3.3 V の範囲内に変動した場合にも、0 点変動量 (dps : Degree per second) を最小限（例えば 0.01 dps 以下）に抑えること可能になる。

#### 【0064】

また本実施形態によれば、検出装置の回路の大部分を占める駆動回路 30、検出回路 60、制御部 140 を、低いレギュレート電源電圧 VDDL により動作させることができる。従って、回路の大部分が低電源電圧で動作することになるため、消費電力についても効果的に削減できるという利点がある。

30

#### 【0065】

しかしながら、このように駆動回路 30 等を、低電圧のレギュレート電源電圧 VDDL で動作させてしまうと、今度は、発振の起動時間が長くなってしまうという問題が生じる。例えば図 3 (B) は、電源電圧と起動時間の関係を示す図である。図 3 (B) に示すように電源電圧が低くなるほど、起動時間が長くなる。例えば図 3 (B) に示すように、振動子 10 の駆動電流が大きいほど、起動時間が長くなる。そして、駆動電流が大きい場合には、電源電圧が例えば 2.7 V 程度以下の場合に、起動時間が指数関数的に長くなってしまい、許容範囲を超えてしまうおそれがある。即ち、駆動回路 30 等の電源電圧として、レギュレート電源電圧 VDDL（例えば 1.8 V）を使用すると、起動時間が非常に長くなってしまい、使用に耐え得ないレベルになるおそれがある。

40

#### 【0066】

そこで本実施形態では図 2 に示すように、レギュレーター回路 22 により生成されたレギュレート電源電圧 VDDL を駆動回路 30、検出回路 60 に供給して検出性能の向上や低消費電力化を図る一方で、駆動信号 DQ をバッファリングするバッファー回路 24 に対しては、レギュレート電源電圧 VDDL ではなく電源電圧 VDD を供給する。即ち、これまで電源電圧 VDD を検出装置の全ての回路に供給していたのに対して、本実施形態では、検出装置の回路（集積回路装置）を、レギュレート電源電圧 VDDL を供給する第 1 の回路部分と、電源電圧 VDD を供給する第 2 の回路部分とに分ける。そして、検出性能の向上や低消費電力化が要求される駆動回路 30、検出回路 60、制御部 140 は、レギュレート電源電圧 VDDL が供給される第 1 の回路部分とする一方で、バッファー回路 2

50

4については、電源電圧VDDが直接に供給される第2の回路部分とする。

【0067】

そしてバッファー回路24は、供給された電源電圧VDDを用いて、駆動回路30からの駆動信号DQの振幅を増加させる変換を行って、高振幅の駆動信号（増幅駆動信号）DQBを振動子10に出力する。即ち、駆動信号DQのピーク・ツー・ピーク電圧よりも高いピーク・ツー・ピーク電圧を有する駆動信号DQBを生成し、この駆動信号DQBにより振動子10を駆動する。

【0068】

このようにすれば図3(B)から明らかなように、レギュレート電源電圧VDDLを用いた駆動信号DQにより振動子10を駆動する場合に比べて、起動時間を短縮できる。即ち本実施形態では、検出性能の向上や低消費電力化と、起動時間の短縮化とを両立して実現することに成功している。

10

【0069】

4. バッファー回路の構成例

次にバッファー回路24の具体的な構成例について説明する。図4にバッファー回路24の第1の構成例を示す。

【0070】

図4では、バッファー回路24は、演算増幅器OPM、第1、第2に抵抗素子RM1、RM2を有する。演算増幅器OPMは、非反転入力端子に駆動回路30からの駆動信号DQが入力される。演算増幅器OPMは電源端子TVDDからの電源電圧VDDを動作電源電圧として動作する。第1、第2の抵抗素子RM1、RM2は、高振幅の駆動信号DQBの出力ノードNM1と低電位側電源(GND)のノードとの間に直列に設けられる。そして第1、第2の抵抗素子RM1、RM2の接続ノードNM2は、演算増幅器OPMの反転入力端子に接続される。なおレギュレーター回路22も図4のバッファー回路24と同様の構成により実現できる。

20

【0071】

図4において抵抗素子RM1、RM2の抵抗をR1、R2とし、駆動信号DQ、DQBの振幅をAP、APBとする。すると、 $APB = \{ (R1 + R2) / R2 \} \times AP$ という関係式が成り立つ。例えば $R1 = 200K$ 、 $R2 = 400K$ である場合には、 $APB = \{ (200K + 400K) / 400K \} \times AP = 1.5 \times AP$ となり、駆動信号DQBは駆動信号DQの振幅（ピーク・ツー・ピーク電圧）を1.5倍にした信号になる。従って、振動子10の高振幅駆動が可能になり、発振の起動時間の短縮化等を実現できる。

30

【0072】

また本実施形態では、駆動回路30及び検出回路60は、低耐圧トランジスター（第1の耐圧のトランジスター）により構成され、バッファー回路24は、高耐圧トランジスター（第1の耐圧よりも高耐圧の第2の耐圧のトランジスター）により構成される。例えば、低耐圧トランジスターは、1.8Vよりも耐圧が高く、高耐圧トランジスターよりも耐圧が低いトランジスターであり、高耐圧トランジスターは3.3Vよりも耐圧が高いトランジスターである。高耐圧トランジスターは、例えば低耐圧トランジスターよりもゲート酸化膜の膜厚を厚くしたり、ゲート長を長くすることなどで実現できる。検出装置の大部分を占める駆動回路30、検出回路60や制御部140を低耐圧トランジスターにより構成することで、検出装置の低消費電力化や回路レイアウトの面積化等を図れるようになる。バッファー回路24を高耐圧トランジスターにより構成することで、高振幅駆動によりトランジスターの故障・破壊等の不具合が発生するのを効果的に防止できる。

40

【0073】

図5(A)、図5(B)にバッファー回路24の第2の構成例を示す。この第2の構成例のバッファー回路24を有する検出装置は、図5(A)の第1のモードでは、バッファー回路24からの高振幅の駆動信号DQBを振動子10（物理量トランスデューサー）に出力する。一方、図5(B)の第2のモードでは、駆動回路30からの駆動信号DQを振

50

動子 10 に出力する。

【 0 0 7 4 】

具体的には第 2 の構成例では、バッファー回路 24 の出力ノード N M 1 と入力ノードとの間にスイッチ素子 S W M が設けられている。そして図 5 ( A ) に示すように第 1 のモードではスイッチ素子 S W M がオフになる。これにより、バッファー回路 24 からの高振幅の駆動信号 D Q が振動子 10 に出力されるようになる。なおこの場合に、例えばイネーブル信号 E N B により演算増幅器 O P M が動作イネーブル状態に設定される。

【 0 0 7 5 】

一方、第 2 のモードではスイッチ素子 S W M がオンになる。これにより、駆動回路 30 からの低振幅の駆動信号 D Q がスイッチ素子 S W M を介して振動子 10 に出力されるようになる。なおこの場合に、例えばイネーブル信号 E N B により演算増幅器 O P M が動作ディスエーブル状態に設定される。例えば演算増幅器 O P M の出力がハイインピーダンス状態に設定される。

【 0 0 7 6 】

また第 2 の構成例では抵抗素子 R M 1、R M 2 に対応してスイッチ素子 S W M 1、S W M 2 が設けられている。そして図 5 ( A ) の第 1 のモードではスイッチ素子 S W M 1、S W M 2 がオンになる一方で、図 5 ( B ) の第 2 のモードではスイッチ素子 S W M 1、S W M 2 がオフになる。これにより、第 2 のモードにおいて、バッファー回路 24 の出力ノード N M 1 から V S S ( G N D ) に対して不要な電流が流れたり、演算増幅器 O P M の反転入力端子に不要な電圧が印加されるのを防止できる。

10

20

【 0 0 7 7 】

例えば図 6 に示すように、振動子 10 の発振の起動期間では、検出装置が第 1 のモードに設定される。これにより、バッファー回路 24 からの高振幅の駆動信号 D Q B が振動子 10 に出力される。一方、起動期間の完了後に、検出装置が第 2 のモードに設定される。例えば発振定常状態では第 2 のモードに設定される。これにより、駆動回路 30 からの低振幅の駆動信号 D Q が振動子 10 に出力される。

【 0 0 7 8 】

例えば起動期間では、振動子 10 の発振の起動時間の短縮化のために、高振幅駆動を行うことが望ましい。従って起動期間では図 5 ( A ) に示すようにスイッチ素子 S W M をオフにして、バッファー回路 24 からの高振幅の駆動信号 D Q B で振動子 10 を駆動し、起動時間の短縮化を図る。

30

【 0 0 7 9 】

一方、起動期間が完了し、振動子 10 が定常発振状態となった場合には、起動時間の短縮化という要請はなくなるため、図 5 ( B ) に示すようにスイッチ素子 S W M をオン ( S W M 1、S W M 2 をオフ ) にして、駆動回路 30 からの低振幅の駆動信号 D Q により振動子 10 を駆動する。このように低振幅の駆動信号 D Q で駆動することで、低消費電力化やノイズ低減等を期待できるようになる。但し、アプリケーションによっては、起動期間が完了して振動子 10 が定常発振状態になった後も、例えば 2.7 V ~ 3.3 V の電源電圧 V D D を用いた駆動信号 D Q B による駆動が望ましい場合もある。従って、このような場合には起動期間が完了した後も、検出装置を第 1 のモードに設定する。

40

【 0 0 8 0 】

なお、第 1、第 2 のモードの設定は例えば制御部 140 の制御処理により実現できる。例えば制御部 140 がスイッチ素子 S W M、S W M 1、S W M 2 のオン・オフを制御することで実現できる。また検出装置に設けられたレジスター部のレジスター設定によって、図 5 ( A )、図 5 ( B ) の第 1、第 2 のモードを設定することができる。例えば外部インターフェースを介してレジスター部にアクセスして、第 1、第 2 のモードの設定を行うようになることができる。

【 0 0 8 1 】

5. 正弦波の駆動信号

本実施形態では、振動子を矩形波の駆動信号で駆動してもよいが、正弦波の駆動信号で

50

駆動することもできる。以下では、この正弦波の駆動信号による駆動手法について詳細に説明する。

【0082】

例えば図7において、ゲイン制御回路40は、駆動信号出力回路50での駆動信号DQの増幅のゲインを制御している。そしてI/V変換回路32はI/V変換用の抵抗素子REを有する。なお以下では図2の増幅回路32をI/V変換回路32と記載する。例えばI/V変換回路32は、演算増幅器OPEと、演算増幅器OPEの出力ノードと反転入力端子のノードとの間に設けられる帰還の抵抗素子REを有する。

【0083】

ここで、抵抗素子REの抵抗値であるI/V変換用（電流-電圧変換用）の抵抗をRIとする。また駆動信号出力回路50とバッファー回路24による駆動信号DQBの増幅のゲインをKとする。また振動子10の基本波モードでの等価直列抵抗（等価直列抵抗値）をRとする。例えば振動子10は、図7に示すようにC、L、Rの等価回路で表され、その等価直列抵抗（共振抵抗）をRとする。

【0084】

この場合にゲイン制御回路40は、 $K \times R_I = R$ となるようにゲイン制御を行う。例えば、 $K \times R_I = R$ の関係式で表されるゲインが目標ゲインとなるようにAGCループによるゲイン制御を行う。そして駆動信号出力回路50及びバッファー回路24は、 $K \times R_I = R$ の関係式が成り立つゲインで、I/V変換回路32によるI/V変換後の電圧信号DVを増幅して、駆動信号DQBを振動子10に出力する。こうすることで、駆動信号DQBとして、矩形波信号ではなく、正弦波信号を振動子10に出力して駆動できるようになる。

【0085】

さて、振動子を発振させるためには、振動子が有する抵抗成分（及び振動子と回路の接続に起因する接触抵抗や配線抵抗などの寄生抵抗）を、打ち消すのに十分な負性抵抗を、アクティブ回路により実現する必要がある。つまり、負性抵抗を実現する回路構成や負性抵抗の値の設定についての設計思想が重要となる。

【0086】

例えば振動子（水晶振動子）の電気的な等価回路は図8（A）に示すように表される。A1に示す等価直列抵抗R、等価直列インダクタンスL、等価直列容量Cは、機械的共振回路に相当する部分である。A2に示す容量C0の電気的要素は、アクティブ回路側の要素として、負性抵抗を考える。

【0087】

例えば図8（B）のようにインバーター回路IVを用いた通常の発振器の回路では、大きな電流を流す必要はなく、振動子が発振さえしてくれればよい。この回路では、負性抵抗RNは下式（1）のように表すことができる。

【0088】

$$RN = - (CG \times CD) / (Gm \times C0) \quad (1)$$

ここでCG、CDは、インバーター回路IVのゲート、ドレインの寄生容量でありGmはトランスクンダクタンスである。

【0089】

一方、図8（C）に示すようにジャイロセンサーの回路では、検出感度を稼ぐために大きく振動子を振動させる必要があるため、大きな駆動電流IDを流す必要がある。この回路では、負性抵抗RNは下式（2）のように表すことができる。

【0090】

$$RN = - K \times R_I \quad (2)$$

ここで、Kは、駆動信号DQBの信号増幅のゲインであり、RIは、I/V変換用の抵抗（例えば抵抗素子REの抵抗値）である。

【0091】

次に負性抵抗RNをどのような値に設定すればよいかについて考察する。図9（A）の

10

20

30

40

50

等価回路において、インピーダンス最小点である共振点は、図9(A)のC1に示す式で表すことができる。ここでC、L、Rは、振動子の等価直列容量、等価直列インダクタンス、等価直列抵抗である。

#### 【0092】

このため、 $R + RN > 0$ の場合には、図9(B)のD1に示すように共振点はS平面の左半面に位置することになる。この場合には、時間経過とともに発振の振幅は減少する。従って、やがて発振は停止することになる。

#### 【0093】

一方、 $R + RN = 0$ の場合には、図9(B)のD2に示すように共振点はS平面の虚軸上に位置し、周波数は  $s = 1 / (L \times C)^{1/2}$  と表され、一定の振幅の発振となる。そして、この場合は発振は持続する。

#### 【0094】

また、 $R + RN < 0$ の場合には、図9(B)のD3に示すように共振点はS平面の右半面に位置し、時間経過とともに発振の振幅は増大する。この場合も発振は持続する。

#### 【0095】

そして図10(A)において、I/V変換回路32の出力信号DVは、入力電流(駆動電流)をIDとした場合に、 $DV = -R_I \times ID$  と表される。そしてこの信号DVが、ゲインKで信号を増幅する駆動信号出力回路50及びバッファー回路24により増幅されるため、駆動信号はDQB =  $-K \times DV = K \times R_I \times ID$  となる。

#### 【0096】

ここで図9(B)のD1のように $R + RN > 0$ の場合には、図10(B)に示すように駆動信号DQBは、その振幅が信号DVよりも小さくなり、発振は停止する。

#### 【0097】

また、図9(B)のD2のように $R + RN = 0$ の場合には、図10(C)に示すように駆動信号DQBは、その振幅が信号DVよりも大きくなり、且つ正弦波の信号となり、発振は継続する。

#### 【0098】

一方、図9(B)のD3のように $R + RN < 0$ の場合には、図10(D)に示すように駆動信号DQBは、その振幅が、高電位側電源電圧VDD～低電位側電源電圧VSS(GND)の電圧範囲を越えてしまい、矩形波の信号になってしまふ。この場合にも発振自体は継続する。

#### 【0099】

しかしながら、図10(D)のように駆動信号DQBが矩形波信号になってしまふと、後述するように矩形波信号には高調波成分が多く含まれるため、この高調波成分が原因となって検出装置の検出性能を低下させてしまう。

#### 【0100】

一方、図10(B)のように $R + RN > 0$ の場合には、駆動信号DQBの振幅が小さくなってしまい、発振が継続せずに停止してしまう。

#### 【0101】

そこで本実施形態では、図7に示すように、I/V変換用の抵抗をRIとし、駆動信号出力回路50及びバッファー回路24でのゲインをKとし、振動子10の等価直列抵抗(寄生抵抗を含む)をRとした場合に、ゲイン制御回路40は、 $K \times R_I = R$ の関係式が成り立つようゲイン制御を行う。つまり  $K \times R_I = R$  の関係になることを目標とするゲイン制御が行われる。なお  $K \times R_I = R$  は目標となるものであり、厳密に  $K \times R_I = R$  となることは必ずしも必要ではない。

#### 【0102】

ここで上述の式(2)に示すように、本実施形態のような駆動回路30においては、負性抵抗について  $R_N = -K \times R_I$  の関係式が成り立つ。従って、 $K \times R_I = R$  となるようにゲイン制御が行われることで、 $R + RN = K \times R_I + (-K \times R_I) = 0$  が成立するようになる。従って、図10(C)に示すような正弦波による振動子10の駆動が可能にな

10

20

30

40

50

る。

【0103】

つまり、 $K \times R_I = R$  となるように設定されたゲイン制御が行われると、 $R + R_N = 0$  の関係が成り立つため、図9(B)のD2に示すように共振点がS平面の虚軸上に位置するようになる。

【0104】

そして例えば、共振点が図9(B)のD1に示すようにS平面の左半面側に移動して、図10(B)のように駆動信号DQBの振幅が小さくなるような状況になると、ゲイン制御回路40のAGCループが働いて、共振点を虚軸上に戻すゲイン制御が行われる。これにより、駆動信号DQBの振幅が小さくなつて発振が停止してしまう事態の発生を抑制できる。

10

【0105】

一方、共振点が図9(B)のD3に示すようにS平面の右半面側に移動して、図10(D)のように駆動信号DQBが矩形信号になるような状況になると、ゲイン制御回路40のAGCループが働いて、共振点を虚軸上に戻すゲイン制御が行われる。これにより、駆動信号DQBが矩形信号になつてしまい検出性能が低下してしまう事態の発生を抑制できる。

【0106】

例えば、従来では、振動子10の駆動電流を一定にすることだけを目的として、AGCループによるゲイン制御を行っていた。この場合に、ゲインKが小さいと、図10(B)に示すように駆動信号DQBの振幅が小さくなつて発振が停止してしまうため、ゲインKを、なるべく大きくするという設計手法で回路設計を行っていた。

20

【0107】

ところが、この設計手法では、ゲインKが大きな値に設定されることで、負性抵抗RN( $= -K \times R_I$ )の絶対値も大きくなつてしまつため、 $R + R_N < 0$ の関係が成り立つようになつてしまつ。従つて、結果的に、図10(D)に示すような矩形波駆動となつてしまい、高調波成分の発生により検出性能が低下してしまう事態の発生を招いていた。

【0108】

この点、本願の発明者は、図10(A)のI/V変換用の抵抗RIとゲインKとの関係に着目した。そして $K \times R_I = R$ となるAGCループによるゲイン制御を行うことで、図10(C)に示すような正弦波の駆動信号DQBによる振動子10の駆動が可能になることを見い出した。

30

【0109】

即ち、単に振動子10の駆動電流を一定にすることだけではなくて、 $K \times R_I = R$ を成立させるための回路として、AGCループを有するゲイン制御回路40を利用する。こうすることで、図9(B)のD2に示すようにS平面の虚軸上に共振点が位置するようAGCループによるゲイン制御が働くようになり、発振が停止してしまつたり、駆動信号DQBが矩形波信号になつてしまつたる事態の発生が抑制される。この結果、正弦波の駆動信号DQBによる振動子10の駆動が可能になり、検出装置の検出性能等を向上させることに成功している。

40

【0110】

### 6. 駆動回路の詳細な構成例

図11に、正弦波駆動の場合の駆動回路30の詳細な構成例を示す。

【0111】

図11において、I/V変換回路32は、ローパスフィルター特性をもつ積分型の電流-電圧変換回路であり、演算増幅器OPE、キャパシターCE、抵抗素子REを有する。ここでは、この抵抗素子REの抵抗値が電流-電圧変換用の抵抗RIとなる。演算増幅器OPEの非反転入力端子(第1の入力端子)は所定電位(例えばAGND)に設定され、反転入力端子(第2の入力端子)には振動子10からの信号DIが入力される。キャパシターCE及び抵抗素子REは、I/V変換回路32の出力ノードと演算増幅器OPEの反

50

転入力端子のノードとの間に設けられる。

【0112】

ゲイン制御回路40(AGC)は、発振定常状態において、ループゲインが1になるようにゲインを自動調整する回路であり、全波整流器42、積分器44を有する。なお、ゲイン制御回路40に、発振状態を検出する発振検出器等を含ませてもよい。

【0113】

全波整流器42は、I/V変換回路32のI/V変換後の信号DVを全波整流し、全波整流後の信号DRを積分器44に出力する。全波整流器42は、演算増幅器OPF、抵抗素子RF1、RF2、コンパレーターCP3、スイッチ素子SF1、SF2、インバータ回路INVを有する。

10

【0114】

抵抗素子RF1は、信号DVの入力ノードと演算増幅器OPFの反転入力端子のノードとの間に設けられ、抵抗素子RF2は、演算増幅器OPFの出力ノードと反転入力端子のノードとの間に設けられる。

【0115】

スイッチ素子SF1は、演算増幅器OPFの出力ノードと積分器44の入力ノードとの間に設けられ、スイッチ素子SF2は、信号DVのノードと積分器44の入力ノードとの間に設けられる。そしてスイッチ素子SF1、SF2は、信号DVの電圧と所定電位の電圧とを比較するコンパレーターCP3の出力信号に基づいて、排他的にオン・オフ制御される。これにより信号DRは、信号DVを全波整流した信号になる。

20

【0116】

積分器44は、駆動信号DQの振幅の制御電圧DSを駆動信号出力回路50に出力する。具体的には積分器44は、全波整流器42により全波整流された信号DRの積分処理を行って、積分処理により得られた制御電圧DSを駆動信号出力回路50に出力する。

【0117】

積分器44は、演算増幅器OPG、抵抗素子RG、キャパシターCGを有する。キャパシターCGは、演算増幅器OPGの出力ノードと演算増幅器OPGの反転入力端子のノードとの間に設けられる。演算増幅器OPGの非反転入力端子は所定電圧VR3に設定される。抵抗素子RGは、積分器44の入力ノードと演算増幅器OPGの反転入力端子のノードとの間に設けられる。

30

【0118】

そして本実施形態では駆動信号出力回路50が、OTA(Operational Transconductance Amplifier)回路36とI/V変換回路39(第2の電流-電圧変換回路)を有する。なお、駆動信号出力回路50の入力段側には、ハイパスフィルター34が設けられている。このハイパスフィルター34は、抵抗素子RHとキャパシターCHを有する。なお、ハイパスフィルター34の構成を省略したり、ハイパスフィルター34の代わりにローパスフィルターなどを設けるなどの種々の変形実施が可能である。

【0119】

OTA回路36は、ゲイン制御回路40からの制御電圧DSと、I/V変換回路32によるI/V変換後の入力電圧信号DV(ハイパスフィルター処理後の信号)を受ける。そしてOTA回路36は、例えば制御電圧DSによってトランスクンダクタンス(Gm)が設定されて、入力電圧信号DVを電流信号DAに変換する。I/V変換回路39は、OTA回路36からの電流信号DAのI/V変換(電流-電圧変換)を行い、駆動信号DQを出力する。

40

【0120】

OTA回路36は例えば入力電圧に比例(略比例)した電流を出力する回路であり、OTA回路36でのトランスクンダクタンスをGmとした場合に、Gmを比例定数として入力電圧信号DVを電流信号DAに変換する。そしてOTA回路36のトランスクンダクタンスGmは、積分器44からの制御電圧DSにより設定されるため、OTA回路36は、制御電圧DSに応じたトランスクンダクタンスGmで入力電圧信号DVを電流信号DAに

50

変換することになる。そして、I / V 変換回路 39 (IV2) は、OTA 回路 36 からの電流信号 DA を電圧信号に変換して、駆動信号 DQ として出力する。従って、結局、駆動信号出力回路 50 は、制御電圧 DS に応じたゲインで入力電圧信号 DV を増幅して、駆動信号 DQ を出力することになる。

【0121】

そしてバッファー回路 24 (BUF) は、駆動信号出力回路 50 からの駆動信号 DQ を受けて、駆動信号 DQ の振幅を増加させた高振幅の駆動信号 DQB を振動子 10 に出力する。

【0122】

さて、図 11 では、I / V 変換用の抵抗は RI = 40K に設定されている。この抵抗 RI は、図 11 では I / V 変換回路 32 の帰還用の抵抗素子 RE の抵抗値である。またハイパスフィルター 34 のゲインは 1 倍である。従って、入力電流信号であるフィードバック信号 DI のピーク・ツー・ピーク電流を 5 μA ppとした場合に、駆動信号出力回路 50 の入力電圧信号 DV のピーク・ツー・ピーク電圧は、VP1 = 5 μA pp × 40K = 0.2V pp となる。つまり、AGND (アナログ基準電圧) を中心電圧として、ピーク・ツー・ピーク電圧が VP1 = 0.2V pp の正弦波の入力電圧信号 DV が、駆動信号出力回路 50 に入力される。

【0123】

そして駆動信号出力回路 50 とバッファー回路 24 によるゲインは K = 7.5 倍となる。例えば駆動信号出力回路 50 (OTA 回路 36 と I / V 変換回路 39 とハイパスフィルター 34) でのゲインが 5 倍であり、バッファー回路 24 でのゲインが 1.5 倍であるため、トータルで K = 7.5 倍のゲインになる。従って、ピーク・ツー・ピーク電圧が VP2 = VP1 × K = 0.2V pp × 7.5 = 1.50V pp となる正弦波信号が、駆動信号 DQB として出力されることになる。

【0124】

一方、振動子 10 の駆動電流のピーク・ツー・ピーク電流は IDR = 5 μA に設定されており、振動子 10 の等価直列抵抗は R = 300K となっている。従って、駆動電流の観点からは、駆動信号 DQ のピーク・ツー・ピーク電圧は VP2 = 5 μA × 300K = 1.50V pp となる。これは、ゲイン K = 7.5 倍から求められた上述の VP2 = VP1 × K = 0.2V pp × 7.5 = 1.50V pp と一致する。

【0125】

このように図 11 では、入力電圧信号 DV のピーク・ツー・ピーク電圧を VP1 とし、駆動信号 DQB のピーク・ツー・ピーク電圧を VP2 とし、ゲイン制御回路 40 の AGC ループにより設定される振動子 10 の駆動電流のピーク・ツー・ピーク電流を IDP とした場合に、VP2 = K × VP1 = IDP × R の関係が成り立っている。これは、前述した K × RI = R、R + RN = 0 の関係が成立していることを意味している。例えば K = 7.5 倍、RI = 40K、R = 300K であり、K × RI = 7.5 × 40K = R が成り立っている。従って、図 9 (B) の D2 や図 10 (C) で説明した適正な正弦波駆動を実現できるようになる。

【0126】

また図 11 では、高電位側電源電圧 VDD と低電位側電源電圧 VSS (GND) の電圧差を VDS とした場合に、VDS > VP2 = K × VP1 = IDP × R の関係が成り立っている。これは、駆動信号 DQB は、その振幅が VDD ~ VSS の電圧差 VDS を越えるような矩形波信号ではなく、その振幅が電圧差 VDS を越えない正弦波信号であることを意味している。

【0127】

例えば矩形波駆動の場合には、駆動信号出力回路 50 がコンパレーターにより構成されており、矩形波の駆動信号を出力する。

【0128】

そして、この矩形駆動では、図 12 に示す駆動信号のスペクトラム図の周波数特性に示

10

20

30

40

50

すように、B 1 に示すような高調波成分が現れるため、検出装置の検出性能が低下する。これに対して図 1 1 の構成によれば、図 1 2 の B 2 に示すような周波数特性になり、矩形波駆動の場合に比べて、高調波成分が低減されて、検出装置の検出性能を向上できる。

#### 【 0 1 2 9 】

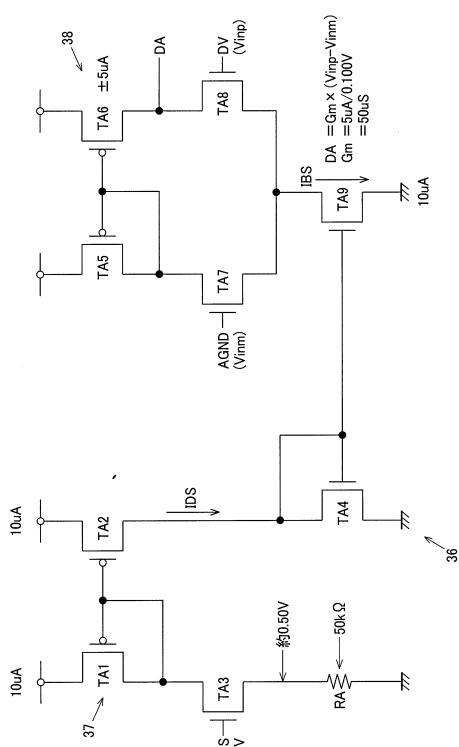

図 1 3 に O T A 回路 3 6 の具体的な構成例を示す。この O T A 回路 3 6 は、V / I 変換回路 3 7 (電圧 - 電流変換回路)、差動部 3 8 を有する。なお O T A 回路 3 6 の構成は図 1 3 に限定されず、種々の変形実施が可能である。

#### 【 0 1 3 0 】

V / I 変換回路 3 7 は、ゲイン制御回路 4 0 からの制御電圧 D S を制御電流 I D S に変換する。この V / I 変換回路 3 7 は、トランジスター T A 1、T A 2、T A 3、T A 4 と抵抗素子 R A により構成される。P 型のトランジスター T A 1、T A 2 は、そのゲートが共通接続される。N 型のトランジスター T A 3 は、そのドレインがトランジスター T A 1 のドレインに接続され、そのゲートに制御電圧 D S が入力され、そのソースが抵抗素子 R A の一端に接続される。N 型のトランジスター T A 4 は、そのドレン及びゲートがトランジスター T A 2 のドレインに接続される。

10

#### 【 0 1 3 1 】

差動部 3 8 は、制御電流 I D S により設定されるバイアス電流 I B S がバイアス電流源 (T A 9) に流れ、第 1 の差動入力端子 (反転入力端子) に、A G N D (アナログ基準電圧) が入力され、第 2 の差動入力端子 (非反転入力端子) に、入力電圧信号 D V が入力される。そして電流信号 D A を I / V 変換回路 3 9 (第 2 の電流 - 電圧変換回路) に出力する。

20

#### 【 0 1 3 2 】

差動部 3 8 は、トランジスター T A 5、T A 6、T A 7、T A 8、T A 9 により構成される。P 型のトランジスター T A 5、T A 6 は、そのゲートが共通接続される。N 型のトランジスター T A 7 は、そのドレインがトランジスター T A 5 のドレインに接続され、そのゲートに A G N D が入力され、そのソースがトランジスター T A 9 のドレインに接続される。N 型のトランジスター T A 8 は、そのドレインがトランジスター T A 6 のドレインに接続され、そのゲートに入力電圧信号 D V が入力され、そのソースがトランジスター T A 9 のドレインに接続される。N 型のトランジスター T A 9 は、バイアス電流源となるトランジスターであり、そのゲートが、V / I 変換回路 3 7 のトランジスター T A 4 のゲートと共に接続される。トランジスター T A 9 に流れるバイアス電流 I B S は、V / I 変換回路 3 7 により生成される制御電流 I D S をカレントミラーした電流となる。

30

#### 【 0 1 3 3 】

図 1 3 では、制御電圧 D S = 0 . 9 V である場合には、トランジスター T A 3 のソース電圧は 0 . 5 V 程度になるため、抵抗素子 R A には 10  $\mu$  A の電流が流れる。従って、制御電流として I D S = 10  $\mu$  A の電流が流れようになる。この制御電流 I D S により、差動部 3 8 には、バイアス電流として I B S = 10  $\mu$  A の電流が流れようになる。そして、このようにバイアス電流 I B S を設定することで、O T A 回路 3 6 は、 $\pm 5 \mu$  A の正弦波の電流信号 D A を出力できるようになる。

#### 【 0 1 3 4 】

40

一方、図 1 1 に示すように、A G N D = 0 . 9 V であり、入力電圧信号 D V は、A G N D を中心電圧とするピーク・ツー・ピーク電圧が V P 1 = 0 . 2 V p p の信号となり、 $\pm 0 . 1$  V の正弦波の電圧信号となる。従って、トランスコンダクタンス G m は、 $5 \mu$  A / (V i n p - V i n m) =  $5 \mu$  A / 0 . 1 V = 50  $\mu$  S に設定されることになる。

#### 【 0 1 3 5 】

図 1 3 の構成では、積分器 4 4 からの制御電圧 D S により制御電流 I D S が設定されて、差動部 3 8 に流れるバイアス電流 I B S が設定される。そして、このバイアス電流 I B S により、O T A 回路 3 6 のトランスコンダクタンス G m が設定される。即ち、制御電圧 D S が増減すると、制御電流 I D S 、バイアス電流 I B S も増減して、トランスコンダクタンス G m も増減する。そして O T A 回路 3 6 は、このように制御電圧 D S によって設定され

50

るトランスコンダクタンス  $G_m$  で、入力電圧信号  $D_V$  を電流信号  $D_A$  に変換する。そして  $I/V$  変換回路 39 は、この電流信号  $D_A$  の  $I/V$  変換を行って、駆動信号  $D_Q$  を出力する。そしてバッファーハイブ 24 は、この駆動信号  $D_Q$  の振幅を増加させた高振幅の駆動信号  $D_QB$  を出力する。こうすることで、制御電圧  $D_S$  によってその振幅（ピーク・ツー・ピーク電圧）が AGC 制御される正弦波の駆動信号  $D_QB$  を、振動子 10 に出力できるようになる。

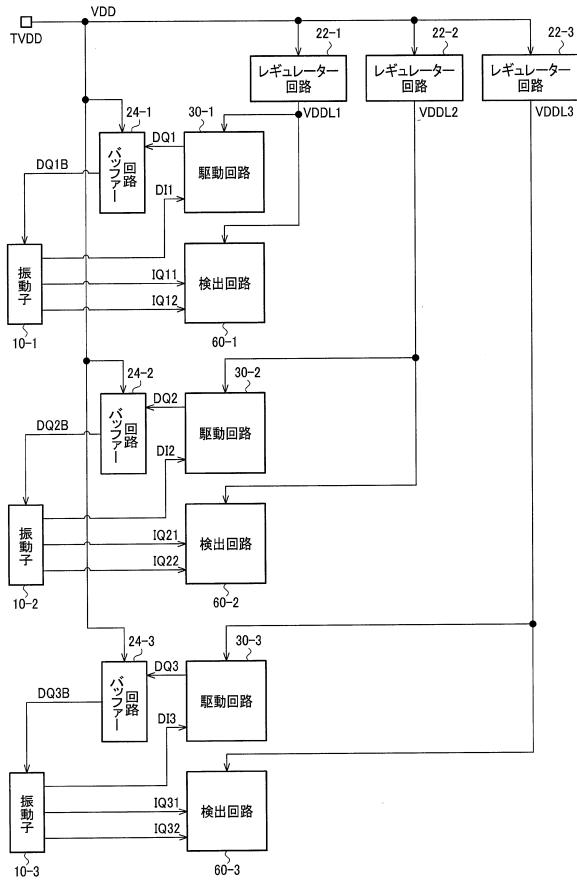

#### 【0136】

##### 7. 変形例

図 14 に本実施形態の検出装置の変形例を示す。図 14 は、複数の軸回りでの回転角速度の検出を行う多軸ジャイロセンサーの検出装置の構成例である。この構成例の検出装置は、複数の振動子 10-1、10-2、10-3 の駆動及び検出を行う。ここで、例えば、振動子 10-1 は、第 1 の軸（例えば X 軸）の回りでの回転角速度を検出するための振動子であり、振動子 10-2 は、第 2 の軸（例えば Y 軸）の回りでの回転角速度を検出するための振動子である。また振動子 10-3 は第 3 の軸（例えば Z 軸）の回りでの回転角速度を検出するための振動子である。

10

#### 【0137】

多軸ジャイロセンサーでは、いわゆる軸間干渉が問題になる。例えば本実施形態の比較例の手法として、検出装置の全ての回路を電源電圧  $V_{DD}$  を動作電源電圧として動作させる手法が考えられる。しかしながら、この比較例の手法では、例えば第 1 の軸用の駆動回路、検出回路が動作することで生じる電源電圧  $V_{DD}$  の微少な変動等が、第 2 の軸用、第 3 の軸用の駆動回路、検出回路に悪影響を及ぼす軸間干渉が生じ、検出性能の低下等の問題を招くおそれがある。特に、複数の各振動子の駆動周波数が互いに異なる場合に大きな問題となる。このような問題を解決するために本実施形態では図 14 に示す構成を採用している。

20

#### 【0138】

具体的には図 14 では、振動子 10-1 用のレギュレーター回路 22-1、バッファーハイブ 24-1、駆動回路 30-1、検出回路 60-1 と、振動子 10-2 用のレギュレーター回路 22-2、バッファーハイブ 24-2、駆動回路 30-2、検出回路 60-2 とが設けられる。また振動子 10-3 用のレギュレーター回路 22-3、バッファーハイブ 24-3、駆動回路 30-3、検出回路 60-3 が設けられる。なお、図 14 は、振動子が 3 つの場合の例であるが、振動子が 2 つの場合には、振動子 10-3 用のレギュレーター回路 22-3、バッファーハイブ 24-3、駆動回路 30-3、検出回路 60-3 の構成は不要となる。

30

#### 【0139】

振動子 10-1 用のレギュレーター回路 22-1、バッファーハイブ 24-1、駆動回路 30-1、検出回路 60-1 の構成及び動作は、図 2 のレギュレーター回路 22、バッファーハイブ 24、駆動回路 30、検出回路 60 と同様であるため、詳細な説明を省略する。

#### 【0140】

振動子 10-2 用の駆動回路 30-2（第 2 の駆動回路）は、振動子 10-2（第 2 の物理量トランスデューサー）からのフィードバック信号  $D_{I2}$ （第 2 のフィードバック信号）を受けて、振動子 10-2 を駆動する。検出回路 60-2（第 2 の検出回路）は、振動子 10-2 からの検出信号  $I_{Q21}$ 、 $I_{Q22}$  を受けて、所望信号を検出する。

40

#### 【0141】

レギュレーター回路 22-2（第 2 のレギュレーター回路）は、電源端子  $T_{VDD}$  からの電源電圧  $V_{DD}$  を降圧する電圧調整を行い、電圧調整により得られたレギュレート電源電圧  $V_{DDL2}$ （第 2 のレギュレート電源電圧）を駆動回路 30-2 及び検出回路 60-2 に出力する。

#### 【0142】

そしてバッファーハイブ 24-2（第 2 のバッファーハイブ）は、電源電圧  $V_{DD}$  が供給され、駆動回路 30-2 からの駆動信号  $D_{Q2}$ （第 2 の駆動信号）を受けて、駆動信号  $D_{Q2B}$  の振幅を増加させた高振幅の駆動信号  $D_{Q2B}$ （第 2 の增幅駆動信号）を振動子 10-2 に出力する。

50

力する。

【0143】

振動子10-3用の駆動回路30-3(第3の駆動回路)は、振動子10-3(第3の物理量トランスデューサー)からのフィードバック信号DI3(第3のフィードバック信号)を受けて、振動子10-3を駆動する。検出回路60-3(第3の検出回路)は、振動子10-3からの検出信号IQ31、IQ32を受けて、所望信号を検出する。

【0144】

レギュレーター回路22-3(第3のレギュレーター回路)は、電源端子TVDDからの電源電圧VDDを降圧する電圧調整を行い、電圧調整により得られたレギュレート電源電圧VDDL3(第3のレギュレート電源電圧)を駆動回路30-3及び検出回路60-3に出力する。

10

【0145】

そしてバッファー回路24-3(第3のバッファー回路)は、電源電圧VDDが供給され、駆動回路30-3からの駆動信号DQ3(第3の駆動信号)を受けて、駆動信号DQ3の振幅を増加させた高振幅の駆動信号DQ3B(第3の増幅駆動信号)を振動子10-3に出力する。

【0146】

以上の図14の構成によれば、電源電圧VDDをレギュレーター回路22-1、22-2、22-3において降圧する電圧調整が行われる。そして得られたレギュレート電源電圧VDD1、VDDL2、VDDL3が、各々、駆動回路30-1及び検出回路60-1、駆動回路30-2及び検出回路60-2、駆動回路30-3及び検出回路60-3に、動作電源電圧として供給される。従って、軸間干渉を最小限に抑えることができる。例えば第1の軸用の駆動回路30-1、検出回路60-1が動作したことによる電源電圧変動が、他の第2の軸用、第3の軸用の駆動回路30-2、30-3、検出回路60-2、60-3に伝達されてしまうのを、レギュレーター回路22-1、22-2、22-3により、最小限に抑制できる。従って、多軸ジャイロセンサーの軸間干渉を低減して検出性能の向上を図れるようになる。

20

【0147】

そして図14では、バッファー回路24-1、24-2、24-3については、レギュレート電源電圧ではなく端子TVDDにより外部から入力される電源電圧VDDで動作させて、高振幅の駆動信号DQ1B、DQ2B、DQB3を生成している。従って、高振幅の駆動による起動時間の短縮と、軸間干渉の低減による検出性能の向上とを両立して実現できる。

30

【0148】

また図14では、図5(A)で説明した第1のモードにおいて、検出装置は、バッファー回路24-1からの高振幅の駆動信号DQ1Bを、振動子10-1に出力する。同様に検出装置は、第1のモードでは、バッファー回路24-2、24-3からの高振幅の駆動信号DQ2B、DQ3Bを、振動子10-2、10-3に出力する。

【0149】

一方、図5(B)で説明した第2のモードでは、検出装置は、駆動回路30-1からの低振幅の駆動信号DQ1を振動子10-1に出力する。同様に検出装置は、第2のモードでは、駆動回路30-2、30-3からの低振幅の駆動信号DQ2、DQ3を振動子10-2、10-3に出力する。

40

【0150】

例えば発振の起動期間においては、所望信号の検出は行われないため、前述の軸間干渉は大きな問題とならない。従って、起動期間においては検出装置を第1のモードに設定して、高振幅の駆動信号DQ1B～DQ3Bで振動子10-1～10-3を駆動するようにする。一方、発振の起動期間が完了した後は、軸間干渉等による検出性能の低下を抑制するために、低振幅の駆動信号DQ1～DQ3で振動子10-1、10-2、10-3を駆動するようになる。こうすることで、多軸ジャイロセンサー等において発振の起動時間の短縮と検出性能の向上とを両立して実現できるようになる。

50

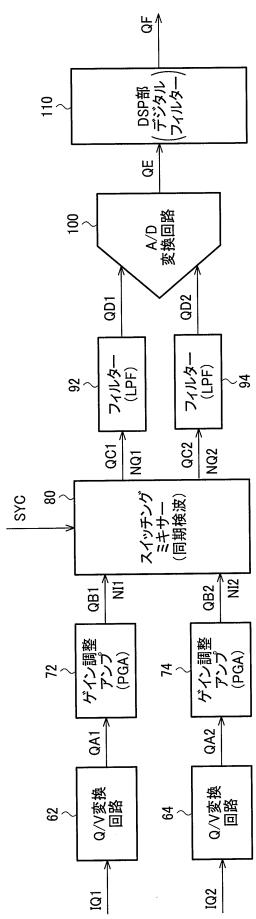

## 【0151】

## 8. 検出回路

図15に検出回路60の詳細な構成例を示す。図15は全差動スイッチングミキサー方式の検出回路60の例である。

## 【0152】

図15に示すように、全差動スイッチングミキサー方式の検出回路60は、第1、第2のQ/V変換回路62、64、第1、第2のゲイン調整アンプ72、74、スイッチングミキサー80、第1、第2のフィルター92、94、A/D変換回路100、DSP部110（デジタル信号処理部）を含む。

## 【0153】

Q/V変換回路62、64（電荷-電圧変換回路）には振動子10からの差動の第1、第2の検出信号IQ1、IQ2が入力される。そしてQ/V変換回路62、64は振動子10で発生した電荷（電流）を電圧に変換する。

## 【0154】

ゲイン調整アンプ72、74は、Q/V変換回路62、64の出力信号QA1、QA2をゲイン調整して増幅する。ゲイン調整アンプ72、74は、いわゆるプログラマブルゲインアンプであり、制御部140により設定されたゲインで信号QA1、QA2を増幅する。例えばA/D変換回路100の電圧変換範囲に適合する振幅の信号に増幅する。

## 【0155】

スイッチングミキサー80は、駆動回路30からの同期信号SYCに基づいて差動の同期検波を行うミキサーである。具体的にはスイッチングミキサー80では、ゲイン調整アンプ72の出力信号QB1が第1の入力ノードNI1に入力され、ゲイン調整アンプ74の出力信号QB2が第2の入力ノードNI2に入力される。そして駆動回路30からの同期信号SYCにより差動の同期検波を行って、差動の第1、第2の出力信号QC1、QC2を第1、第2の出力ノードNQ1、NQ2に出力する。このスイッチングミキサー80により、前段の回路（Q/V変換回路、ゲイン調整アンプ）が発生したノイズ（1/fノイズ）などの不要信号が高周波帯域に周波数変換される。また、コリオリ力に応じた信号である所望信号が直流信号に落とし込まれる。

## 【0156】

フィルター92には、スイッチングミキサー80の第1の出力ノードNQ1からの第1の出力信号QC1が入力される。フィルター94には、スイッチングミキサー80の第2の出力ノードNQ2からの第2の出力信号QC2が入力される。これらのフィルター92、94は、例えば不要信号を除去（減衰）して所望信号を通過させる周波数特性を有するローパスフィルターである。例えばスイッチングミキサー80により高周波帯域に周波数変換された1/fノイズ等の不要信号は、フィルター92、94により除去される。またフィルター92、94は、演算増幅器を用いずに、抵抗素子やキャパシターなどのパッシブ素子で構成されるパッシブフィルターである。

## 【0157】

A/D変換回路100は、フィルター92からの出力信号QD1とフィルター94からの出力信号QD2を受けて、差動のA/D変換を行う。具体的には、A/D変換回路100は、フィルター92、94をアンチエイリアシング用のフィルター（前置きフィルター）として、出力信号QD1、QD2のサンプリングを行ってA/D変換を行う。そして本実施形態では、フィルター92からの出力信号QD1及びフィルター94からの出力信号QD2は、アクティブ素子を介さずにA/D変換回路100に入力される。A/D変換回路100としては、例えばシグマ型や逐次比較型などの種々の方式のA/D変換回路を採用できる。シグマ型を採用する場合には、例えば1/fノイズ低減のためのCDS（Correlated double sampling）やチョッパーの機能などを有し、例えば2次のシグマ変調器などにより構成されるA/D変換回路を用いることができる。

## 【0158】

DSP（Digital Signal Processing）部110は、各種のデジタル信号処理を行う。

10

20

30

40

50

例えばDSP部110は、例えば所望信号のアプリケーションに応じた帯域制限のデジタルフィルター処理や、A/D変換回路100等により発生したノイズを除去するデジタルフィルター処理を行う。また、ゲイン補正（感度調整）、オフセット補正などのデジタル補正処理を行う。

【0159】

図15の検出回路60では、全差動スイッチングミキサー方式を採用している。即ち、振動子10からの差動の検出信号IQ1、IQ2は、Q/V変換回路62、64、ゲイン調整アンプ72、74により信号増幅やゲイン調整が行われて、差動の信号QB1、QB2としてスイッチングミキサー80に入力される。そして、これらの差動の信号QB1、QB2に対して、スイッチングミキサー80により、不要信号が高周波帯域に周波数変換される同期検波処理が行われる。そして、フィルター92、94により、高周波帯域に周波数変換された不要信号が除去されて、差動の信号QD1、QD2としてA/D変換回路100に入力されて、差動のA/D変換が行われる。

10

【0160】

このような全差動スイッチングミキサー方式の検出回路60によれば、Q/V変換回路62、64やゲイン調整アンプ72、74で発生した1/fノイズ等は、スイッチングミキサー80での周波数変換とフィルター92、94によるローパスフィルター特性により除去される。そしてゲイン調整アンプ72、74とA/D変換回路100の間には、ゲインは稼げないが発生ノイズが少ない（1/fノイズが発生しない）スイッチングミキサー80や、低ノイズのパッシブ素子により構成されるフィルター92、94が設けられる構成となっている。従って、Q/V変換回路62、64やゲイン調整アンプ72、74で発生したノイズが除去されると共に、スイッチングミキサー80やフィルター92、94が発生するノイズも最小限に抑えられるため、低ノイズの状態の信号QD1、QD2をA/D変換回路100に入力して、A/D変換できるようになる。しかも、信号QD1、QD2を差動信号としてA/D変換できるため、シングルエンドの信号でA/D変換する場合に比べて、S/N比を更に向上できるようになる。

20

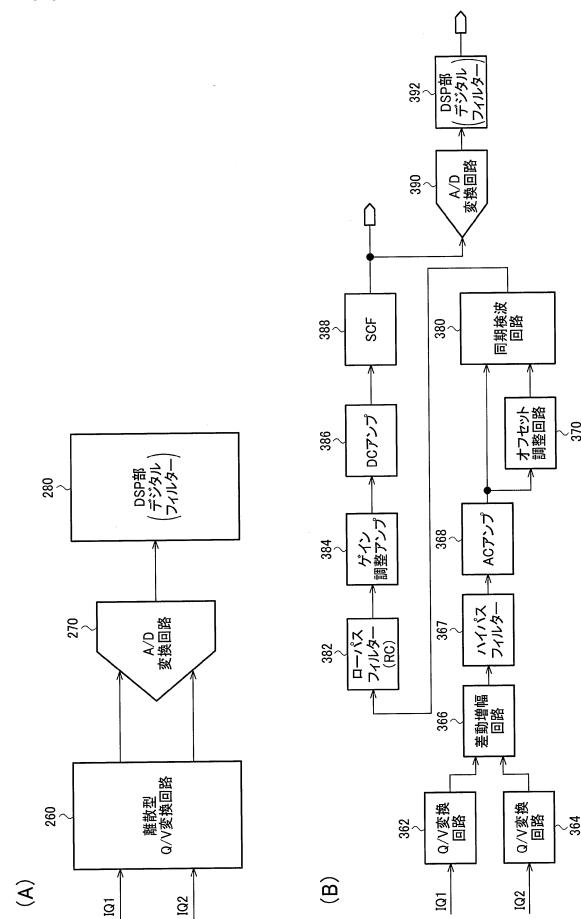

【0161】

なお本実施形態の検出回路60は、図15に示す全差動スイッチングミキサー方式には限定されない。例えば図16（A）に示すダイレクトサンプリング方式や、図16（B）に示すアナログ同期検波方式などの種々の方式の検出回路60を採用できる。

30

【0162】

図16（A）のダイレクトサンプリング方式の検出回路60は、離散型Q/V変換回路260、A/D変換回路270、DSP部280を有する。このダイレクトサンプリング方式は、回路の小規模化という意味において優位な構成となる。但し、A/D変換回路270の前段にアンチエイリアシング用のフィルターがないため、折り返し雑音による性能劣化は避けられないという課題がある。これに対して図15の全差動スイッチングミキサー方式では、Q/V変換回路62、64は、帰還抵抗素子を有する連続型の電荷-電圧変換回路となっているため、ダイレクトサンプリング方式で生じる折り返し雑音による性能劣化の問題を防止でき、小規模の回路構成で低ノイズでの検出処理を実現できるという利点がある。

40

【0163】

図16（B）のアナログ同期検波方式の検出回路60は、Q/V変換回路362、364、差動増幅回路366、ハイパスフィルター367、ACアンプ368、オフセット調整回路370、同期検波回路380、ローパスフィルター382、ゲイン調整アンプ384、DCアンプ386、SCF388（スイッチトキャパシターフィルター）を有する。また、例えば検出装置の外付けの回路として、A/D変換回路390やDSP部392（デジタルフィルター）が設けられている。

【0164】

このアナログ同期検波方式では、例えば検出回路60での信号のゲインを大きくとることで、ノイズ特性を向上できるという利点がある。但し、回路ブロック数が多くなり、回

50

路が大規模化したり、電流を多く消費するアナログの回路ブロックが多いため、消費電力が過大になってしまいうとい課題がある。これに対して図15の全差動スイッチングミキサー方式は、アナログ同期検波方式に比べて回路ブロック数が少なく、回路の小規模化や消費電力の低減化を容易に実現できるという利点がある。また全差動スイッチングミキサー方式では、振動子10からの差動の信号IQ1、IQ2は、差動信号の状態のままで、ゲイン調整、同期検波処理、フィルター処理が行われ、A/D変換回路100に入力されてA/D変換が行われる。このため、シングルエンド信号の状態でフィルター処理、同期検波処理、ゲイン調整処理等が行われるアナログ同期検波方式に比べて、ノイズ低減の点で有利な構成となる。

## 【0165】

10

なお、本実施形態のジャイロセンサー510（センサー）は、例えば、車、飛行機、バイク、自転車、或いは船舶等の種々の移動体に組み込むことができる。移動体は、例えばエンジンやモーター等の駆動機構、ハンドルや舵等の操舵機構、各種の電子機器を備えて、地上や空や海上を移動する機器・装置である。

## 【0166】

図17は移動体の一具体例としての自動車206を概略的に示す。自動車206には振動子10及び検出装置20を有するジャイロセンサー510が組み込まれる。ジャイロセンサー510は車体207の姿勢を検出することができる。ジャイロセンサー510の検出信号は車体姿勢制御装置208に供給されることができる。車体姿勢制御装置208は例えば車体207の姿勢に応じてサスペンションの硬軟を制御したり個々の車輪209のブレーキを制御したりすることができる。その他、こういった姿勢制御は二足歩行ロボットや航空機、ヘリコプター等の各種移動体で利用されることができる。姿勢制御の実現にあたってジャイロセンサー510は組み込まれることができる。

20

## 【0167】

なお、上記のように本実施形態について詳細に説明したが、本発明の新規事項および効果から実体的に逸脱しない多くの変形が可能であることは当業者には容易に理解できるであろう。従って、このような変形例はすべて本発明の範囲に含まれるものとする。例えば、明細書又は図面において、少なくとも一度、より広義または同義な異なる用語（センサー、物理量トランスデューサー、物理量等）と共に記載された用語（ジャイロセンサー、振動子、角速度情報等）は、明細書又は図面のいかなる箇所においても、その異なる用語に置き換えることができる。また、検出装置やセンサーや電子機器や移動体の構成、振動子の構造等も、本実施形態で説明したものに限定されず、種々の変形実施が可能である。

30

## 【符号の説明】

## 【0168】

OPE、OPF、OPG、OPK、OPM 演算増幅器、

CP3 コンパレーター、CE、CG、CH、CK キャパシター、

RE、RF1、RF2、RG、RH、RK、RM1、RM2 抵抗素子、

SF1、SF2、SWM、SWM1、SWM2 スイッチ素子、

TA1～TA9 トランジスター、

10 振動子、20 検出装置、22、22-1～22-3 レギュレーター回路、

24、24-1～24-3 バッファ回路、

30、30-1～30-3 駆動回路、32 増幅回路（I/V変換回路）、

34 ハイパスフィルター、36 OTA回路、

37 V/I変換回路（電圧-電流変換回路）、38 差動部、

39 I/V変換回路（第2の電流-電圧変換回路）、40 ゲイン制御回路、

42 全波整流器、44 積分器、50 駆動信号出力回路、52 同期信号出力回路、

60、60-1～60-3 検出回路、61 増幅回路、62、64 Q/V変換回路、

72、74 ゲイン調整アンプ、80 スイッチングミキサー、81 同期検波回路、

92、94 フィルター、100 A/D変換回路、110 DSP部、140 制御部

40

、

50

206 移動体(自動車)、207 車体、208 車体姿勢制御装置、209 車輪、

260 離散型Q/V変換回路、270 A/D変換回路、280 DSP部、

362、364 Q/V変換回路、366 差動増幅回路、

367 ハイパスフィルター、368 ACアンプ、370 オフセット調整回路、

380 同期検波回路、382 ローパスフィルター、384 ゲイン調整アンプ、

386 DCアンプ、388 SCF、390 A/D変換回路、392 DSP部、

500 電子機器、510 ジャイロセンサー、520 処理部、530 メモリー、

540 操作部、550 表示部

【 义 1 】

【 四 2 】

【図3】

【図4】

【図5】

【図6】

【 义 7 】

【 図 8 】

## 【図9】

【 図 1 0 】

【 図 1 1 】

## 【図 1 2】

【 図 1 3 】

### 【図 1-4】

【図15】

【図16】

【図17】

---

フロントページの続き

(72)発明者 野宮 崇

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

審査官 梶田 真也

(56)参考文献 特開2010-169408 (JP, A)

特開2008-099257 (JP, A)

特開2009-229447 (JP, A)

特開平06-265358 (JP, A)

特開平08-307199 (JP, A)

特開2008-096244 (JP, A)

米国特許出願公開第2011/0146403 (US, A1)

(58)調査した分野(Int.Cl., DB名)

|        |           |   |               |

|--------|-----------|---|---------------|

| G 01 C | 1 9 / 5 6 | - | 1 9 / 5 7 8 3 |

| G 01 P | 7 / 0 0   | - | 1 1 / 0 2     |

| G 01 P | 1 5 / 0 0 | - | 2 1 / 0 2     |

| H 01 L | 2 7 / 2 0 |   |               |

| H 01 L | 2 9 / 8 4 |   |               |

| H 01 L | 4 1 / 0 0 | - | 4 1 / 4 7     |

| H 03 B | 5 / 3 0   | - | 5 / 4 2       |

| H 03 F | 3 / 4 5   |   |               |

| H 03 H | 3 / 0 0 7 | - | 3 / 0 6       |

| H 03 H | 9 / 0 0   | - | 9 / 1 3 5     |

| H 03 H | 9 / 1 5   | - | 9 / 2 4       |

| H 03 H | 9 / 3 0   | - | 9 / 4 0       |

| H 03 H | 9 / 4 6   | - | 9 / 6 2       |

| H 03 H | 9 / 6 6   |   |               |

| H 03 H | 9 / 7 0   |   |               |

| H 03 H | 9 / 7 4   |   |               |