(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-284710

(P2005-284710A)

(43) 公開日 平成17年10月13日(2005.10.13)

(51) Int.C1.<sup>7</sup>G05F 3/26

H01L 33/00

H03K 17/06

F 1

G05F 3/26

H01L 33/00

H03K 17/06

テーマコード(参考)

5FO41

5H420

5J055

(43) 公開日 平成17年10月13日(2005.10.13)

審査請求 未請求 請求項の数 7 O L (全 12 頁)

(21) 出願番号

(22) 出願日特願2004-97607 (P2004-97607)

平成16年3月30日 (2004.3.30)(71) 出願人 000001889

三洋電機株式会社

大阪府守口市京阪本通2丁目5番5号

(74) 代理人 100107906

弁理士 須藤 克彦

(72) 発明者 河井 周平

大阪府守口市京阪本通2丁目5番5号 三

洋電機株式会社内

(72) 発明者 尾形 貴重

大阪府守口市京阪本通2丁目5番5号 三

洋電機株式会社内

(72) 発明者 鈴木 達也

大阪府守口市京阪本通2丁目5番5号 三

洋電機株式会社内

最終頁に続く

(54) 【発明の名称】駆動回路

## (57) 【要約】

【課題】 発光素子の駆動電流を得るための駆動回路のパターン面積を小さくするとともに、効率改善を図る。

【解決手段】 白色LED25のアノード26には正の電源電圧Vddが印加され、そのカノード27には、Nチャネル型MOSトランジスタM42を介して、-0.5Vddが印加される。-0.5Vdd発生回路40は、クロック発生回路30からのクロックに応じて、電圧-0.5Vddを発生する回路である。白色LED25のアノード・カソード間に図6の駆動回路と等価的に1.5Vddの電圧が印加される。-0.5Vdd発生回路40では、Nチャネル型MOSトランジスタが多用される結果、従来と同等のLED25の駆動電流を得るための回路のパターン面積を小さくできる。また、それにより寄生容量が小さくなり、駆動回路の効率改善を実現できる。

【選択図】図1

## 【特許請求の範囲】

## 【請求項 1】

発光素子に電流を供給する駆動回路において、前記発光素子に電流を供給する駆動トランジスタと、正の電源電圧  $V_{dd}$  に応じた負の電圧を発生する負電圧発生回路とを備え、前記発光素子のアノードに前記正の電源電圧を印加し、前記発光素子のカソードに前記駆動トランジスタを介して前記負の電圧を印加することを特徴とする駆動回路。

## 【請求項 2】

前記負の電圧は  $-0.5V_{dd}$  であることを特徴とする請求項 1 に記載の駆動回路。

## 【請求項 3】

前記負電圧発生回路は、入力端子に接地電圧が印加された第 1 のスイッチング素子と、この第 1 のスイッチング素子と直列に接続された第 2 のスイッチング素子と、一方の端子にクロックが供給された第 1 のコンデンサと、一方の端子が前記第 1 のスイッチング素子と前記第 2 のスイッチング素子との接続点に接続された第 2 のコンデンサと、前記第 2 のコンデンサの他方の端子と接地電圧の間に接続された第 3 のスイッチング素子と、前記第 1 のコンデンサの他方の端子と前記第 2 のコンデンサの他方の端子の間に接続された第 4 のスイッチング素子と、前記第 1 のコンデンサの他方の端子と前記第 2 のスイッチング素子の出力端子に接続された第 5 のスイッチング素子と、を備え、

前記クロックが第 1 の電圧レベルのときに、前記第 1 、第 4 のスイッチング素子をオンして前記第 1 及び第 2 のコンデンサを前記第 1 のスイッチング素子を介して前記第 1 の電圧レベルと接地電圧との間に直列に接続して充電し、前記クロックが第 2 の電圧レベルのときに、前記第 5 のスイッチング素子をオンして、前記第 1 のコンデンサを接地電圧と前記出力端子との間に接続して放電すると共に、前記第 2 及び第 3 のスイッチング素子をオンして前記第 2 のコンデンサを前記第 2 のスイッチング素子を介して接地電圧と前記出力端子との間に接続して放電し、

少なくとも前記第 1 、第 2 、第 3 及び第 5 のスイッチング素子を N チャネル型 MOS トランジスタで構成したことを特徴とする請求項 2 に記載の駆動回路。

## 【請求項 4】

前記第 4 のスイッチング素子を N チャネル型 MOS トランジスタで構成したことを特徴とする請求項 3 に記載の駆動回路。

## 【請求項 5】

前記第 4 のスイッチング素子を P チャネル型 MOS トランジスタで構成したことを特徴とする請求項 3 に記載の駆動回路。

## 【請求項 6】

前記駆動トランジスタをカレントミラー型の N チャネル型 MOS トランジスタで構成したことを特徴とする請求項 1 乃至請求項 5 のいずれかに記載の駆動回路。

## 【請求項 7】

前記発光素子は白色発光ダイオードであることを特徴とする請求項 1 乃至請求項 6 のいずれかに記載の駆動回路。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、駆動回路に関し、特に発光素子を駆動するための駆動回路に関する。

## 【背景技術】

## 【0002】

従来、液晶表示パネルのバックライト用として白色発光ダイオード（以下、白色 LED と称する）が用いられている。この白色 LED は  $3.2V \sim 3.8V$  の VF ( 順方向しきい値電圧 ) を有するため、白色 LED を発光させるために、この VF 程度の電圧を白色 LED のアノード・カソード間に印加する必要がある。ところで、白色 LED の駆動回路の動作電源電圧の規格として、例えば  $2.7V \sim 5.5V$  という電源電圧範囲が要求されているため、電源電圧  $V_{dd}$  がある程度低い場合には電源電圧  $V_{dd}$  を 1.5 倍に昇圧して

10

20

30

40

50

白色LEDに供給していた。

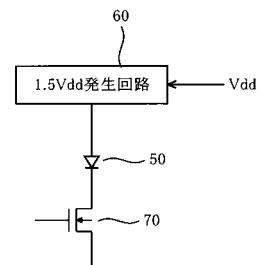

【0003】

図6は、かかる白色LEDを駆動するための駆動回路の回路図である。図6において、白色LED50のアノードには1.5Vdd昇圧回路60から1.5Vddという昇圧電圧が供給され、白色LED50のカソードにはドライバートランジスタ70を介して接地電圧Vss(0V)が印加される。1.5Vdd昇圧回路60は、電源電圧Vddから1.5Vddを生成する回路である。かかる1.5Vdd昇圧回路60は、特許文献1に開示されている。

【特許文献1】特開2001-231249号公報

10

【発明の開示】

【発明が解決しようとする課題】

【0004】

しかしながら、1.5Vdd昇圧回路60では回路構成上の制約からPチャネル型MOSトランジスタが多用されるため、駆動回路のパターン面積が大きくなるという問題を有していた。

【課題を解決するための手段】

【0005】

そこで、本発明の駆動回路は、正の電源電圧Vddに応じた負の電圧を発生する負電圧発生回路を設けることで、発光素子のアノードに正の電源電圧を印加し、発光素子のカソードに駆動トランジスタを介して負の電圧を印加することを特徴とするものである。

また、上記構成において、負の電圧は-0.5Vddであることを特徴とするものである。

【0006】

さらにまた、上記構成において、前記負電圧発生回路は、接地電圧が印加された第1のスイッチング素子と、この第1のスイッチング素子と直列に接続された第2のスイッチング素子と、一方の端子にクロックが供給された第1のコンデンサと、一方の端子が前記第1のスイッチング素子と前記第2のスイッチング素子との接続点に接続された第2のコンデンサと、前記第2のコンデンサの他方の端子と接地電圧の間に接続された第3のスイッチング素子と、前記第1のコンデンサの他方の端子と前記第2のコンデンサの他方の端子の間に接続された第4のスイッチング素子と、前記第1のコンデンサの他方の端子と前記第2のスイッチング素子の出力端子に接続された第5のスイッチング素子と、を備え、前記クロックが第1の電圧レベルのときに、前記第1、第4のスイッチング素子をオンして前記第1及び第2のコンデンサを前記第1のスイッチング素子を介して前記第1の電圧レベルと接地電圧との間に直列に接続して充電し、前記クロックが第2の電圧レベルのときに、前記第5のスイッチング素子をオンして、前記第1のコンデンサを接地電圧と前記出力端子との間に接続して放電すると共に、前記第2及び第3のスイッチング素子をオンして前記第2のコンデンサを前記第2のスイッチング素子を介して接地電圧と前記出力端子との間に接続して放電し、少なくとも前記第1、第2、第3及び第5のスイッチング素子をNチャネル型MOSトランジスタで構成したことを特徴とするものである。

30

【発明の効果】

【0007】

本発明によれば、発光素子の電源として、従来のような正電圧昇圧回路の代わりに、負電圧発生回路を用いているので、Nチャネル型MOSトランジスタが多用されるようになる結果、正電圧昇圧回路に比して、MOSトランジスタのパターン面積を小さくできる。その分、駆動回路のパターン面積も小さくできる。また、MOSトランジスタのパターン面積が小さくなることから、それに付随した寄生容量も低減され、その分消費電流も低減され、駆動回路の効率向上を図ることができる。

【発明を実施するための最良の形態】

【0008】

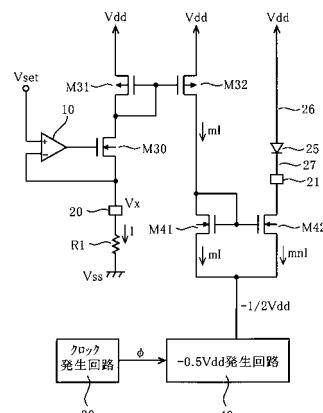

次に本発明の実施形態について、図面を参照しながら説明する。図1は、本実施形態に

40

50

係る駆動回路の回路図である。ボルテージフォロワ用のオペアンプ 10 の正入力端子(+)には電圧  $V_{set}$  が印加され、その出力はNチャネル型MOSトランジスタM30のゲートに印加され、負入力端子(-)はNチャネル型MOSトランジスタM30のソースに接続されている。ソースは端子20に接続され、端子20と接地電圧  $V_{ss}$  の間に外付け抵抗  $R_1$  が接続されている。したがって、端子20の電圧  $V_x$  は電圧  $V_{set}$  に等しくなるようオペアンプ10によって制御され、その結果、外付け抵抗  $R_1$  には電流  $I$  ( $= V_{set} / R_1$ ) が発生する。この電流  $I$  は、第1のカレントミラー回路を構成する一対のPチャネル型MOSトランジスタM31, M32(電流比  $1 : m$ ) に流れる。

#### 【0009】

そして、この電流  $I$  は第1のカレントミラー回路が折り返された第2のカレントミラー回路に入力される。第2のカレントミラー回路は一対のNチャネル型MOSトランジスタM41, M42(電流比  $1 : n$ ) から構成される。そして、駆動トランジスタであるNチャネル型MOSトランジスタM42には電流  $I$  が  $m \times n$  倍された電流  $m n I$  が流れ、この大きな電流  $m n I$  が端子21に外付けされた白色LED25に供給されることになる。

#### 【0010】

白色LED25のアノード26には正の電源電圧  $V_{dd}$  が印加され、そのカノード27には、Nチャネル型MOSトランジスタM42を介して、-0.5  $V_{dd}$  発生回路40からの電圧 -0.5  $V_{dd}$  が印加される。-0.5  $V_{dd}$  発生回路40は、クロック発生回路30からのクロックに応じて、電圧 -0.5  $V_{dd}$  を発生する回路である。

#### 【0011】

したがって、本実施形態によれば、白色LED25のアノード・カソード間には図6の駆動回路と等価的に 1.5  $V_{dd}$  の電圧が印加されることになり、しかも駆動トランジスタであるNチャネル型MOSトランジスタM42によって大電流を流すことが可能である。また、-0.5  $V_{dd}$  発生回路40では、後述するようにNチャネル型MOSトランジスタが多用される結果、従来と同等のLED25の駆動電流  $n I$  を得るための回路のパターン面積を小さくでき、さらに効率改善も実現している。

#### 【0012】

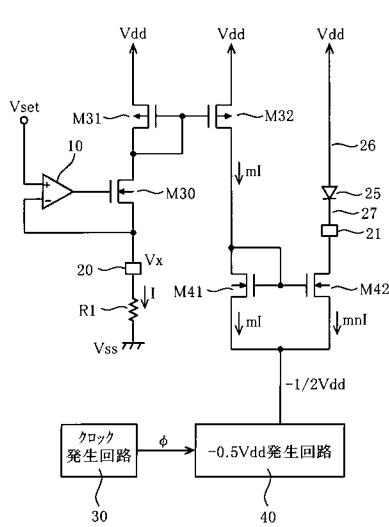

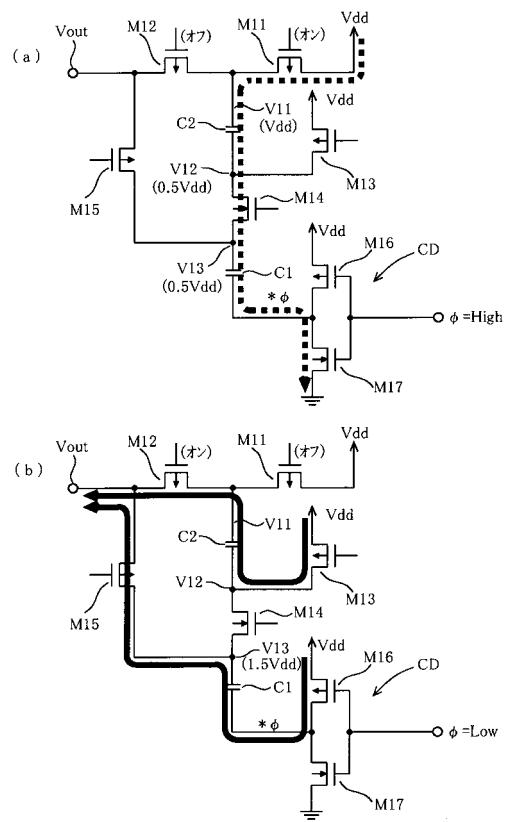

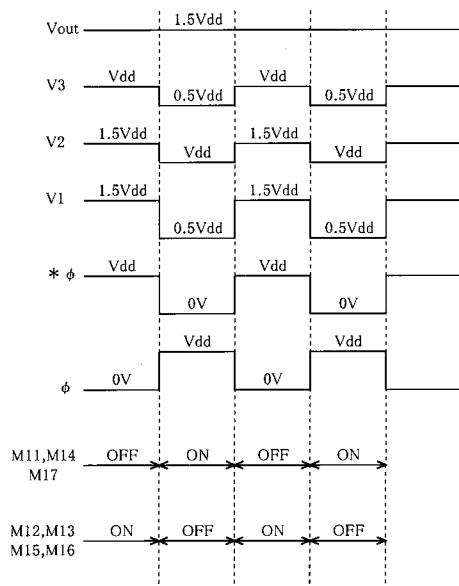

次に、-0.5  $V_{dd}$  発生回路40の具体的な回路構成及び動作について図面を参照しながら説明する。図2は、-0.5  $V_{dd}$  発生回路40の回路図であり、図2(a)は、クロックドライバーCDの入力クロックであるクロックがLowレベル(ロウレベル)の場合、図2(b)はクロックがHighレベル(ハイレベル)の場合を示している。第1のスイッチング用MOSトランジスタM1のソースに接地電圧  $V_{ss}$  (0V) が印加され、この第1のスイッチング用MOSトランジスタM1のドレインは、第2のスイッチング用MOSトランジスタM2のソースに接続されている。第1のスイッチング用MOSトランジスタM1及び第2のスイッチング用MOSトランジスタM2は、電荷転送素子として機能する。

#### 【0013】

ここで、第1のスイッチング用MOSトランジスタM1及び第2のスイッチング用MOSトランジスタM2は、いずれもNチャネル型である。これは、第1のスイッチング用MOSトランジスタM1及び第2のスイッチング用MOSトランジスタM2をオンオフさせるための電圧を同じ回路内から得るためである。第1のスイッチング用MOSトランジスタM1及び第2のスイッチング用MOSトランジスタM2をオンさせるためにはそれらのゲートに電源電圧  $V_{dd}$  を与えればよいし、オフさせる場合にはそれらのゲートにこの回路の出力電圧  $V_{out}$  ( $= -0.5 V_{dd}$ ) を与えればよい。

#### 【0014】

また、第1のコンデンサC1の一方の端子には、クロックドライバーCDの出力が接続されている。クロックドライバーCDは、電源電圧  $V_{dd}$  と接地電圧  $V_{ss}$  の間に、Pチャネル型MOSトランジスタM6、Nチャネル型MOSトランジスタM7を直列に接続してCMOSインバータとして構成される。そして、クロックドライバーCDにはクロックが入力され、このクロックはクロックドライバーCDによって反転される。その反転

10

20

30

40

50

クロック\* が、クロックドライバーCDの出力として第1のコンデンサC1の一方の端子に印加される。

【0015】

なお、クロックドライバーCDの貫通電流を低減するために、Pチャネル型MOSトランジスタM6のゲートにクロック を印加し、Nチャネル型MOSトランジスタM7のゲートにクロック を遅延したクロック'を印加するように構成してもよい。また、第2のコンデンサC2は、その一方の端子が第1及び第2のスイッチング用MOSトランジスタM1, M2の接続点に接続されている。第3のスイッチング用MOSトランジスタM3は、第2のコンデンサC2の他方の端子と接地電圧Vss(0V)の間に接続されている。

10

【0016】

また、第4のスイッチング用MOSトランジスタM4は、第1のコンデンサC1の他方の端子と第2のコンデンサC2の他方の端子の間に接続されている。第5のスイッチング用MOSトランジスタM5は、第1のコンデンサC1の他方の端子と第2のスイッチング用MOSトランジスタM2のドレインである出力端子に接続されている。そして、この回路は、第2のスイッチング用MOSトランジスタM2のドレインから出力電圧Vout(= -0.5Vdd)を得るものである。

【0017】

ここで、第3、第5のスイッチング用MOSトランジスタM3, M5は、Nチャネル型である。これは、第1のスイッチング用MOSトランジスタM1及び第2のスイッチング用MOSトランジスタM2と同様に、これらのトランジスタをオンオフさせるための電圧を同じ回路内から得るためである。即ち、第3のスイッチング用MOSトランジスタM3及び第5のスイッチング用MOSトランジスタM5をオンさせるためにはそれらのゲートに電源電圧Vddを与えればよいし、オフさせる場合にはそれらのゲートにこの回路の出力電圧Vout(= -0.5Vdd)を与えればよい。

20

【0018】

第4のスイッチング用MOSトランジスタM4については、Pチャネル型でもNチャネル型でもよいが、パターン面積を小さくするためにはNチャネル型であることが好ましい。第4のスイッチング用MOSトランジスタM4がNチャネル型である場合、これをオンさせるためには、そのゲートに電源電圧Vddを与えればよいし、オフさせる場合にはそのゲートにこの回路の出力電圧Vout(= -0.5Vdd)を与えればよい。第4のスイッチング用MOSトランジスタM4がPチャネル型である場合、これをオンさせるためには、そのゲートに接地電圧Vssもしくは、出力電圧Voutを与えればよいし、オフさせる場合にはそのゲートに電源電圧Vddを与えればよい。

30

【0019】

また、第1及び第2のコンデンサC1, C2は互いに等しい容量値を有しているものとする。また、第1, 第2, 第3, 第4, 第5のスイッチング用MOSトランジスタM1, M2, M3, M4, M5は、クロック の電圧レベルに応じて、不図示の制御回路によってゲート電圧を制御することにより、後述するようにそれらのオン(ON)、オフ(OFF)が制御されている。

40

【0020】

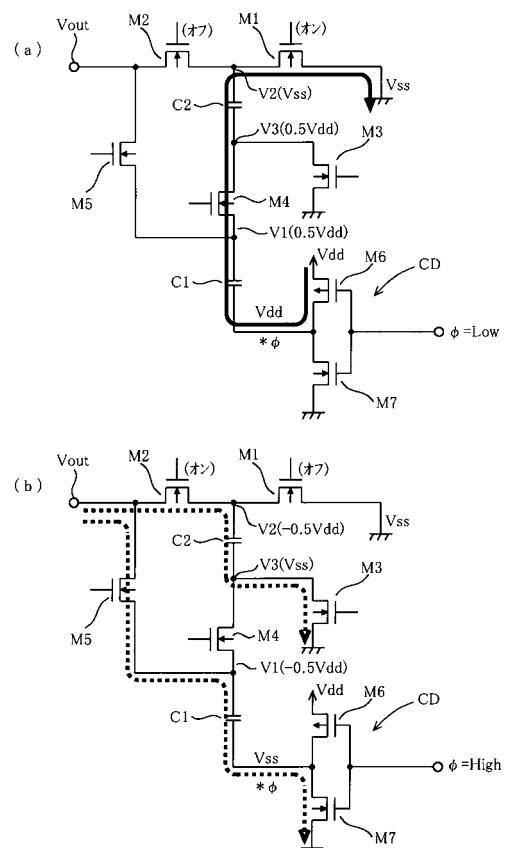

次に、この-0.5Vdd発生回路40の動作について図2(a)(b)、図3を参照しながら説明する。図3はこの-0.5Vdd発生回路40の定常状態における動作タイミング図である。

【0021】

まず、クロック がLowレベルの時のチャージポンプ回路の動作について説明する(図2(a)、図3参照)。このとき、クロックドライバーCDのPチャネル型MOSトランジスタM6はオンし、Nチャネル型MOSトランジスタM7はオフするので、反転クロック\* はHighレベル(Vddレベル)となる。また、第1, 第4のスイッチング用MOSトランジスタM1, M4をオンし、第2、第3、第5のスイッチング用MOSトランジ

50

ンジスタM2, M3, M5をオフする。

【0022】

すると、図2(a)中の太線で示すように、クロックドライバーCDのPチャネル型MOSトランジスタM6、第1のコンデンサC1、第4のスイッチング用MOSトランジスタM4、第2のコンデンサC2、第1のスイッチング用MOSトランジスタM1、接地電圧Vssを通る経路で、第1のコンデンサC1及び第2のコンデンサC2が直列接続されて充電される。

【0023】

これにより、第1のコンデンサC1の一方の端子はVddに充電され、その他方の端子の電圧V1は+0.5Vddに充電され、第2のコンデンサC2の他方の端子の電圧V1も+0.5Vddに充電される。 10

【0024】

次に、クロックがHighレベルの時の回路動作について説明する(図2(b)、図3参照)。このとき、クロックドライバーCDのNチャネル型MOSトランジスタM7がオンし、Pチャネル型MOSトランジスタM6がオフするため、反転クロック\*はLowレベルとなる。(Vssレベル)また、第1, 第4のスイッチング用MOSトランジスタM1, M4をオフし、第2, 第3, 第5のスイッチング用MOSトランジスタM2, M3, M5をオンする。

【0025】

すると、図2(b)中の太い破線で示すように、2つの経路から出力端子に-0.5Vddが供給される。1つの経路は、接地電圧Vssから、第3のスイッチング用MOSトランジスタM3、第2のコンデンサC2、第2のスイッチング用MOSトランジスタM2を通して、第2のコンデンサC2の電荷が放電され、出力端子に-0.5Vddが供給される。これは、第2のコンデンサC2の他方の電圧V3はクロックがLowレベルのときに+0.5Vddに充電されているため、第3のスイッチング用MOSトランジスタM3がオンすることにより、電圧V3が+0.5VddからVssに変化することに伴って、第2のコンデンサC2の容量結合により、第2のコンデンサC2の一方の端子の電圧V2はVss(0V)から-0.5Vddに降圧されるためである。 20

【0026】

もう1つの経路は、接地電圧Vssから、クロックドライバーCDのNチャネル型MOSトランジスタM7、第1のコンデンサC1、第5のスイッチング用MOSトランジスタM5を通して、第1のコンデンサC1の電荷が放電され、出力端子に-0.5Vddが供給される。これは、クロックがLowレベルのときに、第1のコンデンサC1の他方端子の電圧V1は+0.5Vddに充電されるが、クロックがHighレベルに変化すると、Nチャネル型MOSトランジスタM7がオンすることにより、第1のコンデンサC1の一方の端子の電圧がVddからVssに変化することに伴い、第1のコンデンサC1の容量結合により、第1のコンデンサC1の他方の端子の電圧V1は+0.5Vddから-0.5Vddに降圧されるためである。 30

【0027】

このクロックがLowレベルの時の動作と、Highレベル時の動作を交互に繰り返すことにより、出力電圧Voutとして、電源電圧Vddを-0.5倍した-0.5Vddが得られる。 40

【0028】

このように、本実施形態によれば、-0.5Vdd発生回路40を採用したので、Nチャネル型MOSトランジスタが多用される結果、従来と同等のLED25の駆動電流mnIを得るための回路のパターン面積を小さくでき、かつ効率改善をしている。

【0029】

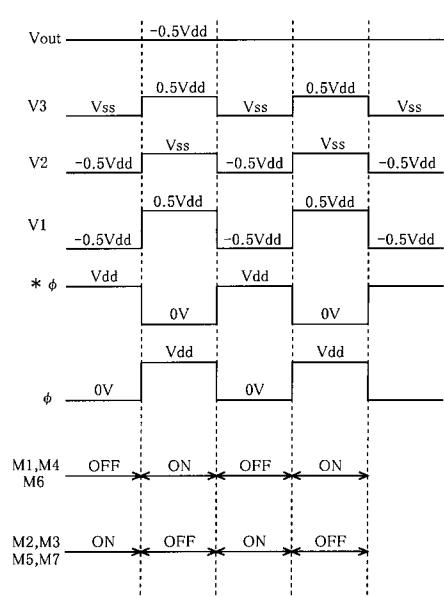

次に、本発明の効果をより明確にするために、-0.5Vdd発生回路40と1.5Vdd発生回路60との対比を行う。そのために、1.5Vdd発生回路60の具体的な構成について図4を参照して説明する。図4(a)は、クロックドライバーCDの入力クロ

ックであるクロック が H i g h レベルの場合、図 4 ( b ) はクロック が L o w レベルの場合を示している。

【 0 0 3 0 】

第 1 のスイッチング用 M O S トランジスタ M 1 1 のソースに電源電圧 V d d が印加され、この第 1 のスイッチング用 M O S トランジスタ M 1 1 のドレインは、第 2 のスイッチング用 M O S トランジスタ M 1 2 のソースに接続されている。第 1 のスイッチング用 M O S トランジスタ M 1 1 及び第 2 のスイッチング用 M O S トランジスタ M 1 2 は、電荷転送素子として機能する。

【 0 0 3 1 】

ここで、第 1 のスイッチング用 M O S トランジスタ M 1 1 及び第 1 2 のスイッチング用 M O S トランジスタ M 2 は、いずれも P チャネル型である。その理由は、第 1 のスイッチング用 M O S トランジスタ M 1 1 及び第 2 のスイッチング用 M O S トランジスタ M 1 2 をオンオフさせるための電圧を同じ回路内から得るためである。第 1 のスイッチング用 M O S トランジスタ M 1 1 及び第 2 のスイッチング用 M O S トランジスタ M 1 2 をオンさせるためにはそれらのゲートに接地電圧 V s s を与えればよいし、オフさせる場合にはそれらのゲートにこの回路の出力電圧 V o u t ( = 1 . 5 V d d ) を与えればよい。

【 0 0 3 2 】

また、第 1 のコンデンサ C 1 の一方の端子には、クロックドライバー C D の出力が接続されている。クロックドライバー C D は、電源電圧 V d d と接地電圧 V s s の間に、P チャネル型 M O S トランジスタ M 1 6 、N チャネル型 M O S トランジスタ M 1 7 を直列に接続して C M O S インバータとして構成される。そして、クロックドライバー C D にはクロック が印加され、このクロック はクロックドライバー C D によって反転される。その反転クロック\* が、クロックドライバー C D の出力として第 1 のコンデンサ C 1 の一方の端子に印加される。

【 0 0 3 3 】

また、第 2 のコンデンサ C 2 は、その一方の端子が第 1 及び第 2 のスイッチング用 M O S トランジスタ M 1 1 , M 1 2 の接続点に接続されている。第 3 のスイッチング用 M O S トランジスタ M 1 3 は、第 2 のコンデンサ C 2 の他方の端子と電源電圧 V d d の間に接続されている。

【 0 0 3 4 】

また、第 4 のスイッチング用 M O S トランジスタ M 1 4 は、第 1 のコンデンサ C 1 の他方の端子と第 2 のコンデンサ C 2 の他方の端子の間に接続されている。第 5 のスイッチング用 M O S トランジスタ M 1 5 は、第 1 のコンデンサ C 1 の他方の端子と第 2 のスイッチング用 M O S トランジスタ M 1 2 のドレインである出力端子に接続されている。そして、この回路は、第 2 のスイッチング用 M O S トランジスタ M 1 2 のドレインから出力電圧 V o u t ( = 1 . 5 V d d ) を得るものである。

【 0 0 3 5 】

ここで、第 3 及び第 5 のスイッチング用 M O S トランジスタ M 1 3 , M 1 5 は P チャネル型、第 4 のスイッチング用 M O S トランジスタ M 1 4 は N チャネル型である。第 3 及び第 5 のスイッチング用 M O S トランジスタ M 1 3 , M 1 5 を P チャネル型とした理由は、前述と同様に、第 3 のスイッチング用 M O S トランジスタ M 1 3 及び第 5 のスイッチング用 M O S トランジスタ M 1 5 をオンオフさせるための電圧を同じ回路内から得るためにある。

【 0 0 3 6 】

また、第 1 及び第 2 のコンデンサ C 1 , C 2 は互いに等しい容量値を有しているものとする。また、第 1 , 第 2 , 第 3 , 第 4 , 第 5 のスイッチング用 M O S トランジスタ M 1 1 , M 1 2 , M 1 3 , M 1 4 , M 1 5 は、クロック の電圧レベルに応じて、不図示の制御回路によってゲート電圧を制御することにより、後述するようにそれらのオン ( O N ) 、オフ ( O F F ) が制御されている。

【 0 0 3 7 】

10

20

30

40

50

次に、この回路の動作について図4(a)(b)、図5を参照しながら説明する。図5はこのチャージポンプ回路の定常状態における動作タイミング図である。

【0038】

まず、クロックがHighレベルの時のチャージポンプ回路の動作について説明する(図4(a)、図5参照)。このとき、クロックドライバーCDのNチャネル型MOSトランジスタM17はオンし、反転クロック\*はLowレベル(0V)となる。また、第1、第4のスイッチング用MOSトランジスタM11、M14をオンし、第2、第3、第5のスイッチング用MOSトランジスタM12、M13、M15をオフする。すると、図4(a)中の太い破線で示すように、電源電圧Vddから、第1のスイッチング用MOSトランジスタM11、第2のコンデンサC2、第4のスイッチング用MOSトランジスタM14、第1のコンデンサC1、クロックドライバーCDのNチャネル型MOSトランジスタM17を通る経路で、第1のコンデンサC1及び第2のコンデンサC2が直列接続されて充電される。これにより、第2のコンデンサC2の一方の端子の電圧V2はVddに充電され、その他方の端子の電圧V3は0.5Vddに充電され、第1のコンデンサC1の他方の端子の電圧V1も0.5Vddに充電される。10

【0039】

次に、クロックがLowレベルの時のチャージポンプ回路の動作について説明する(図4(b)、図5参照)。このとき、クロックドライバーCDのPチャネル型MOSトランジスタM7はオンし、反転クロック\*はHighレベルとなる。また、第1、第4のスイッチング用MOSトランジスタM11、M14をオフし、第2、第3、第5のスイッチング用MOSトランジスタM12、M13、M15をオンする。20

【0040】

すると、図4(b)中の太い線で示すように、2つの経路から出力端子に1.5Vddが供給される。1つの経路は、電源電圧Vddから、第3のスイッチング用MOSトランジスタM13、第2のコンデンサC2、第2のスイッチング用MOSトランジスタM12を通して、第2のコンデンサC2の電荷が放電され、出力端子に1.5Vddが供給される。これは、第2のコンデンサC2の他方の電圧V12はクロックがHighレベルのときに0.5Vddに充電されているため、第3のスイッチング用MOSトランジスタM13がオンすることにより、電圧V12が0.5VddからVddに変化することに伴って、第2のコンデンサC2の容量結合により、第2のコンデンサの一方の端子の電圧V11はVddから1.5Vddに昇圧されるためである。30

【0041】

もう1つの経路は、電源電圧Vddから、クロックドライバーCDのPチャネル型MOSトランジスタM16、第1のコンデンサC1、第5のスイッチング用MOSトランジスタM15を通して、第1のコンデンサC1の電荷が放電され、出力端子に1.5Vddが供給される。

【0042】

これは、クロックがHighレベルのときに、第1のコンデンサC1の他方端子の電圧V13は0.5Vddに充電されるが、クロックがLowレベルに変化すると、Pチャネル型MOSトランジスタM16がオンすることにより、第1のコンデンサC1の一方の端子の電圧が0VからVddに変化することに伴い、第1のコンデンサC1の容量結合により、第1のコンデンサC1の他方の端子の電圧V13は0.5Vddから1.5Vddに昇圧されるためである。40

【0043】

このクロックがLowレベルの時の動作と、Highレベル時の動作を交互に繰り返すことにより、出力電圧Voutとして、電源電圧Vddを1.5倍した1.5Vddが得られる。

【0044】

上述のように、-0.5Vdd発生回路40においては、第1、第2、第3、及び第5のスイッチング用MOSトランジスタM1、M2、M3、M5がNチャネル型であること

10

20

30

40

50

が必要であり、1.5Vdd発生回路60では、第1、第2、第3及び第5のスイッチング用MOSトランジスタM11,M12,M13,M15がPチャネル型であることが必要であることが明らかとなった。そこで、-0.5Vdd発生回路40における第4のスイッチング用MOSトランジスタM4をPチャネル型、1.5Vdd発生回路60における第4のスイッチング用MOSトランジスタM14をNチャネル型、クロックドライバーCDはPチャネル型、Nチャネル型1個ずつから構成されるとして、2つの回路で使用されるトランジスタの種類の数を計算すると、表1のように、1.5Vdd発生回路60では、Pチャネル型が5個、Nチャネル型2個となり、-0.5Vdd発生回路40では逆に、Nチャネル型が5個、Pチャネル型2個となり、Nチャネル型が多用されている。そこで、Pチャネル型とNチャネル型のパターン面積比を3:1とすると、1.5Vdd発生回路60と-0.5Vdd発生回路40との面積比(ただし、トランジスタ部分のみ)は、17:11となる。即ち、-0.5Vdd発生回路40は1.5Vdd発生回路60に比して35%程度小さなパターン面積で形成できる。その分、駆動回路全体の面積も小さくできる。10

#### 【0045】

また、MOSトランジスタのゲート容量等の寄生容量を小さくできるため、駆動回路の消費電流が低減され、その効率改善を実現できる。

#### 【0046】

なお、本発明は白色LEDに限らず、赤色LED、緑色LED、青色LED、アノードとカソードを有する他の発光素子の駆動回路にも広く適用できるものである。また、本実施形態では-0.5Vddという負電圧を発生し、電源電圧Vddとの間で1.5Vddの電位差を得ているが、負電圧の大きさは-0.5Vddに限らず、-0.4Vddあるいは-0.6Vddでもよいし、他の値であってもよい。20

#### 【0047】

#### 【表1】

パターン面積の比較

| トランジスタ  | 1.5Vdd昇圧 | -0.5Vdd昇圧 |

|---------|----------|-----------|

| Pチャネル   | 5        | 2         |

| Nチャネル   | 2        | 5         |

| パターン面積比 | 17       | 11        |

#### 【図面の簡単な説明】

#### 【0048】

【図1】本発明の実施形態に係る駆動回路の回路図である。

【図2】本発明の実施形態に係る駆動回路の-0.5Vdd発生回路の回路図である。

【図3】-0.5Vdd発生回路の動作タイミング図である。

【図4】1.5Vdd発生回路の回路図である。

【図5】1.5Vdd発生回路の動作タイミング図である。

【図6】従来例に係る駆動回路の回路図である。

#### 【符号の説明】

#### 【0049】

- M1 第1のスイッチング用MOSトランジスタ

- M2 第2のスイッチング用MOSトランジスタ

- M3 第3のスイッチング用MOSトランジスタ

- M4 第4のスイッチング用MOSトランジスタ

10

20

30

40

50

|     |                           |

|-----|---------------------------|

| M 5 | 第 5 のスイッチング用 M O S トランジスタ |

| M 6 | P チャネル型 M O S トランジスタ      |

| M 7 | N チャネル型 M O S トランジスタ      |

| C D | クロックドライバー                 |

| C 2 | 第 2 のコンデンサ                |

| 2 1 | 端子                        |

| 3 0 | クロック発生回路                  |

| C 1 | 第 1 のコンデンサ                |

| 2 0 | 端子                        |

| 2 5 | 白色 L E D                  |

| 4 0 | - 0 . 5 V d d 発生回路        |

【図 1】

【図 2】

【図3】

【図4】

【図5】

【図6】

---

フロントページの続き

F ターム(参考) 5F041 AA21 AA24 BB03 BB13 BB24 BB26 BB33 FF16

5H420 NA31 NB02 NB36

5J055 AX05 AX14 AX27 BX16 BX17 CX29 DX22 DX56 DX72 DX73

DX83 EX02 EY10 EY21 EZ04 EZ06 EZ09 EZ12 EZ20 EZ28

EZ53 FX05 FX18 FX19 FX37 GX01 GX04