(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-336010

(P2004-336010A)

(43) 公開日 平成16年11月25日(2004.11.25)

| (51) Int.Cl. <sup>7</sup> |                              | F 1                            | テーマコード (参考)                                                |         |

|---------------------------|------------------------------|--------------------------------|------------------------------------------------------------|---------|

| H 01 L                    | 21/822                       | H 01 L 27/04                   | F                                                          | 5 F 038 |

| H 01 L                    | 21/336                       | H 01 L 27/08                   | 3 3 1 E                                                    | 5 F 048 |

| H 01 L                    | 21/8238                      | H 03 K 19/00                   | A                                                          | 5 F 110 |

| H 01 L                    | 27/04                        | H 01 L 27/04                   | G                                                          | 5 J 056 |

| H 01 L                    | 27/08                        | H 01 L 27/04                   | M                                                          |         |

|                           |                              | 審査請求 未請求 請求項の数 19 O L (全 17 頁) | 最終頁に続く                                                     |         |

| (21) 出願番号                 | 特願2004-44584 (P2004-44584)   | (71) 出願人                       | 000002369<br>セイコーエプソン株式会社<br>東京都新宿区西新宿2丁目4番1号              |         |

| (22) 出願日                  | 平成16年2月20日 (2004. 2. 20)     | (74) 代理人                       | 100079108<br>弁理士 稲葉 良幸                                     |         |

| (31) 優先権主張番号              | 特願2003-112088 (P2003-112088) | (74) 代理人                       | 100080953<br>弁理士 田中 克郎                                     |         |

| (32) 優先日                  | 平成15年4月16日 (2003. 4. 16)     | (74) 代理人                       | 100093861<br>弁理士 大賀 真司                                     |         |

| (33) 優先権主張国               | 日本国 (JP)                     | (72) 発明者                       | 唐木 信雄<br>長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内                     |         |

|                           |                              | F ターム (参考)                     | 5F038 BG06 BG09 DF01 DF03 DF04<br>DF05 DF08 DF17 EZ06 EZ20 |         |

|                           |                              |                                |                                                            | 最終頁に続く  |

(54) 【発明の名称】半導体集積回路、電子機器、及びトランジスタのバックゲート電位制御方法

## (57) 【要約】

【課題】 半導体集積回路の一層の低消費電力化を実現するとともに、回路の待機状態から作動状態への移行を速める。

【解決手段】 本発明の半導体集積回路は、作動状態から待機状態へ又は待機状態から作動状態への状態遷移を有する複数の回路ブロック (20-1, 20-2, ..., 20-M) と、複数の回路ブロック (20-1, 20-2, ..., 20-M) の各々の状態遷移を予め規定する有限ステートマシンに基づいて回路ブロック (20-1, 20-2, ..., 20-M) の論理素子を形成するトランジスタのバックゲート電位をイベントドリブン式に制御するマスタユニット (10) を備える。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

作動状態から待機状態へ又は待機状態から作動状態への状態遷移を有する複数の回路ブロックと、

前記複数の回路ブロックの各々の状態遷移を予め規定する有限ステートマシンに基づいて前記回路ブロックの論理素子を形成するトランジスタのバックゲート電位をイベントドリブン式に制御する制御回路と、

を備える、半導体集積回路。

**【請求項 2】**

請求項 1 に記載の半導体集積回路であって、

前記制御回路は前記回路ブロックが待機状態のときには前記トランジスタの閾値電圧が増加するように前記バックゲート電位を制御する、半導体集積回路。

**【請求項 3】**

請求項 1 又は請求項 2 に記載の半導体集積回路であって、

前記制御回路は前記回路ブロックが作動状態のときには前記トランジスタの閾値電圧が減少するように前記バックゲート電位を制御する、半導体集積回路。

**【請求項 4】**

請求項 1 乃至請求項 3 のうち何れか 1 項に記載の半導体集積回路であって、

前記複数の回路ブロックの各々に電源供給を行うための共通電源線と、

前記複数の回路ブロックの各々を接地するための共通接地線と、

前記共通電源線又は前記共通接地線のうち少なくとも一方と前記回路ブロックとの間の電気的な通電 / 遮電を行うスイッチング素子と、を更に備え、

前記制御回路は前記有限ステートマシンに基づいてイベントドリブン式に前記スイッチング素子の通電 / 遮電を制御する、半導体集積回路。

**【請求項 5】**

作動状態から待機状態へ又は待機状態から作動状態への状態遷移を有する複数の回路ブロックと、

C S P 方式による前記回路ブロック相互間の通信を通じて自律的に動作要求を行い、又は他律的に動作要求を受け入れるためのチャネルと、

前記チャネルを通じて回路ブロック相互間を接続するポートと、を備え、

前記チャネル及びポートは前記回路ブロックの動作状態に応じて前記回路ブロックの論理素子を構成するトランジスタのバックゲート電位を制御する、半導体集積回路。

**【請求項 6】**

請求項 5 に記載の半導体集積回路であって、

前記チャネル及びポートは前記回路ブロックが待機状態のときには前記トランジスタの閾値電圧が増加するように前記バックゲート電位を制御する、半導体集積回路。

**【請求項 7】**

請求項 5 又は請求項 6 に記載の半導体集積回路であって、

前記チャネル及びポートは前記回路ブロックが作動状態のときには前記トランジスタの閾値電圧が減少するように前記バックゲート電位を制御する、半導体集積回路。

**【請求項 8】**

請求項 5 乃至請求項 7 のうち何れか 1 項に記載の半導体集積回路であって、

前記複数の回路ブロックの各々に電源供給を行うための共通電源線と、

前記複数の回路ブロックの各々を接地するための共通接地線と、

前記共通電源線又は前記共通接地線のうち少なくとも一方と前記回路ブロックとの間の電気的な通電 / 遮電を行うスイッチング素子と、を更に備え、

前記チャネル及びポートは前記回路ブロックの状態遷移に応じて前記スイッチング素子の通電 / 遮電を制御する、半導体集積回路。

**【請求項 9】**

請求項 1 乃至請求項 8 のうち何れか 1 項に記載の半導体集積回路であって、

10

20

30

40

50

前記トランジスタはダブルゲートTFTである、半導体集積回路。

**【請求項 10】**

請求項9に記載の半導体集積回路であって、

前記ダブルゲートTFTはチャネル端部とドレイン領域又はソース領域との接面にLD領域を備える、半導体集積回路。

**【請求項 11】**

請求項9又は請求項10に記載の半導体集積回路であって、

前記ダブルゲートTFTのゲート電極とバックゲート電極はチャネル領域を間に挟んで対向配置されており、且つ両者の前記チャネル領域への投影形状が重なるように略同形に形成されている、半導体集積回路。

10

**【請求項 12】**

請求項10に記載の半導体集積回路であって、

前記バックゲート電極はチャネル領域への投影形状が前記LDD領域の全部又は一部と重なるように形成されている、半導体集積回路。

**【請求項 13】**

請求項1乃至請求項12のうち何れか1項に記載の半導体集積回路を備えた電子機器。

**【請求項 14】**

作動状態から待機状態へ又は待機状態から作動状態への状態遷移を有する複数の回路ブロックの各々の状態遷移を予め規定する有限ステートマシンに基づいて、前記回路ブロックの論理素子を形成するトランジスタのバックゲート電位をイベントドリブン式に制御する、バックゲート電位制御方法。

20

**【請求項 15】**

請求項14に記載のバックゲート電位制御方法であって、

前記回路ブロックが待機状態のときには前記トランジスタの閾値電圧が増加するように前記バックゲート電位を制御する、バックゲート電位制御方法。

**【請求項 16】**

請求項14又は請求項15に記載のバックゲート電位制御方法であって、

前記回路ブロックが作動状態のときには前記トランジスタの閾値電圧が減少するように前記バックゲート電位を制御する、バックゲート電位制御方法。

30

**【請求項 17】**

作動状態から待機状態へ又は待機状態から作動状態への状態遷移を有する複数の回路ブロックと、CSP方式による前記回路ブロック相互間の通信を通じて自律的に動作要求を行い、又は他律的に動作要求を受け入れるためのチャネルと、前記チャネルを通じて回路ブロック相互間を接続するポートと、を備える半導体集積回路のバックゲート電位制御方法であって、

前記チャネル及びポートは前記回路ブロックの動作状態に基づいて前記回路ブロックの論理素子を構成するトランジスタのバックゲート電位を制御する、バックゲート電位制御方法。

**【請求項 18】**

請求項17に記載のバックゲート電位制御方法であって、

前記回路ブロックが待機状態のときには前記トランジスタの閾値電圧が増加するように前記バックゲート電位を制御する、バックゲート電位制御方法。

40

**【請求項 19】**

請求項17又は請求項18に記載のバックゲート電位制御方法であって、

前記回路ブロックが作動状態のときには前記トランジスタの閾値電圧が減少するように前記バックゲート電位を制御する、バックゲート電位制御方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

50

本発明は半導体集積回路の低消費電力化を実現するためのトランジスタのバックゲート電位制御技術に関する。

【背景技術】

【0002】

特開平9-83335号公報にはVLSI (Very Large Scale Integration)回路を複数の回路ブロックに分割して構成し、共通電源供給線又は共通接地電源線のうち少なくとも一方と回路ブロックとの間にスイッチングトランジスタを配置し、回路ブロックが待機状態 (standby state) のときにスイッチングトランジスタの閾値電圧が上昇するようにバックゲート電位を制御した上でスイッチングトランジスタをカットオフさせる技術が開示されている。この技術を用いることにより、待機状態におけるリーク電流（オフ電流）を減少させて消費電力を低減することができる。10

【特許文献1】特開平9-83335号公報

【発明の開示】

【発明が解決しようとする課題】

【0003】

しかし、上述の従来技術ではチップ上の回路全体、或いはCPUコアやコ・プロセッサなどの比較的大きな回路ブロック毎にスイッチングトランジスタのバックゲート電位の制御をしていたため、リーク電流を減少させるためのきめ細かい制御ができず、回路全体でみると待機中のリーク電流が増大して消費電力が増加する問題があった。また、制御対象となる回路規模が大きくなる程、バックゲート電位切り換え時の電位安定に時間を要し、待機状態から作動状態への移行に遅れが生じるという問題があった。さらに、上述の従来技術では、回路ブロックの電源を遮断し、その時のリーク電流を減少させるための制御を行っているが、回路ブロックの電源を遮断すると、回路ブロックはその内部状態を保持する事が出来ない。従って、例えば、回路ブロックを順序回路で構成する場合、待機状態から作動状態へ移行させる際に、順序回路の初期設定又は復帰設定を行う必要があり、回路規模の増大や待機状態から作動状態への移行が遅くなるといった不都合を生じてしまう。20

【0004】

そこで、本発明は半導体集積回路の一層の低消費電力化を実現するとともに、回路の待機状態から作動状態への移行を速める改良技術を提案することを課題とする。

【課題を解決するための手段】

【0005】

上記の課題を解決するため、本発明の半導体集積回路は、作動状態から待機状態へ又は待機状態から作動状態への状態遷移を有する複数の回路ブロックと、複数の回路ブロックの各々の状態遷移を予め規定する有限ステートマシンに基づいて回路ブロックの論理素子を形成するトランジスタのバックゲート電位をイベントドリブン式に制御する制御回路を備える。かかる構成により、回路ブロックの動作状態に基づいてトランジスタのバックゲート電位を制御できるため、半導体集積回路全体のリーク電流を効率よく減少させることができる。

【0006】

本発明の好適な形態においては、制御回路は回路ブロックが待機状態のときにはトランジスタの閾値電圧が増加するようにバックゲート電位を制御する。回路ブロックが待機状態のときにトランジスタの閾値電圧が増加するようにバックゲート電位を制御することで、待機状態のときのリーク電流を減少させることができる。特に、回路ブロックを多数に細分割することで、個々の回路ブロックのリーク電流をきめ細かく制御できるため、半導体集積回路全体のリーク電流を大幅に低減することができる。40

【0007】

本発明の好適な形態においては、制御回路は回路ブロックが作動状態のときにはトランジスタの閾値電圧が減少するようにバックゲート電位を制御する。回路ブロックが作動状態のときにトランジスタの閾値電圧が減少するようにバックゲート電位を制御することで、回路の低電圧動作を可能にすることができます。50

**【 0 0 0 8 】**

本発明の好適な形態において、半導体集積回路は複数の回路ブロックの各々に電源供給を行うための共通電源線と、複数の回路ブロックの各々を接地するための共通接地線と、共通電源線又は共通接地線のうち少なくとも一方と回路ブロックとの間の電気的な通電／遮電を行うスイッチング素子をさらに備え、制御回路は有限ステートマシンに基づいてイベントドリブン式にスイッチング素子の通電／遮電を制御する。個々の回路ブロックへの電力供給をオン／オフ制御するスイッチング素子を設けることで、待機時における回路ブロックからのリーク電流を低減できる。

**【 0 0 0 9 】**

本発明の半導体集積回路は、作動状態から待機状態へ又は待機状態から作動状態への状態遷移を有する複数の回路ブロックと、C S P方式による回路ブロック相互間の通信を通じて自律的に動作要求を行い、又は他律的に動作要求を受け入れるためのチャネルと、チャネルを通じて回路ブロック相互間を接続するポートを備え、ポートは回路ブロックの動作状態に応じて、回路ブロックの論理素子を構成するトランジスタのバックゲート電位を制御する。かかる構成により、個々の回路ブロックはC S P方式により他の回路ブロックと通信を行い、自律的に又は他律的に動作する必要があるときにポートを通じてバックゲート電位が制御されるため、半導体集積回路全体のリーク電流を効率よく低減できる。10

**【 0 0 1 0 】**

本発明の好適な形態において、チャネル及びポートは回路ブロックが待機状態のときはトランジスタの閾値電圧が増加するようにバックゲート電位を制御する。かかる構成により、待機状態における個々の回路ブロックからのリーク電流を低減できる。20

**【 0 0 1 1 】**

本発明の好適な形態において、チャネル及びポートは回路ブロックが作動状態のときはトランジスタの閾値電圧が減少するようにバックゲート電位を制御する。かかる構成により、トランジスタの低電圧駆動を可能とし、半導体集積回路の低消費電力化を図ることができる。

**【 0 0 1 2 】**

本発明の好適な形態において、複数の回路ブロックの各々に電源供給を行うための共通電源線と、複数の回路ブロックの各々を接地するための共通接地線と、共通電源線又は共通接地線のうち少なくとも一方と回路ブロックとの間の電気的な通電／遮電を行うスイッチング素子をさらに備え、ポートは回路ブロックの状態遷移に応じてスイッチング素子の通電／遮電を制御する。個々の回路ブロックへの電力供給をオン／オフ制御するスイッチング素子を設けることで、待機時における回路ブロックからのリーク電流を低減できる。30

**【 0 0 1 3 】**

本発明の好適な形態において、回路ブロックの論理素子を形成するトランジスタ、又は回路ブロックへの電源供給をスイッチング制御するスイッチング素子は、M O Sトランジスタとしてもよい。M O Sトランジスタによれば、バックゲート電位を制御することで、リーク電流を抑えることができる。

**【 0 0 1 4 】**

本発明の好適な形態において、制御回路はM O Sトランジスタが通電状態のときの閾値電圧よりも遮電状態のときの閾値電圧が増加するようにM O Sトランジスタのバックゲート電位を制御する。これにより、回路ブロックからのリーク電流を効率よく抑えることができる。40

**【 0 0 1 5 】**

回路ブロックを構成する論理素子が形成されているウェルと、回路ブロックへの電源供給をスイッチング制御するM O Sトランジスタが形成されているウェルとは分離されているのが好適である。かかる構成により、スイッチング素子としてのM O Sトランジスタのバックゲート電位と論理素子を形成するトランジスタのバックゲート電位を互いに影響を及ぼすことなく電位制御できる。

**【 0 0 1 6 】**

50

本発明の好適な形態において、回路ブロックの論理素子を形成するトランジスタ、又は回路ブロックへの電源供給をスイッチング制御するスイッチング素子は、ダブルゲート構造を備えたTFT（ダブルゲートTFT）としてもよい。ダブルゲートTFTによればバルク構造のMOSトランジスタと比べて高速化、低消費電力化を実現できる。

#### 【0017】

このようなダブルゲートTFTとして、チャネル端部とドレイン領域又はソース領域との接面上LD領域を備えたものが好適である。LD領域を形成することによって、ドレイン端空乏領域の電界は弱くなり、リーク電流を低減できる。

#### 【0018】

また、ダブルゲートTFTのゲート電極とバックゲート電極はチャネル領域を間に挟んで対向配置されており、且つ両者の前記チャネル領域への投影形状が重なるように略同形に形成されているのが好適である。チャネル領域の表裏をゲート電極とバックゲート電極によって挟み込むことにより、サブスレッシュルド係数を小さくし、電界移動度を向上できる。

#### 【0019】

また、バックゲート電極はチャネル領域への投影形状がLD領域の全部又は一部と重なるように形成されているのが好適である。これにより、トランジスタ待機時のリーク電流の低減と、トランジスタ作動時の電界移動度の向上を両立できる。

#### 【0020】

本発明の電子機器は本発明の半導体集積回路を備える。本発明の半導体集積回路を実装することにより、消費電力を低減できるため、主として、バッテリ駆動される携帯機器等に好適である。

#### 【0021】

本発明のバックゲート電位制御方法は、作動状態から待機状態へ又は待機状態から作動状態への状態遷移を有する複数の回路ブロックの各々の状態遷移を予め規定する有限ステートマシンに基づいて、回路ブロックの論理素子を形成するトランジスタのバックゲート電位をイベントドリブン式に制御する。かかる構成により、回路ブロックの動作状態に基づいてトランジスタのバックゲート電位を制御できるため、半導体集積回路全体のリーク電流を効率よく減少させることができる。

#### 【0022】

本発明の半導体集積回路は、作動状態から待機状態へ又は待機状態から作動状態への状態遷移を有する複数の回路ブロックと、CSP方式による回路ブロック相互間の通信を通じて自律的に動作要求を行い、又は他律的に動作要求を受け入れるためのチャネルと、チャネルを通じて回路ブロック相互間を接続するポートを備える半導体集積回路のバックゲート電位制御方法であって、チャネル及びポートは回路ブロックの動作状態に基づいて、回路ブロックの論理素子を構成するトランジスタのバックゲート電位を制御する。かかる構成により、個々の回路ブロックはCSP方式により他の回路ブロックと通信を行い、自律的に又は他律的に動作する必要があるときにポートを通じてバックゲート電位が制御されるため、半導体集積回路全体のリーク電流を効率よく低減できる。

#### 【発明を実施するための最良の形態】

#### 【0023】

#### [発明の実施形態1]

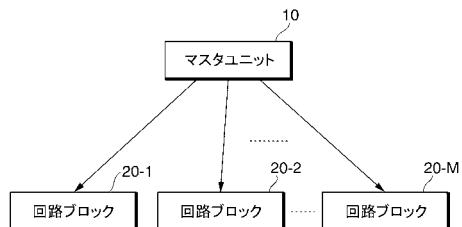

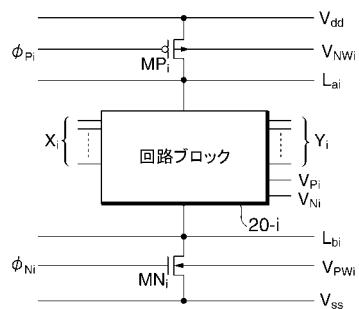

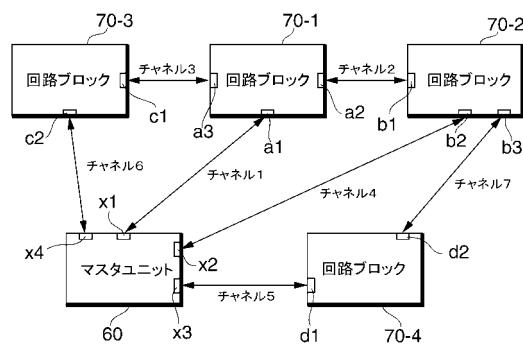

図1はマスタユニットが集中制御的に複数の回路ブロックのバックゲート電位を制御するシステムのブロック図である。VLSIチップ内の半導体集積回路は、待機状態から作動状態へ、又は作動状態から待機状態への状態遷移を有するM個の回路ブロック（論理ブロック）20-1, 20-2, …, 20-Mに分割されている。VLSIチップ全体の消費電力を低減するには、機能別に分類される多数の回路ブロックに分割することが望ましい。マスタユニット（制御回路）10はこれら回路ブロック20-1, 20-2, …, 20-Mのバックゲート電位を一元的に集中制御するためのデータフローと制御ロジックをVLSIの論理設計レベルで構築したイベントドリブンシステムである。

10

20

30

40

50

## 【0024】

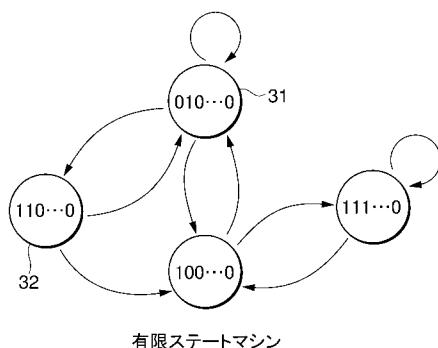

図2はマスタユニット10のバックゲート電位制御ロジックを実現する有限ステートマシン(Finite State Machine)の状態遷移図である。M個の回路ブロック20-1, 20-2, …, 20-Mの待機状態を「0」、作動状態を「1」に対応させ、有限ステートマシンをMビットの2進数で表記すると、全ての回路ブロック20-1, 20-2, …, 20-Mのバックゲート電位制御を行うには最大で $2^M$ 個の状態数が必要となる。有限ステートマシンを構成する個々の状態は回路ブロック20-1, 20-2, …, 20-Mの待機状態「0」と作動状態「1」の全ての組み合わせを規定している。有限ステータムの状態を標記する2進数の上位k(1 ≤ k ≤ M)桁目の「0」、「1」を回路ブロック20-kの「待機状態」、「作動状態」を示すものとすると、図中の符号31が示す状態は2進数の上位2桁目が「1」であるから、回路ブロック20-2の作動状態となることを示している。同様にして、符号32が示す状態は2進数の上位1桁目と2桁目が「1」であるから、回路ブロック20-1と20-2が「作動状態」となることを示している。有限ステートマシンの状態遷移はイベントドリブン式に行われ、マスタユニット10は各々の回路ブロック20-1, 20-2, …, 20-Mの動作状態を有限ステートマシンの状態に対応させることで、VLSIチップ内全回路ブロックのバックゲート電位制御を行う。

## 【0025】

尚、ここでは説明の便宜上、有限ステートマシンの各々の状態における「入力」と「出力」との関係は省略している。また、回路ブロック20-1, 20-2, …, 20-Mへの電源供給を後述するスイッチング素子を介して行うには、マスタユニット10は論理素子を構成するトランジスタのバックゲート電位制御に加えて、当該スイッチング素子のゲート電位とバックゲート電位の制御をも併せて行う。以下の説明においては、スイッチング素子を介してこれらの回路ブロック20-1, 20-2, …, 20-Mに電源供給をオン/オフ制御する構成を第1の構成例とし、回路ブロック20-1, 20-2, …, 20-Mを電源供給線に常時接続して電源供給を行う構成を第2の構成例とする。

## 【0026】

## (第1の構成例)

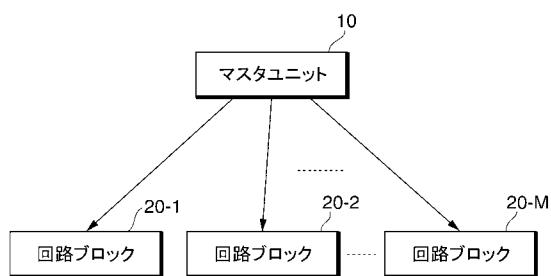

図3は第1の構成例における回路ブロックへの電源供給系統を示す回路図である。ここでは、i番目の回路ブロック20-iの電源供給系統を図示するが、他の回路ブロックについても同様の回路構成を具備している。同図において、共通電源線V<sub>dd</sub>は全ての回路ブロック20-1, 20-2, …, 20-Mに電源供給を行うための電源線であり、共通接地線V<sub>ss</sub>は全ての回路ブロック20-1, 20-2, …, 20-Mを接地するための接地線である。回路ブロック20-iには局的に電源供給を行うための部分電源供給線L<sub>a</sub><sub>i</sub>と、局的に接地するための部分接地線L<sub>b</sub><sub>i</sub>とがそれぞれスイッチング素子としてのPMOSトランジスタM<sub>P</sub><sub>i</sub>とNMOSトランジスタM<sub>N</sub><sub>i</sub>を介して共通電源線V<sub>dd</sub>と共通接地線V<sub>ss</sub>とに接続している。

## 【0027】

尚、同図において、V<sub>p</sub><sub>i</sub>はPMOSトランジスタM<sub>P</sub><sub>i</sub>のゲート電位、V<sub>n</sub><sub>w</sub><sub>i</sub>は同トランジスタM<sub>P</sub><sub>i</sub>のバックゲート電位、V<sub>n</sub><sub>i</sub>はNMOSトランジスタM<sub>N</sub><sub>i</sub>のゲート電位、V<sub>p</sub><sub>w</sub><sub>i</sub>は同トランジスタM<sub>N</sub><sub>i</sub>のバックゲート電位、X<sub>i</sub>は回路ブロック20-iへの入力信号、Y<sub>i</sub>は同回路ブロック20-iからの出力信号、V<sub>n</sub><sub>i</sub>は回路ブロック20-iの論理素子を構成するPMOSトランジスタのバックゲート電位、V<sub>p</sub><sub>i</sub>は回路ブロック20-iの論理素子を構成するNMOSトランジスタのバックゲート電位を示している。

## 【0028】

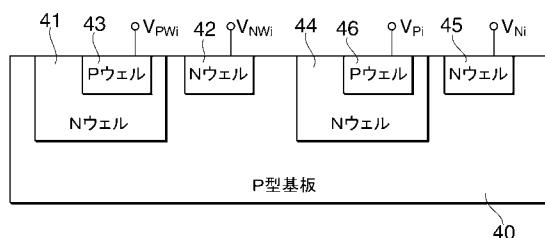

図5はVLSIチップのウェル構造を示している。P型基板40にはそれぞれ独立したNウェル41、42、44、45が各々形成され、さらに、Nウェル41内にはPウェル43が形成され、Nウェル44内にはPウェル46が形成されたトリプルウェル構造となっている。Pウェル43は上述のNMOSトランジスタM<sub>N</sub><sub>i</sub>を形成するためのウェルであり、そのウェル電位V<sub>p</sub><sub>w</sub><sub>i</sub>は同トランジスタM<sub>N</sub><sub>i</sub>のバックゲート電位を示している。また、Nウェル42は上述のPMOSトランジスタM<sub>P</sub><sub>i</sub>を形成するためのウェルであり

10

20

30

40

50

、そのウェル電位 $V_{NW_i}$ は同トランジスタM P iのバックゲート電位を示している。また、Nウェル45、Pウェル46は回路ブロック20-i内の論理素子を構成するPMOSトランジスタ、NMOSトランジスタを形成するためのウェルである。ウェル電位 $V_{P_i}$ はNMOSトランジスタのバックゲート電位を示しており、ウェル電位 $V_{N_i}$ はPMOSトランジスタのバックゲート電位を示している。

#### 【0029】

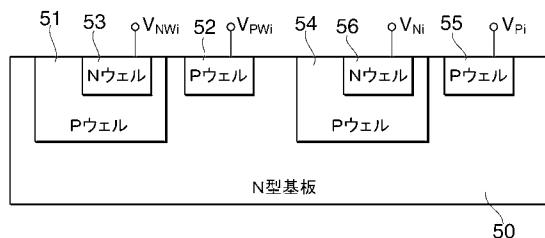

VLSIチップのウェル構造は上述の構成に限らず、例えば、図6に示すウェル構造としてもよい。同図に示すウェル構造は、上述のP型基板40に替えてN型基板50をベースとしている。P型基板50にはそれぞれ独立したPウェル51、52、54、55が各々形成され、さらに、Pウェル51内にはNウェル53が形成され、Pウェル54内にはNウェル56が形成されたトリプルウェル構造となっている。Nウェル53は上述のPMOSトランジスタM P iを形成するためのウェルであり、そのウェル電位 $V_{NW_i}$ はトランジスタM P iのバックゲート電位を示している。また、Pウェル52は上述のNMOSトランジスタM N iを形成するためのウェルであり、そのウェル電位 $V_{PW_i}$ は同トランジスタM N iのバックゲート電位を示している。また、Pウェル55、Nウェル56は回路ブロック20-i内の論理素子を構成するNMOSトランジスタ、PMOSトランジスタを形成するためのウェルである。ウェル電位 $V_{P_i}$ はNMOSトランジスタのバックゲート電位を示しており、ウェル電位 $V_{N_i}$ はPMOSトランジスタのバックゲート電位を示している。

#### 【0030】

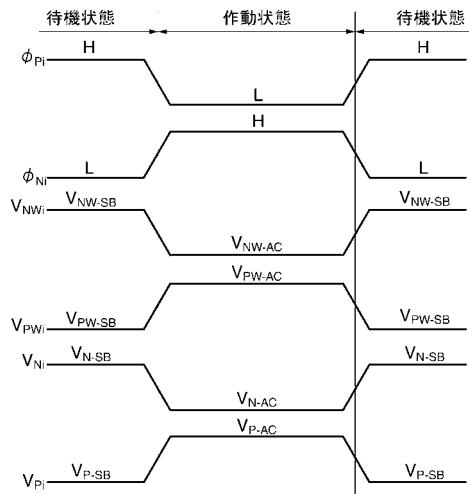

図4は回路ブロック20-iの作動状態/待機状態におけるバックゲート電位の変化を示すタイミングチャートである。上述したように、マスタユニット10はイベントドリブン式に遷移する有限ステートマシンの各状態に応じて回路ブロック20-iの待機状態/作動状態を制御する。マスタユニット10は回路ブロック20-iを待機状態に遷移させるには、PMOSトランジスタM P iのゲート電位 $V_{P_i}$ に論理レベルHを与える、NMOSトランジスタM N iのゲート電位 $V_{N_i}$ に論理レベルLを与える。すると、PMOSトランジスタM P iとNMOSトランジスタM N iは共にオフ状態となり、部分電源供給線 $L_a$ と部分接地線 $L_b$ はそれぞれ共通電源線 $V_{dd}$ と共通接地線 $V_{ss}$ とから電気的に切り離された状態となる。

#### 【0031】

さらに、マスタユニット10はPMOSトランジスタM P iのバックゲート電位 $V_{NW_i}$ を作動時の電位 $V_{NW\_AC}$ よりも昇圧させて $V_{NW\_SB}$ とし、NMOSトランジスタM N iのバックゲート電位 $V_{PW_i}$ を作動時の電位 $V_{PW\_AC}$ よりも降圧させて $V_{PW\_SB}$ とする。すると、これらPMOSトランジスタM P iとNMOSトランジスタM N iの各々はボディエフェクトによって閾値電圧が増加するため、待機時のリーク電流を減少させることができる。

#### 【0032】

マスタユニット10は、回路ブロック20-i内の論理素子を構成するPMOSトランジスタのバックゲート電位 $V_{N_i}$ についても同様に作動時の電位 $V_{N\_AC}$ よりも昇圧させて $V_{N\_SB}$ とし、NMOSトランジスタのバックゲート電位 $V_{P_i}$ についても同様に作動時の電位 $V_{P\_AC}$ よりも降圧させて $V_{P\_SB}$ とする。これにより、回路ブロック20-iの論理素子を構成するトランジスタの閾値電圧を増加させることができ、待機状態における回路ブロック20-iのリーク電流を減少させることができる。

#### 【0033】

一方、マスタユニット10は回路ブロック20-iを作動状態に遷移させるには、PMOSトランジスタM P iのゲート電位 $V_{P_i}$ に論理レベルLを与える、NMOSトランジスタM N iのゲート電位 $V_{N_i}$ に論理レベルHを与える。すると、PMOSトランジスタM P iとNMOSトランジスタM N iは共にオン状態となり、部分電源供給線 $L_a$ と部分接地線 $L_b$ はそれぞれ共通電源線 $V_{dd}$ と共通接地線 $V_{ss}$ に電気的に接続した状態となる。

#### 【0034】

さらに、マスタユニット10はPMOSトランジスタM P iのバックゲート電位 $V_{NW_i}$

10

20

30

40

50

を待機時の電位  $V_{NW-SB}$  よりも降圧させて  $V_{NW-AC}$  とし、N MOSトランジスタ  $M_{Ni}$  のバックゲート電位  $V_{Wi}$  を待機時の電位  $V_{PW-SB}$  よりも昇圧させて  $V_{PW-AC}$  とする。すると、これらPMOSトランジスタ  $M_{Pi}$  とN MOSトランジスタ  $M_{Ni}$  の各々は閾値電圧が減少するため、回路ブロック 20-iへの電源供給を速やかに行うことができる。これと同時に、マスタユニット 10 は、回路ブロック 20-i の論理素子を構成する PMOSトランジスタのバックゲート電位  $V_{Ni}$  を待機時の電位  $V_{N-SB}$  よりも降圧させて  $V_{N-AC}$  とし、NMOSトランジスタのバックゲート電位  $V_{Pi}$  を待機時の電位  $V_{P-SB}$  よりも昇圧させて  $V_{P-AC}$  とする。論理素子を構成するトランジスタの閾値電圧を減少させることで、低電圧動作において回路ブロックの動作スピードの低下を抑えることが出来るが、その代償としてリーク電流は増大する。本発明を以ってすれば、回路ブロック毎にきめ細かく、待機時のリーク電流を低く抑えることが可能となり、結果として回路全体の消費電力を抑えることができる。

10

20

30

40

50

### 【0035】

#### (第2の構成例)

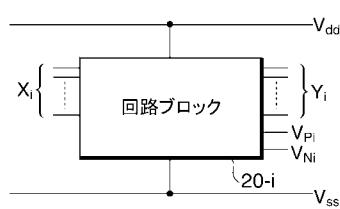

図7は第2の構成例における回路ブロックへの電源供給系統を示す回路図である。ここでは、i番目の回路ブロック 20-i の電源供給系統を図示するが、他の回路ブロックについても同様の回路構成を具備している。同図において、共通電源線  $V_{dd}$  は全ての回路ブロック 20-1, 20-2, ..., 20-M に電源供給を行うための電源線であり、共通接地線  $V_{ss}$  は全ての回路ブロック 20-1, 20-2, ..., 20-M を接地するための接地線である。このように、回路ブロック 20-i は常時電源供給を受ける構成となっている。また、同図において、 $X_i$  は回路ブロック 20-i への入力信号、 $Y_i$  は同回路ブロック 20-i からの出力信号、 $V_{Ni}$  は回路ブロック 20-i の論理素子を構成する PMOSトランジスタのバックゲート電位、 $V_{Pi}$  は回路ブロック 20-i の論理素子を構成する NMOSトランジスタのバックゲート電位を示している。

### 【0036】

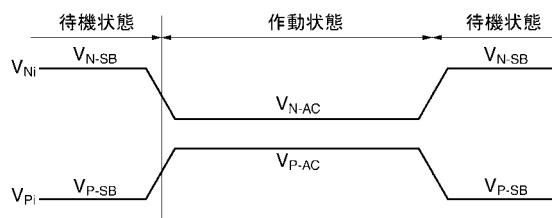

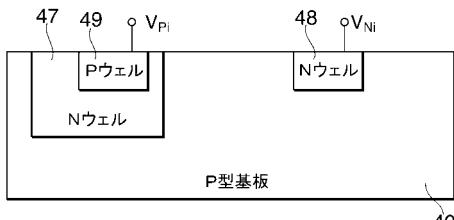

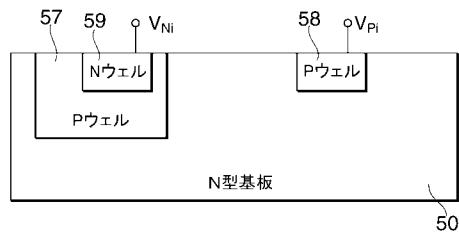

図9は回路ブロック 20-i の論理素子を形成するためのウェル構造を示している。同図に示すように、P型基板 40 をベースとして N ウェル 47、48 が形成され、さらに N ウェル 47 内に P ウェル 49 が形成されたトリプルウェル構造となっている。ウェル電位  $V_{Pi}$  は論理素子を構成する NMOSトランジスタのバックゲート電位を示しており、ウェル電位  $V_{Ni}$  は論理素子を構成する PMOSトランジスタのバックゲート電位を示している。回路ブロック 20-i のウェル構造は図9に示す構造に限らず、例えば、図10に示す構造としてもよい。同図に示す構造は N型基板 50 をベースとして P ウェル 57、58 が形成され、さらに P ウェル 57 内に N ウェル 59 が形成されたトリプルウェル構造となっている。ウェル電位  $V_{Pi}$  は論理素子を構成する NMOSトランジスタのバックゲート電位を示しており、ウェル電位  $V_{Ni}$  は論理素子を構成する PMOSトランジスタのバックゲート電位を示している。

### 【0037】

図8は回路ブロック 20-i の作動状態 / 待機状態におけるバックゲート電位の変化を示すタイミングチャートである。上述したように、マスタユニット 10 はイベントドリブン式に遷移する有限ステートマシンの各状態に応じて回路ブロック 20-i の待機状態 / 作動状態におけるバックゲート電位を制御する。回路ブロック 20-i が待機状態のときは、マスタユニット 10 はバックゲート電位  $V_{Ni}$  を作動状態のときの電位  $V_{N-AC}$  よりも昇圧して  $V_{N-SB}$  とし、バックゲート電位  $V_{Pi}$  を作動状態のときの電位  $V_{P-AC}$  よりも降圧して  $V_{P-SB}$  とする。これにより、論理素子を構成するトランジスタの閾値電圧を増加させることができるために、待機時における回路ブロック 20-i のリーク電流を減少させることができる。一方、回路ブロック 20-i が作動状態になるときは、マスタユニット 10 はバックゲート電位  $V_{Ni}$  を待機状態のときの電位  $V_{N-SB}$  よりも降圧して  $V_{N-AC}$  とし、バックゲート電位  $V_{Pi}$  を待機状態のときの電位  $V_{P-SB}$  よりも昇圧して  $V_{P-AC}$  とする。これにより、論理素子を構成するトランジスタの閾値電圧を低下させて低電圧駆動を行なうことが可能となる。

## 【0038】

このように、本実施形態によれば、VLSIチップ内の半導体集積回路を複数の回路ブロック20-1, 20-2, …, 20-Mに細分割し、待機状態における回路ブロック20-1, 20-2, …, 20-Mの論理素子を形成するトランジスタの閾値電圧が増加するようにバックゲート電位を制御する構成であるため、待機時のリーク電流を大幅に減少させることができる。特に、携帯電話のようにバッテリを主電源とする可搬性電子機器においては低消費電力化が大きな課題であるため、本発明の有用性は高く、汎用性の高い低消費電力のSOC(System On Chip)、SOB(System On Board)、SOP(System On Panel)を構築することができる。また、電力分配制御の対象となる回路ブロックを新たに追加・削除・変更する場合においても、制御ロジックを新たに組み立て直し、有限ステートマシンを再設計することにより対応が可能となる。尚、本発明はウェル構造を有してバックゲートの電圧制御を行うスイッチング素子であれば、MOSトランジスタに限らず、適用できることは言うまでもない。

10

## 【0039】

## [発明の実施形態2]

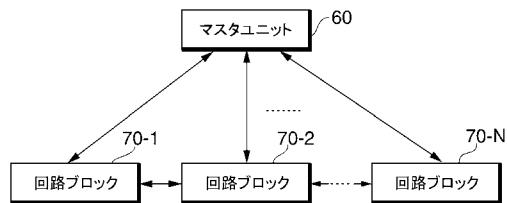

図11は半導体集積回路を構成する複数の回路ブロック同士が相互にコミュニケーションを行ってCSP(Communicating Sequential Processes)方式により自律的に又は他律的にバックゲート電位制御を行うシステムのプロック図である。VLSIチップ内の半導体集積回路は、待機状態から作動状態へ、又は作動状態から待機状態への状態遷移を有するN個の回路ブロック(論理ブロック)70-1, 70-2, …, 70-Nに論理的に分割されている。VLSIチップ全体の消費電力を低減するには、機能別に分類される多数の回路ブロックに分割することが望ましい。これらの回路ブロック70-1, 70-2, …, 70-Nはシステム中央制御用のグローバルクロックを基準に動作するのではなく、各々の回路ブロック70-1, 70-2, …, 70-Nが自律的に又は他律的に動作する必要があると判断した場合に電源供給を受けて動作するよう構成された非同期システムである。マスタユニット60(制御回路)は、主に、外部回路及び回路ブロック70-1, 70-2, …, 70-Nとの直接的又は間接的な通信を行ってシステム全体の調整を司る機能を果たす回路ブロックであるが、回路ブロック70-1, 70-2, …, 70-Nへの電源供給を直接的に制御するものではない。各回路ブロックへの電源供給は各回路ブロックに内蔵又は付帯する電源制御回路によって直接的に制御されるが、作動状態から待機状態への遷移のタイミングは、各回路ブロック自らが自律的に定め、待機状態から作動状態への遷移は他の回路ブロックからのリクエストを受けて他律的に定まる。これらのタイミングにおいて、回路ブロックは自ら内蔵する又は付帯する電源制御回路を通して、自らの電源供給を制御する。

20

30

## 【0040】

図12はCSP方式による回路ブロックへのバックゲート電位制御を行う様子を示す説明図である。ここでは説明の便宜上4つの回路ブロック70-1～70-4を例示して説明するが、実際にはN個の回路ブロック70-1, 70-2, …, 70-Nとマスタユニット60が相互にコミュニケーションを行うことにより回路ブロック70-1, 70-2, …, 70-Nへのバックゲート電位制御を行う。回路ブロック70-1～70-4への電源供給はイベント駆動によって制御され、自律的に動作する必要があると判断した場合と、他律的に動作する必要があると判断した場合に電源供給を受けて動作する。各々の回路ブロック70-1～70-4は「チャネル」を通じて他の回路ブロック70-1～70-4又はマスタユニット60と接続し、局所的な協調の下でイベント駆動を行う。チャネルはその両端において「ポート」と接続する。

40

## 【0041】

同図に示す例では、回路ブロック70-1はポートa1, a2, a3を、回路ブロック70-2はポートb1, b2, b3を、回路ブロック70-3はポートc1, c2を、回路ブロック70-4はポートd1, d2を、マスタユニット60はポートx1, x2, x3をそれぞれ具備している。回路ブロック70-1に着目すると、回路ブロック70-1

50

はチャネル 1 , 2 , 3 を通じてマスタユニット 60 、回路ブロック 70 - 2 , 70 - 3 と接続している。

#### 【 0 0 4 2 】

チャネルを通じたポート間通信においては、全てのポートには 'Active' 又は 'Passive' のうち何れかの属性が付与される。例えば、回路ブロック 70 - 1 がチャネル 2 を通じて自律的に回路ブロック 70 - 2 に向けてデータ転送を要求する場合は、回路ブロック 70 - 1 のポート a2 には 'Send Active' の属性が付与され、他律的にデータ転送の要求を受け入れる回路ブロック 70 - 2 のポート b1 には 'Receive Passive' の属性が付与される。これとは逆に回路ブロック 70 - 1 がチャネル 2 を通じて回路ブロック 70 - 2 から自立的にデータ転送を要求する場合は、ポート a2 には 'Receive Active' の属性が付与され、他律的にデータ転送を行う回路ブロック 70 - 2 のポート b1 には 'Send Passive' の属性が付与される。ポート間通信においては、req/ack 信号を送受信することにより、2 相式又は 4 相式のハンドシェイクが行われる。10

#### 【 0 0 4 3 】

回路ブロック 70 - i の電源供給系統の回路構成は上述した図 3 又は図 7 と同様の構成とすることができる。回路ブロック 70 - i を図 3 に示す回路構成とする場合には、回路ブロック 70 - i の論理素子を形成するトランジスタのバックゲート電位  $V_{Pi}$  ,  $V_{Ni}$  の制御に加えて、スイッチングトランジスタのゲート電位  $V_{Pi}$  ,  $V_{Ni}$  とバックゲート電位  $V_{NWi}$  ,  $V_{PWi}$  の制御も必要となる。 $VLSI$  チップのウェル構造についても、上述の図 5 又は図 6 に示すトリプルウェル構造となる。一方、回路ブロック 70 - i を図 7 に示す回路構成とする場合には、回路ブロック 70 - i の論理素子を形成するトランジスタのバックゲート電位  $V_{Pi}$  ,  $V_{Ni}$  の制御が必要となる。 $VLSI$  チップのウェル構造についても、上述の図 9 又は図 10 に示すトリプルウェル構造となる。20

#### 【 0 0 4 4 】

上述の第 1 実施形態では回路ブロック 70 - i のバックゲート電位制御をマスタユニット 10 が行っていたが、本実施形態では前述した「チャネル」と「ポート」によって回路ブロック 70 - i のバックゲート電位制御を自律的に又は他律的に行う。「チャネル」と「ポート」は回路ブロック 70 - i の動作状態にかかわらず、常時電源供給を受けて作動するように構成されている。30

#### 【 0 0 4 5 】

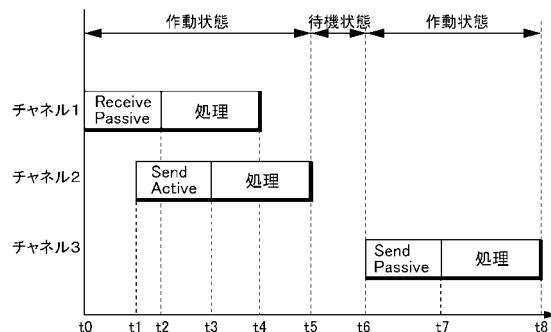

図 13 は回路ブロックへの電源供給のタイミングを説明するためのタイミング図である。ここでは、回路ブロック 70 - 1 に着目して説明するが、他の回路ブロックについても同様となる。上述したように回路ブロック 70 - 1 はチャネル 1 ~ 3 を介してマスタユニット 60 、回路ブロック 70 - 2 , 70 - 3 と接続している。時刻  $t_0$  においてシステムが起動し、マスタユニット 60 からのリクエストに応答して回路ブロック 70 - 1 がデータ受信要求を受け入れる場合には、Receive Passiveとなり、時刻  $t_2$  ~ 時刻  $t_4$  での期間において所望の動作処理を行う。回路ブロック 70 - 1 は、さらに、時刻  $t_1$  においてチャネル 2 を通じて自律的に回路ブロック 70 - 2 へのデータ送信を要求する場合には、Send Activeとなり、時刻  $t_3$  ~ 時刻  $t_5$  までの期間において所望の動作処理を行う。回路ブロック 70 - 1 は、さらに、時刻  $t_6$  においてチャネル 3 を通じて回路ブロック 70 - 3 からのデータ送信要求を受け入れる場合には、Send Passiveとなり、時刻  $t_7$  ~ 時刻  $t_8$  までの期間において所望の動作処理を行う。40

#### 【 0 0 4 6 】

時刻  $t_0$  ~ 時刻  $t_5$  までの期間と、時刻  $t_6$  ~ 時刻  $t_8$  までの期間においては、回路ブロック 70 - 1 はマスタユニット 60 と回路ブロック 70 - 2 , 70 - 3 とのコミュニケーションを通じて自律的に又は他律的に動作するため（作動状態）、チャネル 1 , 2 , 3 とポート a1 , a2 , a3 は、同期間ににおいて回路ブロック 70 - 1 を構成する論理素子の閾値電圧が減少するようにバックゲート電位  $V_{Pi}$  ,  $V_{Ni}$  を制御する。回路ブロック 70 - 1 が図 3 に示すようにスイッチング素子を介して電源供給を受ける場合には、スイッチング素子がオンとなるように、ゲート電位  $V_{Pi}$  ,  $V_{Ni}$  とバックゲート電位  $V_{NWi}$  ,  $V_{PWi}$  の制御50

を併せて行う。具体的な制御方法は図4又は図8に示すように行えばよい。

#### 【0047】

一方、時刻 $t_5$ ～時刻 $t_6$ までの期間では回路ブロック70-1は動作する必要がないため(待機状態)、チャネル1, 2, 3とポート $a_1$ ,  $a_2$ ,  $a_3$ は、同期間において、回路ブロック70-1を構成する論理素子の閾値電圧が増加するようにバックゲート電位 $V_{Pi}$ ,  $V_{Ni}$ を制御する。回路ブロック70-1が図3に示すようにスイッチング素子を介して電源供給を受ける場合には、スイッチング素子がオフとなるように、ゲート電位 $V_{Pi}$ ,  $V_{Ni}$ とバックゲート電位 $V_{NWi}$ ,  $V_{PWi}$ の制御を併せて行う。具体的な制御方法は図4又は図8に示すように行えばよい。

#### 【0048】

10 このように、本実施形態によれば、CSP方式により回路ブロック70-1, 70-2, ..., 70-Nへのきめ細かなバックゲート電位制御が可能となる上に、回路ブロックの追加・削除・変更などが生じても関係する回路ブロックとの交信内容・交信方法を設計し直すだけでよいため、システム再構築の利便性に優れている。

#### 【0049】

##### [発明の実施形態3]

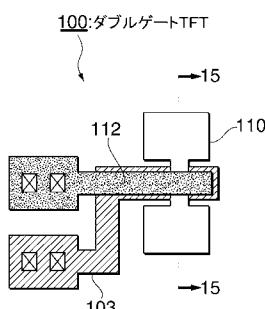

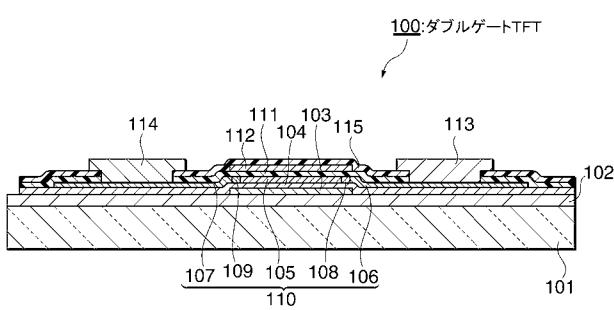

図14と図15にダブルゲートTFT(Thin Film Transistor)100を示す。図14は平面図であり、図15はその15-15線に沿った断面図である。絶縁基板101上には下地層102を介してバックゲート電極103が形成されている。絶縁基板101としては、例えば、ガラス基板、石英基板、プラスチック基板等を用いることができる。バックゲート電極103と下地層102の上面には、バックゲート絶縁膜104、活性層110、ゲート絶縁膜111、ゲート電極112、及び層間絶縁膜115が順次積層されている。活性層110は島状の多結晶シリコン等から成り、上下2つのゲート間に形成されたチャネル領域105と、その両側に形成されたドレイン領域106、及びソース領域107から成る。バックゲート電極103とゲート電極112はチャネル領域105をその間に挟んで対向配置されている。ドレイン領域106、ソース領域107のそれぞれにはコンタクトホールを通じてドレイン電極113、ソース電極114が形成されている。ここで、バックゲート電極103とは、TFT構造がトップゲート型のときには、ゲート電極112に対向するようにボトム側(絶縁基板側)に形成された電極をいい、TFT構造がボトムゲート型のときには、ゲート電極112と対向するようにトップ側に形成された電極をいう。同図に示すTFT構造はトップゲート型であるが、ボトムゲート型でもよい。

#### 【0050】

本実施形態では上述した第1実施形態の回路ブロック20-1, 20-2, ..., 20-Mの論理素子を構成するNMOSトランジスタ或いはPMOSトランジスタ、又は回路ブロック20-iへの電源供給を通電/遮断するスイッチング素子としてのPMOSトランジスタMPi或いはNMOSトランジスタMNi、又は上述した第2実施形態の回路ブロック70-1, 70-2, ..., 70-Nの論理素子を構成するNMOSトランジスタ或いはPMOSトランジスタをダブルゲートTFT100で構成する。ダブルゲートTFT100が待機状態のときにはトランジスタの閾値電圧が増加するようにバックゲート電極103の電位を調整することで、リーキ電流を十分に低減できる。一方、ダブルゲートTFT100が作動状態のときにはトランジスタの閾値電圧が減少するようにバックゲート電極103の電位を調整することでオン電流を増大させ、ドライブ能力を高めることができる。バックゲート電極103の電位制御は第1実施形態と同様にマスタユニット10によってイベントドリブン式に制御してもよく、又は第2実施形態と同様にCSP方式により自律的又は他律的に制御してもよい。また、回路ブロック20-1, 20-2, ..., 20-M、又は回路ブロック70-1, 70-2, ..., 70-Nの論理素子をダブルゲートTFT100で構成する場合には、ゲート電極112とバックゲート電極103を同じ論理で制御することによって、トランジスタの立ち上がり時間又は立下り時間を短縮し、スイッチング速度を向上できる。また、ドライブ能力を高めることで、トランジスタサイズを縮小し、高集積化を可能にできる。

## 【0051】

更に、第1又は第2実施形態で説明したバルク構造のMOSトランジスタに比べると、ダブルゲートTFT100は半導体ウェルを有しないために、そのドレイン容量はチャネル・ドレイン接面の逆バイアス領域分のみであるから極めて小容量であり、スイッチング時の充放電量は被駆動側トランジスタのゲート容量に比べて極めて小さい。従って、同じ移動度を有するバルク構造のMOSトランジスタと比べて更なる高速化、低消費電力化が可能である。また、ダブルゲートTFT100は絶縁基板101及び下地層102を有するため、配線の対電源線容量が極めて小さい。従って、同じ移動度を有するバルク構造のMOSトランジスタと比べて更なる高速化、低消費電力化が可能である。

## 【0052】

このようなダブルゲートTFT100の構造として、例えば、ドレイン領域106又はソース領域107に接するチャネル領域105の端面に不純物がライトドープされたLDD(Lightly Doped Drain)領域108, 109を形成するのが望ましい(図15参照)。LDD領域108, 109を追加することによって、ドレイン端空乏領域の電界は弱くなり、電子と正孔の対生成が速いプール・フレンケル効果(Poole-Frenkel Effect)を伴うフォノン・アシスト・トネリング現象(Phonon Assisted Tunneling)が抑制されて、熱励起現象のみとなるので、ダブルゲートTFT100のリーク電流(オフ電流)を低減できる。また、ゲート電極112とバックゲート電極103はチャネル領域105への投影形状が重なるように略同形に形成されているのが望ましい(図14参照)。チャネル領域105の表裏をゲート電極112とバックゲート電極103によって挟み込むことによりサブスレッシュホールド係数を小さくし、電界移動度を向上できる。更に、バックゲート電極103はチャネル領域105への投影形状がLDD領域108, 109の全部又は一部と重なるような形状(又は大きさ)にするのが望ましい。これにより、トランジスタ待機時のリーク電流の低減と、トランジスタ作動時の電界移動度の向上を両立できる。

## 【0053】

## [発明の実施形態4]

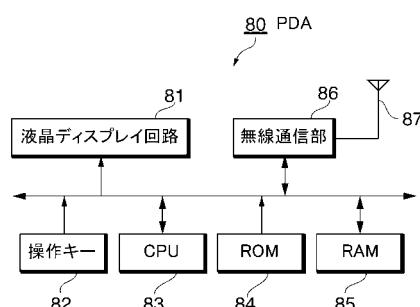

次に、本発明の半導体集積回路を搭載した電子機器の例を示す。図16は通信機能を搭載した携帯型パーソナルデジタルアシスタンス(PDA)のブロック図である。同図に示すように、PDA80は、液晶ディスプレイ回路81と、操作キー82と、CPU83と、ROM84と、RAM85と、無線通信部86と、アンテナ87とを備えて構成されている。CPU83、無線通信部86などは本発明の半導体集積回路を実装したICチップで構成されており、装置全体の低消費電力化を実現している。特に、PDAのような携帯情報端末はバッテリの持続時間を長く確保したいため、特に好適である。

## 【0054】

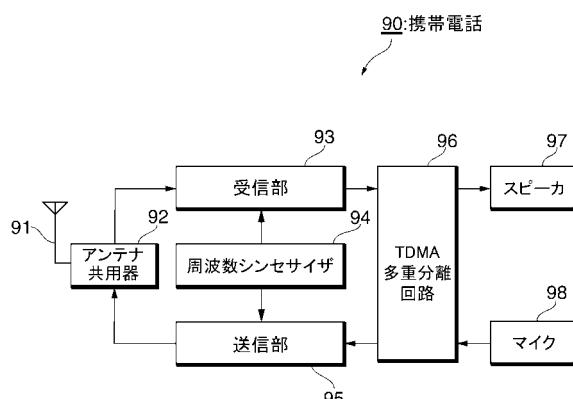

図17はデジタル通信方式の携帯電話のブロック図である。携帯電話90は、アンテナ91と、アンテナ共用器92と、受信部93と、周波数シンセサイザ94と、送信部95と、TDMA多重分離回路96と、スピーカ97と、マイク98を備えて構成されている。受信部93、送信部95、TDMA多重分離回路96などは本発明の半導体集積回路を実装したICチップで構成されており、装置全体の低消費電力化を実現している。

## 【0055】

より詳細には、受信部93は高周波増幅器、受信ミキサ、IF増幅器、遅延検波回路などを含んで構成されており、これらは本発明の半導体集積回路を実装した一又は二以上のICチップで構成されている。同様に、送信部95はIQ信号発生回路、直交変調器、送信ミキサ、送信電力増幅器などを含んで構成されており、これらについても本発明の半導体集積回路を実装した一又は二以上のICチップで構成されている。

## 【0056】

携帯型の電子機器は特に低消費電力化が要求されるため、本発明の半導体集積回路を実装したICチップで電子機器を構成することにより、電子機器に搭載されるバッテリの持続時間をできるだけ長くすることができる。本発明の半導体集積回路を実装したICチップで構成される電子機器としては、PDAや携帯電話の他に、例えば、バッテリ駆動され

10

20

30

40

50

る携帯機器、録音再生機器、録画再生機器、シートコンピュータ、電子ペーパ、ウェアラブルコンピュータ、I C カード、スマート・カード、ビデオカメラ、パーソナルコンピュータ、ヘッドマウントディスプレイ、プロジェクタ、ウェアラブル型健康管理機器、ウェアラブル型トイ、偏在型無線センサ、R F I D、貼付型温度計、表示機能付きファックス装置、携帯型 T V 、電子手帳、電光掲示板、宣伝広告用ディスプレイ、表示機能付き無線タグ、S O P ( System-On-Panel ) 、S O G ( System-On-Glass ) 、S O B ( System-On-Board ) 等が含まれる。

【図面の簡単な説明】

【0057】

【図1】第1実施形態のシステムブロック図である。

10

【図2】電力分配制御を行う有限ステートマシンの状態遷移図である。

【図3】回路ブロックへの電源供給系統を示す回路図である（構成例1）。

【図4】バックゲート電位のタイミングチャートである。

【図5】V L S I チップのウェル構造を示す図である。

【図6】V L S I チップのウェル構造を示す図である。

【図7】回路ブロックへの電源供給系統を示す回路図である（構成例2）。

【図8】バックゲート電位のタイミングチャートである。

【図9】V L S I チップのウェル構造を示す図である。

【図10】V L S I チップのウェル構造を示す図である。

20

【図11】第2実施形態のシステムブロック図である。

【図12】C S P 方式による電力分配制御の説明図である。

【図13】回路ブロックへの電源供給のタイミング図である。

【図14】ダブルゲートT F T の断面図である。

【図15】ダブルゲートT F T の平面図である。

【図16】本発明を応用したP D A のブロック図である。

【図17】本発明を応用した携帯電話のブロック図である。

【符号の説明】

【0058】

10 , 60 ... マスタユニット 20 , 70 ... 回路ブロック  $V_{dd}$  ... 共通電源線  $V_{ss}$  ... 共通接地線  $L_{ai}$  ... 部分電源供給線  $L_{ai}$   $L_{bi}$  ... 部分接地線  $p_i$  ... PMOSトランジスタM P i のゲート電位  $V_{NWi}$  ... PMOSトランジスタM P i のバックゲート電位  $N_i$  ... NMOSトランジスタM N i のゲート電位  $V_{PWi}$  ... NMOSトランジスタM N i のバックゲート電位  $X_i$  ... 回路ブロック20 - iへの入力信号  $Y_i$  ... 回路ブロック20 - iからの出力信号

30

【図1】

【図3】

【図2】

【図4】

【図5】

【図8】

【図6】

【図9】

【図7】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

---

フロントページの続き

| (51)Int.Cl. <sup>7</sup> | F I          | テーマコード(参考) |

|--------------------------|--------------|------------|

| H 01 L 27/092            | H 01 L 29/78 | 6 1 7 N    |

| H 01 L 29/786            | H 01 L 29/78 | 6 1 6 A    |

| H 03 K 19/00             | H 01 L 27/08 | 3 2 1 D    |

F ターム(参考) 5F048 AA01 AC04 BA16 BB14 BC06 BC16

5F110 AA01 AA06 AA08 AA09 BB04 DD01 DD02 DD03 EE30 GG02

GG13 HM15

5J056 AA00 BB17 CC03 EE04 FF07 GG09