## (19) United States

## (12) Patent Application Publication (10) Pub. No.: US 2017/0047274 A1 Shibuya

Feb. 16, 2017 (43) **Pub. Date:**

### (54) DOUBLE SIDE HEAT DISSIPATION FOR SILICON CHIP PACKAGE

(71) Applicant: Texas Instruments Incorporated,

Dallas, TX (US)

Inventor: Makoto Shibuya, Beppu city (JP)

Assignee: TEXAS INSTRUMENTS

**INCORPORATED**, Dallas, TX (US)

Appl. No.: 14/825,154

Aug. 12, 2015 (22) Filed:

#### **Publication Classification**

(51) Int. Cl.

H01L 23/495 (2006.01)H01L 21/56 (2006.01) H01L 21/78 (2006.01)(2006.01) H01L 21/48

(52) U.S. Cl.

CPC ... H01L 23/49568 (2013.01); H01L 23/49548 (2013.01); H01L 23/49562 (2013.01); H01L 21/4825 (2013.01); H01L 21/565 (2013.01); H01L 21/78 (2013.01); H01L 21/4871 (2013.01)

#### (57) ABSTRACT

System, method, and silicon chip package for providing structural strength, heat dissipation and electrical connectivity using "W" shaped frame bonded to the one or more dies, wherein the "W" shaped frame provides compression strength to the silicon chip package when the one or more dies are bonded, and electrically conductivity between for the one or more dies to leads of silicon chip package, and heat dissipation for the silicon chip package.

# DOUBLE SIDE HEAT DISSIPATION FOR SILICON CHIP PACKAGE

#### TECHNICAL FIELD

[0001] This invention relates generally to the field of silicon chip packaging, and particularly dual sided heat dissipating structures.

#### BACKGROUND

[0002] In silicon chip fabrication, a common trend is to provide for smaller chips to support ever increasingly smaller devices. Alternatively, more compact packaging of chips has become a solution to support increasingly smaller devices. Compact packaging becomes smaller packaging. Chip packaging is trending from through-hole design (THD) to surface mounted design (SMD). Further, requirements for such chip packaging are trending to higher power which leads to the need for better heat dissipation of the packages. [0003] In addition to design requirements of chip packaging involving smaller or more compact designs, these chips use more power and generate high heat. There have been many efforts to design compact chips with improved heat dissipation including dual cool packages that dissipate heat from both sides of the chip package. These packages improve heat dissipation; however, the process of assembling the double-sided heat dissipation packages is complicated compared to single side heat dissipation packages.

### SUMMARY

[0004] In accordance with an embodiment, a method for forming a dual sided chip package is provided. The method includes superimposing a frame with increased surface area to a large matrix array of one or more dies, bonding the frame to one or more dies molding the frame to one or more dies with an upside mold die and a downside mold die, and singulating the joints of the frame to expose heat sinks.

[0005] In accordance with an embodiment, a silicon chip package is provided. The silicon chip package comprising: one or more dies, a frame bonded to the one or more dies. The frame provides compression strength to the silicon chip package when the one or more dies are bonded, and electrically conductivity between for the one or more dies to leads of silicon chip package.

[0006] In accordance with an embodiment, a system is provided. The system includes one or more processors; memory coupled to the one or more processors; and a chip package configured to the one or more processors and memory. The system further includes one or more dies; and a frame bonded to the one or more dies. The frame provides dual sided heat dissipation for the chip package and electrically conductivity between for the one or more dies.

#### BRIEF DESCRIPTION OF THE DRAWINGS

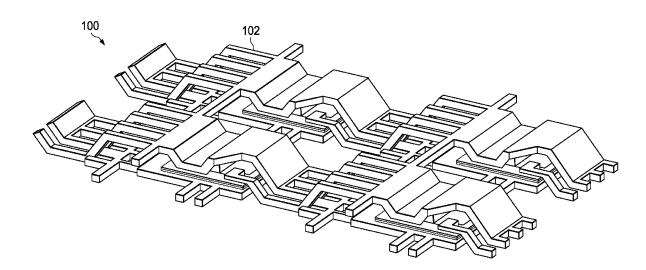

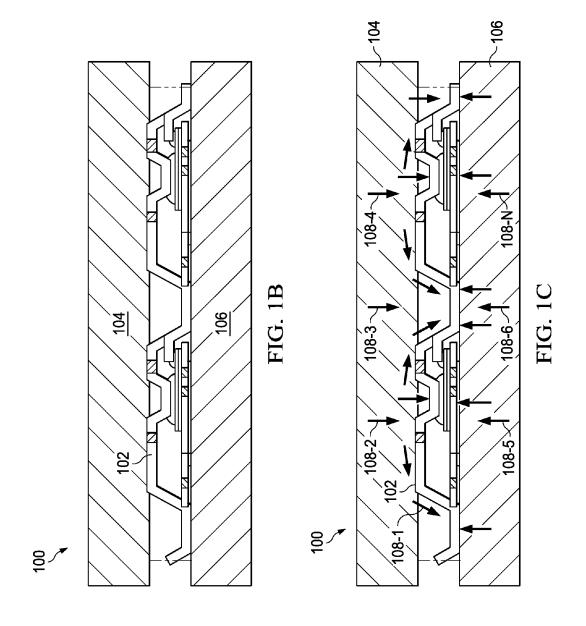

[0007] FIG. 1A is an isometric view of an example a "W" shaped clip for a chip package implementation according to some embodiment.

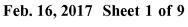

[0008] FIG. 1B is a cross sectional view of a "W" shaped clip for a chip package with upside die mold and downside die mold implementation according to some embodiment.

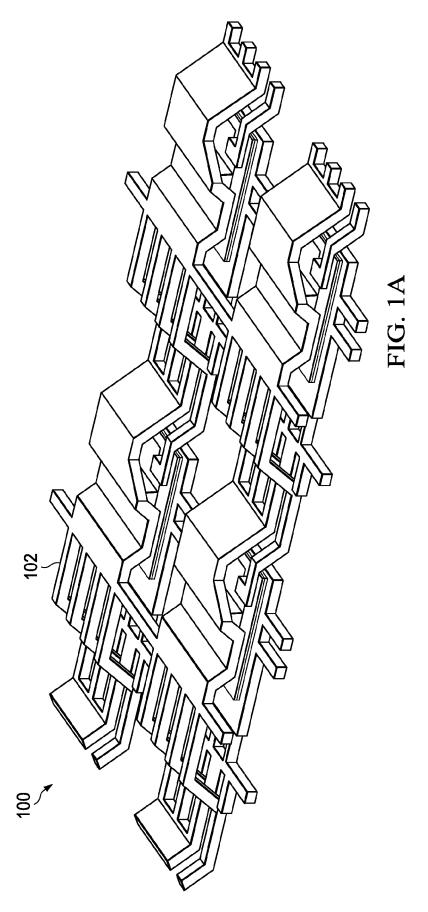

[0009] FIG. 1C is a cross sectional view of a "W" shaped clip for a chip package implementation showing clamping pressure from upside die mold and downside die mold according to some embodiment.

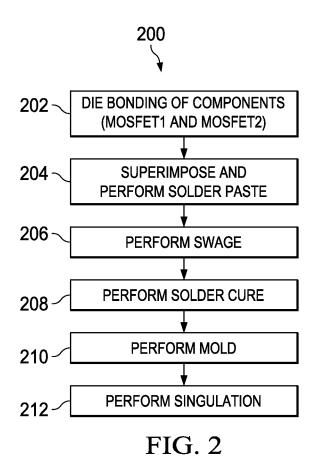

[0010] FIG. 2 illustrates an example flow diagram of a process for forming a silicon chip package for double sided heat dissipation according to some embodiment.

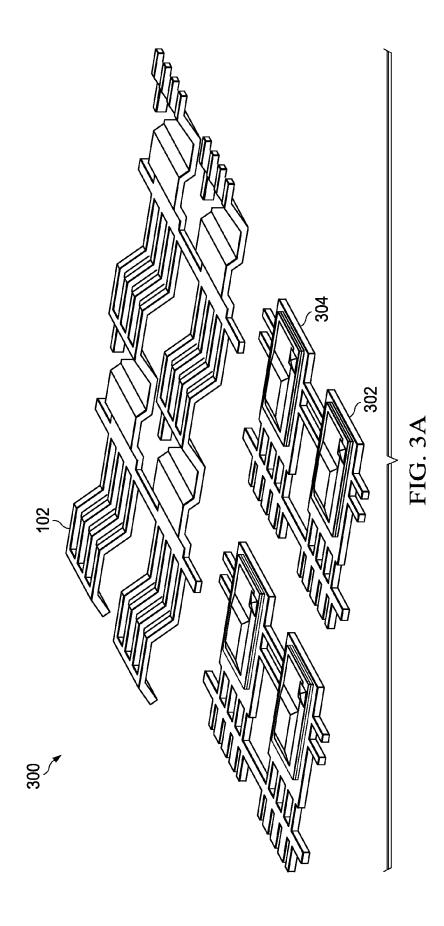

[0011] FIG. 3A illustrates an example die bonding process according to some embodiment.

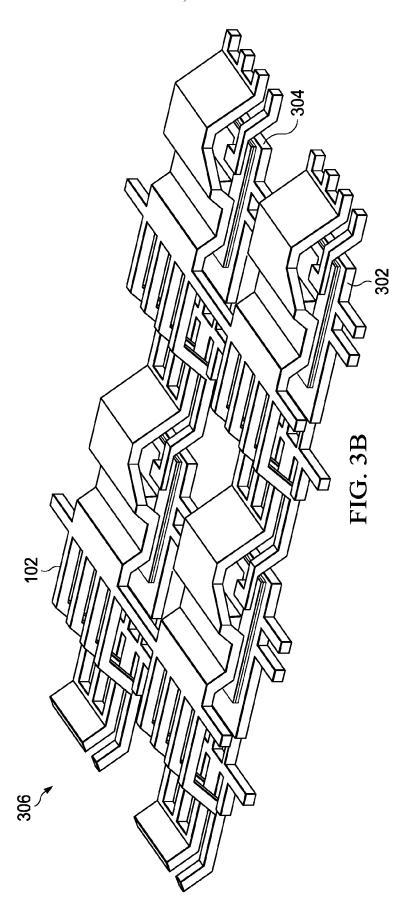

[0012] FIG. 3B illustrates an example superimposition and solder paste process according to some embodiment.

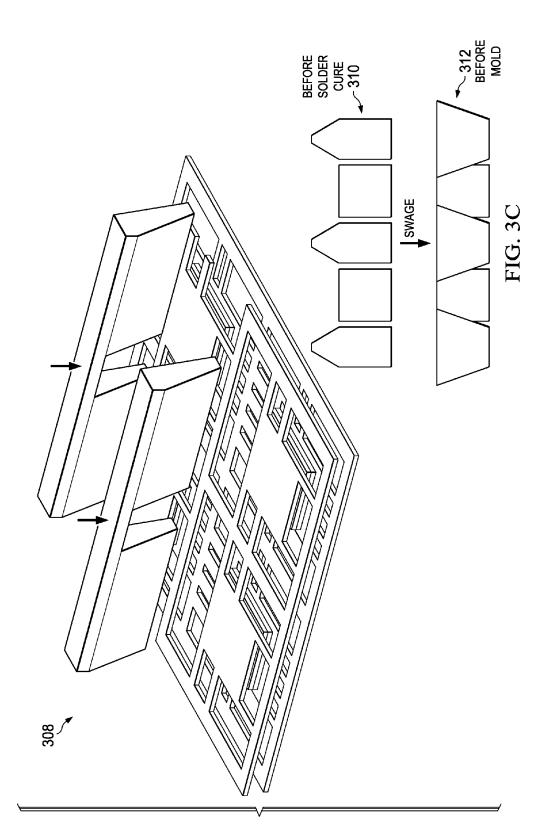

[0013] FIG. 3C illustrates an example swage process according to some embodiment.

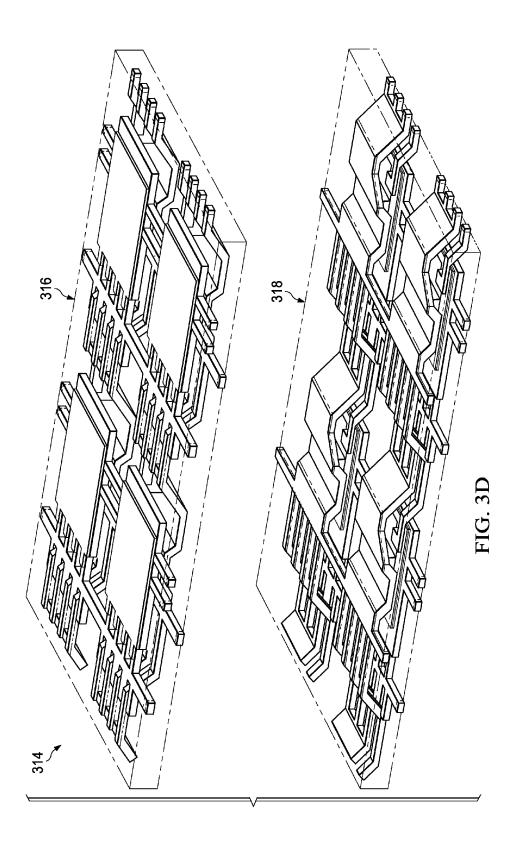

[0014] FIG. 3D illustrates an example molding process according to some embodiment.

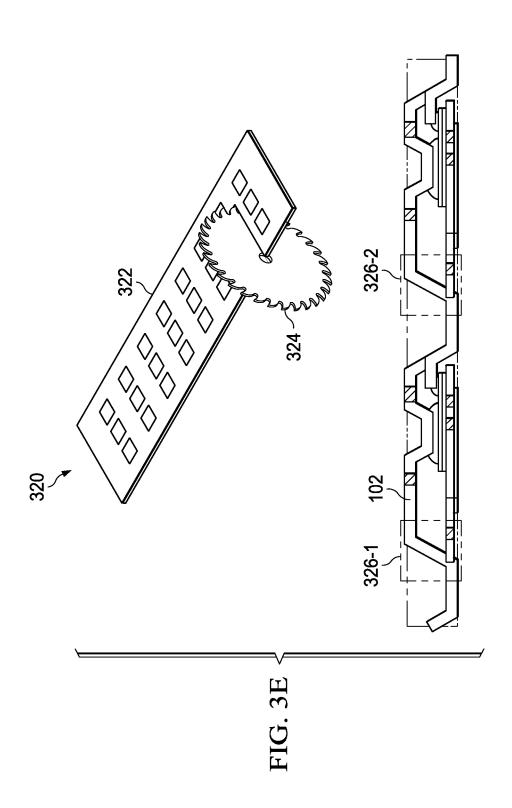

[0015] FIG. 3E illustrates an example singulation process according to some embodiment.

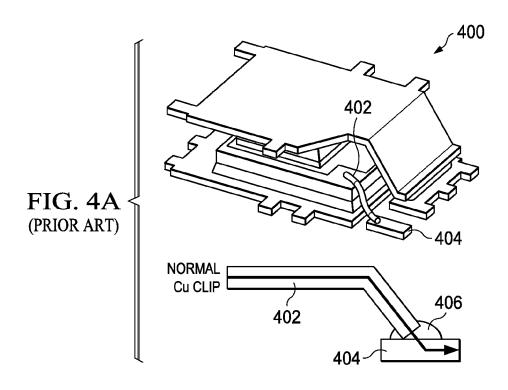

[0016] FIG. 4A illustrates prior art frame clipping structure

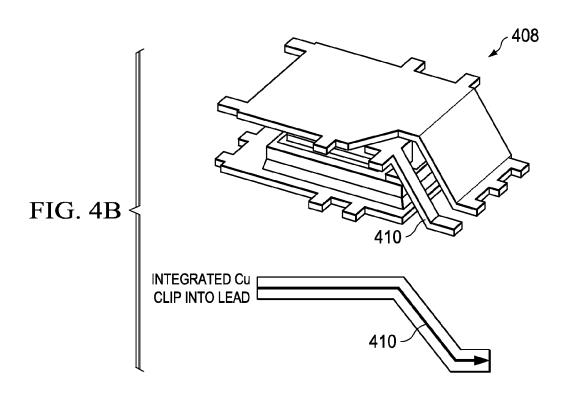

[0017] FIG. 4B illustrates an example integrated frame clipping structure according to some embodiment.

[0018] FIG. 5 illustrates an example of a system using semiconductor chip packaging according to some embodiment.

#### DETAILED DESCRIPTION

[0019] The following description provides many different embodiments, or examples, for implementing different features of the subject matter. These descriptions are merely for illustrative purposes and do not limit the scope of the invention.

[0020] Referring to FIG. 1A, an isometric view of a heatsink frame clip 102 is shown for a chip package 100. The frame clip is shaped such to increase the surface mount area for better heat dissipation. In the present example the clip is "W" shaped; however, the frame clip can be shaped in any form to increase the surface mount area for increased heat dissipation for example the clip can be corrugated, bent, folded into alternate furrows and/or ridges, wrinkled, or the like. The chip package 100 can include quad flat non leads (QFN) packages. In the present example, the "W" shaped clip 102 provides structural strength for loads on a silicon chip. In particular, the "W" shaped clip 102 acts as pillars for structural strength for stress placed on the silicon chip. In addition, the "W" shaped clip 102 acts a dual sided heat disperser for a silicon chip package. In particular, the "W" shaped clip 102 provides a greater surface area on either side as compared to, for example, single sided structures. Other advantages of the "W" shaped clip or frame 102 include foregoing certain wire bonding processes, in particularly when "W" shaped clip 102 is made of electrically conductive material, such as copper (Cu) or similar material. The electrically conductive "W" shaped clip 102 also provides electrical connections.

[0021] The chip package 100 may be connected to or be part of a system, such as an electronic device (not shown). The electronic device may be a computing device, electronic control device, mobile device, or any other device that uses semiconductor chips. The device system may include one or more processors, memory, intra and inter connectivity that can include wireless and wired connections.

[0022] Referring to FIG. 1B, an example cross sectional view is shown of a "W" shaped clip 102 for a chip package 100. The "W" shaped clip or frame 102 is part of the chip package 100. The chip package 100 is formed with the W" shaped clip or frame 102 using an upside mold die 104 and a downside mold die 106. Referring to FIG. 1C, the upside die mold 104 and downside die mold 106 exert clamping

pressure on the "W" shaped clip. During a molding process when upside die mold 104 and downside die mold 106 are applied to the chip package 100, clamping pressure as represented by arrows 108 is observed. The "W" shaped clip or frame 102 possess structural strength to support against such clamping pressure.

[0023] Referring to FIG. 2, an example flow diagram of a process for forming a silicon chip package for double sided heat dissipation is shown. The process 200 may be applied in forming the silicon chip package 100 described above. At 202, die bonding is performed. In this example, the die is metal oxide semiconductor field effect transistors (MOS-FET); however, the process can be applied to any kind of semiconductor die. Further, multiple dies can also be bonded together for example, a MOSFET1 and MOSFET2 can be bonded together. In certain implementations, an electrical conductive "W" shaped clip or frame provide for gate, source, and drain connections of the MOSFETs.

[0024] At 204, dies are superimposed with the frame and the process of solder paste application is performed. In particular the electrical conductive "W" shaped clip or frame is superimposed over the bonded dies, such as MOSFETs. At 206, swaging is performed. Swaging includes pressing the electrical conductive "W" shaped clip or frame and bonded dies together. The shape of the "W" shaped clip or frame provides for strength for the chip package to withstand swaging. At 208, a solder cure is performed on electrical conductive "W" shaped clip or frame and bonded dies (MOSFETs). The molding of the chip is performed at 210. Molding for a dual sided package can involve an upside mold die and a downside mold die as discussed above. Because of the shape of the clip (such as "W" shaped in the present example), the mold die withstands the molding pressure. At 212, the singulation is performed. Singulation is a process of separating the chip package. Singulation can be performed at joints of the heat sink of the "W" shaped clip. Since the "W" shaped clip, the polishing of the surface is not needed and that step is complete eliminated resulting in much simplified and cost effective packaging.

[0025] Referring to FIG. 3A, a process 300 for bonding dies is shown. In this example MOSFETs as represented by MOSFET 302 and MOSFET 304 are bonded to a chip package. As shown in FIG. 3B, the "W" shaped clip or frame 102 is superimposed over the dies or MOSFET 302 and MOSFET 304. The superimposing may include performing a solder paste. FIG. 3C illustrates swaging of the "W" shaped clip or frame and bonded dies. The swaging involves pressing the components together. Cross sectional view 310 shows components before the swaging, and cross sectional view 312 shows the components after the swaging.

[0026] Referring to FIG. 3D, molding of the chip package 314 is shown. In particular, an upside mold die and a downside mold die are used. The chip package is dual sided, having a top side 316 and a downside 318. Since after the molding, both sides of the chip package are exposed, no additional polishing is needed. Referring to FIG. 3E, singulation of the chip package is shown. In particular, the chip package 322 is singulated, such as with a "saw" 324. Singulation of chip package 322 is performed at the joints 326 of the heat sink frame, cutting the W" shaped clip or frame 102.

[0027] Referring to FIG. 4A, a prior art frame clipping structure is shown. The structure 400 includes an electrically conductive clip 402, which may be copper (Cu) that con-

nects to a conductive contact **404**, which may also be copper. The conductive clip is connected by a solder bond **406**. Series resistance for electrical conductivity from the structure to contact point may be summed up as: resistance of the clip+resistance of the clip solder contact+resistance of the solder+resistance of solder lead contact+resistance of contact lead.

[0028] Referring to FIG. 4B is an example integrated frame clipping structure 408 according to an embodiment. An integrated conductive clip 410 is part of the "W" shaped clip or frame. The integrated clip and the "W" shaped clip or frame may be made of copper or similarly conductive material. In contrast to the prior art structure of FIG. 4A, contact points and solders are eliminated in the example embodiment. In the present embodiment, the resistance for electrical conductivity from the structure 408 is simply the resistance of the clip lead. This provides significant improvement in conductivity and in addition, thermal/heat dispersion is also improved in the structure of FIG. 4B, especially when material such as copper is used where copper's thermal conductivity is about 398 W/mK and solder is about 30 W/mK.

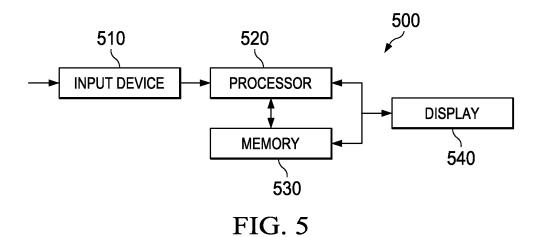

[0029] Referring to FIG. 5, an example of system 500 is illustrated according some embodiment. System 500 can be any system configured to use semiconductor chips packages according to an embodiment. System 500 can be an individual system unit such as a computing device, mobile phone, electronic control device, or any other electronic device including various processing components using semiconductor chip packages or system 500 can a be an integrated system-on-a-chip (SoC) on a single semiconductor chip package including various different components illustrated in FIG. 5 and others not shown as necessary to perform functions necessary for a given application.

[0030] System 500 includes an input device 510. Input device 510 can be any processing unit configured to receive data input including but not limited to an analogue-to-digital converter, baseband processing chip, transceiver for a mobile device, keyboard, or the like various other means for receiving input signals. The processor 520 can be any general purpose or specific application processing unit configured to process signals and data. Memory 530 can be any memory known in the art to store data and programs for the system 500. Display 540 can be configured to display data, video, graphics and similar other depictions. As described hereinabove, all or some of the components of system 500 can be integrated into a SoC for example, the processor can be an integrated chipset including memory, input device, and other processing components or the like or there can be more than one processor performing various functions. The processor 520 itself can be a combination of processors and other auxiliary components necessary for the processor to perform desired functions. Further, the memory 530 can be integrated into the processor as internal memory or can be an independent memory unit configured to interact with one or more processors.

[0031] The foregoing outlines features of several embodiments so that those of ordinary skill in the art may better understand various aspects of the present disclosure. Those of ordinary skill in the art should appreciate that they may readily use the present disclosure as a basis for designing or modifying other processes and structures for carrying out the same purposes and/or achieving the same advantages of various embodiments introduced herein. Those of ordinary

skill in the art should also realize that such equivalent constructions do not depart from the spirit and scope of the present disclosure, and that they may make various changes, substitutions, and alterations herein without departing from the spirit and scope of the present disclosure.

[0032] Although the subject matter has been described in language specific to structural features or methodological acts, it is to be understood that the subject matter of the appended claims is not necessarily limited to the specific features or acts described above. Rather, the specific features and acts described above are disclosed as example forms of implementing at least some of the claims. Various operations of embodiments are provided herein. The order in which some or all of the operations are described should not be construed to imply that these operations are necessarily order dependent. Alternative ordering will be appreciated having the benefit of this description. Further, it will be understood that not all operations are necessarily present in each embodiment provided herein. Also, it will be understood that not all operations are necessary in some embodiments.

[0033] Moreover, "exemplary" is used herein to mean serving as an example, instance, illustration, etc., and not necessarily as advantageous. Also, although the disclosure has been shown and described with respect to one or more implementations, equivalent alterations and modifications will occur to others of ordinary skill in the art based upon a reading and understanding of this specification and the annexed drawings. The disclosure comprises all such modifications and alterations and is limited only by the scope of the following claims. In particular regard to the various functions performed by the above described components (e.g., elements, resources, etc.), the terms used to describe such components are intended to correspond, unless otherwise indicated, to any component which performs the specified function of the described component (e.g., that is functionally equivalent), even though not structurally equivalent to the disclosed structure. In addition, while a particular feature of the disclosure may have been disclosed with respect to only one of several implementations, such feature may be combined with one or more other features of the other implementations as may be desired and advantageous for any given or particular application.

1. A method for forming a dual sided chip package comprising:

superimposing a frame to one or more dies;

bonding the frame to the one or more dies;

molding the frame to one or more dies with an upside mold die and a downside mold die; and

singulating the frame, wherein a surface mount area of the frame is larger than surface mount area of the one or more die, and the singulating exposes heatsink surfaces of the frame.

2. The method of claim 1, wherein the frame is configured as "W" shaped frame.

- 3. The method of claim 1, wherein the frame is electrically conductive.

- **4**. The method of claim **1**, wherein the frame is further configured as contact leads for the dual sided chip package.

- 5. The method of claim 1, wherein the frame is configured to dissipate heat.

- **6**. The method of claim **1**, the one or more dies are MOSFET components.

- 7. The method of claim 6, wherein the frame is configured as source, gate and drain contacts for the MOSFET components.

- 8. The method of claim 1, wherein the frame is configured in corrugated shape.

- 9. A semiconductor chip package comprising:

- one or more dies; and

- a heatsink frame bonded to the one or more dies, wherein the heatsink frame has a surface mount area larger than surface mount area of the one or more dies, and wherein the heatsink frame is a "W" shaped frame.

- 10. The semiconductor chip package of claim 9, wherein the one or more dies are MOSFETs.

- 11. (canceled)

- 12. The semiconductor chip package of claim 9, wherein the semiconductor chip package is dual sided and the "W" shaped frame provides dual sided heat dissipation.

- 13. The semiconductor chip package of claim 9, wherein the frame is electrically conductive.

- 14. The semiconductor chip package of claim 9, wherein the frame is configured in corrugated shape.

- 15. A system comprising:

- a processor;

- a memory coupled to the processor; and

- a display coupled to the processor, wherein at least one of the processor and the memory is configured as a semiconductor chip package comprising,

- one or more dies; and

- a "W" shaped frame bonded to the one or more dies, wherein the "W" shaped frame has a surface mount area greater than surface mount area of the one or more dies and configure to provide

- dual sided heat dissipation for the chip package, and electrical conductivity for the one or more dies.

- 16. The system of claim 15, wherein the semiconductor chip package includes a top side and a bottom side.

- 17. The system of claim 15, wherein the "W" shaped frame is electrically conductive and configured to provide connection from the one or more dies.

- **18**. The system of claim **15**, wherein the one or more dies are MOSFETs.

- 19. (canceled)

- 20. The system of claim 15, wherein the semiconductor chip package is dual sided and the "W" shaped frame is configured to dissipate heat for the semiconductor package.

\* \* \* \* \*