(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

|             |                   |             |                 |

|-------------|-------------------|-------------|-----------------|

| (21) 출원번호   | 10-2000-7003789   | (65) 공개번호   | 10-2001-0031003 |

| (22) 출원일자   | 2000년04월07일       | (43) 공개일자   | 2001년04월16일     |

| 변역문 제출일자    | 2000년04월07일       |             |                 |

| (86) 국제출원번호 | PCT/US1998/021160 | (87) 국제공개번호 | WO 1999/18617   |

| 국제출원일자      | 1998년10월06일       | 국제공개일자      | 1999년04월15일     |

AP ARIPO특허 : 케냐, 레소토, 말라위, 수단, 스와질랜드, 우간다, 짐바브웨, 가나, 감비아,

EA 유라시아특허 : 아르메니아, 아제르바이잔, 벨라루스, 키르키즈스탄, 카자흐스탄, 몰도바, 러시아, 타지키스탄, 투르크맨,

EP 유럽특허 : 오스트리아, 벨기에, 스위스, 독일, 덴마크, 스페인, 프랑스, 영국, 그리스, 아일랜드, 이탈리아, 룩셈부르크, 모나코, 네덜란드, 포르투칼, 스웨덴, 핀란드, 사이프러스,

OA OAPI특허 : 부르키나파소, 베닌, 중앙아프리카, 콩고, 코트디브와르, 카메룬, 가봉, 기니, 말리, 모리타니, 니제르, 세네갈, 차드, 토고,

(30) 웃선권주장 08/944.547 1997년10월07일 미국(US)

(73) 특허권자 크리 인코포레이티드

미국 노쓰 캐롤라이나 27703-8475 더럼 실리콘 드라이브 4600

(72) 발명자 에드몬드존아담

미합중국27511노스캐롤라이나주캐리더블유.줄스번웨이206

콩휴아-슈앙

미합중국27606노스캐롤라이나주랄리백스힐드라이브10840

도버스파크캐서린마리

미합중국27513노스캐롤라이나주케리그랜드하모니웨이1822

레오나드미셀터너

미합중국27513노스캐롤라이나주캐리트래피스런드라이브321

(74) 대리인 유미특허법인

송만호

심사관 : 최광섭

(54) 도전성 버퍼 충간 구조를 갖는 실리콘 카바이드 기판 상의 3족 질화물 광학 소자

요약

3족 질화물 액티브층을 갖는 광전 소자가 실리콘 카바이드 기판; 3족 질화물 액티브층을 갖는 광전 다이오드; 상기 실리콘 카바이드 기판과 상기 광전 다이오드 사이에 갈륨 질화물과 인듐 갈륨 질화물로 이루어지는 군으로부터 선택된 베퍼 구조; 및 상기 베퍼 기판의 결정 구조내에 미리 정해진 복수개의 응력 제거 영역을 포함하여, 상기 베퍼 구조내에 발생하는 크랙 킹을 야기하는 응력이 상기 베퍼 영역에서라기보다 오히려 상기 미리 정해진 응력 제거 영역에서 발생하도록 하는 응력 흡수 구조를 포함하는 것이 기재된다.

## 대표도

도 7

## 색인어

광학소자, 광전소자, 다이오드, 3족질화물

명세서

기술분야

본 발명은 넓은 밴드 갭(band gap) 물질의 광학 소자(photonics device)에 관한 것으로, 더욱 상세하게는 실리콘 카바이드(silicon carbide) 기판 상에 3족 질화물 액티브층(active layer)으로 형성된 광학 소자에 관한 것이다.

배경기술

다이아몬드, 실리콘 카바이드, 갈륨 질화물(gallium nitride)과 같은 넓은 밴드 갭을 갖는 반도체 물질은 상기 물질의 넓은 밴드 갭이 실리콘이나 갈륨 비화물(gallium arsenide)과 같은 다른 반도체 물질보다 (상대적으로 보다 높은 주파수와 보다 짧은 파장을 갖는) 고 에너지의 빛을 방출하는 특성을 제공하기 때문에 최근 많은 관심을 끌고 있다. 특히, 실리콘 카바이드, 갈륨 질화물, 및 소정의 다른 3족 질화물은 고 에너지 청색 부분을 포함하는 가시 스펙트럼(visible spectrum) 동안 가시 광선을 발생하기에 충분한 크기의 밴드 갭을 갖는다. 그래서, 상기 실리콘 카바이드, 갈륨 질화물, 및 소정의 3족 질화물은 청색과 녹색을 발광하는 반도체 레이저 및 발광 다이오드(LED)에 대한 원리를 제공한다.

상기한 물질 중, 갈륨 질화물은 직접 반도체(direct semiconductor)이기 때문에, 즉 가전자대(valence band)에서부터 전도대(conduction band)로의 전이(transition)가 전자의(for) 결정 운동량(crystal momentum) 변화를 요구하지 않기 때문에 특별히 주목받고 있다. 결과적으로, 상기 전이는 매우 효율적으로 빛을 발광한다. 반대로 실리콘 카바이드는 간접 반도체(indirect semiconductor), 즉 밴드 갭 전이 에너지 일부분은 광자(photon)로, 그리고 일부분은 떨기 에너지(vibrational energy)로 방출된다. 그래서, 갈륨 질화물은 소정의 작동 전압 및 작동 전류에 대해 실리콘 카바이드보다 보다 많은 양의 빛을 효율적으로 발광한다는 장점을 제공한다.

그러나 다른 반도체 물질을 갖는 것처럼, 작동 가능한 광학 소자를 형성하는 첫 번째 단계는 원하는 액티브층을 갖는 적당한 결정 구조를 구축하거나 그렇지 않으면 상기 결정 구조를 얻는 것이다. 그러나 3족 질화물 액티브층을 동작 가능하게 지지하는 반도체 물질의 구조적인 특성 차이 때문에, 특히 상기 물질의 결정 격자(crystal lattice)는 다소 제한된다.

현재, 발광 다이오드 광학 소자를 위한 상업적으로 이용 가능한 구조는 사파이어 기판 상에 갈륨 질화물 액티브층 또는 그와 관련된 3족 질화물 액티브층으로 형성된다. 사파이어( $\text{Al}_2\text{O}_3$ )는 3족 질화물에 대해 상대적으로 조밀한 격자 정합(lattice match)을 제공하며, 또한 전기적으로 절연 특성(insulating character)이 가장 많이 제한된다는 소정의 단점이 존재한다. 그래서, 3족 질화물 액티브층 및 베퍼층(즉 기판으로부터 액티브층으로 결정 구조 천이(transition)를 제공하는 중간 층(intermediate layer))이 사파이어 상에 구축될 경우, 상기 사파이어는 상기 광학 소자의 액티브 영역으로의 도전 경로(conductive pathway)로 사용될 수 없다. 이것은 사파이어 상에 설계되고 생산될 수 없는 소자의 유형을 제한하고, 특히 소자의 콘택(contact)이 기판, 베퍼, 및 액티브층 통과하는 직접 도전성 경로(direct conductive path)를 갖는 소자의 대향 표면들 상에 배치될 수 있고, 다른 콘택은 상기 소자의 반대쪽 상에 배치될 수 있는 "수직(vertical)" 소자의 형성을 제한한다.

따라서, 본 발명의 양수인(assignee)을 포함하여 3족 질화물 광학 소자용 기판이 될 수 있는 것으로 다른 물질의 사용에 관심의 초점이 맞춰진다. 실리콘 카바이드(SiC)는 도전성으로 될 수 있고, 적당하게 3족 질화물 액티브층에 대한 베퍼로 될 수 있는 격자 정합을 갖으며, 뛰어난 열 안정성(thermal stability) 및 기계적 안정성(mechanical stability)을 갖기 때문에 특히 매력적인 대체 물질(candidate)이다.

그렇지만, 실리콘 카바이드 결정 격자 구조는 실리콘 카바이드 기판 상에 적절한 3족 베퍼층을 위한 최적의 소정 대체 물질이 도전성이기보다는 오히려 절연성(insulating)을 갖는다. 그래서, 실리콘 카바이드 기판이 도전성으로 이루어질 수 있지만, 실리콘 카바이드 기판과 3족 액티브층 광학 소자 사이의 바람직한 소정의 베퍼층은 절연성이므로, 도전성 실리콘 카바이드 기판의 장점을 최소화시킨다.

예를 들면, 알루미늄 질화물(aluminum nitride; AlN)은 실리콘 카바이드 기판과 3족 액티브층, 특히 갈륨 질화물 액티브층 사이에 탁월한 베퍼를 제공한다. 그러나 알루미늄 질화물은 도전성이기보다는 오히려 절연성이다. 그러므로, 알루미늄 질화물 베퍼층을 갖는 구조는 도전성 실리콘 카바이드 기판을 3족 질화물 액티브층에 전기적으로 연결하도록 상기 알루미늄 질화물 베퍼를 바이패스(bypass)하는 짧은 콘택(shorting contact)을 요구한다. 상기에 기술된 것처럼 상기 짧은 콘택은 보다 유리한 소자의 설계를 방해한다.

대안적으로, 갈륨 질화물(GaN), 알루미늄 갈륨 질화물(AlGaN), 또는 갈륨 질화물과 알루미늄 갈륨 질화물의 혼합물(combination)과 같은 도전성 베퍼층의 물질은 상기 짧은 콘택을 제거할 수 있다. 차례로, 상기 짧은 콘택을 제거하는 것은 에피택셜층(epitaxial layer)의 두께를 감소시키고, 소자를 생산하기 위해 필요한 제조 단계 수를 줄이며, 전체 칩 크기를 감소시키고, 소자의 효율성을 향상시킨다. 따라서, 3족 질화물 소자가 고 성능을 갖으며 낮은 제조 원가로 생산될 수 있다.

그렇지만, 이러한 도전성 베퍼 물질이 상기와 같은 장점을 제공하더라도, 실리콘 카바이드와 상기 도전성 베퍼 물질의 결정 격자 정합 정도는 알루미늄 질화물과의 결정 격자 정합 정도보다 좋지 않다. 따라서, 갈륨 질화물, 알루미늄 갈륨 질화물, 또는 상기 것들의 혼합물로 이루어지는 에피택셜층이 실리콘 카바이드 기판 상에서 성장될 경우, 상기 에피택셜층은 발광 다이오드나 레이저 다이오드와 같은 광학 소자를 위해 필요한 후속의 에피층(epilayer)에 과도한 크랙킹(cracking)을 발생시키는 경향이 있다.

갈륨 질화물과 실리콘 카바이드 기판을 포함하는 소정 소자가 알려져 있다. 예를 들면, JP-A-6 326 416는 실리콘 카바이드 기판, 갈륨 질화물 베퍼층 및 도핑된 갈륨 알루미늄 인듐 질화물 액티브층을 사용하는 화합물 반도체 소자(element)를 개시한다. 그러나, 상기 소자는 갈륨 질화물의 유익한(favorable) 광학 특성을 충분히 사용할 수 없고, 갈륨 질화물 베퍼층은 크랙킹에 영향을 받는다. 유사하게, WO 96/24167은 갈륨 질화물을 포함할 수 있는 다층 베퍼에 의해 실리콘 카바이드 기판으로부터 분리된 갈륨 질화물 액티브층을 포함하는 발광 반도체 레이저를 개시한다.

상기 크랙킹 문제에 대한 다양한 해결책이 연구를 통해 제안되어 왔다. 예를 들면, WO 90/10950은 제1 기판(primary substrate) 상에 제2 기판(secondary substrate)을 성장시켜 부정합된 기판 상에 단결정 고체 소자(single crystal, solid state device)를 성장하기 위한 방법을 개시한다. 상기 제2 기판은 상기 제1 기판 상에서 메사(mesa)로 분할된 에피층을 성장시킨 후 어닐링(annealing)에 의해 얻어진다. 그러나 이 방법은 크랙킹을 줄이거나 제거하기보다는 오히려 비임계 영역(non-critical area)에서 크랙킹이 주로 발생하도록 하는 것이다.

EP-A-0 352 472는 격자-부정합 반도체 물질의 혜테로에피택시(heteroepitaxy)를 개시한다. 상기 EP-A-0 352 472에서 돌출 그리드(protruding grid)는 실리콘 기판 상에 배치된다. 그런 다음, GaAs와 같은 격자-부정화 반도체 물질은 노출된 실리콘과 돌출 그리드 모두에 증착된다. 이 방법 또한 크랙킹을 줄이거나 제거하기보다 오히려 주로 비임계 영역에서 크랙킹이 주로 발생하도록 하는 것이다.

그러므로, 알루미늄 질화물의 결정 격자 정합의 장점을 제공하며 동시에 갈륨 질화물이나 알루미늄 갈륨 질화물에 대한 도전성의 장점을 제공하고 절연성 사파이어 기판보다 오히려 도전성 실리콘 카바이드 기판과 함께 사용될 수 있는 베퍼 기판에 대한 필요가 존재한다.

### 발명의 상세한 설명

그러므로, 본 발명의 목적은 크랙킹, 및 물질과 층의 혼합을 방해하는 다른 문제를 방지하고 3족 질화물 액티브층, 도전성 실리콘 카바이드 기판, 및 도전성 베퍼층을 갖는 광학 소자 및 자신의 웨이퍼 전구체(precursor)를 형성하기 위한 것이다.

본 발명은 실리콘 카바이드 질화물, 3족 질화물 액티브층을 갖는 광전 다이오드(optoelectronic diode), 및 실리콘 카바이드 기판과 광전 다이오드 사이의 베퍼 구조를 포함하고, 상기 베퍼 구조는 도전성이고 적당한 결정 특성(crystalline property)을 제공하는 3족 질화물 액티브층을 갖는 광학 소자로 상기 목적을 달성한다.

본 발명의 하나의 특징으로, 상기 베퍼 구조는 갈륨 질화물 및 인듐 갈륨 질화물(InGaN)로 이루어지는 군(group)으로부터 선택되고, 상기 베퍼층의 결정 구조내에 미리 정해진 복수개의 응력 제거영역(stress relieving area)을 포함하는 응력 흡수 구조(stress absorbing structure)를 결합하므로, 베퍼내에서 발생하는 크랙킹을 야기하는 응력이 베퍼내에서라기보다 오히려 정해진 영역에서 발생한다.

본 발명의 다른 특징으로, 상기 베퍼층은 실리콘 카바이드 및 알루미늄 갈륨 질화물 베퍼 구조 사이에 헤테로배리어(heterobarrier)를 최소화하거나 제거하기 위해 실리콘 카바이드 기판의 표면 상에 갈륨 질화물 및 인듐 갈륨 질화물로 이루어지는 군으로부터 선택된 복수개의 이산 결정부(discrete crystal portion)을 포함한다.

본 발명의 상기 목적과 다른 목적, 및 장점과, 상기한 목적 및 장점을 달성하기 위한 방식은 다음의 상세한 설명 및 첨부된 도면을 참조하면 보다 명백해질 것이다.

### 도면의 간단한 설명

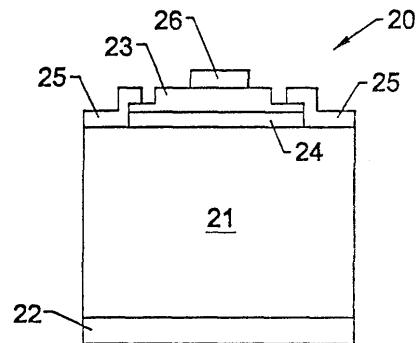

도 1은 짧은 링 콘택(ring contact)을 갖는 종래 다이오드의 단면도.

도 2는 본 발명으로 생산될 수 있는 수직 다이오드의 단면도.

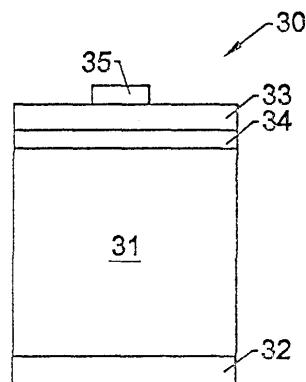

도 3은 본 발명에 따라 형성된 화소(pixel)의 개략적인 확대 도면.

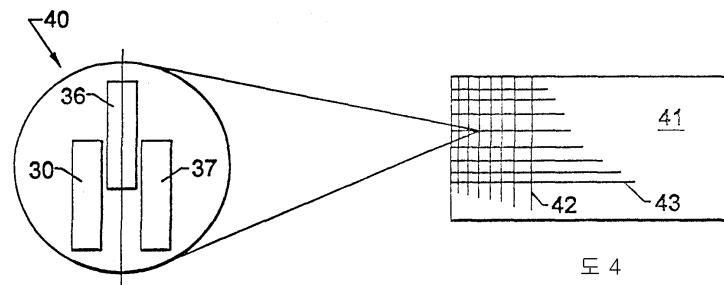

도 4는 본 발명에 따라 복수개의 화소를 포함하고 구조를 결합하는 표시 소자의 개략적인 도면.

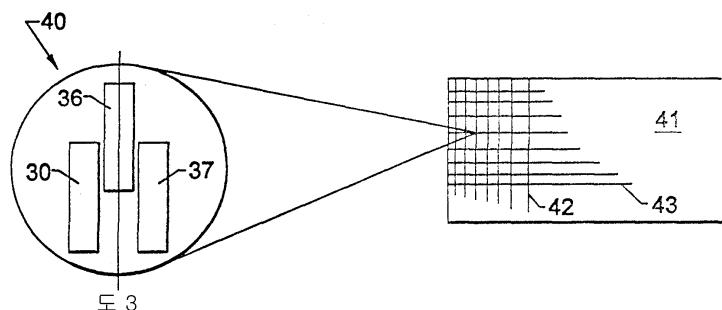

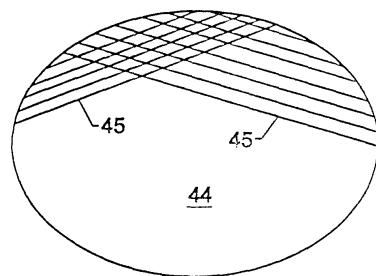

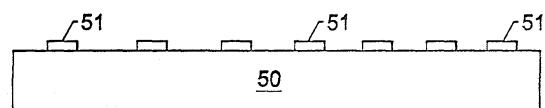

도 5는 본 발명에 따라 응력 제거 구조를 결합하는 실리콘 카바이드 웨이퍼의 개략적인 도면.

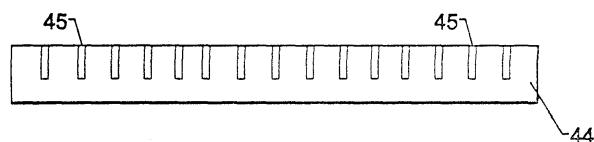

도 6은 도 5의 웨이퍼에 대한 단면도.

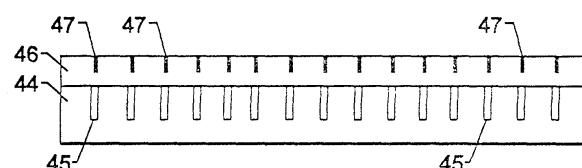

도 7은 도 5의 웨이퍼에 대한 단면도이고 상기 웨이퍼 상에서 성장한 베퍼층의 개략적으로 도시하는 도면.

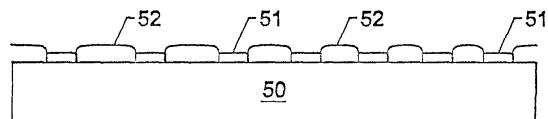

도 8은 본 발명의 제2 실시예를 결합하는 웨이퍼의 단면도.

도 9는 도 8과 동일한 단면도이지만 상기 웨이퍼 상에 부가적인 결정 성장을 도시하는 도면.

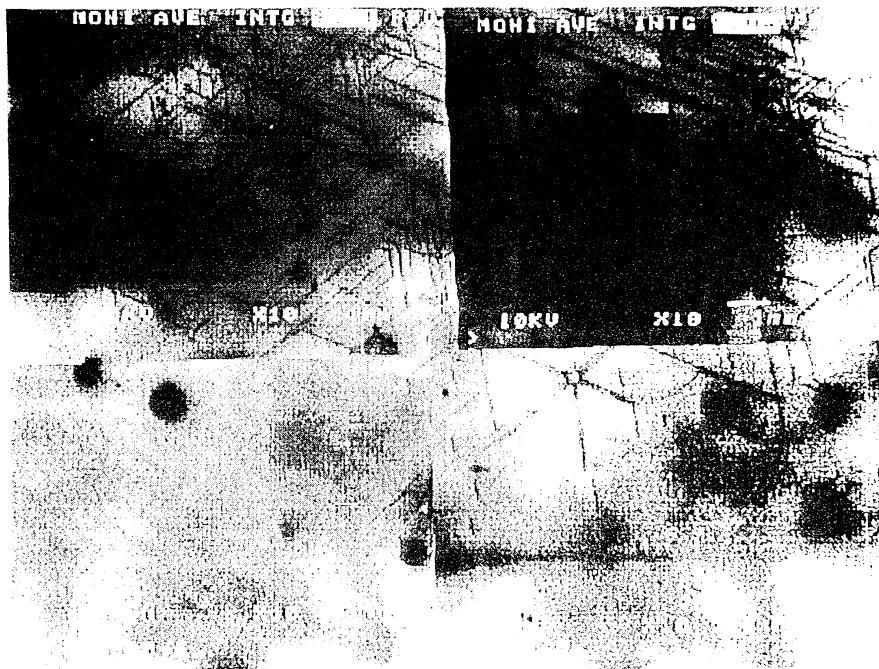

도 10은 본 발명을 결합하지 않은 에피층을 주사 전자 현미경(Scanning Electron Microscope; SEM)으로 10X 배율 확대한 사진을 도시한 도면.

도 11은 본 발명에 따른 에피층을 도시하는 10X SEM 사진을 도시한 도면.

도 12는 본 발명에 따른 에피층을 도시하는 다른 10X SEM 사진을 도시한 도면.

도 13은 도 12와 동일한 에피층에 대한 50X SEM 사진을 도시한 도면.

도 14는 본 발명에 따른 에피층에 대한 100X SEM 사진을 도시한 도면.

도 15는 본 발명을 결합하지 않은 다른 에피층을 도시하는 다른 100X SEM 사진을 도시한 도면.

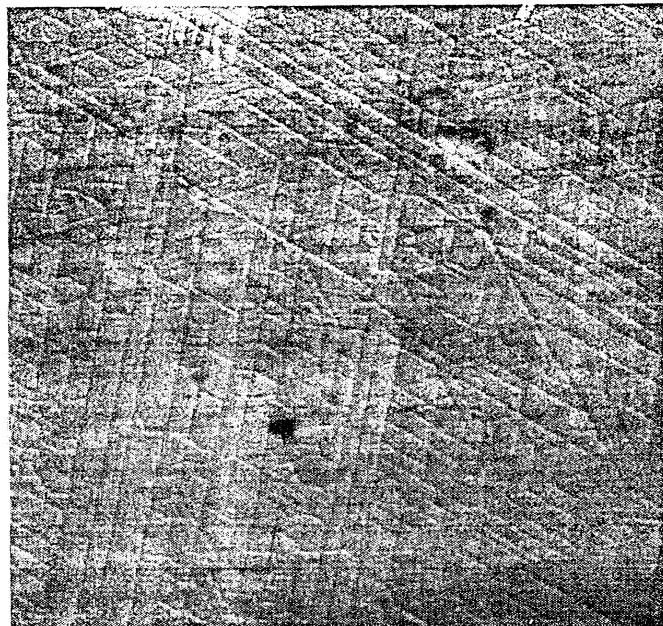

도 16은 본 발명의 제2 실시예에 대한 15,000X SEM 사진을 도시한 도면.

도 17은 본 발명의 상기 제2 실시예에 대한 50,000X SEM 사진을 도시한 도면.

### 실시예

도 1은 도면 부호 20으로 넓게 지정되는 종래 소자의 단면도를 도시한다. 도 1에 예시된 바와 같이, 상기 소자(20)는 실리콘 카바이드 기판(21), 기판(21) "뒷면(back)"의 콘택(22), 3쪽 질화물 액티브층(23), 도전성이라기보다는 오히려 절연성인 베퍼층(24), 상기 도전성 실리콘 베퍼(21)와 상기 액티브층(23) 사이에 전기적인 콘택을 제공하기 위한 짧은 콘택(25), 및 회로를 완성하고 작동시 상기 소자를 통해 전류가 흐를 수 있도록 하는 상부 콘택(26)을 포함한다.

도 2는 본 발명이 보다 단순한(compact) 소자를 제공하는 방식을 도시한다. 도 2에서, 상기 소자는 도면 부호 30으로 넓게 지정되고, 상부 콘택(35)과 함께 도전성 실리콘 카바이드 기판(31), 백 콘택(back contact; 32), 액티브층(33), 및 도전성 베퍼 구조(34)를 포함한다. 그러므로, 본 발명은 도 1에 도시된 소자의 짧은 콘택(전형적으로 짧은 랭 콘택)(25)을 삭제한다. 결과적으로 소자(30)는 제조가 보다 용이하고 작동 효율이 보다 효율적이다. 본 명세서에 기재된 것처럼 상기 액티브층(33)은 단일 p-n 접합(junction), 단일 또는 이중 p-n 혜테로접합(heterojunction), 또는 p-n 접합 퀸텀(quantum) 웰 구조(well structure)를 갖는 소자를 제시할 수 있다는 것이 이해될 것이다. 상기 구조는 미합중국 특허 번호 제5,393,993호 및 동 특허 번호 제5,592,501호에 기재되어 있고, 본 발명을 보다 잘 예시하도록 하는 것 이외에 본 명세서에서는 상세하게 기술하지 않는다.

도 3은 본 발명에 따른 소자(30)가 상이한 발광 파장(emitting wavelength)을 갖는 유사한 소자, 특히 표시 소자(41)의 복수개의 화소 중 차례로 하나가 될 수 있는 도면 부호 40으로 넓게 지정된 3색 화소 부분처럼, 적색 발광 다이오드(36) 및 녹색 발광 다이오드(37)와 결합될 수 있다는 것을 도시한다. 도 4에 개략적으로 도시된 수직 선(42)과 수평 선(43)은 발광 다이오드를 결합하는 표시 소자에 전형적으로 사용된 화소의 열(column)과 행(row)을 도시한다.

첫 번째 특징으로, 본 발명은 실리콘 카바이드 기판(31), 3쪽 질화물 액티브층(33)을 갖는 광학 다이오드, 상기 실리콘 카바이드 기판(31)과 다이오드(33) 사이에 갈륨 질화물 및 인듐 갈륨 질화물로 이루어지는 군으로부터 선택된 베퍼 구조(34)를 포함하는 3쪽 질화물 액티브층을 갖는 광학 소자이다. 특히, 상기 베퍼 구조(34)는 자신의 결정 구조내의 미리 정해진 복수개의 응력 제거 영역으로 만들어지는 응력 흡수 구조를 포함하므로 상기 베퍼 구조에 발생하는 클랙킹을 야기한 응력은 상기 베퍼 구조에서 보다 미리 정해진 영역에서 발생한다.

도 5는 복수개의 소자 전구체를 결합하고 본 발명의 응력 흡수 구조를 결합하는 웨이퍼의 개략적인 도면이다. 도 5는 홈(groove; 45)의 그리드 패턴이 인화된(superimposed) 도면 부호 44로 넓게 지정된 웨이퍼를 예시한다. 도 6은 상기 동일한 웨이퍼(44)와 홈(45)에 대한 단면도를 도시한다. 후속의 에피택설층(46)(도 7)이 홈(45)을 갖는 웨이퍼(44) 상에서 성장될 경우, 상기 에피택설층(46)의 표면은 자신의 위치가 상기 웨이퍼(44)에 패턴을 형성하는 홈(45)의 위치를 나타내는 일련의 불연속부(discontinuity)를 갖기 쉽다. 상기 불연속부(47)는 베퍼층(46)의 결정 격자 구조가 실리콘 카바이드 웨이퍼(44) 상에 성장할 때 응력이 저절로 제거되는(relieve) 영역을 형성한다. 결과적으로, 격자 부정합(lattice mismatch)(또는 다른 요인)으로부터 발생하는 상기 응력이 임의의(random) 위치에서 발생하기보다는 의도된 위치에서 발생하므로, 소자가 심각한 응력 크랙킹의 위험없이 잔여 영역(remaining area)에 형성될 수 있도록 한다.

상기에 기재되고 도 5에 예시된 바와 같이, 하나의 바람직한 실시예에서 미리 정해진 응력 제거 영역 패턴은 그리드를 포함하고, 상기 그리드는 각각의 소자를 한정하는 소정 원하는 크기나 필요한 크기로 바람직하게 형성될 수 있다. 예를 들면, 상기 각각의 소자가 발광 다이오드일 경우, 바람직한 그리드 패턴은 일면(side) 당 약 250 미크론(micron)의 정사각형(square)으로 정해진다. 대안적으로, 레이저 다이오드와 같은 다른 소자용으로 상기 그리드는 약  $250 \times 500$  미크론( $\mu$ )의 정사각형으로 정해질 수 있다.

도 10은 약간 삼각형이거나 육각형 패턴처럼 보이는 크랙킹이 에피택설층을 훼손할 수 있고 광학 소자용으로 상기 에피택설층을 불완전하고 쓸모없게 만드는 정도를 도시하는 10X 배율(실제 크기의 10배)로 얻어진 SEM 사진이다.

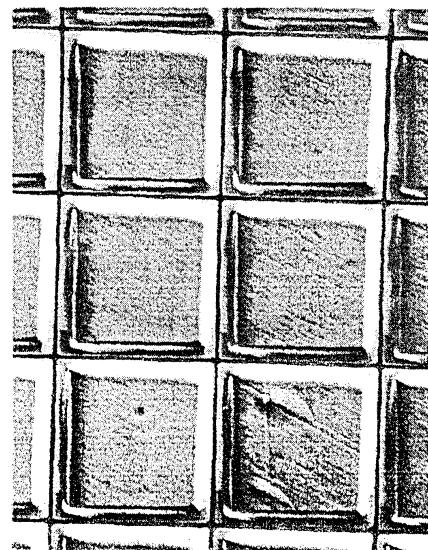

도 11은 다른 10X SEM 사진이고 상기 에피택셜층에 형성된 홈의 그리드 패턴을 예시한다. 도 10과 비교할 때, 도 11에 도시된 표면은 상대적으로 크랙킹 결함이 덜하다(free).

도 12는 다른 10X SEM이고, 유사한 그리드 패턴을 예시한다. 도 11과 같이, 도 10에 예시된 크랙보다 상당히 적게 발생한다.

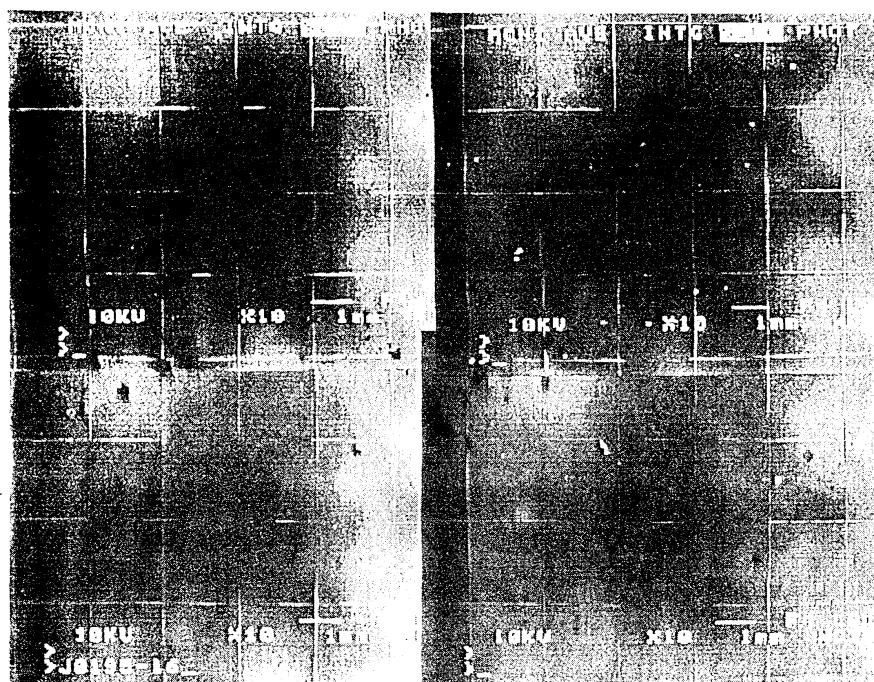

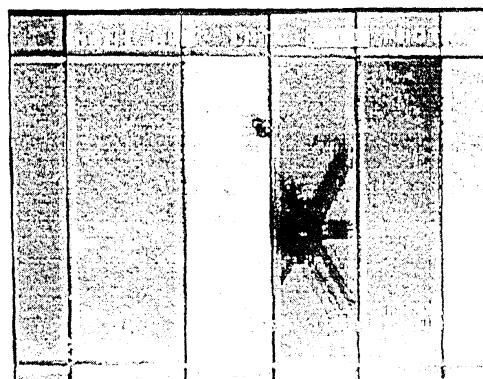

도 13은 본 발명의 장점을 특별히 예시하는 다른 50X SEM 사진이다. 도 13에서, 그리드 섹션 중 하나가 약간 "X"형상의 커다란 결함을 포함한다. 그러나, 상기 결함은 그리드 선에서 끝나서, 웨이퍼의 다수개(multi)의 소자부가 아니라 단지 한 소자(또는 소자 전구체)만을 못쓰게 만든다.

도 14는 결함이 표면을 통과하여 좀더 전파하기 보다 s,s 그리드 선에서 끝나는 (사진의 오른쪽 하부의) 결함이 있는 한 그리드부를 유사하게 예시하는 100X SEM 사진이다.

도 15는 본 발명의 실시예중 소정의 것을 결합하지 않은 표면을 다시 예시하는 100X SEM 사진이다. 도 10과 같이, 기하학적인 패턴(geometric pattern)의 결함이 아주 선명하다(evident).

다른 실시예에서, 응력 흡수 구조는 도 8 및 도 9에 가장 잘 예시되는 미리 정해진 소형 메사 구조(mesa structure) 패턴을 포함할 수 있다. 도 8 및 도 9에서 실리콘 카바이드 기판은 도면 부호 50으로 지정되고, 소형 메사 구조는 도면 부호 51로 지정된다. 메사 구조(51)는 선택된 베퍼 물질의 성장이 잘 이루어지지 않은(disfavored) 물질로 형성된다. 갈륨 질화물 또는 인듐 갈륨 질화물 베퍼 구조용으로, 바람직한 물질은 실리콘 디옥사이드(silicon dioxide), 실리콘 질화물, 및 알루미늄 산화물(aluminum oxide)로 이루어지는 군으로부터 선택된다.

도 9는 도 8과 유사한 구조를 예시하지만, 실리콘 카바이드 기판(50) 상에 에피택셜층으로서 성장된 베퍼 물질을 갖는다. 에피택셜층 부위는 도면 부호 52로 예시된다. 도 9에 예시된 바와 같이, 베퍼 물질의 성장이 메사(51) 상에서는 잘 이루어지지 않기 때문에, 에피택셜층(52)은 상기 에피택셜층(52) 사이에 미리 정해진 응력 제거 불연속부를 다시 드러내는 (exhibit) 패턴을 형성한다. 상기한 실시예에서처럼, 메사 사이의 영역은 이미 기술된 것처럼 LED용으로는 약 250 미크론의 치수를 갖고, 레이저 다이오드용으로는 약 250×500 $\mu$  치수를 갖는 각각의 소자와 거의 동일한 크기가 되도록 만들어질 수 있다. 그러나 그리드나 메사 구조 패턴의 상기 특정 크기는 본 발명을 제한하기보다는 오히려 예시적인 것이라는 것이 이해될 것이다.

본 발명에 따른 웨이퍼 구조가 특히 광전 소자용으로 적합(advantageous)하지만 상기 웨이퍼 구조는 상기에 한정되지 않으며 뛰어난 구조 특성은 웨이퍼 상에 형성된 다른 소자용으로도 적합하다는 것이 이해될 것이다.

종래 기술 부분에서 기술되고 도 1에서 도면 부호 23으로 도 2에서 도면 부호 33으로 통상적으로 예시된 것처럼, 베퍼층 상에 형성된 광전 소자는 일반적으로 단일층(single layer)이 아니고, 오히려, p-n 호모접합(homojunction), p-n 혼태로 접합, p-n 단일 및 이중 혼태로 접합, 및 p-n 접합 쿼텀 웨일 구조로 이루어지는 군으로부터 선택된 다층 다이오드(multi-layer diode)이다.

바람직한 실시예에서, 실리콘 카바이드 기판은 3C, 4H, 6H, 및 15R 폴리형(polytype)으로 이루어지는 군으로부터 선택된 폴리형이다. 가장 바람직한 실시예에서, 다이오드의 3족 질화물 액티브층은 갈륨 질화물 또는 인듐 갈륨 질화물을 포함한다.

도 16 내지 도 18은 본 발명의 다른 실시예를 예시한다. 일반적으로, 전체 구조는 개략적인 형태로, 도 2에 의해 다시 예시되고, 실리콘 카바이드 기판(31), 광학 다이오드(33), 및 베퍼층(34)을 포함한다. 그러나, 이 실시예에서, 상기 베퍼층은 갈륨 질화물 또는 인듐 갈륨 질화물이기보다는 알루미늄 갈륨 질화물이다. 이 실시예에는 도 16 내지 도 18에서 흰색 도트로 나타나는 복수개의 이산 결정부(discrete crystal portion)를 포함한다. 상기 이산 결정부는 갈륨 질화물 및 인듐 갈륨 질화물의 군으로부터 선택되고 실리콘 카바이드 기판(31)과 알루미늄 갈륨 질화물 베퍼 구조(34) 사이에 혼태로 배리어를 최소화하거나 제거하기 위해 실리콘 카바이드 기판의 표면 상에 형성된다.

바람직한 실시예에서, 상기 이산 결정부는 혼태로 배리어를 최소화하거나 제거하기에 충분한 양(amount)으로 존재하지만, 실리콘 카바이드 기판(31) 상에 구축된 소정의 최종 다이오드 소자의 기능에 불리하게 영향을 미치거나 상기 기능을 파괴하는 양보다는 적게 존재한다. 도 16 내지 도 18의 사진에 예시된 바와 같이, 이산 결정부는 평방(square) 미크론 당 약 40 내지 60 개의 양이 존재한다.

또한, 상기 이산 결정부는 헤테로배리어를 최소화하거나 제거하기에 충분한 크기가 바람직하지만, 실리콘 카바이드 기판(31) 상에 구축된 소정의 최종 다이오드 소자의 기능에 불리하게 영향을 미치거나 상기 기능을 파괴하는 크기보다는 작다. 바람직한 실시예에서, 상기 이산 결정부의 직경은 0.01 내지 0.1 미크론이다.

상기 실시예에서처럼, 베퍼 구조 상에 형성된 광전 소자(33)는 발광 다이오드나 레이저 다이오드를 포함할 수 있고 최종 벨광 다이오드는 차례로 표시 소자내에 결합될 수 있는 화소내에 결합될 수 있다.

바람직한 실시예에서, 알루미늄 갈륨 질화물 베퍼층은 약 10% 내지 15%의 알루미늄 원자 구성비(atomic fraction)를 갖는다.

다른 특징으로, 본 발명은 도전성 베퍼 구조를 갖는 실리콘 카바이드 기판 상에 3족 질화물 광전 소자를 형성하는 방법을 포함한다. 상기 방법의 특징으로, 본 발명은 결정 성장용으로 준비된 실리콘 기판의 표면 상에 구조 패턴을 형성하는 단계; 상기 실리콘 카바이드 기판의 패턴 형성된 표면 상에 갈륨 질화물과 인듐 갈륨 질화물로 이루어지는 군으로부터 선택된 베퍼층을 형성하는 단계; 및 상기 베퍼층 상에 3족 질화물 액티브층을 갖는 광전 소자를 형성하는 단계를 포함하고, 상기 베퍼층이 형상(feature)을 드러내면 실리콘 카바이드 기판의 표면에 개구부 패턴을 형성한다.

구조적인 특징에 대해 기술된 것처럼, 상기 구조 패턴 형성 단계는 실리콘 카바이드 기판의 표면에 개구부 패턴을 형성하는 단계 또는 실리콘 카바이드 기판의 표면 상에 메사 구조 패턴을 형성하는 단계를 포함할 수 있다.

상기 패턴이 개구부를 형성할 경우, 개구부 형성 단계는 반응성 이온 에칭(reactive ion etching)이나 마스킹(masking) 단계 및 에칭 단계와 같은 기술을 포함할 수 있다. 상기 단계 각각은 실리콘 카바이드를 위한 것이라는 것이 상대적으로 잘 이해될 것이고, 예를 들면, 실리콘 카바이드를 위한 예시적인 드라이 에칭 과정을 기재한 미합중국 특허 번호 제4,865,685호 및 동 특허 번호 제4,981,551호에만 기재되어 있다.

메사 구조가 결합될 경우, 상기 메사 구조는 실리콘 디옥사이드, 실리콘 질화물, 및 알루미늄 산화물로 이루어지는 군으로부터 바람직하게 선택된다. 구조적인 환경(environment)에서처럼, 3족 액티브층을 갖는 광전 소자는 갈륨 질화물이나 인듐 갈륨 질화물로 바람직하게 형성된다.

구조적인 실시예에서처럼, 본 발명의 방법은 발광 다이오드나 레이저 다이오드를 형성하는 단계를 포함할 수 있고, 발광 다이오드가 형성될 경우, 상기 방법은 화소내에 LED를 결합하고 표시 소자내에 상기 화소를 결합하는 단계를 추가로 포함할 수 있다.

대안적인 방법 특징으로서, 본 발명의 구조 중 베퍼 구조는 실리콘 카바이드 표면 상에 갈륨 질화물과 인듐 갈륨 질화물로 이루어지는 군으로부터 선택된 복수개의 이산 결정부를 형성하여 미리 준비해 놓은 실리콘 카바이드 기판 상에 알루미늄 갈륨 질화물로 형성된다. 그 후, 3족 질화물 액티브층을 갖는 광전 소자가 상기 베퍼층 상에 형성된다.

본 발명의 구조적인 특징에서 기술한 것처럼, 상기 방법은 헤�테로배리어를 최소화하거나 제거하기에 충분한 크기와 양을 갖지만 실리콘 카바이드 기판 상에 구축된 소정의 최종 다이오드 소자의 기능에 불리하게 영향을 미치거나 상기 기능을 파괴하는 양보다는 적게 이산 결정부를 형성하는 단계를 포함한다. 특히 본 발명은 일반적으로 예상된 정전기의 방전 정도를 견딜 수 있는 튼튼한 구조를 제공한다.

두 번째 방법 특징으로, 최종 소자는 발광 다이오드로 형성될 수 있으므로 상기 방법은 화소내에 LED를 결합하고 표시 소자내에 상기 화소를 결합하는 단계를 추가로 포함할 수 있다. 상기 방법은 LED보다 오히려 레이저 발광 다이오드를 대안적으로 형성하는 단계를 포함할 수 있다.

본 발명의 다른 특징에서처럼, 알루미늄 갈륨 질화막 베퍼층이 사용될 경우, 약 10% 내지 15%의 알루미늄 원자 구성비(atomic fraction)를 바람직하게 갖는다.

### 예시예

도전성 베퍼 LED와 레이저 다이오드를 형성하기 위한 현재 공정에서, GaN 도트가 먼저 증착된다. GaN 도트의 목적은 SiC 기판과 Si 도핑된 AlGaN 베퍼층 사이에 배리어를 감소시키기 위한 것이다. 이것은 구조에서 다른 에피택셜 층을 위해 사용되는 온도보다 상대적으로 낮은 온도에서 행해진다. 상기 도트의 크기와 밀도(density)는 도 16 및 도 17에 도시된다.

상대적으로 작은 도트를 유지하여 정전기 방전이 불리하게 영향을 미치지 않도록 하는 것이 중요하다. GaN 도트는 약 6초간 증착된 후 약 15초 동안 Si 도핑된  $\text{Al}_{.10}\text{Ga}_{.90}$ 으로 "캡(cap)"으로 덮여진다. 상기한 캡의 목적은 가열(heating)할 때 GaN 도트의 해리(dissociation)를 방지하기 위한 것이다. 이러한 물질 구조(material system)에서, 소정의 Al 내지 GaN 즉,  $\text{Al}_{(1-x)}\text{Ga}_{(x)}\text{N}$ 을 첨가하는 것은  $\text{AlGaN}$ 이  $\text{NH}_3/\text{H}_2$  분위기(atmosphere)에서 GaN보다 더 안정적이기 때문에 물질의 해리율(dissociation rate)을 감소시킨다. 그런 다음, 상기 캡핑 동작(capping) 후에, 온도는 베퍼층 온도로 서서히(ramped) 상승한다. 온도는 베퍼층 성장을 개시하기 전에 서서히 증가(ramp)한 후 2분 동안 안정화되도록 한다.

특별한 진행(specific run)으로, SiC 웨이퍼는  $\text{NH}_3$  및  $\text{HH}_2$ 의 분위기에서 13 SLM 및 15 SLM에서 각각 가열된다. 상기 유체는 GaN 도트, AlGaN 캡(cap), 및 후속 베퍼층의 성장 동안 일정하게 유지된다. 온도는 GaN 도트 온도가 약 960°C에 도달할 때까지 10분 이상 서서히 상승한다. 시스템의 온도를 거의 5분 동안 안정화시킨 후, 상기 도트는 약 6초 동안 트리메틸 갈륨(trimethyl gallium)(TMG; -5°C, 600 토르(torr))의 유체 10cc 내지 15cc에 의해 증착된다. 또한, 도트가 확실히 도전성을 갖도록 하기 위해,  $\text{SiH}_4$ 는 TMG 유체와 혼합된다(added).  $\text{SiH}_4$ 의 양은 약  $1 \times 10^{18} \text{ cm}^{-3}$ 의 캐리어 농도(concentration)를 갖는 별크 GaN층을 성장시키는 것에 의해 정해진다. 다음에 GaN 도트의 증착하자마자, TMG 및  $\text{SiH}_4$ 는 계속 흘러가지만, 트리메틸 알루미늄(TMA, 92cc, 25°C, 600 타르)과 혼합된다. 이것은 약 10% 내지 11%의 AlGaN의 "캡"이 된다. 상기 캡의 성장 시간은 15초이다. 그런 다음, 상기 유체(TMGA, TMA, 및  $\text{SiH}_4$ )의 흐름은 끝나고 온도는 전형적으로 1060°C 전후인 베퍼 온도로 서서히 상승된다. 상기 온도 상승은 1분이고 2분 동안 온도가 안정화된다. 그런 다음 베퍼층이 성장된다. 전형적인 성장 조건은 18cc TMG/110cc TMA/.087cc $\text{SiH}_4$ 이다. 베퍼층은 거의 11% 내지 12%의 A1GaN으로 이루어지고 전형적으로 약 1600Å 내지 2700Å의 두께를 갖는다.

도면 및 명세서에, 본 발명의 대표적인 실시예가 기재되고, 특정 용어가 사용되었지만 상기 용어는 단지 일반적이며 기술적인(descriptive) 의미로 사용되고 특허청구범위에 기술되는 본 발명의 범위를 제한하기 위한 목적은 아니다.

## (57) 청구의 범위

### 청구항 1.

삭제

### 청구항 2.

삭제

### 청구항 3.

삭제

### 청구항 4.

삭제

### 청구항 5.

삭제

### 청구항 6.

삭제

### 청구항 7.

삭제

### 청구항 8.

삭제

### 청구항 9.

삭제

청구항 10.

삭제

청구항 11.

삭제

청구항 12.

삭제

청구항 13.

삭제

청구항 14.

삭제

청구항 15.

삭제

청구항 16.

삭제

청구항 17.

삭제

청구항 18.

삭제

청구항 19.

삭제

청구항 20.

삭제

청구항 21.

삭제

청구항 22.

삭제

청구항 23.

삭제

청구항 24.

삭제

청구항 25.

삭제

청구항 26.

삭제

### 청구항 27.

3족 질화물 소자용 웨이퍼 전구체에 있어서,

표면에 미리 정해진 홈(groove) 패턴을 포함하는 실리콘 카바이드 기판 웨이퍼;

갈륨 질화물 및 인듐 갈륨 질화물로 이루어지는 군으로부터 선택되고, 상기 기판 상에 형성되는 베퍼층; 및

상기 베퍼층의 결정 구조내에 미리 정해진 복수개의 응력 제거 영역을 포함하여, 상기 베퍼 구조내에 발생하는 크랙킹을 야기하는 응력이 상기 베퍼 영역에서라기보다 오히려 상기 미리 정해진 응력 제거 영역에서 발생하도록 하는 응력 흡수 구조

를 포함하는 웨이퍼 전구체.

### 청구항 28.

제27항에 있어서,

상기 미리 정해진 패턴이 일면 당 250 미크론(micron)의 정사각형(square)을 한정하는 그리드(grid), 및  $250 \times 500$  미크론의 직사각형을 한정하는 그리드로 이루어지는 그룹으로부터 선택되는 웨이퍼 전구체.

### 청구항 29.

3족 질화물 액티브층을 갖는 광전 다이오드를 포함하는 제28항의 웨이퍼 전구체로부터 형성된 광전 소자.

### 청구항 30.

제29항에 있어서,

상기 다이오드는 p-n 호모접합(homojunction), p-n 단일 및 이중 혜테로접합(heterojunction), 및 p-n 퀸텀 접합(quantum junction) 웰 구조(well structure)로 이루어지는 군으로부터 선택되고, 상기 실리콘 카바이드 기판은 3C, 4H, 6H, 및 15R 폴리형(polytype)으로 이루어지는 군으로부터 선택된 폴리형을 갖는 광전 소자.

### 청구항 31.

제29항에 있어서,

상기 3족 질화물 액티브층이 갈륨 질화물 및 인듐 갈륨 질화물로 이루어지는 군으로부터 선택되는 광전 소자.

### 청구항 32.

3족 질화물 소자용 웨이퍼 전구체에 있어서,

베퍼 물질의 성장에 대해 저항성을 갖는 물질로 형성된 미리 정해진 소형 응력 흡수 메사 구조 패턴과 자신의 노출 표면 상에 증착된 베퍼층을 포함하는 실리콘 카바이드 기판을 포함하는 웨이퍼 전구체.

### 청구항 33.

제32항에 있어서,

상기 벼피 물질의 성장에 대해 저항성을 갖는 상기 물질이 실리콘 디옥사이드( $\text{SiO}_2$ ), 실리콘 질화물, 및 알루미늄 산화물로 이루어지는 군으로부터 선택되는 웨이퍼 전구체.

### 청구항 34.

제32항에 있어서,

상기 벼피층이 갈륨 질화물 및 인듐 갈륨 질화물로 이루어지는 군으로부터 선택되는 웨이퍼 전구체.

### 청구항 35.

제32항의 웨이퍼 전구체로부터 형성되고 3족 질화물 액티브층을 갖는 광전 다이오드를 추가로 포함하는 광전 소자.

### 청구항 36.

제35항에 있어서,

상기 다이오드는 p-n 호모접합, p-n 단일 및 이중 해테로접합, 및 p-n 퀸텀 접합 웰 구조로 이루어지는 군으로부터 선택되고, 상기 실리콘 카바이드 기판은 3C, 4H, 6H, 및 15R 폴리형으로 이루어지는 군으로부터 선택된 폴리형을 갖는 광전 소자.

### 청구항 37.

제35항에 있어서,

상기 3족 질화물 액티브층이 갈륨 질화물 및 인듐 갈륨 질화물로 이루어지는 군으로부터 선택되는 광전 소자.

### 청구항 38.

3족 질화물 소자용 웨이퍼 전구체에 있어서,

실리콘 카바이드 기판 웨이퍼;

상기 실리콘 카바이드 기판 상의 알루미늄 갈륨 질화물 벼피층; 및

상기 실리콘 카바이드 기판의 표면 상에 갈륨 질화물 및 인듐 갈륨 질화물로 이루어지는 군으로부터 선택되고 평방 (square) 미크론 당 40 내지 60개의 양으로 존재하는 복수개의 이산 결정부

를 포함하는 웨이퍼 전구체.

### 청구항 39.

제38항에 있어서,

상기 알루미늄 갈륨 질화물 버퍼층이 10% 내지 15%의 알루미늄 원자 구성비(atomic fraction)를 갖는 웨이퍼 전구체.

### 청구항 40.

3족 질화물 액티브층을 갖는 광전 다이오드를 포함하는 제38항의 웨이퍼 전구체로부터 형성된 광전 소자.

### 청구항 41.

제40항에 있어서,

상기 다이오드는 p-n 호모접합, p-n 단일 및 이중 해테로접합, 및 p-n 퀸텀접합 웰 구조로 이루어지는 군으로부터 선택되고, 상기 실리콘 카바이드 기판은 3C, 4H, 6H, 및 15R 폴리형으로 이루어지는 군으로부터 선택된 폴리형을 갖는 광전 소자.

### 청구항 42.

제40에 있어서,

상기 3족 질화물 액티브층이 갈륨 질화물 및 인듐 갈륨 질화물로 이루어지는 군으로부터 선택되는 광전 소자.

### 청구항 43.

제29항, 제35항, 또는 제40항에 있어서,

발광 다이오드를 포함하는 광전 소자.

### 청구항 44.

제43항에 따른 발광 다이오드를 결합한 화소.

### 청구항 45.

제44항에 따른 복수개의 화소를 결합한 표시 소자.

### 청구항 46.

제29항, 제35항, 또는 제40항에 있어서,

레이저 다이오드를 포함하는 광전 소자.

### 청구항 47.

실리콘 카바이드 기판 상에 3족 질화물 광전 소자를 형성하기 위한 방법에 있어서,

결정 성장용으로 준비된 상기 실리콘 카바이드 기판의 표면 상에 미리 정해진 홈(groove) 패턴을 형성하는 단계;

상기 실리콘 카바이드 기판의 패턴 형성된 기판 상에 갈륨 질화물과 인듐 갈륨 질화물로 이루어지는 군으로부터 선택된 벼퍼층을 형성하는 단계; 및

상기 벼퍼층 상에 3족 질화물 액티브층을 갖는 광학 소자를 형성하는 단계

를 포함하고,

상기 벼퍼층이 형상(feature)을 드러내면 실리콘 카바이드 기판의 표면에 패턴을 형성하는

광전 소자 형성 방법.

### 청구항 48.

제47항에 있어서,

상기 홈 형성 단계가 실리콘 카바이드 기판의 표면을 마스킹한 후 상기 패턴을 형성하도록 상기 마스크된 표면을 에칭하는 단계를 포함하는 광전 소자 형성방법.

### 청구항 49.

제47항에 있어서,

상기 3족 질화물 액티브층을 갖는 광전 소자 형성 단계가 갈륨 질화물과 인듐 갈륨 질화물로 이루어지는 군으로부터 선택되는 광전 소자 형성방법.

### 청구항 50.

실리콘 카바이드 기판 상에 3족 질화물 광전 소자를 형성하기 위한 방법에 있어서,

벼퍼 물질의 성장에 대해 저항성을 갖는 물질로부터 상기 실리콘 카바이드 기판의 표면 상에 미리 정해진 메사 구조 패턴을 형성하는 단계;

상기 실리콘 카바이드 기판의 노출 표면 상에 벼퍼층을 형성하는 단계; 및

상기 벼퍼층 상에 3족 질화물 액티브층을 갖는 광전 소자를 형성하는 단계

를 포함하는 광전 소자 형성방법.

### 청구항 51.

제50항에 있어서,

상기 베퍼 물질의 성장에 대해 저항성을 갖는 상기 물질이 실리콘 디옥사이드, 실리콘 질화물, 및 알루미늄 산화물로 이루어지는 군으로부터 선택되는 광전 소자 형성방법.

### 청구항 52.

제50항에 있어서,

상기 베퍼 물질이 갈륨 질화물 및 인듐 갈륨 질화물로 이루어지는 군으로부터 선택되는 광전 소자 형성방법.

### 청구항 53.

제50항에 있어서,

3족 질화물 액티브층을 갖는 광전 소자 형성 단계가 갈륨 질화물 및 인듐 갈륨 질화물로 이루어지는 군으로부터 선택된 액티브층을 갖는 소자를 형성하는 단계를 포함하는 광전 소자 형성방법.

### 청구항 54.

실리콘 카바이드 기판 상에 3족 질화물 광전 소자를 형성하는 방법에 있어서,

상기 실리콘 카바이드 기판 상에 갈륨 질화물과 인듐 갈륨 질화물로 이루어지는 군으로부터 선택된 복수개의 이산 결정부를 형성하는 단계;

상기 이산 결정부를 갖는 실리콘 카바이드 기판의 표면 상에 알루미늄 갈륨 질화물 베퍼를 형성하는 단계; 및

상기 베퍼층에 3족 질화물 액티브층을 갖는 광전 소자를 형성하는 단계

를 포함하고,

상기 이산 결정부는 상기 실리콘 카바이드 기판과 상기 알루미늄 갈륨 질화물 베퍼층 사이에 헤테로배리어를 최소화하거나 제거하는

광전 소자 형성방법.

### 청구항 55.

제54항에 있어서,

상기 이산 결정부 형성 단계가 평방(square) 미크론 당 40 내지 60개의 양으로 상기 이산 결정부를 형성하는 단계를 포함하는 광전 소자 형성방법.

### 청구항 56.

제54항에 있어서,

상기 이산 결정부의 직경이 0.01 내지 0.1 미크론인 광전 소자 형성방법.

도면

도면1

도면2

도면3

도면4

도면5

도면6

도면7

도면8

도면9

도면10

도면11

도면12

도면13

도면14

도면15

도면16

도면17