(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6824001号

(P6824001)

(45) 発行日 令和3年2月3日(2021.2.3)

(24) 登録日 令和3年1月14日(2021.1.14)

(51) Int.Cl.

F 1

|             |                |                  |             |               |             |

|-------------|----------------|------------------|-------------|---------------|-------------|

| <b>H03K</b> | <b>3/354</b>   | <b>(2006.01)</b> | <b>H03K</b> | <b>3/354</b>  | <b>B</b>    |

| <b>H03K</b> | <b>3/014</b>   | <b>(2006.01)</b> | <b>H03K</b> | <b>3/014</b>  |             |

| <b>H01L</b> | <b>21/8234</b> | <b>(2006.01)</b> | <b>H01L</b> | <b>27/06</b>  | <b>102A</b> |

| <b>H01L</b> | <b>27/06</b>   | <b>(2006.01)</b> | <b>H01L</b> | <b>27/088</b> | <b>331E</b> |

| <b>H01L</b> | <b>27/088</b>  | <b>(2006.01)</b> | <b>H01L</b> | <b>27/092</b> | <b>G</b>    |

請求項の数 7 (全 64 頁) 最終頁に続く

(21) 出願番号

特願2016-211192 (P2016-211192)

(22) 出願日

平成28年10月28日 (2016.10.28)

(65) 公開番号

特開2017-85571 (P2017-85571A)

(43) 公開日

平成29年5月18日 (2017.5.18)

審査請求日 令和1年10月21日 (2019.10.21)

(31) 優先権主張番号 特願2015-213708 (P2015-213708)

(32) 優先日 平成27年10月30日 (2015.10.30)

(33) 優先権主張国・地域又は機関

日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 岡本 佑樹

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 黒川 義元

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 工藤 一光

最終頁に続く

(54) 【発明の名称】 半導体装置および電子機器

(57) 【特許請求の範囲】

【請求項 1】

第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、第4のトランジスタと、第5のトランジスタと、容量素子と、を有する半導体装置であって、

前記第1のトランジスタは前記第2のトランジスタと異なる極性を有し、

前記第5のトランジスタは前記第2のトランジスタと同じ極性を有し、

前記第1のトランジスタのゲートは前記第2のトランジスタのゲートと電気的に接続され、

前記第1のトランジスタのソースまたはドレインの一方は前記第2のトランジスタのソースまたはドレインの一方と電気的に接続され、

前記第1のトランジスタのソースまたはドレインの一方は前記第5のトランジスタのソースまたはドレインの一方と電気的に接続され、

前記第5のトランジスタのゲートは前記第1のトランジスタのソースまたはドレインの他方と電気的に接続され、

前記第5のトランジスタのソースまたはドレインの他方は前記第3のトランジスタのソースまたはドレインの一方と電気的に接続され、

前記第3のトランジスタのゲートは前記第4のトランジスタのソースまたはドレインの一方と電気的に接続され、

前記第3のトランジスタのゲートは前記容量素子の一方の電極と電気的に接続され、

前記容量素子の他方の電極は前記第2のトランジスタのソースまたはドレインの他方と

10

20

電気的に接続されている半導体装置。

**【請求項 2】**

請求項1において、

前記第3のトランジスタ、前記第4のトランジスタおよび前記第5のトランジスタは、チャネルが形成される領域に酸化物半導体を有する半導体装置。

**【請求項 3】**

請求項1または請求項2において、

前記第1のトランジスタのソースまたはドレインの他方は高電位電源線と電気的に接続され、

前記第2のトランジスタのソースまたはドレインの他方は低電位電源線と電気的に接続されている半導体装置。 10

**【請求項 4】**

請求項1乃至請求項3のいずれか一項において、

前記第2のトランジスタは、チャネルが形成される領域に酸化物半導体を有する半導体装置。

**【請求項 5】**

請求項1乃至請求項4のいずれか一項において、

前記酸化物半導体は、Inと、Znと、M(MはAl、Ga、YまたはSn)と、を有する半導体装置。 20

**【請求項 6】**

請求項1乃至請求項5のいずれか一項において、

前記第1のトランジスタはpチャネル型であり、

前記第2のトランジスタはnチャネル型である半導体装置。

**【請求項 7】**

請求項1乃至請求項6のいずれか一項に記載の半導体装置と、表示装置と、を有する電子機器。 30

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明の一態様は、半導体装置に関する。 30

**【0002】**

なお、本発明の一態様は、上記の技術分野に限定されない。本明細書等で開示する発明の一態様の技術分野は、物、方法、または、製造方法に関するものである。または、本発明の一態様は、プロセス、マシン、マニュファクチャ、または、組成物(コンポジション・オブ・マター)に関するものである。そのため、より具体的に本明細書で開示する本発明の一態様の技術分野としては、半導体装置、表示装置、液晶表示装置、発光装置、照明装置、蓄電装置、記憶装置、撮像装置、それらの動作方法、または、それらの製造方法、を一例として挙げることができる。

**【0003】**

なお、本明細書等において半導体装置とは、半導体特性を利用して機能しうる装置全般を指す。トランジスタ、半導体回路は半導体装置の一態様である。また、記憶装置、表示装置、撮像装置、電子機器は、半導体装置を有する場合がある。 40

**【背景技術】**

**【0004】**

電圧制御発振器(VCO: Voltage Controlled Oscillator)は発振回路の1つであり、供給する信号電圧により出力信号の発振周波数を制御することができる。例えば、リングオシレータ型のVCOが知られており、特許文献1にその一例が開示されている。

**【0005】**

電圧制御発振器は、位相同期回路(PLL: Phase-Locked Loop)やD 50

C - D C コンバータに用いられている。PLLは、安定した周波数信号を生成するための回路として、CPU(Central Processing Unit)やプログラマブルロジックデバイス等に用いられる。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開平6-310994号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

CPUなどの高機能回路では高速化が望まれる一方で、低消費電力化が課題となっている。低消費電力化の一手段として、アイドリング時に電源供給を停止するなどの制御方法がある。

【0008】

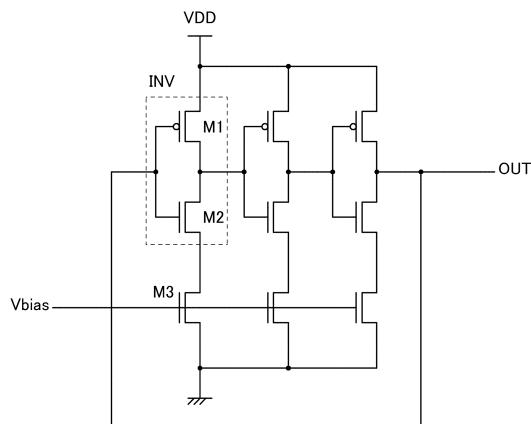

図9はリングオシレータ型電圧制御発振器の一例である。pチャネル型のトランジスタM1およびnチャネル型のトランジスタM2で構成されるインバータINVと、トランジスタM2と接地端子との間に接続されたnチャネル型のトランジスタM3で信号伝達回路(遅延回路ともいう)を構成し、トランジスタM3のオン抵抗をVbiasで変化させることで発振周波数を制御する。

【0009】

上記の電圧制御発振器においては、電源供給を停止するとトランジスタを介して電荷が流出するため、インバータの入力電位が変化する。そのため、再度電源を投入してから発振周波数が安定化するまでに時間を要してしまう。つまり、図9に示すような電圧制御発振器は高速起動することが困難である。

【0010】

したがって、本発明の一態様では、高速起動することができる発振器を提供することを目的の一つとする。または、電源電圧の供給を停止し、電源電圧の供給を再開したときに速やかに電源電圧供給停止前の周波数で発振することのできる発振器を提供することを目的の一つとする。または、インバータの入力端子に入力信号を保持することのできる発振器を提供することを目的の一つとする。または、発振周波数を制御する信号を記憶する回路を有する発振器を提供することを目的の一つとする。または、広い温度範囲において使用可能な発振器を提供することを目的の一つとする。または、信頼性の高い発振器を提供することを目的の一つとする。または、新規な発振器などを提供することを目的の一つとする。または、上記発振器の動作方法を提供することを目的の一つとする。または、新規な半導体装置などを提供することを目的の一つとする。

【0011】

なお、これらの課題の記載は、他の課題の存在を妨げるものではない。なお、本発明の一態様は、これらの課題の全てを解決する必要はないものとする。なお、これら以外の課題は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の課題を抽出することが可能である。

【課題を解決するための手段】

【0012】

本発明の一態様は、高速起動することができる発振器に関する。

【0013】

本発明の一態様は、第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、第4のトランジスタと、容量素子と、を有する半導体装置であって、第1のトランジスタは第2のトランジスタと異なる極性を有し、第1のトランジスタのゲートは第2のトランジスタのゲートと電気的に接続され、第1のトランジスタのソースまたはドレインの一方は第2のトランジスタのソースまたはドレインの一方と電気的に接続され、第1のトランジスタのソースまたはドレインの一方は第3のトランジスタのソースまたはドレイン

10

20

30

40

50

の一方と電気的に接続され、第3のトランジスタのゲートは第4のトランジスタのソースまたはドレインの一方と電気的に接続され、第3のトランジスタのゲートは容量素子の一方の電極と電気的に接続され、容量素子の他方の電極は第1のトランジスタのソースまたはドレインの他方と電気的に接続されていることを特徴とする半導体装置である。

**【0014】**

また、本発明の他の一態様は、第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、第4のトランジスタと、第5のトランジスタと、容量素子と、を有する半導体装置であって、第1のトランジスタは第2のトランジスタと異なる極性を有し、第5のトランジスタは第2のトランジスタと同じ極性を有し、第1のトランジスタのゲートは第2のトランジスタのゲートと電気的に接続され、第1のトランジスタのソースまたはドレインの一方は第2のトランジスタのソースまたはドレインの一方と電気的に接続され、第1のトランジスタのソースまたはドレインの一方は第5のトランジスタのソースまたはドレインの一方と電気的に接続され、第5のトランジスタのゲートは第1のトランジスタのソースまたはドレインの他方と電気的に接続され、第5のトランジスタのソースまたはドレインの他方は第3のトランジスタのソースまたはドレインの一方と電気的に接続され、第3のトランジスタのゲートは第4のトランジスタのソースまたはドレインの一方と電気的に接続され、第3のトランジスタのゲートは容量素子の一方の電極と電気的に接続され、容量素子の他方の電極は第2のトランジスタのソースまたはドレインの他方と電気的に接続されていることを特徴とする半導体装置である。

**【0015】**

上記二つの態様の半導体装置において、第1のトランジスタのソースまたはドレインの他方は高電位電源線と電気的に接続し、第2のトランジスタのソースまたはドレインの他方は低電位電源線と電気的に接続することができる。

**【0016】**

上記二つの態様の半導体装置に用いられるトランジスタのうち、第3のトランジスタ、第4のトランジスタおよび第5のトランジスタは、チャネルが形成される領域に酸化物半導体を有することが好ましい。

**【0017】**

酸化物半導体は、Inと、Znと、M(MはAl、Ga、YまたはSn)と、を有することが好ましい。また、第2のトランジスタもチャネルが形成される領域に酸化物半導体を有していてもよい。

**【発明の効果】**

**【0018】**

本発明の一態様を用いることで、高速起動することができる発振器を提供することができる。または、電源電圧の供給を停止し、電源電圧の供給を再開したときに速やかに電源電圧供給停止前の周波数で発振することのできる発振器を提供することができる。または、インバータの入力端子に入力信号を保持することのできる発振器を提供することができる。または、発振周波数を制御する信号を記憶する回路を有する発振器を提供することができる。または、広い温度範囲において使用可能な発振器を提供することができる。または、信頼性の高い発振器を提供することができる。または、新規な発振器などを提供することができる。または、上記発振器の動作方法を提供することができる。または、新規な半導体装置などを提供することができる。

**【0019】**

なお、本発明の一態様はこれらの効果に限定されるものではない。例えば、本発明の一態様は、場合によっては、または、状況に応じて、これらの効果以外の効果を有する場合もある。または、例えば、本発明の一態様は、場合によっては、または、状況に応じて、これらの効果を有さない場合もある。

**【図面の簡単な説明】**

**【0020】**

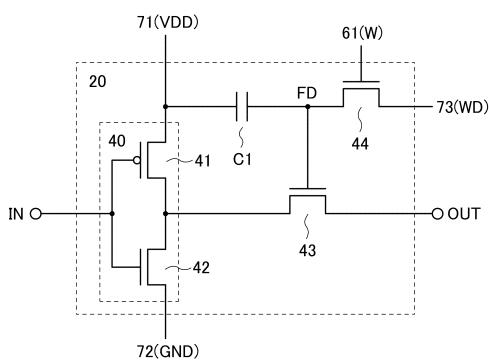

【図1】信号伝遡回路を説明する回路図。

10

20

30

40

50

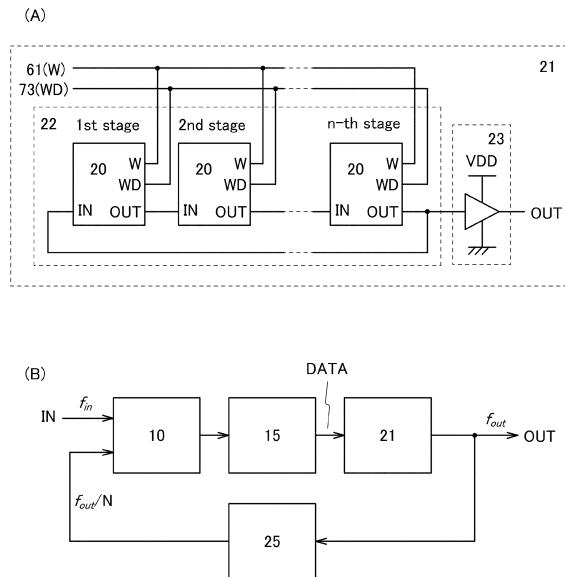

- 【図2】電圧制御発振器およびPLLを説明するブロック図。

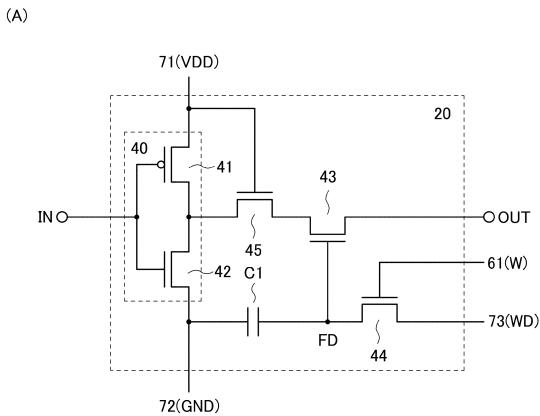

- 【図3】信号伝回路を説明する回路図。

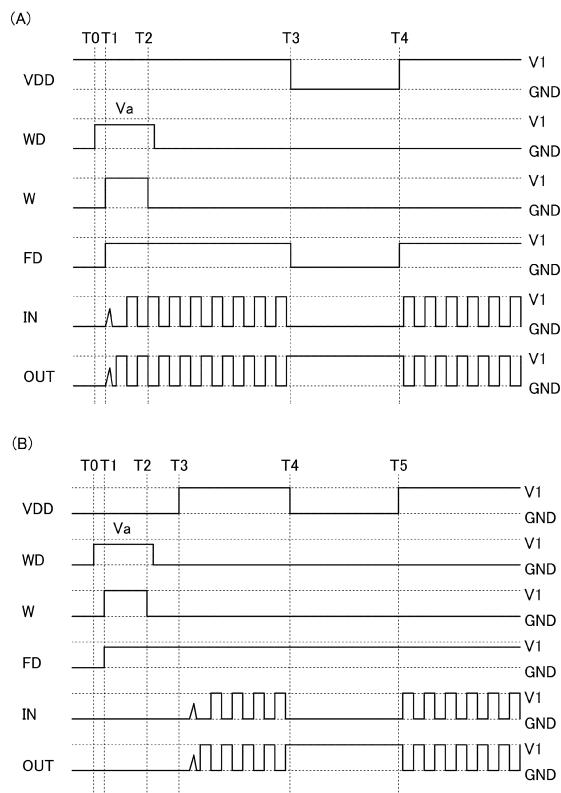

- 【図4】電圧制御発振器の動作を説明するタイミングチャート。

- 【図5】信号伝回路を説明する回路図。

- 【図6】信号伝回路を説明する回路図。

- 【図7】電圧制御発振器を説明するブロック図。

- 【図8】電圧制御発振器の動作を説明するタイミングチャート。

- 【図9】信号伝回路を説明する回路図。

- 【図10】信号伝回路を説明する回路図。

- 【図11】信号伝回路を説明する断面図。 10

- 【図12】信号伝回路を説明する断面図。

- 【図13】信号伝回路を説明する断面図。

- 【図14】トランジスタを説明する上面図および断面図。

- 【図15】トランジスタを説明する上面図および断面図。

- 【図16】トランジスタのチャネル幅方向の断面を説明する図。

- 【図17】トランジスタのチャネル長方向の断面を説明する図。

- 【図18】半導体層を説明する上面図および断面図。

- 【図19】トランジスタを説明する上面図および断面図。

- 【図20】トランジスタを説明する上面図および断面図。 20

- 【図21】トランジスタのチャネル幅方向の断面を説明する図。

- 【図22】トランジスタのチャネル長方向の断面を説明する図。

- 【図23】トランジスタを説明する上面図および断面図。

- 【図24】トランジスタを説明する上面図。

- 【図25】酸化物半導体の原子数比の範囲を説明する図。

- 【図26】InMznO<sub>4</sub>の結晶を説明する図。

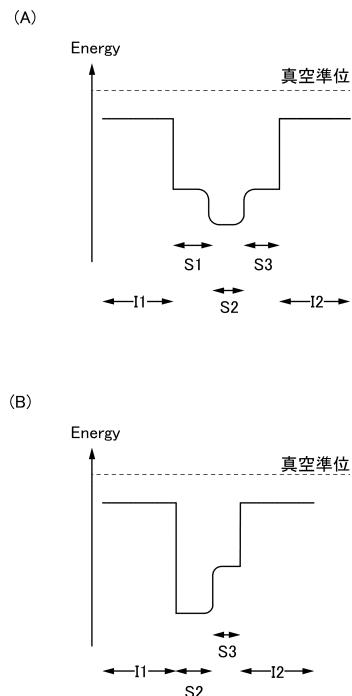

- 【図27】酸化物半導体の積層構造におけるバンド図。

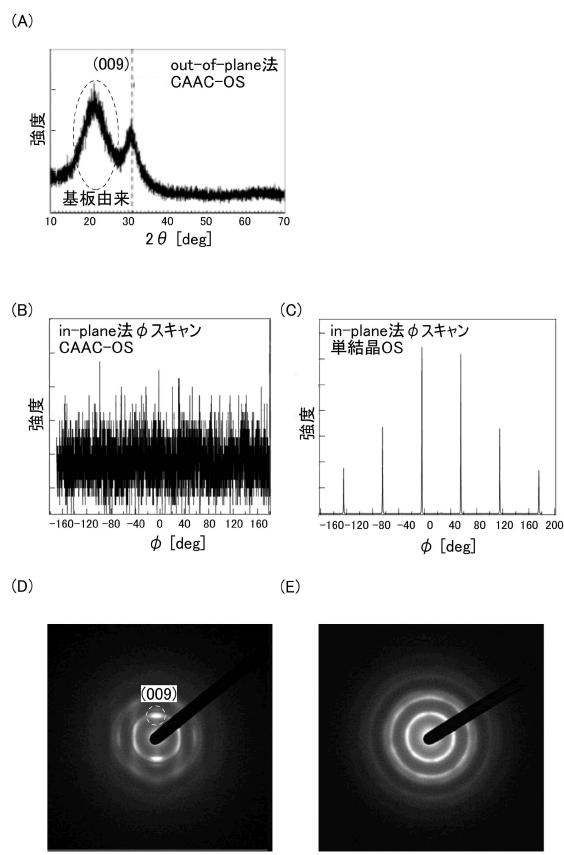

- 【図28】CAAC-OSおよび単結晶酸化物半導体のXRDによる構造解析を説明する図、ならびにCAAC-OSの制限視野電子回折パターンを示す図。

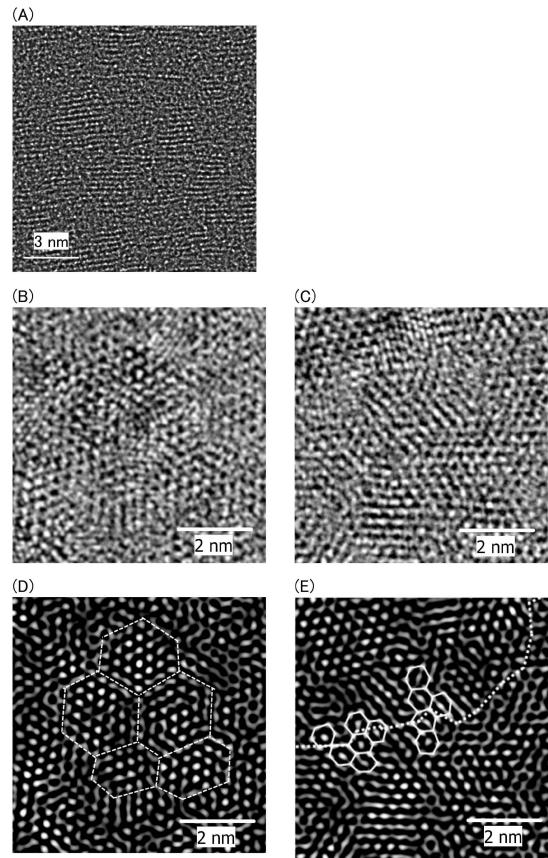

- 【図29】CAAC-OSの断面TEM像、ならびに平面TEM像およびその画像解析像。 30

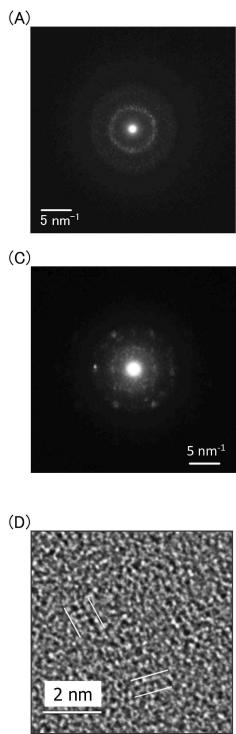

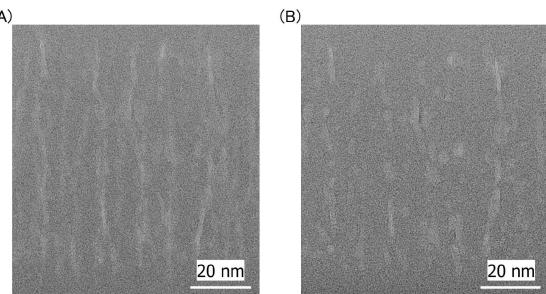

- 【図30】n<sub>c</sub>-OSの電子回折パターンを示す図、およびn<sub>c</sub>-OSの断面TEM像。

- 【図31】a-like OSの断面TEM像。

- 【図32】In-Ga-Zn酸化物の電子照射による結晶部の変化を示す図。

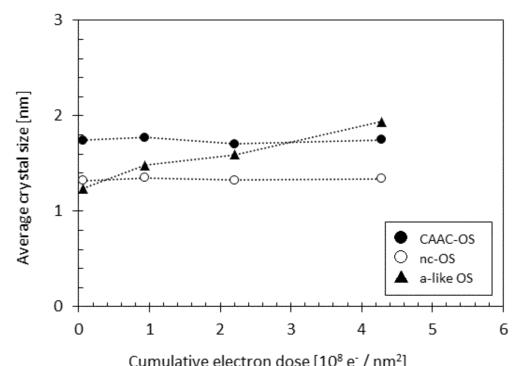

- 【図33】プロセッシングユニット（無線IC）の構成例を示すブロック図。

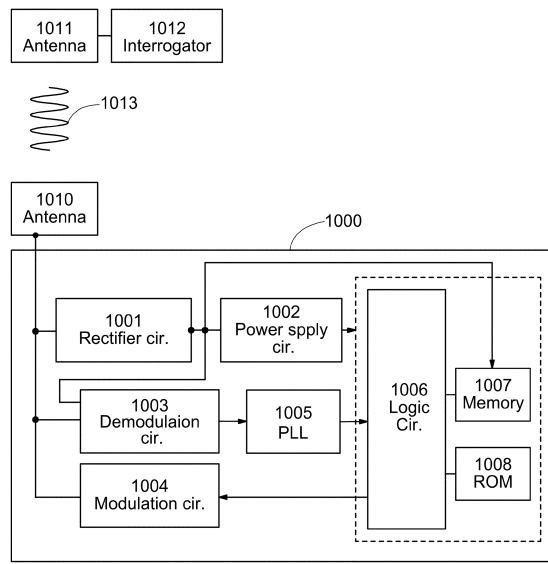

- 【図34】プロセッシングユニット（PLD）の構成例を示す模式図。

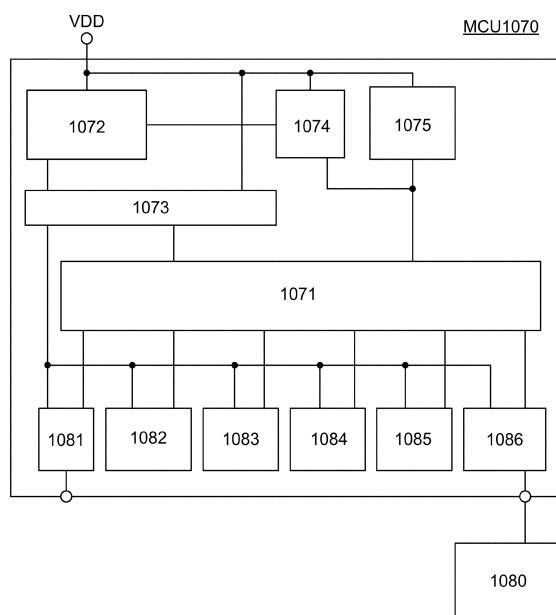

- 【図35】プロセッシングユニット（MCU）の構成例を示すブロック図。

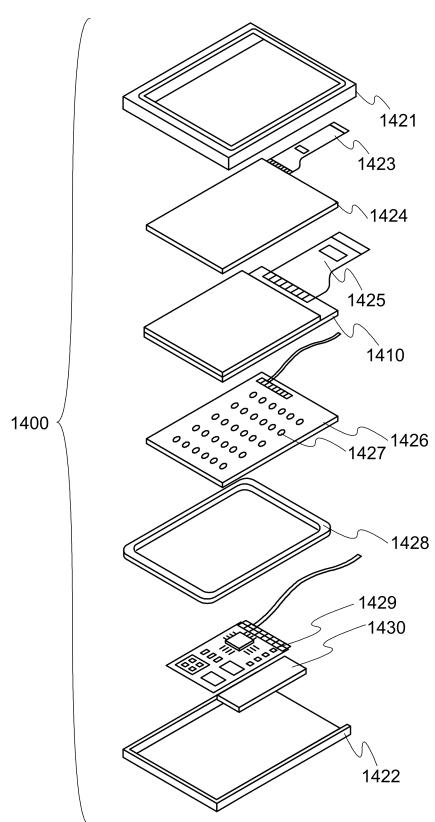

- 【図36】表示装置の一例を示す分解斜視図。

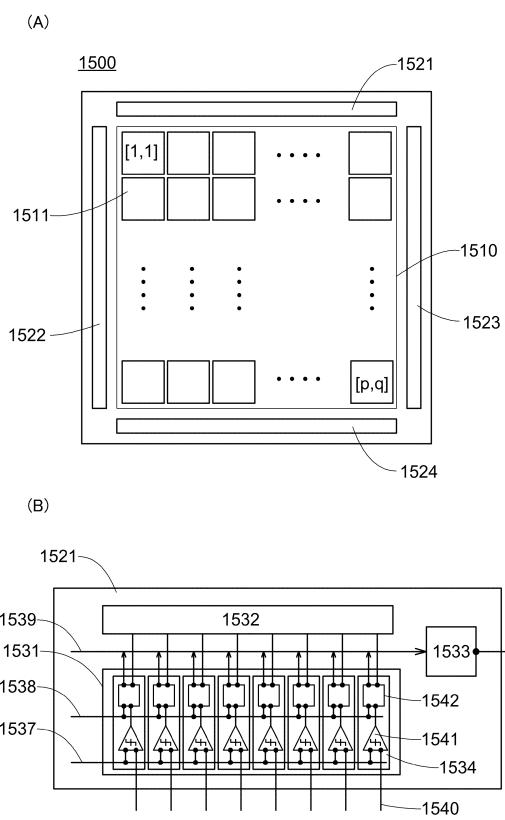

- 【図37】撮像装置の構成例を示すブロック図、および駆動回路の構成例を示すブロック図。

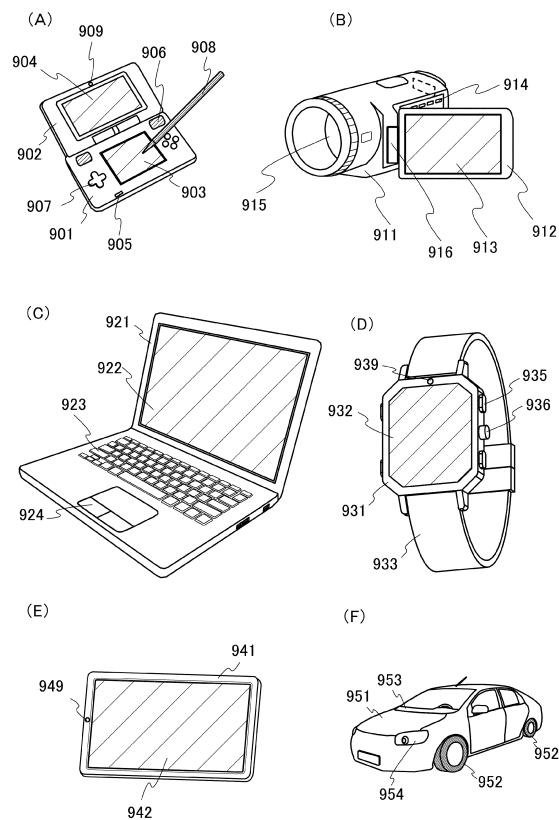

- 【図38】電子機器の構成例を示す図。 40

- 【発明を実施するための形態】**

- 【0021】**

- 実施の形態について、図面を用いて詳細に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨およびその範囲から逸脱することなくその形態および詳細を様々に変更し得ることは当業者であれば容易に理解される。したがって、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する発明の構成において、同一部分または同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略することがある。なお、図を構成する同じ要素のハッチングを異なる図面間で適宜省略または変更する場合もある。

- 【0022】** 50

なお、第1、第2として付される序数詞は便宜的に用いるものであり、工程順または積層順を示すものではない。そのため、例えば、「第1の」を「第2の」または「第3の」などと適宜置き換えて説明することができる。また、本明細書などに記載されている序数詞と、本発明の一態様を特定するために用いられる序数詞は一致しない場合がある。

#### 【0023】

例えば、本明細書等において、XとYとが接続されている、と明示的に記載されている場合は、XとYとが電気的に接続されている場合と、XとYとが機能的に接続されている場合と、XとYとが直接接続されている場合とが、本明細書等に開示されているものとする。

したがって、所定の接続関係、例えば、図または文章に示された接続関係に限定されず、図または文章に示された接続関係以外のものも、図または文章に記載されているものとする。

10

#### 【0024】

ここで、X、Yは、対象物（例えば、装置、素子、回路、配線、電極、端子、導電膜、層、など）であるとする。

#### 【0025】

XとYとが直接的に接続されている場合の一例としては、XとYとの電気的な接続を可能とする素子（例えば、スイッチ、トランジスタ、容量素子、インダクタ、抵抗素子、ダイオード、表示素子、発光素子、負荷など）が、XとYとの間に接続されていない場合であり、XとYとの電気的な接続を可能とする素子（例えば、スイッチ、トランジスタ、容量素子、インダクタ、抵抗素子、ダイオード、表示素子、発光素子、負荷など）を介さずに、XとYとが、接続されている場合である。

20

#### 【0026】

XとYとが電気的に接続されている場合の一例としては、XとYとの電気的な接続を可能とする素子（例えば、スイッチ、トランジスタ、容量素子、インダクタ、抵抗素子、ダイオード、表示素子、発光素子、負荷など）が、XとYとの間に1個以上接続されることが可能である。なお、スイッチは、オンオフが制御される機能を有している。つまり、スイッチは、導通状態（オン状態）、または、非導通状態（オフ状態）になり、電流を流すか流さないかを制御する機能を有している。または、スイッチは、電流を流す経路を選択して切り替える機能を有している。なお、XとYとが電気的に接続されている場合は、XとYとが直接的に接続されている場合を含むものとする。

30

#### 【0027】

XとYとが機能的に接続されている場合の一例としては、XとYとの機能的な接続を可能とする回路（例えば、論理回路（インバータ、NAND回路、NOR回路など）、信号変換回路（D/A変換回路、A/D変換回路、ガンマ補正回路など）、電位レベル変換回路（電源回路（昇圧回路、降圧回路など）、信号の電位レベルを変えるレベルシフタ回路など）、電圧源、電流源、切り替え回路、增幅回路（信号振幅または電流量などを大きく出来る回路、オペアンプ、差動增幅回路、ソースフォロワ回路、バッファ回路など）、信号生成回路、記憶回路、制御回路など）が、XとYとの間に1個以上接続されることが可能である。なお、一例として、XとYとの間に別の回路を挟んでいても、Xから出力された信号がYへ伝達される場合は、XとYとは機能的に接続されているものとする。なお、XとYとが機能的に接続されている場合は、XとYとが直接的に接続されている場合と、XとYとが電気的に接続されている場合とを含むものとする。

40

#### 【0028】

なお、XとYとが電気的に接続されている、と明示的に記載されている場合は、XとYとが電気的に接続されている場合（つまり、XとYとの間に別の素子または別の回路を挟んで接続されている場合）と、XとYとが機能的に接続されている場合（つまり、XとYとの間に別の回路を挟んで機能的に接続されている場合）と、XとYとが直接接続されている場合（つまり、XとYとの間に別の素子または別の回路を挟まずに接続されている場合）とが、本明細書等に開示されているものとする。つまり、電気的に接続されている、と明示的に記載されている場合は、単に、接続されている、とのみ明示的に記載されている

50

場合と同様な内容が、本明細書等に開示されているものとする。

**【0029】**

なお、例えば、トランジスタのソース（または第1の端子など）が、Z1を介して（または介さず）、Xと電気的に接続され、トランジスタのドレイン（または第2の端子など）が、Z2を介して（または介さず）、Yと電気的に接続されている場合や、トランジスタのソース（または第1の端子など）が、Z1の一部と直接的に接続され、Z1の別の一部がXと直接的に接続され、トランジスタのドレイン（または第2の端子など）が、Z2の一部と直接的に接続され、Z2の別の一部がYと直接的に接続されている場合では、以下のように表現することが出来る。

**【0030】**

例えば、「XとYとトランジスタのソース（または第1の端子など）とドレイン（または第2の端子など）とは、互いに電気的に接続されており、X、トランジスタのソース（または第1の端子など）、トランジスタのドレイン（または第2の端子など）、Yの順序で電気的に接続されている。」と表現することができる。または、「トランジスタのソース（または第1の端子など）は、Xと電気的に接続され、トランジスタのドレイン（または第2の端子など）はYと電気的に接続され、X、トランジスタのソース（または第1の端子など）、トランジスタのドレイン（または第2の端子など）、Yは、この順序で電気的に接続されている」と表現することができる。または、「Xは、トランジスタのソース（または第1の端子など）とドレイン（または第2の端子など）とを介して、Yと電気的に接続され、X、トランジスタのソース（または第1の端子など）、トランジスタのドレイン（または第2の端子など）、Yは、この接続順序で設けられている」と表現することができる。これらの例と同様な表現方法を用いて、回路構成における接続の順序について規定することにより、トランジスタのソース（または第1の端子など）と、ドレイン（または第2の端子など）とを、区別して、技術的範囲を決定することができる。

10

**【0031】**

または、別の表現方法として、例えば、「トランジスタのソース（または第1の端子など）は、少なくとも第1の接続経路を介して、Xと電気的に接続され、前記第1の接続経路は、第2の接続経路を有しておらず、前記第2の接続経路は、トランジスタを介した、トランジスタのソース（または第1の端子など）とトランジスタのドレイン（または第2の端子など）との間の経路であり、前記第1の接続経路は、Z1を介した経路であり、トランジスタのドレイン（または第2の端子など）は、少なくとも第3の接続経路を介して、Yと電気的に接続され、前記第3の接続経路は、前記第2の接続経路を有しておらず、前記第3の接続経路は、Z2を介した経路である。」と表現することができる。または、「トランジスタのソース（または第1の端子など）は、少なくとも第1の接続経路によって、Z1を介して、Xと電気的に接続され、前記第1の接続経路は、第2の接続経路を有しておらず、前記第2の接続経路は、トランジスタを介した接続経路を有し、トランジスタのドレイン（または第2の端子など）は、少なくとも第3の接続経路によって、Z2を介して、Yと電気的に接続され、前記第3の接続経路は、前記第2の接続経路を有していない。」と表現することができる。または、「トランジスタのソース（または第1の端子など）は、少なくとも第1の電気的バスによって、Z1を介して、Xと電気的に接続され、前記第1の電気的バスは、第2の電気的バスを有しておらず、前記第2の電気的バスは、トランジスタのソース（または第1の端子など）からトランジスタのドレイン（または第2の端子など）への電気的バスであり、トランジスタのドレイン（または第2の端子など）は、少なくとも第3の電気的バスによって、Z2を介して、Yと電気的に接続され、前記第3の電気的バスは、第4の電気的バスを有しておらず、前記第4の電気的バスは、トランジスタのドレイン（または第2の端子など）からトランジスタのソース（または第1の端子など）への電気的バスである。」と表現することができる。これらの例と同様な表現方法を用いて、回路構成における接続経路について規定することにより、トランジスタのソース（または第1の端子など）と、ドレイン（または第2の端子など）とを、区別して、技術的範囲を決定することができる。

20

30

40

50

**【 0 0 3 2 】**

なお、これらの表現方法は、一例であり、これらの表現方法に限定されない。ここで、X、Y、Z1、Z2は、対象物（例えば、装置、素子、回路、配線、電極、端子、導電膜、層、など）であるとする。

**【 0 0 3 3 】**

なお、回路図上は独立している構成要素同士が電気的に接続しているように図示されている場合であっても、1つの構成要素が、複数の構成要素の機能を併せ持っている場合もある。例えば配線の一部が電極としても機能する場合は、一の導電膜が、配線の機能、および電極の機能の両方の構成要素の機能を併せ持っている。したがって、本明細書における電気的に接続とは、このような、一の導電膜が、複数の構成要素の機能を併せ持っている場合も、その範疇に含める。10

**【 0 0 3 4 】**

なお、「膜」という言葉と、「層」という言葉とは、場合によっては、または、状況に応じて、互いに入れ替えることが可能である。例えば、「導電層」という用語を、「導電膜」という用語に変更することが可能な場合がある。または、例えば、「絶縁膜」という用語を、「絶縁層」という用語に変更することが可能な場合がある。

**【 0 0 3 5 】**

なお、一般的に、電位（電圧）は、相対的なものであり、基準の電位からの相対的な大きさによって大きさが決定される。したがって、「接地」「GND」「グラウンド」などと記載されている場合であっても、必ずしも、電位が0ボルトであるとは限らないものとする。例えば、回路で最も低い電位を基準として、「接地」や「GND」を定義する場合もある。または、回路で中間くらいの電位を基準として、「接地」や「GND」を定義する場合もある。その場合には、その電位を基準として、正の電位と負の電位が規定されることとなる。20

**【 0 0 3 6 】****(実施の形態1)**

本実施の形態では、本発明の一態様である発振器について、図面を参照して説明する。

**【 0 0 3 7 】**

本発明の一態様は、発振中に電源電圧の供給を停止し、電源電圧の供給を再開したときに、電源電圧供給停止直前の周波数で速やかに発振することのできる電圧制御発振器の回路構成および動作方法である。30

**【 0 0 3 8 】**

本発明の一態様を用いることによって、CPUなどにおいてアイドリング時に一時的に、電圧制御発振器への電源電圧の供給を停止し、発振を停止した場合においても電源電圧の供給再開時に速やかに発振を開始することができる。つまり、特定の発振周波数の出力信号に同期して動作する回路を高速に起動することができる。

**【 0 0 3 9 】**

本発明の一態様では、電圧制御発振器が有する前段のインバータの出力端子と後段のインバータの入力端子との間にトランジスタを設け、当該トランジスタのオン抵抗によって出力信号の発振周波数を制御する。また、電源電圧の供給停止時には当該トランジスタをオフすることによってインバータの入力端子に電源電圧の供給停止直前に入力された信号を保持する。この動作により、電源電圧の供給再開時に電源電圧の供給停止前と同じ周波数の信号を速やかに出力することができる。40

**【 0 0 4 0 】**

上記トランジスタには、チャネル形成領域に酸化物半導体を有するトランジスタを用いることができる。当該トランジスタはオフ電流が小さく、電源電圧の供給停止直前に入力された信号を保持するメモリを簡易に構成することができる。

**【 0 0 4 1 】**

チャネル形成領域に酸化物半導体を有するトランジスタは、シリコンを活性領域または活性層に用いたトランジスタよりも電気特性変動の温度依存性が小さいため、極めて広い温50

度範囲で使用することができる。したがって、チャネル形成領域に酸化物半導体を有するトランジスタが設けられた発振器および半導体装置は、自動車、航空機、宇宙機などへの搭載にも適する。

#### 【 0 0 4 2 】

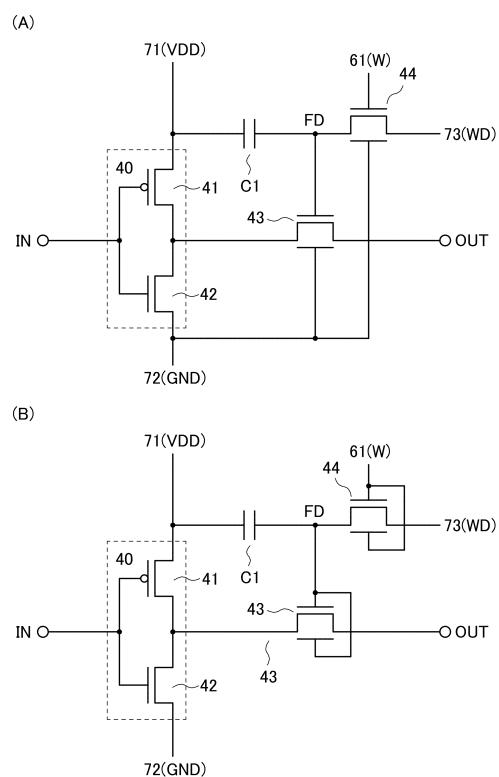

図1は、本発明の一態様の発振器が有する回路20の回路図である。回路20は、トランジスタ41、トランジスタ42と、トランジスタ43と、トランジスタ44と、容量素子C1と、を有する。ここで、トランジスタ41およびトランジスタ42は、インバータ40を構成する。

#### 【 0 0 4 3 】

図1に示す回路20において、トランジスタ41のゲートは、トランジスタ42のゲートと電気的に接続される。トランジスタ41のソースまたはドレインの一方は、トランジスタ42のソースまたはドレインの一方と電気的に接続される。トランジスタ41のソースまたはドレインの一方は、トランジスタ43のソースまたはドレインの一方と電気的に接続される。トランジスタ43のゲートは、トランジスタ44のソースまたはドレインの一方と電気的に接続される。トランジスタ43のゲートは、容量素子C1の一方の電極と電気的に接続される。容量素子C1の他方の電極は、トランジスタ41のソースまたはドレインの他方と電気的に接続される。

#### 【 0 0 4 4 】

なお、図1に示す構成ではトランジスタ41をpチャネル型、トランジスタ42をnチャネル型としたCMOS回路でインバータ40を構成した例を示しているが、本発明の一態様はこれに限定されず、インバータ40はNMOS型インバータまたはPMOS型インバータであってもよい。また、トランジスタ44がnチャネル型である場合の例を示しているが、pチャネル型トランジスタに置き換えてよい。

#### 【 0 0 4 5 】

ここで、トランジスタ43のゲート、容量素子C1の一方の電極、トランジスタ44のソースまたはドレインの一方が接続される配線をノードFDとする。また、トランジスタ41のゲートおよびトランジスタ42のゲートが電気的に接続される配線は、回路20の入力端子INとして機能する。また、トランジスタ43のソースまたはドレインの他方と電気的に接続される配線は、回路20の出力端子OUTとして機能する。

#### 【 0 0 4 6 】

図1において、トランジスタ41のソースまたはドレインの他方は、配線71と電気的に接続される。トランジスタ42のソースまたはドレインの他方は、配線72(GND)と電気的に接続される。トランジスタ44のソースまたはドレインの他方は、配線73(WD)と電気的に接続される。トランジスタ44のゲートは、配線61(W)と電気的に接続される。

#### 【 0 0 4 7 】

配線71(VDD)および配線72(GND)は、電源線としての機能を有することができる。配線71(VDD)は高電位電源線として機能させることができ、例えば電源電圧VDDを供給する。配線72(GND)は低電位電源線として機能させることができ、例えば0Vまたは接地電位GNDを供給する。なお、電源電圧の供給を停止するとき、配線71(VDD)は、例えば0Vまたは接地電位GNDを供給する。

#### 【 0 0 4 8 】

配線61(W)は、トランジスタ44の導通を制御する信号線として機能させることができる。配線73(WD)は、ノードFDに所望の電位を供給するための信号線として機能させることができる。

#### 【 0 0 4 9 】

回路20は、リングオシレータの信号伝達回路として機能させることができる。図2(A)は、本発明の一態様の電圧制御発振器21の回路図であり、n段(nは奇数)の回路20を有するリングオシレータ22と、バッファ回路23を有する。前段の回路20の出力端子OUTは後段の回路20の入力端子INと電気的に接続され、最終段の回路20の出

10

20

30

40

50

力端子 OUT は 1 段目の回路 20 の入力端子 IN およびバッファ回路 23 の入力端子と電気的に接続される。

#### 【 0050 】

回路 20 は入力信号に対して反転信号を出力する機能を有し、奇数段が接続されることでリングオシレータ 22 を構成し、特定の発振周波数の出力信号を出力することができる。バッファ回路 23 は、リングオシレータ 22 が出力する出力信号を外部へ出力する際に電流を增幅する機能を有する。なお、バッファ回路 23 を設けない構成とすることもできる。

#### 【 0051 】

図 2 (B) に、本発明の一態様の電圧制御発振器 21 を用いることができる PLL の構成の一例を示す。PLL は位相比較器 10、ループフィルタ 15、電圧制御発振器 21 および分周器 25 を有する。位相比較器 10 は二つの入力信号の位相差を検出する機能を有し、 $f_{in}$  (基本周波数) および  $f_{out}/N$  (比較周波数) の周波数を持つ信号の位相差を電圧信号として出力する。ループフィルタ 15 は、電圧制御発振器 21 に入力するための直流電圧信号 DATA を生成する機能を有する。ループフィルタ 15 には、位相比較器 10 の出力信号に含まれる高周波数成分を取り除く必要があるため、ローパスフィルタなどが用いられる。電圧制御発振器 21 は、DATA に依存して特定の発振周波数を示す出力信号を出力する機能を有する。分周器 25 は電圧制御発振器 21 から出力された特定の発振周波数を示す出力信号を  $1/N$  ( $N$  は整数) 倍に変化させた信号を生成する機能を有する。

10

20

#### 【 0052 】

図 1 に示す回路 20 の動作、および当該回路 20 を適用した図 2 (A) に示す電圧制御発振器 21 の動作を説明する。まず、トランジスタ 44 を導通させ、配線 73 (WD) の電位に対応するアナログデータをノード FD に書き込む。その後、トランジスタ 44 を非導通として、ノード FD に当該アナログデータを保持する。

#### 【 0053 】

トランジスタ 43 はノード FD に保持したアナログデータに応じて導通、非導通が制御される。トランジスタ 43 が導通する場合、回路 20 は入力信号に対して反転信号を出力する。すなわち、電圧制御発振器 21 は発振する。一方、トランジスタ 43 が非導通の場合、回路 20 の信号の伝達経路は遮断される。すなわち、電圧制御発振器 21 は発振しない。

30

#### 【 0054 】

トランジスタ 43 のオン電流は、ノード FD に保持したアナログデータに応じて制御される。ノード FD に比較的高いアナログ電位が与えられているとき、トランジスタ 43 のオン抵抗は低い値をとる。すなわち、電圧制御発振器 21 の出力信号の発振周波数は大きくなる。一方、ノード FD に比較的低いアナログ電位が与えられているとき、トランジスタ 43 のオン抵抗は高い値をとる。すなわち、電圧制御発振器 21 の出力信号の発振周波数は小さくなる。つまり、電圧制御発振器 21 は、回路 20 のノード FD に保持させるアナログ電位に応じて発振周波数を制御することができる。

#### 【 0055 】

40

トランジスタ 43 およびトランジスタ 44 にはオフ電流が非常に小さい、チャネル形成領域に酸化物半導体を有するトランジスタを用いることが好ましい。

#### 【 0056 】

当該トランジスタを用いることで、トランジスタ 44 をオフ状態とした場合、ノード FD の電位は長時間保持される。また、トランジスタ 43 をオフ状態とした場合、回路 20 の出力端子 OUT の電位（リングオシレータ 22 における後段の回路 20 の入力端子 IN の電位）は、長期間保持される。

#### 【 0057 】

したがって、電圧制御発振器 21 が発振しているときにノード FD の電位を "L" レベルとして発振を停止させた場合、各回路 20 の入力端子 IN および出力端子 OUT に発振を

50

停止させる直前の電圧が保持される。例えば、1段目の回路20の出力端子OUT(2段目の回路20の入力端子IN)に”H”レベルの電位が保持され、2段目の回路20の出力端子OUT(3段目の回路20の入力端子IN)に”L”レベルの電位が保持される。そのため、電圧制御発振器21は、ノードFDの電位を”L”レベルとして発振を長時間停止させた場合でも、再びノードFDの電位を”H”レベルとすることで、各回路20の入力端子INおよび出力端子OUTに保持された電圧に従って速やかに発振を開始することができる。

#### 【0058】

電圧制御発振器21の発振を停止する場合には、配線71(VDD)から電源電圧VDD(”H”レベル)の供給を停止することが有効である。具体的には、配線71(VDD)の電圧レベルを”H”レベルから”L”レベル(0VまたはGND電位など)に変化させる。このとき、インバータ40は機能しなくなるため、回路20は信号を伝達できなくなる。すなわち、電圧制御発振器21は発振を停止する。

10

#### 【0059】

また、配線71(VDD)の電圧レベルを”H”レベルから”L”レベルへと変化させることにより容量素子C1を介した容量結合が起こり、ノードFDの電位は”L”レベルへと低下する。すなわち、トランジスタ43は非導通となる。つまり、電源電圧VDDの供給の停止とともにトランジスタ43を非導通とすることはできる。また、トランジスタ43が非導通となると同時に、各回路20の入力端子INおよび出力端子OUTに電圧制御発振器21が発振を停止する直前の電圧が保持される。

20

#### 【0060】

配線71(VDD)に電源電圧VDDを再度供給したときには、配線71(VDD)の電圧レベルが”L”レベルから”H”レベルに変化するため、容量素子C1を介した容量結合が起こりノードFDの電位は”H”レベルに上昇する。したがって、トランジスタ43は導通し、電圧制御発振器21は発振を速やかに再開する。

#### 【0061】

なお、電圧制御発振器21の発振を停止するには、配線73(WD)を”L”レベルとし、トランジスタ44を導通させてノードFDを”L”レベルとする動作を行ってもよい。この場合、再度電圧制御発振器21を発振させる場合は、配線71(VDD)の電圧レベルは変化させず、配線73(WD)を”H”レベルとし、トランジスタ44を導通させてノードFDを”H”レベルとする動作を行えばよい。

30

#### 【0062】

図4(A)は、図2(A)に示す電圧制御発振器21に図1に示す回路20を用いた場合の駆動方法の一例を示すタイミングチャートである。VDDは配線71(VDD)の電位、WDは配線73(WD)の電位、Wは配線61(W)の電位、FDはノードFDの電位、INは特定の回路20の入力端子INの電位、OUTは特定の回路20の出力端子OUTの電位である。また、正論理を与える電圧をV1(”H”レベル)とし、負論理を与える電圧をGND(”L”レベル)とする。

#### 【0063】

時刻T0にて、配線71(VDD)に”H”レベルの電位(電源電圧VDD)、配線73(WD)にアナログ電位Vaを供給する。なお、Vaはトランジスタ43のしきい値電圧(V<sub>th</sub>)以上の値とする。

40

#### 【0064】

時刻T1にて、配線61(W)に”H”レベルの電位を供給することで、トランジスタ44が導通し、ノードFDの電位がVaとなる。これに伴ってトランジスタ43が導通するため、電圧制御発振器21は発振を開始する。ただし、初めて動作させる場合においては、回路20の入力端子INの電位が定まっていないため、発振初期に動作が安定せず不規則な信号を出力する。

#### 【0065】

時刻T2にて配線61(W)に”L”レベルの電位を供給することで、トランジスタ44

50

は非導通となり、ノードF Dにアナログ電位V aが保持される。その後、配線7 3 ( W D )には”L”レベルの電位が供給される。

#### 【0066】

時刻T 3にて、配線7 1 ( V D D )に”L”レベルの電位を供給すると、インバータ4 0が非動作となるとともに、容量素子C 1を介した容量結合によりノードF Dの電位が低下し、”L”レベルとなる。したがって、トランジスタ4 3は非導通となる。トランジスタ4 3が非導通となることで、各回路2 0の入力端子I Nおよび出力端子O U Tの電位は保持される。このとき、特定の回路2 0において、入力端子I Nには”L”レベルの電位が、出力端子O U Tには”H”レベルの電位が保持されたものとする。

#### 【0067】

時刻T 4にて、配線7 1 ( V D D )に”H”レベルの電位を供給すると、インバータ4 0が動作状態となるとともに、容量素子C 1を介した容量結合によりノードF Dの電位が昇圧され、V aとなる。したがって、トランジスタ4 3は導通する。トランジスタ4 3が導通することで、各回路2 0は保持されている入力信号に対して出力信号を出力する。すなわち、電圧制御発振器2 1は、配線7 1 ( V D D )に電源電圧V D Dが再度供給されると速やかに発振することができる。

#### 【0068】

回路2 0は、図3 ( A )に示す構成であってもよい。図3 ( A )に示す回路2 0は、トランジスタ4 1、トランジスタ4 2と、トランジスタ4 3と、トランジスタ4 4と、トランジスタ4 5と、容量素子C 1と、を有する。

#### 【0069】

図3 ( A )に示す回路2 0において、トランジスタ4 1のゲートは、トランジスタ4 2のゲートと電気的に接続される。トランジスタ4 1のソースまたはドレインの一方は、トランジスタ4 2のソースまたはドレインの一方と電気的に接続される。トランジスタ4 1のソースまたはドレインの一方は、トランジスタ4 5のソースまたはドレインの一方と電気的に接続される。トランジスタ4 5のゲートはトランジスタ4 1のソースまたはドレインの他方と電気的に接続される。トランジスタ4 5のソースまたはドレインの他方は、トランジスタ4 3のソースまたはドレインの一方と電気的に接続される。トランジスタ4 3のゲートは、トランジスタ4 4のソースまたはドレインの一方と電気的に接続される。トランジスタ4 3のゲートは、容量素子C 1の一方の電極と電気的に接続される。容量素子C 1の他方の電極は、トランジスタ4 2のソースまたはドレインの他方と電気的に接続される。

#### 【0070】

図3 ( A )に示す回路2 0は、トランジスタ4 5を有する点、トランジスタ4 5のゲートがトランジスタ4 1のソースまたはドレインの他方と電気的に接続する点、および容量素子C 1の他方の電極がトランジスタ4 2のソースまたはドレインの他方と電気的に接続する点が図1に示す回路2 0と異なる。なお、図3 ( B )に示すように、トランジスタ4 3のソースまたはドレインの一方がトランジスタ4 1のソースまたはドレインの一方と電気的に接続され、トランジスタ4 3のソースまたはドレインの他方とトランジスタ4 5のソースまたはドレインの一方が電気的に接続される構成であってもよい。

#### 【0071】

トランジスタ4 5にはオフ電流が非常に小さい、チャネル形成領域に酸化物半導体を有するトランジスタを用いることが好ましい。当該トランジスタを用いることで、トランジスタ4 5をオフ状態とした場合、回路2 0の出力端子O U Tの電位(リングオシレータ2 2における後段の回路2 0の入力端子I Nの電位)は、長期間保持される。

#### 【0072】

図3 ( A )、( B )に示す回路2 0では、インバータ4 0の出力側と回路2 0の出力端子O U Tとの間にトランジスタ4 5が設けられ、トランジスタ4 5のゲートが配線7 1 ( V D D )と電気的に接続されている。したがって、配線7 1 ( V D D )に電源電圧V D Dを供給するとインバータ4 0が動作状態となり、かつトランジスタ4 5が導通し、回路2 0

10

20

30

40

50

は入力信号に対して反転信号を出力する。すなわち、電圧制御発振器 21 は発振する。また、電源電圧 VDD の供給を停止するとインバータ 40 が非動作状態となり、かつトランジスタ 45 が非導通となるため、回路 20 の信号の伝達経路は遮断される。すなわち、電圧制御発振器 21 は発振しない。

#### 【0073】

電圧制御発振器 21 が発振しているときに電源電圧 VDD の供給を停止すると、配線 71 (VDD) の電圧レベルが "H" レベルから "L" レベルに変化する。したがって、トランジスタ 45 が非導通となり、各回路 20 の入力端子 IN および出力端子 OUT に電圧制御発振器 21 が発振を停止する直前の電圧が保持される。

#### 【0074】

配線 71 (VDD) に電源電圧 VDD を再度供給したときには、配線 71 (VDD) の電圧レベルが "L" レベルから "H" レベルに変化するため、トランジスタ 45 が導通し、電圧制御発振器 21 は発振を速やかに再開する。

#### 【0075】

図 4 (B) は図 2 (A) に示す電圧制御発振器 21 に図 3 (A) または図 3 (B) に示す回路 20 を用いた場合の駆動方法の一例を示すタイミングチャートである。

#### 【0076】

時刻 T0 にて、配線 73 (WD) にアナログ電位 Va を供給する。なお、Va はトランジスタ 43 のしきい値電圧 (Vth) 以上の値とする。

#### 【0077】

時刻 T1 にて、配線 61 (W) に "H" レベルの電位を供給することで、トランジスタ 44 が導通し、ノード FD の電位が Va となる。

#### 【0078】

時刻 T2 にて、配線 61 (W) に "L" レベルの電位を供給することで、トランジスタ 44 は非導通となり、ノード FD にアナログ電位 Va が保持される。その後、配線 73 (WD) には "L" レベルの電位が供給される。

#### 【0079】

時刻 T3 にて、配線 71 (VDD) に "H" レベルの電位 (電源電圧 VDD) を供給すると、トランジスタ 45 が導通するため、電圧制御発振器 21 は発振を開始する。ただし、初めて動作させる場合においては、回路 20 の入力端子 IN の電位が定まっていないため、発振初期に動作が安定せず不規則な信号を出力する。

#### 【0080】

時刻 T4 にて、配線 71 (VDD) に "L" レベルの電位を供給すると、トランジスタ 45 は非導通となる。トランジスタ 45 が非導通となることで、各回路 20 の入力端子 IN および出力端子 OUT の電位は保持される。

#### 【0081】

時刻 T5 にて、配線 71 (VDD) に "H" レベルの電位を供給すると、トランジスタ 45 は導通する。トランジスタ 45 が導通することで、各回路 20 は保持されている入力信号に対して出力信号を出力する。すなわち、電圧制御発振器 21 は、配線 71 (VDD) に電源電圧 VDD が再度供給されると速やかに発振することができる。

#### 【0082】

上述した回路 20 (図 1、図 3 (A)、(B)) は、ノード FD の電位を書き換えることによって異なる発振周波数の出力信号を出力することのできる構成であったが、マルチコンテキスト機能を備えた回路を電圧制御発振器 21 の信号伝達回路に用いてもよい。

#### 【0083】

マルチコンテキスト機能を有する信号伝達回路を用いることで、発振周波数の切り替えが容易になる。ここで、コンテキストとは、電圧制御発振器の発振を制御する回路構成を意味し、選択されたコンテキストに保持されたアナログ電位に従って、電圧制御発振器 21 は特定の発振周波数で発振する。

#### 【0084】

10

20

30

40

50

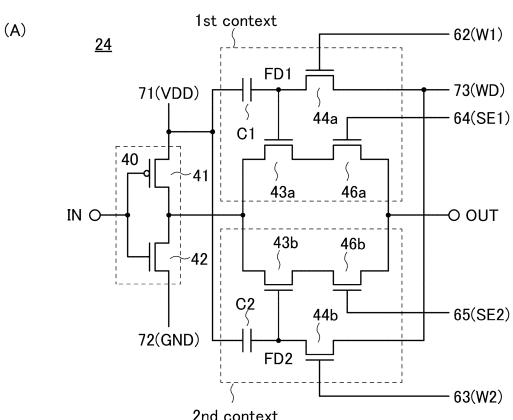

図5( A )は、2つのコンテキスト機能を備えた回路24の回路図である。回路24は、トランジスタ41、トランジスタ42と、トランジスタ43aと、トランジスタ43bと、トランジスタ44aと、トランジスタ44bと、トランジスタ46aと、トランジスタ46bと、容量素子C1と、容量素子C2と、を有する。ここで、トランジスタ41およびトランジスタ42は、インバータ40を構成する。また、トランジスタ43a、トランジスタ44a、トランジスタ46aおよび容量素子C1は、第1のコンテキストを構成する。また、トランジスタ43b、トランジスタ44b、トランジスタ46bおよび容量素子C2は、第2のコンテキストを構成する。

#### 【0085】

図5( A )に示す回路24において、トランジスタ41のゲートは、トランジスタ42のゲートと電気的に接続される。トランジスタ41のソースまたはドレインの一方は、トランジスタ42のソースまたはドレインの一方と電気的に接続される。トランジスタ41のソースまたはドレインの一方は、トランジスタ43aのソースまたはドレインの一方と電気的に接続される。トランジスタ43aのゲートは、トランジスタ44aのソースまたはドレインの一方と電気的に接続される。トランジスタ43aのソースまたはドレインの他方はトランジスタ46aのソースまたはドレインの一方と電気的に接続される。トランジスタ43aのゲートは、容量素子C1の一方の電極と電気的に接続される。容量素子C1の他方の電極は、トランジスタ41のソースまたはドレインの他方と電気的に接続される。トランジスタ41のソースまたはドレインの一方は、トランジスタ43bのソースまたはドレインの一方と電気的に接続される。トランジスタ43bのゲートは、トランジスタ44bのソースまたはドレインの一方と電気的に接続される。トランジスタ43bのソースまたはドレインの他方はトランジスタ46bのソースまたはドレインの一方と電気的に接続される。トランジスタ43bのゲートは、容量素子C2の一方の電極と電気的に接続される。容量素子C2の他方の電極は、トランジスタ41のソースまたはドレインの他方と電気的に接続される。トランジスタ46aのソースまたはドレインの他方は、トランジスタ46bのソースまたはドレインの他方と電気的に接続される。

#### 【0086】

なお、図5( B )に示すように、トランジスタ46aをインバータ40の出力側とトランジスタ43aとの間に設け、トランジスタ46bをインバータ40の出力側とトランジスタ43bとの間に設けてもよい。この場合、トランジスタ43aのソースまたはドレインの他方とトランジスタ43bのソースまたはドレインの他方は電気的に接続される。

#### 【0087】

ここで、トランジスタ43aのゲート、容量素子C1の一方の電極、トランジスタ44aのソースまたはドレインの一方が接続される配線をノードF D 1とする。トランジスタ43bのゲート、容量素子C2の一方の電極、トランジスタ44bのソースまたはドレインの一方が接続される配線をノードF D 2とする。また、トランジスタ41のゲートおよびトランジスタ42のゲートが電気的に接続される配線は、回路24の入力端子I Nとして機能する。また、図5( A )において、トランジスタ46aのソースまたはドレインの他方およびトランジスタ46bのソースまたはドレインの他方と電気的に接続される配線は、回路24の出力端子O U Tとして機能する。また、図5( B )において、トランジスタ43aのソースまたはドレインの他方およびトランジスタ43bのソースまたはドレインの他方と電気的に接続される配線は、回路24の出力端子O U Tとして機能する。

#### 【0088】

図5( A )、( B )において、トランジスタ41のソースまたはドレインの他方は、配線71( V D D )と電気的に接続される。トランジスタ42のソースまたはドレインの他方は、配線72( G N D )と電気的に接続される。トランジスタ44aのソースまたはドレインの他方は、配線73( W D )と電気的に接続される。トランジスタ44aのゲートは、配線62( W 1 )と電気的に接続される。トランジスタ46aのゲートは、配線64( S E 1 )と電気的に接続される。トランジスタ44bのソースまたはドレインの他方は、配線73( W D )と電気的に接続される。トランジスタ44bのゲートは、配線63( W

10

20

30

40

50

2) と電気的に接続される。トランジスタ 46b のゲートは、配線 65 (SE2) と電気的に接続される。

#### 【0089】

配線 62 (W1) は、トランジスタ 44a の導通を制御する信号線として機能させることができる。配線 63 (W2) は、トランジスタ 44b の導通を制御する信号線として機能させることができる。配線 64 (SE1) は、トランジスタ 46a の導通を制御する信号線として機能させることができる。配線 65 (SE2) は、トランジスタ 46b の導通を制御する信号線として機能させることができる。配線 73 (WD) は、ノード FD1 またはノード FD2 に所望の電位を供給するための信号配線として機能させることができる。

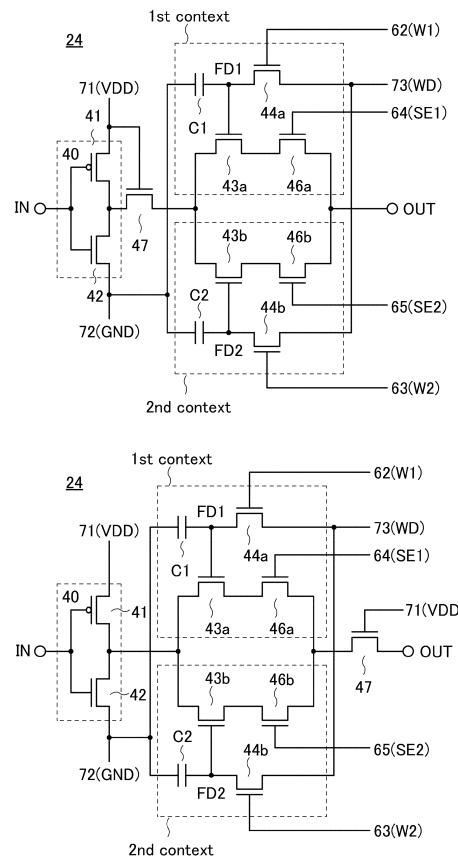

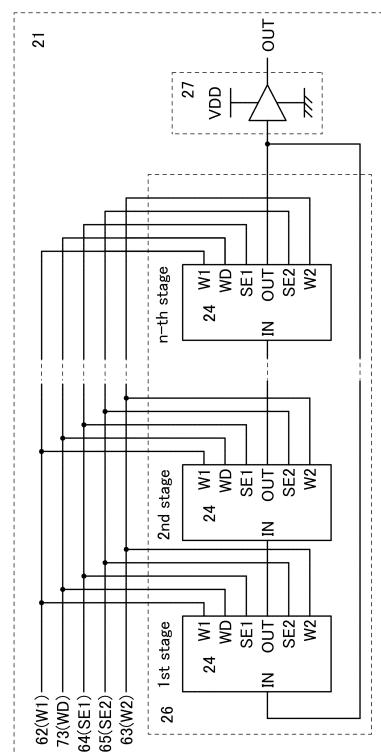

#### 【0090】

図 7 は、回路 24 を適用することのできる電圧制御発振器 21 であり、n 段 (n は奇数) の回路 24 を有するリングオシレータ 26 と、バッファ回路 27 を有する。前段の回路 24 の出力端子 OUT は後段の回路 24 の入力端子 IN と電気的に接続され、最終段の回路 24 の出力端子 OUT は 1 段目の回路 24 の入力端子 IN およびバッファ回路 27 の入力端子と電気的に接続される。なお、バッファ回路 27 を設けない構成とすることもできる。

#### 【0091】

図 5 (A)、(B) に示す回路 24 の動作、および当該回路 24 を適用した図 7 に示す電圧制御発振器 21 の動作を説明する。まず、トランジスタ 44a を導通させ、配線 73 (WD) の電位 Vb をノード FD1 に書き込む。その後、トランジスタ 44a を非導通として、ノード FD1 にアナログ電位 Vb を保持する。また、配線 73 (WD) の電位を Vc に変化させた後、トランジスタ 44b を導通させ、配線 73 (WD) の電位 Vc をノード FD2 に書き込む。その後、トランジスタ 44b を非導通として、ノード FD2 にアナログ電位 Vc を保持する。

#### 【0092】

トランジスタ 43a は、ノード FD1 に保持したアナログデータに応じて導通、非導通が制御される。また、トランジスタ 43b は、ノード FD2 に保持したアナログデータに応じて導通、非導通が制御される。

#### 【0093】

トランジスタ 43a のオン電流は、ノード FD1 に保持したアナログデータに応じて制御される。また、トランジスタ 43b のオン電流は、ノード FD2 に保持したアナログデータに応じて制御される。第 1 のコンテキストにおいて、ノード FD1 に比較的高いアナログ電位が与えられているとき、トランジスタ 43a のオン抵抗は低い値をとる。すなわち、電圧制御発振器 21 の出力信号の発振周波数は大きくなる。一方、ノード FD1 に比較的低いアナログ電位が与えられているとき、トランジスタ 43a のオン抵抗は高い値をとる。すなわち、電圧制御発振器 21 の出力信号の発振周波数は小さくなる。第 2 のコンテキストも同様にノード FD2 の電位に応じて、電圧制御発振器 21 の出力信号の発振周波数が変化する。

#### 【0094】

第 1 のコンテキストにおいて、トランジスタ 46a は配線 64 (SE1) から入力される信号により、導通、非導通が制御される。配線 64 (SE1) の電位が "H" レベルのとき、トランジスタ 46a は導通する。したがって、トランジスタ 43a がノード FD1 の電位 Vb に応じたオン状態であって、かつトランジスタ 46a が導通する場合、回路 24 は入力信号に対して反転信号を出力する。すなわち、電圧制御発振器 21 は、第 1 の発振周波数で発振する。一方、トランジスタ 46a が非導通の場合、回路 24 の信号の伝達経路は遮断される。すなわち、電圧制御発振器 21 は発振しない。

#### 【0095】

また、第 2 のコンテキストにおいて、トランジスタ 46b は配線 65 (SE2) から入力される信号により、導通、非導通が制御される。配線 65 (SE2) の電位が "H" レベルのとき、トランジスタ 46b は導通する。したがって、トランジスタ 43b がノード FD2 の電位 Vc に応じたオン状態であって、かつトランジスタ 46b が導通する場合、回路 24 は入力信号に対して反転信号を出力する。すなわち、電圧制御発振器 21 は、第 2 の発振周波数で発振する。

10

20

30

40

50

D 2 の電位 V c に応じたオン状態であって、かつトランジスタ 4 6 b が導通する場合、回路 2 4 は入力信号に対して反転信号を出力する。すなわち、電圧制御発振器 2 1 は、第 2 の発振周波数で発振する。一方、トランジスタ 4 6 b が非導通の場合、回路 2 4 の信号の伝達経路は遮断される。すなわち、電圧制御発振器 2 1 は発振しない。

#### 【 0 0 9 6 】

つまり、第 1 のコンテキストまたは第 2 のコンテキストのいずれか一方を選択することで、電圧制御発振器 2 1 は周波数の異なる第 1 の発振周波数または第 2 の発振周波数で発振することができる。第 1 のコンテキストを選択するには、配線 6 4 ( S E 1 ) の電位を " H " レベル、配線 6 5 ( S E 2 ) の電位を " L " レベルとすればよい。また、第 2 のコンテキストを選択するには、配線 6 4 ( S E 1 ) の電位を " L " レベル、配線 6 5 ( S E 2 ) の電位を " H " レベルとすればよい。10

#### 【 0 0 9 7 】

トランジスタ 4 3 a、トランジスタ 4 3 b、トランジスタ 4 6 a およびトランジスタ 4 6 b にはオフ電流が非常に小さい、チャネル形成領域に酸化物半導体を有するトランジスタを用いることが好ましい。当該トランジスタを用いることで、トランジスタ 4 6 a、トランジスタ 4 6 b をオフ状態とした場合、回路 2 4 の出力端子 O U T の電位（リングオシレータ 2 6 における後段の回路 2 4 の入力端子 I N の電位）は、長期間保持される。

#### 【 0 0 9 8 】

したがって、第 1 のコンテキストを選択した場合、電圧制御発振器 2 1 が第 1 の発振周波数で発振しているときにトランジスタ 4 6 a を非導通として電圧制御発振器 2 1 の発振を停止させると、各回路 2 4 の入力端子 I N および出力端子 O U T に電圧制御発振器 2 1 が発振を停止する直前の電圧が保持される。そのため、電圧制御発振器 2 1 は、トランジスタ 4 6 a を非導通として発振を長時間停止させた場合でも、再びトランジスタ 4 6 a を導通することで、各回路 2 4 の入力端子 I N および出力端子 O U T に保持された電圧に従つて速やかに第 1 の発振周波数で発振を開始することができる。同様に第 2 のコンテキストを選択した場合も、第 2 の発振周波数で発振しているときに、電圧制御発振器 2 1 の発振を長時間停止させた場合であっても、速やかに第 2 の発振周波数で発振を開始することができる。20

#### 【 0 0 9 9 】

電圧制御発振器 2 1 の発振を停止する場合には、配線 7 1 ( V D D ) からの電源電圧 V D D (" H " レベル) の供給を停止してもよい。具体的には、配線 7 1 ( V D D ) の電圧レベルを " H " レベルから " L " レベル ( 0 V または G N D 電位など) に変化させる。このとき、インバータ 4 0 は機能しなくなるため、回路 2 4 は信号を伝達できなくなる。すなわち、電圧制御発振器 2 1 は発振を停止する。30

#### 【 0 1 0 0 】

また、第 1 のコンテキストを選択した場合において、配線 7 1 ( V D D ) の電圧レベルを " H " レベルから " L " レベルへと変化させることにより容量素子 C 1 を介した容量結合が起こり、ノード F D 1 の電位は " L " レベルへと低下する。すなわち、トランジスタ 4 3 a は非導通となる。つまり、電源電圧 V D D の供給の停止とともにトランジスタ 4 3 a を非導通とすることができます。また、トランジスタ 4 3 a が非導通となると同時に各回路 2 4 の入力端子 I N および出力端子 O U T に、第 1 の発振周波数で発振している電圧制御発振器 2 1 が発振を停止する直前の電圧が保持される。40

#### 【 0 1 0 1 】

配線 7 1 ( V D D ) に電源電圧 V D D を再度供給したときには、配線 7 1 ( V D D ) の電圧レベルが " L " レベルから " H " レベルに変化するため、容量素子 C 1 を介した容量結合が起こりノード F D 1 の電位は " H " レベルに上昇する。したがって、トランジスタ 4 3 a は導通し、電圧制御発振器 2 1 は第 1 の発振周波数で発振を速やかに再開する。同様に第 2 のコンテキストを選択した場合も、各回路 2 4 の入力端子 I N および出力端子 O U T に第 2 の発振周波数で発振している電圧制御発振器 2 1 が発振を停止する直前の電圧を保持することができ、電源電圧 V D D を再度供給したときに第 2 の発振周波数で発振を速50

やかに再開することができる。

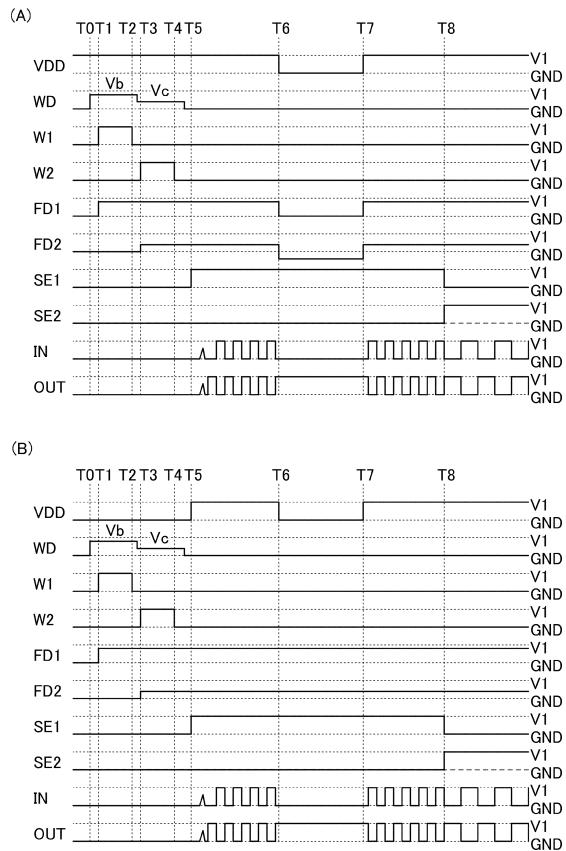

**【0102】**

図8(A)は、図7に示す電圧制御発振器21に図5(A)または図5(B)に示す回路24を用いた場合の駆動方法の一例を示すタイミングチャートである。VDDは配線71(VDD)の電位、WDは配線73(WD)の電位、W1は配線62(W1)の電位、W2は配線63(W2)の電位、FD1はノードFD1の電位、FD2はノードFD2の電位、SE1は配線64(SE1)の電位、SE2は配線65(SE2)の電位、INは特定の回路24の入力端子INの電位、OUTは特定の回路24の出力端子OUTの電位である。また、正論理を与える電圧をV1("H"レベル)とし、負論理を与える電圧をGND("L"レベル)とする。

10

**【0103】**

時刻T0にて、配線71(VDD)に"H"レベルの電位(電源電圧VDD)、配線73(WD)にアナログ電位Vbを供給する。なお、Vbはトランジスタ43aおよびトランジスタ43bのしきい値電圧(Vth)以上の値とする。

**【0104】**

時刻T1にて、配線62(W1)に"H"レベルの電位を供給することで、トランジスタ44aが導通し、ノードFD1の電位がVbとなる。

**【0105】**

時刻T2にて、配線62(W1)に"L"レベルの電位を供給することで、トランジスタ44aは非導通となり、ノードFD1にアナログ電位Vbが保持される。その後、配線73(WD)にはアナログ電位Vcが供給される。ここでは、Vcはトランジスタ43aおよびトランジスタ43bのしきい値電圧(Vth)以上であってVbより小さい値とする。

20

**【0106】**

時刻T3にて、配線63(W2)に"H"レベルの電位を供給することで、トランジスタ44bが導通し、ノードFD2の電位がVcとなる。

**【0107】**

時刻T4にて、配線63(W2)に"L"レベルの電位を供給することで、トランジスタ44bは非導通となり、ノードFD2にアナログ電位Vcが保持される。その後、配線73(WD)には"L"レベルの電位が供給される。

30

**【0108】**

時刻T5にて、配線64(SE1)に"H"レベルの電位を供給するとトランジスタ46aは導通し、回路24は入力信号に対して出力信号を出力する。すなわち、電圧制御発振器21が第1の発振周波数で発振し始める。ただし、初めて動作させる場合においては、回路24の入力端子INの電位が定まっていないため、発振初期に動作が安定せず不規則な信号を出力する。このとき、配線64(SE1)に"H"レベルの電位が供給され、配線65(SE2)に"L"レベルの電位が供給されることで、第1のコンテキスト回路が選択された状態となる。

**【0109】**

時刻T6にて、配線71(VDD)に"L"レベルの電位が供給されると、インバータ40が非動作となり、第1の発振周波数で発振している電圧制御発振器21の発振が停止するとともに、容量素子C1を介した容量結合によりノードFD1の電位が低下し、"L"レベルとなる。したがって、トランジスタ43aは非導通となる。トランジスタ43aが非導通となることで、各回路24の入力端子INおよび出力端子OUTの電位は保持される。

40

**【0110】**

時刻T7にて、配線71(VDD)に"H"レベルの電位が供給されると、容量素子C1を介した容量結合によりノードFD1の電位が昇圧され、Vbとなる。したがって、トランジスタ43aは導通する。トランジスタ43aが導通することで、各回路24は保持されている入力信号に対して出力信号を出力する。すなわち、電圧制御発振器21は配線7

50

1 (VDD) に電源電圧 VDD が再度供給されると、第 1 の発振周波数で速やかに発振することができる。

#### 【0111】

時刻 T8 にて、配線 64 (SE1) に "L" レベルの電位を供給し、配線 65 (SE2) に "H" レベルの電位を供給すると、トランジスタ 46a は非導通となり、トランジスタ 46b は導通状態となる。すなわち、第 2 のコンテキスト回路が選択された状態となる。すなわち、電圧制御発振器 21 は、第 2 の発振周波数で発振する。

#### 【0112】

このとき、ノード FD2 に保持されている電位 Vc は、ノード FD1 に保持されている電位 Vb より小さいため、トランジスタ 43b のオン抵抗はトランジスタ 43a のオン抵抗よりも大きくなる。したがって、第 2 の発振周波数は、第 1 の発振周波数よりも小さくなる。

10

#### 【0113】

また、図 7 に示す電圧制御発振器 21 の信号伝達回路に用いることのできるマルチコンテキスト機能を備えた回路は、図 6 (A)、(B) に示す回路 24 であってもよい。

#### 【0114】

図 6 (A) は、2つのコンテキスト機能を備えた回路 24 の回路図である。回路 24 は、トランジスタ 41、トランジスタ 42 と、トランジスタ 43a と、トランジスタ 43b と、トランジスタ 44a と、トランジスタ 44b と、トランジスタ 46a と、トランジスタ 46b と、トランジスタ 47 と、容量素子 C1 と、容量素子 C2 と、を有する。ここで、トランジスタ 41 およびトランジスタ 42 は、インバータ 40 を構成する。また、トランジスタ 43a、トランジスタ 44a、トランジスタ 46a および容量素子 C1 は、第 1 のコンテキストを構成する。また、トランジスタ 43b、トランジスタ 44b、トランジスタ 46b および容量素子 C2 は、第 2 のコンテキストを構成する。

20

#### 【0115】

図 6 (A) に示す回路 24 は、トランジスタ 47 を有する点、トランジスタ 47 のゲートがトランジスタ 41 のソースまたはドレインの一方と電気的に接続する点、および容量素子 C1 の他方の電極および容量素子 C2 の他方の電極がトランジスタ 42 のソースまたはドレインの他方と電気的に接続する点が図 5 (A) に示す回路 24 と異なる。

#### 【0116】

30

なお、図 6 (A) では、インバータ 40 と、第 1 のコンテキストおよび第 2 のコンテキストとの間にトランジスタ 47 を設ける構成であるが、図 6 (B) に示すように第 1 のコンテキストおよび第 2 のコンテキストと、出力端子 OUT との間にトランジスタ 47 を設ける構成であってもよい。

#### 【0117】

トランジスタ 47 にはオフ電流が非常に小さい、チャネル形成領域に酸化物半導体を有するトランジスタを用いることが好ましい。当該トランジスタを用いることで、トランジスタ 47 をオフ状態とした場合、回路 24 の出力端子 OUT の電位 (リングオシレータ 26 における後段の回路 24 の入力端子 IN の電位) は、長期間保持される。

#### 【0118】

40

図 6 (A)、(B) に示す回路 24 では、インバータ 40 の出力側と回路 24 の出力端子 OUT との間にトランジスタ 47 が設けられ、トランジスタ 47 のゲートが配線 71 (VDD) と電気的に接続されている。したがって、配線 71 (VDD) に電源電圧 VDD を供給するとインバータ 40 が動作状態となり、かつトランジスタ 47 が導通する。そして、トランジスタ 46a またはトランジスタ 46b のいずれか一方が導通状態であれば、回路 24 は入力信号に対して反転信号を出力する。すなわち、電圧制御発振器 21 は発振する。また、電源電圧 VDD の供給を停止するとインバータ 40 が非動作状態となり、かつトランジスタ 47 が非導通となるため、回路 24 の信号の伝達経路は遮断される。すなわち、電圧制御発振器 21 は発振しない。

#### 【0119】

50

電圧制御発振器 2 1 が発振しているときに電源電圧 V D D の供給を停止すると、配線 7 1 ( V D D ) の電圧レベルが " H " レベルから " L " レベルに変化する。したがって、トランジスタ 4 7 が非導通となり、各回路 2 4 の入力端子 I N および出力端子 O U T に電圧制御発振器 2 1 が発振を停止する直前の電圧が保持される。

#### 【 0 1 2 0 】

配線 7 1 ( V D D ) に電源電圧 V D D を再度供給したときには、配線 7 1 ( V D D ) の電圧レベルが " L " レベルから " H " レベルに変化するため、トランジスタ 4 7 が導通し、電圧制御発振器 2 1 は発振を速やかに再開する。

#### 【 0 1 2 1 】

図 8 ( B ) は図 7 に示す電圧制御発振器 2 1 に図 6 ( A ) または図 6 ( B ) に示す回路 2 4 を用いた場合の駆動方法の一例を示すタイミングチャートである。10

#### 【 0 1 2 2 】

時刻 T 0 にて、配線 7 3 ( W D ) にアナログ電位 V b を供給する。なお、 V b はトランジスタ 4 3 a およびトランジスタ 4 3 b のしきい値電圧 ( V t h ) 以上の値とする。

#### 【 0 1 2 3 】

時刻 T 1 にて、配線 6 2 ( W 1 ) に " H " レベルの電位を供給することで、トランジスタ 4 4 a が導通し、ノード F D 1 の電位が V b となる。

#### 【 0 1 2 4 】

時刻 T 2 にて、配線 6 2 ( W 1 ) に " L " レベルの電位を供給することで、トランジスタ 4 4 a は非導通となり、ノード F D 1 にアナログ電位 V b が保持される。その後、配線 7 3 ( W D ) にはアナログ電位 V c が供給される。ここでは、 V c はトランジスタ 4 3 a およびトランジスタ 4 3 b のしきい値電圧 ( V t h ) 以上であって V b より小さい値とする。20

#### 【 0 1 2 5 】

時刻 T 3 にて、配線 6 3 ( W 2 ) に " H " レベルの電位を供給することで、トランジスタ 4 4 b が導通し、ノード F D 2 の電位が V c となる。

#### 【 0 1 2 6 】

時刻 T 4 にて、配線 6 3 ( W 2 ) に " L " レベルの電位を供給することで、トランジスタ 4 4 b は非導通となり、ノード F D 2 にアナログ電位 V c が保持される。その後、配線 7 3 ( W D ) には " L " レベルの電位が供給される。30

#### 【 0 1 2 7 】

時刻 T 5 にて、配線 7 1 ( V D D ) に " H " レベルの電位 ( 電源電圧 V D D ) 、配線 6 4 ( S E 1 ) に " H " レベルの電位を供給すると、トランジスタ 4 7 およびトランジスタ 4 6 a は導通し、回路 2 4 は入力信号に対して出力信号を出力する。すなわち、電圧制御発振器 2 1 が第 1 の発振周波数で発振し始める。ただし、初めて動作させる場合においては、回路 2 4 の入力端子 I N の電位が定まっていないため、発振初期に動作が安定せず不規則な信号を出力する。このとき、配線 6 4 ( S E 1 ) に " H " レベルの電位が供給され、配線 6 5 ( S E 2 ) に " L " レベルの電位が供給されることで、第 1 のコンテキスト回路が選択された状態となる。

#### 【 0 1 2 8 】

時刻 T 6 にて、配線 7 1 ( V D D ) に " L " レベルの電位が供給されると、インバータ 4 0 が非動作となり、第 1 の発振周波数で発振している電圧制御発振器 2 1 の発振が停止するとともに、トランジスタ 4 7 は非導通となる。トランジスタ 4 7 が非導通となることで、各回路 2 4 の入力端子 I N および出力端子 O U T の電位は保持される。40

#### 【 0 1 2 9 】

時刻 T 7 にて、配線 7 1 ( V D D ) に " H " レベルの電位が供給されると、トランジスタ 4 7 は導通する。トランジスタ 4 7 が導通することで、各回路 2 4 は保持されている入力信号に対して出力信号を出力する。すなわち、電圧制御発振器 2 1 は、配線 7 1 ( V D D ) に電源電圧 V D D が再度供給されると、第 1 の発振周波数で速やかに発振することができる。50

**【 0 1 3 0 】**

時刻 T 8 にて、配線 6 4 ( S E 1 ) に " L " レベルの電位を供給し、配線 6 5 ( S E 2 ) に " H " レベルの電位を供給すると、トランジスタ 4 6 a は非導通となり、トランジスタ 4 6 b は導通状態となる。すなわち、第 2 のコンテキスト回路が選択された状態となり、電圧制御発振器 2 1 は第 2 の発振周波数で発振する。

**【 0 1 3 1 】**

上述した図 1 、図 3 ( A ) 、 ( B ) 、図 5 ( A ) 、 ( B ) 、図 6 ( A ) 、 ( B ) の構成、および動作方法を用いることで、電圧制御発振器 2 1 は一時的に電源電圧の供給を停止しても電源電圧の供給再開時に速やかに発振することができる。

**【 0 1 3 2 】**

また、回路 2 0 および回路 2 4 に用いるトランジスタは、バックゲートを設けた構成であってもよい。例えば、図 1 0 ( A ) 、 ( B ) は、図 1 に示す回路 2 0 のトランジスタ 4 3 およびトランジスタ 4 4 にバックゲートを設けた構成である。図 1 0 ( A ) は、当該バックゲートに定電位を印加する構成であり、しきい値電圧を制御することができる。図 1 0 ( A ) では、一例としてバックゲートが低電位を供給する配線 7 2 ( G N D ) と接続する例を示しているが、その他の配線に接続する構成であってもよい。また、図 1 0 ( B ) はフロントゲートと同じ電位がバックゲートに印加される構成であり、オン電流を増加させ、かつオフ電流を減少させることができる。また、所望のトランジスタが適切な電気特性を有するように、図 1 0 ( A ) および図 1 0 ( B ) の構成などを組み合わせた構成としてもよい。なお、バックゲートが設けられないトランジスタがあってもよい。また、トランジスタにバックゲートを設ける構成は、図 3 ( A ) 、 ( B ) 、図 5 ( A ) 、 ( B ) 、図 6 ( A ) 、 ( B ) の構成にも適用することができる。

10

**【 0 1 3 3 】**

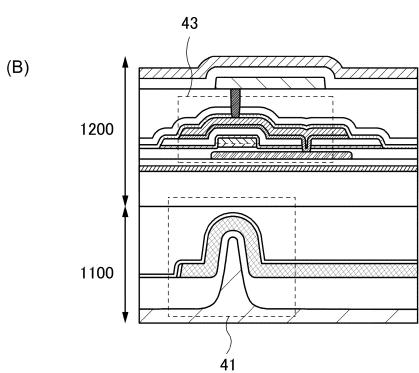

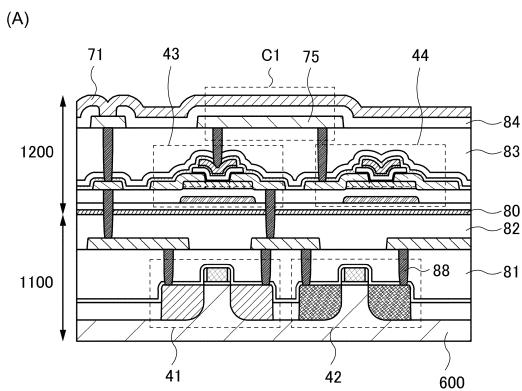

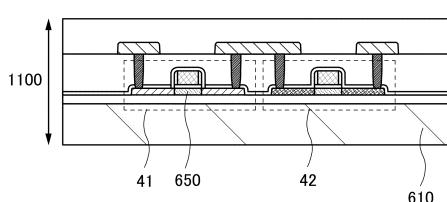

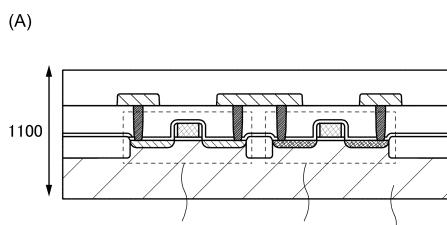

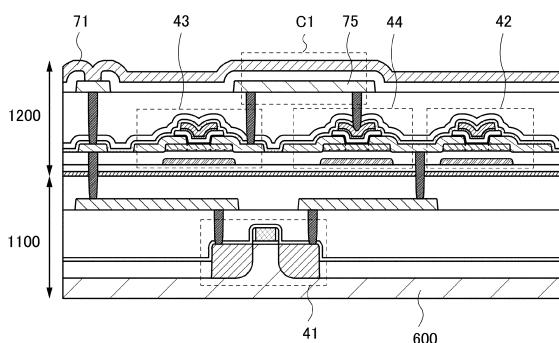

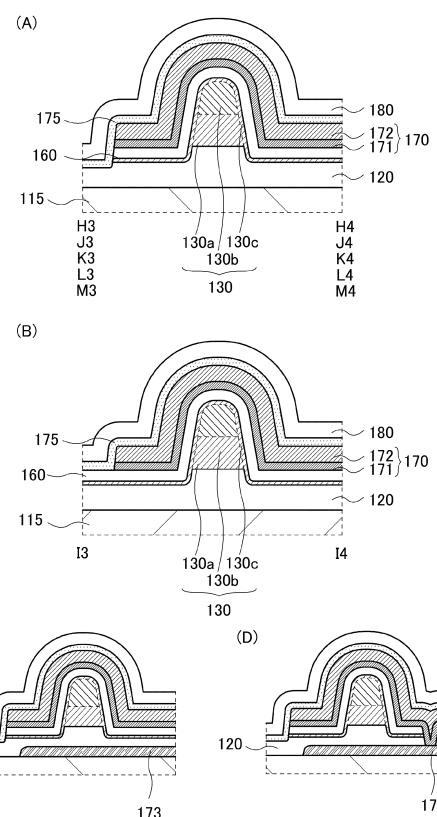

本発明の一態様の発振器の具体的な構成例について、図面を参照して説明する。図 1 1 ( A ) 、 ( B ) は、図 1 に示す回路 2 0 におけるトランジスタ 4 1 、トランジスタ 4 2 、トランジスタ 4 3 、トランジスタ 4 4 および容量素子 C 1 の具体的な接続形態の一例を示している。図 1 1 ( A ) はトランジスタのチャネル長方向を表す断面図であり、図 1 1 ( B ) はトランジスタのチャネル幅方向を表す断面図である。

**【 0 1 3 4 】**

トランジスタ 4 1 およびトランジスタ 4 2 は、高速動作と C M O S 回路での構成を両立させるため、シリコンを用いたトランジスタ（以下、S i トランジスタ）を用いて作製することが好ましい。例えば、基板 6 0 0 をシリコン基板とし、基板 6 0 0 にトランジスタ 4 1 およびトランジスタ 4 2 を形成することができる。また、トランジスタ 4 3 およびトランジスタ 4 4 は、オフ電流が低いなどの理由から酸化物半導体を用いたトランジスタ（以下、O S トランジスタ）を用いて作製することが好ましい。

30

**【 0 1 3 5 】**

基板 6 0 0 はバルクのシリコン基板に限らず、ゲルマニウム、シリコンゲルマニウム、炭化シリコン、ガリウムヒ素、アルミニウムガリウムヒ素、インジウムリン、窒化ガリウム、有機半導体を材料とする基板を用いることもできる。

**【 0 1 3 6 】**

したがって、図 1 1 ( A ) に示すように、トランジスタ 4 1 およびトランジスタ 4 2 が設けられる層 1 1 0 0 と、トランジスタ 4 3 およびトランジスタ 4 4 が設けられる層 1 2 0 0 との積層構成とすることができます。当該構成とすることで、発振器の面積を小さくすることができる。

40

**【 0 1 3 7 】**

容量素子 C 1 は、例えば、トランジスタ 4 3 のゲートとトランジスタ 4 4 のソースまたはドレインの一方を接続する配線 7 5 を一方の電極、配線 7 1 ( V D D ) を他方の電極、絶縁層 8 4 を誘電体として、層 1 2 0 0 に設けることができる。絶縁層 8 4 には、例えば、酸化シリコン膜、酸化窒化シリコン膜などの無機絶縁膜を用いることができる。なお、容量素子 C 1 は、層 1 1 0 0 に設けてもよい。

50

## 【0138】

本実施の形態で説明する断面図において、配線、電極およびコンタクトプラグ（導電体88）を個別の要素として図示しているが、それらが電気的に接続している場合においては、同一の要素として設けられる場合もある。また、配線と電極が導電体88を介して接続される形態は一例であり、電極が配線と直接接続される場合もある。

## 【0139】

各要素上には保護膜、層間絶縁膜または平坦化膜としての機能を有する絶縁層81乃至絶縁層83等が設けられる。例えば、絶縁層81乃至絶縁層83等は、酸化シリコン膜、酸化窒化シリコン膜などの無機絶縁膜を用いることができる。または、アクリル樹脂、ポリイミド樹脂などの有機絶縁膜などを用いてもよい。絶縁層81乃至絶縁層83等の上面は、必要に応じてCMP（Chemical Mechanical Polishing）法等で平坦化処理を行ってもよい。10

## 【0140】

なお、図面に示される配線等の一部が設けられない場合や、図面に示されない配線等やトランジスタ等が各層に含まれる場合もある。また、図面に示されない層が当該積層構造に含まれる場合もある。また、図面に示される層の一部が含まれない場合もある。

## 【0141】

図11（A）において、トランジスタ43およびトランジスタ44はバックゲートを有する形態を例示しているがバックゲートを有さない形態であってもよい。または、一部のトランジスタ、例えばトランジスタ43のみにバックゲートを有するような形態であってもよい。当該バックゲートは、対向して設けられるトランジスタのフロントゲートと電気的に接続する場合がある。または、当該バックゲートにフロントゲートとは異なる固定電位が供給される場合がある。なお、当該バックゲート有無に関する形態は、本実施の形態で説明する他の回路の構成にも適用することができる。20

## 【0142】

ここで、図11（A）、（B）において、Siトランジスタはフィン型の構成を例示しているが、図12（A）に示すようにプレーナー型であってもよい。または、図12（B）に示すように、シリコン薄膜の活性層650を有するトランジスタであってもよい。また、活性層650は、多結晶シリコンやSOI（Silicon on Insulator）の単結晶シリコンとすることができる。また、図12（B）の構成において、基板610にはガラス基板などを用いることができる。30

## 【0143】

図11（A）、（B）に示すように、酸化物半導体を有するトランジスタ（OSトランジスタ）が形成される領域と、Siトランジスタが形成される領域との間には絶縁層80が設けられる。

## 【0144】

トランジスタ41およびトランジスタ42の活性領域近傍に設けられる絶縁層中の水素はシリコンのダングリングボンドを終端する。したがって、当該水素はトランジスタ41およびトランジスタ42の信頼性を向上させる効果がある。一方、トランジスタ43等の活性層である酸化物半導体層の近傍に設けられる絶縁層中の水素は、酸化物半導体層中にキャリアを生成する要因の一つとなる。そのため、当該水素はトランジスタ43等の信頼性を低下させる要因となる場合がある。したがって、シリコン系半導体材料を用いたトランジスタを有する一方の層と、OSトランジスタを有する他方の層を積層する場合、これらの間に水素の拡散を防止する機能を有する絶縁層80を設けることが好ましい。絶縁層80により、一方の層に水素を閉じ込めてトランジスタ41およびトランジスタ42の信頼性が向上することができる。また、一方の層から他方の層への水素の拡散が抑制されることでトランジスタ41等の信頼性も向上させることができる。40

## 【0145】

絶縁層80としては、例えば、酸化アルミニウム、酸化窒化アルミニウム、酸化ガリウム、酸化窒化ガリウム、酸化イットリウム、酸化窒化イットリウム、酸化ハフニウム、酸化

窒化ハフニウム、イットリア安定化ジルコニア(YSZ)等を用いることができる。

**【0146】**

また、本発明の一態様の発振器は、図13に示す構成とすることができます。図13に示す発振器は図11(A)に示す発振器の変形例であり、OSトランジスタおよびSiトランジスタでCMOSインバータを構成する例を図示している。

**【0147】**

ここで、層1100に設けるSiトランジスタであるトランジスタ41はp-ch型とし、層1200に設けるOSトランジスタであるトランジスタ42はn-ch型とする。p-ch型トランジスタのみを基板600に設けることで、ウェル形成やn型不純物層形成など工程を省くことができる。

10

**【0148】**

図13に示す発振器において、トランジスタ42は、層1200に形成するトランジスタ43およびトランジスタ44と同一の工程で作製することができる。したがって、発振器の製造工程を簡略化することができる。また、OSトランジスタは極めてオフ電流が低いため、静的な消費電力が極めて少ないCMOS回路を構成することができる。

**【0149】**

なお、本実施の形態における発振器が有するトランジスタの構成は一例である。したがって、例えば、トランジスタ41およびトランジスタ42の両方または一方を活性層に酸化物半導体層を有するトランジスタで構成することもできる。また、トランジスタ43およびトランジスタ44の両方または一方を活性領域または活性層にシリコン等を有するトランジスタで構成することもできる。

20

**【0150】**

なお、本実施の形態において、本発明の一態様について述べた。または、他の実施の形態において、本発明の一態様について述べる。ただし、本発明の一態様は、これらに限定されない。つまり、本実施の形態および他の実施の形態では、様々な発明の態様が記載されているため、本発明の一態様は、特定の態様に限定されない。例えば、本発明の一態様として、発振器に適用した場合の例を示したが、本発明の一態様は、これに限定されない。場合によっては、または、状況に応じて、本発明の一態様は、発振器に適用しなくてもよい。例えば、本発明の一態様は、別の機能を有する半導体装置に適用してもよい。例えば、本発明の一態様として、トランジスタのチャネル形成領域、ソースドレイン領域などが、酸化物半導体を有する場合の例を示したが、本発明の一態様は、これに限定されない。場合によっては、または、状況に応じて、本発明の一態様における様々なトランジスタ、トランジスタのチャネル形成領域、または、トランジスタのソースドレイン領域などは、様々な半導体を有していてもよい。場合によっては、または、状況に応じて、本発明の一態様における様々なトランジスタ、トランジスタのチャネル形成領域、または、トランジスタのソースドレイン領域などは、例えば、シリコン、ゲルマニウム、シリコンゲルマニウム、炭化シリコン、ガリウムヒ素、アルミニウムガリウムヒ素、インジウムリン、窒化ガリウム、または、有機半導体などの少なくとも一つを有していてもよい。または例えば、場合によっては、または、状況に応じて、本発明の一態様における様々なトランジスタ、トランジスタのチャネル形成領域、または、トランジスタのソースドレイン領域などは、酸化物半導体を有していないなくてもよい。

30

**【0151】**

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

**【0152】**

(実施の形態2)

本実施の形態では、本発明の一態様に用いることのできるOSトランジスタについて図面を用いて説明する。なお、本実施の形態における図面では、明瞭化のために一部の要素を拡大、縮小、または省略して図示している。

**【0153】**

40

50

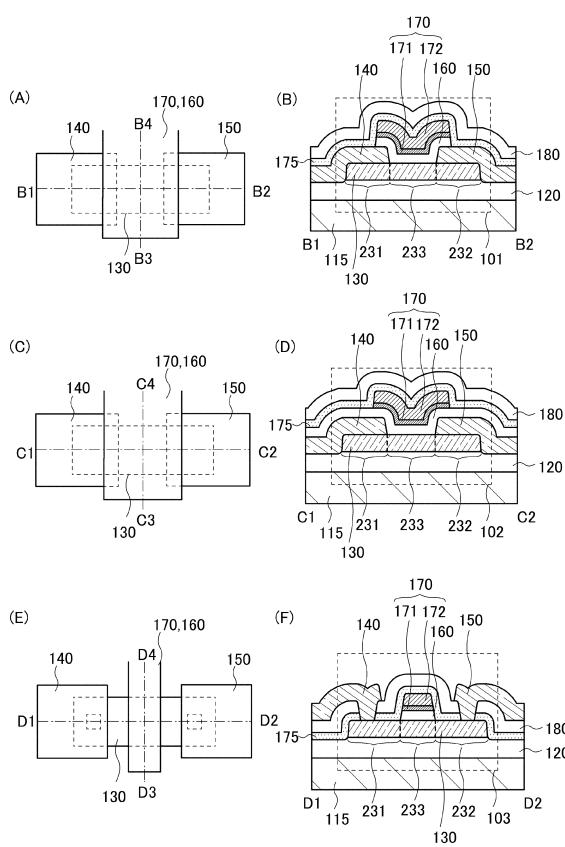

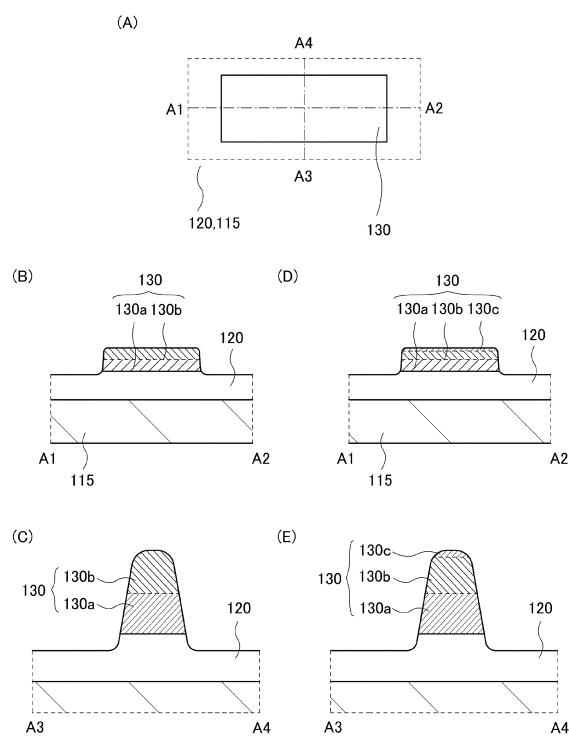

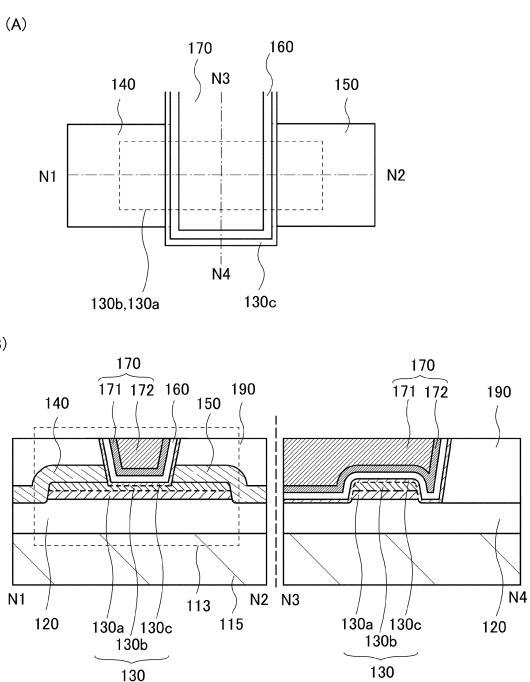

図14( A )、( B )は、本発明の一態様のトランジスタ101の上面図および断面図である。図14( A )は上面図であり、図14( A )に示す一点鎖線B1-B2方向の断面が図14( B )に相当する。また、図14( A )に示す一点鎖線B3-B4方向の断面が図16( A )に相当する。また、一点鎖線B1-B2方向をチャネル長方向、一点鎖線B3-B4方向をチャネル幅方向と呼称する。

#### 【0154】

トランジスタ101は、基板115と接する絶縁層120と、絶縁層120と接する酸化物半導体層130と、酸化物半導体層130と電気的に接続する導電層140および導電層150と、酸化物半導体層130、導電層140および導電層150と接する絶縁層160と、絶縁層160と接する導電層170と、導電層140、導電層150、絶縁層160および導電層170と接する絶縁層175と、絶縁層175と接する絶縁層180と、を有する。また、必要に応じて絶縁層180に平坦化膜としての機能を附加してもよい。

10

#### 【0155】

導電層140はソース電極層、導電層150はドレイン電極層、絶縁層160はゲート絶縁膜、導電層170はゲート電極層としてそれぞれ機能することができる。

#### 【0156】

図14( B )に示す領域231はソース領域、領域232はドレイン領域、領域233はチャネル形成領域として機能することができる。領域231および領域232は導電層140および導電層150とそれぞれ接しており、導電層140および導電層150として酸素と結合しやすい導電材料を用いれば領域231および領域232を低抵抗化することができる。

20

#### 【0157】

具体的には、酸化物半導体層130と導電層140および導電層150とが接することで酸化物半導体層130内に酸素欠損が生じ、当該酸素欠損と酸化物半導体層130内に残留または外部から拡散する水素との相互作用により、領域231および領域232は低抵抗のn型となる。

#### 【0158】

なお、トランジスタの「ソース」や「ドレイン」の機能は、異なる極性のトランジスタを採用する場合や、回路動作において電流の方向が変化する場合などには入れ替わることがある。このため、本明細書においては、「ソース」や「ドレイン」という用語は、入れ替えて用いることができるものとする。また、「電極層」は、「配線」と言い換えることができる。

30

#### 【0159】

導電層170は、導電層171および導電層172の二層で形成される例を図示しているが、一層または三層以上の積層であってもよい。当該構成は本実施の形態で説明する他のトランジスタにも適用できる。

#### 【0160】

導電層140および導電層150は単層で形成される例を図示しているが、二層以上の積層であってもよい。当該構成は本実施の形態で説明する他のトランジスタにも適用できる。

40

#### 【0161】

本発明の一態様のトランジスタは、図14( C )、( D )に示す構成であってもよい。図14( C )はトランジスタ102の上面図であり、図14( C )に示す一点鎖線C1-C2方向の断面が図14( D )に相当する。また、図14( C )に示す一点鎖線C3-C4方向の断面は、図16( B )に相当する。また、一点鎖線C1-C2方向をチャネル長方向、一点鎖線C3-C4方向をチャネル幅方向と呼称する。

#### 【0162】

トランジスタ102は、ゲート絶縁膜として作用する絶縁層160の端部とゲート電極層として作用する導電層170の端部とを一致させない点を除き、トランジスタ101と同

50

様の構成を有する。トランジスタ 102 の構造は、導電層 140 および導電層 150 が絶縁層 160 で広く覆われているため、導電層 140 および導電層 150 と導電層 170 との間の抵抗が高く、ゲートリーク電流の少ない特徴を有している。

#### 【0163】

トランジスタ 101 およびトランジスタ 102 は、導電層 170 と導電層 140 および導電層 150 が重なる領域を有するトップゲート構造である。当該領域のチャネル長方向の幅は、寄生容量を小さくするために 3 nm 以上 300 nm 未満とすることが好ましい。当該構成では、酸化物半導体層 130 にオフセット領域が形成されないため、オン電流の高いトランジスタを形成しやすい。

#### 【0164】

本発明の一態様のトランジスタは、図 14 (E)、(F) に示す構成であってもよい。図 14 (E) はトランジスタ 103 の上面図であり、図 14 (E) に示す一点鎖線 D1 - D2 方向の断面が図 14 (F) に相当する。また、図 14 (E) に示す一点鎖線 D3 - D4 方向の断面は、図 16 (A) に相当する。また、一点鎖線 D1 - D2 方向をチャネル長方向、一点鎖線 D3 - D4 方向をチャネル幅方向と呼称する。

#### 【0165】

トランジスタ 103 は、基板 115 と接する絶縁層 120 と、絶縁層 120 と接する酸化物半導体層 130 と、酸化物半導体層 130 と接する絶縁層 160 と、絶縁層 160 と接する導電層 170 と、酸化物半導体層 130、絶縁層 160 および導電層 170 を覆う絶縁層 175 と、絶縁層 175 と接する絶縁層 180 と、絶縁層 175 および絶縁層 180 に設けられた開口部を通じて酸化物半導体層 130 と電気的に接続する導電層 140 および導電層 150 を有する。また、必要に応じて絶縁層 180、導電層 140 および導電層 150 に接する絶縁層（平坦化膜）などを有していてもよい。

#### 【0166】

導電層 140 はソース電極層、導電層 150 はドレイン電極層、絶縁層 160 はゲート絶縁膜、導電層 170 はゲート電極層としてそれぞれ機能することができる。

#### 【0167】

図 14 (F) に示す領域 231 はソース領域、領域 232 はドレイン領域、領域 233 はチャネル形成領域として機能することができる。領域 231 および領域 232 は絶縁層 175 と接しており、例えば絶縁層 175 として水素を含む絶縁材料を用いれば領域 231 および領域 232 を低抵抗化することができる。

#### 【0168】

具体的には、絶縁層 175 を形成するまでの工程により領域 231 および領域 232 に生じる酸素欠損と、絶縁層 175 から領域 231 および領域 232 に拡散する水素との相互作用により、領域 231 および領域 232 は低抵抗の n 型となる。なお、水素を含む絶縁材料としては、例えば窒化シリコンや窒化アルミニウムなどを用いることができる。

#### 【0169】

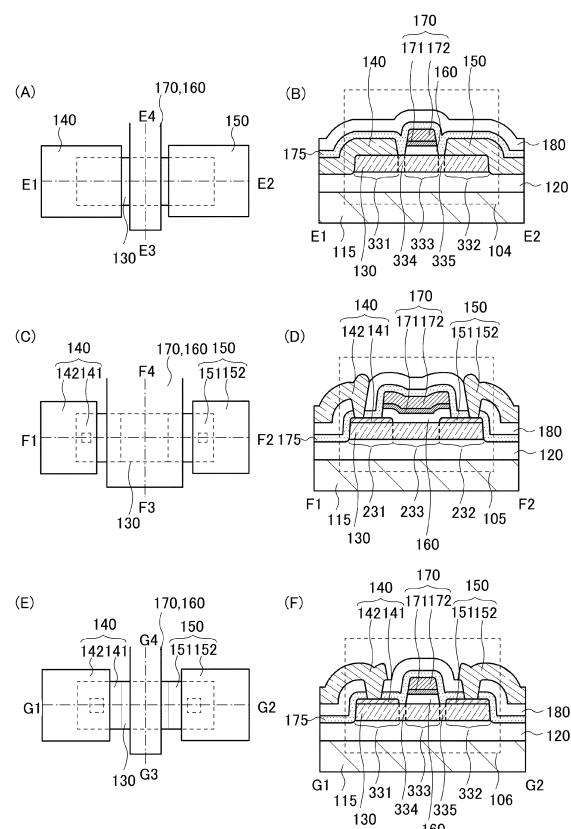

本発明の一態様のトランジスタは、図 15 (A)、(B) に示す構成であってもよい。図 15 (A) はトランジスタ 104 の上面図であり、図 15 (A) に示す一点鎖線 E1 - E2 方向の断面が図 15 (B) に相当する。また、図 15 (A) に示す一点鎖線 E3 - E4 方向の断面は、図 16 (A) に相当する。また、一点鎖線 E1 - E2 方向をチャネル長方向、一点鎖線 E3 - E4 方向をチャネル幅方向と呼称する。

#### 【0170】

トランジスタ 104 は、導電層 140 および導電層 150 が酸化物半導体層 130 の端部を覆うように接している点を除き、トランジスタ 103 と同様の構成を有する。

#### 【0171】

図 15 (B) に示す領域 331 および領域 334 はソース領域、領域 332 および領域 335 はドレイン領域、領域 333 はチャネル形成領域として機能することができる。

#### 【0172】

領域 331 および領域 332 は、トランジスタ 101 における領域 231 および領域 23

10

20

30

40

50

2と同様に低抵抗化することができる。

**【0173】**

領域334および領域335は、トランジスタ103における領域231および領域232と同様に低抵抗化することができる。なお、チャネル長方向における領域334および領域335の長さが100nm以下、好ましくは50nm以下の場合には、ゲート電界の寄与によりオン電流は大きく低下しない。したがって、領域334および領域335の低抵抗化を行わない場合もある。

**【0174】**

トランジスタ103およびトランジスタ104は、導電層170と導電層140および導電層150が重なる領域を有さないセルフアライン構造である。10セルフアライン構造のトランジスタはゲート電極層とソース電極層およびドレイン電極層間の寄生容量が極めて小さいため、高速動作用途に適している。

**【0175】**

本発明の一態様のトランジスタは、図15(C)、(D)に示す構成であってもよい。図15(C)はトランジスタ105の上面図であり、図15(C)に示す一点鎖線F1-F2方向の断面が図15(D)に相当する。また、図15(C)に示す一点鎖線F3-F4方向の断面は、図16(A)に相当する。また、一点鎖線F1-F2方向をチャネル長方向、一点鎖線F3-F4方向をチャネル幅方向と呼称する。

**【0176】**

トランジスタ105は、基板115と接する絶縁層120と、絶縁層120と接する酸化物半導体層130と、酸化物半導体層130と電気的に接続する導電層141および導電層151と、酸化物半導体層130、導電層141、導電層151と接する絶縁層160と、絶縁層160と接する導電層170と、酸化物半導体層130、導電層141、導電層151、絶縁層160および導電層170と接する絶縁層175と、絶縁層175と接する絶縁層180と、絶縁層175および絶縁層180に設けられた開口部を通じて導電層141および導電層151とそれぞれ電気的に接続する導電層142および導電層152を有する。また、必要に応じて絶縁層180、導電層142および導電層152に接する絶縁層などを有していてもよい。20

**【0177】**

導電層141および導電層151は、酸化物半導体層130の上面と接し、側面には接しない構成となっている。30

**【0178】**

トランジスタ105は、導電層141および導電層151を有する点、絶縁層175および絶縁層180に設けられた開口部を有する点、ならびに当該開口部を通じて導電層141および導電層151とそれぞれ電気的に接続する導電層142および導電層152を有する点を除き、トランジスタ101と同様の構成を有する。導電層140(導電層141および導電層142)はソース電極層として作用させることができ、導電層150(導電層151および導電層152)はドレイン電極層として作用させることができる。

**【0179】**

本発明の一態様のトランジスタは、図15(E)、(F)に示す構成であってもよい。図15(E)はトランジスタ106の上面図であり、図15(E)に示す一点鎖線G1-G2方向の断面が図15(F)に相当する。また、図15(E)に示す一点鎖線G3-G4方向の断面は、図16(A)に相当する。また、一点鎖線G1-G2方向をチャネル長方向、一点鎖線G3-G4方向をチャネル幅方向と呼称する。40

**【0180】**

トランジスタ106は、基板115と接する絶縁層120と、絶縁層120と接する酸化物半導体層130と、酸化物半導体層130と電気的に接続する導電層141および導電層151と、酸化物半導体層130と接する絶縁層160と、絶縁層160と接する導電層170と、絶縁層120、酸化物半導体層130、導電層141、導電層151、絶縁層160、導電層170と接する絶縁層175と、絶縁層175と接する絶縁層180と50

、絶縁層175および絶縁層180に設けられた開口部を通じて導電層141および導電層151とそれぞれ電気的に接続する導電層142および導電層152を有する。また、必要に応じて絶縁層180、導電層142および導電層152に接する絶縁層(平坦化膜)などを有していてもよい。

#### 【0181】

導電層141および導電層151は、酸化物半導体層130の上面と接し、側面には接しない構成となっている。

#### 【0182】

トランジスタ106は、導電層141および導電層151を有する点を除き、トランジスタ103と同様の構成を有する。導電層140(導電層141および導電層142)はソース電極層として作用させることができ、導電層150(導電層151および導電層152)はドレイン電極層として作用させることができる。10

#### 【0183】

トランジスタ105およびトランジスタ106の構成では、導電層140および導電層150が絶縁層120と接しない構成であるため、絶縁層120中の酸素が導電層140および導電層150に奪われにくくなり、絶縁層120から酸化物半導体層130中への酸素の供給を容易とすることができます。

#### 【0184】

トランジスタ105における領域231および領域232、トランジスタ104およびトランジスタ106における領域334および領域335には、酸素欠損を形成し導電率を高めるための不純物を添加してもよい。酸化物半導体層に酸素欠損を形成する不純物としては、例えば、リン、砒素、アンチモン、ホウ素、アルミニウム、シリコン、窒素、ヘリウム、ネオン、アルゴン、クリプトン、キセノン、インジウム、フッ素、塩素、チタン、亜鉛、および炭素のいずれかから選択される一つ以上を用いることができる。当該不純物の添加方法としては、プラズマ処理法、イオン注入法、イオンドーピング法、プラズマイマージョンイオンインプランテーション法などを用いることができる。20

#### 【0185】

不純物元素として、上記元素が酸化物半導体層に添加されると、酸化物半導体層中の金属元素および酸素の結合が切断され、酸素欠損が形成される。酸化物半導体層に含まれる酸素欠損と酸化物半導体層中に残存または後から添加される水素の相互作用により、酸化物半導体層の導電率を高くすることができる。30

#### 【0186】

不純物元素の添加により酸素欠損が形成された酸化物半導体に水素を添加すると、酸素欠損サイトに水素が入り伝導帯近傍にドナー準位が形成される。その結果、酸化物導電体を形成することができる。ここでは、導電体化された酸化物半導体を酸化物導電体という。なお、酸化物導電体は酸化物半導体と同様に透光性を有する。

#### 【0187】

酸化物導電体は、縮退半導体であり、伝導帯端とフェルミ準位とが一致または略一致していると推定される。このため、酸化物導電体層とソース電極層およびドレイン電極層として機能する導電層との接触はオーミック接触であり、酸化物導電体層とソース電極層およびドレイン電極層として機能する導電層との接触抵抗を低減することができる。40

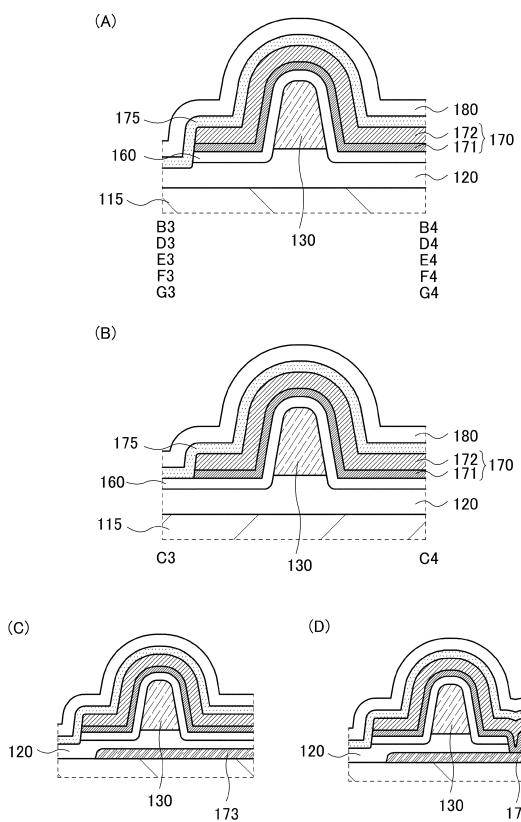

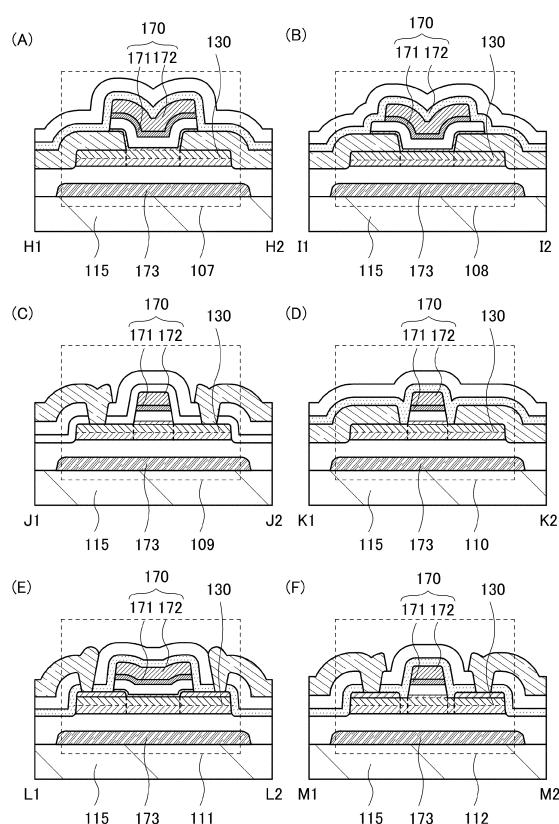

#### 【0188】

本発明の一態様のトランジスタは、図17(A)、(B)、(C)、(D)、(E)、(F)に示すチャネル長方向の断面図、ならびに図16(C)、(D)に示すチャネル幅方向の断面図のように、酸化物半導体層130と基板115との間に導電層173を備えていてもよい。当該導電層を第2のゲート電極層(バックゲート)として用いることで、オン電流の増加や、しきい値電圧の制御を行うことができる。なお、図17(A)、(B)、(C)、(D)、(E)、(F)に示す断面図において、導電層173の幅を酸化物半導体層130よりも短くしてもよい。さらに、導電層173の幅を導電層170の幅よりも短くしてもよい。50

## 【0189】

オン電流を増加させるには、例えば、導電層170と導電層173を同電位とし、ダブルゲートトランジスタとして駆動させればよい。また、しきい値電圧の制御を行うには、導電層170とは異なる定電位を導電層173に供給すればよい。導電層170と導電層173を同電位とするには、例えば、図16(D)に示すように、導電層170と導電層173とをコンタクトホールを介して電気的に接続すればよい。

## 【0190】

図14および図15におけるトランジスタ101乃至トランジスタ106では、酸化物半導体層130が単層である例を図示したが、酸化物半導体層130は積層であってもよい。トランジスタ101乃至トランジスタ106の酸化物半導体層130は、図18(B)、(C)または図18(D)、(E)に示す酸化物半導体層130と入れ替えることができる。

10

## 【0191】

図18(A)は酸化物半導体層130の上面図であり、図18(B)、(C)は、二層構造である酸化物半導体層130の断面図である。また、図18(D)、(E)は、三層構造である酸化物半導体層130の断面図である。

## 【0192】

酸化物半導体層130a、酸化物半導体層130b、酸化物半導体層130cには、それぞれ組成の異なる酸化物半導体層などを用いることができる。

20

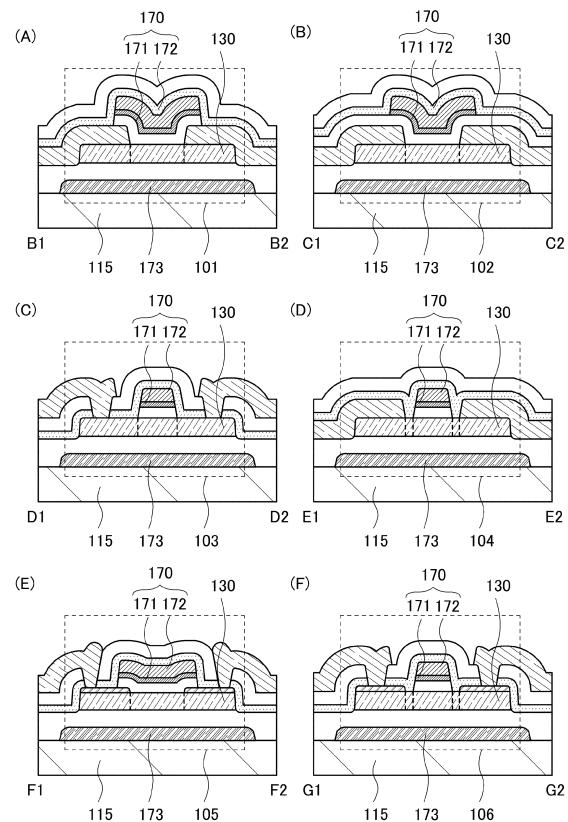

## 【0193】

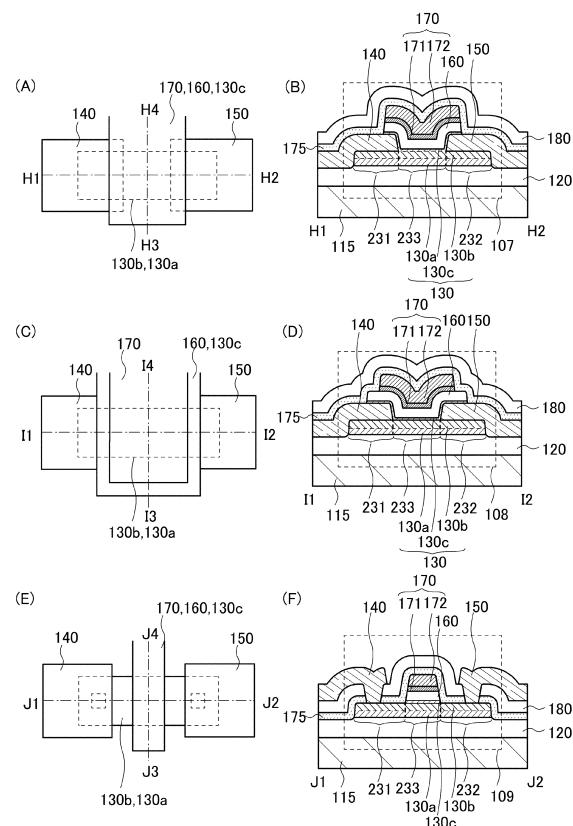

本発明の一態様のトランジスタは、図19(A)、(B)に示す構成であってもよい。図19(A)はトランジスタ107の上面図であり、図19(A)に示す一点鎖線H1-H2方向の断面が図19(B)に相当する。また、図19(A)に示す一点鎖線H3-H4方向の断面が図21(A)に相当する。また、一点鎖線H1-H2方向をチャネル長方向、一点鎖線H3-H4方向をチャネル幅方向と呼称する。

## 【0194】

トランジスタ107は、基板115と接する絶縁層120と、絶縁層120と接する酸化物半導体層130aおよび酸化物半導体層130bからなる積層と、当該積層と電気的に接続する導電層140および導電層150と、当該積層、導電層140および導電層150と接する酸化物半導体層130cと、酸化物半導体層130cと接する絶縁層160と、絶縁層160と接する導電層170と、導電層140、導電層150、酸化物半導体層130c、絶縁層160および導電層170と接する絶縁層175と、絶縁層175と接する絶縁層180と、を有する。また、必要に応じて絶縁層180に平坦化膜としての機能を付加してもよい。

30

## 【0195】

トランジスタ107は、領域231および領域232において酸化物半導体層130が二層(酸化物半導体層130a、酸化物半導体層130b)である点、領域233において酸化物半導体層130が三層(酸化物半導体層130a、酸化物半導体層130b、酸化物半導体層130c)である点、および導電層140および導電層150と絶縁層160との間に酸化物半導体層の一部(酸化物半導体層130c)が介在している点を除き、トランジスタ101と同様の構成を有する。

40

## 【0196】

本発明の一態様のトランジスタは、図19(C)、(D)に示す構成であってもよい。図19(C)はトランジスタ108の上面図であり、図19(C)に示す一点鎖線I1-I2方向の断面が図19(D)に相当する。また、図19(C)に示す一点鎖線I3-I4方向の断面が図21(B)に相当する。また、一点鎖線I1-I2方向をチャネル長方向、一点鎖線I3-I4方向をチャネル幅方向と呼称する。

## 【0197】

トランジスタ108は、絶縁層160および酸化物半導体層130cの端部が導電層170の端部と一致しない点がトランジスタ107と異なる。

50

## 【0198】

本発明の一態様のトランジスタは、図19( E )、( F )に示す構成であってもよい。図19( E )はトランジスタ109の上面図であり、図19( E )に示す一点鎖線J1-J2方向の断面が図19( F )に相当する。また、図19( E )に示す一点鎖線J3-J4方向の断面が図21( A )に相当する。また、一点鎖線J1-J2方向をチャネル長方向、一点鎖線J3-J4方向をチャネル幅方向と呼称する。

## 【0199】

トランジスタ109は、基板115と接する絶縁層120と、絶縁層120と接する酸化物半導体層130aおよび酸化物半導体層130bからなる積層と、当該積層と接する酸化物半導体層130cと、酸化物半導体層130cと接する絶縁層160と、絶縁層160と接する導電層170と、当該積層、酸化物半導体層130c、絶縁層160および導電層170を覆う絶縁層175と、絶縁層175と接する絶縁層180と、絶縁層175および絶縁層180に設けられた開口部を通じて当該積層と電気的に接続する導電層140および導電層150を有する。また、必要に応じて絶縁層180、導電層140および導電層150に接する絶縁層(平坦化膜)などを有してもよい。

10

## 【0200】

トランジスタ109は、領域231および領域232において酸化物半導体層130が二層(酸化物半導体層130a、酸化物半導体層130b)である点、領域233において酸化物半導体層130が三層(酸化物半導体層130a、酸化物半導体層130b、酸化物半導体層130c)である点を除き、トランジスタ103と同様の構成を有する。

20

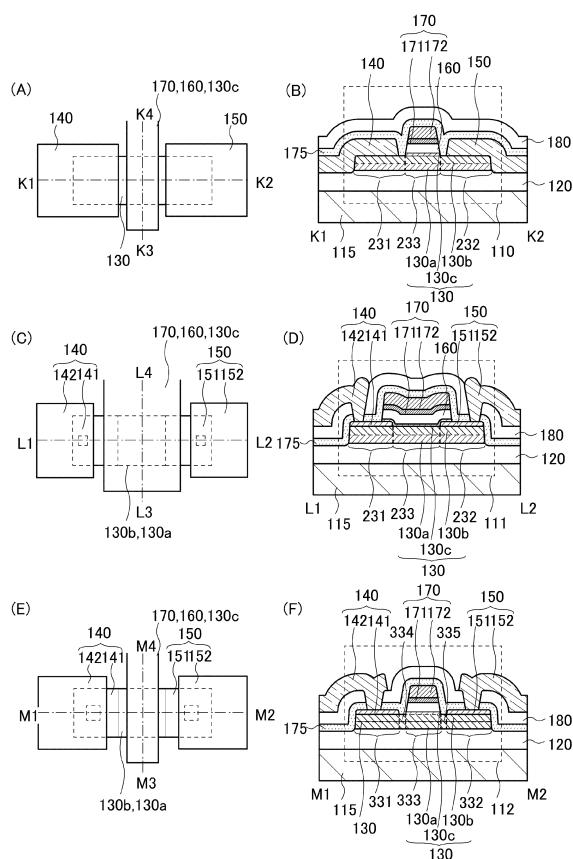

## 【0201】

本発明の一態様のトランジスタは、図20( A )、( B )に示す構成であってもよい。図20( A )はトランジスタ110の上面図であり、図20( A )に示す一点鎖線K1-K2方向の断面が図20( B )に相当する。また、図20( A )に示す一点鎖線K3-K4方向の断面が図21( A )に相当する。また、一点鎖線K1-K2方向をチャネル長方向、一点鎖線K3-K4方向をチャネル幅方向と呼称する。

## 【0202】

トランジスタ110は、領域331および領域332において酸化物半導体層130が二層(酸化物半導体層130a、酸化物半導体層130b)である点、領域333において酸化物半導体層130が三層(酸化物半導体層130a、酸化物半導体層130b、酸化物半導体層130c)である点を除き、トランジスタ104と同様の構成を有する。

30

## 【0203】

本発明の一態様のトランジスタは、図20( C )、( D )に示す構成であってもよい。図20( C )はトランジスタ111の上面図であり、図20( C )に示す一点鎖線L1-L2方向の断面が図20( D )に相当する。また、図20( C )に示す一点鎖線L3-L4方向の断面が図21( A )に相当する。また、一点鎖線L1-L2方向をチャネル長方向、一点鎖線L3-L4方向をチャネル幅方向と呼称する。

## 【0204】

トランジスタ111は、基板115と接する絶縁層120と、絶縁層120と接する酸化物半導体層130aおよび酸化物半導体層130bからなる積層と、当該積層と電気的に接続する導電層141および導電層151と、当該積層、導電層141および導電層151と接する酸化物半導体層130cと、酸化物半導体層130cと接する絶縁層160と、絶縁層160と接する導電層170と、当該積層、導電層141、導電層151、酸化物半導体層130c、絶縁層160および導電層170と接する絶縁層175と、絶縁層175と接する絶縁層180と、絶縁層175および絶縁層180に設けられた開口部を通じて導電層141および導電層151とそれぞれ電気的に接続する導電層142および導電層152を有する。また、必要に応じて絶縁層180、導電層142および導電層152に接する絶縁層(平坦化膜)などを有してもよい。

40

## 【0205】

トランジスタ111は、領域231および領域232において酸化物半導体層130が二

50

層（酸化物半導体層 130a、酸化物半導体層 130b）である点、領域 233において酸化物半導体層 130 が三層（酸化物半導体層 130a、酸化物半導体層 130b、酸化物半導体層 130c）である点、ならびに導電層 141 および導電層 151 と絶縁層 160との間に酸化物半導体層の一部（酸化物半導体層 130c）が介在している点を除き、トランジスタ 105 と同様の構成を有する。

#### 【0206】

本発明の一態様のトランジスタは、図 20 (E)、(F) に示す構成であってもよい。図 20 (E) はトランジスタ 112 の上面図であり、図 20 (E) に示す一点鎖線 M1 - M2 方向の断面が図 20 (F) に相当する。また、図 20 (E) に示す一点鎖線 M3 - M4 方向の断面が図 21 (A) に相当する。また、一点鎖線 M1 - M2 方向をチャネル長方向 10 、一点鎖線 M3 - M4 方向をチャネル幅方向と呼称する。

#### 【0207】

トランジスタ 112 は、領域 331、領域 332、領域 334 および領域 335 において酸化物半導体層 130 が二層（酸化物半導体層 130a、酸化物半導体層 130b）である点、領域 333 において酸化物半導体層 130 が三層（酸化物半導体層 130a、酸化物半導体層 130b、酸化物半導体層 130c）である点を除き、トランジスタ 106 と同様の構成を有する。

#### 【0208】

本発明の一態様のトランジスタは、図 22 (A)、(B)、(C)、(D)、(E)、(F) に示すチャネル長方向の断面図、ならびに図 21 (C)、(D) に示すチャネル幅方向の断面図のように、酸化物半導体層 130 と基板 115 との間に導電層 173 を備えていてもよい。当該導電層を第 2 のゲート電極層（バックゲート）として用いることで、オ ン電流の増加や、しきい値電圧の制御を行うことができる。なお、図 22 (A)、(B)、(C)、(D)、(E)、(F) に示す断面図において、導電層 173 の幅を酸化物半導体層 130 よりも短くしてもよい。さらに、導電層 173 の幅を導電層 170 の幅よりも短くしてもよい。

#### 【0209】

本発明の一態様のトランジスタは、図 23 (A) および図 23 (B) に示す構成とするこ ともできる。図 23 (A) は上面図であり、図 23 (B) は、図 23 (A) に示す一点鎖線 N1 - N2、および一点鎖線 N3 - N4 に対応する断面図である。なお、図 23 (A) 30 の上面図では、図の明瞭化のために一部の要素を省いて図示している。

#### 【0210】

図 23 (A) および図 23 (B) に示すトランジスタ 113 は、基板 115 と、基板 115 上の絶縁層 120 と、絶縁層 120 上の酸化物半導体層 130（酸化物半導体層 130a、酸化物半導体層 130b、酸化物半導体層 130c）と、酸化物半導体層 130 に接し、間隔を開けて配置された導電層 140 および導電層 150 と、酸化物半導体層 130c と接する絶縁層 160 と、絶縁層 160 と接する導電層 170 を有する。なお、酸化物半導体層 130c、絶縁層 160 および導電層 170 は、トランジスタ 113 上の絶縁層 190 に設けられた酸化物半導体層 130a、酸化物半導体層 130b および絶縁層 120 に達する開口部に設けられている。

#### 【0211】

トランジスタ 113 の構成は、前述したその他のトランジスタの構成と比較して、ソースまたはドレインとなる導電体とゲート電極となる導電体の重なる領域が少ないため、寄生容量を小さくすることができる。したがって、トランジスタ 113 は、高速動作を必要とする回路の要素として適している。トランジスタ 113 の上面は、図 23 (B) に示すよ うに CMP (Chemical Mechanical Polishing) 法等を用いて平坦化することが好ましいが、平坦化しない構成とすることもできる。

#### 【0212】

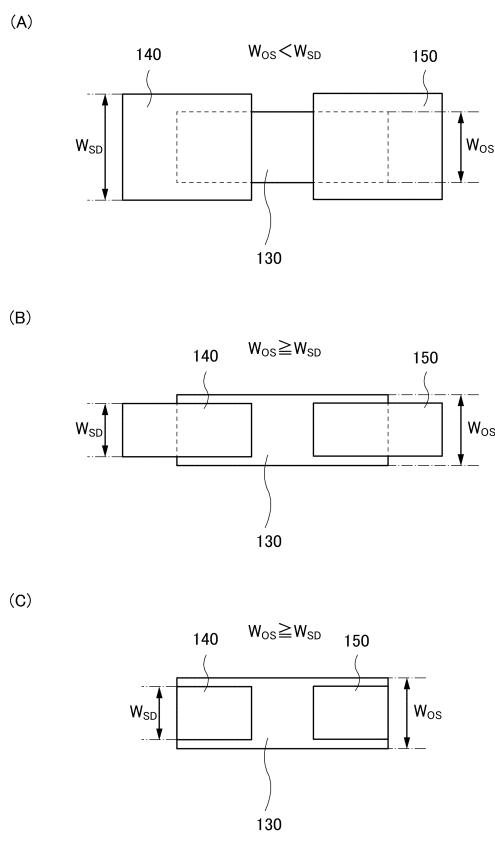

本発明の一態様のトランジスタにおける導電層 140（ソース電極層）および導電層 150（ドレイン電極層）は、図 24 (A)、(B) に示す上面図（酸化物半導体層 130、50

導電層 140 および導電層 150 のみを図示) のように酸化物半導体層 130 の幅 ( $W_{o_s}$ ) よりも導電層 140 および導電層 150 の幅 ( $W_{SD}$ ) が長く形成されていてもよいし、短く形成されていてもよい。 $W_{o_s} < W_{SD}$  ( $W_{SD}$  は  $W_{o_s}$  以下) とすることで、ゲート電界が酸化物半導体層 130 全体にかかりやすくなり、トランジスタの電気特性を向上させることができる。また、図 24 (C) に示すように、導電層 140 および導電層 150 が酸化物半導体層 130 と重なる領域のみに形成されていてもよい。

#### 【0213】

本発明の一態様のトランジスタ (トランジスタ 101 乃至トランジスタ 113) では、いずれの構成においても、ゲート電極層である導電層 170 は、ゲート絶縁膜である絶縁層 160 を介して酸化物半導体層 130 のチャネル幅方向を電気的に取り囲み、オン電流が高められる。このようなトランジスタの構造を、*surrounded channel (s-channel)* 構造とよぶ。

#### 【0214】

酸化物半導体層 130a および酸化物半導体層 130b を有するトランジスタ、ならびに酸化物半導体層 130a、酸化物半導体層 130b および酸化物半導体層 130c を有するトランジスタにおいては、酸化物半導体層 130 を構成する二層または三層の材料を適切に選択することで酸化物半導体層 130b に電流を流すことができる。酸化物半導体層 130b に電流が流れることで、界面散乱の影響を受けにくく、高いオン電流を得ることができる。したがって、酸化物半導体層 130b を厚くすることでオン電流が向上する場合がある。

#### 【0215】

以上の構成とすることで、トランジスタの電気特性を向上することができる。

#### 【0216】

本実施の形態に示す構成は、他の実施の形態に示す構成と適宜組み合わせて用いることができる。

#### 【0217】

##### (実施の形態 3)

本実施の形態では、実施の形態 2 に示したトランジスタの構成要素について詳細を説明する。

#### 【0218】

基板 115 には、ガラス基板、石英基板、半導体基板、セラミックス基板、表面が絶縁処理された金属基板などを用いることができる。または、トランジスタやフォトダイオードが形成されたシリコン基板、および当該シリコン基板上に絶縁層、配線、コンタクトプラグとして機能を有する導電体等が形成されたものを用いることができる。なお、シリコン基板に p - c h 型のトランジスタを形成する場合は、n - 型の導電型を有するシリコン基板を用いることが好ましい。または、n - 型または i 型のシリコン層を有する SOI 基板であってもよい。また、シリコン基板に設けるトランジスタが p - c h 型である場合は、トランジスタを形成する面の面方位は、(110) 面であるシリコン基板を用いることが好ましい。(110) 面に p - c h 型トランジスタを形成することで、移動度を高くすることができる。

#### 【0219】

絶縁層 120 は、基板 115 に含まれる要素からの不純物の拡散を防止する役割を有するほか、酸化物半導体層 130 に酸素を供給する役割を担うことができる。したがって、絶縁層 120 は酸素を含む絶縁膜であることが好ましく、化学量論組成よりも多い酸素を含む絶縁膜であることがより好ましい。例えば、膜の表面温度が 100 以上 700 以下、好ましくは 100 以上 500 以下の加熱処理で行われる TDS 法にて、酸素原子に換算した酸素の放出量が  $1.0 \times 10^{19} \text{ atoms/cm}^3$  以上である膜とする。また、基板 115 が他のデバイスが形成された基板である場合、絶縁層 120 は、層間絶縁膜としての機能も有する。その場合は、表面が平坦になるように CMP 法等で平坦化処理を行うことが好ましい。

10

20

30

40

50

## 【0220】

例えば、絶縁層120には、酸化アルミニウム、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニアム、酸化ランタン、酸化ネオジム、酸化ハフニウムおよび酸化タンタルなどの酸化物絶縁膜、窒化シリコン、窒化酸化シリコン、窒化アルミニウム、窒化酸化アルミニウムなどの窒化物絶縁膜、またはこれらの混合材料を用いることができる。また、上記材料の積層であつてもよい。

## 【0221】

酸化物半導体層130は、酸化物半導体層130a、酸化物半導体層130bおよび酸化物半導体層130cを絶縁層120側から順に積んだ三層構造とすることができる。 10

## 【0222】

なお、酸化物半導体層130が単層の場合は、本実施の形態に示す、酸化物半導体層130bに相当する層を用いればよい。

## 【0223】

酸化物半導体層130が二層の場合は、酸化物半導体層130aに相当する層および酸化物半導体層130bに相当する層を絶縁層120側から順に積んだ積層を用いればよい。この構成の場合、酸化物半導体層130aと酸化物半導体層130bとを入れ替えることもできる。

## 【0224】

一例としては、酸化物半導体層130bには、酸化物半導体層130aおよび酸化物半導体層130cよりも電子親和力（真空準位から伝導帯下端までのエネルギー差）が大きい酸化物半導体を用いる。 20

## 【0225】

このような構造において、導電層170に電界を印加すると、酸化物半導体層130のうち、伝導帯下端のエネルギーが最も小さい酸化物半導体層130bにチャネルが形成される。したがって、酸化物半導体層130bは半導体として機能する領域を有するといえるが、酸化物半導体層130aおよび酸化物半導体層130cは絶縁体または半絶縁体として機能する領域を有するともいえる。

## 【0226】

酸化物半導体層130a、酸化物半導体層130b、および酸化物半導体層130cとして用いることのできる酸化物半導体は、少なくともInもしくはZnを含むことが好ましい。または、InとZnの双方を含むことが好ましい。また、該OSトランジスタの電気特性のばらつきを減らすため、それらと共に、Al、Ga、Y、またはSn等のスタビライザーを含むことが好ましい。 30

## 【0227】

酸化物半導体層130a、酸化物半導体層130bおよび酸化物半導体層130cには、結晶部が含まれることが好ましい。特にc軸に配向した結晶を用いることでトランジスタに安定した電気特性を付与することができる。また、c軸に配向した結晶は歪曲に強く、フレキシブル基板を用いた半導体装置の信頼性を向上させることができる。

## 【0228】

ソース電極層として作用する導電層140およびドレイン電極層として作用する導電層150には、例えば、Al、Cr、Cu、Ta、Ti、Mo、W、Ni、Mn、Nd、Sc、および当該金属材料の合金から選ばれた材料の単層、または積層を用いることができる。また、低抵抗のCuやCu-Mnなどの合金と上記材料との積層を用いてもよい。トランジスタ105、トランジスタ106、トランジスタ111、トランジスタ112においては、例えば、導電層141および導電層151にW、導電層142および導電層152にTiとAlとの積層膜などを用いることができる。 40

## 【0229】

上記材料は酸化物半導体層から酸素を引き抜く性質を有する。そのため、上記材料と接した酸化物半導体層の一部の領域では酸化物半導体層中の酸素が脱離し、酸素欠損が形成さ 50

れる。層の中に僅かに含まれる水素と当該酸素欠損が結合することにより当該領域は顕著にn型化する。したがって、n型化した当該領域はトランジスタのソースまたはドレインとして作用させることができる。

#### 【0230】

導電層140および導電層150にWを用いる場合には、窒素をドーピングしてもよい。窒素をドーピングすることで酸素を引き抜く性質を適度に弱めることができ、n型化した領域がチャネル領域まで拡大することを防ぐことができる。また、導電層140および導電層150をn型の半導体層との積層とし、n型の半導体層と酸化物半導体層を接触させることによってもn型化した領域がチャネル領域まで拡大することを防ぐことができる。

n型の半導体層としては、窒素が添加されたIn-Ga-Zn酸化物、酸化亜鉛、酸化インジウム、酸化スズ、酸化インジウムスズなどを用いることができる。

10

#### 【0231】

ゲート絶縁膜として作用する絶縁層160には、酸化アルミニウム、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニア、酸化ランタン、酸化ネオジム、酸化ハフニウムおよび酸化タンタルを一種以上含む絶縁膜を用いることができる。また、絶縁層160は上記材料の積層であってもよい。なお、絶縁層160に、La、N、Zrなどを、不純物として含んでいてもよい。

#### 【0232】

また、絶縁層160の積層構造の一例について説明する。絶縁層160は、例えば、酸素、窒素、シリコン、ハフニウムなどを有する。具体的には、酸化ハフニウム、および酸化シリコンまたは酸化窒化シリコンを含むと好ましい。

20

#### 【0233】

酸化ハフニウムおよび酸化アルミニウムは、酸化シリコンや酸化窒化シリコンと比べて比誘電率が高い。したがって、酸化シリコンを用いた場合と比べて、絶縁層160の膜厚を大きくできるため、トンネル電流によるリーク電流を小さくすることができる。即ち、オフ電流の小さいトランジスタを実現することができる。さらに、結晶構造を有する酸化ハフニウムは、非晶質構造を有する酸化ハフニウムと比べて高い比誘電率を備える。したがって、オフ電流の小さいトランジスタとするためには、結晶構造を有する酸化ハフニウムを用いることが好ましい。結晶構造の例としては、単斜晶系や立方晶系などが挙げられる。ただし、本発明の一態様は、これらに限定されない。

30

#### 【0234】

また、酸化物半導体層130と接する絶縁層120および絶縁層160は、窒素酸化物の放出量の少ない膜を用いることが好ましい。窒素酸化物の放出量の多い絶縁層と酸化物半導体が接した場合、窒素酸化物に起因する準位密度が高くなることがある。絶縁層120および絶縁層160には、例えば、窒素酸化物の放出量の少ない酸化窒化シリコン膜または酸化窒化アルミニウム膜等の酸化物絶縁層を用いることができる。

#### 【0235】

窒素酸化物の放出量の少ない酸化窒化シリコン膜は、TDS法において、窒素酸化物の放出量よりアンモニアの放出量が多い膜であり、代表的にはアンモニアの放出量が $1 \times 10^{-8} \text{ cm}^{-3}$ 以上 $5 \times 10^{-9} \text{ cm}^{-3}$ 以下である。なお、アンモニアの放出量は、膜の表面温度が50以上650以下、好ましくは50以上550以下の加熱処理による放出量とする。

40

#### 【0236】

絶縁層120および絶縁層160として、上記酸化物絶縁層を用いることで、トランジスタのしきい値電圧のシフトを低減することが可能であり、トランジスタの電気特性の変動を低減することができる。

#### 【0237】

ゲート電極層として作用する導電層170には、例えば、Al、Ti、Cr、Co、Ni、Cu、Y、Zr、Mo、Ru、Ag、Mn、Nd、Sc、TaおよびWなどの導電膜を

50

用いることができる。また、上記材料の合金や上記材料の導電性窒化物を用いてもよい。また、上記材料、上記材料の合金、および上記材料の導電性窒化物から選ばれた複数の材料の積層であってもよい。代表的には、タンゲステン、タンゲステンと窒化チタンの積層、タンゲステンと窒化タンタルの積層などを用いることができる。また、低抵抗のCuまたはCu-Mnなどの合金や上記材料とCuまたはCu-Mnなどの合金との積層を用いてもよい。本実施の形態では、導電層171に窒化タンタル、導電層172にタンゲステンを用いて導電層170を形成する。

#### 【0238】

また、導電層170にはIn-Ga-Zn酸化物、酸化亜鉛、酸化インジウム、酸化スズ、酸化インジウムスズなどの酸化物導電層を用いてもよい。

10

#### 【0239】

絶縁層175には、水素を含む窒化シリコン膜または窒化アルミニウム膜などを用いることができる。実施の形態2に示したトランジスタ103、トランジスタ104、トランジスタ106、トランジスタ109、トランジスタ110、およびトランジスタ112では、絶縁層175として水素を含む絶縁膜を用いることで酸化物半導体層の一部をn型化することができる。また、窒化絶縁膜は水分などのプロッキング膜としての作用も有し、トランジスタの信頼性を向上させることができる。

#### 【0240】

また、絶縁層175としては酸化アルミニウム膜を用いることもできる。特に、実施の形態2に示したトランジスタ101、トランジスタ102、トランジスタ105、トランジスタ107、トランジスタ108、およびトランジスタ111では絶縁層175に酸化アルミニウム膜を用いることが好ましい。酸化アルミニウム膜は、水素、水分などの不純物、および酸素の両方に対して膜を透過させない遮断効果が高い。したがって、酸化アルミニウム膜は、トランジスタの作製工程中および作製後において、水素、水分などの不純物の酸化物半導体層130への混入防止、酸素の酸化物半導体層からの放出防止、絶縁層120からの酸素の不必要的放出防止の効果を有する保護膜として用いることに適している。

20

#### 【0241】

絶縁層175上には絶縁層180が形成されていることが好ましい。当該絶縁層には、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニア、酸化ランタン、酸化ネオジム、酸化ハフニウムおよび酸化タンタルを一種以上含む絶縁膜を用いることができる。また、当該絶縁層は上記材料の積層であってもよい。

30

#### 【0242】

ここで、絶縁層180は絶縁層120と同様に化学量論組成よりも多くの酸素を有することが好ましい。絶縁層180から放出される酸素は絶縁層160を経由して酸化物半導体層130のチャネル形成領域に拡散させることができることから、チャネル形成領域に形成された酸素欠損に酸素を補填することができる。したがって、安定したトランジスタの電気特性を得ることができる。

#### 【0243】

40

半導体装置を高集積化するにはトランジスタの微細化が必須である。一方、トランジスタの微細化によりトランジスタの電気特性は悪化する傾向にあり、例えばチャネル幅を縮小させるとオン電流は低下してしまう。

#### 【0244】

本発明の一態様のトランジスタ107乃至トランジスタ112では、チャネルが形成される酸化物半導体層130bを覆うように酸化物半導体層130cが形成されており、チャネル形成層とゲート絶縁膜が接しない構成となっている。そのため、チャネル形成層とゲート絶縁膜との界面で生じるキャリアの散乱を抑えることができ、トランジスタのオン電流を大きくすることができる。

#### 【0245】

50

本発明の一態様のトランジスタでは、前述したように酸化物半導体層130のチャネル幅方向を電気的に取り囲むようにゲート電極層（導電層170）が形成されているため、酸化物半導体層130に対しては上面に垂直な方向からのゲート電界に加えて、側面に垂直な方向からのゲート電界が印加される。すなわち、チャネル形成層に対して全体的にゲート電界が印加されることになり実効チャネル幅が拡大するため、さらにオン電流を高められる。

#### 【0246】

本実施の形態で説明した金属膜、半導体膜、無機絶縁膜など様々な膜は、代表的にはスパッタ法やプラズマCVD法により形成することができるが、他の方法、例えば、熱CVD法により形成してもよい。熱CVD法の例としては、MOCVD (Metal Organic Chemical Vapor Deposition) 法やALD (Atomic Layer Deposition) 法などがある。10

#### 【0247】

熱CVD法は、プラズマを使わない成膜方法のため、プラズマダメージにより欠陥が生成されることが無いという利点を有する。

#### 【0248】

また、熱CVD法では、原料ガスと酸化剤を同時にチャンバー内に送り、チャンバー内を大気圧または減圧下とし、基板近傍または基板上で反応させて基板上に堆積させることで成膜を行ってもよい。20

#### 【0249】

ALD法は、チャンバー内を大気圧または減圧下とし、反応のための原料ガスをチャンバーに導入・反応させ、これを繰り返すことで成膜を行う。原料ガスと一緒に不活性ガス（アルゴン、或いは窒素など）をキャリアガスとして導入しても良い。例えば2種類以上の原料ガスを順番にチャンバーに供給してもよい。その際、複数種の原料ガスが混ざらないように第1の原料ガスの反応後、不活性ガスを導入し、第2の原料ガスを導入する。あるいは、不活性ガスを導入する代わりに真空排気によって第1の原料ガスを排出した後、第2の原料ガスを導入してもよい。第1の原料ガスが基板の表面に吸着・反応して第1の層を成膜し、後から導入される第2の原料ガスが吸着・反応して、第2の層が第1の層上に積層されて薄膜が形成される。このガス導入順序を制御しつつ所望の厚さになるまで複数回繰り返すことで、段差被覆性に優れた薄膜を形成することができる。薄膜の厚さは、ガス導入の繰り返す回数によって調節することができるため、精密な膜厚調節が可能であり、微細なFETを作製する場合に適している。30

#### 【0250】

MOCVD法やALD法などの熱CVD法は、これまでに記載した実施形態に開示された金属膜、半導体膜、無機絶縁膜など様々な膜を形成することができ、例えば、In-Ga-Zn-O膜を成膜する場合には、トリメチルインジウム(  $In(CH_3)_3$  )、トリメチルガリウム(  $Ga(CH_3)_3$  )、およびジメチル亜鉛(  $Zn(CH_3)_2$  )を用いることができる。これらの組み合わせに限定されず、トリメチルガリウムに代えてトリエチルガリウム(  $Ga(C_2H_5)_3$  )を用いることもでき、ジメチル亜鉛に代えてジエチル亜鉛(  $Zn(C_2H_5)_2$  )を用いることもできる。40

#### 【0251】

例えば、ALDを利用する成膜装置により酸化ハフニウム膜を形成する場合には、溶媒とハフニウム前駆体を含む液体（ハフニウムアルコキシドや、テトラキスジメチルアミドハフニウム(  $TDMAH, Hf[N(CH_3)_2]_4$  )やテトラキス(エチルメチルアミド)ハフニウムなどのハフニウムアミド）を気化させた原料ガスと、酸化剤としてオゾン(  $O_3$  )の2種類のガスを用いる。

#### 【0252】

例えば、ALDを利用する成膜装置により酸化アルミニウム膜を形成する場合には、溶媒とアルミニウム前駆体を含む液体（トリメチルアルミニウム(  $TMA, Al(CH_3)_3$  )など）を気化させた原料ガスと、酸化剤として  $H_2O$  の2種類のガスを用いる。他の材50

料としては、トリス(ジメチルアミド)アルミニウム、トリイソブチルアルミニウム、アルミニウムトリス(2,2,6,6-テトラメチル-3,5-ヘプタンジオナート)などがある。

#### 【0253】

例えば、ALDを利用する成膜装置により酸化シリコン膜を形成する場合には、ヘキサクロロジシランを被成膜面に吸着させ、酸化性ガス( $O_2$ 、一酸化二窒素)のラジカルを供給して吸着物と反応させる。

#### 【0254】

例えば、ALDを利用する成膜装置によりタンゲステン膜を成膜する場合には、 $WF_6$ ガスと $B_2H_6$ ガスを順次導入して初期タンゲステン膜を形成し、その後、 $WF_6$ ガスと $H_2$ ガスを順次導入してタンゲステン膜を形成する。なお、 $B_2H_6$ ガスに代えて $SiH_4$ ガスを用いてもよい。

10

#### 【0255】

例えば、ALDを利用する成膜装置により酸化物半導体層、例えばIn-Ga-Zn-O膜を成膜する場合には、 $In(CH_3)_3$ ガスと $O_3$ ガスを順次導入してIn-O層を形成し、その後、 $Ga(CH_3)_3$ ガスと $O_3$ ガスを順次導入してGaO層を形成し、さらにその後 $Zn(CH_3)_2$ ガスと $O_3$ ガスを順次導入してZnO層を形成する。なお、これらの層の順番はこの例に限らない。これらのガスを用いてIn-Ga-O層やIn-Zn-O層、Ga-Zn-O層などの混合化合物層を形成しても良い。なお、 $O_3$ ガスに変えてAr等の不活性ガスでバーピングして得られた $H_2O$ ガスを用いても良いが、Hを含まない $O_3$ ガスを用いる方が好ましい。

20

#### 【0256】

酸化物半導体層の成膜には、対向ターゲット式スパッタ装置を用いることもできる。当該対向ターゲット式スパッタ装置を用いた成膜法を、VDS-P(vapor deposition SP)と呼ぶこともできる。

#### 【0257】

対向ターゲット式スパッタ装置を用いて酸化物半導体層を成膜することによって、酸化物半導体層の成膜時におけるプラズマ損傷を低減することができる。そのため、膜中の酸素欠損を低減することができる。また、対向ターゲット式スパッタ装置を用いることで低圧での成膜が可能となるため、成膜された酸化物半導体層中の不純物濃度(例えば水素、希ガス(アルゴンなど)、水など)を低減させることができる。

30

#### 【0258】

本実施の形態に示す構成は、他の実施の形態に示す構成と適宜組み合わせて用いることができる。

#### 【0259】

##### (実施の形態4)

本実施の形態では、本発明の一態様に用いることのできる酸化物半導体の材料について説明する。

#### 【0260】

酸化物半導体は、少なくともインジウムまたは亜鉛を含むことが好ましい。特にインジウムおよび亜鉛を含むことが好ましい。また、それらに加えて、元素Mとしてアルミニウム、ガリウム、イットリウムまたはスズなどが含まれていることが好ましい。また、元素Mとしては、ホウ素、シリコン、チタン、鉄、ニッケル、ゲルマニウム、ジルコニウム、モリブデン、ランタン、セリウム、ネオジム、ハフニウム、タンタル、タンゲステン、またはマグネシウムなどから選ばれた一種、または複数種が含まれていてもよい。

40

#### 【0261】

ここで、酸化物半導体が、インジウム、元素Mおよび亜鉛を有する場合を考える。

#### 【0262】

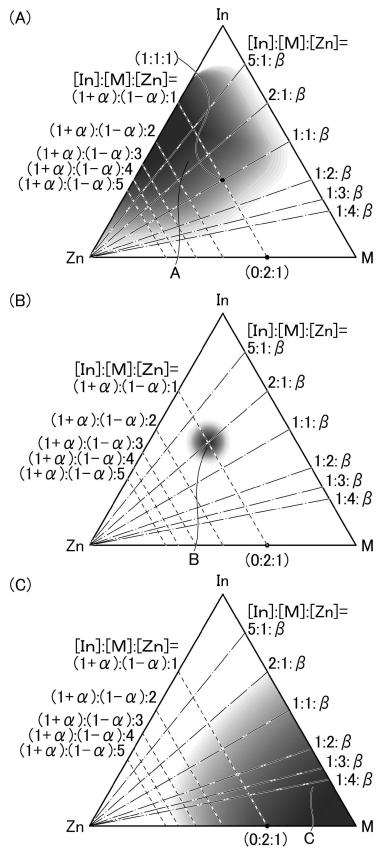

まず、図25(A)、図25(B)、および図25(C)を用いて、本発明に係る酸化物半導体が有するインジウム、元素Mおよび亜鉛の原子数比の好ましい範囲について説明す

50

る。なお、酸素の原子数比については記載しない。また、酸化物半導体が有するインジウム、元素M、および亜鉛の原子数比のそれぞれの項を [ I n ] 、 [ M ] 、および [ Z n ] とする。

### 【 0 2 6 3 】

図25(A)、図25(B)、および図25(C)において、破線は、 $[ I n ] : [ M ] : [ Z n ] = (1+ \quad) : (1- \quad) : 1$  の原子数比 (- 1 1) となるライン、 $[ I n ] : [ M ] : [ Z n ] = (1+ \quad) : (1- \quad) : 2$  の原子数比となるライン、 $[ I n ] : [ M ] : [ Z n ] = (1+ \quad) : (1- \quad) : 3$  の原子数比となるライン、 $[ I n ] : [ M ] : [ Z n ] = (1+ \quad) : (1- \quad) : 4$  の原子数比となるライン、および $[ I n ] : [ M ] : [ Z n ] = (1+ \quad) : (1- \quad) : 5$  の原子数比となるラインを表す。

10

### 【 0 2 6 4 】

また、一点鎖線は、 $[ I n ] : [ M ] : [ Z n ] = 1 : 1 : 0$  の原子数比 ( 0 ) となるライン、 $[ I n ] : [ M ] : [ Z n ] = 1 : 2 : 0$  の原子数比となるライン、 $[ I n ] : [ M ] : [ Z n ] = 1 : 3 : 0$  の原子数比となるライン、 $[ I n ] : [ M ] : [ Z n ] = 2 : 1 : 0$  の原子数比となるライン、および $[ I n ] : [ M ] : [ Z n ] = 5 : 1 : 0$  の原子数比となるラインを表す。

### 【 0 2 6 5 】

また、図25に示す、 $[ I n ] : [ M ] : [ Z n ] = 0 : 2 : 1$  の原子数比またはその近傍値の酸化物半導体は、スピネル型の結晶構造をとりやすい。

20

### 【 0 2 6 6 】

図25(A)および図25(B)では、本発明の一態様の酸化物半導体が有する、インジウム、元素M、および亜鉛の原子数比の好ましい範囲の一例について示している。

### 【 0 2 6 7 】

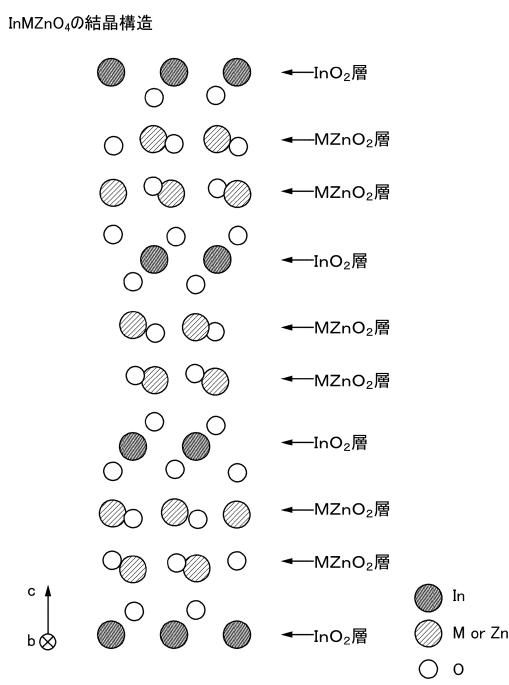

一例として、図26に、 $[ I n ] : [ M ] : [ Z n ] = 1 : 1 : 1$  である、 $I_n M Z_n O_4$  の結晶構造を示す。また、図26は、b軸に平行な方向から観察した場合の $I_n M Z_n O_4$  の結晶構造である。なお、図26に示すM、Zn、酸素を有する層(以下、(M, Zn)層)における金属元素は、元素Mまたは亜鉛を表している。この場合、元素Mと亜鉛の割合が等しいものとする。元素Mと亜鉛とは、置換が可能であり、配列は不規則である。

30

### 【 0 2 6 8 】

$I_n M Z_n O_4$  は、層状の結晶構造(層状構造ともいう)をとり、図26に示すように、インジウム、および酸素を有する層(以下、In層)が1に対し、元素M、亜鉛、および酸素を有する(M, Zn)層が2となる。

### 【 0 2 6 9 】

また、インジウムと元素Mは、互いに置換可能である。そのため、(M, Zn)層の元素Mがインジウムと置換し、(In, M, Zn)層と表すこともできる。この場合、In層が1に対し、(In, M, Zn)層が2である層状構造をとる。

### 【 0 2 7 0 】

$[ I n ] : [ M ] : [ Z n ] = 1 : 1 : 2$  となる原子数比の酸化物半導体は、In層が1に対し、(M, Zn)層が3である層状構造をとる。つまり、[ In ] および [ M ] に対し [ Zn ] が大きくなると、酸化物半導体が結晶化した場合、In層に対する(M, Zn)層の割合が増加する。

40

### 【 0 2 7 1 】

ただし、酸化物半導体中において、In層が1層に対し、(M, Zn)層の層数が非整数である場合、In層が1層に対し、(M, Zn)層の層数が整数である層状構造を複数種有する場合がある。例えば、 $[ I n ] : [ M ] : [ Z n ] = 1 : 1 : 1 . 5$  である場合、In層が1に対し、(M, Zn)層が2である層状構造と、(M, Zn)層が3である層状構造とが混在する層状構造となる場合がある。

50

**【0272】**

例えば、酸化物半導体をスパッタリング装置にて成膜する場合、ターゲットの原子数比からずれた原子数比の膜が形成される。特に、成膜時の基板温度によっては、ターゲットの [Zn] よりも、膜の [Zn] が小さくなる場合がある。

**【0273】**

また、酸化物半導体中に複数の相が共存する場合がある（二相共存、三相共存など）。例えば、[In] : [M] : [Zn] = 0 : 2 : 1 の原子数比の近傍値である原子数比では、スピネル型の結晶構造と層状の結晶構造との二相が共存しやすい。また、[In] : [M] : [Zn] = 1 : 0 : 0 を示す原子数比の近傍値である原子数比では、ビックスバイト型の結晶構造と層状の結晶構造との二相が共存しやすい。酸化物半導体中に複数の相が共存する場合、異なる結晶構造の間ににおいて、粒界（グレインバウンダリーともいう）が形成される場合がある。10

**【0274】**

また、インジウムの含有率を高くすることで、酸化物半導体のキャリア移動度（電子移動度）を高くすることができます。これは、インジウム、元素 M および亜鉛を有する酸化物半導体では、主として重金属の s 軌道がキャリア伝導に寄与しており、インジウムの含有率を高くすることにより、s 軌道が重なる領域がより大きくなるため、インジウムの含有率が高い酸化物半導体はインジウムの含有率が低い酸化物半導体と比較してキャリア移動度が高くなるためである。20

**【0275】**

一方、酸化物半導体中のインジウムおよび亜鉛の含有率が低くなると、キャリア移動度が低くなる。したがって、[In] : [M] : [Zn] = 0 : 1 : 0 を示す原子数比、およびその近傍値である原子数比（例えば図 25 (C) に示す領域 C）では、絶縁性が高くなる。

**【0276】**

したがって、本発明の一態様の酸化物半導体は、キャリア移動度が高く、かつ、粒界が少ない層状構造となりやすい、図 25 (A) の領域 A で示される原子数比を有することが好ましい。

**【0277】**

また、図 25 (B) に示す領域 B は、[In] : [M] : [Zn] = 4 : 2 : 3 から 4.1、およびその近傍値を示している。近傍値には、例えば、原子数比が [In] : [M] : [Zn] = 5 : 3 : 4 が含まれる。領域 B で示される原子数比を有する酸化物半導体は、特に、結晶性が高く、キャリア移動度も高い優れた酸化物半導体である。30

**【0278】**

なお、酸化物半導体が、層状構造を形成する条件は、原子数比によって一義的に定まらない。原子数比により、層状構造を形成するための難易の差はある。一方、同じ原子数比であっても、形成条件により、層状構造になる場合も層状構造にならない場合もある。したがって、図示する領域は、酸化物半導体が層状構造を有する原子数比を示す領域であり、領域 A 乃至領域 C の境界は厳密ではない。

**【0279】**

続いて、上記酸化物半導体をトランジスタに用いる場合について説明する。40

**【0280】**

なお、上記酸化物半導体をトランジスタに用いることで、粒界におけるキャリア散乱等を減少させることができるために、高い電界効果移動度のトランジスタを実現することができる。また、信頼性の高いトランジスタを実現することができる。

**【0281】**

また、トランジスタには、キャリア密度の低い酸化物半導体を用いることが好ましい。例えば、酸化物半導体は、キャリア密度が  $8 \times 10^{11} / \text{cm}^3$  未満、好ましくは  $1 \times 10^{11} / \text{cm}^3$  未満、さらに好ましくは  $1 \times 10^{10} / \text{cm}^3$  未満であり、 $1 \times 10^{-9} / \text{cm}^3$  以上とすればよい。50

**【0282】**

なお、高純度真性または実質的に高純度真性である酸化物半導体は、キャリア発生源が少ないため、キャリア密度を低くすることができる。また、高純度真性または実質的に高純度真性である酸化物半導体は、欠陥準位密度が低いため、トラップ準位密度も低くなる場合がある。

**【0283】**

また、酸化物半導体のトラップ準位に捕獲された電荷は、消失するまでに要する時間が長く、あたかも固定電荷のように振る舞うことがある。そのため、トラップ準位密度の高い酸化物半導体にチャネル領域が形成されるトランジスタは、電気特性が不安定となる場合がある。

10

**【0284】**

したがって、トランジスタの電気特性を安定にするためには、酸化物半導体中の不純物濃度を低減することが有効である。また、酸化物半導体中の不純物濃度を低減するためには、近接する膜中の不純物濃度も低減することが好ましい。不純物としては、水素、窒素、アルカリ金属、アルカリ土類金属、鉄、ニッケル、シリコン等がある。

**【0285】**

ここで、酸化物半導体中における各不純物の影響について説明する。

**【0286】**

酸化物半導体において、第14族元素の一つであるシリコンや炭素が含まれると、酸化物半導体において欠陥準位が形成される。このため、酸化物半導体または酸化物半導体と接する層との界面近傍においては、シリコンや炭素の濃度（二次イオン質量分析法（SIMS：Secondary Ion Mass Spectrometry）により得られる濃度）が、 $2 \times 10^{18}$  atoms / cm<sup>3</sup>以下、好ましくは $2 \times 10^{17}$  atoms / cm<sup>3</sup>以下となる領域を有するように制御する。

20

**【0287】**

また、酸化物半導体にアルカリ金属またはアルカリ土類金属が含まれると、欠陥準位を形成し、キャリアを生成する場合がある。したがって、アルカリ金属またはアルカリ土類金属が含まれているOSトランジスタはノーマリーオン特性となりやすい。このため、酸化物半導体中のアルカリ金属またはアルカリ土類金属の濃度を低減することが好ましい。具体的には、酸化物半導体中のアルカリ金属またはアルカリ土類金属の濃度（SIMS分析により得られる濃度）が、 $1 \times 10^{18}$  atoms / cm<sup>3</sup>以下、好ましくは $2 \times 10^{16}$  atoms / cm<sup>3</sup>以下となる領域を有するように制御する。

30

**【0288】**

また、酸化物半導体において、窒素が含まれると、キャリアである電子が生じ、キャリア密度が増加し、n型化しやすい。この結果、窒素が含まれている酸化物半導体を半導体に用いたトランジスタはノーマリーオン特性となりやすい。したがって、該酸化物半導体において、窒素はできる限り低減されていることが好ましい。具体的には、酸化物半導体中の窒素濃度（SIMS分析により得られる濃度）が、 $5 \times 10^{19}$  atoms / cm<sup>3</sup>未満、好ましくは $5 \times 10^{18}$  atoms / cm<sup>3</sup>以下、より好ましくは $1 \times 10^{18}$  atoms / cm<sup>3</sup>以下、さらに好ましくは $5 \times 10^{17}$  atoms / cm<sup>3</sup>以下となる領域を有するように制御する。

40

**【0289】**

また、酸化物半導体に含まれる水素は、金属原子と結合する酸素と反応して水になるため、酸素欠損を形成する場合がある。該酸素欠損に水素が入ることで、キャリアである電子が生成される場合がある。また、水素の一部が金属原子と結合する酸素と結合して、キャリアである電子を生成することができる。したがって、水素が含まれているOSトランジスタはノーマリーオン特性となりやすい。このため、酸化物半導体中の水素はできる限り低減されていることが好ましい。具体的には、酸化物半導体中の水素濃度（SIMS分析により得られる濃度）が、 $1 \times 10^{20}$  atoms / cm<sup>3</sup>未満、好ましくは $1 \times 10^{19}$  atoms / cm<sup>3</sup>未満、より好ましくは $5 \times 10^{18}$  atoms / cm<sup>3</sup>未満、さらに

50

好ましくは  $1 \times 10^{18}$  atoms/cm<sup>3</sup> 未満となる領域を有するように制御する。

#### 【0290】

不純物が十分に低減された酸化物半導体をトランジスタのチャネル形成領域に用いることで、安定した電気特性を付与することができる。また、高純度化された酸化物半導体をチャネル形成領域に用いたトランジスタのオフ電流は極めて小さい。例えば、ソースヒドレインとの間の電圧を 0.1V、5V、または、10V 程度とした場合に、トランジスタのチャネル幅あたりのオフ電流を数 y A / μm 乃至数 z A / μm にまで低減することが可能となる。

#### 【0291】

続いて、該酸化物半導体を 2 層構造、または 3 層構造とした場合について述べる。酸化物半導体 S1、酸化物半導体 S2、および酸化物半導体 S3 の積層構造に接する絶縁体のバンド図と、酸化物半導体 S2 および酸化物半導体 S3 の積層構造に接する絶縁体のバンド図と、について、図 27 を用いて説明する。なお、酸化物半導体 S1 は酸化物半導体層 130a、酸化物半導体 S2 は酸化物半導体層 130b、酸化物半導体 S3 は酸化物半導体層 130c に相当する。

10

#### 【0292】

図 27 (A) は、絶縁体 I1、酸化物半導体 S1、酸化物半導体 S2、酸化物半導体 S3、および絶縁体 I2 を有する積層構造の膜厚方向のバンド図の一例である。また、図 27 (B) は、絶縁体 I1、酸化物半導体 S2、酸化物半導体 S3、および絶縁体 I2 を有する積層構造の膜厚方向のバンド図の一例である。なお、バンド図は、理解を容易にするため絶縁体 I1、酸化物半導体 S1、酸化物半導体 S2、酸化物半導体 S3、および絶縁体 I2 の伝導帯下端のエネルギー準位 (Ec) を示す。

20

#### 【0293】

酸化物半導体 S1、酸化物半導体 S3 は、酸化物半導体 S2 よりも伝導帯下端のエネルギー準位が真空準位に近く、代表的には、酸化物半導体 S2 の伝導帯下端のエネルギー準位と、酸化物半導体 S1、酸化物半導体 S3 の伝導帯下端のエネルギー準位との差が、0.15 eV 以上、または 0.5 eV 以上、かつ 2 eV 以下、または 1 eV 以下であることが好ましい。すなわち、酸化物半導体 S1、酸化物半導体 S3 の電子親和力よりも、酸化物半導体 S2 の電子親和力が大きく、酸化物 S1、酸化物 S3 の電子親和力と、酸化物 S2 の電子親和力との差は、0.15 eV 以上、または 0.5 eV 以上、かつ 2 eV 以下、または 1 eV 以下であることが好ましい。

30

#### 【0294】

図 27 (A)、および図 27 (B) に示すように、酸化物半導体 S1、酸化物半導体 S2、酸化物半導体 S3 において、伝導帯下端のエネルギー準位はなだらかに変化する。換言すると、連続的に変化または連続接合するともいうことができる。このようなバンド図を有するためには、酸化物半導体 S1 と酸化物半導体 S2 との界面、または酸化物半導体 S2 と酸化物半導体 S3 との界面において形成される混合層の欠陥準位密度を低くするといい。

40

#### 【0295】

具体的には、酸化物半導体 S1 と酸化物半導体 S2、酸化物半導体 S2 と酸化物半導体 S3 が、酸素以外に共通の元素を有する（主成分とする）ことで、欠陥準位密度が低い混合層を形成することができる。例えば、酸化物半導体 S2 が In-Ga-Zn 酸化物半導体の場合、酸化物半導体 S1、酸化物半導体 S3 として、In-Ga-Zn 酸化物半導体、Ga-Zn 酸化物半導体、酸化ガリウムなどを用いるとよい。

#### 【0296】

このとき、キャリアの主たる経路は酸化物半導体 S2 となる。酸化物半導体 S1 と酸化物半導体 S2 との界面、および酸化物半導体 S2 と酸化物半導体 S3 との界面における欠陥準位密度を低くすることができるため、界面散乱によるキャリア伝導への影響が小さく、高いオン電流が得られる。

#### 【0297】

50

トラップ準位に電子が捕獲されることで、捕獲された電子は固定電荷のように振る舞うため、トランジスタのしきい値電圧はプラス方向にシフトしてしまう。酸化物半導体S1、酸化物半導体S3を設けることにより、トラップ準位を酸化物半導体S2より遠ざけることができる。当該構成とすることで、トランジスタのしきい値電圧がプラス方向にシフトすることを防止することができる。

#### 【0298】

酸化物半導体S1、酸化物半導体S3は、酸化物半導体S2と比較して、導電率が十分に低い材料を用いる。このとき、酸化物半導体S2、酸化物半導体S2と酸化物半導体S1との界面、および酸化物半導体S2と酸化物半導体S3との界面が、主にチャネル領域として機能する。例えば、酸化物半導体S1、酸化物半導体S3には、図25(C)において、絶縁性が高くなる領域Cで示す原子数比の酸化物半導体を用いればよい。10

#### 【0299】

特に、酸化物半導体S2に領域Aで示される原子数比の酸化物半導体を用いる場合、酸化物半導体S1および酸化物半導体S3には、[M]/[In]が1以上、好ましくは2以上となる原子数比の酸化物半導体を用いることが好ましい。また、酸化物半導体S3として、十分に高い絶縁性を得ることができる[M]/([Zn]+[In])が1以上となるような原子数比の酸化物半導体を用いることが好適である。

#### 【0300】

本実施の形態に示す構成は、他の実施の形態に示す構成と適宜組み合わせて用いることができる。20

#### 【0301】

##### (実施の形態5)

以下では、本発明の一態様に用いることのできる酸化物半導体の構造について説明する。

#### 【0302】

なお、本明細書において、「平行」とは、二つの直線が-10°以上10°以下の角度で配置されている状態をいう。したがって、-5°以上5°以下の場合も含まれる。また、「垂直」とは、二つの直線が80°以上100°以下の角度で配置されている状態をいう。したがって、85°以上95°以下の場合も含まれる。

#### 【0303】

また、本明細書において、結晶が三方晶または菱面体晶である場合、六方晶系として表す。30

#### 【0304】

##### <酸化物半導体の構造>

以下では、酸化物半導体の構造について説明する。

#### 【0305】

酸化物半導体は、単結晶酸化物半導体と、それ以外の非単結晶酸化物半導体と、に分けられる。非単結晶酸化物半導体としては、CAAC-OS(c-axis-aligned crystalline oxide semiconductor)、多結晶酸化物半導体、nc-OS(nanocrystalline oxide semiconductor)、擬似非晶質酸化物半導体(a-like OS: amorphous-like oxide semiconductor)および非晶質酸化物半導体などがある。40

#### 【0306】

また別の観点では、酸化物半導体は、非晶質酸化物半導体と、それ以外の結晶性酸化物半導体と、に分けられる。結晶性酸化物半導体としては、単結晶酸化物半導体、CAAC-OS、多結晶酸化物半導体およびnc-OSなどがある。

#### 【0307】

非晶質構造は、一般に、等方的であって不均質構造を持たない、準安定状態で原子の配置が固定化していない、結合角度が柔軟である、短距離秩序は有するが長距離秩序を有さない、などといわれている。50

## 【0308】

逆の見方をすると、安定な酸化物半導体を完全な非晶質（c o m p l e t e l y a m o r p h o u s）酸化物半導体とは呼べない。また、等方的でない（例えば、微小な領域において周期構造を有する）酸化物半導体を、完全な非晶質酸化物半導体とは呼べない。一方、a - l i k e O Sは、等方的でないが、鬆（ボイドともいう。）を有する不安定な構造である。不安定であるという点では、a - l i k e O Sは、物性的に非晶質酸化物半導体に近い。

## 【0309】

&lt; C A A C - O S &gt;

まずは、C A A C - O Sについて説明する。

10

## 【0310】

C A A C - O Sは、c 軸配向した複数の結晶部（ペレットともいう。）を有する酸化物半導体の一種である。

## 【0311】

C A A C - O SをX線回折（X R D : X - R a y D i f f r a c t i o n）によって解析した場合について説明する。例えば、空間群R - 3 mに分類されるInGaZnO<sub>4</sub>の結晶を有するC A A C - O Sに対し、o u t - o f - p l a n e法による構造解析を行うと、図28(A)に示すように回折角(2θ)が31°近傍にピークが現れる。このピークは、InGaZnO<sub>4</sub>の結晶の(009)面に帰属されることから、C A A C - O Sでは、結晶がc軸配向性を有し、c軸がC A A C - O Sの膜を形成する面（被形成面ともいう。）、または上面に略垂直な方向を向いていることが確認できる。なお、2θが31°近傍のピークの他に、2θが36°近傍にもピークが現れる場合がある。2θが36°近傍のピークは、空間群Fd - 3 mに分類される結晶構造に起因する。そのため、C A A C - O Sは、該ピークを示さないことが好ましい。

20

## 【0312】

一方、C A A C - O Sに対し、被形成面に平行な方向からX線を入射させるi n - p l a n e法による構造解析を行うと、2θが56°近傍にピークが現れる。このピークは、InGaZnO<sub>4</sub>の結晶の(110)面に帰属される。そして、2θを56°近傍に固定し、試料面の法線ベクトルを軸(c軸)として試料を回転させながら分析（スキャン）を行っても、図28(B)に示すように明瞭なピークは現れない。一方、単結晶InGaZnO<sub>4</sub>に対し、2θを56°近傍に固定してスキャンした場合、図28(C)に示すように(110)面と等価な結晶面に帰属されるピークが6本観察される。したがって、X R Dを用いた構造解析から、C A A C - O Sは、a軸およびb軸の配向が不規則であることが確認できる。

30

## 【0313】

次に、電子回折によって解析したC A A C - O Sについて説明する。例えば、InGaZnO<sub>4</sub>の結晶を有するC A A C - O Sに対し、C A A C - O Sの被形成面に平行にプローブ径が300 nmの電子線を入射させると、図28(D)に示すような回折パターン（制限視野電子回折パターンともいう。）が現れる場合がある。この回折パターンには、InGaZnO<sub>4</sub>の結晶の(009)面に起因するスポットが含まれる。したがって、電子回折によっても、C A A C - O Sに含まれるペレットがc軸配向性を有し、c軸が被形成面または上面に略垂直な方向を向いていることがわかる。一方、同じ試料に対し、試料面に垂直にプローブ径が300 nmの電子線を入射させたときの回折パターンを図28(E)に示す。図28(E)より、リング状の回折パターンが確認される。したがって、プローブ径が300 nmの電子線を用いた電子回折によっても、C A A C - O Sに含まれるペレットのa軸およびb軸は配向性を有さないことがわかる。なお、図28(E)における第1リングは、InGaZnO<sub>4</sub>の結晶の(010)面および(100)面などに起因すると考えられる。また、図28(E)における第2リングは(110)面などに起因すると考えられる。

40

## 【0314】

50

また、透過型電子顕微鏡(TEM: Transmission Electron Microscope)によって、CAAC-OSの明視野像と回折パターンとの複合解析像(高分解能TEM像ともいう。)を観察すると、複数のペレットを確認することができる。一方、高分解能TEM像であってもペレット同士の境界、即ち結晶粒界(グレインバウンドリーともいう。)を明確に確認することができない場合がある。そのため、CAAC-OSは、結晶粒界に起因する電子移動度の低下が起こりにくいといえる。

#### 【0315】

図29(A)に、試料面と略平行な方向から観察したCAAC-OSの断面の高分解能TEM像を示す。高分解能TEM像の観察には、球面収差補正(Spherical Aberration Corrector)機能を用いた。球面収差補正機能を用いた高分解能TEM像を、特にCs補正高分解能TEM像と呼ぶ。Cs補正高分解能TEM像は、例えば、日本電子株式会社製原子分解能分析電子顕微鏡JEM-ARM200Fなどによって観察することができる。

#### 【0316】

図29(A)より、金属原子が層状に配列している領域であるペレットを確認することができる。ペレット一つの大きさは1nm以上のものや、3nm以上のものがあることがわかる。したがって、ペレットを、ナノ結晶(nc:nanocrystal)と呼ぶこともできる。また、CAAC-OSを、CANC(C-Axis Aligned nanocrystals)を有する酸化物半導体と呼ぶこともできる。ペレットは、CAAC-OSの被形成面または上面の凹凸を反映しており、CAAC-OSの被形成面または上面と平行となる。

#### 【0317】

また、図29(B)および図29(C)に、試料面と略垂直な方向から観察したCAAC-OSの平面のCs補正高分解能TEM像を示す。図29(D)および図29(E)は、それぞれ図29(B)および図29(C)を画像処理した像である。以下では、画像処理の方法について説明する。まず、図29(B)を高速フーリエ変換(FFT: Fast Fourier Transform)処理することでFFT像を取得する。次に、取得したFFT像において原点を基準に、 $2.8\text{ nm}^{-1}$ から $5.0\text{ nm}^{-1}$ の間の範囲を残すマスク処理をする。次に、マスク処理したFFT像を、逆高速フーリエ変換(IFFT: Inverse Fast Fourier Transform)処理することで画像処理した像を取得する。こうして取得した像をFFTフィルタリング像と呼ぶ。FFTフィルタリング像は、Cs補正高分解能TEM像から周期成分を抜き出した像であり、格子配列を示している。

#### 【0318】

図29(D)では、格子配列の乱れた箇所を破線で示している。破線で囲まれた領域が、一つのペレットである。そして、破線で示した箇所がペレットとペレットとの連結部である。破線は、六角形状であるため、ペレットが六角形状であることがわかる。なお、ペレットの形状は、正六角形状とは限らず、非正六角形状である場合が多い。

#### 【0319】

図29(E)では、格子配列の揃った領域と、別の格子配列の揃った領域との間を点線で示している。点線近傍においても、明確な結晶粒界を確認することはできない。点線近傍の格子点を中心に周囲の格子点を繋ぐと、歪んだ六角形や、五角形または/および七角形などが形成できる。即ち、格子配列を歪ませることによって結晶粒界の形成を抑制していることがわかる。これは、CAAC-OSが、a-b面方向において原子間の結合距離が稠密でないことや、金属元素が置換することで原子間の結合距離が変化することなどによって、歪みを許容することができるためと考えられる。

#### 【0320】

以上に示すように、CAAC-OSは、c軸配向性を有し、かつa-b面方向において複数のペレット(ナノ結晶)が連結し、歪みを有した結晶構造となっている。よって、CAAC-OSを、CAA crystal(c-axis-aligned a-b-p1

10

20

30

40

50

ane - anchored crystal) を有する酸化物半導体と称することもできる。

#### 【0321】

C A A C - O S は結晶性の高い酸化物半導体である。酸化物半導体の結晶性は不純物の混入や欠陥の生成などによって低下する場合があるため、逆の見方をすると C A A C - O S は不純物や欠陥(酸素欠損など)の少ない酸化物半導体ともいえる。

#### 【0322】

なお、不純物は、酸化物半導体の主成分以外の元素で、水素、炭素、シリコン、遷移金属元素などがある。例えば、シリコンなどの、酸化物半導体を構成する金属元素よりも酸素との結合力の強い元素は、酸化物半導体から酸素を奪うことで酸化物半導体の原子配列を乱し、結晶性を低下させる要因となる。また、鉄やニッケルなどの重金属、アルゴン、二酸化炭素などは、原子半径(または分子半径)が大きいため、酸化物半導体の原子配列を乱し、結晶性を低下させる要因となる。10

#### 【0323】

酸化物半導体が不純物や欠陥を有する場合、光や熱などによって特性が変動する場合がある。例えば、酸化物半導体に含まれる不純物は、キャリアトラップとなる場合や、キャリア発生源となる場合がある。例えば、酸化物半導体中の酸素欠損は、キャリアトラップとなる場合や、水素を捕獲することによってキャリア発生源となる場合がある。

#### 【0324】

不純物および酸素欠損の少ない C A A C - O S は、キャリア密度の低い酸化物半導体である。具体的には、 $8 \times 10^{11} \text{ cm}^{-3}$  未満、好ましくは  $1 \times 10^{11} \text{ cm}^{-3}$  未満、さらに好ましくは  $1 \times 10^{10} \text{ cm}^{-3}$  未満であり、 $1 \times 10^{-9} \text{ cm}^{-3}$  以上のキャリア密度の酸化物半導体とすることができます。そのような酸化物半導体を、高純度真性または実質的に高純度真性な酸化物半導体と呼ぶ。C A A C - O S は、不純物濃度が低く、欠陥準位密度が低い。即ち、安定な特性を有する酸化物半導体であるといえる。20

#### 【0325】

< n c - O S >

次に、n c - O S について説明する。

#### 【0326】

n c - O S を X R D によって解析した場合について説明する。例えば、n c - O S に対し、out-of-plane 法による構造解析を行うと、配向性を示すピークが現れない。即ち、n c - O S の結晶は配向性を有さない。30

#### 【0327】

また、例えば、InGaZnO<sub>4</sub> の結晶を有する n c - O S を薄片化し、厚さが 34 nm の領域に対し、被形成面に平行にプローブ径が 50 nm の電子線を入射させると、図 30 (A) に示すようなリング状の回折パターン(ナノビーム電子回折パターン)が観測される。また、同じ試料にプローブ径が 1 nm の電子線を入射させたときの回折パターン(ナノビーム電子回折パターン)を図 30 (B) に示す。図 30 (B) より、リング状の領域内に複数のスポットが観測される。したがって、n c - O S は、プローブ径が 50 nm の電子線を入射させることでは秩序性が確認されないが、プローブ径が 1 nm の電子線を入射させることでは秩序性が確認される。40

#### 【0328】

また、厚さが 10 nm 未満の領域に対し、プローブ径が 1 nm の電子線を入射させると、図 30 (C) に示すように、スポットが略正六角状に配置された電子回折パターンを観測される場合がある。したがって、厚さが 10 nm 未満の範囲において、n c - O S が秩序性の高い領域、即ち結晶を有することがわかる。なお、結晶が様々な方向を向いているため、規則的な電子回折パターンが観測されない領域もある。

#### 【0329】

図 30 (D) に、被形成面と略平行な方向から観察した n c - O S の断面の Cs 補正高分解能 TEM 像を示す。n c - O S は、高分解能 TEM 像において、補助線で示す箇所など50