(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) DE 698 24 972 T2 2005.07.14

(12)

## Übersetzung der europäischen Patentschrift

(97) EP 1 043 774 B1

(21) Deutsches Aktenzeichen: 698 24 972.0

(86) PCT-Aktenzeichen: PCT/JP98/05770

(96) Europäisches Aktenzeichen: 98 961 441.7

(87) PCT-Veröffentlichungs-Nr.: WO 99/034445

(86) PCT-Anmeldetag: 21.12.1998

(87) Veröffentlichungstag

der PCT-Anmeldung: 08.07.1999

(97) Erstveröffentlichung durch das EPA: 11.10.2000

(97) Veröffentlichungstag

der Patenterteilung beim EPA: 07.07.2004

(47) Veröffentlichungstag im Patentblatt: 14.07.2005

(51) Int Cl.<sup>7</sup>: G11C 5/14

G11C 11/34, H01L 27/04, G11C 11/407

(30) Unionspriorität:

35927197 26.12.1997 JP

(84) Benannte Vertragsstaaten:

DE, FR, GB, IT

(73) Patentinhaber:

Hitachi, Ltd., Tokio/Tokyo, JP

(72) Erfinder:

Mizuno, Hiroyuki, Kokubunji-shi-Tokyo 185-8601, JP; ISHIBASHI, Koichiro, Kokubunji-shi, Tokyo 185-8601, JP; SHIMURA, Takanori, Kokubunji-shi, Tokyo 185-8601, JP; HATTORI, Toshihiro, Kodaira-shi, Tokyo 187-8588, JP

(74) Vertreter:

BEETZ & PARTNER Patentanwälte, 80538 München

(54) Bezeichnung: INTEGRIERTER HALBLEITERSCHALTKREIS

Anmerkung: Innerhalb von neun Monaten nach der Bekanntmachung des Hinweises auf die Erteilung des europäischen Patents kann jedermann beim Europäischen Patentamt gegen das erteilte europäische Patent Einspruch einlegen. Der Einspruch ist schriftlich einzureichen und zu begründen. Er gilt erst als eingelebt, wenn die Einspruchsgebühr entrichtet worden ist (Art. 99 (1) Europäisches Patentübereinkommen).

Die Übersetzung ist gemäß Artikel II § 3 Abs. 1 IntPatÜG 1991 vom Patentinhaber eingereicht worden. Sie wurde vom Deutschen Patent- und Markenamt inhaltlich nicht geprüft.

**Beschreibung****TECHNISCHES GEBIET**

**[0001]** Die vorliegende Erfindung bezieht sich auf eine Halbleiter-IC-Einheit und insbesondere auf eine Halbleiter-IC-Einheit einerseits mit hoher Geschwindigkeit und andererseits mit niedrigem Stromverbrauch.

**[0002]** Die vorliegende Anmeldung ist Teil der US-Patentanmeldung PCT/JP97/04253 vom 21. November 1997, die EP-A-0 943 978 entspricht.

**HINTERGRUND**

**[0003]** Gegenwärtig werden weitgehend integrierte CMOS-Schaltungen (Integrated Circuits, IC) verwendet, um eine Halbleiter-IC-Einheit wie zum Beispiel einen Mikroprozessor und dergleichen herzustellen. Bei einem CMOS-IC wird elektrische Leistung auf zwei Arten verbraucht: als dynamischer Stromverbrauch und als statischer Stromverbrauch. Der dynamische Stromverbrauch ist durch Aufladen und Entladen zu den Schaltzeitpunkten bedingt, und der statische Stromverbrauch ist durch unterschwelligen Leckstrom bedingt. Der dynamische Stromverbrauch führt dazu, dass der Verbrauch bei großen Strömen proportional mit dem Quadrat einer Versorgungsspannung VDD steigt, so dass die Versorgungsspannung herabgesetzt werden sollte, um den Stromverbrauch des betreffenden CMOS-IC effektiv zu senken. In den vergangenen Jahren wurden daher immer niedrigere Versorgungsspannungen eingesetzt, um dieses Ziel zu erreichen.

**[0004]** Auf der anderen Seite werden einige der gegenwärtig verfügbaren Mikroprozessoren mit Energiesparfunktion mit einer Leistungssteuerung ausgestattet und der Prozessor mit mehreren Betriebszuständen versehen, so dass die Versorgung einer aktiven Einheit mit dem Taktsignal zu Standby-Intervallen gestoppt wird, wenn sich dieser Betriebszustand einstellt.

**[0005]** Da auf diese Art die Versorgung mit dem Taktsignal gestoppt wird, ist es möglich, den unnötigen dynamischen Stromverbrauch in einer solchen aktiven Einheit so weit wie möglich zu reduzieren. Der statische Stromverbrauch, der durch einen unterschwelligen Leckstrom hervorgerufen wird, kann jedoch nicht reduziert werden und bleibt in diesem Intervall immer noch auf seinem ursprünglichen Niveau.

**[0006]** Die Betriebsgeschwindigkeit einer CMOS-Schaltung fällt bei niedrigen Versorgungsspannungen ab. Um eine derartige Abnahme der Geschwindigkeit bei einer CMOS-Schaltung zu vermeiden, muss in Verbindung mit der Abnahme der Ver-

sorgungsspannung daher die Schwellenspannung des MOS-Transistors herabgesetzt werden. Wenn eine Schwellenspannung herabgesetzt wird, so nimmt jedoch der unterschwellige Leckstrom extrem zu. Und mit dem Absenken der Versorgungsspannung nimmt der statische Stromverbrauch auf Grund des unterschwelligen Leckstroms in stärkerem Maße zu, als es üblich ist. Dies ist der Grund dafür, dass nun dringend eine Halbleiter-IC-Einheit wie zum Beispiel ein Mikroprozessor hergestellt werden muss, der sowohl für den Betrieb mit hoher Geschwindigkeit geeignet ist als auch einen niedrigen Stromverbrauch aufweist.

**[0007]** Um dieses Problem zu lösen, wurde beispielsweise in der amtlichen Gazette der veröffentlichten ungeprüften japanischen Patentanmeldungen unter Nr. Hei-6-53496 (EP-A-0 573 009) ein Verfahren zum Steuern einer Schwellenspannung von MOS-Transistoren durch Vorgabe einer variablen Substratvorspannung vorgeschlagen.

**[0008]** Die Substratvorspannung wird im aktiven Zustand auf das Potential der Stromquelle für PMOS (P-Kanal-MOS-Transistoren) und das Massepotential für NMOS (N-Kanal-MOS-Transistoren) gesetzt, wenn die entsprechende CMOS-Schaltung für den Betrieb mit hoher Geschwindigkeit eingesetzt werden soll. Auf der anderen Seite wird im Standby-Zustand, in dem der CMOS nicht für den Betrieb mit hoher Geschwindigkeit eingesetzt werden soll, die Substratvorspannung auf ein Potential gesetzt, das höher als die Versorgungsspannung für PMOS und niedriger als die Versorgungsspannung für NMOS ist (im Folgenden wird dieser Betrieb oft als "Anlegen einer Vorspannung an ein Substrat" bezeichnet).

**[0009]** Mit einer derartigen Vorgabe einer Substratvorspannung im Standby-Zustand wird es möglich, den Schwellenwertpegel der MOS-Transistoren, aus denen die betreffende CMOS-Schaltung besteht, anzuheben, wodurch der statische Stromverbrauch reduziert wird, der durch einen unterschwelligen Leckstrom hervorgerufen wird.

**[0010]** In US 5 659 517 wird eine Halbleiterspeichervorrichtung beschrieben, wie sie in dem Oberbegriff von Anspruch 1 zusammengefasst ist. Die Leitfähigkeit der MOS-Transistoren Q1 und Q2 ist abhängig von einem Signal, das einen Betriebszyklus definiert, und sie stellen eine elektrische Verbindung mit einer Hauptstromquellenleitung sowie mit einer Nebenstromquellenleitung her. Q1 ist zwischen die Hauptstromquellenleitung und die Nebenstromquellenleitung geschaltet, und Q1 ist zwischen die Nebenmasseleitung und die Hauptmasseleitung geschaltet.

**[0011]** In JP 08-249882 A wird eine integrierte Halbleiterschaltung offenbart, bei der eine Substratspannungserfassungsschaltung, eine Oszillatorschaltung

und eine Spannungsgeneratorschaltung vorgesehen sind, um eine bestimmte Spannung, durch die das Substrat in Gegenrichtung vorgespannt wird, an das Substrat anzulegen.

**[0012]** In EP 0 573 009 A1 wird eine Halbleitervorrichtung offenbart, bei der die Substratvorspannungsgeneratorschaltung über eine I/O-Schaltung gesteuert wird. Die Vorspannung an dem Substrat und dem P-Wannenbereich wird je nach Betriebsart der Hauptschaltung variiert.

#### BESCHREIBUNG DER ERFINDUNG

**[0013]** Um eine Halbleiter-IC-Einheit wie zum Beispiel einen Mikroprozessoren und dergleichen herzustellen, so dass sowohl ein Betrieb mit hoher Geschwindigkeit möglich ist als auch die Stromaufnahme gering ist, muss die Substratvorspannung wie oben beschrieben für jede CMOS-Schaltung eingestellt werden, so dass die Schwellenspannung der MOS-Transistoren herabgesetzt wird, wenn die Halbleiter-IC-Einheit aktiv ist, und angehoben wird, wenn die Halbleiter-IC-Einheit im Standby läuft, so dass dadurch der unterschwellige Leckstrom reduziert wird.

**[0014]** Als ein Ergebnis der Untersuchung hat der Erfinder jedoch festgestellt, dass die folgenden Probleme nach wie vor ungelöst sind, wenn die Substratvorspannung in einer tatsächlichen Halbleiter-IC-Einheit eingestellt wird.

- (1) Eine Schaltung zum Steuern der Substratvorspannung muss nach wie vor einfach getestet werden können.

- (2) Eine CMOS-Schaltung muss vor Fehlfunktionen geschützt werden, indem die Substratvorspannung eingestellt wird.

- (3) Eine Zunahme der Schaltungsfläche muss minimiert werden, indem die Substratvorspannung eingestellt wird.

- (4) Eine Halbleiter-IC-Einheit muss vor Fehlfunktionen geschützt werden, wenn die Substratvorspannung umgeschaltet wird.

**[0015]** Um die obigen Probleme zu lösen, werden erfundungsgemäß die folgenden, als wesentlich angesehenen Einrichtungen vorgeschlagen.

**[0016]** Um es einfacher zu machen, die Schaltung zum Steuern der Substratvorspannung zu testen, wird der Ausgang der negativen Spannungsgeneratorschaltung mit einem Pad verbunden. Mit anderen Worten, die negative Spannungsgeneratorschaltung muss überprüft werden, wenn ein vorgegebener Spannungspegel als Ausgangssignal erreicht wird. Für diese Überprüfung sollte die negative Spannungsgeneratorschaltung mit einem Anschluss versehen werden, an dem das Signal am Ausgang abgegriffen werden kann, so wie es ist.

**[0017]** Um die Substrat-Impedanz abzusenken, werden mehrere Substrat-MOS-Transistoren in der Hauptschaltung zur Steuerung der Substratvorspannung vorgesehen. Die Substrat-Treiber-MOS-Transistoren werden verwendet, um die Substratvorspannung bereitzustellen, wenn die Halbleiter-IC-Einheit aktiv ist. Dies ist erforderlich, da die Impedanz herabgesetzt werden muss, um das Substratpotential zu fixieren und Schwankungen der Transistorschwellenpegel zu unterdrücken, wenn die IC-Schaltung aktiv ist, so dass die jeweiligen Schaltungen in der Hauptschaltung dadurch in die Lage versetzt werden, zu arbeiten.

**[0018]** Die Treiberleistung der Halbleiter-IC-Einheit steigt im aktiven Zustand mehr als im Standby-Zustand. Vorzugsweise sollte die Treiberleistung daher das Fünffache betragen. Ideal sollte sie das Zehnfache von derjenigen in dem Standby-Zustand betragen.

**[0019]** Üblicherweise wird jede Schaltung instabil, wenn die Substratvorspannung umgeschaltet wird. Um dies zu vermeiden, ist das Gate-Steuersignal zur Steuerung der Gate-Spannung eines Substrat-Treiber-MOS-Transistors fest verdrahtet, so dass das Steuersignal nach der Verbindung mit dem Substrat-Treiber-MOS-Transistor an die Schaltung zur Steuerung der Substratvorspannung zurückgeführt wird, und das Potential des zurückgeführten Signals wird durch die Schaltung zum Steuern der Substratvorspannung verwendet, um zu erfassen, ob die Hauptschaltungssubstratvorspannung stabilisiert ist.

**[0020]** Die Halbleiter-IC-Einheit ist mit einer Einschalt-Reset-Schaltung versehen. Die Einschalt-Reset-Schaltung stellt sicher, dass die Hauptschaltung mit Strom versorgt wird. Die Halbleiter-IC-Einheit wird im aktiven Zustand gehalten, so dass jeder Substrat-Treiber-MOS-Transistor die Substratvorspannung auf flache Art und Weise für eine feste Zeit bereitstellt, nachdem die Hauptschaltung mit Strom versorgt worden ist.

**[0021]** Während die Halbleiter-IC-Einheit aus dem Standby-Zustand in den aktiven Zustand überwechselt, steuert die Schaltung für die Steuerung der Substratvorspannung die Ausgangsimpedanz des Gate-Steuersignals so, dass diese größer als die Impedanz wird, die eingestellt wird, nachdem die Halbleiter-IC-Einheit vollständig in den aktiven Zustand übergewechselt ist.

**[0022]** Die Halbleiter-IC-Einheit ist außerdem mit einer negativen Spannungsgeneratorschaltung versehen. Die Schaltung für die Steuerung der Substratvorspannung steuert die Ausgangsimpedanz der negativen Spannungsgeneratorschaltung im Standby-Zustand so, dass sie kleiner als die Ausgangsimpedanz im aktiven Zustand wird.

**[0023]** Die Hauptschaltung umfasst mehrere Zellen. Diese Zellen bilden ein Stromversorgungsnetz, das durch die ersten Metall-Ebenen bestimmt wird. Ein weiteres Stromversorgungsnetz wird durch die zweiten Verdrahtungsschichten gebildet, die orthogonal zu den ersten Metall-Ebenen verlaufen. Außerdem ist eine Schaltzelle an jedem Schnittpunkt der Stromversorgungsnetze mit den ersten und zweiten Verdrahtungsschichten angeordnet. Die Stromversorgungsnetze mit der ersten und zweiten Verdrahtungsschicht sind in den Schaltzellen miteinander verbunden. Ein Substrat-Treiber-MOS-Transistor, wie er oben beschrieben wurde, ist in jeder dieser Schaltzellen vorgesehen.

**[0024]** Die Substratvorspannungsversorgungsleitung eines MOS-Transistors bei einer der obigen Zellen ist aus den ersten Metall-Ebenen aufgebaut, die parallel zu dem Stromversorgungsnetz verlaufen, das in den ersten Metall-Ebenen angeordnet ist, wie auch die zweiten Verdrahtungsschichten, die parallel zu dem Stromversorgungsnetz mit den zweiten Verdrahtungsschichten verlaufen. Auf die gleiche Art wie diese Stromversorgungsnetze ist die Substratvorspannungsversorgungsleitung mit den ersten Metall-Ebenen mit der Substratvorspannungsversorgungsleitung mit den zweiten Verdrahtungsschichten in jeder der Schaltzellen verbunden, so dass dadurch das Gate-Steuersignal zum Steuern der Gate-Spannung bei jedem Substrat-Treiber-MOS-Transistor durch die zweiten Verdrahtungsschichten über der Schaltzelle parallel zu dem Stromversorgungsnetz mit den zweiten Verdrahtungsschichten bereitgestellt wird. Das Gate-Steuersignal wird dann mit dem Gate-Anschluss des Substrat-Treiber-MOS-Transistors in einer der oben beschriebenen Schaltzellen verbunden.

**[0025]** Die erfindungsgemäße Halbleiter-IC-Einheit ist in Anspruch 1 definiert. Sie umfasst eine Hauptschaltung aus wenigstens einem Transistor, eine Substratvorspannungssteuerschaltung zum Steuern einer Spannung, die an jedes Transistorsubstrat angelegt werden soll, und eine Standby-Steuerschaltung zum Umschalten zwischen wenigstens den zwei Zuständen aktiv und Standby. In dem aktiven Zustand wird die Substratvorspannungssteuerschaltung verwendet, um den unterschwelligen Leckstrom in der Hauptschaltung anzuheben. In dem Standby-Zustand wird die Vorspannungssteuerschaltung verwendet, um den unterschwelligen Leckstrom abzusenken. Die Halbleiter-IC-Einheit ist außerdem mit einer negativen Spannungsgeneratorschaltung versehen, die in die Substratvorspannungssteuerschaltung eingebaut ist, wie auch einem Anschluss für die Ausgabe einer negativen Spannung nach außen, die von der negativen Spannungsgeneratorschaltung erzeugt wurde.

**[0026]** Zu diesem Zeitpunkt ist die Halbleiter-IC-Einheit mit einem Halbleiter-Chip mit Ausgangs-Pads und einer Verpackung um den Halbleiter-Chip herum sowie mit externen Pins versehen, wobei eines der Ausgangs-Pads als Anschluss verwendet wird, der mit keinem externen Pin verbunden ist.

**[0027]** Bei einer weiteren Ausführungsform ist die Halbleiter-IC-Einheit mit einer Hauptschaltung aus wenigstens einem MOS-Transistor, einer Substratvorspannungssteuerschaltung zum Steuern einer Spannung an dem Substrat des MOS-Transistors, einer Standby-Steuerschaltung zum Umschalten der Halbleiter-IC-Einheit zwischen wenigstens den zwei Zuständen aktiv und Standby versehen. Der aktive Zustand lässt große unterschwellige Leckströme in der Hauptschaltung zu, und der Standby-Zustand erlaubt kleinere unterschwellige Leckströme in der Hauptschaltung. Die Halbleiter-IC-Einheit steuert somit die Substratvorspannung flach in dem aktiven Zustand und tief in dem Standby-Zustand, so dass der Strom zum Treiben der Substratvorspannung in einer flachen Art und Weise in dem aktiven Zustand zehnmal so groß oder mehr wie die Leistung zum Treiben der Substratvorspannung auf tiefe Art und Weise in dem Standby-Zustand wird.

**[0028]** Wenn die Substratvorspannung tief gesteuert wird, sollte man vorzugsweise vermeiden, die Hauptschaltung aus Transistoren dann zu betreiben, wenn an dem Substrat eine Vorspannung anliegt. Wenn eine Vorspannung an das Substrat eines Transistors angelegt wird, ist die Substrat-Impedanz hoch. Wenn ein MOS-Transistor daher aktiviert wird, ändert sich das Substratpotential schnell. Folglich wird der MOS-Transistor in einem derartigen Fall wahrscheinlich fehlerhaft arbeiten.

**[0029]** Bei dieser Ausführungsform werden wenigstens zwei MOS-Transistoren zum Treiben der Substratvorspannung im aktiven Zustand auf flache Art und Weise verwendet. Diese MOS-Transistoren sind in einem Abstand von 20 µm oder mehr zueinander angeordnet. Das Gate-Potential jedes der Substrat-Treiber-MOS-Transistoren wird durch die Substratvorspannungssteuerschaltung eingestellt.

**[0030]** Das Gate-Steuersignal zum Steuern der Gate-Spannung der Substrat-Treiber-MOS-Transistoren wird an die Substratvorspannungssteuerschaltung zurückgeführt, nachdem eine Verbindung mit dem Gate von jedem der Substrat-Treiber-MOS-Transistoren hergestellt wurde. Danach kann je nach Potential des zurückgeführten Signals die Substratvorspannungssteuerschaltung erkennen, ob sich die Substratvorspannung an der Hauptschaltung stabilisiert hat.

**[0031]** Vorzugsweise sollte die Schwellenspannung der Substrat-Treiber-MOS-Transistoren auf einen Wert größer als das Schwellenwertniveau der

MOS-Transistoren der Hauptschaltung gesetzt werden. Wenn die Halbleiter-IC-Einheit mit einer I/O-Schaltung als Schnittstelle nach außen versehen ist, sollte wenigstens einer der MOS-Transistoren der I/O-Schaltung vorzugsweise mit einer Oxidationschicht bedeckt sein, die dicker als der Oxidationsfilm der MOS-Transistoren der Hauptschaltung ist. Auf diese Art sollte die Maximalspannung in Bereichen, wo eine hohe Spannung angelegt wird, vorzugsweise einen hohen Wert haben.

**[0032]** Die Halbleiter-IC-Einheit ist außerdem mit einer Einschalt-Reset-Schaltung versehen, um zu erkennen, ob die Hauptschaltung mit Strom versorgt wird. Der aktive Zustand wird für eine feste Zeit aufrechterhalten, nachdem die Hauptschaltung mit Strom versorgt worden ist. In dem aktiven Zustand treibt jeder Substrat-MOS-Transistor die Substratvorspannung auf flache Art und Weise.

**[0033]** Bei einer weiteren Ausführungsform der vorliegenden Erfindung ist die Halbleiter-IC-Einheit mit zwei Versorgungsspannungen versehen, der ersten (VDDQ) und der zweiten (VDD). Die erste Versorgungsspannung hat einen Absolutwert, der größer als derjenige der zweiten Versorgungsspannung ist, die 2 V oder weniger beträgt. Die zweite Versorgungsspannung (VDD) wird an die Hauptschaltung (LOG) angelegt, und die erste Versorgungsspannung (VDDQ) wird sowohl an die Substratvorspannungssteuerschaltung (VBC) als auch an die Standby-Steuerschaltung (VBCC) angelegt. Die erste Versorgungsspannung wird vor der zweiten Versorgungsspannung angelegt. Die Substratvorspannungssteuerschaltung steuert in der Art, dass sich die Hauptschaltung während einer festen Zeit im aktiven Zustand befindet, nachdem die Substratvorspannungssteuerschaltung die zweite Versorgungsspannung angelegt hat.

**[0034]** Wenn darüber hinaus die Ausgangs-Impedanz des Gate-Steuersignals der Substrat-Treiber-MOS-Transistoren in einem Prozess, bei dem sich der Zustand von Standby zu aktiv ändert, höher ist als nachdem der Zustand bereits in den aktiven Zustand übergegangen ist, ist es möglich, die Geschwindigkeit für das Umschalten des Zustandes von Standby zu aktiv anzupassen, so dass der Anfangstrom bei dem Umschaltprozess gering ist.

**[0035]** Wenn darüber hinaus die Ausgangs-Impedanz des Gate-Steuersignals der Substrat-Treiber-MOS-Transistoren in einem Prozess, bei dem sich der Zustand von Standby zu aktiv ändert, höher ist als nachdem der Zustand bereits in den aktiven Zustand übergegangen ist, ist es möglich, die Geschwindigkeit für das Umschalten des Zustandes von Standby zu aktiv anzupassen, so dass der Anfangstrom bei dem Umschaltprozess gering ist.

**[0036]** Es wird außerdem möglich, über das zurückgeführte Signal festzustellen, ob sich die Hauptschaltung bereits im aktiven Zustand befindet.

**[0037]** Es ist außerdem möglich, die Amplitude des Gate-Steuersignals größer als die Gate-Durchbruchspannung der Substrat-Treibertransistoren einzustellen.

**[0038]** Darüber hinaus ist die Halbleiter-IC-Einheit mit einer negativen Spannungsgeneratorschaltung versehen, so dass die Substratvorspannungssteuerschaltung die Ausgangsimpedanz der negativen Spannungsgeneratorschaltung in dem Standby-Zustand niedriger als in dem aktiven Zustand einstellen kann.

**[0039]** In einer weiteren Ausführungsform der vorliegenden Erfindung ist die negative Spannungsgeneratorschaltung mit der ersten und zweiten Ladungspumpenschaltung versehen, so dass die Substratvorspannungssteuerschaltung die erste Ladungspumpenschaltung im Standby-Zustand und die zweite Ladungspumpenschaltung im aktiven Zustand verwendet, um dadurch jeweils eine negative Spannung zu erzeugen. Außerdem ist die Pumpkapazität der ersten Ladungspumpe kleiner gewählt als die der zweiten Ladungspumpenschaltung.

**[0040]** Die Halbleiter-IC-Einheit kann außerdem so aufgebaut sein, dass die negative Spannungsgeneratorschaltung zusätzlich zu der ersten und zweiten Versorgungsspannung die dritte Versorgungsspannung erzeugen kann, so dass die erste Versorgungsspannung größer als die zweite Versorgungsspannung ist, die 2 V oder weniger beträgt, und die Hauptschaltung mit der zweiten Versorgungsspannung versorgt wird, während die Substratvorspannungssteuerschaltung und die Standby-Steuerschaltung mit wenigstens der ersten Versorgungsspannung versorgt werden, und die Substratvorspannungssteuerschaltung die Substratvorspannung der PMOS-Transistoren derart steuert, dass eine Anpassung an das zweite Versorgungsspannungspotential im Standby-Zustand erfolgt, und die Substratvorspannung der NMOS-Transistoren derart steuert, dass eine Anpassung an das dritte Versorgungsspannungspotential erfolgt, so dass die Bedingung (dritte Versorgungsspannung) = (erste Versorgungsspannung) – (zweite Versorgungsspannung) erfüllt wird.

**[0041]** Darüber hinaus wird die negative Spannungsgeneratorschaltung mit wenigstens einer Ladungspumpenschaltung, einem Komparator, der ersten Referenzspannungsschaltung zum Erzeugen eines Potentials auf halber Höhe desjenigen der zweiten Versorgungsspannung und der zweiten Referenzspannungsschaltung zum Erzeugen eines Zwischenpotentials zwischen der ersten und dritten Versorgungsspannung versehen. Der Komparator ver-

gleicht den Spannungsausgang von der ersten Referenzspannungsschaltung mit dem Spannungsausgang von der zweiten Referenzspannungsgeneratorschaltung, so dass dadurch wenigstens eine der Ladungspumpen so gesteuert wird, dass die dritte Versorgungsspannung stabilisiert wird.

**[0042]** Die erste und zweite Referenzspannungsgeneratorschaltung werden jeweils aus einer seriellen Schaltung aufgebaut, bei der die MOS-Transistoren gleichen Leitfähigkeitstyps seriell hintereinander geschaltet werden. Bei jedem der Leitfähigkeits-MOS-Transistoren wird der Substratanschluss mit dem Source-Anschluss verbunden, und der Gate-Anschluss wird mit dem Drain-Anschluss verbunden. Sowohl die erste als auch die zweite Referenzspannungsgeneratorschaltung kann ausgewählt werden, um mehrere MOS-Transistoren im Sättigungsbereich zu betrieben. Der Aufbau kann auch in der Art sein, dass sich ein Schmitt-Schaltverhalten einstellt.

**[0043]** Die Hauptschaltung ist aus mehreren Zellen aufgebaut. Ein Stromversorgungsnetz für derartige Zellen wird durch die ersten Metall-Ebenen versorgt. Ein weiteres Stromversorgungsnetz wird aus der zweiten Verdrahtungsschicht über den ersten Metall-Ebenen aufgebaut, so dass sie orthogonal zu den ersten Metall-Ebenen ist. Eine Schaltzelle ist an jedem Schnittpunkt der Stromversorgungsnetze aus der ersten und zweiten Verdrahtungsschicht vorgesehen, so dass beide Stromversorgungsnetze mit der ersten und zweiten Verdrahtungsschicht in diesen Schaltzellen miteinander verbunden sind. Außerdem ist ein Substrat-Treiber-MOS-Transistor in jeder dieser Schaltzellen vorgesehen.

**[0044]** Eine Schaltzelle kann außerdem so aufgebaut sein, dass ein Entkopplungskondensator zwischen Stromquelle und Masse angeordnet ist.

**[0045]** Außerdem ist über dem Stromversorgungsnetz mit den zweiten Verdrahtungsschichten ein Stromversorgungsnetz mit vierten Verdrahtungsschichten angeordnet, die sich parallel zu dem Stromversorgungsnetz mit den zweiten Verdrahtungsschichten erstrecken. Die Stromversorgungsnetze mit den zweiten und vierten Verdrahtungsschichten können außerhalb dieser Schaltzellen miteinander verbunden werden.

**[0046]** Es gibt ein weiteres Stromversorgungsnetz mit den fünften Verdrahtungsschichten. Das Stromversorgungsnetz ist mit dem Stromversorgungsnetz mit den vierten Verdrahtungsschichten in Schaltzellen verbunden. Ein Stromversorgungsgitter mit den Stromversorgungsnetzen der vierten und fünften Verdrahtungsschichten kann größer sein als das Stromversorgungsgitter mit den Stromversorgungsnetzen mit den ersten und zweiten Verdrahtungsschichten.

Außerdem können die vierten und fünften Verdrahtungsschichten dicker als sowohl die ersten als auch die zweiten Verdrahtungsschichten sein.

**[0047]** Die Substratvorspannungsversorgungsleitungen der MOS-Transistoren, aus denen die Zellen aufgebaut sind, können mit den ersten Metall-Ebenen parallel zu dem Stromversorgungsnetz mit den ersten Metall-Ebenen verlaufen, wie auch parallel zu dem Stromversorgungsnetz mit den zweiten Verdrahtungsschichten. Genau wie bei den oben beschriebenen Stromversorgungsnetzen können die Substratvorspannungsversorgungsleitungen mit den ersten Metall-Ebenen mit den Substratvorspannungsversorgungsleitungen mit den zweiten Verdrahtungsschichten in Schaltzellen verbunden sein.

**[0048]** Das Gate-Steuersignal zum Steuern der Gate-Spannung jedes der Substrat-Treiber-MOS-Transistoren kann durch die zweiten Verdrahtungsschichten über den Schaltzellen bereitgestellt werden, die parallel zu dem Stromversorgungsnetz mit den zweiten Verdrahtungsschichten angeordnet sind und mit dem Gate-Anschluss jedes der Substrat-Treiber-MOS-Transistoren in einer Schaltzelle verbunden sind.

**[0049]** Die Substratvorspannungsversorgungsleitungen, die über die zweiten Verdrahtungsschichten über den Schaltzellen verdrahtet sind, und die Gate-Steuerung können zwischen den Stromversorgungsnetzen angeordnet sein, die durch die zweiten Verdrahtungsschichten über den Schaltzellen verdrahtet sind.

**[0050]** Die Halbleiter-IC-Einheit der vorliegenden Erfindung ist außerdem mit einer Datenpfadschaltung versehen. Die Datenflussrichtung der Datenpfadschaltung kann parallel zu dem Stromversorgungsnetz verlaufen, das durch die ersten Metall-Ebenen verdrahtet ist, die für mehrere der Zellen verwendet werden.

**[0051]** Die Substratvorspannung kann so eingestellt sein, dass der Schwellenwertpegel wenigstens eines MOS-Transistors angehoben wird, wenn die Halbleiter-IC-Einheit gemäß der vorliegenden Erfindung ausgewählt wird.

**[0052]** Bei einer weiteren Ausführungsform der vorliegenden Erfindung werden in einer Ladungspumpenschaltung aus dem ersten und zweiten Pumpkondensator, dem ersten und zweiten (zwei) P-Kanal-Transistor, dem ersten und zweiten (zwei) N-Kanal-Transistor und einer Oszillatorschaltung der erste Pumpkondensator, der erste P-Kanal-Transistor und der erste N-Kanal-Transistor zum Pumpen der elektrischen Ladung des ersten Pumpkondensators verwendet, wenn der Ausgang der Oszillatorschaltung "H" ist, und der zweite Pumpkondensator, der zweite

P-Kanal-Transistor und der zweite N-Kanal-Transistor werden für das Pumpen der elektrischen Ladung des zweiten Pumpkondensators verwendet, wenn der Ausgang der Oszillatorschaltung "L" ist.

**[0053]** Bei einer weiteren Ausführungsform der vorliegenden Erfindung ist die Halbleiter-IC-Einheit mit einer Hauptschaltung (LOG) mit Transistoren auf jeweils einem Halbleitersubstrat und einer Substratvorspannungssteuerschaltung (VBC) zum Steuern einer Spannung, die an jedes Substrat angelegt werden soll, versehen. Die Hauptschaltung ist mit Schalttransistoren (MN1 und MP1) versehen, um eine Spannung zu steuern, die an jedes Substrat angelegt werden soll, und empfängt über das Gate von jedem der Schalttransistoren Steuersignale, die von der Substratvorspannungssteuerschaltung ausgegeben werden. Die Steuersignale sind so aufgebaut, dass sie an die Substratvorspannungssteuerschaltung zurückgeführt werden.

**[0054]** Jeder Schalttransistor ist in einer rechteckigen Schaltzelle vorgesehen, und jeder der anderen Transistoren befindet sich in einer rechteckigen Standardzelle. Eine Schaltzelle und eine Standardzelle sollten im Layout vorzugsweise Seite an Seite angeordnet werden.

**[0055]** Die Leistungsquellen (VSS und VDD) zum Treiben der Transistoren (MN2 und MP2) in der Hauptschaltung wie auch die Stromquellen (vbp und vbn) der Substratvorspannung, die von der Substratvorspannungssteuerschaltung bereitgestellt wird, sollten vorzugsweise so verdrahtet sein, dass beide, Schaltzelle und Standardzelle, vertikal in der Richtung überkreuzt werden, in der diese Zellen angeordnet sind.

**[0056]** Der Schwellenwertpegel der Schalttransistoren sollte bezüglich des Transistorwiderstands vorzugsweise größer sein als der von anderen Transistoren.

**[0057]** Die Schalttransistoren (MN1 und MP1) sollten vorzugsweise zwischen den Treiberstromquellen (VSS und VDD) für die Transistoren in der Hauptschaltung und den Stromquellen (vbp und vbn) der Substratvorspannung, die von der Substratvorspannungssteuerschaltung bereitgestellt wird, in dem Layout eingesetzt werden.

**[0058]** Die Source oder der Drain jedes Transistors kann mit Treiberstromquellen (VSS und VDD) verbunden sein, und das Transistorsubstratpotential kann mit den Substratvorspannungsstromquellen (vbp und vbn) verbunden sein.

**[0059]** Die Substratvorspannungssteuerschaltung kann ermitteln, ob die Steuersignale (vbp und vbn), nachdem sie ausgegeben wurden, über die Haupt-

schaltung als Steuersignale (vbpr und vbnr) zurückgeführt wurden und dann eine vorgegebene Spannung erreicht wurde. Dann kann die Substratvorspannungssteuerschaltung ein Erfassungssignal (vbbnrb) erzeugen, so dass der Betrieb der Hauptschaltung stabilisiert wird.

#### KURZE BESCHREIBUNG DER ZEICHNUNGEN

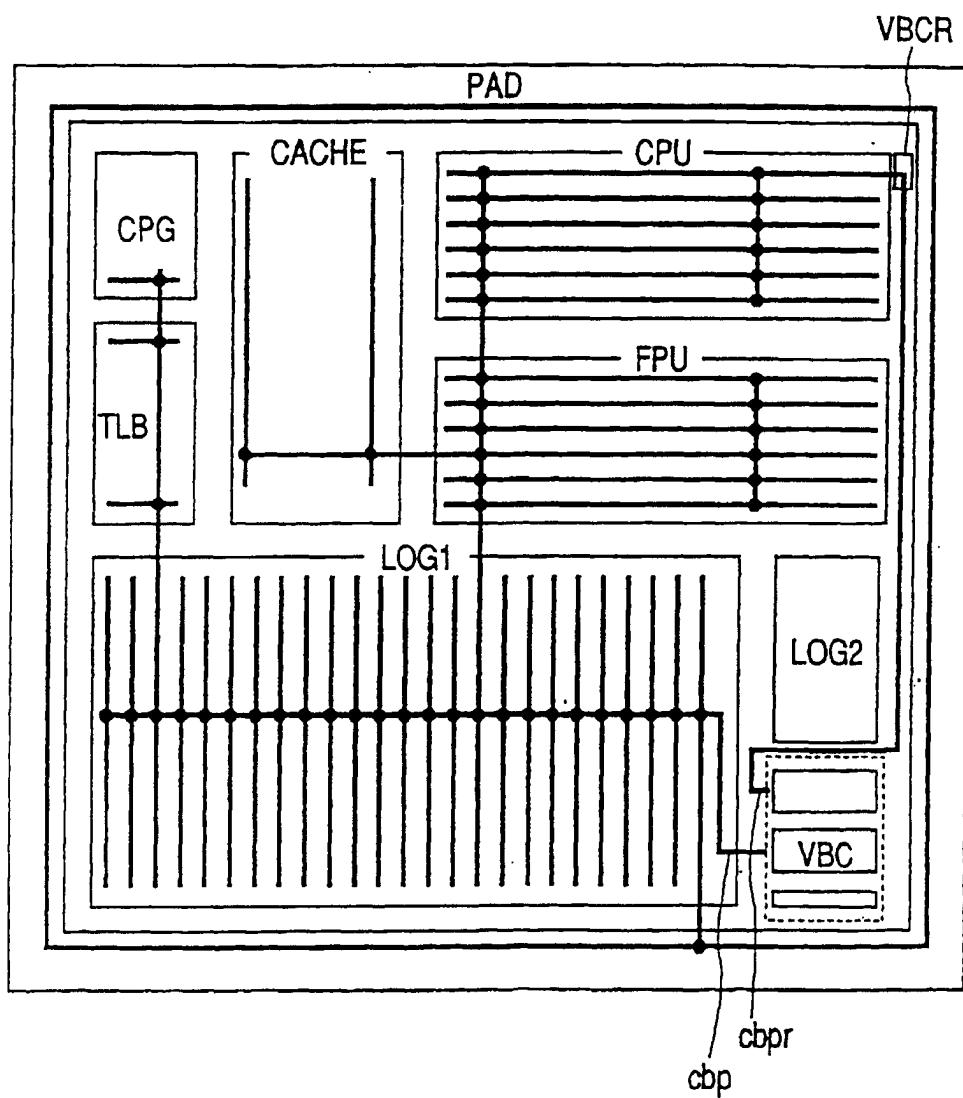

**[0060]** [Fig. 1](#) ist das Blockdiagramm einer Halbleiter-IC-Einheit gemäß der vorliegenden Erfindung.

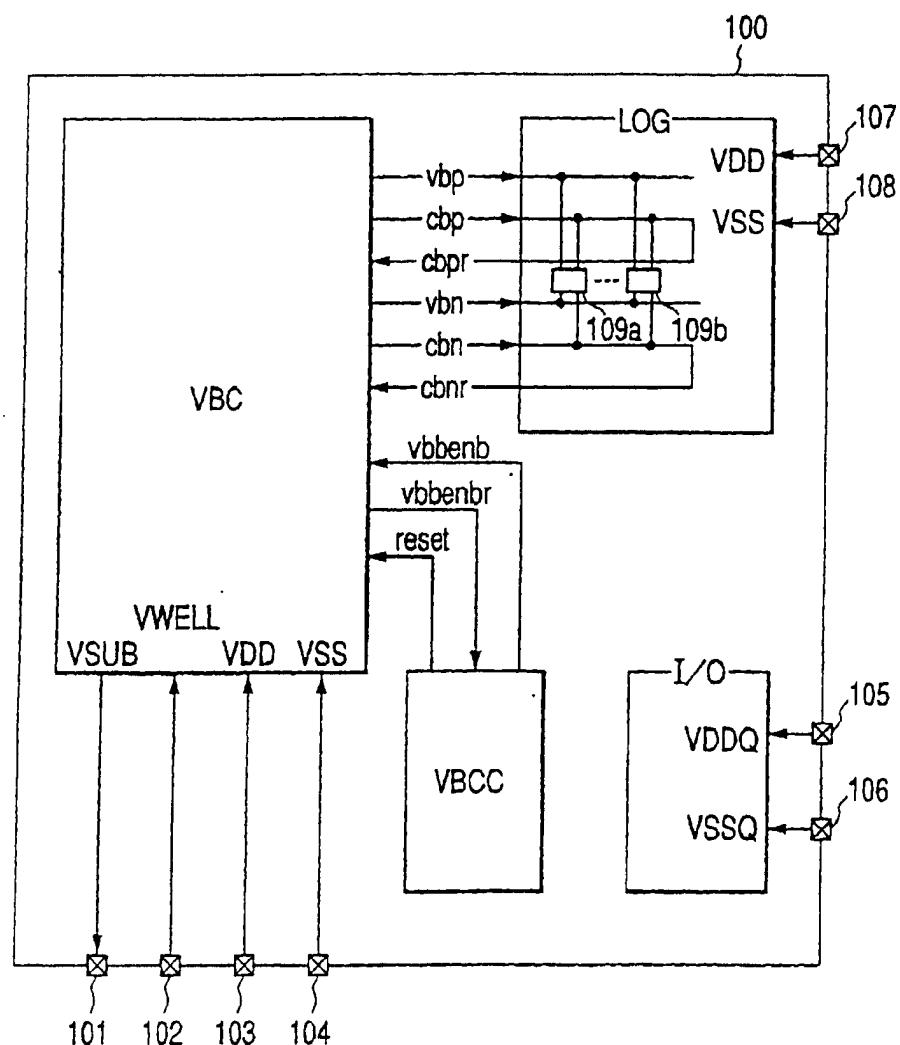

**[0061]** [Fig. 2](#) zeigt Einzelheiten des Schaltungsaufbaus einer Hauptschaltung.

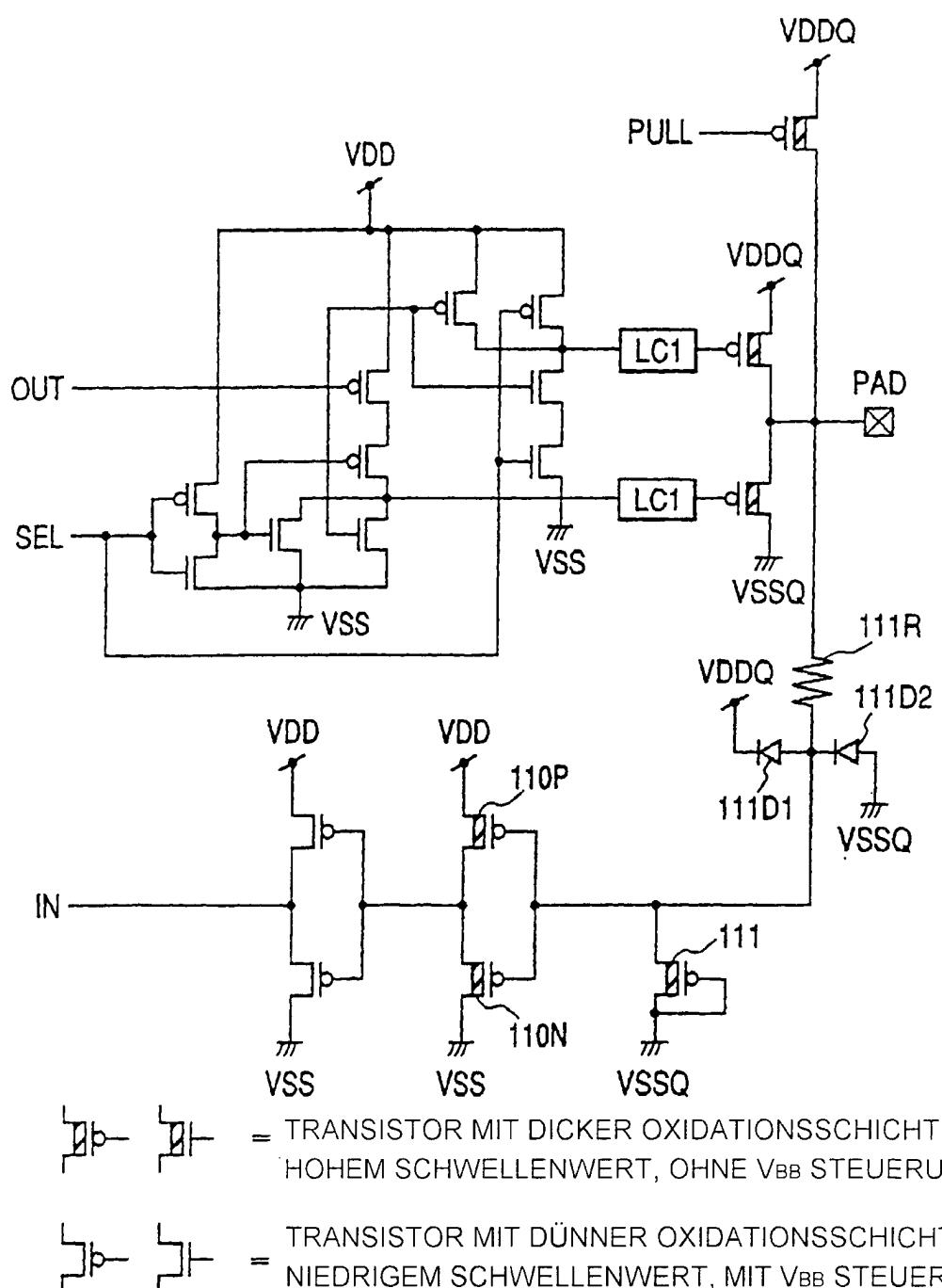

**[0062]** [Fig. 3](#) zeigt den Schaltplan einer I/O-Schaltung.

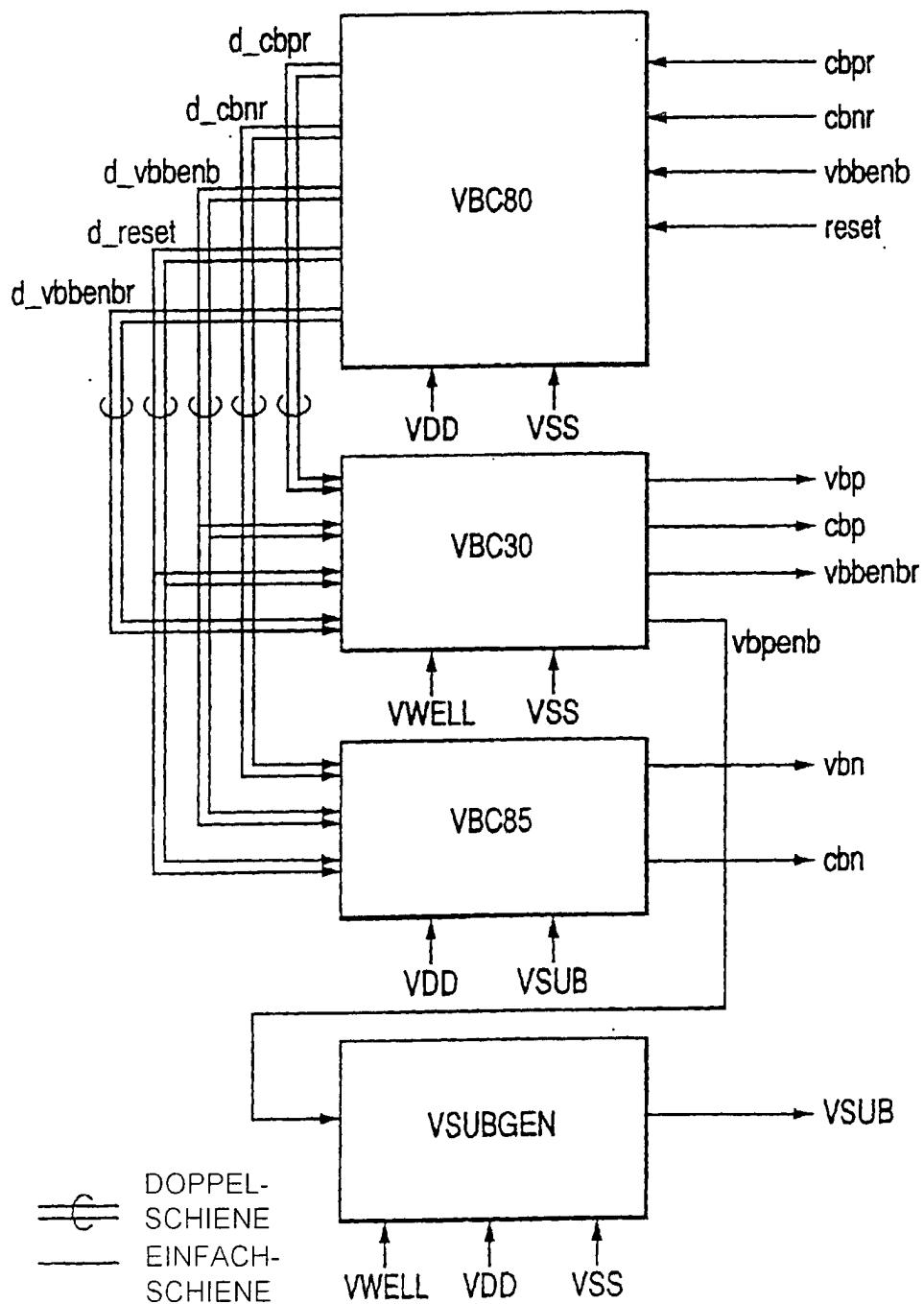

**[0063]** [Fig. 4](#) ist das Blockdiagramm mit jeder Schaltung in einer Substratvorspannungssteuerschaltung.

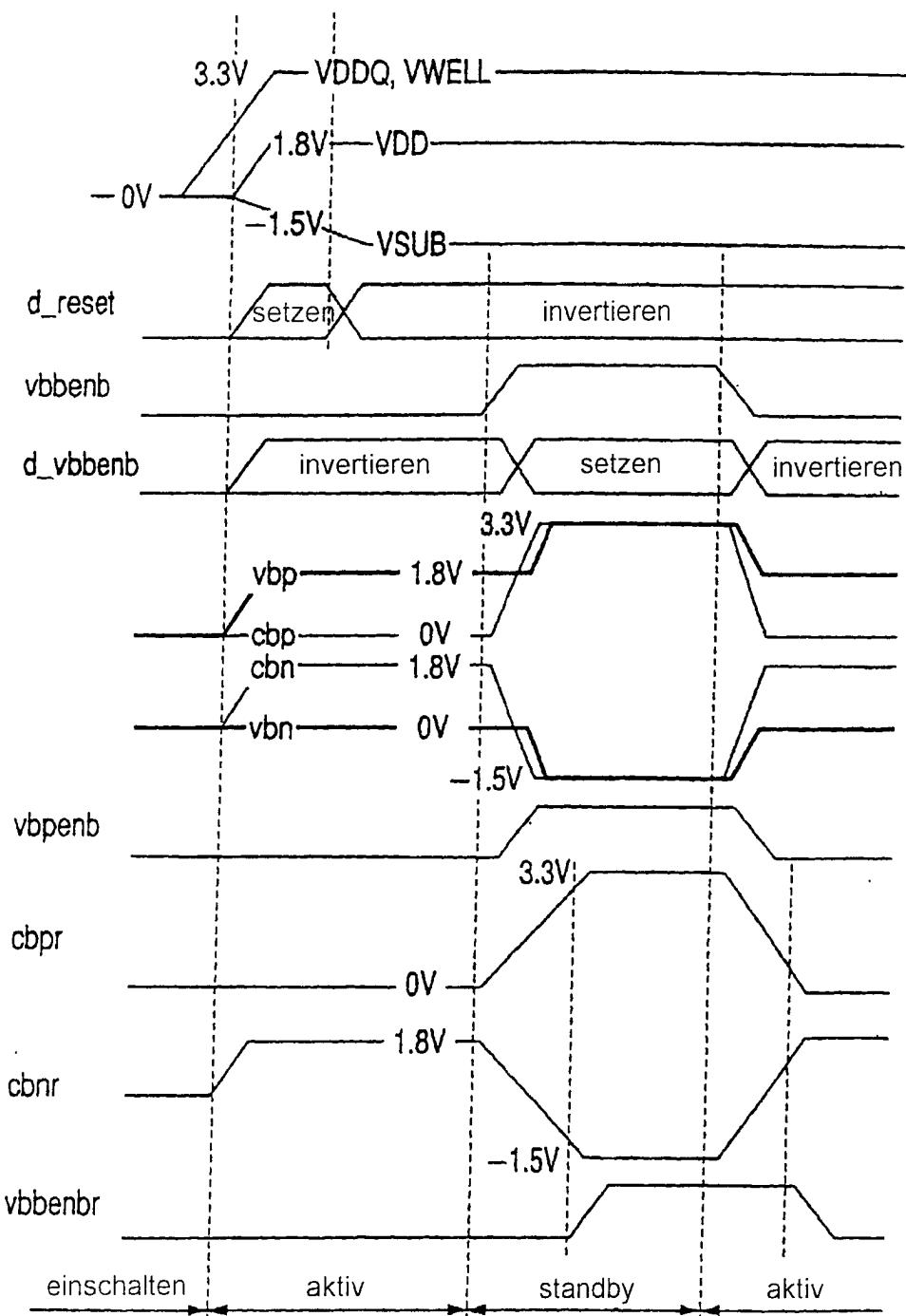

**[0064]** [Fig. 5](#) zeigt Signalformen bei der Substratvorspannungssteuerschaltung.

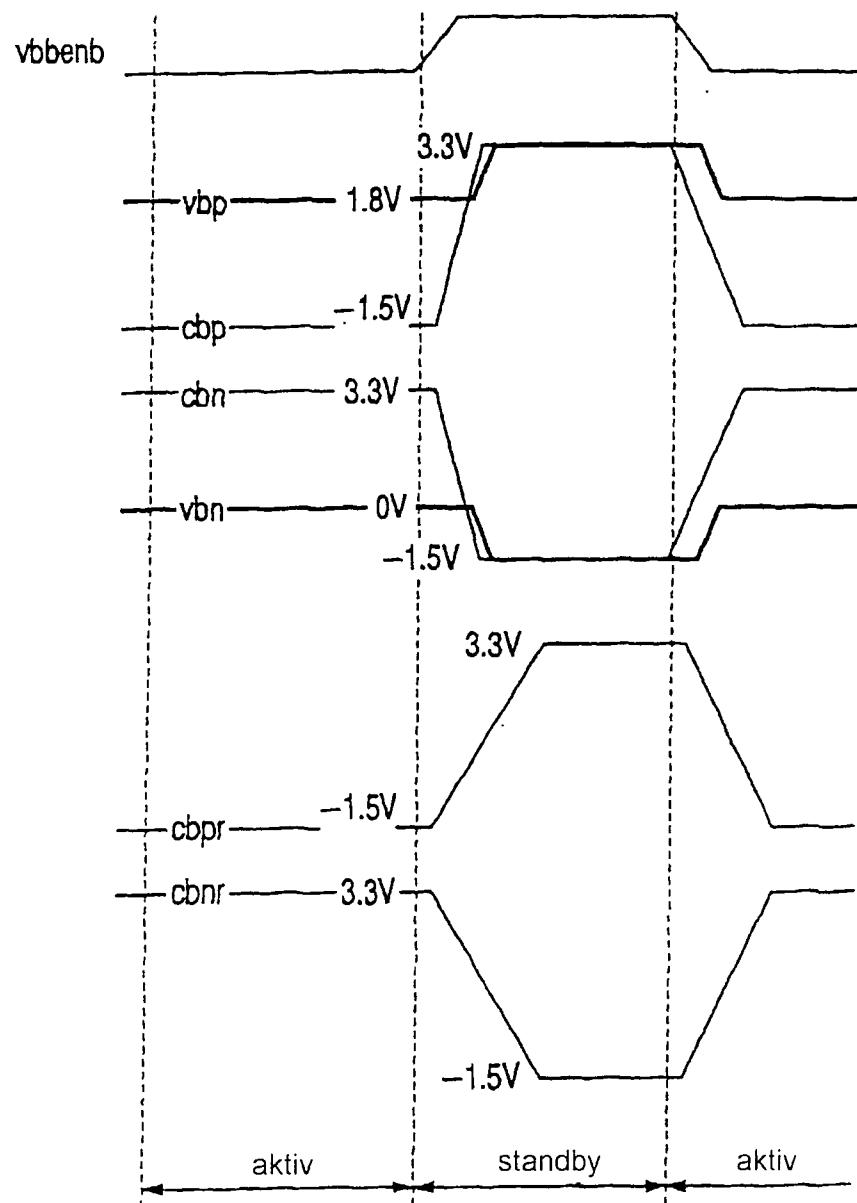

**[0065]** [Fig. 6](#) zeigt Signalformen bei der Substratvorspannungssteuerschaltung bei einer weiteren Ausführungsform der vorliegenden Erfindung.

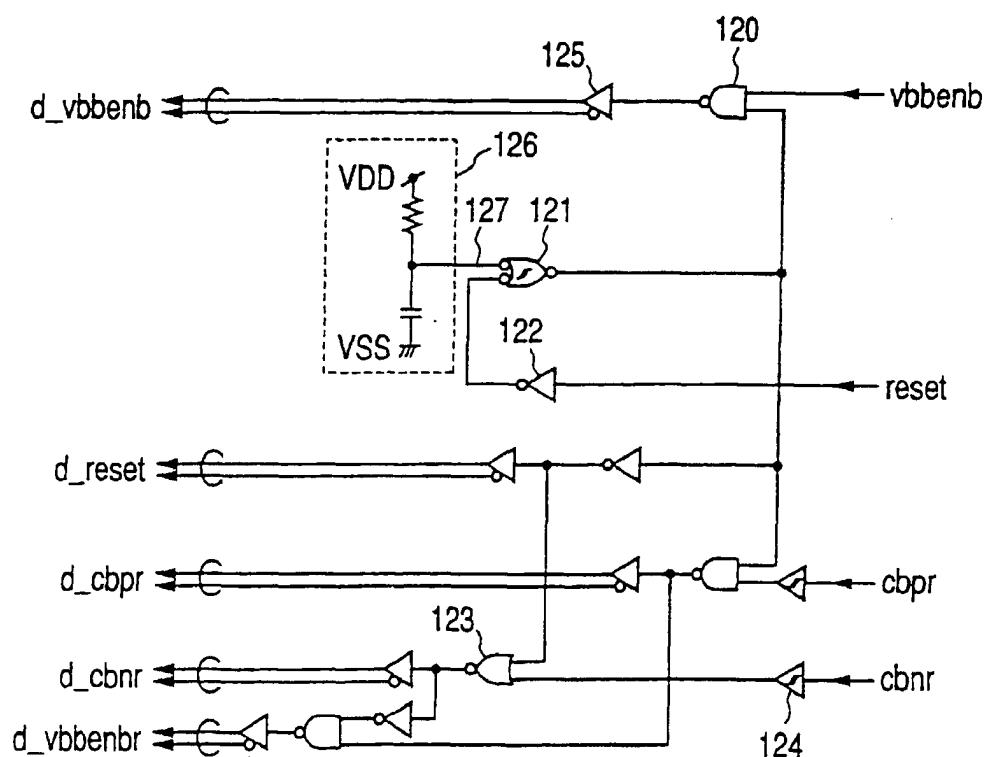

**[0066]** [Fig. 7](#) zeigt den Schaltplan einer VBC80.

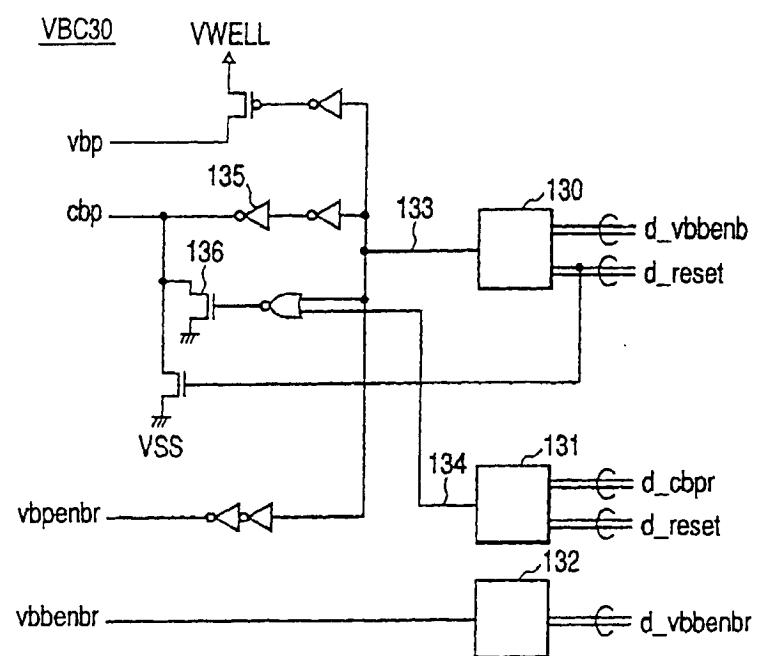

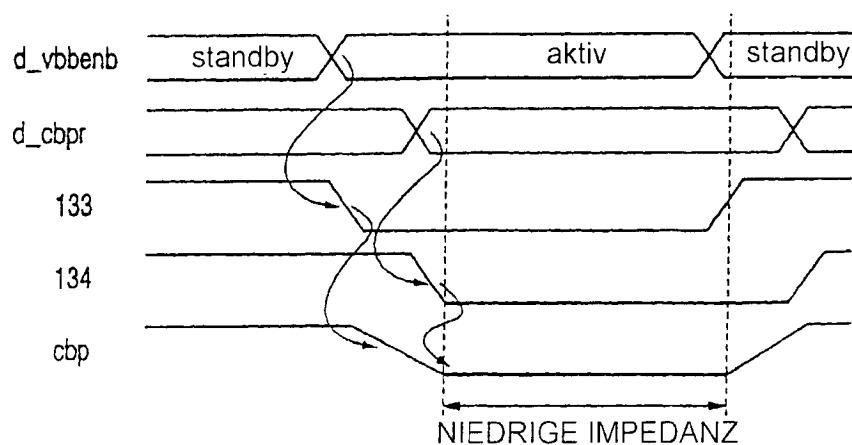

**[0067]** [Fig. 8](#) zeigt den Schaltplan einer VBC30.

**[0068]** [Fig. 9](#) zeigt eine Signalform der VBC30.

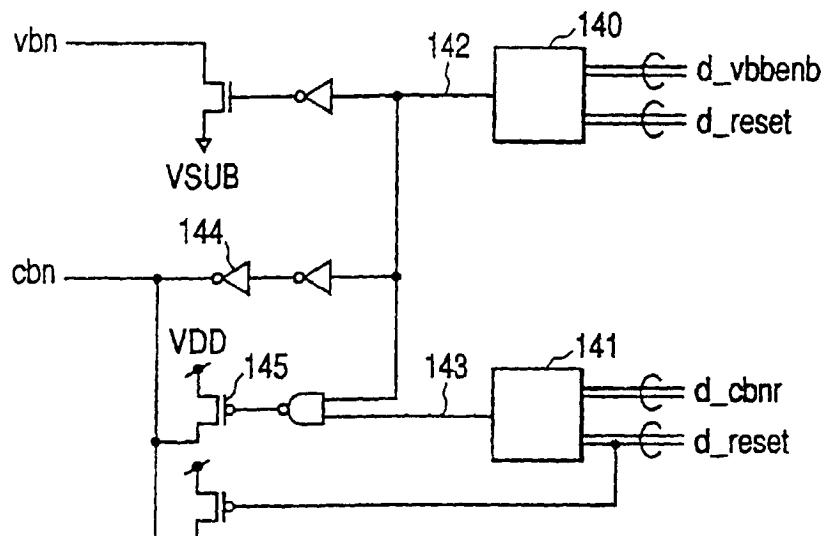

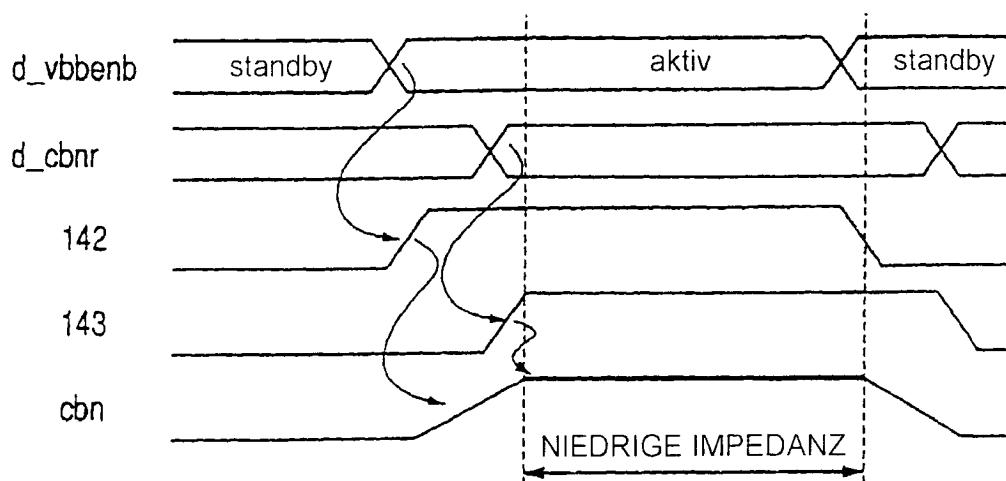

**[0069]** [Fig. 10](#) zeigt den Schaltplan einer VBC85.

**[0070]** [Fig. 11](#) zeigt eine Signalform der VBC85.

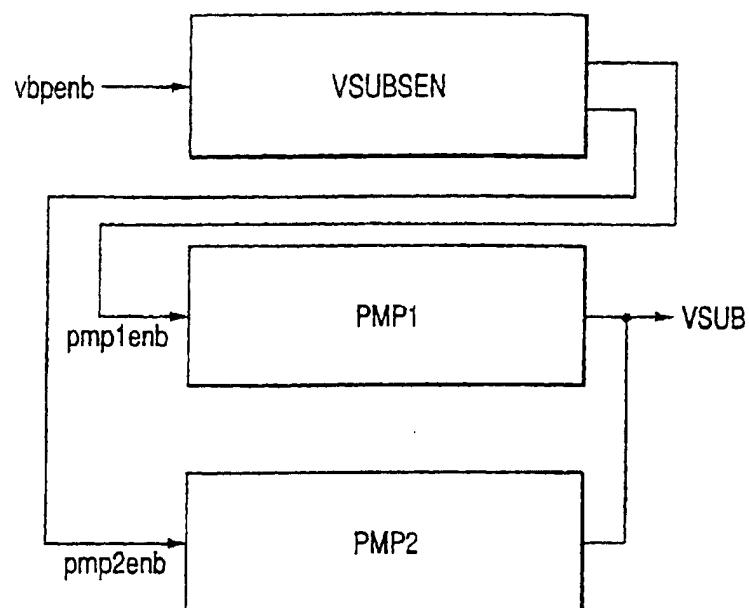

**[0071]** [Fig. 12](#) zeigt das Blockdiagramm mit jeder Schaltung, die in einer VSUBGEN vorgesehen ist.

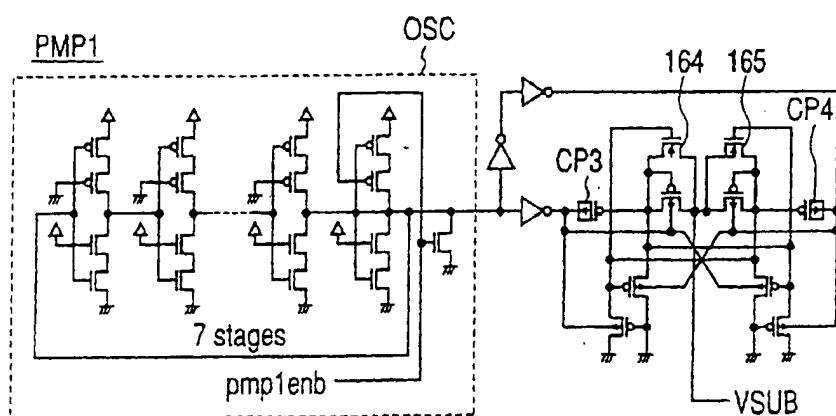

**[0072]** [Fig. 13](#) zeigt den Schaltplan einer Ladungspumpe.

**[0073]** [Fig. 14](#) zeigt einen weiteren Schaltplan der Ladungspumpe.

**[0074]** [Fig. 15](#) zeigt den Schaltplan der VSUBGEN.

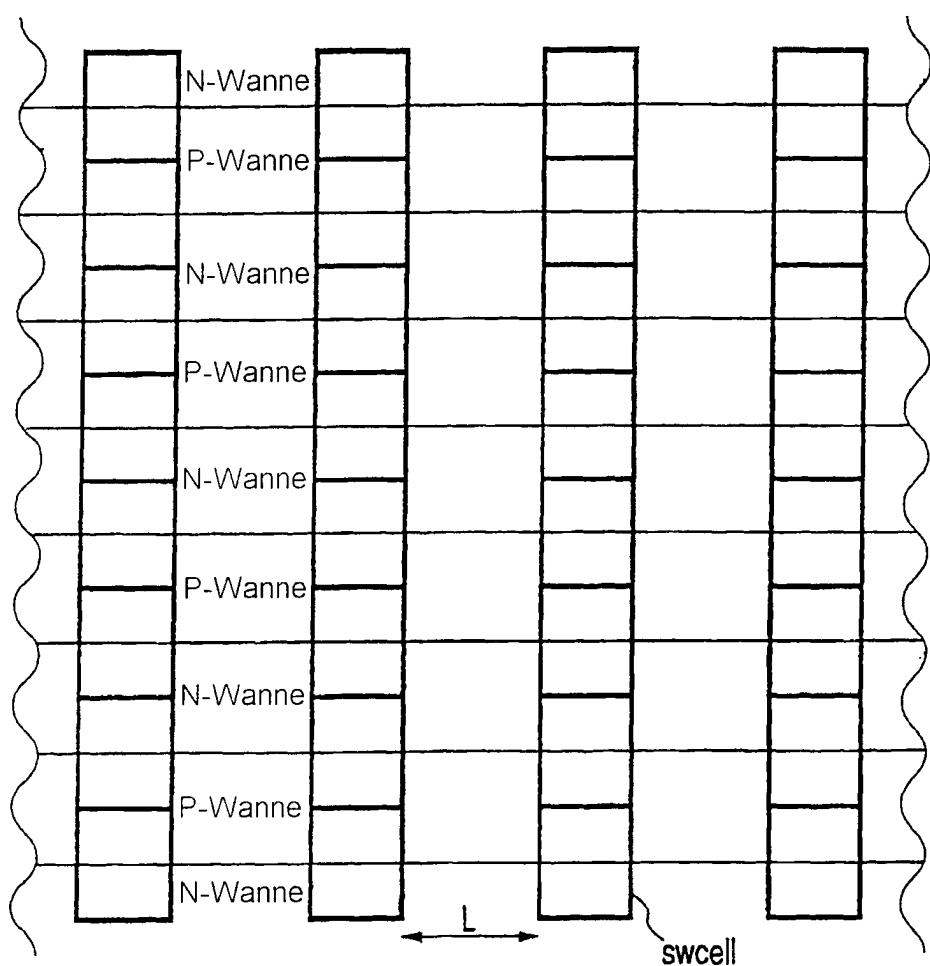

**[0075]** [Fig. 16](#) zeigt die Art, in der Schaltzellen gemäß der vorliegenden Erfindung vorgesehen sind.

**[0076]** [Fig. 17](#) zeigt das Layout einer Standardzelle.

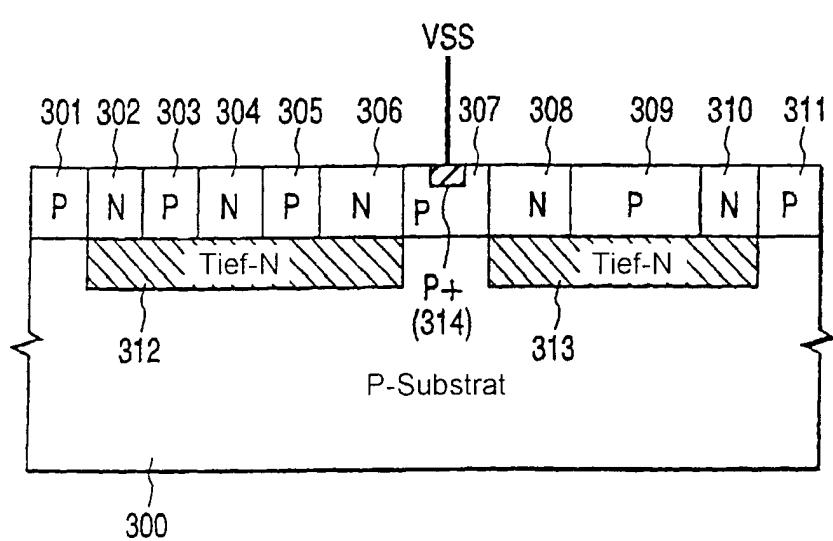

**[0077]** [Fig. 18](#) zeigt den Querschnitt einer Standardzelle in [Fig. 17](#).

**[0078]** [Fig. 19](#) zeigt das Layout von Schaltzellen.

[0079] [Fig. 20](#) ist ein Querschnitt von Schaltzellen in [Fig. 19](#).

[0080] [Fig. 21](#) zeigt die Verdrahtung einer Stromquelle und Verdrahtungen zu vbp, vbn, cbp und cbn.

[0081] [Fig. 22](#) zeigt die Verdrahtung von Stromquellenverstärkungsleitungen.

[0082] [Fig. 23](#) zeigt ein Blockdiagramm mit Wannen.

[0083] [Fig. 24](#) zeigt die Art, in der Schaltzellen in einer Speicherschaltung angeordnet sind.

[0084] [Fig. 25](#) zeigt einen Querschnitt einer Wanne.

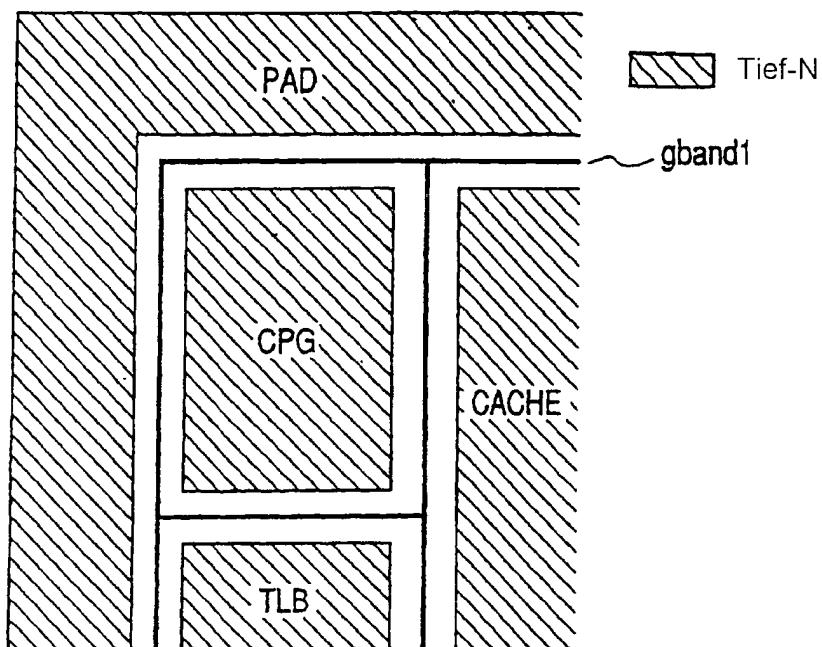

[0085] [Fig. 26](#) zeigt das Layout von tiefen N-Wannen.

[0086] [Fig. 27](#) zeigt das Layout von tiefen N-Wannen und einem Schutzband.

[0087] [Fig. 28](#) zeigt einen Querschnitt durch [Fig. 27](#).

[0088] [Fig. 29](#) zeigt die Art, in der cbpr, cbnr und VBCR angeordnet sind.

#### BEVORZUGTE ART DER UMSETZUNG DER ERFINDUNG

[0089] [Fig. 1](#) zeigt ein Blockdiagramm einer Halbleiter-IC-Einheit **100**, bei der eine Substratvorspannungssteuerschaltung gemäß der vorliegenden Erfindung eingesetzt wird. VBC ist eine Substratvorspannungssteuerschaltung. LOG ist die Hauptschaltung, bei der die Substratvorspannung gesteuert wird. Die LOG ist aus Logikschaltungen und Speicherschaltungen aufgebaut. VBCC ist eine Standby-Steuerschaltung zum Steuern der Substratvorspannungssteuerschaltung. I/O ist eine I/O-Schaltung als Schnittstelle zwischen der Halbleiter-IC-Einheit **100** und außen. Verdrahtungen zwischen Schaltungsblöcken, die nicht ausdrücklich zum Steuern des Substrats benötigt werden, wurden hier fortgelassen. **109a** und **109b** sind Substrat-Treiberschaltungen.

[0090] Die Halbleiter-IC-Einheit ist mit drei Arten von Stromquellen ausgestattet, die als VDDQ, VDD und VWELL bezeichnet sind. VSS und VSSQ sind Massepotentiale für VDD und VDDQ. VDDQ und VSSQ sind Stromquellen für die I/O-Schaltung. VDD und VSS sind Stromquellen für die Hauptschaltung. VWELL ist eine Stromquelle für die Substratvorspannungssteuerschaltung VBC.

[0091] Wie in [Fig. 1](#) gezeigt werden VDD und VSS ebenfalls an die Substratvorspannungssteuerschaltungen VBC angelegt. Die Substratvorspannungssteuerschaltung VBC umfasst eine interne negative Spannungsgeneratorschaltung, die eine negative Spannung VSUB erzeugt, die bezüglich Polarität VDDQ entgegengesetzt ist. Bei dieser Ausführungsform wird von folgenden Pegeln für die Versorgungsspannungen ausgegangen: VDDQ = VWELL = 3,3 V und VDD = 1,8 V und VSUB = -1,5 V.

[0092] **101**, **102**, **103** und **104** sind Pads für die Halbleiter-IC-Einheit. Pad **102** wird von VWELL mit 3,3 V versorgt, Pad **103** ist von VDD mit 1,8 V versorgt, und Pad **104** wird mit VSS (Masse) 0 V versorgt. **101** ist ein VSUB-Pad, aber es wird verwendet, um eine negative Spannung auszugeben, die innerhalb der Substratvorspannungssteuerschaltung erzeugt wurde. Die Spannung des Pad **101** kann überwacht werden, um Fehler der negativen Spannungsgeneratorschaltung in der Substratvorspannungssteuerschaltung VBC zu erkennen, wenn ein Wafer-Test bei der Halbleiter-IC-Einheit **100** durchgeführt wird. Üblicherweise sind die Pads **102** bis **104** mit externen Pins der Halbleiter-IC-Einheit **100** gebondet, aber Pad **101** ist nicht mit irgendeinem äußeren Pin gebondet. Bei diesen Testverfahren kann die Anzahl der externen Pins beibehalten werden.

[0093] vbbenb ist ein Signal, das zum Starten der Substratvorspannungssteuerung dient, und vbbenbr ist ein Signal, das anzeigt, dass die Substratvorspannung jetzt eingestellt worden ist. Auf der anderen Seite ist Reset ein RESET-Signal, das als RESET-Signal an der Halbleiter-IC-Einheit anlegt. vbp ist eine PMOS-Substratvorspannungsleitung, vbn ist eine NMOS-Substratvorspannungsleitung, cbp ist eine PMOS-Substratsteuerleitung, cbn ist eine NMOS-Substratsteuerleitung, cbpr ist eine PMOS-Substratsteuerrückführleitung und cbnr ist eine NMOS-Substratsteuerrückführleitung. Die Substratsteuerrückführleitungen cbpr und cbnr werden für Signale verwendet, die zurückgeführt werden, nachdem sowohl das cbp- als auch das cbn-Signal die Hauptschaltung durchlaufen haben. Dasselbe Netz wird für die beiden Rückführleitungen cbpr und cbnr verwendet. Mit anderen Worten, beide Treiberspannungen cbp und cbn erscheinen nach einer Verzögerung in cbpr und cbnr. (Siehe [Fig. 2](#), die im Folgenden erläutert wird.) An jede der Substrat-Treiberschaltungen **109a** und **109b** wird cbp, vbp, cbn und vbn angelegt.

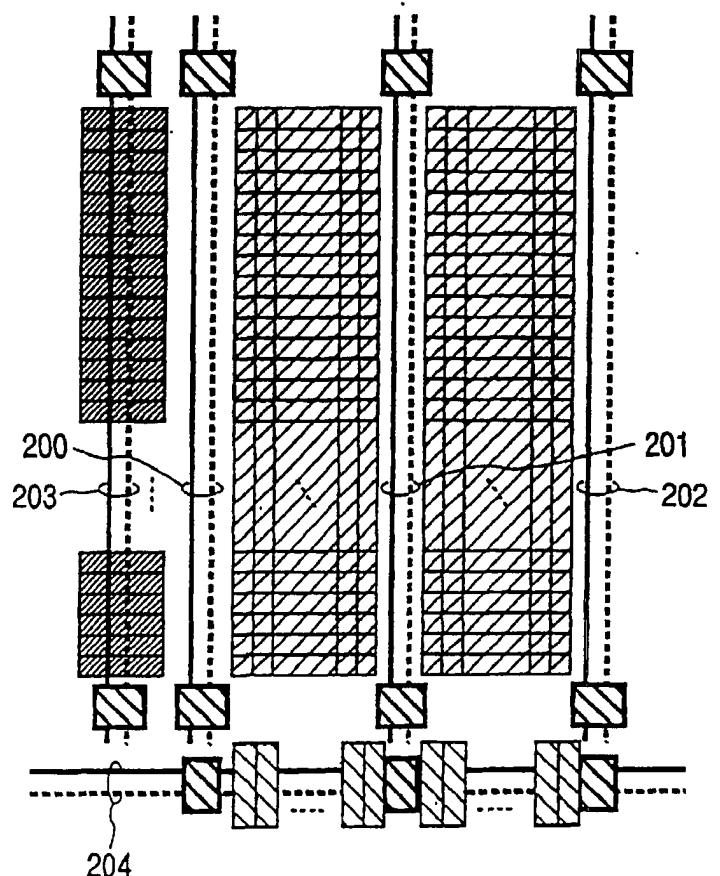

[0094] [Fig. 2](#) zeigt, wie 6 Substratvorspannungssteuerleitungen (vbp bis cbnr) mit der Hauptschaltung LOG verbunden sind. VBCR ist eine Rückgabezelle. In dieser VBCR ist die PMOS-Substratsteuerleitung cbp mit der PMOS-Substratsteuerrückführleitung cbpr verbunden, wie auch die NMOS-Substratsteuerleitung cbn mit der NMOS-Substratsteuerrückführleitung cbnr verbunden ist.

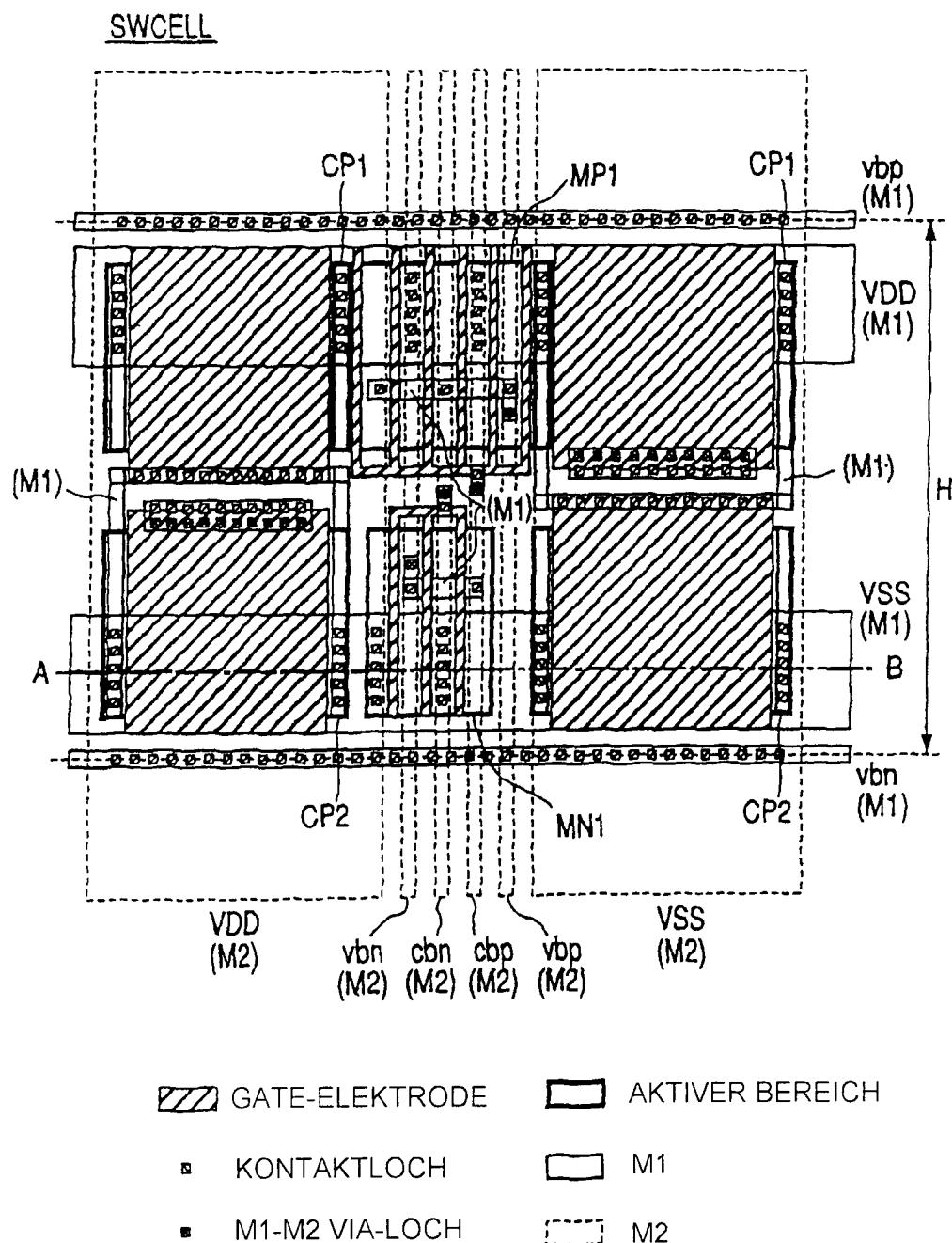

**[0095]** ncell ist eine Standardzelle. Bei dieser Ausführungsform ist jede ncell als CMOS-Inverter mit dem PMOS MP2 und dem NMOS MN2 dargestellt, um die Beschreibung zu vereinfachen. Selbstverständlich kann jede ncell in ihrer Struktur komplizierter sein, wie zum Beispiel eine Zelle, die unabhängig von weiteren Elementen mit NAND-Gattern, einem Latch-Gatter etc. aufgebaut ist. Das Substratpotential jedes MOS-Transistors wird mit vbp beim PMOS bzw. vbn beim NMOS verbunden. Diese MOS-Transistoren bilden jeweils eine ncell, wie es in [Fig. 2](#) gezeigt ist.

**[0096]** swcell ist eine Schaltzelle aus Substrat-Treiberschaltungen (äquivalent zu [109a](#) und [109b](#) in [Fig. 1](#)), die aus dem PMOS MP1 und NMOS MN1 aufgebaut sind, sowie den Entkopplungskondensatoren CP1 bzw. CP2. Bei dem MP1 ist das Gate mit cbp verbunden, der Drain ist mit VBP verbunden, und die Source ist mit VDD verbunden. Wenn die cbp-Spannung niedriger als VDD-Vthp ist (Vthp: Absolutwert der Schwellenspannung von MP1), wird folglich der MP1 aktiviert, und vbp wird mit dem VDD-Potential (1,8 V) angetrieben.

**[0097]** Auf der anderen Seite sind Gate, Drain und Source des MN1 mit cbn, VBN und VSS (0 V) verbunden. Wenn die cbn-Spannung höher als Vthn ist (Vthn: Absolutwert der Schwellenspannung von MN1), wird folglich der MN1 aktiviert, und vbn wird mit dem VSS-Potential (0 V) angetrieben.

**[0098]** Allgemein ist mehr als eine ncell vorgesehen. Dasselbe gilt für swcell. Die Anzahl der ncell kann erhöht werden, um komplizierte Schaltungen in der Hauptschaltung LOG zu integrieren. Die Anzahl der swcell kann ebenfalls erhöht werden, um den MP1 und den MN1 mit niedrigerer Impedanz zu betreiben, wenn sie aktiviert werden, wie auch vbp und vbn mit VDD und VSS angetrieben werden können.

**[0099]** Zusätzlich zu dem Entkopplungskondensator in einer Schaltzelle swcell kann ein weiterer Entkopplungskondensator in einer Raumzelle unabhängig von dem oben Gesagten eingebaut werden. Eine Raumzelle bedeutet eine Zelle, die in einen Raum eingefügt wird, der für einen Verdrahtungsbereich vorgesehen ist, beispielsweise wenn Standardzellen Seite an Seite angeordnet werden sollen. Wenn ein Entkopplungskondensator in einer solchen Raumzelle eingebaut wird, nimmt die Gesamtkapazität der Entkopplungskondensatoren auf dem Gesamt-Chip zu, so dass das Rauschen der Stromquelle in höherem Maße reduziert wird. Da eine Raumzelle ein freier Raum ist, der ursprünglich nur in der Verdrahtungsschicht vorgesehen ist, vergrößert sich nicht der Raumbedarf, selbst wenn ein Kondensator dort eingesetzt wird.

**[0100]** In einer swcell müssen sowohl der MP1 als

auch der MN1 einen Schwellenwert aufweisen, der größer als der eines MOS-Transistors in einer ncell ist. Der Grund ist der folgende: Obgleich das MOS-Transistor-Substratpotential (mit vbp oder vbn verbunden) in einer ncell unabhängig von dem Source-Potential ist, ist das Substratpotential sowohl des MP1 als auch des MN1 in der swcell immer das gleiche wie das Drain-Potential, so dass dadurch auf Grund einer Substratvorspannung keinerlei Auswirkungen erwartet werden. Es fließt daher in der Halbleiter-IC-Einheit ein unterschwelliger Leckstrom.

**[0101]** Wenn beispielsweise angenommen wird, dass  $vbp = 3,3$  V,  $vbn = -1,5$  V,  $Vdd = 1,8$  V und  $Vss = 0$  V für NMOS-Transistoren MN1 und MN2 gesetzt wird, so wird das Source-Potential S, das Drain-Potential D und das Substratpotential B von MN2 in ncell zu  $S = 0,0$  V,  $D = 1,8$  V und  $B = -1,5$  V. Folglich steigt die Schwellenspannung von MN2 auf Grund des Effekts der Substratvorspannung an, so dass der unterschwellige Leckstrom reduziert wird. Dagegen wird für das Source-Potential S, Drain-Potential D und Substratpotential B von MN1 in swcell  $S = 0,0$  V,  $D = -1,5$  V und  $B = -1,5$  V. Folglich führt der Effekt auf Grund der Substratvorspannung zu keiner Änderung der Schwellenspannung. Ein großer unterschwelliger Leckstrom fließt somit zwischen VSS und vbn in dem MN1.

**[0102]** Es gibt einige Verfahren zum Einstellen der Schwellenspannungspegel sowohl bei MP1 als auch MN1 in swcell, so dass sie größer als die der MOS-Transistoren in ncell sind. Beispielsweise kann die Konzentration der Verunreinigungen unter dem Gate, die Gate-Länge (L) oder die Filmdicke der Gate-Oxidation verändert werden. Es gibt keine Beschränkung in Bezug auf diese Verfahren, aber es wird bei dieser Ausführungsform davon ausgegangen, dass die Gate-Länge L und die Filmdicke der Gate-Oxidation verändert worden sind, um eine hohe Schwellenspannung für sowohl MP1 als auch MN1 einzustellen. Mit irgendeinem dieser Verfahren ist es möglich, Hochspannungs-MOS-Transistoren für Eingangs-/Ausgangsschaltungen (im Folgenden als I/O-Schaltung bezeichnet) zu/von einer externen Einheit des Mikrocomputers einzusetzen.

**[0103]** [Fig. 3](#) zeigt eine Ausführungsform der I/O-Schaltung. In [Fig. 3](#) wird nur ein Bit-Abschnitt der I/O-Schaltung gezeigt. Die I/O-Schaltung erhält bzw. schickt Signale an und von dem Chip über ein Eingang-/Ausgangsanschluss-PAD. Wenn SEL den Wert "L" hat, dient das PAD als Eingangsanschluss. Wenn SEL den Wert "H" hat, dient das PAD als Ausgangsanschluss. LC1 ist eine Pegelwandlerschaltung, um ein Signal mit Amplitude VDD in ein Signal mit Amplitude VDDQ zu konvertieren. Die VDDQ-Amplitude ist größer als die VDD-Amplitude. Folglich ist ein Transistor mit dicker Oxidationschicht zwischen der Pegelwandlerzelle LC1 und

dem Eingangs/Ausgangsanschluss-PAD vorgesehen. Der Transistor mit dicker Oxidationsschicht wird mit VDDQ betrieben. Bei dieser Ausführungsform wird SEL auf den Wert "L" gesetzt, um auf diese Art PULL mit einem PMOS-Pullup-Transistor hochzuziehen. Dies erfolgt nur, wenn PULL hochgezogen werden muss. Der PMOS ist ebenfalls ein Transistor mit dicker Oxidationsschicht.

**[0104]** Auf der Eingangsseite wird ein Signal mit VDDQ-Amplitude von außen eingegeben und durch einen Inverter mit **110P** und **100N** in ein Signal mit VDD-Amplitude konvertiert. Folglich verarbeiten diese beiden Transistoren Signale, deren Pegel noch nicht geändert wurde. Damit müssen sie Transistoren mit dicker Oxidationsschicht sein. Ein Widerstand **111R**, die Dioden **111D1** und **111D2** sowie ein Transistor **111** sind Eingangsschutzschaltungen. Die Dioden **111D1**, **111D2** können MOS-Transistoren sein. Die Transistoren in jeder dieser Eingangsschutzschaltungen sind Transistoren mit dicker Oxidationsschicht.

**[0105]** Eine hohe Schwellenwertspannung kann daher für die oben beschriebenen Transistoren mit dicker Oxidationsschicht eingestellt werden, da die Transistoren keine hohen Schaltgeschwindigkeiten aufweisen müssen und mit Spannungen arbeiten, die größer als VDD sind. Die Schwellenwertpegelspannung kann höher eingestellt werden als die für die Transistoren, die bei ncell verwendet werden. Folglich ist es möglich, den unterschwelligen Strom sehr niedrig zu machen, wenn ein solcher Transistor mit dicker Oxidationsschicht ausgeschaltet ist. Solche Transistoren mit dicker Oxidationsschicht können für MP1 und MN1 verwendet werden, aus denen eine Schaltzelle swcell aufgebaut ist, wie es in [Fig. 2](#) gezeigt ist. Es wird kein zusätzlicher, aufwendiger Prozess für MP1 und MN1 benötigt.

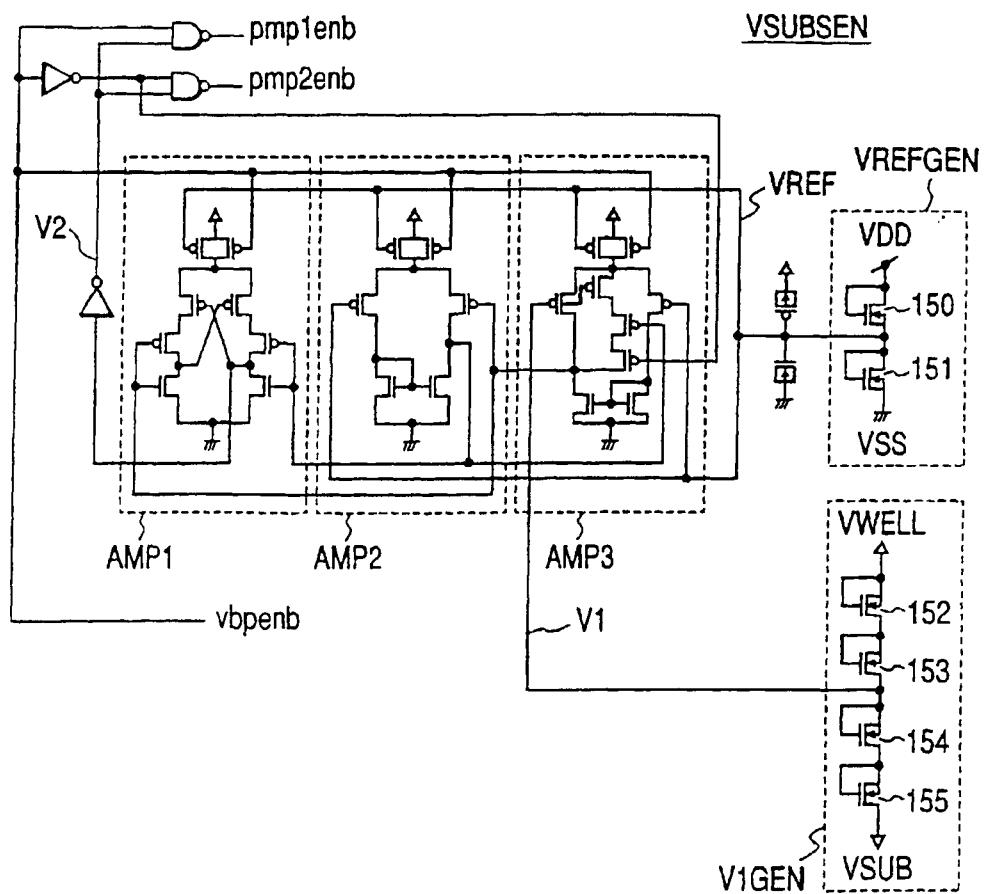

**[0106]** [Fig. 4](#) zeigt eine interne Konfiguration der Substratvorspannungssteuerschaltung VBC. Diese Steuerschaltung umfasst vier Schaltungsblöcke. VBC80 wird mit den Spannungen VDD und VSS versorgt, VBC30 wird mit den Spannungen VWELL und VSS versorgt, VBC85 wird mit den Spannungen VDD und VSUB versorgt, und VSUBGEN wird versorgt mit VWELL, VDD und VSS.

**[0107]** Folglich beträgt die Versorgungsspannung an den Schaltungen VBC30, VBC85 und VSUBGEN höchstens 3,3 V. Wenn VDDQ = VWELL gilt, so sind jedoch die Spannungen an der I/O-Schaltung VDDQ und VSSQ, wobei sich insgesamt 3,3 V ergeben. Folglich können die I/O-Schaltung und die Substratvorspannungssteuerschaltung sich ihre Einrichtungen teilen.

**[0108]** Auf der anderen Seite wird die VBC80 mit 1,8 V versorgt. Folglich wird bei den Signalleitungen von

VBC80 zu VBC30 und VBC85 ein Doppelschienensignal verwendet (ein Ausgleichssignal als Paar aus einem positiven Logiksignal und einem negativen Logiksignal). Jeder Signalpegel ändert sich (Konvertierung eines Signals mit 1,8 V-Amplitude in ein Signal mit 3,3 V-Amplitude) sowohl in VBC30 als auch in VBC85.

**[0109]** Die VBC80 ist ein Schnittstellenschaltungsblock, der als Schnittstelle zwischen den Signalen cbpr, cbnr, vbbnb und reset dient, was von einem externen Teil der Substratvorspannungssteuerschaltung und VBC30 und/oder VBC85 eingegeben wird. Die VBC30 ist ein Schaltungsblock zum Steuern der PMOS-Substratvorspannung, die VBC85 ist ein Schaltungsblock zum Steuern der NMOS-Substratvorspannung und VSUBGEN ist ein negativer Spannungsgeneratorschaltkreisblock.

**[0110]** [Fig. 5](#) zeigt Beispiele für Signalformen beim Betrieb. Die Spannung der Hauptschaltung VDD wird aktiviert, nachdem die Spannung VDDQ der I/O-Schaltung und die Spannung VWELL der Substratvorspannungssteuerschaltung VBC aktiviert worden sind. Folglich wird der negative Spannungsgeneratorschaltungsblock VSUBGEN damit gestartet, die negative Spannung VSUB zu erzeugen. Wenn auf der anderen Seite die Spannung VDD aktiviert worden ist, wird d\_reset als Signal für eine fest Zeit aufrechterhalten. Und wenn dieses Signal auf diese Art aufrechterhalten wird, wechselt die Substratvorspannungssteuerschaltung in den Zustand mit der höchsten Priorität, in welchem die Substratvorspannungen der Hauptschaltung nicht angelegt werden. Mit anderen Worten, die Substratvorspannungssteuerschaltung wechselt in den aktiven Zustand. (Das Anlegen einer Vorspannung an das Substrat auf diese Art bedeutet einen Wechsel der Substratvorspannung auf das VDD-Potential bei PMOS und auf das VSS-Potential bei NMOS. Außerdem bedeutet das Nichtanlegen einer Vorspannung an das Substrat einen Wechsel der Substratvorspannung auf ein Potential, das höher als das VDD-Potential bei PMOS ist, und ein Potential, das niedriger als das VSS-Potential bei NMOS ist.)

**[0111]** In diesem aktiven Zustand wird vbp = 1,8 V, vbn = 0 V, cbp = 0 V, cbn = 1,8 V für die PMOS-Substratvorspannungsleitung, die NMOS-Substratvorspannungsleitung, die PMOS-Substratsteuerleitung und die NMOS-Substratsteuerleitung eingestellt. Da die Substratsteuerrückführleitungen cbpr und cbnr für Rückgabesignale von cbp und cbn verwendet werden, sind die Bedingungen cbpr = cbp = 0 V und cbnr = cbn = 1,8 V erfüllt.

**[0112]** Wenn d\_reset als Signal nach einer bestimmten Zeit negiert wird, nachdem VDD aktiviert worden ist, wird die Substratvorspannung durch das vbbnb-Signal gesteuert. Wenn das vbbnb-Signal

3,3 V ist, so wird der Standby-Zustand eingestellt, so dass eine Vorspannung an das Objektsubstrat angelegt wird. Wenn das vbbnb-Signal 0 V beträgt, wird der aktive Zustand eingestellt, so dass keine Vorspannung an das Objektsubstrat angelegt wird.

**[0113]** Mit anderen Worten, wenn der Pegel des vbbnb-Signals von 0 V auf 3,3 V angehoben wird, ändert sich der Zustand so, dass  $vbp = cbp = 3,3$  V und  $vbn = cbn = -1,5$  V gilt. Danach wird der Zustand umgeschaltet, so dass  $cbpr = cbp = 3,3$  V und  $cbnr = cbn = -1,5$  V gilt. Das vbbnbr-Signal wird dann auf 3,3 V geschaltet, wenn  $cbpr = 3,3$  V und  $cbnr = 0$  V gilt. Folglich, wenn der Pegel des vbbnb-Signals von 0 V auf 3,3 V umgeschaltet wird, wird das Signal nach einer bestimmten Zeit auf 3,3 V gesetzt (nachdem die Rückföhrensignale cbpr und cbnr von cbp oder cbn zurückgekommen sind).

**[0114]** Wenn das vbbnb-Signal von 0 V auf 3,3 V im Pegel umgeschaltet wird, werden andere Signale bezüglich ihres Pegels ebenfalls umgeschaltet wie folgt:  $vbp = 1,8$  V,  $cbp = 0$  V,  $vbn = 0$  V und  $cbn = 1,8$  V. Dann werden diese anderen Signale im Pegel eine bestimmte Zeit später wie folgt umgeschaltet:  $cbpr = cbp = 0$  V,  $cbnr = cbn = 1,8$  V und  $vbbnbr = 0$  V. vbbnbr arbeitet auf diese Art und Weise als Rückgabesignal von vbbnb. Wie in [Fig. 2](#) gezeigt, ist es außerdem möglich, da das Substratpotential durch die Potentiale von cbp und cbn festgelegt ist, den Substratpotentialzustand zu erfassen, indem vbbnbr überwacht wird, das sich aus den Potentialen von cbp und cbn ergibt.

**[0115]** [Fig. 6](#) zeigt Signalformen im Betrieb der Substratvorspannungssteuerschaltung bei einer weiteren Ausführungsform, die sich alle von denen in [Fig. 5](#) unterscheiden. Wie in [Fig. 6](#) gezeigt, wird dann, wenn cbp und cbn gesteuert werden, die Steuerschaltung in Bezug auf die Konfiguration etwas komplizierter, aber eine Steuerschaltung, die auf diese Weise komplizierter ist, macht es möglich, dass eine größere Spannung sowohl an den Source- als auch an den Gate-Anschluss von MP1 und MN2 in [Fig. 2](#) im aktiven Zustand angelegt werden kann. So mit können sowohl vbp als auch vbn mit niedrigerer Impedanz betrieben werden. In diesem Fall wird das cbp- und cbn-Äquivalent zu dem Gate-Steuersignal in der Amplitude größer als die Gate-Durchbruchspannung der Substrat-Treibertransistoren MP1 und MN1. Wie jedoch in [Fig. 6](#) gezeigt, werden dann, wenn sowohl cbp als auch cbn langsam in ihrem Pegel geändert werden, die Spannungen zwischen dem Gate- und dem Drain-Anschluss wie auch zwischen dem Gate- und dem Source-Anschluss sowohl bei MP1 als auch MN1 höchstens 3,3 V betragen, was der Gate-Durchbruchspannung entspricht oder niedriger ist.

**[0116]** Im Folgenden wird zu jedem Schaltungs-

block der Schaltplan genauer beschrieben. Um die Beschreibung zu vereinfachen, wird bei jedem Schaltungsblock angenommen, dass er eine Schaltung ist, die die Signalform in [Fig. 4](#) erzeugt.

**[0117]** [Fig. 7](#) zeigt einen Schaltplan der VBC80. Die Ziffer **120** ist ein NAND mit 2-fachem Eingang, **121** ist ein AND mit 2-fachem Eingang und Schmitt-Schaltverhalten, **122** ist ein Inverter, **123** ist ein NOR, **124** ist ein Puffer mit Schmitt-Eigenschaften, und **125** ist ein Puffer mit einem Differenzausgang. **126** ist eine Einschalt-Reset-Schaltung, deren Ausgang **127** von 0 V Schritt für Schritt auf 1,8 V aufgeladen wird, nachdem die Stromquelle VDD aktiviert wurde. Folglich liefert der Zweifacheingangs-AND **121** während einer festen Zeit 0 V und gibt dann 1,8 V aus. Das  $d_{reset}$ -Signal wird daher bei diesem Ausgang für eine feste Zeit aufrechterhalten, wie es in [Fig. 5](#) gezeigt ist, wenn die Stromquelle VDD aktiviert wurde. Obgleich die Einschalt-Reset-Schaltung **126** in [Fig. 7](#) einfach mit Widerständen und Kondensatoren aufgebaut ist, kann die Schaltung **126** genauso gut auf andere Weise aufgebaut werden, wenn es möglich ist, die stabilisierte Stromquelle VDD zu erkennen.

**[0118]** Die Signale  $d_{vbbnb}$ ,  $d_{cbpr}$  und  $d_{cbnr}$  erhält man durch jeweiliges Konvertieren der Signale vbbnb, cbpr und cbnr zu Doppelschienensignalen. Diese Doppelschienensignale werden verwendet, um die Substratsteuerung zu aktivieren, wenn der Einschaltzustand zurückgesetzt worden ist.  $d_{vbbnbr}$  wird als Doppelschienensignal zum Erzeugen von vbbnbr in [Fig. 5](#) aus cbpr und cbnr erzeugt.

**[0119]** [Fig. 8](#) ist ein Schaltplan von VBC30. Die Ziffer **130** ist eine Pegelwandlerschaltung, um Signale **133** (VWELL bis VSS) mit 3,3 V-Amplitude aus den Doppelschienensignalen (VDD bis VSS) mit 1,8 V-Amplitude sowohl der  $d_{vbbnb}$ - als auch der  $d_{reset}$ -Signale zu erzeugen. Ein Signal **133** geht in "L" in den aktiven Zustand über oder wenn das Einschaltsignal zurückgesetzt worden ist.

**[0120]** Die Ziffer **131** ist ebenfalls eine Pegelwandlerschaltung zum Erzeugen von Signalen **134** (VWELL bis VSS) mit 3,3 V-Amplitude aus Doppelschienensignalen (VDD bis VSS) mit 1,8 V-Amplitude sowohl der  $d_{cbpr}$ - als auch der  $d_{reset}$ -Signale. Ein Signal **134** wird 0 V, wenn das Signal cbpr 0 V ist oder wenn das Einschaltsignal zurückgesetzt worden ist. Wenn ein Signal **133** seinen Pegel auf 0 V verändert, so kommt das Signal vbp in den Hochimpedanzzustand, und sowohl cbp als auch cbnbr werden 0 V. Wenn das Signal cbp 0 V wird, so wird der MP1 in jeder swcell in der Hauptschaltung aktiviert, und das Signal vbp wird auf 1,8 V gesetzt.

**[0121]** Die Ziffer **132** ist ebenfalls eine Pegelwandlerschaltung, um das Signal  $d_{vbbnbr}$  von der

VBC80 in [Fig. 7](#) als ein Signal vbbenbr mit 3,3 V-Amplitude auszugeben.

**[0122]** [Fig. 9](#) zeigt, wie sich der Signalpegel von cbp ändert. Die Ausgangsimpedanz von cbp ändert sich in zwei Stufen. cbp wird durch den Inverter **135** getrieben, der durch ein Signal **133** gesteuert wird. Wenn beide Signale **133** und **134** auf 0 V liegen, wird der NMOS **136** aktiviert, so dass dadurch cbp angetrieben wird. Bei dieser Ausführungsform wird die Gate-Breite des NMOS **136** breiter eingestellt als die des NMOS in dem Inverter **135**. Wenn die Halbleiter-IC-Einheit in den aktiven Zustand gelangt und das Signal **133** zu 0 V wird, dann treibt der Inverter **135** cbp auf 0 V. Da jedoch die cbp in der ganzen Hauptschaltung verdrahtet ist und versehen ist mit einer großen Ladekapazität, wird cbp langsam auf 0 V getrieben. Diese Änderung von cbp wird durch eine Änderung des Signals cbpr erfasst, das ein Rückgabesignal zu cbp ist. Das Signal **c\_cbpr** ändert sich damit im Pegel. Folglich wird das Signal **134** auf 0 V getrieben, und der NMOS **136** wird aktiviert. Folglich wird cbp bei niedriger Impedanz auf 0 V getrieben. Auf diese Art wird cbp bei niedriger Impedanz in den aktiven Zustand getrieben und weniger durch Rauschen auf Grund des Betriebes der Hauptschaltung beeinträchtigt. Und wenn cbp auf 0 V getrieben wird, wird der MP1 in jeder swcell in der Hauptschaltung aktiviert. Wenn cbp auf 0 V langsam getrieben wird, wie es in [Fig. 8\(B\)](#) gezeigt ist, so kann jedoch der MP1 in jeder swcell signifikant vor Rauschen bei gleichzeitigem Schalten geschützt werden.

**[0123]** [Fig. 10](#) zeigt einen Schaltplan der VBC85. **140** ist eine Pegelwandlerschaltung, um Signale **142** (VDD bis VSUB) mit 3,3 V-Amplitude aus Doppelschienensignalen (VDD bis VSS) mit 1,8 V-Amplitude sowohl bei **d\_vbbenb-** als auch **d\_reset**-Signalen zu erzeugen. Ein Signal **142** liegt auf 1,8 V im aktiven Zustand oder wenn das Einschaltsignal zurückgesetzt worden ist.

**[0124]** **141** ist ebenfalls eine Pegelwandlerschaltung, um Signale **143** (VDD bis VSUB) mit 3,3 V-Amplitude aus Doppelschienensignalen (VDD bis VSS) mit 1,8 V-Amplitude sowohl bei **d\_cbnr-** als auch **d\_reset**-Signalen zu bilden. Ein Signal **143** liegt auf 1,8 V, wenn das Signal cbnr 1,8 V ist oder wenn das Einschaltsignal zurückgesetzt worden ist. Wenn ein Signal **142** auf 1,8 V getrieben wird, gelangt das Signal vbn in den Hochimpedanzzustand, und das Signal cbn wird auf 1,8 V getrieben. Wenn das Signal cbn auf 1,8 V getrieben wird, wird der MN1 in jeder swcell in der Hauptschaltung aktiviert. Das Signal vbn wird damit auf 0 V getrieben.

**[0125]** [Fig. 11](#) zeigt, wie sich cbn ändert. Die Ausgangsimpedanz von cbn wird in zwei Schritten geändert, wie es der Fall bei cbp ist. cbn wird durch den Inverter **144** getrieben, der durch das Signal **143** ge-

steuert wird. Wenn das Signal **142** auf 1,8 V liegt und das Signal **143** auf 1,8 V liegt, so wird jedoch der PMOS **145** aktiviert, damit wird er also durch den PMOS **145** getrieben. Bei dieser Ausführungsform ist die Gate-Breite des PMOS **145** größer eingestellt als die Gate-Breite des PMOS in dem Inverter **144**. Wenn die Halbleiter-IC-Einheit in den aktiven Zustand umschaltet und das Signal **142** auf 1,8 V getrieben wird, so treibt der Inverter **144** cbn auf 0 V. cbn ist jedoch in der ganzen Hauptschaltung verdrahtet, und die dazugehörige Ladekapazität ist groß. cbn wird daher langsam auf 0 V getrieben. Dieses Umschalten wird auf Grund einer Veränderung des Rückgabesignals cbnr zu cbn erkannt, wobei sich das Signal **d\_cbnr** im Pegel ändert. Dadurch wird das Signal **143** auf 1,8 V getrieben und der PMOS **145** aktiviert. Folglich wird bei niedriger Impedanz cbn auf 1,8 V getrieben. Auf diese Art wird, wenn die Halbleiter-IC-Einheit aktiv ist, cbn bei niedriger Impedanz genau wie cbp getrieben, so dass dadurch die Halbleiter-IC-Einheit effektiv vor Rauschen geschützt werden kann, das durch Betrieb der Hauptschaltung erzeugt wird. Wenn cbn auf 1,8 V getrieben wird, wird der MN1 in jeder swell in der Hauptschaltung aktiviert. Wenn cbn langsam auf 1,8 V getrieben wird, wie es in [Fig. 11](#) gezeigt ist, so kann jedoch das Rauschen auf Grund gleichzeitigen Schaltens beim MN1 in jeder swell reduziert werden.

**[0126]** Wie oben beschrieben, ist gemäß dem Substratvorspannungssteuerverfahren der vorliegenden Erfindung die Substrat-Treiberimpedanz in dem aktiven Zustand, bei dem keine Vorspannung an jedes Substrat angelegt wird (das Substrat wird bei jeder swell getrieben), kleiner als in dem Standby-Zustand, bei dem eine Vorspannung an jedes Substrat angelegt wird (das Substrat wird mit VBC getrieben). Wenn die Halbleiter-IC-Einheit in den aktiven Zustand umgeschaltet wird, wobei sie, wie oben beschrieben, mit Strom versorgt wird, ist es folglich möglich, Probleme beim Anstieg des Stromes, die auf Instabilitäten des Substratpotentials zurückzuführen sind, was sich zu einem Einschaltzeitpunkt über die Stromquellen fortpflanzt, wie auch ein Latch-up-Problem zu vermeiden. Obgleich das Substratrauschen durch den Betrieb der Hauptschaltung in dem aktiven Zustand zunimmt, kann das Rauschen zusätzlich reduziert werden, wodurch bei der Hauptschaltung Probleme wie Fehlfunktion, Latch-up etc. vermieden werden, wenn die Substrat-Treiberimpedanz auf einen niedrigen Wert gedrückt wird.

**[0127]** [Fig. 12](#) zeigt eine interne Konfiguration der negativen Spannungsgeneratorschaltung VSUB-GEN. Die Schaltung ist aus drei Schaltungsblöcken zusammengesetzt. VSUBSEN ist eine Substratvorspannungserfassungsschaltung, PMP1 ist eine Ladeungspumpenschaltung 1 und PMP2 ist eine Ladeungspumpenschaltung 2. Die Substratvorspannungserfassungsschaltung VSUBSEN überwacht

das VSUB-Potential wie auch sowohl den aktiven als auch den Standby-Zustand unter Verwendung des Signals `vbpemb`. Entsprechend können PMP1 und PMP2 unter Verwendung der Steuersignale `pmp1enb` und `pmp2enb` gesteuert werden, um sicherzustellen, dass  $VSUB = VDD + VSS - VWELL$  gilt.

**[0128]** PMP1 wird gestartet, wenn das Signal `pmp1enb` gesetzt ist, und PMP2 wird gestartet, wenn das Signal `pmp2enb` gesetzt wird. In der Pumpkapazität unterscheiden sich PMP1 und PMP2. PMP1 hat eine Pumpkapazität, die größer ist als die von PMP2. Das Signal `vbpemb` dient zur Wahl zwischen PMP1 oder PMP2. PMP2 wird im aktiven Zustand verwendet, und PMP1 wird im Standby-Zustand verwendet.

**[0129]** Das VSUB-Potential wird nur in der Substratvorspannungssteuerschaltung verwendet, wenn sich die Halbleiter-IC-Einheit in dem aktiven Zustand befindet. Somit fließt soweit nicht viel Strom in das VSUB. Folglich wird die PMP2 verwendet, deren Pumpkapazität klein ist. In dem Standby-Zustand wird das VSUB-Potential an die gesamte Hauptschaltung angelegt. Somit fließt als Strom ein Übergangsstrom etc. in VSUB. Folglich wird die PMP1 verwendet, deren Pumpkapazität groß ist.

**[0130]** [Fig. 13](#) zeigt ein Schaltbild der Ladungspumpe 1 PMP1 gemäß der vorliegenden Erfindung. OSC ist ein schwimmender Ringoszillatator, mit dem VSUB auf eine negative Spannung gebracht wird, und zwar nur, wenn das Signal `pmp1enb` gesetzt ist.

**[0131]** [Fig. 14](#) zeigt einen Schalplan der Ladungspumpe, die man dadurch erhält, dass man die PMOS **162** und **163** zu einer Ladungspumpenschaltung hinzufügt, wie es von Kiyoo Ito in "VLSI memory (p266)", veröffentlicht bei Baifukan, beschrieben wird. Die Ladungspumpe erzeugt VSUB mit den PMOS **160** und **162**, die zweimal während eines Oszillatorzyklus des Ringoszillators eingesetzt werden. Gemäß der vorliegenden Erfindung werden außerdem NMOS **164** und **165** zu der Ladungspumpe wie in [Fig. 13](#) hinzugefügt. Folglich ist die VSUB weniger betroffen durch die Schwellenwertpegel der beiden PMOS **160** und **161**, so dass die VSUB selbst bei Betrieb mit niedriger Spannung zufriedenstellend arbeitet. Wenn  $VWELL$  auf 3,3 V liegt, so erhält man mit dem Aufbau nach [Fig. 14](#) nur  $VSUB = -3,3 V + vthp$  ( $vthp$  = absoluter Schwellenwertpegel für beide PMOS **160** und **161**); maximal ist  $VSUB = -2,3 V$  erreichbar. Dagegen ist es mit dem Verfahren nach der vorliegenden Erfindung möglich, ein  $VSUB = -3,3 V$  oder ähnlich zu erreichen.

**[0132]** Bei dieser Ausführungsform wird kein Schalplan speziell für die Ladungspumpe 2 PMP2 gezeigt. Jedoch kann die Kapazität jedes der PMOS CP3 und CP4, die als Kondensatoren in [Fig. 3](#) eingesetzt wer-

den, auf diese Weise reduziert werden, um so die Kapazität jedes der Kondensatoren zu reduzieren. Selbstverständlich können die Größen anderer MOS-Transistoren optimiert werden, um sie in Bezug auf diesen CP3 oder CP4 anzupassen.

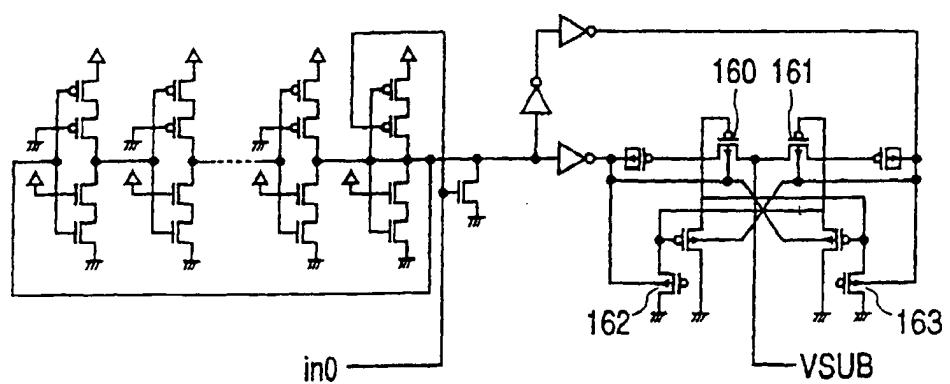

**[0133]** [Fig. 15](#) zeigt ein Schaltbild der Substratvorspannungserfassungsschaltung VSUBSEN. VREF-GEN ist eine Referenzspannungsgeneratorschaltung, um einen Ausgang  $VREF = (VDD - VSS)/2$  mit den NMOS-Transistoren **150** und **151** zu erzeugen, die in Serie geschaltet sind. V1 GEN ist eine VSUB-Potentialerfassungsschaltung, um einen Ausgang  $V1 = (VWELL - VSUB)/2$  mit den NMOS-Transistoren **152** bis **155** zu erzeugen, die in Serie geschaltet sind. Die Schaltung wird so aufgebaut, dass etwa 1 V zwischen Source und Drain jedes NMOS-Transistors angelegt wird, wobei außerdem das Gate lang ist. Folglich wird es möglich, den kontinuierlichen Strom von  $VDD$  auf  $VSS$  oder von  $VWELL$  auf  $VSUB$  auf niedrige Werte zu drücken. Da die Schaltung im Sättigungsbereich betrieben wird, kann die Schaltung außerdem  $VREF$  oder  $V1$  erzeugen, ohne von Schwankungen abzuhängen. Außerdem werden bei der vorliegenden Erfindung NMOS-Transistoren und nicht PMOS-Transistoren eingesetzt. NMOS-Transistoren haben im Vergleich zu PMOS-Transistoren exzellente Sättigungseigenschaften. Die Schaltung kann somit  $VREF$  oder  $V1$  erzeugen, ohne von Schwankungen bei NMOS-Transistoren abzuhängen, selbst wenn nur etwa 1 V zwischen Source und Drain anliegt.

**[0134]** AMP1, AMP2 und AMP3 sind Differenzverstärker, die zusammengeschaltet sind, um einen Differenzverstärker zu bilden. Der Differenzverstärker aus AMP1, AMP2 und AMP3 wird mit  $VREF$  und  $V1$  versorgt, und wenn  $VREF < V1$  gilt, so wird `pmp1enb` oder `pmp2enb` gesetzt. Folglich wird VSUB auf eine negative Spannung gebracht. Wenn  $VREF > V1$  gilt, so wird `pmp1enb` oder `pmp2enb` negiert. Da VSUB für einen Leckstrom nach  $VSS$ ,  $VWELL$  und  $VDD$  sorgt, wenn sowohl `pmp1enb` als auch `pmp2enb` negiert sind, wird VSUB auf ein positives Potential kurzgeschlossen. `pmp1enb` oder `pmp2enb` wird gesetzt bzw. negiert, so dass  $V1 = VREF$  gilt, das heißt  $VSUB = VDD - VWELL$  gehalten wird. Wenn `vbpemb` auf 3,3 V liegt (Standby-Zustand), wie es oben beschrieben wurde, so wird `pmp1enb` gesetzt. Wenn `vbpemb` auf 0 V liegt (aktiver Zustand), so wird `pmp2enb` gesetzt.

**[0135]** Zwischen AMP1 und AMP2 besteht ein Rückkopplungspfad. Der Differenzverstärker aus AMP1, AMP2 und AMP3 erhält damit eine Hysterese. Die Hysterese, die hier gemeint ist, hat eine Änderung des Differenzierungspunktes des Differenzverstärkers zur Folge, was sich an einem Ausgang des Verstärkers auswirkt. Mit anderen Worten, man hat ein Schmitt-Schaltverhalten. Damit wird vermieden, dass `pmp1enb` oder `pmp2enb` vielfach und wieder-

holt um  $V1 = VREF$  herum gesetzt/negiert wird, so dass man damit auch die Zunahme des Stromverbrauchs reduziert.

**[0136]** Darüber hinaus wird der Betriebsstrom des Differenzverstärkers im AMP1 bis AMP3 verändert, je nachdem, ob  $vbp_{enb}$  gesetzt oder negiert ist. Im Standby-Zustand, in dem  $vbp$  gesetzt ist, ist  $vbn$  der Hauptschaltung mit  $VSUB$  verbunden. Dies bedeutet, dass eine große Substratkapazität mit der Hauptschaltung verbunden ist. Der Pegel von  $VSUB$  ändert sich damit langsam. Da kein Betrieb mit hoher Geschwindigkeit zwischen AMP1 und AMP3 benötigt wird, kann der Betriebsstrom begrenzt werden, so dass der Stromverbrauch von AMP1 bis AMP3 im Betrieb reduziert wird. Auf der anderen Seite, wenn im aktiven Zustand  $vbp$  negiert ist, ist nur die Substratvorspannungssteuerschaltung VBC mit  $VSUB$  verbunden. Dies bedeutet, dass eine relativ kleine Kapazität mit  $VSUB$  verbunden ist. Folglich ändert sich der Pegel von  $VSUB$  schnell, so dass ein Betrieb mit hoher Geschwindigkeit beim Betrieb von AMP1 bis AMP3 benötigt wird. Im aktiven Zustand ist der Stromverbrauch nicht so hoch. Ein großer Betriebsstrom wird daher im Prozess zwischen AMP1 und AMP3 bereitgestellt, um Betrieb mit hoher Geschwindigkeit zu ermöglichen.

**[0137]** Im Folgenden wird das Substratvorspannungsversorgungsverfahren im Einzelnen anhand einer Ausführungsform der vorliegenden Erfindung erläutert.

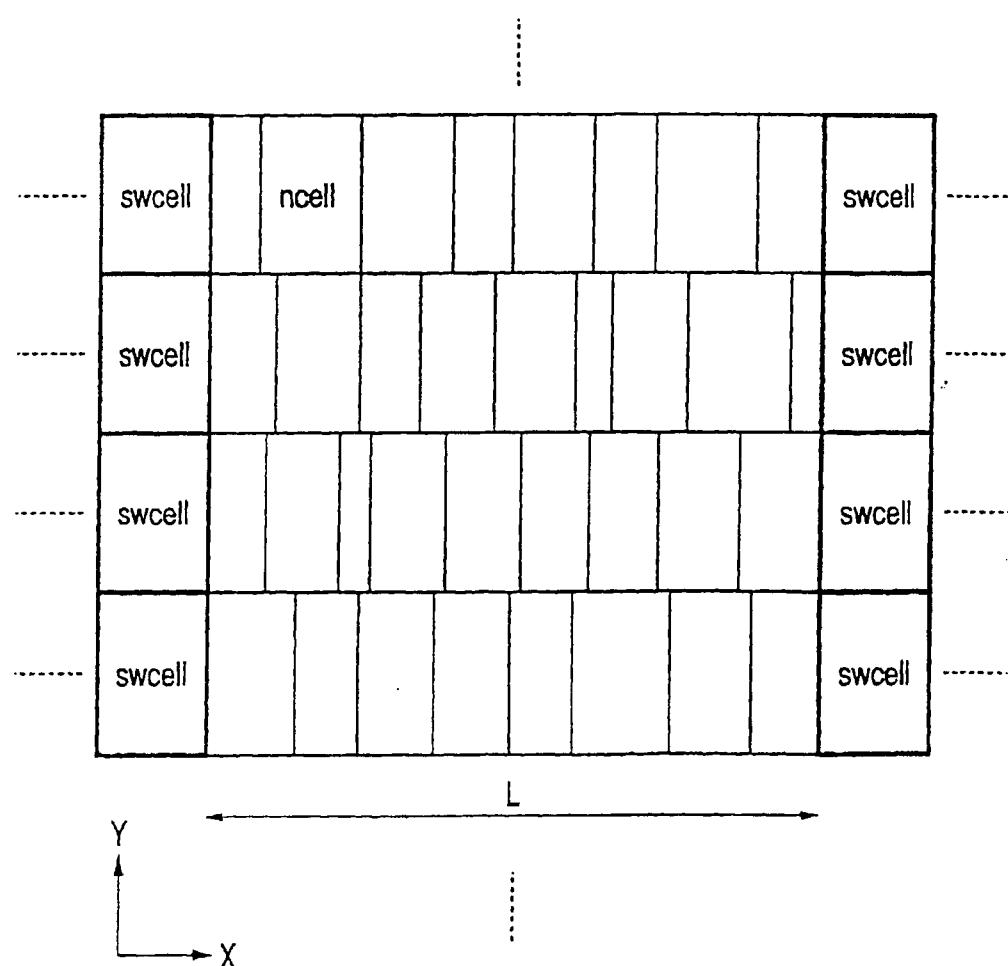

**[0138]** [Fig. 16](#) zeigt das Layout von  $ncell$  und  $swcell$ . Die  $swcell$  werden kontinuierlich in vertikaler Richtung (Y) angeordnet. Sowohl  $swcell$  als auch  $ncell$  sind in Bezug auf die Höhe ausgerichtet. In der horizontalen Richtung (X) sind die  $swcell$  mit variablen Abständen  $L$  innerhalb eines bestimmten Wertes angeordnet. Selbstverständlich können diese Zellen in gleichen Abständen angeordnet werden, aber das Variieren der Abstände eröffnet mehr Möglichkeiten beim Layout. Auf jeden Fall kann der Abstand  $L$  nach den folgenden Kriterien ausgewählt werden:

- (1) Stromleitungsimpedanz,

- (2) Stromverdrahtungsmigration,

- (3) Substratauschen im  $vbp$  und  $vbn$  je nach Betrieb von  $ncell$ .

**[0139]** [Fig. 17](#) zeigt das interne Layout einer  $ncell$ . Wie im Fall von [Fig. 2](#) wird ein Inverter als Beispiel genommen. Bei  $vbp$ ,  $vbn$ ,  $VDD$  und  $VSS$  erfolgt die Versorgung durch die erste Schicht metallischer Verdrahtungen aus vier Leitungen, die parallel zueinander verlaufen (im Folgenden mit  $M1$  bezeichnet). Bei  $vbp$  und  $vbn$  erfolgt außerdem die Versorgung über die Oberflächenschicht hoher Dichte.  $H$  ist die Zellenhöhe, mit der eine Basiseinheit für die Wiederholung in vertikaler Richtung (Y) angegeben wird.  $ncell$  ist in der vertikalen Richtung (Y) angeordnet, so dass alle

in Bezug auf diese Höhe spiegelbildlich zueinander sind. Folglich können die  $ncells$  sich sowohl  $vbp$  als auch  $vbn$  teilen, die in vertikalen Positionen benachbart sind, so dass die  $ncell$ -Fläche reduziert wird.

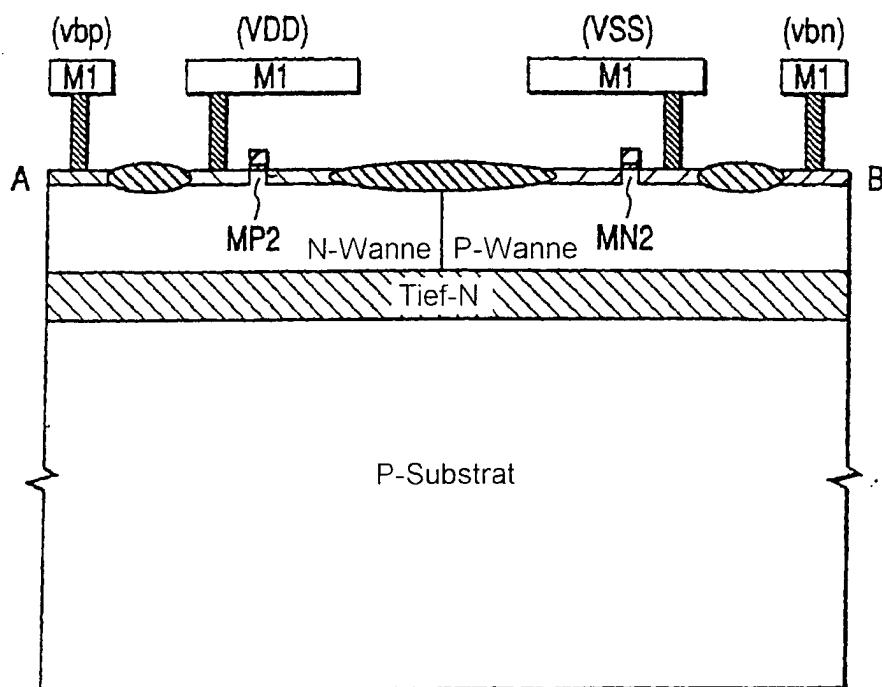

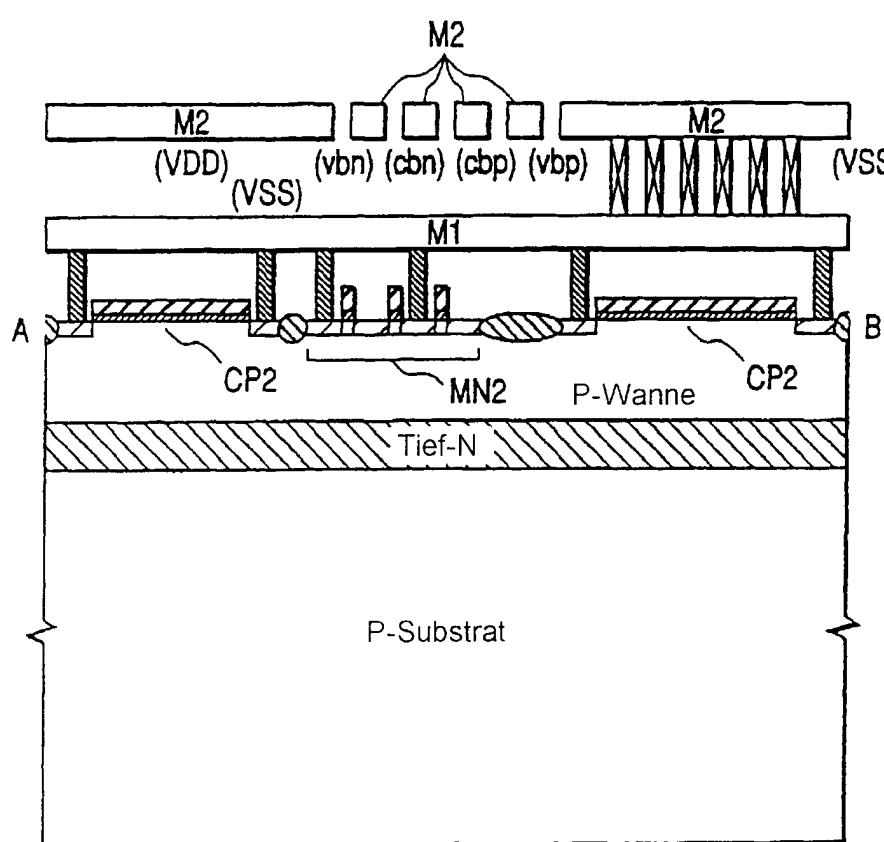

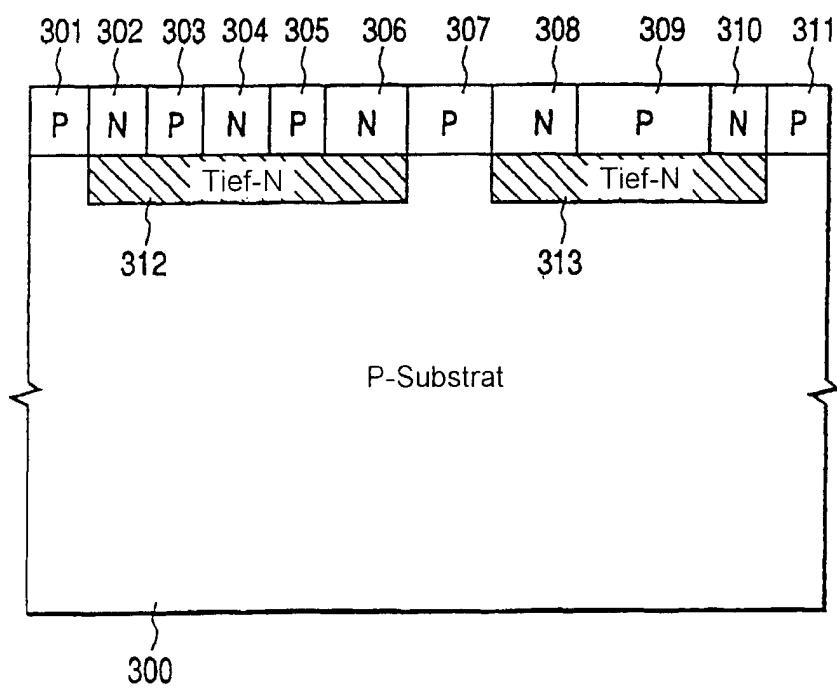

**[0140]** [Fig. 18](#) zeigt einen Querschnitt durch [Fig. 17](#) entlang der Linie A-B. Die N-Wanne ist eine N-Wanne zur Herstellung von MP2, und die P-Wanne ist eine P-Wanne zur Herstellung von MN2. Tief-N ist eine N-Wanne, die tiefer angelegt ist als die N-Wanne und die P-Wanne. Mit anderen Worten, die  $ncell$  hat eine Dreischichten-Wannenstruktur.

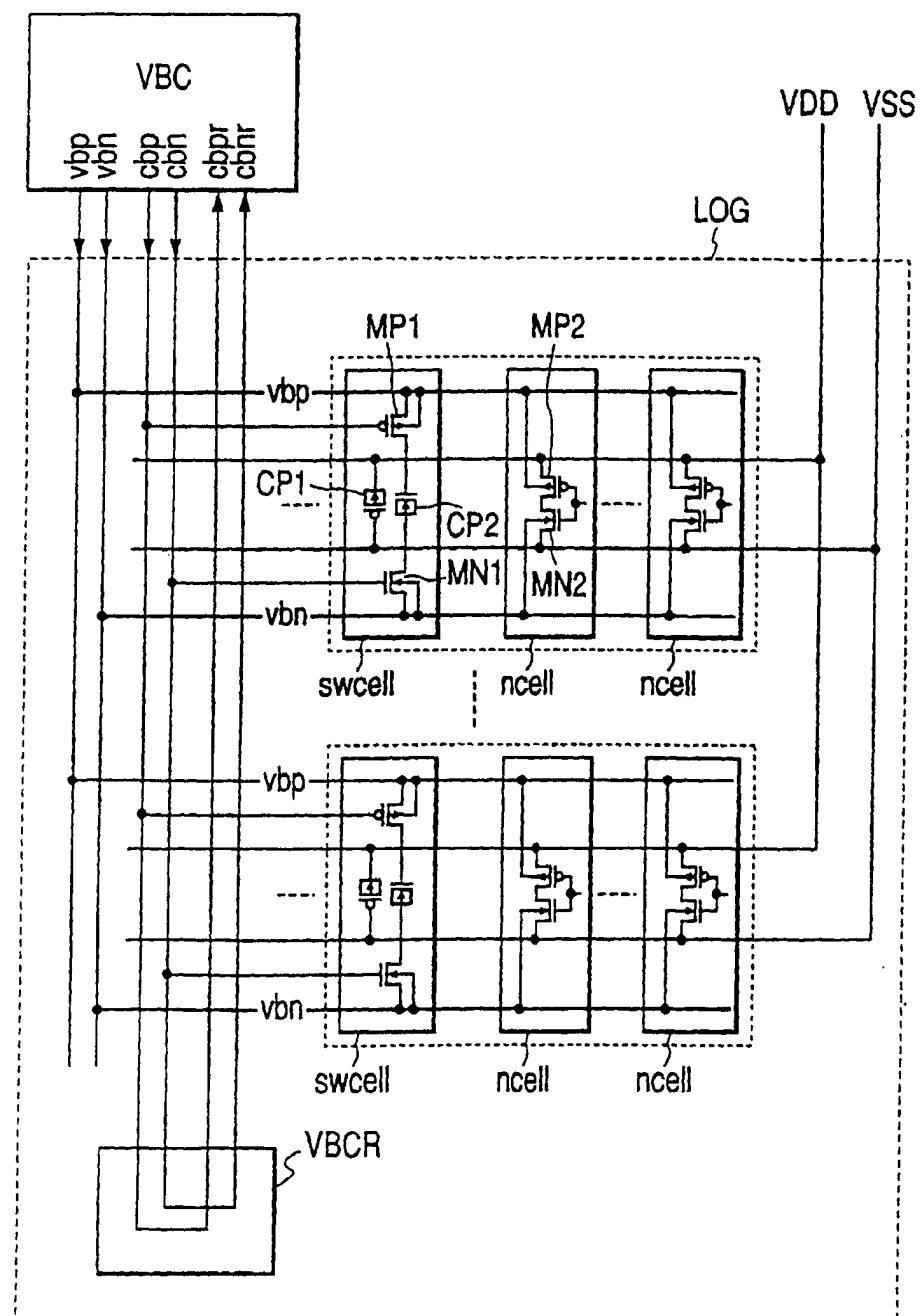

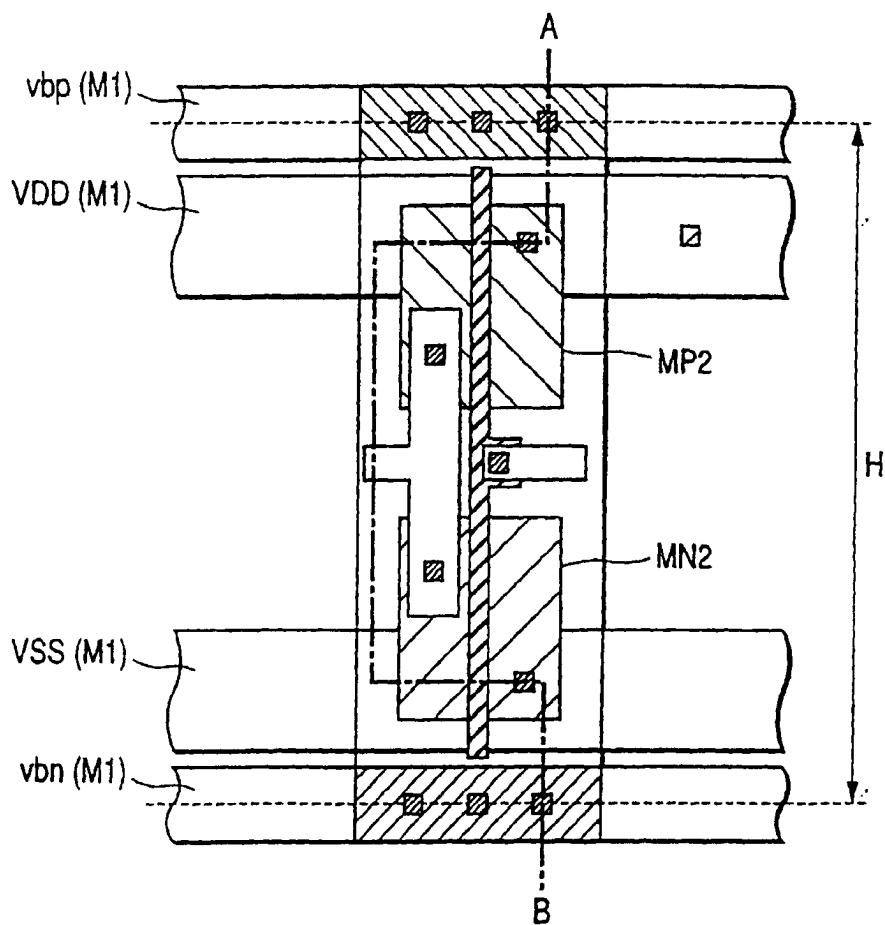

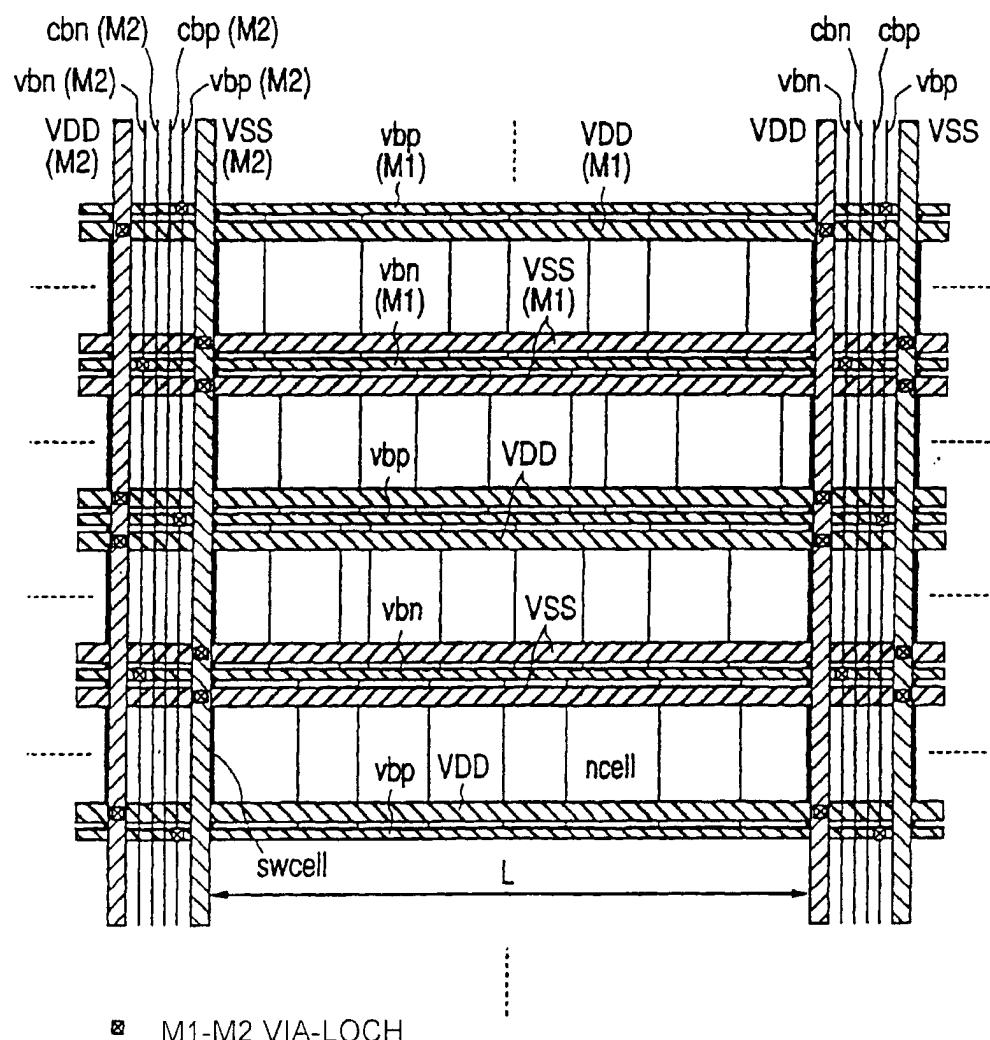

**[0141]** [Fig. 19](#) zeigt das interne Layout einer  $swcell$ .  $H$  ist eine Zellenhöhe wie im Fall von  $ncell$ .  $vbp$ ,  $vbn$ ,  $VDD$  und  $VSS$  werden durch  $M1$  bereitgestellt, und zwar auf die gleiche Art wie bei  $ncell$ . Wie in [Fig. 16](#) gezeigt, sind die  $swcells$  kontinuierlich in vertikaler Richtung (Y) angeordnet. Horizontal haben diese Zellen einen Abstand, der auf einen bestimmten Wert beschränkt ist. Mit einem solchen Aufbau wird es möglich, die Verdrahtung von Stromrückfallleitungen an den Orten der  $swcell$  vorzunehmen. In [Fig. 19](#) sind die metallischen Leitungen der zweiten Schicht parallel zu der vertikalen Richtung zwei Stromrückfallleitungen. Zwischen diesen beiden Stromrückfallleitungen sind zwei Rückfallleitungen  $vbp$  und  $vbn$  und zwei weitere Leitungen  $cbp$  und  $cbn$  angeordnet. Die Stromrückfallleitungen  $VDD$  und  $VSS$  an beiden Enden dienen dazu, die vier Substratvorspannungssteuerleitungen vor Rauschen von außen zu schützen.

**[0142]** MP1 wird mit sechs einzelnen Transistoren aufgebaut. Gate, Drain und Source jedes Transistors in MP1 sind mit  $cbp$ ,  $vbp$  bzw.  $VDD$  verbunden. MN1 ist aus drei einzelnen Transistoren aufgebaut. Gate, Drain und Source jedes Transistors in MN1 sind mit  $cbn$ ,  $vbn$  bzw.  $VSS$  verbunden. Jeder der Entkopplungskondensatoren CP1 und CP2 ist auf zwei Transistoren aufgeteilt. Die Transistoren von CP1 als auch CP2 befinden sich an beiden Enden von MP1 bzw. MN1. Die Kapazität von CP1 und CP2 wird durch die MOS-Gate-Kapazität erzeugt.

**[0143]** Das Verhältnis der Entkopplungskondensatoren CP1 und CP2 zu denen von MP1 und MN1 ist nicht speziell eingeschränkt. In einem Extrembeispiel ist einer oder sind beide der Entkopplungskondensatoren CP1 und CP2 überflüssig. Die Rauschleistung kann mit einem Entkopplungskondensator reduziert werden, wenn seine Größe zunimmt. Auf der anderen Seite, wenn MP1 und MN1 in ihrer Größe zunehmen, kann die Substratvorspannung mit einer Stromquelle niedriger Impedanz verbunden werden, wenn sich der Mikroprozessor in dem Normalzustand befindet, um einen besseren Schutz vor Rauschen zu bewirken, und um auch Schwierigkeiten durch Latch-up zu vermeiden.

[0144] Die VIA-Löcher zwischen den VDD-Leitungen von M1 und M2 wie auch die VIA-Löcher zwischen den VSS-Leitungen von M1 und M2 sind hier fortgelassen, um die Beschreibung zu vereinfachen. Ein VIA-Loch kann an jedem Schnittpunkt der Verdrahtung erzeugt werden.

[0145] [Fig. 20](#) zeigt einen Querschnitt nach [Fig. 19](#) entlang der Linie A-B. Wie in [Fig. 18](#) gezeigt, ist die P-Wanne eine P-Wanne zum Herstellen von MN1, und Tief-N ist eine N-Wanne, die tiefer gelagert ist als die P-Wanne. swcell hat daher eine so genannte Dreischichten-Wannenstruktur. In diesem Fall sind die VIA-Löcher, die in [Fig. 19](#) fortgelassen worden, tatsächlich zwischen den VSS-Leitungen bei M1 wie auch bei M2 eingezeichnet. Wie in [Fig. 2](#) gezeigt, wird ein Transistor mit dicker Oxidationsschicht für MN2 verwendet, um den Schwellenwertpegel anzuheben.

[0146] [Fig. 21](#) zeigt ein konkretes Beispiel für die Art, in der die Stromleitungen VDD und VSS verdrahtet werden können, wie auch die Substratvorspannungssteuerleitungen vbp, vbn, cbp und cbn. Das Layout der Stromleitungen in [Fig. 21](#) erhält man durch Hinzufügen der obigen Leitungen zu dem Layout zu [Fig. 16](#). In der horizontalen Richtung (X) werden VDD, VSS, vbp und vbn mit M1 parallel zueinander verdrahtet. Wie in [Fig. 17](#) gezeigt, teilen sich zwei Zellen vbp, die übereinander liegen, wobei vbp dazwischen liegt. Und damit werden zwei VDD-Leitungen parallel übereinander und unter diesen beiden Zellen verlegt. Außerdem teilen sich vbn zwei Zellen, die vertikal übereinander angeordnet sind, wobei vbn dazwischen liegt. Und somit liegen zwei VSS-Leitungen parallel über und unter diesen zwei Zellen. Selbstverständlich können sowohl die VDD- als auch die VSS-Leitungen dicker als die vbp- und vbn-Leitungen sein.

[0147] Wie in [Fig. 19](#) gezeigt, sind VDD, VSS, vbp, vbn, cbp und cbn mit M2 verdrahtet und auf den swcells in der vertikalen Richtung (Y) angeordnet. VDD, VSS, vbp und vbn sind miteinander verbunden, wie ein Gitter, an den Schnittpunkten von M1 und M2.

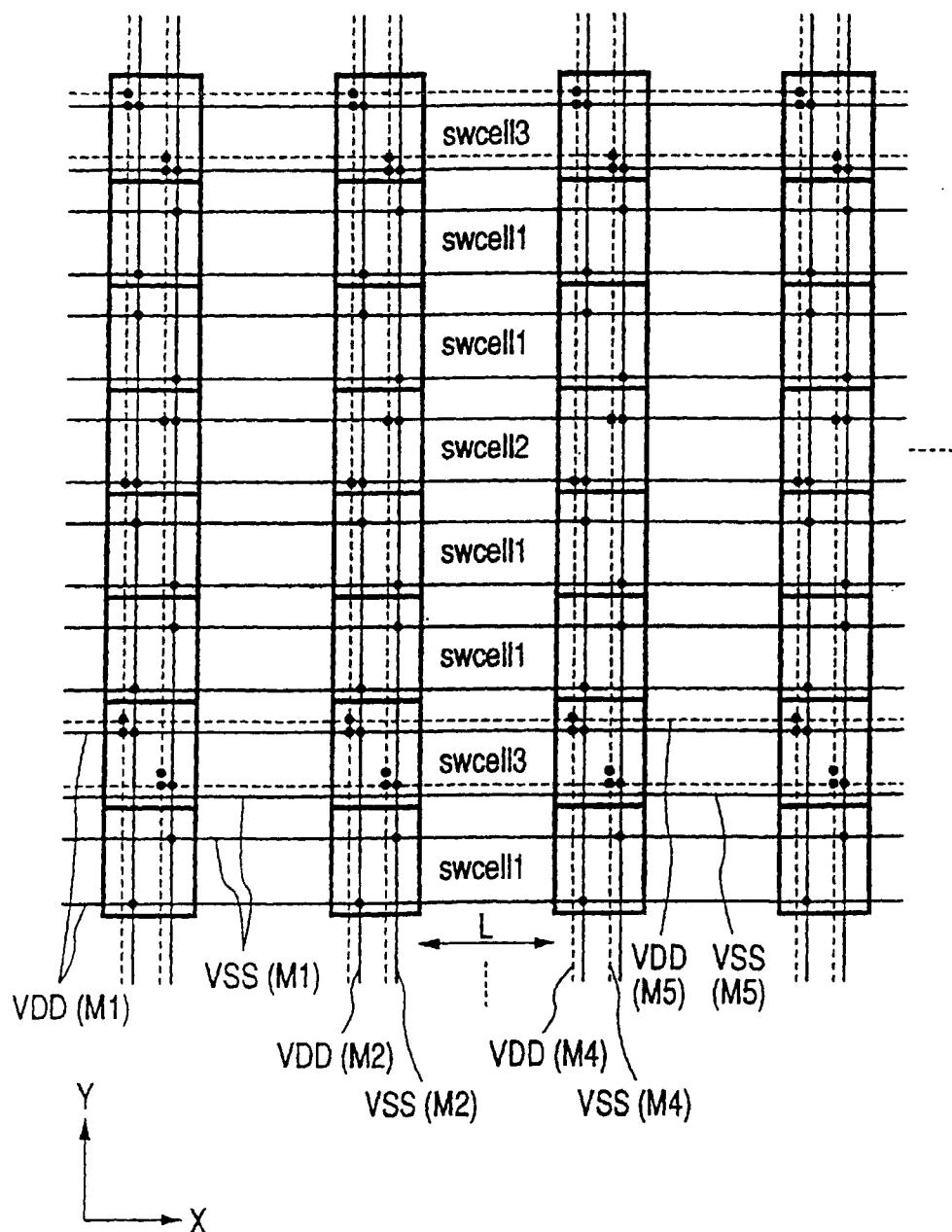

[0148] [Fig. 22](#) zeigt die Art, in der die Stromquellen VDD und VSS verstärkt sind. Die Stromquellenleitungen VDD und VSS mit der vierten und fünften Metallverdrahtungsschicht (M4 und M5) sind wie ein Gitter bei der Wiederholungsbasisseinheit nach [Fig. 21](#) verdrahtet.

[0149] Über VDD und VSS mit M2, die in der vertikalen Richtung (Y) verdrahtet sind, sind sowohl VDD als auch VSS verdrahtet mit M4. Und um VDD und VSS miteinander zu verbinden, benötigt man die dritte Metallverdrahtungsschicht (M3). Wenn VDD und VSS bei jeder swcell verbunden werden, so wird M3 vertikal verdrahtet. Dies führt zu dem Problem, dass

kein M3-Pfad in der horizontalen Richtung (X) gebildet wird.

[0150] In [Fig. 22](#) sind die M2- und M4-Stromleitungen bei jeder dritten swcell verbunden, dargestellt als swcell2 oder swcell3. Bei dieser Verbindung können die M3-Verdrahtungspfade in der horizontalen Richtung (X) sichergestellt werden.

[0151] Die M5-Stromleitung wird nur alle sechs swcells verdrahtet, dargestellt als swcell3. Die M5-Stromleitung ist damit mit der M4-Leitung bei jedem swcell3 verbunden, die einen Schnittpunkt von M5 und M4 darstellt.

[0152] Wie oben beschrieben, werden die Stromquellengitter mit kleinem Abstand bei M1 und M2 durch die Stromquellengitter mit großem Abstand bei M4 und M5 verstärkt, so dass dadurch die Impedanz jeder der VDD- und VSS-Stromquellenleitungen verringert wird.

[0153] Obgleich jeder der M4-Stromquellenleitungen in der vertikalen Richtung bei jeder swcell verdrahtet wird, kann die Leitung auch etwa alle zwei oder drei swcells verdrahtet werden. Obgleich die Impedanz von jeder der Stromquellenleitungen zunimmt, wird es mit diesem Verdrahtungsverfahren möglich, M4-Pfade in der vertikalen Richtung sicherzustellen.

[0154] [Fig. 23](#) zeigt die Beziehung zwischen swcells und Wannen, die, wie in [Fig. 22](#) gezeigt, angeordnet sind. P-Wannen und N-Wannen werden alternierend wie Bänder angeordnet, so dass sich zwei ncells eine Wanne miteinander teilen.

[0155] [Fig. 24](#) zeigt ein Layout sowohl der swcells der Speicherschaltung als auch der Stromquellenleitungen. In [Fig. 24](#) sind weder Wortnoch Bit-Leitungen eingetragen, aber Wortleitungen sind tatsächlich in der horizontalen Richtung (X) angeordnet, und Bit-Leitungen sind tatsächlich in der vertikalen Richtung (Y) angeordnet. Die Stromquellenleitungen der Speichermatte, die horizontal in den Speicherzellen verdrahtet sind, werden durch die Stromleitungen **200**, **201** und **202** verstärkt, die sich an beiden Enden davon befinden. Die Ziffer **203** bezeichnet eine Stromleitung für die Versorgung jedes Worttreibers und Decoders mit elektrischem Strom. **204** ist eine Stromleitung für die Versorgung jedes Sense-Verstärkers mit elektrischem Strom. Die Zellen swcell sind zu jeder der Stromleitungen **200** bis **204** in [Fig. 24](#) vorgesehen.

[0156] Üblicherweise sind nur einer oder zwei von mehreren Worttreibern und mehrere Wortdecoder gleichzeitig in Betrieb. Folglich wird nicht sehr viel Substrattrauschen erzeugt. Dies ist der Grund, warum nur zwei swcells an beiden Enden der Stromleitung

203 angeordnet sind, wie dies in [Fig. 24](#) gezeigt ist.

**[0157]** Dagegen können viele Sense-Verstärker gleichzeitig in Betrieb sein. Jedoch sind die Potentiale innerhalb der Sense-Verstärker so eingestellt, dass die Anzahl der Knoten, bei denen der Pegel von "L" auf "H" umgeschaltet wird, und die Anzahl der Knoten, bei denen der Pegel von "H" auf "L" umgeschaltet wird, in etwa gleich sind. Selbst wenn viele Sense-Verstärker gleichzeitig in Betrieb sind, wird folglich nicht sehr viel Substratraschen erzeugt. In diesem Fall werden swcells an anderen Positionen als an den beiden Enden der Stromleitung 204 in [Fig. 24](#) angeordnet, so dass dadurch das Substratraschen reduziert wird.

**[0158]** Es gibt viele weitere Verfahren, wie die swcells angeordnet werden können. Kurz gesagt ist es jedoch wichtig, dass viele weitere swcells in derselben Wanne angeordnet werden sollten, je nachdem, wie viele Vorrichtungen in derselben Wanne gleichzeitig in Betrieb gehen sollen. Es ist außerdem möglich, die Änderung einer Diffusionsschicht in einer Wanne durch  $|NH - NL|/NA$  zu evaluieren (wobei NH die Fläche der Diffusionsschichten außer bei der Diffusionsschicht in Verbindung mit einer Stromquelle ist, NH die Fläche einer Diffusion ist, deren Potential von "H" auf "L" gesetzt wird, NL die Fläche einer Diffusionsschicht ist, deren Potential von "L" auf "H" geändert wird), dann die Anzahl der swcells festzusetzen, die Abstände L der swcells und die Größe der MOS-Transistoren in einer swcell mit Bezug auf das Evaluierungsergebnis. Kurz gesagt muss man nur den Wert  $|NH - NL|/NA$  minimieren.

**[0159]** Bei einer Schaltung mit regelmäßigem Datenfluss wie bei einem Datenpfad ist es beispielsweise nur notwendig, so zu steuern, dass Daten in X-Richtung in [Fig. 22](#) auf dem Datenpfad fließen. Da die Zellen, die gleichzeitig betrieben werden, auf mehrere Wannen verteilt sind, wird der Wert oben  $|NH - NL|/NA$  reduziert.

**[0160]** [Fig. 25](#) zeigt einen Querschnitt einer Halbleiter-IC-Einheit gemäß der vorliegenden Erfindung. Wie in [Fig. 18](#) gezeigt sind die N, bezeichnet mit 302, 304, 306, 308 und 310, die gleichen wie eine N-Wanne zur Herstellung einer PMOS-Transistors. Die P, bezeichnet als 301, 303, 305, 307, 309 und 311 sind die gleichen wie eine P-Wanne zur Herstellung eines NMOS-Transistors. Die Tief-N, bezeichnet als 312 und 313, sind N-Wannen an tieferen Positionen als die N und die P. Die Halbleiter-IC-Einheit hat eine "Dreifachwannenstruktur".

**[0161]** Die Tief-N 312 und 313 sind elektrisch durch ein P-Substrat 310 und eine P-Wanne 307 voneinander getrennt. Folglich kann das Substratpotential der MOS-Transistoren A auf 302, 304, 306, 308 und 310 unabhängig von dem Substratpotential des

MOS-Transistors B auf 301, 303, 305, 307, 309 und 311 bestimmt werden und umgekehrt. Zusätzlich kann das Rauschen etc. auf Grund der MOS-Transistoren A unterdrückt werden, um so effektiv die MOS-Transistoren B vor Beeinflussung dadurch zu schützen.

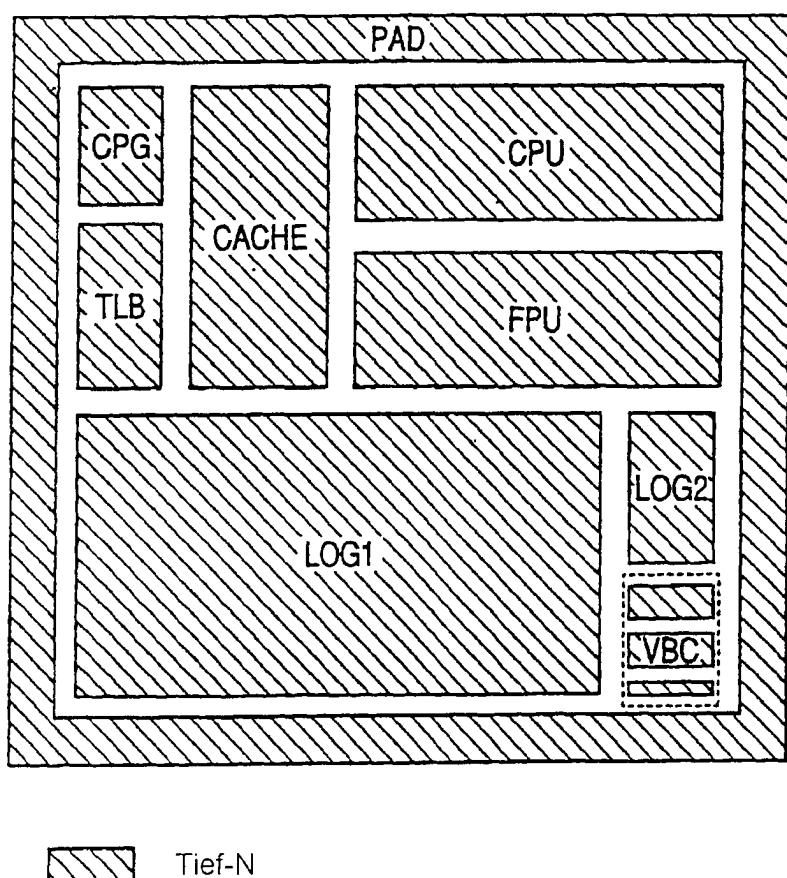

**[0162]** [Fig. 26](#) zeigt die Tief-N-Struktur der Halbleiter-IC-Einheit gemäß der vorliegenden Erfindung. CPG ist ein Takt-Controller und beinhaltet analoge Schaltungen, wie zum Beispiel einen PLL- (Phase Locked Loop) Regelkreis etc. TLB ist ein Adressenkonverter und CACHE ist ein Cache-Speicher. CPU ist eine zentrale Verarbeitungseinheit, FPU ist eine Fließpunkt-Arithmetikeinheit, LOG1 ist eine Schreib-Lese-Logik 1 (Random Logic 1), LOG2 ist eine Schreib-Lese-Logik 2 (Random Logic 2), und PAD ist eine I/O-Einheit. Jeder Schaltungsblock wird auf diese Art anders als andere auf einem Tief-N aufgebaut.

**[0163]** Wie in [Fig. 25](#) gezeigt ist es möglich, den Einfluss von Rauschen, das durch jeden Schaltungsblock ausgeübt wird und auf andere Blöcke Auswirkungen zeigt, zu reduzieren. Beispielsweise wird, da die PAD externe Pins mit größerer Amplitude als das interne Amplitudensignal treiben, mehr Rauschen erzeugt. Es kann verhindert werden, dass sich dieses Rauschen auf analoge Schaltungen wie CPG etc. auswirkt.