(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4538830号

(P4538830)

(45) 発行日 平成22年9月8日(2010.9.8)

(24) 登録日 平成22年7月2日(2010.7.2)

(51) Int.Cl.

F 1

|               |           |              |      |

|---------------|-----------|--------------|------|

| HO 1 L 25/065 | (2006.01) | HO 1 L 25/08 | Z    |

| HO 1 L 25/07  | (2006.01) | HO 1 L 23/12 | 501W |

| HO 1 L 25/18  | (2006.01) |              |      |

| HO 1 L 23/12  | (2006.01) |              |      |

請求項の数 8 (全 21 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2004-98440 (P2004-98440)    |

| (22) 出願日  | 平成16年3月30日 (2004.3.30)        |

| (65) 公開番号 | 特開2005-286126 (P2005-286126A) |

| (43) 公開日  | 平成17年10月13日 (2005.10.13)      |

| 審査請求日     | 平成19年3月29日 (2007.3.29)        |

|           |                                                      |

|-----------|------------------------------------------------------|

| (73) 特許権者 | 302062931<br>ルネサスエレクトロニクス株式会社<br>神奈川県川崎市中原区下沼部1753番地 |

| (74) 代理人  | 100080001<br>弁理士 筒井 大和                               |

| (72) 発明者  | 黒田 宏<br>東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内             |

| (72) 発明者  | 阪本 慶成<br>東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内            |

| (72) 発明者  | 菊池 隆文<br>東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内            |

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

互いに対向する一対の第1辺と、互いに対向し、かつ前記第1辺と交差する方向に延在する一対の第2辺とを有する四角形の平面形状から成り、前記第1辺のみに沿って設けられた複数のフリップチップ用電極、前記第2辺のみに沿って設けられた複数のワイヤ接続用電極、および前記複数のフリップチップ用電極と前記複数のワイヤ接続用電極とをそれぞれ電気的に接続する複数の共通配線が形成された主面と、前記主面と反対側の裏面とを有する配線基板と、

互いに対向する一対の第1チップ辺と、互いに対向し、かつ前記第1チップ辺と交差する方向に延在する一対の第2チップ辺とを有する四角形の平面形状から成り、複数の第1パッドが前記第1チップ辺のみに沿って形成された第1チップ主面と、前記第1チップ主面と反対側の第1チップ裏面とを有し、前記第1チップ主面が前記配線基板の主面と対向し、かつ前記第1チップ辺が前記配線基板の第1辺と並ぶように前記配線基板の主面上に搭載された第1半導体チップと、

前記第1半導体チップと同種であり、互いに対向する一対の第3チップ辺と、互いに対向し、かつ前記第3チップ辺と交差する方向に延在する一対の第4チップ辺とを有する四角形の平面形状から成り、複数の第2パッドが前記第3チップ辺のみに沿って形成された第2チップ主面と、前記第2チップ主面と反対側の第2チップ裏面とを有し、前記第2チップ裏面が前記第1半導体チップの第1チップ裏面と対向し、前記第3チップ辺が前記配線基板の第2辺と並ぶように前記第1半導体チップ上に搭載された第2半導体チップと、

前記第1半導体チップの複数の第1パッドと前記配線基板の複数のフリップチップ用電極とをそれぞれ電気的に接続する複数のバンプと、

前記第2半導体チップの複数の第2パッドと前記配線基板の複数のワイヤ接続用電極とをそれぞれ電気的に接続する複数のワイヤと、

前記第1半導体チップ、前記第2半導体チップ、および前記複数のワイヤを封止する封止体と、

前記配線基板の裏面に設けられた複数の外部端子と、を含み、

前記第1半導体チップおよび前記第2半導体チップは、それぞれメモリ回路を有しており、

前記第2半導体チップは、前記第1半導体チップと並列動作し、

10

前記複数の第2パッドの配列順は、前記複数の第1パッドの配列順と同じであることを特徴とする半導体装置。

#### 【請求項2】

請求項1記載の半導体装置において、前記第2半導体チップのサイズは、前記第1半導体チップのサイズと同じであることを特徴とする半導体装置。

#### 【請求項3】

請求項1記載の半導体装置において、四角形の平面形状から成り、複数の第3パッドが各辺に沿って形成された第3チップ正面と、前記第3チップ正面と反対側の第3チップ裏面とを有し、前記第3チップ裏面が前記第2半導体チップの第2チップ正面と対向するよう前記第2半導体チップの第2チップ正面に搭載された第3半導体チップを含むことを特徴とする半導体装置。

20

#### 【請求項4】

請求項3記載の半導体装置において、前記第3半導体チップのサイズは、前記第1半導体チップおよび前記第2半導体チップのそれぞれのサイズよりも小さいことを特徴とする半導体装置。

#### 【請求項5】

請求項3記載の半導体装置において、前記第3半導体チップは、演算処理機能を有していることを特徴とする半導体装置。

#### 【請求項6】

請求項3記載の半導体装置において、前記第3半導体チップの複数の第3パッドは、前記配線基板の各辺に沿って設けられた複数の第3半導体チップ用電極と複数のワイヤを介してそれぞれ電気的に接続されていることを特徴とする半導体装置。

30

#### 【請求項7】

請求項6記載の半導体装置において、前記配線基板の複数の第3半導体チップ用電極は、前記複数のフリップチップ用電極および前記複数のワイヤ接続用電極のそれより前記配線基板の各辺に近い位置に設けられていることを特徴とする半導体装置。

#### 【請求項8】

請求項6記載の半導体装置において、前記第3半導体チップ用電極は、前記フリップチップ用電極および前記ワイヤ接続用電極のそれと前記共通配線を介して電気的に接続されていることを特徴とする半導体装置。

40

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、半導体装置に関し、特に、複数の半導体チップを有した半導体装置に適用して有効な技術に関する。

##### 【背景技術】

##### 【0002】

従来の複数の半導体チップを有した半導体装置（マルチチップモジュール）では、そのパッケージ基板の主面上に実装された3個のチップのうち、DRAM（Dynamic Random Access Memory）が形成されたチップおよびフラッシュメモリが形成されたチップは、それ

50

それ A u バンプを介してパッケージ基板の配線と電気的に接続されており、さらに 2 個のチップの上には高速マイクロプロセッサが形成されたチップが実装され、このチップは A u ワイヤを介してパッケージ基板のボンディングパッドと電気的に接続されている（例えば、特許文献 1 参照）。

#### 【 0 0 0 3 】

また、従来の複数の半導体メモリチップを相互接続基板上に含むメモリモジュールでは、1 つのチップの出力接続部がスタック内のそのすぐ下にあるチップを超えたところにくるように交差された互いに積層された 2 つ以上のチップを含んでいる（例えば、特許文献 2 参照）。

【特許文献 1】国際公開番号 WO 02/103793 A1 号公報（図 2）

10

【特許文献 2】特開平 5 - 121643 号公報（図 1）

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【 0 0 0 4 】

複数の半導体チップを有する半導体装置の一例として、演算処理機能を有する半導体チップ（以降、マイコンチップという）と、メモリ回路を有する半導体チップ（以降、メモリチップという）とが配線基板上に搭載された S I P (System In Package) と呼ばれる半導体装置が知られている。

#### 【 0 0 0 5 】

近年、顧客からの要求により、大量のデータを処理するために半導体装置のメモリの大容量化が必要になり、加えてこの半導体装置を小型の電子機器に搭載するため、半導体装置の小型化も必要とされている。

20

#### 【 0 0 0 6 】

なお、メモリを大容量化するにあたり、1 チップで大容量にすると、チップサイズが大きくなり、その結果、配線基板も大きくなつて半導体装置の小型化が図れないことが問題となる。

#### 【 0 0 0 7 】

そこで、本発明者は、メモリの大容量化と半導体装置の小型化の両方を図る上で、同種メモリの積層（スタック）構造を検討した。

#### 【 0 0 0 8 】

30

なお、メモリチップを配線基板上に積層する構造は、前記特許文献 2 に記載されているが、配線基板の配線レイアウトについては前記特許文献 2 には全く記載されていない。

#### 【 0 0 0 9 】

本発明の目的は、メモリの大容量化と装置本体の小型化を実現することができる半導体装置を提供することにある。

#### 【 0 0 1 0 】

また、本発明の他の目的は、メモリの大容量化を図りつつ高速処理を行うことができる半導体装置を提供することにある。

#### 【 0 0 1 1 】

さらに、本発明の他の目的は、配線基板における配線レイアウトの容易化を図ることができる半導体装置を提供することにある。

40

#### 【 0 0 1 2 】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

#### 【課題を解決するための手段】

#### 【 0 0 1 3 】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、以下のとおりである。

#### 【 0 0 1 4 】

すなわち、本発明は、互いに対向する一対の第 1 辺と、互いに対向し、かつ前記第 1 边

50

と交差する方向に延在する一対の第2辺とを有する四角形の平面形状から成り、前記第1辺のみに沿って設けられた複数のフリップチップ用電極、前記第2辺のみに沿って設けられた複数のワイヤ接続用電極、および前記複数のフリップチップ用電極と前記複数のワイヤ接続用電極とをそれぞれ電気的に接続する複数の共通配線が形成された主面と、前記主面と反対側の裏面とを有する配線基板と、互いに対向する一対の第1チップ辺と、互いに対向し、かつ前記第1チップ辺と交差する方向に延在する一対の第2チップ辺とを有する四角形の平面形状から成り、複数の第1パッドが前記第1チップ辺のみに沿って形成された第1チップ主面と、前記第1チップ主面と反対側の第1チップ裏面とを有し、前記第1チップ主面が前記配線基板の主面と対向し、かつ前記第1チップ辺が前記配線基板の第1辺と並ぶように前記配線基板の主面上に搭載された第1半導体チップと、前記第1半導体チップと同種であり、互いに対向する一対の第3チップ辺と、互いに対向し、かつ前記第3チップ辺と交差する方向に延在する一対の第4チップ辺とを有する四角形の平面形状から成り、複数の第2パッドが前記第3チップ辺のみに沿って形成された第2チップ主面と、前記第2チップ主面と反対側の第2チップ裏面とを有し、前記第2チップ裏面が前記第1半導体チップの第1チップ裏面と対向し、前記第3チップ辺が前記配線基板の第2辺と並ぶように前記第1半導体チップ上に搭載された第2半導体チップと、前記第1半導体チップの複数の第1パッドと前記配線基板の複数のフリップチップ用電極とをそれぞれ電気的に接続する複数のバンプと、前記第2半導体チップの複数の第2パッドと前記配線基板の複数のワイヤ接続用電極とをそれぞれ電気的に接続する複数のワイヤと、前記第1半導体チップ、前記第2半導体チップ、および前記複数のワイヤを封止する封止体と、前記配線基板の裏面に設けられた複数の外部端子と、を含み、前記第1半導体チップおよび前記第2半導体チップは、それぞれメモリ回路を有しており、前記第2半導体チップは、前記第1半導体チップと並列動作し、前記複数の第2パッドの配列順は、前記複数の第1パッドの配列順と同じである。

**【発明の効果】**

**【0017】**

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば、以下のとおりである。

**【0018】**

配線基板上にフリップチップ接続された第1の半導体チップと、第1の半導体チップと同種でありかつ第1の半導体チップ上にフェイスアップ実装された第2の半導体チップを有しており、配線基板に、第1の半導体チップの複数の第1電極と、これらの第1電極に対応する第2の半導体チップの複数の第2電極とをそれぞれ接続する複数の共通配線が形成されており、さらに第1の半導体チップは、複数の第1電極の列に沿って形成された第1の辺とそれ以外の他の辺とを有し、一方、第2の半導体チップは、複数の第2電極が第1の半導体チップの他の辺に沿って配列されるように第1の半導体チップ上に積み重ねられていることにより、第1の半導体チップ上に同種の第2の半導体チップが向きを変えて積層されるため、配線基板上で共通配線を引き回す際に各共通配線をクロスさせることなく引き回すことが可能になる。その結果、配線基板の配線層の数の増加を抑えて共通配線を引き回すことができ、配線基板の薄型化を図ることができるとともに、コスト上昇を抑えることができる。さらに、第1の半導体チップ上に同種の第2の半導体チップが向きを変えて積層されるため、配線基板においてフリップチップ接続用の電極とワイヤ接続用の電極とを異なった領域に分散させて配置することができ、配線基板上で各電極を効率良く配置することができる。したがって、配線基板の小型化を図ることができ、両チップがメモリ回路を有している場合には、メモリの大容量化と半導体装置の小型化の両者を実現することができる。

**【発明を実施するための最良の形態】**

**【0019】**

以下の実施の形態では特に必要なとき以外は同一または同様な部分の説明を原則として繰り返さない。

10

20

30

40

50

## 【0020】

さらに、以下の実施の形態では便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらはお互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明などの関係にある。

## 【0021】

また、以下の実施の形態において、要素の数など（個数、数値、量、範囲などを含む）に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合などを除き、その特定の数に限定されるものではなく、特定の数以上でも以下でも良いものとする。

10

## 【0022】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の機能を有する部材には同一の符号を付し、その繰り返しの説明は省略する。

## 【0023】

## （実施の形態）

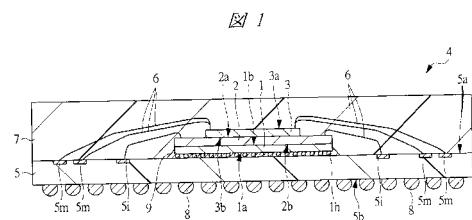

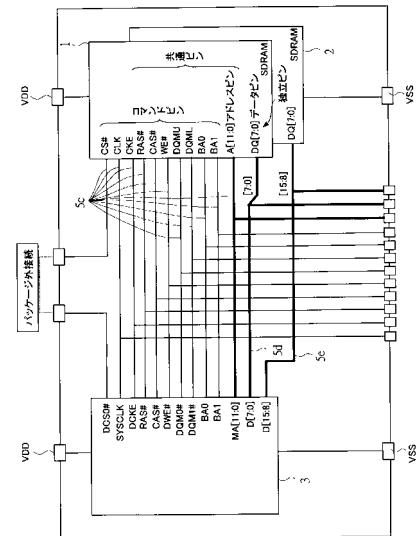

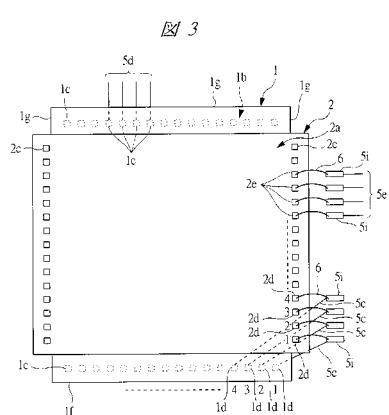

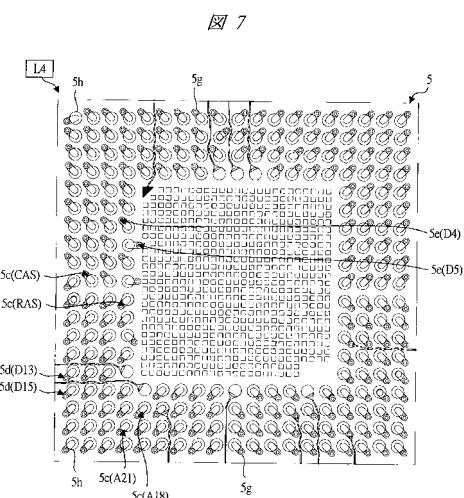

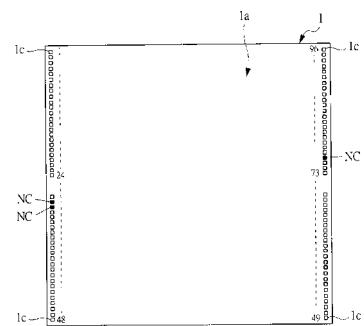

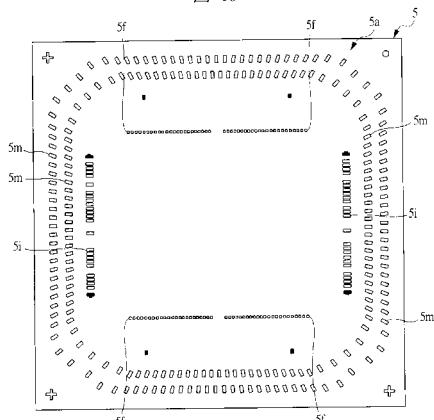

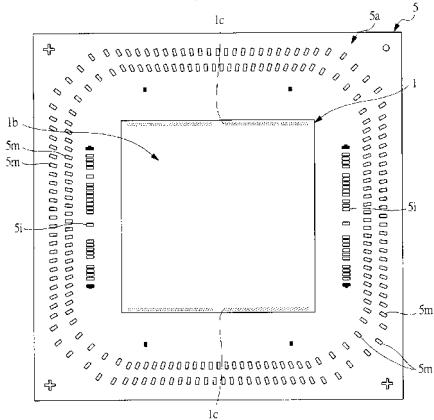

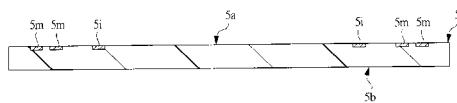

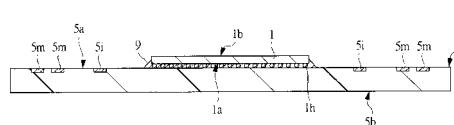

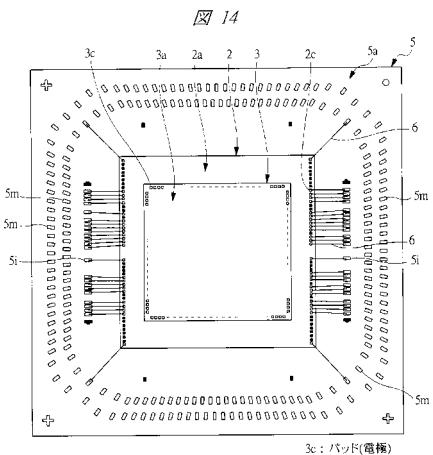

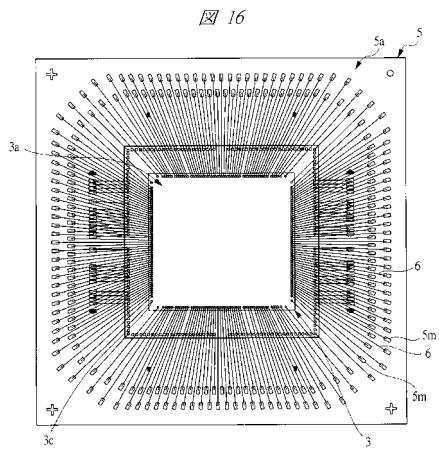

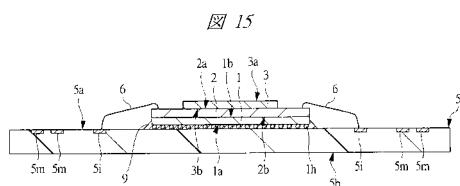

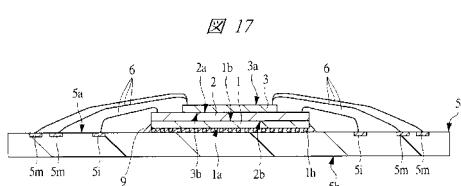

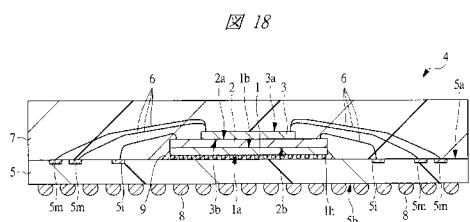

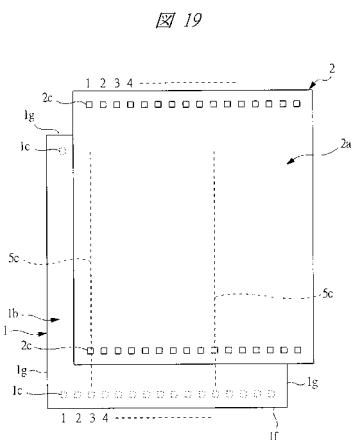

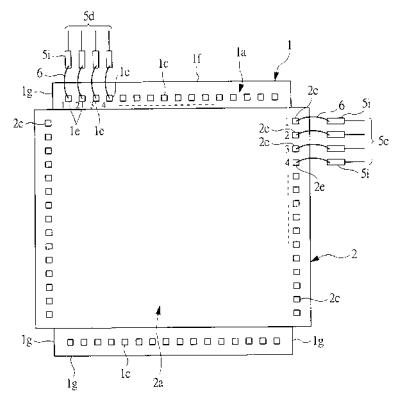

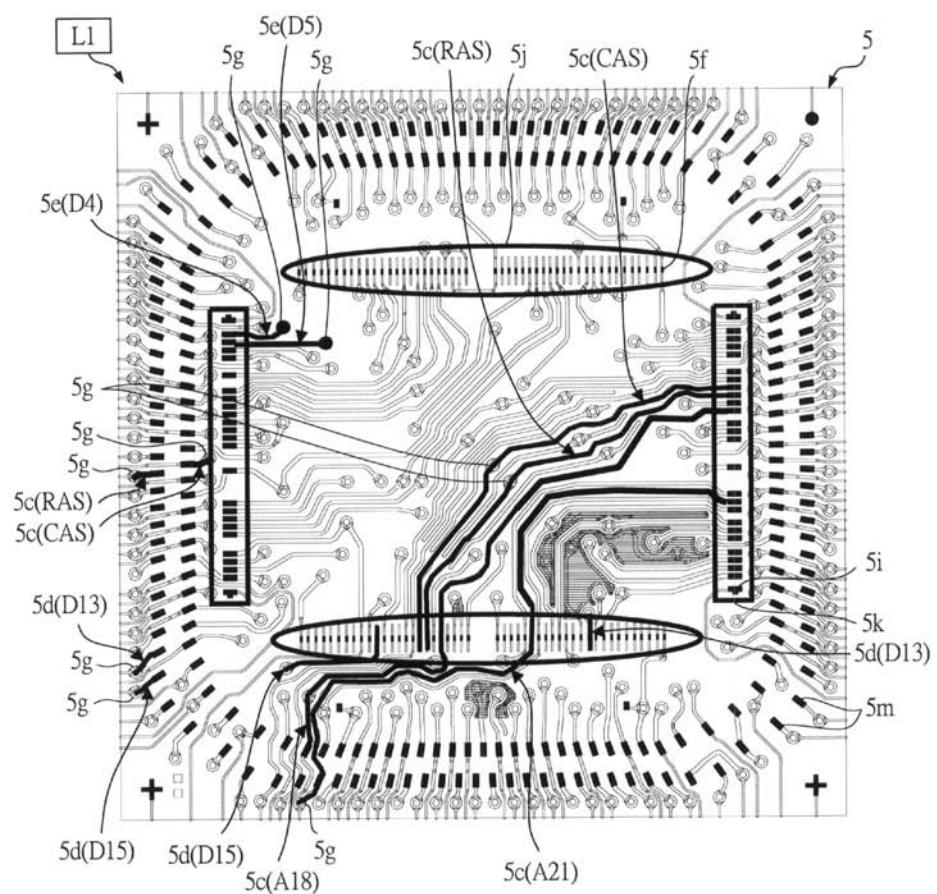

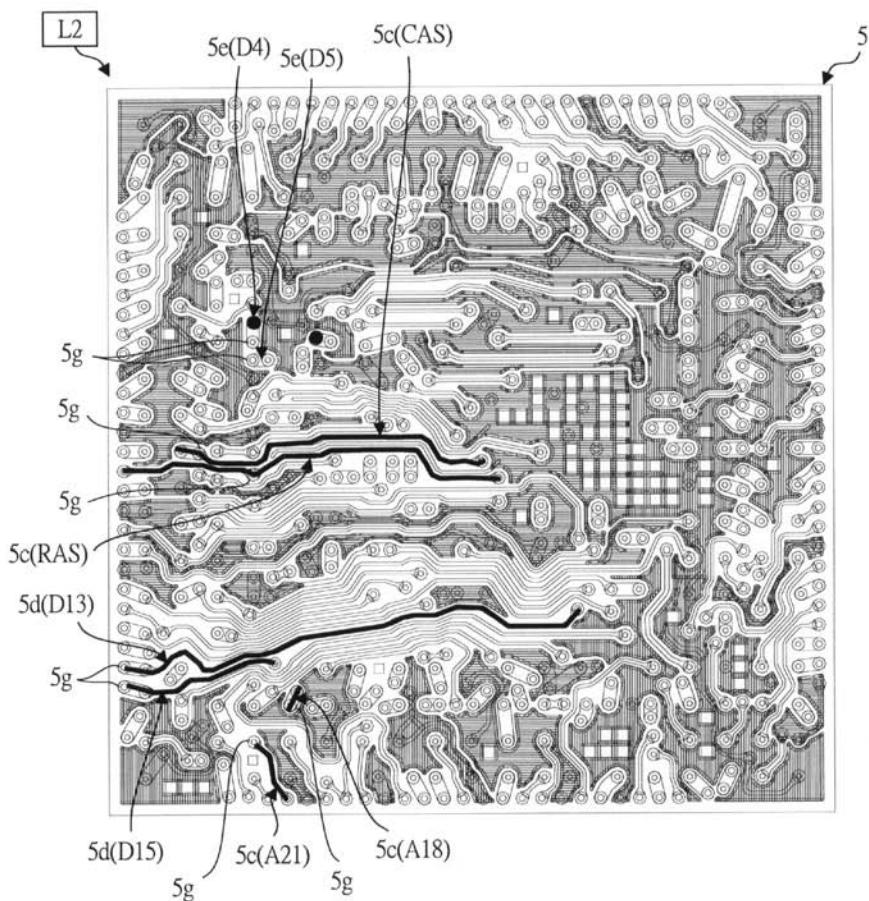

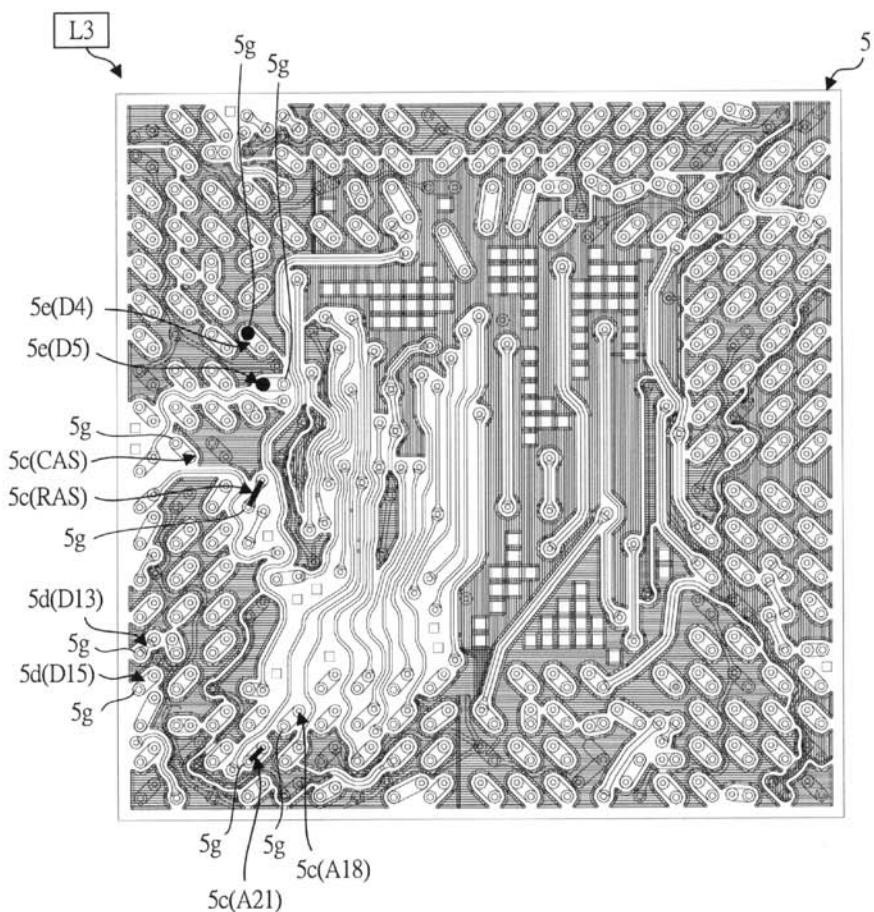

図1は本発明の実施の形態の半導体装置の構造の一例を示す断面図、図2は図1に示す半導体装置のシステムの一例を示すブロック構成図、図3は図1に示す半導体装置に搭載される第1の半導体チップと第2の半導体チップの実装方向の一例を示す平面図、図4は図1に示す半導体装置に組み込まれる配線基板の最上配線層（L1）の配線パターンの一例を示す平面図、図5は図1に示す半導体装置に組み込まれる配線基板の上から2層めの配線層（L2）の配線パターンの一例を示す平面図、図6は図1に示す半導体装置に組み込まれる配線基板の上から3層めの配線層（L3）の配線パターンの一例を示す平面図、図7は図1に示す半導体装置に組み込まれる配線基板の上から4層めの配線層（L4）の配線パターンの一例を示す平面図、図8は図1に示す半導体装置の組み立て手順の一例を示す製造フロー図、図9は図1に示す半導体装置に搭載される第1の半導体チップの構造の一例を示す平面図、図10は図1に示す半導体装置に組み込まれる配線基板の構造の一例を示す平面図、図11は図10に示す配線基板の断面図、図12は図8に示す組み立てにおけるフリップチップ接続完了時の構造の一例を示す平面図、図13は図12に示すフリップチップ接続完了時の構造の断面図、図14は図8に示す組み立てにおける第2の半導体チップのワイヤボンディング完了時の構造の一例を示す平面図、図15は図14に示す第2の半導体チップのワイヤボンディング完了時の構造の断面図、図16は図8に示す組み立てにおける第3の半導体チップのワイヤボンディング完了時の構造の一例を示す平面図、図17は図16に示す第3の半導体チップのワイヤボンディング完了時の構造の断面図、図18は図8に示す組み立てにおける組み立て完了時の構造の一例を示す断面図、図19は本発明の実施の形態の変形例の第1の半導体チップと第2の半導体チップの実装方向を示す平面図、図20は本発明の実施の形態の他の変形例の第1の半導体チップと第2の半導体チップの実装状態を示す平面図である。

20

30

## 【0024】

図1に示す本実施の形態の半導体装置は、複数の同種の半導体チップと、これらのチップを制御し、かつ演算処理機能を備えた半導体チップ（CPU（Central Processing Unit））とを有する半導体パッケージであり、本実施の形態では、前記半導体装置の一例として、2つの同種のメモリチップ（第1の半導体チップと第2の半導体チップ）と、これらを制御するマイコンチップ（第3の半導体チップ）3とが組み込まれたSIP（System In Package）4を取り上げて説明する。

40

## 【0025】

すなわち、SIP4は、同種のメモリチップを複数有していることにより、メモリの大容量化を図ることが可能なものであり、さらに、組み込まれる複数の半導体チップを積層してパッケージ本体の小型化を図るものである。

## 【0026】

50

なお、本実施の形態では、SIP 4 に搭載された 2 つのメモリチップが、それぞれメモリ回路を有する同種のDRAM (Dynamic Random Access Memory) の場合を説明する。図 1 に示すように、SIP 4 では、配線基板上に、まず第 1 の半導体チップである第 1 のDRAM 1 がフェイスダウン実装で配置され、かつ配線基板とフリップチップ接続によって電気的に接続されており、また、この第 1 のDRAM 1 上に第 2 の半導体チップである第 2 のDRAM 2 がフェイスアップ実装で積層されている。さらに、第 2 のDRAM 2 上に第 3 の半導体チップであるマイコンチップ 3 がフェイスアップ実装で積層されている。

【0027】

したがって、第 2 のDRAM 2 とマイコンチップ 3 は、それぞれワイヤ接続によって配線基板と電気的に接続されている。

10

【0028】

なお、第 1 のDRAM 1 と第 2 のDRAM 2 は、同種のチップであるため、相互の大きさ、パッド配列、パッド数およびピン機能などは全く同じである。

【0029】

また、配線基板の正面 5a に対するその反対側の裏面 5b には、外部端子である複数のボール電極 8 がマトリクス配置で設けられているとともに、正面 5a 側には 3 つの半導体チップおよび複数のワイヤ 6 を樹脂封止する封止体 7 が形成されている。

【0030】

つまり、SIP 4 は、BGA (Ball Grid Array) 型の半導体装置である。

【0031】

図 1 に示す SIP 4 の詳細構造について説明すると、正面 5a とその反対側の裏面 5b とを有した配線基板であるパッケージ基板 5 と、その正面 1a に半導体素子および複数のパッド (電極) 1c を有しており、かつ正面 1a がパッケージ基板 5 の正面 5a と対向して配置されているとともに、フリップチップ接続によってパッケージ基板 5 と電気的に接続された第 1 の半導体チップである第 1 のDRAM 1 と、第 1 のDRAM 1 と同種のチップであるとともに、正面 2a に半導体素子および複数のパッド (電極) 2c を有しており、かつ第 1 のDRAM 1 上に正面 2a を上方に向けて積み重ねて配置され、さらにパッケージ基板 5 と導電性のワイヤ 6 によって電気的に接続された第 2 の半導体チップである第 2 のDRAM 2 と、第 2 のDRAM 2 上に積み重ねて配置されているとともに、演算処理機能を有し、かつパッケージ基板 5 と導電性のワイヤ 6 によって電気的に接続された第 3 の半導体チップであるマイコンチップ 3 と、3 つの半導体チップおよび複数のワイヤ 6 を樹脂封止する封止体 7 と、パッケージ基板 5 の裏面 5b に設けられた外部端子である複数のボール電極 8 とからなる。

20

30

【0032】

さらに、パッケージ基板 5 には、図 3 に示すように、第 1 のDRAM 1 のパッド 1c のうちの複数の第 1 電極 1d とこれらの第 1 電極 1d にそれぞれ対応する第 2 のDRAM 2 の複数の第 2 電極 2d とをそれぞれ電気的に接続する複数の共通配線 5c が形成されている。

【0033】

また、パッケージ基板 5 には、第 1 のDRAM 1 のパッド 1c のうちの共通配線 5c と接続しない複数の第 3 電極 1e にそれぞれ接続しており、かつそれぞれ対応するボール電極 8 と電気的に接続する複数の第 1 の独立配線 5d と、第 2 のDRAM 2 のパッド 2c のうちの共通配線 5c と接続しない複数の第 4 電極 2e にそれぞれ接続しており、かつそれぞれ対応するボール電極 8 と電気的に接続する複数の第 2 の独立配線 5e とが形成されている。

40

【0034】

また、第 1 のDRAM 1 は、共通配線 5c に接続する複数の第 1 電極 1d の列に沿って形成された第 1 の辺 1f とそれ以外の他の辺 1g とを有している。一方、第 2 のDRAM 2 は、共通配線 5c に接続する複数の第 2 電極 2d が第 1 のDRAM 1 の他の辺 1g に沿って配列されるように第 1 のDRAM 1 上に積み重ねられている。

50

## 【0035】

なお、共通配線 5 c、第1の独立配線 5 d および第2の独立配線 5 e は、それぞれに対応する図14に示すマイコンチップ3のパッド(電極)3cとそれぞれ電気的に接続されている。

## 【0036】

次に、本実施の形態のSIP4のシステム構成の一例を図2を用いて説明する。マイコンチップ3と第1のDRAM1、およびマイコンチップ3と第2のDRAM2とは、それぞれ電極ごとに共通配線5c、第1の独立配線5d、第2の独立配線5eで接続されている。共通配線5cによって接続されているのは、CS、CLC、CKE、RAS、CAS、WE、DQM、BAなどのコマンド信号用の電極、およびアドレス信号用の電極である。したがって、複数の共通配線5cが設けられている。

10

## 【0037】

また、第1の独立配線5dによって接続されているのは、マイコンチップ3と第1のDRAM1のデータ信号用の電極であり、さらに、第2の独立配線5eによって接続されているのは、マイコンチップ3と第2のDRAM2のデータ信号用の電極であり、第1の独立配線5dおよび第2の独立配線5eともそれぞれ複数設けられている。

## 【0038】

すなわち、SIP4では、マイコンチップ3と2つのメモリチップそれぞれの間で、データ信号用の配線が別々に複数独立して設けられており、データバスを分割した配線構造となっている。その際、アドレス信号は、共通配線5cを介して第1のDRAM1と第2のDRAM2に入るよう接続されているため、第1のDRAM1と第2のDRAM2それぞれのアドレスにデータ読み出しの信号が入ると、第1のDRAM1と第2のDRAM2は、それぞれの対応するマイコンチップ3の電極に対して一斉にデータを出力する。

20

## 【0039】

例えば、第1のDRAM1より割り当てられたデータ線DQ0～7および第2のDRAM2より割り当てられたデータ線DQ8～15は、それぞれ独立してマイコンチップ3とデータのやり取りを行うことができる。つまり、SIP4では、2つのメモリチップを並列動作させることができる。これにより、各メモリチップにおけるデータ転送時の負担を軽減することができる。

## 【0040】

30

したがって、SIP4では、データ転送の高速化を図ることができる。

## 【0041】

さらに、2つの同種のメモリチップ(第1のDRAM1と第2のDRAM2)を有しているため、メモリの大容量化を図ることができる。また、さらに容量が大きい大容量チップに置き換える際にも、ピン配置を変更することなく大容量のメモリチップを搭載することが可能である。

## 【0042】

次に、本実施の形態のSIP4において、図2に示すシステムを構造として小型化して実現するための特徴について説明する。

## 【0043】

40

まず、SIP4に搭載された同種の2つのメモリチップである第1のDRAM1および第2のDRAM2は、それぞれ正面1a, 2aの対向する2辺にパッド1c, 2cが設けられている(図3参照)。さらに、第1のDRAM1は、金バンプ1hを介してフリップチップ接続でパッケージ基板5と電気的に接続しており、これによって、図4に示すように、フリップチップ用電極群5jを第1のDRAM1のチップ領域内に配置することができる。

## 【0044】

また、第2のDRAM2は、第1のDRAM1の裏面1b上に、その正面2aを上方に向けてフェイスアップ実装で積層されている。したがって、第1のDRAM1の裏面1bと第2のDRAM2の裏面2bとが接着材などによって接続されており、第2のDRAM

50

2は、フェイスアップ実装であるため、パッケージ基板5とワイヤ接続によって電気的に接続されている。

【0045】

なお、SIP4では、第2のDRAM2は、図3に示すように、複数の第2電極2dが第1のDRAM1の他の辺1gに沿って配列されるように第1のDRAM1上に積み重ねられている。例えば、図3に示すように、第1のDRAM1に対して、第2のDRAM2が、そのパッド2cの配列方向が90°向きが変わるように配置されている。すなわち、フェイスタウン実装された第1のDRAM1に対して、第1のDRAM1上にフェイスアップ実装される第2のDRAM2が、第1のDRAM1のパッド1cの配列方向に対して、第2のDRAM2のパッド2cの配列方向が90°向きが変わるように第1のDRAM1上に積層されている。10

【0046】

これにより、第1のDRAM1上に同種の第2のDRAM2が向きを変えて積層されるため、パッケージ基板5上で共通配線5cを引き回す際に、図3に示すように、各共通配線5cをクロスさせることなく引き回すことが可能になる。

【0047】

その結果、パッケージ基板5における配線層の数の増加を抑えて共通配線5cを引き回すことができ、パッケージ基板5の薄型化を図ることができるとともに、コスト上昇を抑えることができる。

【0048】

さらに、第1のDRAM1上に同種の第2のDRAM2が向きを変えて積層されるため、パッケージ基板5の表層において、図4に示すように、複数のフリップチップ用電極5fと複数のワイヤ接続用電極5iとを異なった領域に分散させて配置することができ、パッケージ基板5の表層上で各電極や各配線を効率良く配置することができる。20

【0049】

その結果、パッケージ基板5の小型化を図ることができ、SIP4のメモリの大容量化とSIP4の小型化の両者を実現することができる。

【0050】

なお、パッケージ基板5は、例えば、樹脂材の基材と、銅合金などからなる複数の配線および電極、さらに表層配線を絶縁する絶縁膜などから構成され、複数の配線層を有した多層配線基板である。30

【0051】

また、図1に示すワイヤ6は、例えば、金線であり、さらに、ボール電極8は、例えば、半田などからなる。また、第1のDRAM1のフリップチップ接続部は、絶縁性の樹脂などからなるアンダーフィル封止部9によって保護されている。また、パッケージ基板5の正面5a上で複数のワイヤ6および3つの半導体チップを覆う封止体7は、例えば、熱硬化性のエポキシ樹脂などによって形成されるものである。

【0052】

次に、メモリの大容量化とパッケージ本体の小型化を図るSIP4のパッケージ基板5における各配線層の配線パターンの一例について説明する。図4、図5、図6および図7は、それぞれパッケージ基板5における正面5aの配線層である最上配線層(L1)、上から2層めの配線層(L2)、上から3層めの配線層(L3)、上から4層めの配線層(L4)の各配線パターンを示している。40

【0053】

図4に示す最上配線層(L1)には、第1のDRAM1とフリップチップ接続を行うための複数のフリップチップ用電極5fが対向して2列に設けられており、さらに、第2のDRAM2とワイヤ接続を行うための複数のワイヤ接続用電極5iが、フリップチップ用電極群5jと向きを90°変えた状態で対向して2列に設けられ、ワイヤ接続用電極群5kを形成している。

【0054】

したがって、対向する2列のフリップチップ用電極群5jと、これと90°向きを変えて対向する2列のワイヤ接続用電極群5kとが、ほぼ四角形を成しており、これらフリップチップ用電極群5jとワイヤ接続用電極群5kの周囲に、マイコンチップ3とワイヤボンディングを行うためのマイコン用ワイヤ接続用電極5mが、ほぼ全周に亘って2列で設けられている。

【0055】

さらに、それぞれに第1のDRAM用のフリップチップ用電極5fと第2のDRAM用のワイヤ接続用電極5iとを接続する複数の共通配線5cと、それに第1のDRAM1のフリップチップ用電極5fと接続する複数の第1の独立配線5dと、それに第2のDRAM2のワイヤ接続用電極5iと接続する複数の第2の独立配線5eとが設けられている。

10

【0056】

ここで、一例を挙げて、パッケージ基板5の各配線層における共通配線5cと第1の独立配線5dと第2の独立配線5eの配線の引き回しについて説明する。

【0057】

まず、図4に示すように、第1のDRAM1のフリップチップ用電極5fとそれぞれ接続する2つの共通配線5c（例えば、CAS用、RAS用）は、フリップチップ用電極群5jの内側で引き回されてそれぞれ同種の第2のDRAM2のワイヤ接続用電極5iと接続されている。同様に、アドレス用の2つの共通配線5c（A18、A21）もフリップチップ用電極群5jの内側で引き回されてそれぞれ同種の第2のDRAM2のワイヤ接続用電極5iと接続されている。

20

【0058】

さらに、CAS用とRAS用の共通配線5cは、それぞれスルーホール配線5gを介して図5に示す2層めの配線層（L2）の共通配線5cを経由して表層配線層（L1）のマイコン用ワイヤ接続用電極5mと接続しており、また、アドレス用の2つの共通配線5cは、それぞれ表層配線層（L1）の引き回しによってマイコン用ワイヤ接続用電極5mと接続しており、これらにより、それぞれ対応するマイコンチップ3のパッド3cと接続可能となっている。

【0059】

一方、図4に示す第1のDRAM用のフリップチップ用電極5fと接続する2つの第1の独立配線5d（例えば、データ線のD13、D15）と、第2のDRAM用のワイヤ接続用電極5iと接続する2つの第2の独立配線5e（例えば、データ線のD4、D5）は、それぞれスルーホール配線5gを介して図5に示す2層めの配線層（L2）の配線を経由して表層配線層（L1）のマイコン用ワイヤ接続用電極5mと接続しており、それに対応するマイコンチップ3のパッド3cと接続可能となっている。

30

【0060】

それぞれの共通配線5c、第1の独立配線5dおよび第2の独立配線5eは、図5に示す2層めの配線層（L2）および図6に示す3層めの配線層（L3）においてそれぞれスルーホール配線5gを介してさらに下層の配線に接続され、図7に示す4層めの配線層（L4）でスルーホール配線5gを経由してそれぞれ対応するバンブランド5hに接続されている。

40

【0061】

その結果、複数の共通配線5c、複数の第1の独立配線5dおよび複数の第2の独立配線5eが、それぞれ対応するマイコンチップ3のパッド3cおよび外部端子であるボール電極8と接続される。

【0062】

このように本実施の形態のSIP4に組み込まれるパッケージ基板5では、フリップチップ接続とワイヤボンディングとを組み合わせ、かつフリップチップ接続の第1のDRAM1に対して、これに積層されるワイヤボンディングの第2のDRAM2を、そのパッド配列の向きを90°変えて配置したことにより、複数のフリップチップ用電極5fと複数

50

のワイヤ接続用電極 5 i を 90° 異なった位置の領域に分散させて配置することができる。したがって、第 1 の D R A M 1 と第 2 の D R A M 2 を接続する複数の共通配線 5 c を、パッケージ基板 5 の表層の配線層においてクロスさせずに引き回すことができ、パッケージ基板 5 における配線層の数の増加を抑制することができるとともに、パッケージ基板 5 の小型化を図ることができる。

【 0 0 6 3 】

さらに、配線層の数の増加を抑制することができるため、パッケージ基板 5 の薄型化を図ることができ、かつコスト増加を抑えることができる。

【 0 0 6 4 】

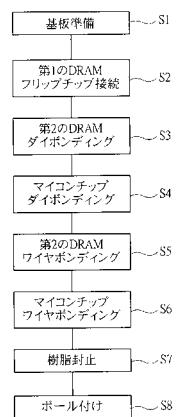

次に、本実施の形態の S I P 4 の組み立てを図 8 に示すフローに沿って説明する。

10

【 0 0 6 5 】

まず、図 8 のステップ S 1 に示す基板準備を行う。ここでは、図 4 ~ 図 7 に示す各配線層を有した配線基板である図 1 0 および図 1 1 に示すパッケージ基板 5 を準備する。なお、パッケージ基板 5 の正面 5 a には、第 1 の D R A M 1 の各パッド 1 c に対応した複数のフリップチップ用電極 5 f と、第 2 の D R A M 2 の各パッド 2 c に対応した複数のワイヤ接続用電極 5 i と、マイコンチップ 3 の各パッド 3 c に対応した複数のマイコン用ワイヤ接続用電極 5 m が設けられている。

【 0 0 6 6 】

一方、各パッド 1 c に金パンプ 1 h が設けられた図 9 に示す第 1 の半導体チップである第 1 の D R A M 1 を準備する。すなわち、第 1 の D R A M 1 は、メモリ回路を有したメモリチップである。

20

【 0 0 6 7 】

その後、ステップ S 2 に示す第 1 の D R A M フリップチップ接続を行う。その際、まず、パッケージ基板 5 の正面 5 a 上にペースト状の接着材を塗布し、その上に図 9 に示す第 1 の D R A M 1 をフェイスダウン実装で配置する。その後、図 1 2 および図 1 3 に示すように熱圧着によって第 1 の D R A M 1 をパッケージ基板 5 にフリップチップ接続する。

【 0 0 6 8 】

これにより、第 1 の D R A M 1 の各パッド 1 c が金パンプ 1 h を介してそれぞれに対応するパッケージ基板 5 の各フリップチップ用電極 5 f に電気的に接続するとともに、前記接着材が硬化して各フリップチップ接続部を保護するアンダーフィル封止部 9 が形成される。

30

【 0 0 6 9 】

その後、ステップ S 3 に示す第 2 の D R A M ダイボンディングを行う。ここでは、第 1 の D R A M 1 と同種の第 2 の D R A M 2 を、第 1 の D R A M 1 の裏面 1 b 上にフェイスアップ実装で積層し、第 1 の D R A M 1 の裏面 1 b と、第 2 の D R A M 2 の裏面 2 b とを接着材などで接続する。

【 0 0 7 0 】

その際、第 2 の D R A M 2 を、そのパッド配列の向きが第 1 の D R A M 1 のパッド配列に対して 90° 変わるように第 1 の D R A M 1 上に積層する。

【 0 0 7 1 】

40

その後、ステップ S 4 に示すマイコンチップダイボンディングを行う。ここでは、第 1 の D R A M 1 と第 2 の D R A M 2 を制御することができ、かつ演算処理機能を備えた第 3 の半導体チップであるマイコンチップ 3 を、その正面 3 a を上方に向けて第 2 の D R A M 2 の正面 2 a 上にフェイスアップ実装で積層し、図 1 5 に示すように第 2 の D R A M 2 の正面 2 a と、マイコンチップ 3 の裏面 3 b とを接着材などで接続する。

【 0 0 7 2 】

その後、ステップ S 5 に示す第 2 の D R A M ワイヤボンディングを行う。すなわち、図 1 4 および図 1 5 に示すように第 2 の D R A M 2 の各パッド 2 c と、これに対応するパッケージ基板 5 のワイヤ接続用電極 5 i とを金線などのワイヤ 6 で電気的に接続する。

【 0 0 7 3 】

50

続いて、ステップS6に示すマイコンチップワイヤボンディングを行う。すなわち、図16および図17に示すようにマイコンチップ3の各パッド3cと、これに対応するパッケージ基板5のマイコン用ワイヤ接続用電極5mとを金線などのワイヤ6で電気的に接続する。

【0074】

その後、ステップS7に示す樹脂封止を行う。ここでは、例えば、熱硬化性のエポキシ樹脂などを用いてパッケージ基板5の正面5a上を樹脂成形して図18に示す封止体7を形成し、3つの半導体チップと複数のワイヤ6を封止体7によって樹脂封止する。

【0075】

その後、ステップS8に示すボール付けを行う。ここでは、パッケージ基板5の裏面5bの各バンブランド5hに半田などで形成されたボール電極8をリフローなどで溶融して電気的に接続する。

【0076】

これによって、SIP4の組み立て完了となる。

【0077】

なお、多数個取り基板を用いて一括して複数のSIP4を形成する場合には、ボール付け工程の後、個片化のための切断を行って組み立て完了となる。

【0078】

次に、本実施の形態の変形例の半導体装置について説明する。

【0079】

図19に示す変形例は、フェイスダウン実装の第1のDRAM1上にこれと同種の第2のDRAM2をフェイスアップ実装で積層する際に、そのパッド配列の向きが第1のDRAM1のパッド配列に対して180°変わるように第1のDRAM1上に積層した場合である。

【0080】

この場合、パッケージ基板5の表層の配線層において共通配線5cを引き回す際に、隣り合ったフリップチップ用電極5f間に共通配線5cを通さなければならぬため、微細配線加工技術が必要となるが、表層の配線層において複数の共通配線5cをクロスさせずに引き回すことができるため、90°向きを変えた場合と同様の効果を得ることが可能である。

【0081】

また、図20に示す他の変形例は、2つの同種の半導体チップを積層する際に、データ線の分割（データバス分割）によってそれぞれの半導体チップに別々に独立した複数のデータ用の配線、すなわち複数の第1の独立配線5dと複数の第2の独立配線5eを接続するものであり、この場合に、フェイスアップ実装された第1のDRAM1上にこれと同種の第2のDRAM2を同じくフェイスアップ実装で積層する。その際、第2のDRAM2のパッド配列の向きが第1のDRAM1のパッド配列に対して90°変わるように第1のDRAM1上に積層する。さらに、両チップともフェイスアップ実装であるため、両チップともパッケージ基板5とワイヤ接続を行う。

【0082】

この場合、第2のDRAM2のパッド配列の方向が第1のDRAM1のパッド配列と90°方向が変わっているため、それぞれのチップにワイヤ6を介して接続する複数のワイヤ接続用電極5iの配列を90°異なった位置の領域に分散させて配置することができ、これにより、配線の引き回しのためのスペースを確保し易くすることができ、配線レイアウトの容易化を図ることができる。

【0083】

したがって、第1のDRAM1の複数のパッド1c（第3電極1e）とワイヤ6を介してそれぞれ接続する複数の第1の独立配線5dを、複数のワイヤ接続用電極5iより外側に配置することが可能となり、かつ第2のDRAM2のパッド2c（第4電極2e）とワイヤ6を介してそれぞれ接続する複数の第2の独立配線5eも、複数のワイヤ接続用電極

10

20

30

40

50

5 i より外側に配置することが可能となり、複数の第 1 の独立配線 5 d と複数の第 2 の独立配線 5 e を容易に引き回すことができる。

【 0 0 8 4 】

以上、本発明者によってなされた発明を発明の実施の形態に基づき具体的に説明したが、本発明は前記発明の実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることは言うまでもない。

【 0 0 8 5 】

例えば、前記実施の形態では、同種の半導体チップが D R A M として 2 つ積層されている場合を説明したが、半導体装置に組み込まれる同種の半導体チップの数は 2 つ以上であれば何個であってもよい。

10

【 0 0 8 6 】

また、前記実施の形態では、半導体装置が、外部端子としてボール電極 8 を有している場合を例に取り上げて説明したが、前記半導体装置は、配線基板と、その上に搭載される少なくとも 2 つ以上の同種の半導体チップとを有しているものであれば、前記外部端子はボール電極 8 以外のものであってもよく、例えば、前記半導体装置は、L G A (Land Grid Array)型のものであってもよい。

【 産業上の利用可能性 】

【 0 0 8 7 】

本発明は、電子装置および半導体装置に好適である。

【 図面の簡単な説明 】

20

【 0 0 8 8 】

【 図 1 】本発明の実施の形態の半導体装置の構造の一例を示す断面図である。

【 図 2 】図 1 に示す半導体装置のシステムの一例を示すブロック構成図である。

【 図 3 】図 1 に示す半導体装置に搭載される第 1 の半導体チップと第 2 の半導体チップの実装方向の一例を示す平面図である。

【 図 4 】図 1 に示す半導体装置に組み込まれる配線基板の最上配線層 (L 1) の配線パターンの一例を示す平面図である。

【 図 5 】図 1 に示す半導体装置に組み込まれる配線基板の上から 2 層めの配線層 (L 2) の配線パターンの一例を示す平面図である。

【 図 6 】図 1 に示す半導体装置に組み込まれる配線基板の上から 3 層めの配線層 (L 3) の配線パターンの一例を示す平面図である。

30

【 図 7 】図 1 に示す半導体装置に組み込まれる配線基板の上から 4 層めの配線層 (L 4) の配線パターンの一例を示す平面図である。

【 図 8 】図 1 に示す半導体装置の組み立て手順の一例を示す製造フロー図である。

【 図 9 】図 1 に示す半導体装置に搭載される第 1 の半導体チップの構造の一例を示す平面図である。

【 図 1 0 】図 1 に示す半導体装置に組み込まれる配線基板の構造の一例を示す平面図である。

【 図 1 1 】図 1 0 に示す配線基板の構造の一例を示す断面図である。

【 図 1 2 】図 8 に示す組み立てにおけるフリップチップ接続完了時の構造の一例を示す平面図である。

40

【 図 1 3 】図 1 2 に示すフリップチップ接続完了時の構造を示す断面図である。

【 図 1 4 】図 8 に示す組み立てにおける第 2 の半導体チップのワイヤボンディング完了時の構造の一例を示す平面図である。

【 図 1 5 】図 1 4 に示す第 2 の半導体チップのワイヤボンディング完了時の構造を示す断面図である。

【 図 1 6 】図 8 に示す組み立てにおける第 3 の半導体チップのワイヤボンディング完了時の構造の一例を示す平面図である。

【 図 1 7 】図 1 6 に示す第 3 の半導体チップのワイヤボンディング完了時の構造を示す断面図である。

50

【図18】図8に示す組み立てにおける組み立て完了時の構造の一例を示す断面図である。

【図19】本発明の実施の形態の変形例の第1の半導体チップと第2の半導体チップの実装方向を示す平面図である。

【図20】本発明の実施の形態の他の変形例の第1の半導体チップと第2の半導体チップの実装状態を示す平面図である。

【符号の説明】

【0089】

- |     |                    |    |

|-----|--------------------|----|

| 1   | 第1のDRAM(第1の半導体チップ) | 10 |

| 1 a | 正面                 |    |

| 1 b | 裏面                 |    |

| 1 c | パッド(電極)            |    |

| 1 d | 第1電極               |    |

| 1 e | 第3電極               |    |

| 1 f | 第1の辺               |    |

| 1 g | 他の辺                |    |

| 1 h | 金パンプ               |    |

| 2   | 第2のDRAM(第2の半導体チップ) |    |

| 2 a | 正面                 | 20 |

| 2 b | 裏面                 |    |

| 2 c | パッド(電極)            |    |

| 2 d | 第2電極               |    |

| 2 e | 第4電極               |    |

| 3   | マイコンチップ(第3の半導体チップ) |    |

| 3 a | 正面                 |    |

| 3 b | 裏面                 |    |

| 3 c | パッド(電極)            |    |

| 4   | SIP(半導体装置)         |    |

| 5   | パッケージ基板(配線基板)      | 30 |

| 5 a | 正面                 |    |

| 5 b | 裏面                 |    |

| 5 c | 共通配線               |    |

| 5 d | 第1の独立配線            |    |

| 5 e | 第2の独立配線            |    |

| 5 f | フリップチップ用電極         |    |

| 5 g | スルーホール配線           |    |

| 5 h | パンプランド             |    |

| 5 i | ワイヤ接続用電極           |    |

| 5 j | フリップチップ用電極群        |    |

| 5 k | ワイヤ接続用電極群          | 40 |

| 5 m | マイコン用ワイヤ接続用電極      |    |

| 6   | ワイヤ                |    |

| 7   | 封止体                |    |

| 8   | ボール電極(外部端子)        |    |

| 9   | アンダーフィル封止部         |    |

【図1】

図1

1a: 主面

3: マイコンチップ(第3の半導体チップ)

4: SDRAM半導体装置

5: パッケージ基板(配線基板)

5a: 主面

5b: 基面

6: 封止材

7: ポール電極(外部端子)

8: ポール電極(外部端子)

【図2】

図2

【図3】

図3

1: 第1のDRAM(第1の半導体チップ)

1a: パッケージ

1b: 第1電極

1c: 第3電極

1d: 第4電極

1e: 第5の辺

1f: 第6の辺

1g: 第7の辺

2: 第2のDRAM(第2の半導体チップ)

2a: 主面

2b: 第2電極

2c: 第3電極

2d: 第4電極

2e: 第5電極

3a: 第6電極

3b: 第7電極

3c: 第8電極

3d: 第9電極

3e: 第10電極

3f: 第11電極

3g: 第12電極

4a: 第13電極

4b: 第14電極

4c: 第15電極

4d: 第16電極

4e: 第17電極

4f: 第18電極

4g: 第19電極

5a: 第20電極

5b: 第21電極

5c: 第22電極

5d: 第23電極

5e: 第24電極

5f: 第25電極

5g: 第26電極

6a: 第27電極

6b: 第28電極

6c: 第29電極

6d: 第30電極

6e: 第31電極

6f: 第32電極

6g: 第33電極

6: ワイヤ

【図7】

図7

【図 8】

図 8

【図 9】

図 9

【図 10】

図 10

【図 12】

図 12

【図 11】

図 11

【図 13】

図 13

【図14】

【図16】

【図15】

【図17】

【図18】

【図19】

【図20】

图 20

【図4】

図4

【図5】

図5

【図6】

図6

---

フロントページの続き

審査官 宮本 靖史

(56)参考文献 特開2002-280516 (JP, A)

特開平06-177322 (JP, A)

特開2002-237566 (JP, A)

特開2003-031763 (JP, A)

特開2003-051580 (JP, A)

特開2000-164796 (JP, A)

特開平11-354713 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 25/065

H01L 23/12

H01L 25/07