(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5427390号

(P5427390)

(45) 発行日 平成26年2月26日(2014.2.26)

(24) 登録日 平成25年12月6日(2013.12.6)

(51) Int.Cl.

F 1

|             |           |            |      |

|-------------|-----------|------------|------|

| HO1L 21/336 | (2006.01) | HO1L 29/78 | 627C |

| HO1L 29/786 | (2006.01) | HO1L 29/78 | 612D |

| HO1L 21/28  | (2006.01) | HO1L 21/28 | E    |

| HO1L 29/417 | (2006.01) | HO1L 29/50 | M    |

| HO1L 29/423 | (2006.01) | HO1L 29/58 | G    |

請求項の数 6 (全 23 頁) 最終頁に続く

(21) 出願番号 特願2008-269014 (P2008-269014)

(22) 出願日 平成20年10月17日 (2008.10.17)

(65) 公開番号 特開2009-124122 (P2009-124122A)

(43) 公開日 平成21年6月4日 (2009.6.4)

審査請求日 平成23年9月7日 (2011.9.7)

(31) 優先権主張番号 特願2007-275804 (P2007-275804)

(32) 優先日 平成19年10月23日 (2007.10.23)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 藤川 最史

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 細谷 邦雄

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 千葉 陽子

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 鈴木 聰一郎

最終頁に続く

(54) 【発明の名称】半導体装置の作製方法

## (57) 【特許請求の範囲】

## 【請求項 1】

透光性を有する基板上にゲート電極を形成し、

前記基板及び前記ゲート電極上にゲート絶縁膜を成膜し、

前記ゲート絶縁膜上に第1の半導体膜を成膜し、

前記第1の半導体膜上に一導電型の不純物元素を含有する第2の半導体膜を成膜し、

前記第2の半導体膜上に接して、多階調フォトマスクを用いて第1のフォトレジストパターンを形成し、

前記第1のフォトレジストパターンをマスクとして前記第1の半導体膜及び前記第2の半導体膜のエッチングを行い、

前記第1のフォトレジストパターンを加工して第2のフォトレジストパターンを形成し、

前記ゲート絶縁膜、前記エッチングが行われた前記第2の半導体膜、及び前記第2のフォトレジストパターン上に導電膜を成膜し、

前記第2のフォトレジストパターン上に成膜された前記導電膜を前記第2のフォトレジストパターンと同時に除去することによってソース電極及びドレイン電極を形成することを特徴とする半導体装置の作製方法。

## 【請求項 2】

透光性を有する基板上に画素部のゲート電極及び端子部に延在するゲート配線を同一の材料で形成し、

10

20

前記基板、前記ゲート電極、及び前記ゲート配線上にゲート絶縁膜を成膜し、

前記ゲート絶縁膜上に第1の半導体膜を成膜し、

前記第1の半導体膜上に一導電型の不純物元素を含有する第2の半導体膜を成膜し、

前記第2の半導体膜上に接して、多階調フォトマスクを用いて第1のフォトレジストパ

ターンを形成し、

前記第1のフォトレジストパターンをマスクとして前記第1の半導体膜及び前記第2の半導体膜のエッチングを行い、

前記第1のフォトレジストパターンを加工して第2のフォトレジストパターンを形成し

、

前記ゲート絶縁膜、前記エッチングが行われた前記第2の半導体膜、及び前記第2のフォトレジストパターン上に導電膜を成膜し、

前記第2のフォトレジストパターン上に成膜された前記導電膜を前記第2のフォトレジストパターンと同時に除去することによって前記画素部のソース電極及びドレイン電極と、前記端子部に延在するソース配線と、を形成することを特徴とする半導体装置の作製方法。

【請求項3】

透光性を有する基板上に第1の導電膜を成膜し、

前記第1の導電膜上に、第1のフォトマスクを用いて第1のフォトレジストパターンを形成し、

前記第1のフォトレジストパターンをマスクとして前記第1の導電膜のエッチングを行い、画素部のゲート電極及び端子部に延在するゲート配線を形成し、

前記基板、前記ゲート電極、及び前記ゲート配線上にゲート絶縁膜を成膜し、

前記ゲート絶縁膜上に第1の半導体膜を成膜し、

前記第1の半導体膜上に一導電型の不純物元素を含有する第2の半導体膜を成膜し、

前記第2の半導体膜上に、多階調フォトマスクである第2のフォトマスクを用いて第2のフォトレジストパターンを形成し、

前記第2のフォトレジストパターンをマスクとして前記第1の半導体膜及び前記第2の半導体膜に第1のエッチングを行い、

前記第2のフォトレジストパターンを加工して第3のフォトレジストパターンを形成し

、

前記ゲート絶縁膜、前記第1のエッチングが行われた前記第2の半導体膜、及び前記第3のフォトレジストパターン上に第2の導電膜を成膜し、

前記第3のフォトレジストパターン上に成膜された前記第2の導電膜を前記第3のフォトレジストパターンと同時に除去することによって前記画素部のソース電極及びドレイン電極と、前記端子部に延在するソース配線と、を形成し、

前記ソース電極、前記ドレイン電極、及び前記ソース配線をマスクとして前記第1の半導体膜及び前記第2の半導体膜に第2のエッチングを行い、

前記ゲート電極、前記ゲート配線、前記ソース電極、前記ドレイン電極、及び前記ソース配線をフォトマスクとした裏面露光により、第4のフォトレジストパターンを形成し、

前記第4のフォトレジストパターンをマスクとして前記第1の半導体膜に第3のエッチングを行い、

前記ゲート絶縁膜、前記第3のエッチングが行われた前記第1の半導体膜、前記ソース電極、前記ドレイン電極、及び前記ソース配線上に絶縁膜を成膜し、

前記絶縁膜上に、第3のフォトマスクを用いて第5のフォトレジストパターンを形成し

、

前記第5のフォトレジストパターンをマスクとして前記絶縁膜に第4のエッチングを行い、前記絶縁膜に開口部を形成し、

前記ゲート配線、前記ソース電極、前記ドレイン電極、前記ソース配線、及び前記第4のエッチングが行われた前記絶縁膜上に透明導電膜を成膜し、

前記透明導電膜上に、第4のフォトマスクを用いて第6のフォトレジストパターンを形

10

20

30

40

50

成し、

前記第6のフォトレジストパターンをマスクとして前記透明導電膜に第5のエッティングを行うことを特徴とする半導体装置の作製方法。

【請求項4】

請求項1または2において、

前記第2のフォトレジストパターンは逆テーパー形状であることを特徴とする半導体装置の作製方法。

【請求項5】

請求項3において、

前記第3のフォトレジストパターンは逆テーパー形状であることを特徴とする半導体装置の作製方法。 10

【請求項6】

請求項1乃至5のいずれか一において、前記多階調フォトマスクはハーフトーンフォトマスク又はグレートーンフォトマスクであることを特徴とする半導体装置の作製方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、薄膜トランジスタ（以下、TFTという）で構成された回路を有する半導体装置の作製方法に関する。例えば、液晶や自発光素子を用いた表示装置に代表される電気光学装置の作製方法に関する。 20

【0002】

なお、本明細書中において半導体装置とは、半導体特性を利用することで機能しうる装置全般を指し、電気光学装置、半導体回路及び電子機器は全て半導体装置である。

【背景技術】

【0003】

近年、絶縁表面を有する基板上に形成された半導体薄膜（厚さ数nm～数百nm程度）を用いてTFTを形成する技術が普及している。TFTは、ICや電気光学装置のような電子デバイスに応用され、特に画像を表示する電気光学装置のスイッチング素子として広く応用されている。 30

【0004】

画像を表示する電気光学装置として、薄型テレビ、パソコンコンピュータ、携帯電話等のディスプレイに広く利用されている液晶表示装置が知られている。液晶表示装置ではパッシブマトリクス型に比べ高精細な画像が得られるアクティブマトリクス型が多く用いられるようになっている。アクティブマトリクス型の液晶表示装置においては、表示領域である画素部や、他の基板に設けられた回路の配線と電気的に接続するために基板の端部に作製される端子部などから構成され、ゲート配線とソース配線とがマトリクス状に延在し、そのマトリクスの中に配置された画素電極をTFTによって制御することで、画像が表示される。詳しくは、選択された画素電極とその画素電極に対応する対向電極との間に電圧が印加されることによって、画素電極と対向電極との間に配置された液晶層の光学変調が行われ、この光学変調が表示パターンとして観察者に認識されるというものである。 40

【0005】

このようなアクティブマトリクス型の液晶表示装置を代表とする電気光学装置の用途は広がっており、画面サイズの大面積化とともに高精細化、高開口率化や高信頼性の要求が高まっている。また、それらと同時に生産性の向上や低コスト化の要求も高まっている。

【0006】

従来では、300以下の低温で大面積の基板上に形成可能であることから非晶質半導体膜として非晶質シリコン膜が好適に用いられている。また、非晶質半導体膜で形成されたチャネル形成領域を有する逆スタガ型（若しくはボトムゲート型）のTFTが多く用いられており、その標準的な作製方法は確立されている。例えば、特開平9-171197には、基板上に5枚のフォトマスク（5次写真工程）を用いてTFT部と端子部（パッド

部)を形成する方法が開示されている。

【特許文献1】特開平9-171197号公報

【発明の開示】

【発明が解決しようとする課題】

【0007】

従来、アクティブマトリクス型の液晶表示装置を代表とする電気光学装置は、写真蝕刻(フォトリソグラフィー)技術により、最低でも5枚以上のフォトマスクを使用してTFTを有する画素部と端子部を基板上に作製していたため製造コストが高かった。生産性を向上させ歩留まりを向上させるためには、工程数を削減することが有効な手段として考えられる。

10

【0008】

具体的には、TFTを有する画素部と端子部の製造に要するフォトマスクの枚数を削減することが必要である。フォトマスクとは、フォトリソグラフィーの技術において、基板上に成膜された薄膜をエッチング等によって所望の形状に加工する際にマスクとして機能するフォトレジストパターンを形成するために用いる。なお、基板上に成膜された薄膜を所望の形状に加工することをパターニングと呼ぶ。

【0009】

このフォトマスクを1枚使用することによって、レジスト形成、プリベーク、フォトマスクを用いた露光、現像、ポストベーク等の工程と、その前後の工程において、被膜の成膜及びエッチング等の工程、さらにレジスト剥離、洗浄、乾燥工程や検査工程等の製造工程が付加され、非常に煩雑なものとなっていた。従来の5枚以上のフォトマスクを使用することはこれらの工程を5回以上繰り返すことになるから、TFTを有する画素部と端子部の生産性、歩留まりに大きな影響を及ぼしている。TFTを有する画素部と端子部の生産性、歩留まりを向上させ、製造コストを低減するために、フォトマスクを削減することは大きな課題である。

20

【0010】

本発明はこのような問題に答えるものであり、アクティブマトリクス型の液晶表示装置に代表される電気光学装置において、TFTを有する画素部と端子部を作製する工程数を削減して、具体的にはフォトリソグラフィー工程で使用するフォトマスクの枚数を削減して、TFTを有する画素部と端子部の生産性、歩留まりを向上させ、製造コストの低減を実現することを課題としている。

30

【課題を解決するための手段】

【0011】

上記課題を解決するために、本発明は、逆スタガ型のTFT構造を採用し、透光性基板に透過部と光強度を低減する機能を有する中間透過部と遮光部が設けられたフォトマスク(多階調フォトマスク)によって第1のフォトレジストパターンを形成し、第1のフォトレジストパターンをマスクとして第1の半導体膜及び一導電型の不純物元素を含有する第2の半導体膜のエッチングを行い、第1のフォトレジストパターンを加工して第2のフォトレジストパターンを形成し、全面に導電膜を成膜し、第2のフォトレジストパターンと第2のフォトレジストパターン上に成膜された導電膜を同時に除去することで、画素部のソース電極及びドレイン電極と端子部に延在するソース配線を形成することを特徴とする。

40

【0012】

また、本発明においては、画素部のソース電極及びドレイン電極と端子部に延在するソース配線を同一の材料かつ同一の工程によって形成する。

【0013】

なお、本発明においては、第1の半導体膜および第2の半導体膜に非晶質半導体膜を適用することも出来るし、第1の半導体膜に微結晶半導体膜と非晶質半導体膜の積層を適用することも出来る。

【0014】

50

本発明は、透光性を有する基板上の全面に第1の導電膜を成膜し、透光性基板に透過部と遮光部が設けられた第1のフォトマスクによって第1のフォトレジストパターンを形成し、第1のフォトレジストパターンをマスクとして第1の導電膜のエッチングを行い、画素部のゲート電極と端子部に延在するゲート配線を形成し、ゲート絶縁膜として機能する絶縁膜、第1の半導体膜、及び一導電型の不純物元素を含有する第2の半導体膜を順次に成膜し、透光性基板に透過部と光強度を低減する機能を有する中間透過部と遮光部が設けられた第2のフォトマスク（多階調フォトマスク）によって第2のフォトレジストパターンを形成し、第2のフォトレジストパターンをマスクとして第1の半導体膜及び一導電型の不純物元素を含有する第2の半導体膜のエッチングを行い、第2のフォトレジストパターンを加工して第3のフォトレジストパターンを形成し、基板全面に第2の導電膜を成膜し、第3のフォトレジストパターンと第3のフォトレジストパターン上に成膜された第2の導電膜を同時に除去することで、画素部のソース電極及びドレイン電極と端子部に延在するソース配線を形成し、第2の導電膜からなる画素部のソース電極及びドレイン電極と端子部に延在するソース配線とをマスクとして第1の半導体膜及び一導電型の不純物元素を含有する第2の半導体膜のエッチングを行い、第1の導電膜からなる画素部のゲート電極と端子部に延在するゲート配線、第2の導電膜からなる画素部のソース電極及びドレイン電極と端子部に延在するソース配線を遮光部として利用すること（裏面露光）によって第4のフォトレジストパターンを形成し、第4のフォトレジストパターンをマスクとして第1の半導体膜のエッチングを行い、パッシベーション膜として機能する絶縁膜を成膜し、透光性基板に透過部と遮光部が設けられた第3のフォトマスクによって第5のフォトレジストパターンを形成し、第5のフォトレジストパターンを用いて電気的接触を実現する開口部を形成し、全面に透明導電膜を成膜し、透光性基板に透過部と遮光部が設けられた第4のフォトマスクによって第6のフォトレジストパターンを形成し、第6のフォトレジストパターンをマスクとして透明導電膜のエッチングを行い、画素部の画素電極と端子部の電極を形成することを特徴とする。10

#### 【0015】

また、本発明においては、画素部のゲート電極と端子部に延在するゲート配線を同一の材料かつ同一の工程によって形成し、画素部のソース電極及びドレイン電極と端子部に延在するソース配線を同一の材料かつ同一の工程によって形成する。20

#### 【0016】

なお、本発明においては、第1の半導体膜および第2の半導体膜に非晶質半導体膜を適用することも出来るし、第1の半導体膜に微結晶半導体膜と非晶質半導体膜の積層を適用することも出来る。30

#### 【発明の効果】

#### 【0017】

本発明により、アクティブマトリクス型の液晶表示装置に代表される電気光学装置において、逆スタガ型のTFTを有する画素部と端子部を4枚のフォトマスクで作製することができ、従来必要であったフォトマスクの枚数（最低5枚以上）より1枚削減することができる。1枚のフォトマスクの削減により、電気光学装置の生産性、歩留まりを向上させ、製造コストの低減を実現することができる。40

#### 【0018】

より具体的には、本発明により、逆スタガ型のTFTを有する画素部のソース電極及びドレイン電極と端子部に延在するソース配線のバーニング用のフォトマスクを削減することができ、画素部のソース電極及びドレイン電極と端子部に延在するソース配線のバーニングのためのエッチング工程も省略することができるため、電気光学装置の生産性、歩留まりを向上させ、製造コストの低減を実現することができる。

#### 【発明を実施するための最良の形態】

#### 【0019】

以下、本発明の実施の形態について図面を参照しながら説明する。

#### 【0020】

50

## (実施の形態 1 )

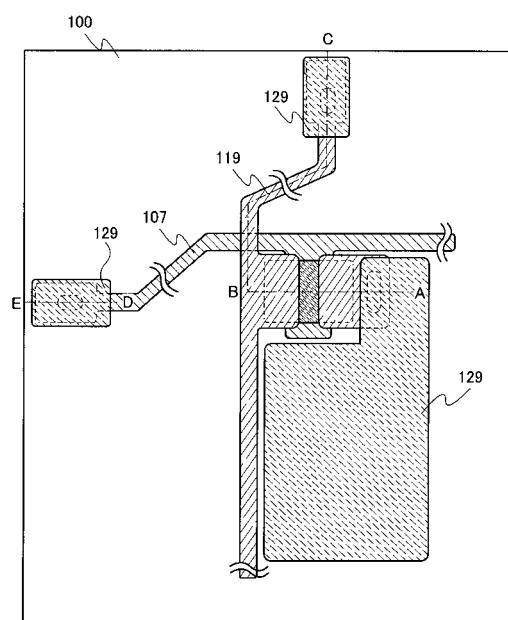

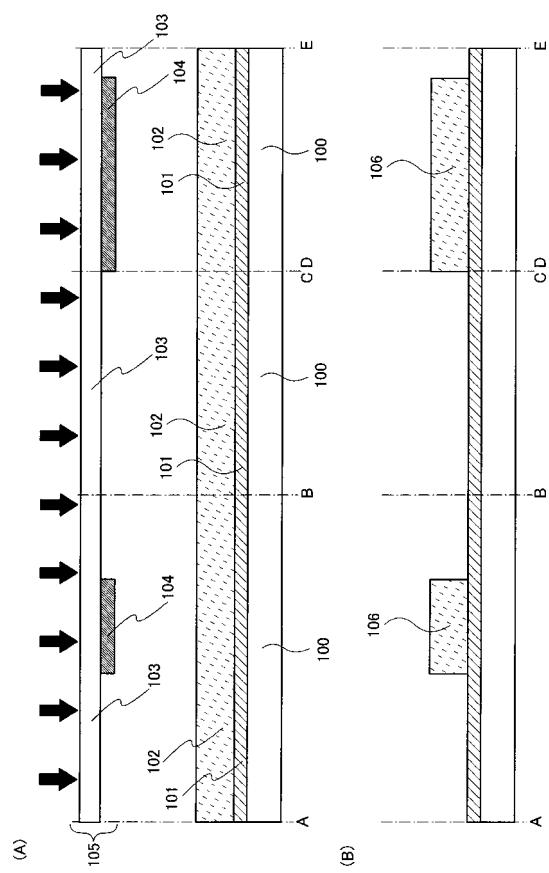

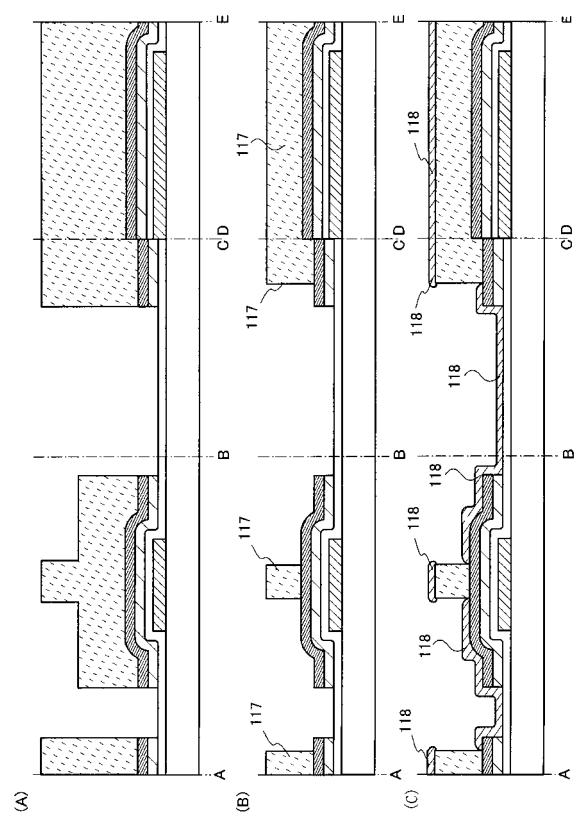

本発明の実施の形態について、図1～図12を用いて説明する。本実施の形態では基板100上に、チャネル形成領域に非晶質半導体膜を適用したTFTを逆スタガ型で作製する方法について工程に従って詳細に説明する。また、それと同時に、他の基板に設けられた回路の配線と電気的に接続するために、基板100の端部に作製される端子部の作製工程を示す。図1は本実施の形態によって作製される半導体装置の上面図であり、図2～図12は図1のA-B、B-C及びD-E断面を示しており、A-B断面は画素部、B-C及びD-E断面は端子部にそれぞれ該当する。なお、図1においては、一本のソース線及び一本のゲート線が延在した端子部の構成が示されているが、実際の液晶や自発光素子を用いた表示装置では複数の画素がマトリクス状に存在しており、それに対応して複数のソース線及びゲート線が存在していることはいうまでもない。10

## 【0021】

なお、本発明は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその趣旨から逸脱することなくその形態及び詳細を様々に変更しうることは当業者であれば容易に理解できる。従って、本発明は本実施の形態の記載内容に限定して解釈されるものではない。

## 【0022】

まず、図2(A)において、透光性を有する基板100を用意する。基板100にはコーニング社の7059ガラスや1737ガラス等に代表されるバリウムホウケイ酸ガラスやアルミノホウケイ酸ガラス等のガラス基板を用いることができる。その他に、石英基板、プラスチック基板等の透光性基板を使用することもできる。基板100がマザーガラスの場合には、基板の大きさとして、第1世代(320mm×400mm)、第2世代(400mm×500mm)、第3世代(550mm×650mm)、第4世代(680mm×880mm、または730mm×920mm)、第5世代(1000mm×1200mm、または1100mm×1250mm)、第6世代(1500mm×1800mm)、第7世代(1900mm×2200mm)、第8世代(2160mm×2460mm)、第9世代(2400mm×2800mm、2450mm×3050mm)、第10世代(2950mm×3400mm)等のものを用いればよい。20

## 【0023】

次いで、画素部のゲート電極と端子部に延在するゲート配線を構成する導電膜101を基板100の上の全面に成膜した後、レジスト102を形成する。30

## 【0024】

そして、透光性の基板103に透過部とクロム(Cr)等の金属膜から成る遮光部104が設けられた第1のフォトマスク105を用いて、フォトリソグラフィー工程を行う。図2(A)に示される矢印は照射される露光の光をイメージしており、露光の光は第1のフォトマスク105を通過した後、レジスト102に照射される。露光及び現像工程を経て、フォトレジストパターン106を形成し(図2(B)参照)、エッチングにより導電膜101の不要な部分を除去することでパターニングを行い(図3(A)参照)、フォトレジストパターン106を剥離することによって画素部のゲート電極157と端子部に延在するゲート配線107を形成する(図3(B)参照)。画素部のゲート電極と端子部に延在するゲート配線は同一の材料から形成されている。40

## 【0025】

画素部のゲート電極157と端子部に延在するゲート配線107はアルミニウム(Al)や銅(Cu)等の低抵抗導電性材料で形成することが望ましいが、単体では耐熱性が劣り、ヒロック等の問題を生じやすく、また腐蝕しやすい、剥離しやすい(基板との密着性)等の問題点があるので耐熱性導電性材料と組み合わせて形成する。また、低抵抗導電性材料としてAgPdCu合金を用いても良い。耐熱性導電性材料としては、チタン(Ti)、タンタル(Ta)、タンゲステン(W)、モリブデン(Mo)、クロム(Cr)、ネオジム(Nd)から選ばれた元素、または前記元素を成分とする合金か、前記元素を組み合わせた合金膜、または前記元素を成分とする窒化物で形成する。例えば、チタン(Ti)50

)と銅 (Cu) の積層、窒化タンタルと銅 (Cu) との積層が挙げられる。また、チタン (Ti)、シリコン (Si)、クロム (Cr)、ネオジム (Nd) 等の耐熱性導電性材料と組み合わせて形成した場合、平坦性が向上するため好ましい。また、このような耐熱性導電性材料のみ、例えばモリブデン (Mo) とタングステン (W) を組み合わせて形成しても良い。

【0026】

液晶表示装置を実現するためには、画素部のゲート電極 157 と端子部に延在するゲート配線 107 は耐熱性導電性材料と低抵抗導電性材料とを組み合わせて形成することが望ましい。この時の適した組み合わせを説明する。

【0027】

画面サイズが 5 型程度までなら耐熱性導電性材料の窒化物から成る導電膜 (A) と耐熱性導電性材料からなる導電膜 (B) とを積層した二層構造とする。導電膜 (B) は、タンタル (Ta)、チタン (Ti)、タングステン (W)、ネオジム (Nd)、クロム (Cr) から選ばれた元素、または前記元素を成分とする合金か、前記元素を組み合わせた合金膜で形成すれば良く、導電膜 (A) は窒化タンタル膜、窒化タングステン膜、窒化チタン膜等で形成する。導電膜 (A) は 10 ~ 100 nm (好ましくは 20 ~ 50 nm) とし、導電膜 (B) は 200 ~ 400 nm (好ましくは 250 ~ 350 nm) とする。

【0028】

一方、大画面に適用するには耐熱性導電性材料から成る導電膜 (A) と低抵抗導電性材料から成る導電膜 (B) と耐熱性導電性材料から成る導電膜 (C) とを積層した三層構造とすることが好ましい。低抵抗導電性材料から成る導電膜 (B) は、アルミニウム (Al) を成分とする材料で形成し、純アルミニウム (Al) の他に、0.01 ~ 5 atomic % のスカンジウム (Sc)、チタン (Ti)、ネオジム (Nd)、シリコン (Si) 等を含有するアルミニウム (Al) を使用する。導電膜 (C) は導電膜 (B) のアルミニウム (Al) にヒロックが発生するのを防ぐ効果がある。導電膜 (A) は 10 ~ 100 nm (好ましくは 20 ~ 50 nm) とし、導電膜 (B) は 200 ~ 400 nm (好ましくは 250 ~ 350 nm) とし、導電膜 (C) は 10 ~ 100 nm (好ましくは 20 ~ 50 nm) とする。本実施の形態では、チタン (Ti) をターゲットとしたスパッタ法により導電膜 (A) をチタン (Ti) 膜で 50 nm の厚さに成膜し、アルミニウム (Al) をターゲットとしたスパッタ法により導電膜 (B) をアルミニウム (Al) 膜で 200 nm の厚さに成膜し、チタン (Ti) をターゲットとしたスパッタ法により導電膜 (C) をチタン (Ti) 膜で 50 nm の厚さに成膜する。

【0029】

なお、本実施の形態においてレジストにはポジ型レジストを使用する。ポジ型レジストとは、露光の光の照射領域が現像液に可溶化するタイプのレジストである。もちろん適用可能であればネガ型レジストを用いても良い。ネガ型レジストとは、露光の光の照射領域が現像液に不溶化するタイプのレジストのことである。

【0030】

次いで、絶縁膜 108 を全面に成膜する (図 3 (C) 参照)。絶縁膜 108 はプラズマ CVD 法やスパッタ法等の方法を用いて成膜し、膜厚を 50 ~ 200 nm とする。この絶縁膜 108 はゲート絶縁膜として機能する。

【0031】

例えば、絶縁膜 108 として窒化シリコン膜を用い、150 nm の厚さで成膜する。もちろん、絶縁膜 108 は窒化シリコン膜に限定されるものではなく、酸化シリコン膜、酸化窒化シリコン膜、窒化酸化シリコン膜、酸化タンタル膜等の他の絶縁膜を用い、これらの材料から成る単層または積層構造として成膜しても良い。例えば、窒化シリコン膜の積層構造や、下層を窒化シリコン膜とし、上層を酸化シリコン膜とする積層構造としても良い。ここでは、酸化窒化シリコン膜とは、その組成として、窒素よりも酸素の含有量が多いものであって、濃度範囲として酸素が 55 ~ 65 原子%、窒素が 1 ~ 20 原子%、Si が 25 ~ 35 原子%、水素が 0.1 ~ 10 原子% の範囲で含まれるものという。また、窒

10

20

30

40

50

化酸化シリコン膜とは、その組成として、酸素よりも窒素の含有量が多いものであって、濃度範囲として酸素が15～30原子%、窒素が20～35原子%、シリコン(Si)が25～35原子%、水素が15～25原子%の範囲で含まれるものをいう。さらには、周波数が1GHzのマイクロ波プラズマCVD装置を用いて絶縁膜108を成膜することが好ましい。マイクロ波プラズマCVD装置で成膜した酸化窒化シリコン膜、窒化酸化シリコン膜等は、耐圧が高く、後に形成されるTFTの信頼性を高めることができる。

【0032】

次いで、プラズマCVD法やスパッタ法等の方法を用いて絶縁膜108の上に50～200nm(好ましくは100～150nm)の厚さで第1の非晶質半導体膜109を成膜する(図3(C)参照)。

10

【0033】

代表的には、この第1の非晶質半導体膜には非晶質シリコン(a-Si)膜を用いるが、その他には、非晶質シリコングルマニウム膜、非晶質シリコンカーバイド等の非晶質構造を有する化合物半導体膜を適用することも可能である。

【0034】

次いで、一導電型の不純物元素を含有する第2の非晶質半導体膜110を20～80nmの厚さで成膜する。一導電型の不純物元素を含有する第2の非晶質半導体膜110は、プラズマCVD法やスパッタ法等の方法で全面に成膜する(図3(C)参照)。

20

【0035】

一導電型の不純物元素を含有する第2の非晶質半導体膜110は、n型のTFTを形成する場合には、代表的な不純物元素としてリン(P)を添加すれば良い。

【0036】

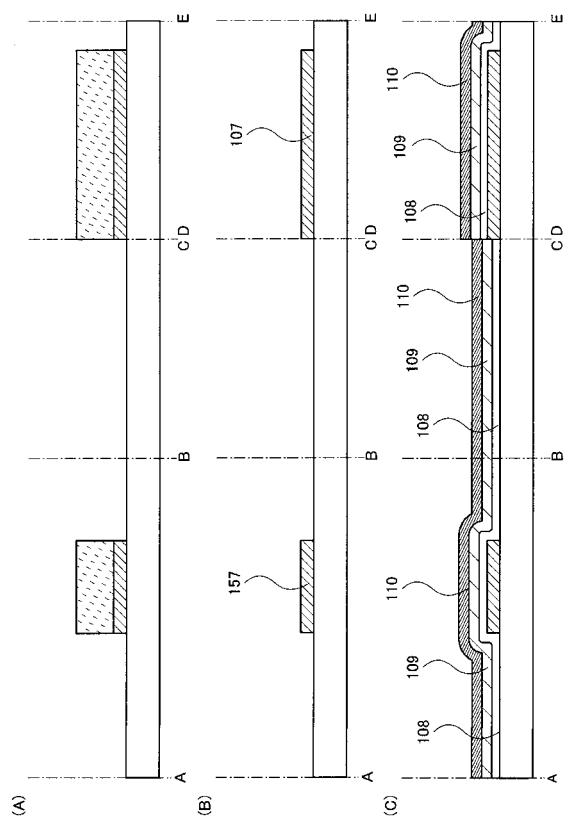

次いで、図4(A)に示すように全面にレジスト111を塗布する。

【0037】

そして、透光性の基板112に透過部と光強度を低減する機能を有する中間透過部113とCr等の金属膜から成る遮光部114が設けられた第2のフォトマスク115を用いて、フォトリソグラフィー工程を行う。図4(A)に示される矢印は照射される露光の光をイメージしており、露光の光は第2のフォトマスク115を通過した後、レジスト111に照射される。露光及び現像工程を経て、フォトレジストパターン116を形成する(図4(B)参照)。

30

【0038】

第2のフォトマスク115は、多階調フォトマスクと呼ばれ、通常のフォトマスクが透過部と遮光部のみを有するのに対し、それに加えて中間透過部が形成されていることに特徴がある。つまり、多階調フォトマスクとは露光の光が透過する割合がほぼ100%となる透光性基板上に透過率が1%以上99%以下となる中間透過部を設け、さらに透過率がほぼ0%となる遮光部を設けた構造のフォトマスクを意味する。この中間透過部の形成方法により、ハーフトーンフォトマスクとグレートーンフォトマスクに分類される。

【0039】

ハーフトーンフォトマスクは中間透過部に中間透過膜を形成することで実現する。一方、グレートーンフォトマスクは透過部に解像度以下のスリットを形成し、そのスリットによって露光の光の一部を遮ることで、中間透過部を形成する。このような多階調フォトマスクで露光されたレジストは露光部分、半露光部分、未露光部分がそれぞれ形成される。半露光部分のレジストを現像するとその厚みは露光部分と未露光部分のレジストの間の厚みになる(図4(B)参照)。

40

【0040】

次いで、フォトレジストパターン116を用いて、第1の非晶質半導体膜109と第2の非晶質半導体膜110の不要な部分をエッチングによって除去することでパターニングを行う(図5(A)参照)。

【0041】

次いで、酸素プラズマアッティング等の処理によって、フォトレジストパターン116の

50

膜厚及び幅を薄くするように加工を行い、フォトレジストパターン117を形成する（図5（B）参照）。

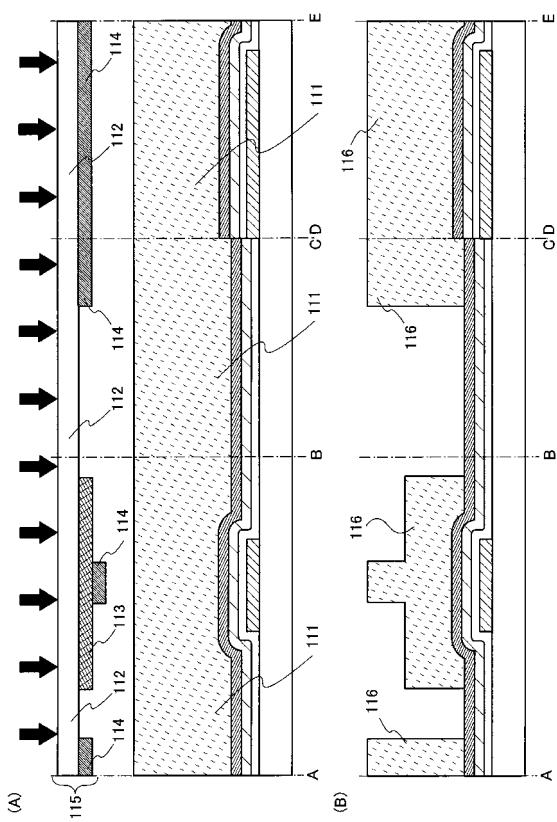

【0042】

次いで、全面に金属材料から成る導電膜118をスパッタ法や真空蒸着法等の方法を用いて成膜する。導電膜118の材料としては、第2の非晶質半導体膜110とオーミックコンタクトのとれる金属材料であれば特に限定されず、アルミニウム（Al）、クロム（Cr）、タンタル（Ta）、チタン（Ti）から選ばれた元素、または前記元素を成分とする合金か、前記元素を組み合わせた合金膜等が挙げられる。本実施の形態ではスパッタ法を用い、導電膜118として、50～150nmの厚さで成膜したチタン（Ti）膜と、そのチタン（Ti）膜上に重ねてアルミニウム（Al）を300～400nmの厚さで成膜し、さらにその上にチタン（Ti）膜を100～150nmの厚さで成膜する（図5（C）参照）。

10

【0043】

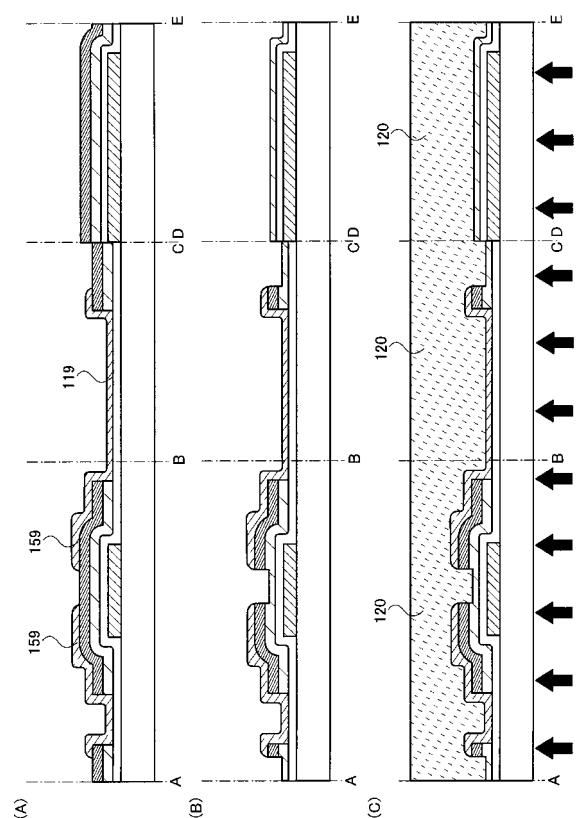

この時、図5（C）に示すように、フォトレジストパターン117上の導電膜118とそれ以外の領域上の導電膜118とでは、フォトレジストパターン117の存在により段差が生じる。この段差によって、導電膜118は分断される。これにより、フォトレジストパターン117を剥離して除去する際に、フォトレジストパターン117上の分断された導電膜118を、フォトレジストパターン117と一緒にして同時に除去することができる（リフトオフ法）。結果として、新たなフォトマスクを必要とせず、パターニングのためのエッチング工程を行うことなく導電膜118のパターニングをすることができ、画素部のソース電極及びドレイン電極159と端子部に延在するソース配線119を形成することができる（図6（A）参照）。画素部のソース電極及びドレイン電極と端子部に延在するソース配線は同一の材料から形成されている。

20

【0044】

なお、フォトレジストパターン117上の導電膜118とそれ以外の領域上の導電膜118との段差による分断を確実に行うためには、フォトレジストパターン117の膜厚及び形状と導電膜118の膜厚及び形状との関係を十分に考慮する必要がある。フォトレジストパターン117については、段差を大きくするために膜厚を厚くした方が好ましく（数μm～数十μm）、または導電膜118の被覆性を下げるために形状を逆テーパー形状にしても良い。フォトレジストパターン117は、レジスト111を第2のフォトマスク115を用いて露光、現像した後、さらに酸素プラズマアッシングして加工した後の形状であるため、レジスト111には十分な膜厚が必要とされる。

30

【0045】

一方、導電膜118については、導電膜118の被覆性を下げるために膜厚は薄い方が好ましい。また、本実施の形態のように、導電膜118を積層構造で成膜することは、同じ膜厚を有する導電膜118を単層で成膜するよりも好ましい。導電膜118を被覆性の低い薄い膜厚の積層によって成膜するので、導電膜118を単層で成膜する場合よりも、導電膜118の被覆性は下がる。さらに、導電膜118を構成する第2層目（以下、第2層目と呼ぶ）を成膜するときには、フォトレジストパターン117上には分断された導電膜118を構成する第1層目（以下、第1層目と呼ぶ）が存在している。このため、フォトレジストパターン117上の分断された第1層目とそれ以外の領域上の分断された第1層目との段差は、第1層目を成膜する前のフォトレジストパターン117の存在による段差と同じ高さを有することになり、この段差によって第2層目も分断されやすくなっている。導電膜118の第3層目以降を成膜する場合についても同様のことがいえる。

40

【0046】

次いで、画素部のソース電極及びドレイン電極159と端子部に延在するソース配線119をマスクとして、画素部のソース電極及びドレイン電極159と端子部に延在するソース配線119に覆われていない第2の非晶質半導体膜110と第1の非晶質半導体膜109の一部をエッチングによって除去することでパターニングを行う。第1の非晶質半導体膜109のチャネルが形成される部分については、その表層面はエッチングされ膜厚が

50

薄くなっている（図6（B）参照）。

【0047】

次いで、図6（C）に示すように全面にレジスト120を形成する。そして、すでに基板100の上に形成されている画素部のゲート電極と端子部に延在するゲート配線107、画素部のソース電極及びドレイン電極159と端子部に延在するソース配線119を遮光部として利用して、基板100の裏面側（薄膜が形成されていない面側）から露光の光を照射し、フォトリソグラフィー工程を行う（裏面露光）。図6（C）に示される矢印は照射される露光の光をイメージしており、露光の光は基板100を通過した後、レジスト120に照射される。露光及び現像工程を経て、フォトレジストパターン121を形成する（図7（A）参照）。

10

【0048】

次いで、フォトレジストパターン121を用いて、第1の非晶質半導体膜109の不要な部分をエッティングによって除去することでパターニングを行う（図7（B）参照）。フォトレジストパターン121を剥離することによって図7（C）に示す状態を得る。

【0049】

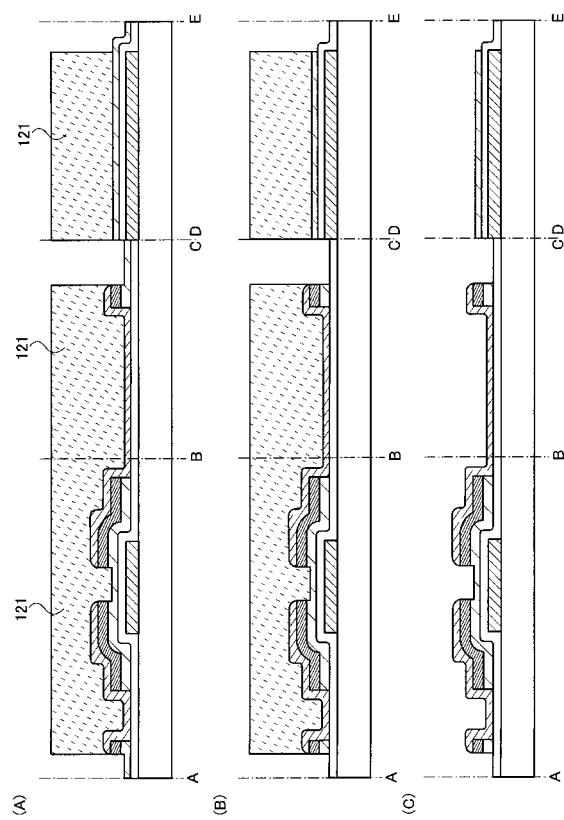

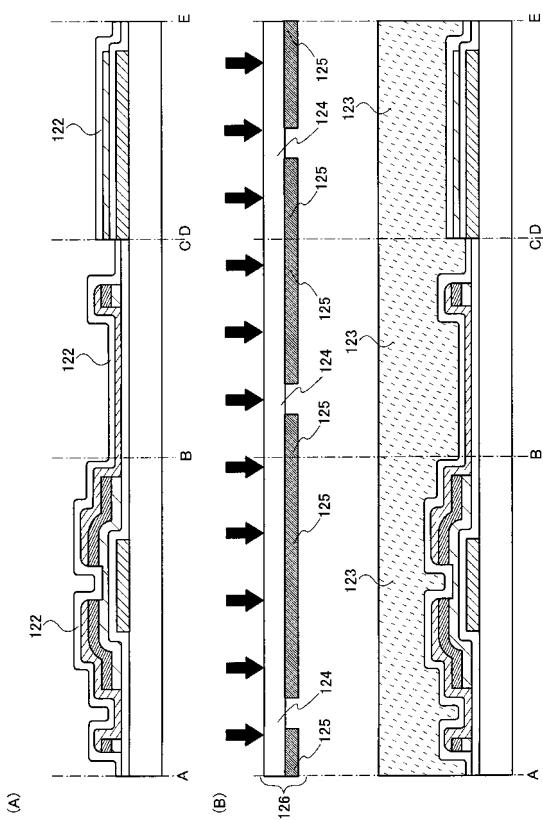

次いで、プラズマCVD法やスパッタ法等の方法を用い、絶縁膜122を全面に成膜する（図8（A）参照）。絶縁膜122は窒化シリコン膜、酸化シリコン膜、酸化窒化シリコン膜、窒化酸化シリコン等を用い、これらの材料から成る単層または積層構造として成膜しても良く、パッシベーション膜として機能する。

20

【0050】

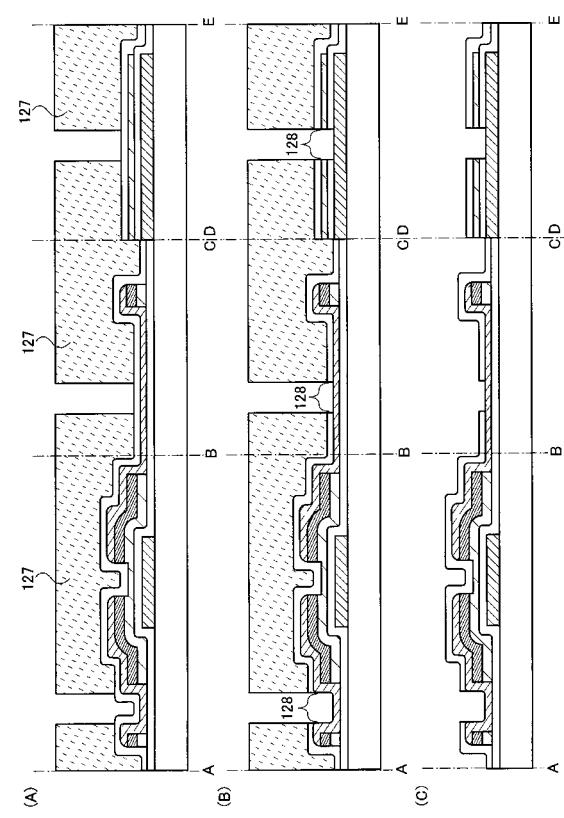

次いで、図8（B）に示すように全面にレジスト123を形成する。そして、透光性の基板124に透過部と金属膜から成る遮光部125が設けられた第3のフォトマスク126を用いて、フォトリソグラフィー工程を行う。図8（B）に示される矢印は照射される露光の光をイメージしており、露光の光は第3のフォトマスク126を通過した後、レジスト123に照射される。露光及び現像工程を経て、フォトレジストパターン127を形成する（図9（A）参照）。

【0051】

次いで、フォトレジストパターン127を用いて、後の工程において形成される透明導電膜との電気的接続を実現するための開口部128を形成する（図9（B）参照）。フォトレジストパターン127を剥離することによって図9（C）に示す状態を得る。

30

【0052】

次いで、スパッタリング法や真空蒸着法等の方法を用い、全面に透明導電膜129を成膜する（図10（A）参照）。透明導電膜129の材料として、酸化インジウム（In<sub>2</sub>O<sub>3</sub>）や酸化インジウム酸化スズ合金（In<sub>2</sub>O<sub>3</sub> - SnO<sub>2</sub>、以下ITOという）等を用いる。ITOのエッティングは残渣が発生しやすいので、エッティング加工性を改善するために酸化インジウム酸化亜鉛合金（In<sub>2</sub>O<sub>3</sub> - ZnO）を用いても良い。In<sub>2</sub>O<sub>3</sub> - ZnOは表面平滑性に優れ、ITOと比較して熱安定性にも優れており、アルミニウム（Al）膜との腐蝕反応を防止することもできる。同様に、酸化亜鉛（ZnO）も適した材料であり、さらに可視光の透過率や導電率を高めるためにガリウム（Ga）を添加したものを用いることもできる。

40

【0053】

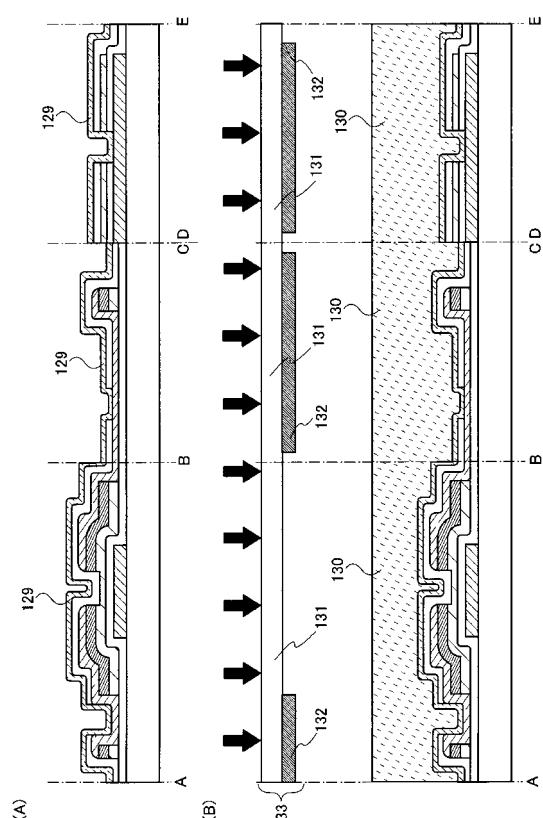

次いで、図10（B）に示すように全面にレジスト130を形成する。そして、透光性の基板131に透過部と金属膜から成る遮光部132が設けられた第4のフォトマスク133を用いて、フォトリソグラフィー工程を行う。図10（B）に示される矢印は照射される露光の光をイメージしており、露光の光は第4のフォトマスク133を通過した後、レジスト130に照射される。露光及び現像工程を経て、フォトレジストパターン134を形成する（図11（A）参照）。

【0054】

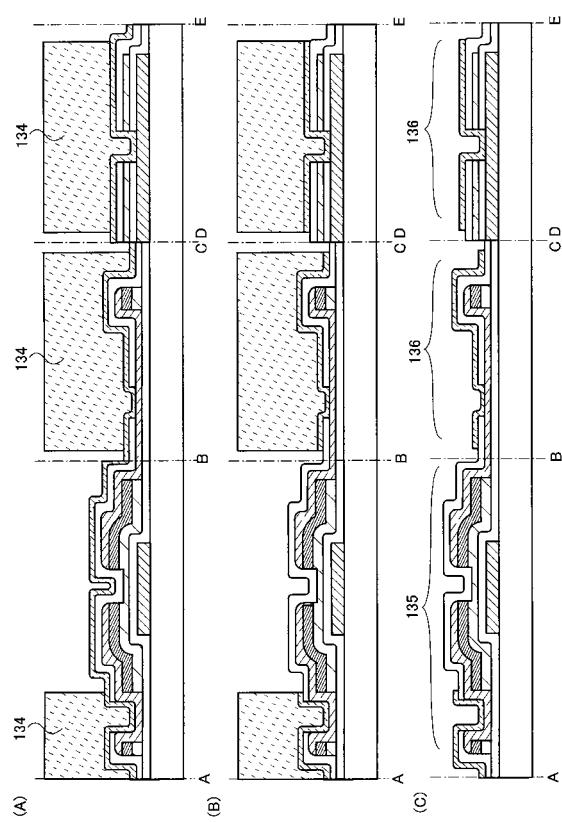

次いで、フォトレジストパターン134を用いて、透明導電膜129の不要な部分をエッティングによって除去することでパターニングを行う（図11（B）参照）。フォトレジ

50

ストパターン 134 を剥離することによって、図 11 (C) に示す状態を得る。透明導電膜 129 は、画素部においては画素電極として機能し、端子部においては他の基板に設けられた回路の配線と電気的に接続するための電極として機能する。

【0055】

このように、本実施の形態では 4 枚のフォトマスクを使用して、逆スタガ型の TFT を有する画素部 135 と端子部 136 を完成させることができる。そして、これらを個々の画素に対応してマトリクス状に配置して画素部を構成することによりアクティブマトリクス型の電気光学装置を作製するための一方の基板（以下 TFT 基板という）とすることができる。

【0056】

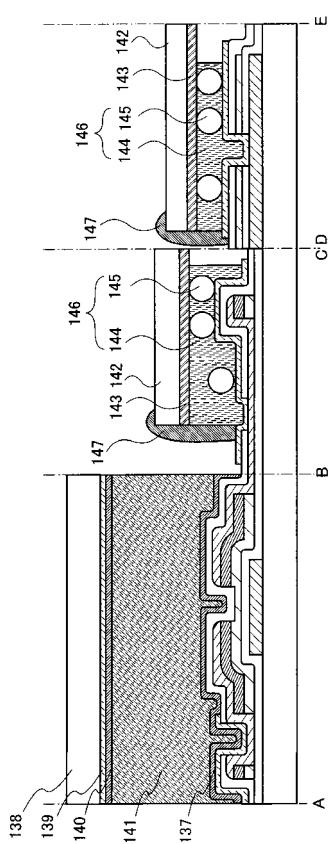

次いで、図 12 に示すように、画素部にのみポリイミド樹脂等から成る配向膜 137 を選択的に形成する。配向膜 137 を選択的に形成する方法としては、スクリーン印刷法を用いても良いし、フォトレジストパターンを形成するフォトリソグラフィー工程を用いても良い。そして、配向膜 137 にラビング処理を施して、後の工程において設けられる液晶分子がある一定のプレチルト角を持って配向するようにする。

【0057】

次いで、TFT 基板と、対向電極 139 と配向膜 140 とが設けられた対向基板 138 とをスペーサ（図示しない）で基板間隔を保持しながらシール材（図示しない）により貼り合わせた後、TFT 基板と対向基板との間に液晶 141 を注入し、注入口（図示しない）は樹脂材料で封止する。液晶 141 を設ける方法としては、上述のような注入方法でも構わないし、TFT 基板と対向基板とを貼り合わせる前に液晶を滴下する滴下方法を用いても良い。

【0058】

次いで、端子部にフレキシブルプリント基板（FPC）を接続する。FPC はポリイミド等の有機樹脂フィルム 142 に銅配線 143 が形成されていて、異方性導電性接着剤 146 によって端子部を覆う透明導電膜 129 と接続する。異方性導電性接着剤 146 は接着剤 144 と導電性粒子 145 から構成される。導電性粒子 145 は金等のメッキが施された数十  $\mu\text{m}$  ~ 数百  $\mu\text{m}$  径の導電性表面を有する粒子であり、この導電性粒子 145 が端子部を覆う透明導電膜と銅配線 143 とに接触することにより電気的な接続が実現される。さらに、この部分の機械的強度を高めるために樹脂層 147 を設ける。なお、図 12 で新たに示される構成要素については、図 1 では図示していない。

【0059】

以上の従来よりもフォトマスクの使用枚数を削減した工程を経て、アクティブマトリクス型の液晶表示装置を代表とする電気光学装置を完成させることができる。

【0060】

なお、本実施の形態においては、電気光学装置の代表の一つとして液晶表示装置について説明を行ったが、有機 EL 表示装置のような自発光表示装置にも適用できることはいうまでもない。

【0061】

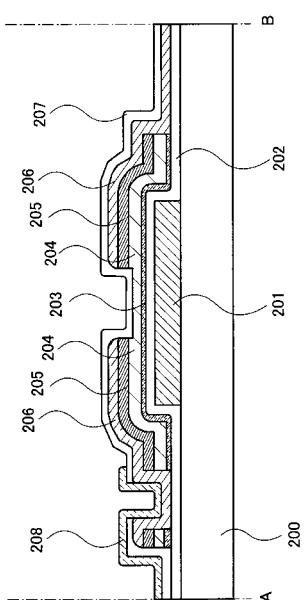

（実施の形態 2）

本実施の形態では、TFT のチャネル形成領域として機能する薄膜に微結晶半導体膜を用いる例について図 13 を用いて説明する。なお、図 13 では、図 1 の A-B 断面に対応する画素部についてのみ図示している。

【0062】

まず、実施の形態 1 に従って、基板 200 の上に第 1 のフォトマスクを用いて画素部のゲート電極 201 と端子部に延在するゲート配線を形成する。続いて、全面に絶縁膜 202 を成膜する。

【0063】

次いで、絶縁膜 202 上に微結晶半導体膜 203、第 1 の非晶質半導体膜 204、一導電型の不純物元素を含有する第 2 の非晶質半導体膜 205 を順に成膜する。なお、少なく

10

20

30

40

50

とも、絶縁膜202、微結晶半導体膜203、及び第1の非晶質半導体膜204を連続的に成膜することが好ましい。さらには、絶縁膜202、微結晶半導体膜203、第1の非晶質半導体膜204、及び一導電型の不純物元素を含有する第2の非晶質半導体膜205を連続的に成膜することが好ましい。少なくとも、絶縁膜202、微結晶半導体膜203、及び第1の非晶質半導体膜204を大気に触れさせることなく連続成膜することで、大気成分や大気中に浮遊する汚染不純物元素に汚染されることなく各積層界面を形成することができる、TFT特性のばらつきを低減することができる。

#### 【0064】

この微結晶半導体膜203は、非晶質と結晶構造（単結晶、多結晶を含む）の中間的な構造の半導体を含む膜である。この半導体は、自由エネルギー的に安定な第3の状態を有する半導体であって、短距離秩序を持ち格子歪みを有する結晶質なものであり、その粒径を0.5~20nmとして非単結晶半導体中に分散させて存在せしめることが可能である。微結晶半導体の代表例である微結晶シリコンは、そのラマンスペクトルが単結晶シリコンを示す520.6cm<sup>-1</sup>よりも低波数側にシフトしている。即ち、単結晶シリコンを示す520.6cm<sup>-1</sup>と非晶質シリコンを示す480cm<sup>-1</sup>の間に微結晶シリコンのラマンスペクトルのピークがある。また、未結合手（ダングリングボンド）を終端するため水素またはハロゲンを少なくとも1原子%またはそれ以上含ませている。さらに、ヘリウム（He）、アルゴン（Ar）、クリプトン（Kr）、ネオン（Ne）等の希ガス元素を含ませて格子歪みをさらに助長させることで、安定性が増し良好な微結晶半導体膜203が得られる。このような微結晶半導体膜に関する記述は、例えば、米国特許4,409,134号で開示されている。

#### 【0065】

また、微結晶半導体膜203は、周波数が数十MHz~数百MHzの高周波プラズマCVD装置、または周波数が1GHz以上のマイクロ波プラズマCVD装置により成膜することができる。代表的には、SiH<sub>4</sub>、Si<sub>2</sub>H<sub>6</sub>、SiH<sub>2</sub>Cl<sub>2</sub>、SiHCl<sub>3</sub>、SiCl<sub>4</sub>、SiF<sub>4</sub>等の水素化シリコン又はハロゲン化シリコンを水素で希釈して成膜することができる。また、これらに加え、ヘリウム（He）、アルゴン（Ar）、クリプトン（Kr）、ネオン（Ne）から選ばれた一種または複数種の希ガス元素で希釈して微結晶半導体膜203を成膜することができる。これらのときの水素化シリコン又はハロゲン化シリコンに対して水素の流量比を5倍以上200倍以下、好ましくは50倍以上150倍以下、更に好ましくは100倍とする。

#### 【0066】

また、微結晶半導体膜203は、価電子制御を目的とした不純物元素を意図的に添加しないときに弱いn型の電気伝導性を示すので、TFTのチャネル形成領域として機能する微結晶半導体膜203に対しては、p型を付与する不純物元素を、成膜と同時に、或いは成膜後に添加することで、しきい値制御をすることが可能となる。p型を付与する不純物元素としては、代表的には硼素であり、B<sub>2</sub>H<sub>6</sub>、BF<sub>3</sub>等の不純物気体を1ppm~1000ppm、好ましくは1~100ppmの割合で水素化シリコン又はハロゲン化シリコンに混入させると良い。そしてボロン（B）の濃度を、例えば1×10<sup>-4</sup>~6×10<sup>-6</sup>atoms/cm<sup>3</sup>とすると良い。

#### 【0067】

また、微結晶半導体膜203の酸素濃度を、5×10<sup>-9</sup>atoms/cm<sup>3</sup>以下、好ましくは1×10<sup>-9</sup>atoms/cm<sup>3</sup>以下、窒素及び炭素の濃度を5×10<sup>-8</sup>atoms/cm<sup>3</sup>以下とすることが好ましい。酸素、窒素、及び炭素が微結晶半導体膜203に混入する濃度を低減することで、微結晶半導体膜203がn型になることを防止することができる。

#### 【0068】

また、微結晶半導体膜203は、0nmより厚く50nm以下、好ましくは0nmより厚く20nm以下で成膜する。微結晶半導体膜203は後に形成されるTFTのチャネル形成領域として機能する。微結晶半導体膜203の厚さを上記の範囲内とすることで、後

10

20

30

40

50

に形成されるTFTは、完全空乏型となる。また、微結晶半導体膜203は微結晶で構成されているため、非晶質半導体膜と比較して抵抗が低い。このため、微結晶半導体膜203を用いたTFTは、電流電圧特性を示す曲線の立ち上がり部分の傾きが急峻となり、スイッチング素子としての応答性が優れ、高速動作が可能となる。また、TFTのチャネル形成領域に微結晶半導体膜203を用いることで、TFTの閾値の変動を抑制することができる。このため、電気特性のばらつきの少ない電気光学装置を作製することができる。

#### 【0069】

また、微結晶半導体膜203は非晶質半導体膜と比較して移動度が高い。このため、表示素子のスイッチングとして、チャネル形成領域が微結晶半導体膜203で形成されるTFTを用いることで、チャネル形成領域の面積、即ちTFTの面積を縮小することが可能である。このため、一画素あたりに示すTFTの面積が小さくなり、画素の開口率を高めることができる。この結果、解像度の高い電気光学装置を作製することができる。

#### 【0070】

第1の非晶質半導体膜204は、 $\text{SiH}_4$ 、 $\text{Si}_2\text{H}_6$ 、 $\text{SiH}_2\text{Cl}_2$ 、 $\text{SiHCl}_3$ 、 $\text{SiCl}_4$ 、 $\text{SiF}_4$ 等の水素化シリコン気体又はハロゲン化シリコン気体を用いて、プラズマCVD法により成膜することができる。また、上記気体に、ヘリウム(He)、アルゴン(Arg)、クリプトン(Kr)、ネオン(Ne)から選ばれた一種または複数種の希ガス元素で希釈して第1の非晶質半導体膜204を成膜することができる。水素化シリコン又はハロゲン化シリコンの流量は1倍以上5倍未満の流量の水素を用いて、水素を含む第1の非晶質半導体膜204を成膜することができる。また、上記気体と窒素またはアンモニアとを用いることで、窒素を含む第1の非晶質半導体膜204を成膜することができる。また、上記気体と、フッ素または塩素を含む気体( $\text{F}_2$ 、 $\text{Cl}_2$ 、 $\text{HF}$ 、 $\text{HCl}$ 等)を用いることで、フッ素または塩素を含む第1の非晶質半導体膜204を成膜することができる。

#### 【0071】

また、第1の非晶質半導体膜204は、ターゲットに非晶質半導体を用いて水素、または希ガスでスパッタリングして成膜することができる。このとき、アンモニア、窒素、または $\text{N}_2\text{O}$ を雰囲気中に含ませることにより、窒素を含む第1の非晶質半導体膜204を成膜することができる。また、雰囲気中にフッ素または塩素を含む気体( $\text{F}_2$ 、 $\text{Cl}_2$ 、 $\text{HF}$ 、 $\text{HCl}$ 等)を含ませることにより、フッ素または塩素を含む第1の非晶質半導体膜204を成膜することができる。

#### 【0072】

また、第1の非晶質半導体膜204として、微結晶半導体膜203の表面にプラズマCVD法またはスパッタリング法により第1の非晶質半導体膜204を成膜した後、第1の非晶質半導体膜204の表面を水素プラズマ、窒素プラズマ、またはハロゲンプラズマで処理して、第1の非晶質半導体膜204の表面を水素化、窒素化、またはハロゲン化してもよい。

#### 【0073】

この第1の非晶質半導体膜204は、結晶粒を含まない非晶質半導体膜で成膜することが好ましい。このため、周波数が数十MHz～数百MHzの高周波プラズマCVD法、またはマイクロ波プラズマCVD法で成膜する場合は、結晶粒を含まない非晶質半導体膜となるように、成膜条件を制御することが好ましい。

#### 【0074】

また、第1の非晶質半導体膜204は、後の工程において、一部エッチングされるため、そのときに、第1の非晶質半導体膜204の一部が残存する厚さで成膜することが好ましい。代表的には、10nm以上100nm以下の厚さで成膜することが好ましい。

#### 【0075】

微結晶半導体膜203の表面に、第1の非晶質半導体膜204を成膜することで、微結晶半導体膜203に含まれる結晶粒の表面の自然酸化を防止することが可能である。特に

10

20

30

40

50

、非晶質半導体と微結晶粒が接する領域では、結晶格子の歪に由来し、亀裂が入りやすい。この亀裂が酸素に触れると結晶粒は酸化され、酸化シリコンが形成される。しかしながら、微結晶半導体膜203の表面に第1の非晶質半導体膜204を成膜することで、微結晶粒の酸化を防ぐことができる。

【0076】

また、第1の非晶質半導体膜204は、非晶質半導体、または、水素、窒素、若しくはハロゲンを含む非晶質半導体で成膜するため、チャネル形成領域として機能する微結晶半導体膜203よりも抵抗が高い。このため、後に形成されるTFTにおいて、一導電型の不純物元素を含有する第2の非晶質半導体膜205と、微結晶半導体膜203との間に成膜される第1の非晶質半導体膜204は高抵抗領域として機能する。このため、TFTのオフ電流を低減することができる。このようなTFTを電気光学装置のスイッチング素子として用いた場合、液晶表示装置等のコントラストを向上させることができる。10

【0077】

一導電型の不純物元素を含有する第2の非晶質半導体膜205は、n型のTFTを形成する場合には、代表的な不純物元素としてリン(P)を添加すれば良く、水素化シリコン等にPH<sub>3</sub>等の不純物気体を加えれば良い。一導電型の不純物元素を含有する第2の非晶質半導体膜205は膜厚2~50nm(好ましくは10~30nm)とすれば良い。

【0078】

次いで、実施の形態1に従って、第2のフォトマスクを用いて形成される第2のフォトレジストパターンをマスクとして、微結晶半導体膜203、第1の非晶質半導体膜204、及び一導電型の不純物元素を含有する第2の非晶質半導体膜205のエッチングを行う。続けて、実施の形態1と同様の手法によって、新たなフォトマスクを用い、第2のフォトレジストパターンを加工することによって第3のフォトレジストパターンを形成し、第3のフォトレジストパターンも含めた基板全面に導電膜を成膜し、第3のフォトレジストパターンと第3のフォトレジストパターン上に形成された導電膜を同時に除去することで、エッチング工程を行うことなく画素部のソース電極及びドレイン電極206と端子部に延在するソース配線を形成する。20

【0079】

以下、実施の形態1に従って、第3のフォトマスク及び第4のフォトマスクを用いて、合計4枚のフォトマスクによって、チャネル形成領域に微結晶半導体膜203を用いた逆スタガ型のTFTを完成させることができる。なお、図13において、207は絶縁膜、208は透明導電膜を示している。30

【0080】

(実施の形態3)

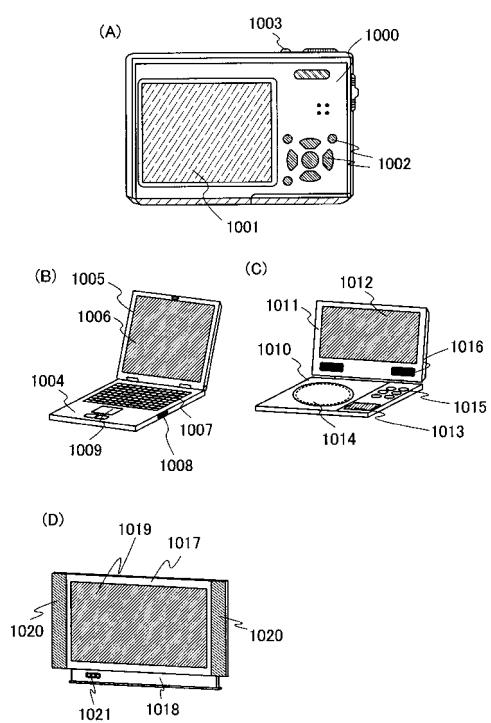

本発明の半導体装置及び電子機器として、ビデオカメラ、デジタルカメラ、ゴーグル型ディスプレイ(ヘッドマウントディスプレイ)、ナビゲーションシステム、音響再生装置(カーオーディオ、オーディオコンポ等)、ノート型パーソナルコンピュータ、ゲーム機器、携帯情報端末(モバイルコンピュータ、携帯電話、携帯型ゲーム機又は電子書籍等)、記録媒体を備えた画像再生装置(具体的にはDigital Versatile Disc(DVD)等の記録媒体を再生し、その画像を表示しうるディスプレイを備えた装置)などが挙げられる。それら電子機器の具体例を図14及び図15に示す。40

【0081】

図14(A)はデジタルカメラであり、本体1000、表示部1001、撮像部、操作キー1002、シャッターボタン1003等を含む。なお、図14(A)は表示部1001側からの図であり、撮像部は示していない。本発明により、より安価な表示部を有するデジタルカメラが実現できる。

【0082】

図14(B)はノート型パーソナルコンピュータであり、本体1004、筐体1005、表示部1006、キーボード1007、外部接続ポート1008、ポインティングデバイス1009等を含む。本発明により、より安価な表示部を有するノート型パーソナルコンピュータ50

ンピュータを実現することができる。

**【0083】**

図14(C)は記録媒体を備えた携帯型の画像再生装置(具体的にはDVD再生装置)であり、本体1010、筐体1011、第1の表示部1012、第2の表示部1013、記録媒体(DVD等)読込部1014、操作キー1015、スピーカ部1016等を含む。第1の表示部1012は主として画像情報を表示し、第2の表示部1013は主として文字情報を表示する。なお、記録媒体を備えた画像再生装置には家庭用ゲーム機器なども含まれる。本発明により、安価な表示部を有する画像再生装置を実現することができる。

**【0084】**

また、図14(D)は表示装置であり、筐体1017、支持台1018、表示部1019、スピーカ1020、ビデオ入力端子1021などを含む。この表示装置は、上述した実施の形態で示した作製方法により形成したTFTをその表示部1019及び駆動回路に用いることにより作製される。なお、表示装置には液晶表示装置、発光装置などがあり、具体的には薄型テレビ、パソコン用コンピュータ、広告表示などの全ての情報表示用表示装置が含まれる。本発明により、安価な表示部を有する表示装置、特に22インチ~50インチの大画面を有する大型の表示装置を実現することができる。

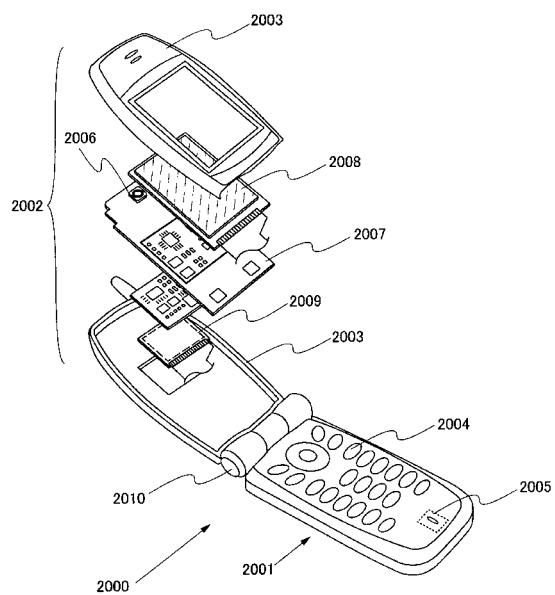

**【0085】**

また、図15で示す携帯電話機2000は、操作スイッチ類2004、マイクロフォン2005などが備えられた本体(A)2001と、表示パネル(A)2008、表示パネル(B)2009、スピーカ2006等が備えられた本体(B)2002とが、蝶番2010で開閉可能に連結されている。表示パネル(A)2008と表示パネル(B)2009は、回路基板2007と共に本体(B)2002の筐体2003の中に収納される。表示パネル(A)2008及び表示パネル(B)2009の画素部は筐体2003に形成された開口窓から視認できるように配置される。

**【0086】**

表示パネル(A)2008と表示パネル(B)2009は、その携帯電話機2000の機能に応じて画素数などの仕様を適宜設定することができる。例えば、表示パネル(A)2008を主画面とし、表示パネル(B)2009を副画面として組み合わせができる。

**【0087】**

本発明により、安価な表示部を有する携帯電話機を実現することができる。

**【0088】**

本実施の形態に係る携帯電話機2000は、その機能や用途に応じてさまざまな態様に変容し得る。例えば、蝶番2010の部位に撮像素子を組み込んで、カメラ付きの携帯電話機としても良い。また、操作スイッチ類2004、表示パネル(A)2008、表示パネル(B)2009を一つの筐体内に納めた構成としても、上記した作用効果を奏することができる。また、表示部を複数個そなえた情報表示端末に本実施の形態の構成を適用しても、同様な効果を得ることができる。

**【0089】**

以上の様に、本発明を実施する、即ち実施の形態1及び2のいずれか一の作製方法を用いて、様々な電子機器を完成させることができる。

**【産業上の利用可能性】**

**【0090】**

本発明は、アクティブマトリクス型の液晶表示装置に代表される電気光学装置の分野において、逆スタガ型のTFTを有する画素部及び端子部の作製に関して、透光性基板に透過部と光強度を低減する機能を有する中間透過部と遮光部が設けられたフォトマスク(多階調フォトマスク)を採用する。さらには、画素部のソース電極及びドレイン電極と端子部に延在するソース配線のパターニングにリフトオフ方法を採用する。これにより、従来必要であったフォトマスクの枚数(最低5枚以上)を削減することができ、さらには画素部のソース電極及びドレイン電極と端子部に延在するソース配線のパターニングのための

10

20

30

40

50

エッチング工程も省略することができるため、電気光学装置の生産性、歩留まりを向上させ、製造コストの低減を実現することができる。

【図面の簡単な説明】

【0091】

【図1】本発明によって作製される半導体装置の上面図。

【図2】本発明によって作製される半導体装置の作製工程を示す断面図。

【図3】本発明によって作製される半導体装置の作製工程を示す断面図。

【図4】本発明によって作製される半導体装置の作製工程を示す断面図。

【図5】本発明によって作製される半導体装置の作製工程を示す断面図。

【図6】本発明によって作製される半導体装置の作製工程を示す断面図。

10

【図7】本発明によって作製される半導体装置の作製工程を示す断面図。

【図8】本発明によって作製される半導体装置の作製工程を示す断面図。

【図9】本発明によって作製される半導体装置の作製工程を示す断面図。

【図10】本発明によって作製される半導体装置の作製工程を示す断面図。

【図11】本発明によって作製される半導体装置の作製工程を示す断面図。

【図12】本発明によって作製される半導体装置の作製工程を示す断面図。

【図13】本発明によって作製される半導体装置の作製工程を示す断面図。

【図14】電子機器の一例を示す図。

【図15】電子機器の一例を示す図。

【符号の説明】

20

【0092】

100 基板

101 導電膜

102 レジスト

103 基板

104 遮光部

105 第1のフォトマスク

106 フォトレジストパターン

107 ゲート配線

108 絶縁膜

30

109 第1の非晶質半導体膜

110 第2の非晶質半導体膜

111 レジスト

112 基板

113 中間透過部

114 遮光部

115 第2のフォトマスク

116 フォトレジストパターン

117 フォトレジストパターン

118 導電膜

40

119 ソース配線

120 レジスト

121 フォトレジストパターン

122 絶縁膜

123 レジスト

124 基板

125 遮光部

126 第3のフォトマスク

127 フォトレジストパターン

128 開口部

50

|         |                     |    |

|---------|---------------------|----|

| 1 2 9   | 透明導電膜               |    |

| 1 3 0   | レジスト                |    |

| 1 3 1   | 基板                  |    |

| 1 3 2   | 遮光部                 |    |

| 1 3 3   | 第4のフォトマスク           |    |

| 1 3 4   | フォトレジストパターン         |    |

| 1 3 5   | 画素部                 |    |

| 1 3 6   | 端子部                 |    |

| 1 3 7   | 配向膜                 |    |

| 1 3 8   | 対向基板                | 10 |

| 1 3 9   | 対向電極                |    |

| 1 4 0   | 配向膜                 |    |

| 1 4 1   | 液晶                  |    |

| 1 4 2   | 有機樹脂フィルム            |    |

| 1 4 3   | 銅配線                 |    |

| 1 4 4   | 接着剤                 |    |

| 1 4 5   | 導電性粒子               |    |

| 1 4 6   | 異方性導電性接着剤           |    |

| 1 4 7   | 樹脂層                 |    |

| 1 5 7   | ゲート電極               | 20 |

| 1 5 9   | ソース電極及びドレイン電極       |    |

| 2 0 0   | 基板                  |    |

| 2 0 1   | ゲート電極               |    |

| 2 0 2   | 絶縁膜                 |    |

| 2 0 3   | 微結晶半導体膜             |    |

| 2 0 4   | 第1の非晶質半導体膜          |    |

| 2 0 5   | 第2の非晶質半導体膜          |    |

| 2 0 6   | ソース電極及びドレイン電極       |    |

| 2 0 7   | 絶縁膜                 |    |

| 2 0 8   | 透明導電膜               | 30 |

| 1 0 0 0 | 本体                  |    |

| 1 0 0 1 | 表示部                 |    |

| 1 0 0 2 | 操作キー                |    |

| 1 0 0 3 | シャッターボタン            |    |

| 1 0 0 4 | 本体                  |    |

| 1 0 0 5 | 筐体                  |    |

| 1 0 0 6 | 表示部                 |    |

| 1 0 0 7 | キーボード               |    |

| 1 0 0 8 | 外部接続ポート             |    |

| 1 0 0 9 | ポインティングデバイス         | 40 |

| 1 0 1 0 | 本体                  |    |

| 1 0 1 1 | 筐体                  |    |

| 1 0 1 2 | 第1の表示部              |    |

| 1 0 1 3 | 第2の表示部              |    |

| 1 0 1 4 | 記録媒体( D V D 等 ) 読込部 |    |

| 1 0 1 5 | 操作キー                |    |

| 1 0 1 6 | スピーカ部               |    |

| 1 0 1 7 | 筐体                  |    |

| 1 0 1 8 | 支持台                 |    |

| 1 0 1 9 | 表示部                 | 50 |

- 1 0 2 0 スピーカ

1 0 2 1 ビデオ入力端子

2 0 0 0 携帯電話機

2 0 0 1 本体 (A)

2 0 0 2 本体 (B)

2 0 0 3 筐体

2 0 0 4 操作スイッチ類

2 0 0 5 マイクロフォン

2 0 0 6 スピーカ

2 0 0 7 回路基板

2 0 0 8 表示パネル (A)

2 0 0 9 表示パネル (B)

2 0 1 0 蝶番

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図 1 5】

---

フロントページの続き

| (51)Int.Cl.              | F I          |   |

|--------------------------|--------------|---|

| H 01 L 29/49 (2006.01)   | H 01 L 21/88 | C |

| H 01 L 21/3213 (2006.01) | H 01 L 21/88 | G |

| H 01 L 21/768 (2006.01)  |              |   |

| H 01 L 21/3205 (2006.01) |              |   |

(56)参考文献 特開2008-010810 (JP, A)

特開2002-026011 (JP, A)

特開平09-127707 (JP, A)

特開2001-324725 (JP, A)

特開2007-165860 (JP, A)

特開2005-322845 (JP, A)

## (58)調査した分野(Int.Cl., DB名)

H 01 L 21 / 28 - 21 / 288

H 01 L 21 / 3205 - 21 / 3213

H 01 L 21 / 329

H 01 L 21 / 336

H 01 L 21 / 44 - 21 / 445

H 01 L 21 / 768

H 01 L 23 / 522

H 01 L 23 / 532

H 01 L 29 / 40 - 29 / 49

H 01 L 29 / 786

H 01 L 29 / 872