(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2013-120858

(P2013-120858A)

(43) 公開日 平成25年6月17日(2013.6.17)

(51) Int.Cl.

**H01L 23/532 (2006.01)**

**H01L 21/768 (2006.01)**

**H01L 21/3205 (2006.01)**

**H01L 21/285 (2006.01)**

**H01L 21/28 (2006.01)**

F 1

H01L 21/88

H01L 21/285

H01L 21/28

H01L 21/28

C23C 14/34

テーマコード(参考)

4K029

4M104

5F033

S

審査請求 未請求 請求項の数 6 O L (全 10 頁) 最終頁に続く

(21) 出願番号

(22) 出願日特願2011-268331 (P2011-268331)

平成23年12月7日 (2011.12.7)

(71) 出願人

000231464

株式会社アルパック

神奈川県茅ヶ崎市萩園2500番地

(74) 代理人

110000305

特許業務法人青義

(72) 発明者

中村 真也

静岡県裾野市須山1220-14 株式会社アルパック富士裾野工場内

(72) 発明者

濱口 純一

静岡県裾野市須山1220-1 株式会社アルパック半導体電子技術研究所内

(72) 発明者

武田 直樹

静岡県裾野市須山1220-14 株式会社アルパック富士裾野工場内

最終頁に続く

(54) 【発明の名称】 Cu層形成方法及び半導体装置の製造方法

## (57) 【要約】

【課題】微細な凹部の内部に、隙間無く導電材料たるCuを埋め込み形成でき、導電性に優れた配線を生産性よく得ることに最適なCu膜形成方法を提供する。

【解決手段】被処理物11の表面に形成された凹部16にCuを埋め込み形成する本発明のCu層形成方法は、凹部16の内面を含む被処理物表面にCu膜17を形成する第1工程と、このCu膜をリフロー処理により流動させて凹部内をCuで埋め込む第2工程とを含み、第2工程の途中でCu原子やCuイオンを被処理物表面に供給する。

## 【選択図】図1

## 【特許請求の範囲】

## 【請求項 1】

被処理物の表面に形成された凹部に Cu を埋め込み形成する Cu 層形成方法において、前記凹部の内面を含む被処理物表面に Cu 膜を形成する第 1 工程と、この Cu 膜をリフロー処理により流動させて凹部内を Cu で埋め込む第 2 工程とを含み、

前記第 2 工程の途中で前記 Cu 原子及び Cu イオンの少なくとも一方を被処理物表面に供給することを特徴とする Cu 層形成方法。

## 【請求項 2】

前記 Cu 原子及び Cu イオンの少なくとも一方の被処理物表面への供給速度を、前記 Cu 層のリフロー処理時の流動速度より遅くすることを特徴とする請求項 1 記載の Cu 層形成方法。

## 【請求項 3】

前記 Cu 原子及び Cu イオンの少なくとも一方の被処理物表面への供給を、Cu をターゲットとするスパッタリング法にて行うことを特徴とする請求項 1 または請求項 2 記載の Cu 層形成方法

## 【請求項 4】

前記第 2 工程を、100 ~ 300 の温度範囲で行うことを特徴とする請求項 1 ~ 3 のいずれか 1 項に記載の Cu 層形成方法。

## 【請求項 5】

請求項 1 ~ 4 のいずれか 1 項に記載の Cu 層形成方法を利用した半導体装置の製造方法であって、

被処理物を半導体基板の一方の面側に有する絶縁膜中に形成した溝部とし、この被処理物を真空中で加熱する脱ガス工程と、

前記被処理物を水素プラズマに曝して不純物を除去する不純物除去工程と、

前記溝部内面にバリア層を形成するバリア層形成工程と、を含み、このバリア層が形成された溝部を凹部とし、上記 Cu 層形成方法を実施することを特徴とする半導体装置の製造方法。

## 【請求項 6】

前記バリア膜は、Ta, Ti, W, Ru, V, Co, Nb のうち、少なくとも一種を含む材料で構成されることを特徴とする請求項 5 項記載の半導体装置の製造方法。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、Cu 層形成方法及び半導体装置の製造方法に関し、より詳しくは、半導体基板の一方の面に形成された溝部(トレンチ)に効率よく微細な Cu 配線層を形成するためのものに関する。

## 【背景技術】

## 【0002】

近年では、融点が高く、しかも、耐マイグレーション性に優れる等の理由から、半導体装置の配線材料として、Cu(銅)が注目されている。従来、シリコンウエハ等の半導体基板の一方の面に有する絶縁膜中の溝部(トレンチ)内面(内壁面)にバリア膜を形成した後、当該溝部内にスパッタリング法にて Cu を埋め込み、その後、溝部から上方にはみ出した余分な Cu を除去して Cu 配線層を得る方法は、例えば特許文献 1 で知られている。このものでは、溝部内に隙間無く Cu を埋め込むことが困難であるという課題がある。つまり、スパッタリング法で Cu 層を形成すると、溝部内まで Cu が付着して堆積せず、溝部内に、空洞(ボイド)のまま溝部の上側の開口端付近だけに Cu が堆積してしまう(所謂、オーバーハング)。

## 【0003】

他方、バリア膜で覆われた溝部内面を覆うようにスパッタリング法にて Cu を付着、堆

積させ、リフロー処理によりこの堆積させたCuを流動させて溝部内をCuで埋め込み、Cu配線層を得ることが知られている（例えば、特許文献2参照）。然し、この従来例の方法では、金属または金属化合物からなるバリア膜とCuとの濡れ性がよく、かつ、密着性が高いので、リフロー処理時、特にバリア膜側のCuが流動し難くなる。結果として、溝部内での流動性が異なることで埋め込み特性が悪化、つまり、トレンチ内部に空洞が生じた状態でCuが固化するという不具合が生じる。

#### 【0004】

このように溝部内に形成したCu配線層に空洞が生じていると、銅配線の抵抗値が高くなり、断線の虞がある。そこで、溝部内に空洞が残らないように真空雰囲気内で上記処理を複数回繰り返すことが考えられるが、これでは生産性が悪い。しかも、Cuを流動させる際、400以上に加熱することが必要であり、半導体基板に形成した素子が熱でダメージを受ける虞もある。

10

#### 【先行技術文献】

#### 【特許文献】

#### 【0005】

【特許文献1】特公平6-103681号公報

【特許文献2】特開2008-71850号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0006】

本発明は、以上の点に鑑み、微細な凹部の内部に、隙間無く導電材料たるCuを埋め込み形成でき、導電性に優れた配線層を生産性よく得ることに最適なCu膜形成方法及び半導体装置の製造方法を提供することをその課題とするものである。

20

#### 【課題を解決するための手段】

#### 【0007】

上記課題を解決するために、被処理物の表面に形成された凹部にCuを埋め込む本発明のCu層形成方法は、前記凹部の内面を含む被処理物の表面にCu膜を形成する第1工程と、このCu膜をリフロー処理により流動させて凹部内をCuで埋め込む第2工程とを含み、前記第2工程の途中で前記Cu原子及びCuイオンの少なくとも一方を基材表面に供給することを特徴とする。

30

#### 【0008】

本発明によれば、リフロー処理時、凹部の内面でのCuの流動性が異なる場合でも、その途中で前記Cu原子及びCuイオンの少なくとも一方を供給するようにしたため、予め形成された被処理物から流動するCuに、Cu原子またはCuイオンが更に付着し、流動するCuと共に凹部内へと埋め込まれることで、一度のリフロー処理で、凹部内に空洞が生じることなくCuが埋め込まれていく。この場合、前記Cu原子及びCuイオンの少なくとも一方の被処理物表面への供給は、リフロー処理によりCuの流動が開始した後であれば、特に制限されないが、Cuの流動開始直後に被処理物表面への供給を開始することが好ましい。これにより、凹部が高アスペクト比のものであっても、上記従来例のものと比較して低い温度で、Cuが凹部の隅々まで空洞を生じることなく行き渡って、凹部に隙間無く導電材料たるCuを埋め込み形成でき、その結果、局所的な断線部分のない高精度なCuからなる導電体を得ることができる。

40

#### 【0009】

本発明において、Cuが凹部の隅々まで空洞を生じることなく確実に行き渡させるには、前記前記Cu原子及びCuイオンの少なくとも一方の被処理物表面への供給速度を、前記Cu層のリフロー処理時の流動速度より遅くすることが好ましい。この場合、流動速度は、リフロー時間と凹部（トレンチ）の深さを考慮して適宜設定され、また、供給速度は、例えば、所定の基板にCu原子またはCuイオンを供給して付着、堆積させたときの膜厚と成膜時間から定まるレートを基に決定すればよい。

#### 【0010】

50

また、本発明において、強い直進性を持ってCu原子またはCuイオンを被処理物、ひいては、流動するCuに供給するために、前記Cu原子及びCuイオンの少なくとも一方を、Cuをターゲットとするスパッタリング法にて行なうことが好ましい。なお、前記第2工程を、100～300の温度範囲で行なえば、Cuが凹部の隅々まで空洞を生じることなく確実に行き渡らせることが確認された。

## 【0011】

また、上記課題を解決するために、請求項1～4のいずれか1項に記載のCu層形成方法を利用した本発明の半導体装置の製造方法は、被処理物を半導体基板の一方の面側に有する絶縁膜中に形成した溝部とし、この被処理物を真空中で加熱する脱ガス工程と、前記被処理物を水素プラズマに曝して不純物を除去する不純物除去工程と、前記溝部内面にバリア層を形成するバリア層形成工程と、を含み、このバリア層が形成された溝部を凹部とし、上記Cu層形成方法を実施することを特徴とする。

10

## 【0012】

これによれば、溝部内に、隙間無くかつ効率よく導電材料たるCuが埋め込まれ、導電性に優れた配線層を持つ半導体装置を得ることができる。この場合、バリア膜は、Ta, Ti, W, Ru, V, Co, Nbのうち、少なくとも一種を含む材料からなるものとすればよい。

## 【図面の簡単な説明】

## 【0013】

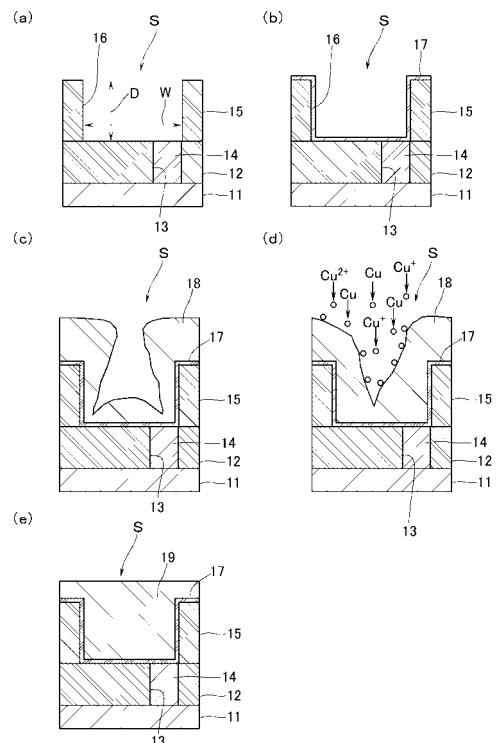

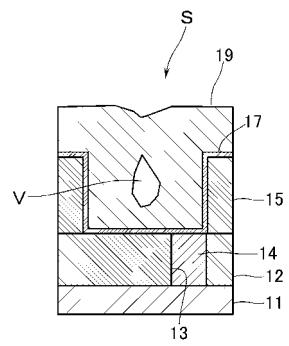

【図1】本発明のCu層形成方法を実施してCu配線層が形成される半導体装置の一例を示す拡大断面図。

20

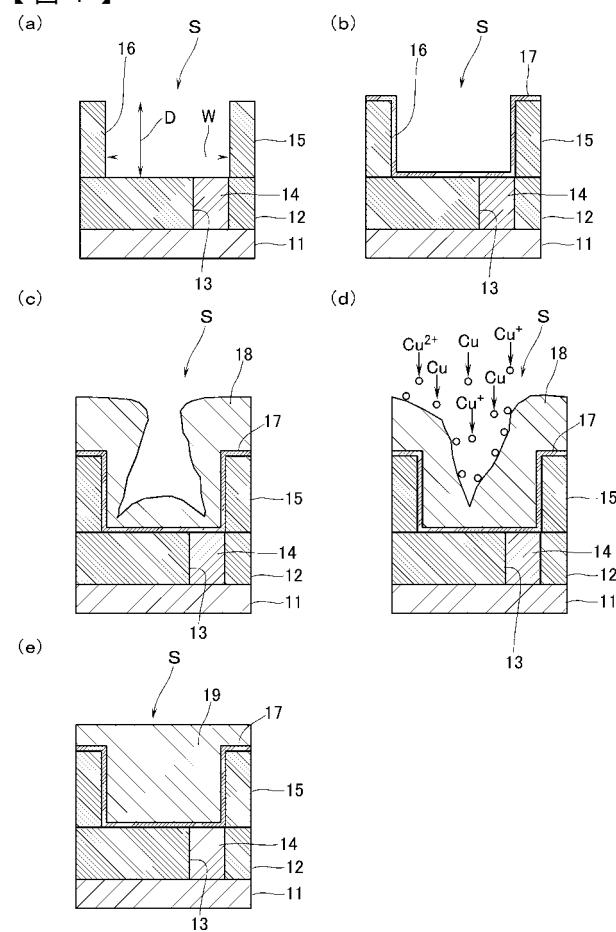

【図2】本発明の半導体装置の製造方法を実施する真空処理装置の構成を模式的に説明する図。

21

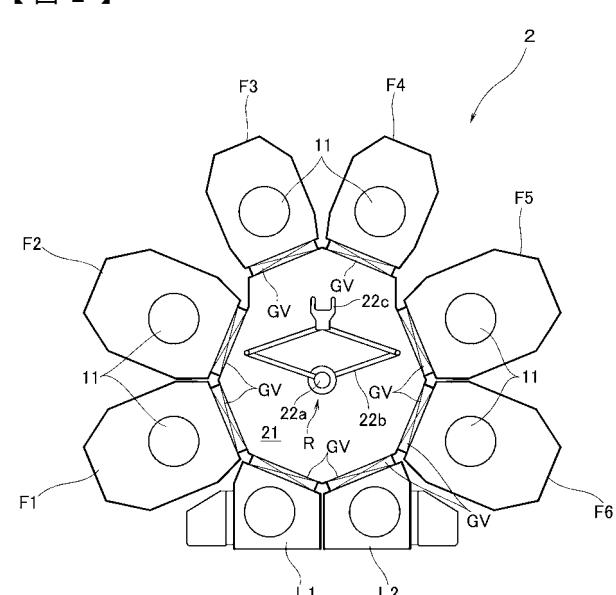

【図3】リフロー処理が実施される真空処理室の内部構造を模式的に説明する断面図。

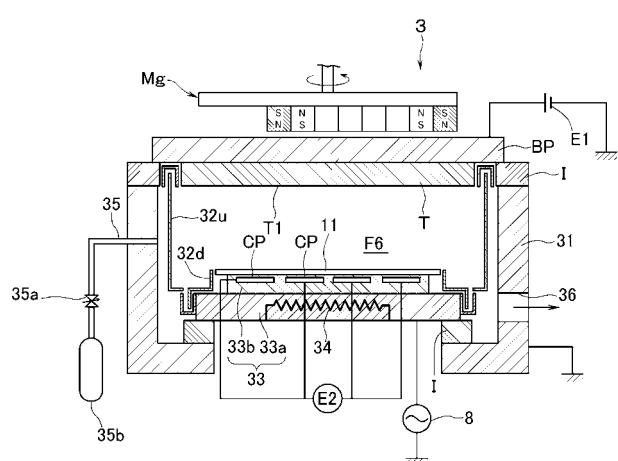

【図4】比較実験で得たCu配線層を模式的に示す断面図。

## 【発明を実施するための形態】

## 【0014】

以下、図面を参照して、被処理物を、シリコンウエハ等の半導体基板であってその表面に形成した絶縁膜中に凹部たる溝部(トレンチ)を形成したものとし、この溝部内にCu配線層を形成する場合を例に、本発明の実施形態のCu層形成方法及びこれを利用した半導体装置の製造方法を説明する。

30

## 【0015】

図1を参照して、Sは、本発明の実施形態の製造方法を実施してCu層が埋め込み形成される半導体装置である。半導体装置Sは、トランジスタ等の素子が形成されたシリコンウエハからなる基板11の素子形成面側に、例えばSiO<sub>2</sub>からなる層間絶縁膜12を形成した後、基板11に達する状態の接続孔13が形成され、接続孔13内に、例えばタンゲステンからなる配線層14が埋め込み形成される。その後、層間絶縁膜12上に、例えばSiO<sub>2</sub>からなる他の層間絶縁膜15が形成される。そして、層間絶縁膜15上に図示省略のレジストパターンが形成され、このレジストパターンをマスクとし、ドライエッチングにより層間絶縁膜15に、配線用の溝部16が形成される(図1(a)参照)。

40

## 【0016】

ここで、溝部16は、その底部の幅Wが例えば10nm～40nm程度になるように形成され、その深さDは、例えば80nm～100nm程度になるように形成されたものである。そして、このような溝部16の内部に、例えば半導体素子の配線材料となる導電体たるCuが埋め込み形成される。以下に、Cu層形成方法を具体的に説明する。

## 【0017】

図2を参照して、2は、Cu層形成方法を実施する真空処理装置を示している。真空処理装置2は、中央の搬送室21を備え、搬送室21には、上記基板11を搬送する搬送ロボットRが設置されている。搬送ロボットRは、回転及び上下動自在な回転軸22aと、回転軸22aの上端に連結した水平方向に伸縮自在なフロッギレッグ式の一対のロボット

50

アーム 22b と、両口ボットアーム 22b の先端に取り付けた、基板 11 を支持する口ボットハンド 22c とを備えている。

【0018】

搬送室 21 の周囲前側（図 2 中、下側）には、2 つのロードロック室 L1, L2 が左右対称に設けられている。そして、ロードロック室 L1, L2 を起点として反時計まわりに、脱ガス処理を行う第 1 真空処理室 F1 と、水素プラズマを用いたクリーニング処理を行う第 2 真空処理室 F2 と、基板 11 を冷却する第 3 真空処理室 F3 と、バリア膜の形成を行う第 4 真空処理室 F4 と、Cu シート層の形成を行う第 5 真空処理室 F5 と、リフロー処理を行う第 6 真空処理室 F6 とが配置されている。これら各ロードロック室 L1, L2 及び各処理室 F1 ~ F6 には、搬送口ボット R によりゲートバルブ GV を介して基板 11 が搬入、搬出される。

10

【0019】

ここで、第 1 真空処理室 F1 としては、特に図示して説明しないが、基板 11 を保持するステージと、基板を所定温度に加熱する赤外線ランプ等を備えたものが利用され、第 2 真空処理室 F2 としては、例えば誘導結合型のプラズマを発生させる機構を備えるものが利用され、第 3 真空処理室 F3 としては、基板が載置されるステージに冷媒循環機構を内蔵して熱交換で基板 11 を冷却するものが利用され、これらは、公知のものであるため、ここでは、詳細な説明を省略する。また、バリア膜の形成及び Cu シード層の形成（第 4 及び第 5 の真空処理室）には、公知の構造のマグネットロンスパッタリング装置が利用でき、これらもまた公知のものであるため、ここでは、成膜条件を含め、詳細な説明を省略する。なお、バリア膜の形成及び Cu シード層の形成方法を上記に限定されるものではなく、蒸着装置や CVD 装置を用いることもできる。

20

【0020】

図 3 を参照して、3 は、本実施形態の第 2 工程を実施する、第 6 真空処理室 F6 を構成するリフロー装置を示している。リフロー装置 3 は、第 6 真空処理室 F6 を画成する真空チャンバ 31 を備え、その天井部にはカソードユニットが取付けられている。以下においては、図 3 中、真空チャンバ 31 の天井部側を向く方向を「上」とし、その底部側を向く方向を「下」として説明する。

【0021】

カソードユニットは、ターゲット T と、このターゲット T の上方に配置された磁石ユニット Mg とから構成されている。ターゲット T は、Cu 製で、基板 11 の輪郭より大きな表面積でかつ公知の方法で平面視円形や矩形に形成されたものであり、バッキングプレート BP に装着した状態で、そのスパッタ面 T1 を下方にして絶縁体 I を介して真空チャンバ 31 の上部に取り付けられる。また、ターゲット T は、DC 電源 E1 に接続され、Cu 原子や Cu イオンを供給する際にターゲット T に負の電位を持った電力が投入される。

30

【0022】

ターゲット T の上方に配置される磁石ユニット Mg は、ターゲット T のスパッタ面 T1 の下方空間に磁場を発生させ、スパッタ時にスパッタ面 T1 の下方でのプラズマ密度を高める公知の閉鎖磁場若しくはカスプ磁場構造を有するものであり、ここでは詳細な説明を省略する。なお、磁石ユニット Mg は、一定の T - S 間距離の下、未使用状態のターゲット T にて、所定条件（圧力、ターゲット T への投入電力等）で基板 11 に対して成膜したときに、基板 11 表面における膜厚分布がその全面に亘って均等になるように設計されている。

40

【0023】

第 6 真空処理室 F6 内には、導電性を有するアノードシールド 32d, 32u が配置され、その底部には、ターゲット T に対向させてステージ 33 が絶縁体 I を介して設けられている。ステージ 33 は、熱伝導のよい金属製の基台 33a と、その上面に設けられた、正負のチャック電極 Cp, Cp を埋設したセラミックスプレート 33b とで構成され、正負のチャック電極 Cp, Cp に図外のチャック電源から所定の電圧を印加することで、セラミックスプレート 33b 表面に基板 11 が吸着保持される。また、基台 33a には、抵

50

抗加熱式ヒータ等の加熱手段34が内蔵され、ステージ33に吸着された基板11を所定温度（例えば、100～300）に加熱保持できるようになっている。なお、特に図示して説明しないが、ステージ33に高周波電源8を接続し、Cu原子やCuイオンを供給する際に基板11にバイアス電圧を印加する構造にしてもよい。

#### 【0024】

真空チャンバ31の側壁には、所定のガスを導入するガス管35が接続され、このガス管35がマスフローコントローラ35aを介してガス源35bに連通する。この場合、本実施形態では、アルゴンガスが導入されるようになっているが、窒素やヘリウム等の他の不活性ガスを用いることもできる。真空チャンバ31の側壁にはまた、ターボ分子ポンプやロータリーポンプなどからなる図示省略の真空排気装置に通じる排気管の接続口36が形成されている。

10

#### 【0025】

以下に、再び図1及び図2を参照して、本実施形態のCu層形成を具体的に説明する。以下では、基板11は、上記の如く、半導体装置Sとして層間絶縁膜15中に配線用の溝部16が形成されたものとし、基板11は、各処理が施された後のものを指す場合があるものとする。先ず、搬送口ボットRにより一方のロードロック室L1から第1真空処理室F1に未処理の基板11を搬送し、第1真空処理室F1で脱ガス処理を施す。この場合、脱ガス処理では、基板11を100～200に所定時間(1min)加熱保持する。そして、脱ガス処理済みの基板11を第2真空処理室F2に搬送し、水素プラズマでクリーニング処理を施す。そして、第3真空処理室F3にクリーニング済みの基板11を搬送し、基板11を100以下の温度まで冷却する。

20

#### 【0026】

冷却完了後、第4真空処理室F4に基板11を搬送し、溝部16の内面をその全体に亘って覆うように、スパッタリング法によりバリア層（バリアメタル）17が形成される（図1（b）参照）。バリア層17は、例えば、Ta（タンタル）窒化物、Ta珪化物、Ta炭化物、Ti（チタン）窒化物、Ti珪化物、Ti炭化物、W（タンゲステン）窒化物、W珪化物、W炭化物、Ru（ルテニウム）、およびRu酸化物、V（バナジウム）酸化物、Co（コバルト）酸化物、Nb（ニオブ）酸化物などから構成される。この場合、バリア層17をTaで構成する場合、その厚みが2nm～7nm程度になるように形成される。

30

#### 【0027】

バリア層17が形成されると、第5真空処理室F5にバリア層17形成済みの基板11を搬送し、バリア層17を覆うように、スパッタリング法によりCu膜（Cuシード層）18が形成される（図1（c）参照）。この場合、スパッタリングによる成膜中、基板11を、例えば室温以下の温度、好ましくは-20に保持する。これにより、膜中のグレインサイズが小さいCu膜を形成することができ、また、凝集を抑制できるという利点がある。Cu膜18が形成されると、第6真空処理室F6にCu膜形成済みの基板11を搬送し、リフロー処理が施される。

#### 【0028】

第6処理室F6では、先ず、基板11をステージ33上に吸着保持させた後、不活性ガス、好ましくはアルゴンガスを導入し、不活性ガス雰囲気中で加熱手段34を稼働して基板11を急速加熱する。この場合、第6真空処理室内の圧力が0.1Pa～0.2Paの範囲に設定され、また、昇温速度は、20～40/secの範囲、好ましくは40/secに設定される。この場合、基板温度を100～300の範囲、好ましくは基板11の面内平均温度が300となるように設定される。100より低い温度ではCuの流動が起きず、また、300より高い温度では、製品（素子）がダメージを受けるという問題が生じる。そして、基板11が上記温度に達すると、Cu膜18が流動し始める。

40

#### 【0029】

Cu膜18が流動し始めると、ターゲットTに所定電力（2kW～5kW）を投入し、

50

既に導入しているアルゴンガスのイオンでターゲットTをスパッタリングする。これにより、ターゲットTのスパッタリングで生じたCu原子やCu<sup>+</sup>、Cu<sup>2+</sup>といったCuイオンが、流動しているCu膜18に供給される(図1(d)参照)。この場合、ターゲットTのスパッタリングレートを、Cu膜の流動速度より低く設定する。基板温度を300

に設定する場合、スパッタリングレートは1nm/sec~2nm/secに設定すればよい。これにより、溝部16内にCuが隙間なく埋め込まれ、当該溝部18内にCu配線層19が形成される(図1(e)参照)。

#### 【0030】

上記実施形態によれば、リフロー処理時、溝部16の内面でのCuの流動性が異なる場合でも、その途中でスパッタリング法にて強い直進性を持ってCu原子またはCuイオンを供給するようにしたため、被処理物から流動するCu膜18に、Cu原子またはCuイオンが更に付着しながら流動するCu膜18と共に溝部16内へと埋め込まれることで、一度のリフロー処理で、凹部16内に空洞が生じることなくCuが埋め込まれていく。これにより、溝部16が高アスペクト比のものであっても、上記従来例のものと比較して低い温度で、Cuが溝部16の隅々まで空洞を生じることなく行き渡って、溝部16に隙間無く導電材料たるCuを埋め込み形成でき、その結果、局所的な断線部分のない高精度なCu配線層19が得られ、導電性に優れた配線を持つ半導体装置Sとなる。

10

#### 【0031】

ところで、上記のような真空処理装置2を用いる場合、いずれかの真空処理室F1~F6やロードロック室L1、L2でプロセス異常や搬送不良が生じた場合、異常のない各真空処理室F1~F6での処理が終了した後、大気開放を適宜行い、復帰操作が行われる。このとき、上記従来の如く、Cuシード層の形成とリフロー処理とを繰り返してCuを埋め込み形成する場合には、最終的にCuが埋め込まれた基板11のみが製品となり得るが、その他の基板11は製品不良として扱われる。それに対して、上記実施形態では、一度の処理でCuの埋め込み形成が行われるので、第6真空処理室F6でプロセス異常が生じた場合のみ製品不良となるだけで、製品歩留まりを高める上で有利である。

20

#### 【0032】

次に、上記効果を確認するために次の実験を行った。被処理物を、厚み0.775mmのシリコン酸化膜付シリコン基板11の一方の面に、フォトリソグラフィーによるエッチング加工により、深さ100nmの溝部をパターニング形成し、当該溝部の内壁面含むシリコン基板11表面に、スパッタリング法にて厚みの3nm~5nmのTaからなるバリア層17を形成したものとした。そして、公知のスパッタリング装置を用い、バリア層17を覆うように厚み15nmのCuからなるCu膜18を形成した。このとき、シリコン基板11の温度を-20に制御した。

30

#### 【0033】

以上の如く、溝部16にバリア層17及びCu膜18が形成されたシリコン基板11に対して、上記リフロー装置3を用いてリフロー処理を行った。この場合、真空雰囲気内の第6真空処理室内F6で、正負の電極Cp、Cpへの印加電圧を0.6kVに設定してシリコン基板11をセラミックスプレート33bに吸着し、基板11の加熱温度を275に設定して加熱した。この場合、昇温速度を40/secとした。また、加熱開始と共に、第6真空処理室内にアルゴンガスを15sccmの流量で導入し、圧力を0.1aとした。そして、基板の加熱開始から基板温度が275に到達すると、ターゲットに2.5kWの直流電力を投入し、ターゲットTをスパッタリングすることとした。この場合のスパッタレートは、約1nm/secであった。そして、スパッタリング開始後、30sec~40sec間、Cu原子やCuイオンを供給しながらシリコン基板11に対してリフロー処理を施した(発明実験)。

40

#### 【0034】

比較実験として、溝部にバリア層及びCuシード層が形成されたシリコン基板に対して、上記リフロー装置を用いてリフロー処理を施した。この場合、基板の加熱温度を400に設定し、リフロー時にCu原子やCuイオンの供給は行わず、30sec~40sec

50

c の間熱処理を施した。

【0035】

以上の実験により夫々作製したものに対して、走査型電子顕微鏡（SEM）を用いて、溝部16の充填率（溝部がCuで充填されている割合、体積%）を確認したところ、比較実験のものは、一度の処理では、その充填率が80%未満であり、また、SEM像を模式的に示す図4の如く、溝部の中央領域にボイド（空洞）Vが発生しているものが多いことが確認された。それに対して、発明実験のものでは、一度の処理で、充填率が略100%になり、SEM像で確認すると、図1（e）に示すように、基板全面に亘ってパターンングされた溝部16にCuが埋め込まれていることが確認された。

【0036】

以上、本発明の実施形態について説明したが、本発明は上記のものに限定されるものではない。上記実施形態では、半導体基板に形成した溝部にCuを埋め込み形成するものと例に説明したが、他の用途にもの本発明は適用できる。また、上記実施形態では、リフロー処理中のCu原子またはCuイオンの供給をスパッタリング法を用いるものを例に説明したが、これに限定されるものではなく、蒸着法やCVD法等の他の方法を用いることができる。

【符号の説明】

【0037】

S…半導体装置、11…基板（被処理物）、16…溝部（トレンチ：凹部）、17…バリア層（バリアメタル）、18…Cu膜（Cuシード層）、19…Cu配線層、3…リフロー装置、33…ステージ、34…加熱手段、T…Cu製ターゲット。

10

20

【図1】

【図2】

【図3】

【図4】

## フロントページの続き

(51) Int.CI. F I テーマコード(参考)

C 2 3 C 14/34 (2006.01) C 2 3 C 14/58 A

C 2 3 C 14/58 (2006.01)

(72)発明者 坂本 勇太

静岡県裾野市須山1220-1 株式会社アルパック半導体電子技術研究所内

(72)発明者 遠藤 洋平

静岡県裾野市須山1220-1 株式会社アルパック半導体電子技術研究所内

(72)発明者 小平 周司

静岡県裾野市須山1220-1 株式会社アルパック半導体電子技術研究所内

(72)発明者 岩澤 宏明

静岡県裾野市須山1220-14 株式会社アルパック富士裾野工場内

(72)発明者 内田 洋平

静岡県裾野市須山1220-1 株式会社アルパック半導体電子技術研究所内

F ターム(参考) 4K029 BA08 BA16 CA05 CA13 DC20 DC34 FA04 FA06 GA00 GA01

JA01

4M104 AA01 BB04 BB13 BB14 BB17 BB18 BB25 BB27 BB28 BB30

BB32 BB33 BB34 BB36 DD39 DD40 DD41 DD79 DD99 FF16

FF17 FF18 HH01 HH20

5F033 HH07 HH11 HH15 HH17 HH18 HH19 HH21 HH27 HH28 HH30

HH32 HH33 HH34 HH35 HH36 JJ19 KK01 LL08 MM01 MM12

MM13 PP15 PP33 QQ09 QQ11 QQ73 QQ74 QQ75 QQ85 QQ92

QQ98 RR04 WW03 XX00 XX05 XX33