# WORLD INTELLECTUAL PROPERTY ORGANIZATION International Bureau

# INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(51) International Patent Classification 6:

(11) International Publication Number:

WO 95/12264

H04L 12/22, 29/06, 12/56

**A1**

(43) International Publication Date:

4 May 1995 (04.05.95)

(21) International Application Number:

PCT/EP94/03482

(22) International Filing Date:

25 October 1994 (25.10.94)

(81) Designated States: AU, BG, BR, BY, CA, CN, CZ, EE, FI, HU, JP, KG, KP, KR, KZ, LT, LV, NO, NZ, PL, RO, RU,

SI, SK, UA, US, UZ, VN, European patent (AT, BE, CH, DE, DK, ES, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE).

(30) Priority Data:

9301841

25 October 1993 (25.10.93) NL

Published

With international search report.

(71) Applicant (for all designated States except US): KONINKLI-JKE PTT NEDERLAND N.V. [NL/NL]; P.O. Box 95321, NL-2509 CH The Hague (NL).

(72) Inventors; and

(75) Inventors/Applicants (for US only): FEIKEN, Albertus [NL/NL]; Praam 135, NL-1186 TD Amstelveen (NL). DE LANGE, Martin, Klaas [NL/NL]; Kersengaarde 188, NL-2272 NN Voorburg (NL). ROELOFSEN, Gerrit [NL/NL]; Drossaardslag 58, NL-2805 DD Gouda (NL). FEIJEN, Maurice, Matthias [NL/NL]; Prinses Beatrixlaan 100, NL-2286 LC Rijswijk (NL). BOLY, Jean, Paul [NL/NL]; Loethe 22, NL-2381 BL Zoeterwoude (NL).

(54) Title: DEVICE FOR PROCESSING DATA PACKETS

(57) Abstract

The invention relates to a device (1) for processing data packets, comprising identification means (14) for identifying a data packet, processing means (11, 12) for cryptographically processing the data packet, and memory means (13) for storing information relating to the processing, in which device the processing means comprise at least a first (11) and a second (12) processing unit. Control means (14) are provided to assign, on the basis of the identification of a data packet, said data packet to one of the processing units and to process said data packet with the aid of information related to said data packet. Preferably, at least one processing unit (11; 12) is designed to encrypt or decrypt data packets, and the information relating to the processing comprises a key and a status of a processing procedure.

## FOR THE PURPOSES OF INFORMATION ONLY

Codes used to identify States party to the PCT on the front pages of pamphlets publishing international applications under the PCT.

| AT | Austria                  | GB | United Kingdom               | MR | Mauritania               |

|----|--------------------------|----|------------------------------|----|--------------------------|

| AU | Australia                | GE | Georgia                      | MW | Malawi                   |

| BB | Barbados                 | GN | Guinea                       | NE | Niger                    |

| BE | Belgium                  | GR | Greece                       | NL | Netherlands              |

| BF | Burkina Faso             | HU | Hungary                      | NO | Norway                   |

| BG | Bulgaria                 | IE | Ireland                      | NZ | New Zealand              |

| BJ | Benin                    | IT | Italy                        | PL | Poland                   |

| BR | Brazil                   | JP | Japan                        | PT | Portugal                 |

| BY | Belarus                  | KE | Kenya                        | RO | Romania                  |

| CA | Canada                   | KG | Kyrgystan                    | RU | Russian Federation       |

| CF | Central African Republic | KP | Democratic People's Republic | SD | Sudan                    |

| CG | Congo                    |    | of Korea                     | SE | Sweden                   |

| СН | Switzerland              | KR | Republic of Korea            | SI | Slovenia                 |

| CI | Côte d'Ivoire            | KZ | Kazakhstan                   | SK | Slovakia                 |

| CM | Cameroon                 | LI | Liechtenstein                | SN | Senegal                  |

| CN | China                    | LK | Sri Lanka                    | TD | Chad                     |

| CS | Czechoslovakia           | LU | Luxembourg                   | TG | Togo                     |

| CZ | Czech Republic           | LV | Latvia                       | TJ | Tajikistan               |

| DE | Germany                  | MC | Monaco                       | TT | Trinidad and Tobago      |

| DK | Denmark                  | MD | Republic of Moldova          | UA | Ukraine                  |

| ES | Spain                    | MG | Madagascar                   | US | United States of America |

| FI | Finland                  | ML | Mali                         | UZ | Uzbekistan               |

| FR | France                   | MN | Mongolia                     | VN | Viet Nam                 |

| GA | Gabon                    |    |                              |    |                          |

Title: Device for processing data packets.

### BACKGROUND OF THE INVENTION

5

10

15

20

25

The present invention relates to a device for processing data packets. More in particular, the present invention relates to a device for cryptographically processing data packets, said device comprising identification means for identifying a data packet, processing means for cryptographically processing the data packet, memory means for storing information relating to the processing, and control means for selecting information related to the data packet. A device of this type is disclosed in US Patent Specification 5,048,087.

In practice it is known to arrange for data communication, including telephony, to take place by means of data packets. Diverse techniques for data communication with the aid of data packets, such as X.25 and ATM ("asynchronous transfer mode"), are known. The need exists to an increasing extent to secure the data traffic by means of encrypting the messages (data packets). For this purpose, an encrypting device can be incorporated at the transmitting end and a decrypting device at the receiving end in the data connection concerned.

In modern data communication techniques, data packets belonging to a plurality of logical connections are transmitted via a single physical connection. Such logical connections will hereinafter generally be referred to as channels. Thus, for example, in the case of ATM, a plurality of "virtual channels" and "virtual paths" may make use of the same physical connection. At the same time, there is no fixed correlation between the consecutive data packets, referred to as "cells" in the case of ATM. The channel to which the data packet belongs can be read off only from the header of each data packet.

2

If one or more of said channels is to be secured by encrypting, measures have to be taken to encrypt and decrypt data packets of a particular logical connection in a particular way, for example with a key belonging to the logical connection. For this purpose, the data packets of the different logical connections have to be identified in order to be able to determine the particular channel, and consequently, for example, the associated key, of a particular data packet.

5

10

15

20

25

In the device disclosed in US 5,048,087, the identification means are formed by a packet identifier. Stored in a memory is a plurality of keys, one of which is retrieved in each case in order to process a data packet of a particular channel (logical connection) in the cryptographic unit provided therefor. In addition, in the known device, a cryptographic residue is in each case retrieved or, respectively, stored in addition to the key. Such a cryptographic residue can represent the status of a cryptographic process by which related data packets are encrypted or decrypted, respectively.

The known device has the disadvantage that it is relatively slow. For each incoming data packet, the matching key and the matching residue have to be loaded on the basis of the identification, after which the cryptographic processing (encrypting or decrypting) takes place. After the processing, the new residue (and possibly the key) has to be stored in each case before a subsequent data packet can be processed. It will be clear that the repeated performance, that is to say the performance for each data packet, of said steps takes place at the expense of the processing speed of the known device and, consequently, of the throughput speed of the data packets to be processed.

The storage and retrieval of only a key for each channel, which is disclosed per se, for example, in the publication "Data security in packet switched networks", which is specified in greater detail below, may in

3

principle be faster but still requires a relatively large amount of processing time. Such a solution is furthermore unsuitable for cryptographic procedures whose status has to be stored between two processing steps. It is precisely such procedures which are at present much used for encrypting data communication.

In modern data communication, speed plays an ever greater role.

Devices for processing data packets, such as cryptographic devices, therefore have to satisfy ever higher speed requirements. In the known device, which involves reloading and storing related processing information for each data packet, said retrieval and storage of information forms a speed-limiting factor.

## SUMMARY OF THE INVENTION

5

10

15

20

25

The object of the invention is to eliminate the abovementioned and other disadvantages of the prior art and to provide a device for processing data packets which makes possible a rapid processing of data packets even if a status of a processing procedure has to be stored for each data packet and the data packets belong to different channels. In particular, the object of the invention is to provide a device which is suitable for encrypting and/or decrypting data packets in ATM networks.

For this purpose, the device according to the present invention is characterized in that the processing means comprise at least a first and a second processing unit, and in that the control means are designed to assign, on the basis of the identification of a data packet, said data packet to one of the processing units and to process said data packet with the aid of information related to said data packet. In other words, in the device according to the invention, there is present a plurality of, preferably parallel, processing devices, so that a plurality of data packets can be processed

4

essentially simultaneously. At the same time, the control means are designed in such a way that they assign an identified data packet to a suitable processing unit. A suitable processing unit may be understood as meaning either a processing unit which is available at a particular instant or one in which certain information of a processing procedure is present.

5

10

15

20

25

In a first embodiment of the device according to the invention, at least one processing unit is designed to encrypt data packets, while in a second embodiment, at least one processing unit is designed to decrypt data packets. Because the device according to the invention is provided with a plurality of processing units, it is possible both to encrypt and to decrypt data packets in a single device, optionally essentially simultaneously. The device according to the invention can be used not only for cryptographic functions but also for other applications such as parity control of data packets. Advantageously, the processing units are of programmable design, so that various processing procedures can be performed with one processing unit. The programs for performing the processing procedures are advantageously stored in the memory means, so that a suitable procedure can be loaded under the influence of the control means, optionally in conjunction with the identification means.

Preferably, a buffer is provided upstream of the processing units, that is to say between the input of the device and the processing units. Data packets can be temporarily stored in said buffer before they are transferred to a processing unit. The temporary storage provides the control means, in conjunction with the identification means, with the time needed to determine the respective channels of the data packets and to select and optionally adjust a suitable processing unit. In the case of low data speeds, it may be possible to omit the buffer. Optionally, the buffer can be incorporated in the processing

5

10

units, for example by providing each processing unit with a separate input buffer.

In an advantageous embodiment, the control means are designed to assign data packets which belong to the same channel to the same processing unit. In this way, the processing time for the data packets of said channel is reduced still further.

Advantageously, the device according to the invention can be used in ATM networks. For this purpose, the device can be designed in such a way that a fixed time relationship exists between the arrival and the departure of data packets. Such a fixed time relationship can be achieved by a suitable design of the control means. Optionally, an output buffer can be provided for this purpose, but also to fulfil (other) synchronization purposes.

### REFERENCES

- J. R. Sherwood, "Data security in packet switched networks", Second IEE National Conference on Telecommunications, York, U.K., 2-5 April 1989.

- [2] W. Diffie et al., "Privacy and Authentication: An Introduction to Cryptography", Proceedings of the IEEE, Vol. 67, No. 3, March 1979.

- 20 [3] US 5,048,087

- [4] WO 90/12465

- [5] WO 93/09627

These references are herewith incorporated in this text.

# 25 BRIEF DESCRIPTION OF THE DRAWINGS

The invention will be explained below in greater detail with reference to the figures.

6

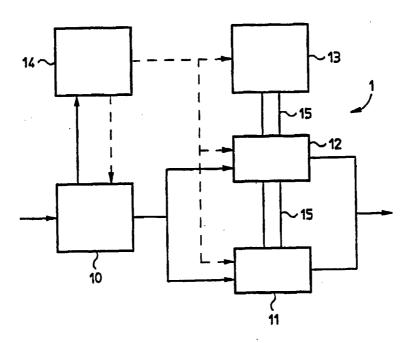

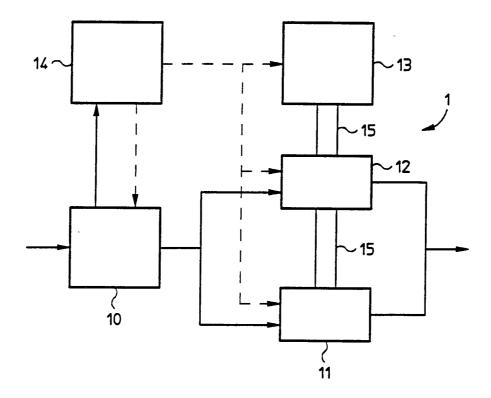

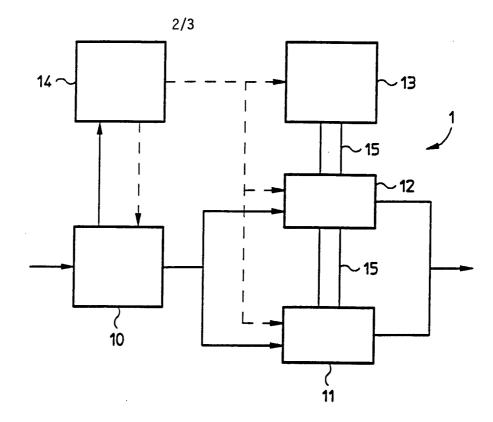

Fig. 1 shows diagrammatically a device according to the invention for processing data packets.

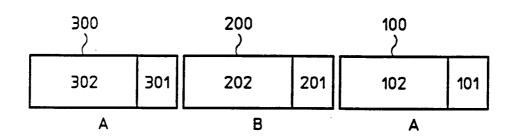

Fig. 2 shows diagrammatically a number of consecutive data packets to be processed.

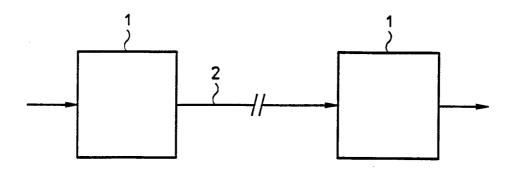

Fig. 3 shows diagrammatically a data communication system provided with devices according to Fig. 1.

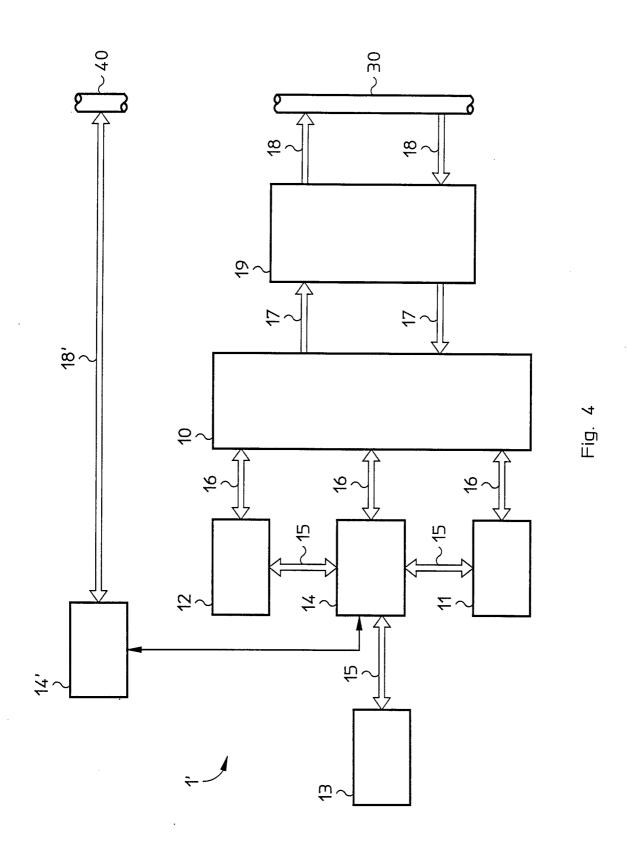

Fig. 4 shows diagrammatically an alternative embodiment of the device according to the invention.

### 10 DESCRIPTION OF PREFERRED EMBODIMENTS

5

15

20

25

The device 1 according to the invention shown diagrammatically in Fig. 1 comprises a buffer 10, a first processing unit 11, a second processing unit 12, a memory 13 and an identification and control unit 14. The processing units 11 and 12 and the memory 13 are connected by a common data bus 15. Data connections are indicated in Fig. 1 by continuous lines and control connections by broken lines.

A data packet which enters the device 1 is first temporarily stored in the buffer 10. During this time, the header of the data packet is copied to the identification unit 14, where the channel (in the case of ATM, the virtual channel or the virtual path) of the data packet is determined. On the basis of this identification, the control unit, which is incorporated in the identification unit in the embodiment shown but can also form a separate unit, activates the other sections of the device 1. If a processing unit (11 or 12) is free, it is given the instruction to receive a data packet. Essentially simultaneously, the buffer 10 is instructed to release the data packet concerned, while the memory 13 is instructed to place the information belonging to said channel (for example, the key and the status of the encrypting/decrypting procedure,

7

and optionally the software of a processing) on the bus 15. Subsequently, the processing unit concerned reads in both the information and the data packet and performs the desired processing, after which the data packet (for example, under the control of the control unit) is transmitted by the processing unit. If said transmission does not take place under the control of the control unit, the processing units are preferably coupled in such a manner that they cannot transmit a data packet simultaneously. In order to prevent synchronization problems, for example, it may be advantageous to provide a further buffer (not shown) at the output of the device 1 or to provide each processing unit with its own output buffer.

5

10

15

20

25

The device 1 has, according to the invention, at least two (parallel) processing units. As a result, it is possible, in the first place, to process two data packets simultaneously. In this case, said data packets may either be of the same channel or of different channels. It will be clear that the throughput speed of the data packets is substantially increased by the presence of a plurality of parallel processing units. If desired, more than two processing units, such as three, four, five or more processing units may, as was stated above, be used, as a result of which a further increase in speed can be achieved.

In the second place, the presence of two (or more) parallel processing units offers the possibility of processing data packets of a particular channel in one processing unit, while data packets of another channel or of other channels are processed in another processing unit. In other words, the control is designed in such a way that data packets of a particular channel are sent to that processing unit in which a data packet of the same channel has previously been processed. As a result, the processing speed can be increased because loading the information needed from the memory and optionally storing

8

information after processing every time can be omitted in the case of that processing unit. Furthermore there is the possibility of reserving one of the processing units (or, in the case of more than two processing units, several processing units) for a particular channel, for example if a relatively large amount of data packets belong to said channel. Said reservation may optionally take place dynamically, for example on the basis of statistical data stored by the identification and control unit. As a result, the throughput speed can be increased further, at least for the channel concerned. Suitable measures, for example the adjustment of the buffer capacity to the expected quantity of data packets which cannot be processed directly, can be taken for this purpose, if necessary, in the buffer 10.

5

10

15

20

25

In the third place, the device according to the invention offers the possibility, for example, of encrypting in one processing unit, while the other processing unit is used at the same instant for decrypting. In other words, with the device according to the invention, it is possible to perform a plurality of processes and different processes simultaneously in one device. At the same time, it is also possible to perform no processing at all in one processing unit at a particular instant, optionally depending on the channel of the data packet concerned. If it is desired not to perform any processing on the data packets in many cases, for example for many channels, it may be advantageous to provide, parallel to the processing units, a connection which connects the buffer 10 directly to the output of the device 1.

It should be pointed out, that in the embodiment shown, one memory is present which is connected via a common data bus to all the processing units, i.e. two in the case shown. It may be advantageous to design the device in such a way that each of the processing units has its own memory, in which case the common data bus may optionally be omitted. However, a common

9

data bus for the two or more processing units provides the possibility for the porcessing units to exchange data, e.g. cryptographic data.

It is furthermore possible to incorporate the identification unit (the identification means) in the memory 13. In this case, the header of a data packet may, for example, be used to address the memory directly or indirectly (for example, by means of multiplexing).

5

10

15

20

25

The device according to the invention may be constructed of standard components. In this connection, reference is made to general handbooks in the field of electronics, such as "The Art of Electronics" by P. Horowitz and W. Hill, Cambridge University Press, 1989. Advantageously, the device may, however, be designed as an ASIC ("application-specific integrated circuit"). The processing units preferably comprise a processor (for example, a microprocessor) for performing the processing. The processing itself may be a known cryptographic processing or a different type of processing. In this context, reference is made to the publication entitled "Privacy and Authentication: An Introduction to Cryptography" by W. Diffie et al. in proceedings of the IEEE, Vol. 67, No. 3, March 1979 and to the bibliography incorporated therein.

Fig. 2 shows a series of data packets which are being encrypted with the aid of the device according to the invention. Three consecutive data packets 100, 200 and 300 each have a header 101, 201 and 301, respectively, and a data field 102, 202 and 302, respectively. In the example shown, the data packets 100 and 300 belong to the channel A, while the data packet 200 belongs to the channel B. For this purpose, the headers 101, 201 and 301 are provided with suitable identification information.

If the data packet 100 arrives in the device 1 and no other data packet was previously present in one of the processing units 11 or 12, the data packet

5

10

15

20

25

10

100 can be loaded directly into a processing unit, say the processing unit 11, together with the information belonging to the channel A which is retrieved from the memory 13 on the basis of the header 101. As soon as the connection between the buffer 10 or the memory 13 and the processing unit 12 is free, the data packet 200 can be loaded into the processing unit 12. In the meantime, the data packet 100 can be processed. As soon as this processing is completed, the processed data packet 100 can be transmitted. Information relating to channel A, for example the status of the encrypting procedure, has now possibly to be written back into the memory 13, depending on the processing performed. It will be clear that this writing-back and the subsequent retrieval of information relating to another channel can be omitted if the subsequent data packet loaded into the processing unit 11 also belongs to the channel A. In the case shown, the subsequent data packet (300) belongs to the channel A, so that time can in fact be saved since the processing unit 11 is already prepared for processing data packets of channel A. If the data packet were to belong to channel B, it could in some cases be advantageous to allow said data packet to wait in the buffer 10 until the processing unit 12 is free since said processing unit is already prepared for channel B. This could be the case, for example, if a further data packet (not shown) were to belong to the channel A. In order to perform such waiting effectively, the buffer 10 should be provided with adequate buffer capacity. Furthermore, it is advantageous to design the identification unit in such a way that the identity (the channel) of a plurality of buffered data packets can be determined in order to be able to perform the assignment of the data packets to the processing units efficiently.

Fig. 3 diagrammatically shows a data communication system. The system comprises two devices 1 (or 1', see Fig. 4) for processing data packets,

the devices being connected by a link 2. With the aid of the device according to the invention, it is possible to transmit a plurality of encrypted logical channels via a single link at a high speed. In the system of Fig. 3, a plurality of devices 1 can, if necessary, be provided, for example in series, in order to be able to perform processes on data packets in a plurality of steps or at a plurality of positions.

5

10

15

20

25

The embodiment of the inventive device 1' shown schematically in Fig. 4 comprises, like the embodiment shown in Fig. 1, an input/output buffer 10, a first processing unit 11, a second processing unit 12, a memory 13 and an identification and control unit 14. The device of Fig. 4 is further provided with a system control unit 14', connected with an external data bus or data link 40 by a data bus 18'. This system control unit 14' may serve to control the system the device 1' is a constituent part of. The external bus 40 may, for example, serve to load suitable software and/or commands into the unit 14'.

The data bus 15, connecting the processing units 11 and 12 and the memory 13, is shown in Fig. 4 to consist of three separate parts, but it will be understood that these parts may be interconnected or reconfigured so as to form a data bus 15 consisting of one part only. Data buses 16 connect the units 11, 12 and 14 respectively on the one hand with the unit 10 on the other hand. Unidirectional data buses 17 interconnect the unit 10 and an interface unit 19, while unidirectional data buses 18 interconnect the interface unit 19 and an external bus or link 30. The buses 17 and/or 18 may each be configured as a single bidirectional data bus.

The main components of the device, such as the units 10, 11, 12, 14 and 19 may be constituted by programmable gate arrays (PGAs), such as supplied by Xilinx. The memory 13 may be constituted by a random access

12

memory (RAM), and the system control 14' may comprise a microprocessor (e.g. a Motorola 68000), RAM and EEPROM memory.

5

10

15

For (temporarily or permanently) storing the key(s) and status, e.g. the cryptographic residue, relating to a particular channel the memory 13 is provided. However, an even greater operating speed of the devices 1 and 1' can be achieved if separate buffers are provided for temporarily storing status data, such as a cryptographic residue or a cryptographic initialization value (newstate). Such buffers can advantageously be implemented as registers ("shadow registers") in the processing units 11 and 12. Preferably, the control unit 14 is designed so as to load data relating to a certain cell into a shadow register while the previous cell is still being processed in the processing unit concerned. This loading of data into a shadow register can be done as soon a data packet has been identified. The data of a shadow register can be loaded into the processing unit proper in a very short time, e.g. one clock cycle, as this loading need not involve the data bus 15.

It will be understood by those skilled in the art that the invention is not limited to the embodiments shown and that many modifications and extensions are possible without departing from the spirit and scope of the present invention.

#### **CLAIMS**

- 1. Device for cryptographically processing data packets, comprising

- identification means for identifying a data packet,

- processing means for cryptographically processing the data packet,

- 5 memory means for storing information relating to the processing, and

- control means for selecting information related to the data packet, characterized in that

- the processing means comprise at least a first and a second processing unit, and in that

- the control means are designed to assign, on the basis of the identification of

a data packet, said data packet to one of the processing units and to process

said data packet with the aid of information related to said data packet.

- 2. Device according to claim 1, wherein at least one processing unit is designed to encrypt data packets.

- Device according to claim 1 or 2, wherein at least one processing unit is designed to decrypt data packets.

- 4. Device according to Claim 2 or 3, wherein the information relating to the processing comprises a key and a status of a processing procedure.

- Device according to any of the preceding claims, designed to process data packets which comprise a header and an information field, wherein the identification means are designed to identify the channel to which the data packet belongs on the basis of the header.

- 6. Device according to Claim 5, wherein the processing means are designed to process only the information field of a data packet.

- 7. Device according to any of the preceding claims, wherein a buffer is provided upstream of the processing units.

14

- 8. Device according to any of the preceding claims, wherein the control means are designed to assign data packets which belong to the same channel to the same processing unit.

- 9. Device according to any of the preceding claims, wherein the5 first processing unit, the second processing unit and the memory means are connected by means of a common data bus.

- 10. Device according to any of the preceding claims, wherein at least one processing unit is provided with its own separate memory means.

- Device according to any of the preceding claims, wherein at leastone processing unit is programmable.

- 12. Device according to any of the preceding claims, designed to process ATM data packets.

- 13. System for data communication by means of data cells, provided with at least one device according to any of claims 1 to 12 inclusive.

Fig. 1

Fig. 1

Fig. 2

Fig. 3

#### INTERNATIONAL SEARCH REPORT

Intern al Application No

PCT/EP 94/03482

A. CLASSIFICATION OF SUBJECT MATTER

IPC 6 H04L12/22 H04L29/06 H04L12/56 According to International Patent Classification (IPC) or to both national classification and IPC **B. FIELDS SEARCHED** Minimum documentation searched (classification system followed by classification symbols) H04L IPC 6 Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched Electronic data base consulted during the international search (name of data base and, where practical, search terms used) C. DOCUMENTS CONSIDERED TO BE RELEVANT Relevant to claim No. Citation of document, with indication, where appropriate, of the relevant passages 1-13 WO,A,90 12465 (CHIAPPA J.) 18 October 1990 Y see abstract see page 11, line 30 - page 12, line 34 see page 14, line 4 - line 14 see page 32, line 15 - page 33, line 4 1-13 WO, A, 93 09627 (LEE E.S. ET AL.) 13 May Y 1993 see abstract; claim 1; figure 2 EP,A,O 360 478 (AMERICAN TELEPHONE AND 1-13 A TELEGRAPH COMPANY) 28 March 1990 see abstract 1-4 EP.A.O 464 562 (DIGITAL EQUIPMENT A CORPORATION) 8 January 1992 see abstract -/--Patent family members are listed in annex. Further documents are listed in the continuation of box C. IX "T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the Special categories of cited documents: "A" document defining the general state of the art which is not considered to be of particular relevance invention "E" earlier document but published on or after the international "X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to filing date involve an inventive step when the document is taken alone "L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified) "Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such docu-"O" document referring to an oral disclosure, use, exhibition or ments, such combination being obvious to a person skilled document published prior to the international filing date but later than the priority date claimed in the art. "&" document member of the same patent family Date of mailing of the international search report Date of the actual completion of the international search 0 9, 02, 95 1 February 1995 Authorized officer Name and mailing address of the ISA European Patent Office, P.B. 5818 Patentlaan 2 NL - 2280 HV Rijswijk Tel. (+31-70) 340-2040, Tx. 31 651 epo nl, Staessen, B Fax: (+31-70) 340-3016

Form PCT/ISA/210 (second sheet) (July 1992)

1

4

# INTERNATIONAL SEARCH REPORT

Inter nal Application No

PCT/EP 94/03482

| gory ° Citati | on of document, with inc            | Relevant to claim No.   |     |

|---------------|-------------------------------------|-------------------------|-----|

| 1             | E,C,41 25 830<br>993<br>ee abstract | (SYSTEMHAUS) 21 January | 1-4 |

|               |                                     |                         |     |

|               |                                     |                         |     |

|               |                                     |                         |     |

|               |                                     |                         |     |

|               |                                     |                         |     |

1

# INTERNATIONAL SEARCH REPORT

information on patent family members

Inte onal Application No

PCT/EP 94/03482

| Patent document cited in search report | Publication date | Patent family<br>member(s) |                               | Publication date                 |

|----------------------------------------|------------------|----------------------------|-------------------------------|----------------------------------|

| WO-A-9012465                           | 18-10-90         | EP-A-<br>JP-T-<br>US-A-    | 0465532<br>4504339<br>5249292 | 15-01-92<br>30-07-92<br>28-09-93 |

| WO-A-9309627                           | 13-05-93         | AU-A-<br>CA-A-             | 2912692<br>2123199            | 07-06-93<br>13-05-93             |

| EP-A-0360478                           | 28-03-90         | US-A-<br>JP-A-<br>JP-B-    | 4910777<br>2121441<br>6083262 | 20-03-90<br>09-05-90<br>19-10-94 |

| EP-A-0464562                           | 08-01-92         | CA-A-                      | 2045933                       | 30-12-91                         |

| DE-C-4125830                           | 21-01-93         | NONE                       |                               |                                  |