(43) International Publication Date

28 August 2014 (28.08.2014)(51) International Patent Classification:

**H04B 5/00** (2006.01)(21) International Application Number:

**PCT/US2014/016191**(22) International Filing Date:

13 February 2014 (13.02.2014)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

61/769,152 25 February 2013 (25.02.2013) US

14/108,155 16 December 2013 (16.12.2013) US(71) Applicant: **QUALCOMM INCORPORATED** [US/US];

ATTN: International IP Administration, 5775 Morehouse Drive, San Diego, California 92121-1714 (US).(72) Inventors: **LOW, Zhen Ning**, 5775 Morehouse Drive, San Diego, California 92121-1714 (US). **WHEATLEY, Charles Edward III**, 5775 Morehouse Drive, San Diego, California 92121-1714 (US).(74) Agent: **ABUMERI, Mark M.**; Knobbe Martens Olson & Bear LLP, 2040 Main Street, Fourteenth Floor, Irvine, California 92614 (US).

(81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT,

HN, HR, HU, ID, IL, IN, IR, IS, JP, KE, KG, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SA, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, KM, ML, MR, NE, SN, TD, TG).

**Declarations under Rule 4.17:**

- as to applicant's entitlement to apply for and be granted a patent (Rule 4.17(ii))

- as to the applicant's entitlement to claim the priority of the earlier application (Rule 4.17(iii))

**Published:**

- with international search report (Art. 21(3))

- before the expiration of the time limit for amending the claims and to be republished in the event of receipt of amendments (Rule 48.2(h))

(54) Title: IMPEDANCE TRANSFORMATION NETWORK FOR IMPROVED DRIVER CIRCUIT PERFORMANCE

FIG. 13

(57) **Abstract:** This disclosure provides systems, methods and apparatus for reducing harmonic emissions. One aspect of the disclosure provides a transmitter apparatus. The transmitter apparatus includes a driver circuit characterized by an efficiency and a power output level. The driver circuit further a filter circuit electrically connected to the driver circuit and configured to modify the impedance of the transmit circuit to maintain the efficiency of the driver circuit at a level that is within 20% of a maximum efficiency of the driver circuit when the impedance is within the complex impedance range. The filter circuit is further configured to maintain a substantially constant power output level irrespective of the reactive variations within the complex impedance range. The filter circuit is further configured to maintain a substantially linear relationship between the power output level and the resistive variations within the impedance range.

## IMPEDANCE TRANSFORMATION NETWORK FOR IMPROVED DRIVER CIRCUIT PERFORMANCE

### FIELD

**[0001]** The present invention relates generally to wireless power. More specifically, the disclosure is directed to improving the efficiency and power output of transmit circuit driving a load varying over a wide resistive and reactive range.

### BACKGROUND

**[0002]** An increasing number and variety of electronic devices are powered via rechargeable batteries. Such devices include mobile phones, portable music players, laptop computers, tablet computers, computer peripheral devices, communication devices (e.g., Bluetooth devices), digital cameras, hearing aids, and the like. While battery technology has improved, battery-powered electronic devices increasingly require and consume greater amounts of power. As such, these devices constantly require recharging. Rechargeable devices are often charged via wired connections that require cables or other similar connectors that are physically connected to a power supply. Cables and similar connectors may sometimes be inconvenient or cumbersome and have other drawbacks. Wireless charging systems that are capable of transferring power in free space to be used to charge rechargeable electronic devices may overcome some of the deficiencies of wired charging solutions. As such, wireless charging systems and methods that efficiently and safely transfer power for charging rechargeable electronic devices are desirable.

### SUMMARY

**[0003]** Various implementations of systems, methods and devices within the scope of the appended claims each have several aspects, no single one of which is solely responsible for the desirable attributes described herein. Without limiting the scope of the appended claims, some prominent features are described herein.

**[0004]** Details of one or more implementations of the subject matter described in this specification are set forth in the accompanying drawings and the description below. Other features, aspects, and advantages will become apparent from the description, the drawings, and the claims. Note that the relative dimensions of the following figures may not be drawn to scale.

**[0005]** One aspect of the subject matter described in the disclosure provides a transmitter apparatus. The transmitter apparatus includes a driver circuit characterized by an efficiency and a power output level. The driver circuit is electrically connected to a transmit circuit having an impedance. The impedance of the transmit circuit is within a complex impedance range including resistive and reactive variations. The complex impedance range is defined by a minimum real impedance value, a maximum real impedance, a minimum imaginary impedance value, and a maximum imaginary impedance value. A ratio of the maximum to the minimum real impedance value is at least two to one. A magnitude of the difference between the maximum and minimum imaginary impedance values being at least twice a magnitude of the difference between the minimum and maximum real impedance values. The transmitter apparatus further includes a filter circuit electrically connected to the driver circuit and configured to modify the impedance of the transmit circuit to maintain the efficiency of the driver circuit at a level that is within 20% of a maximum efficiency of the driver circuit when the impedance is within the complex impedance range. The filter circuit is further configured to maintain a substantially constant power output level irrespective of the reactive variations within the complex impedance range. The filter circuit is further configured to maintain a substantially linear relationship between the power output level and the resistive variations within the complex impedance range.

**[0006]** Another aspect of the subject matter described in the disclosure provides a transmitter apparatus. The transmitter apparatus includes a driver circuit including a switching amplifier circuit comprising a switch, a switch shunt capacitor, and a series inductor electrically connected to the output of the driver circuit. The transmitter apparatus further includes a transmit circuit including a coil having an inductance electrically connected in series to a capacitor to form a resonant circuit. The transmitter apparatus further includes a filter circuit electrically connected between the driver circuit and the transmit circuit, the filter circuit comprising solely of a single shunt capacitor network.

**[0007]** Yet another aspect of the subject matter described in the disclosure provides a method of selecting component values of one or more reactive components of a filter circuit for a wireless power transmitter device. The filter circuit is electrically connected between a driver circuit and a transmit circuit. The method includes determining a first set of complex impedance values for which efficiency of the driver

circuit is above a threshold. The first set of complex impedance values substantially map to complex impedance values along a half circle path. The method further includes determining a second set of complex impedance values for which power output of the driver circuit is substantially constant. The second set of complex impedance values substantially map to values along a full circle path that is orthogonal to the half circle and which crosses the half circle at a maximum. The method further includes selecting the component values to provide an impedance transformation that modifies a variable complex impedance of the transmit circuit to complex impedance values derived from the first and second set of complex impedance values.

**[0008]** Another aspect of the subject matter described in the disclosure provides a transmitter apparatus. The transmitter apparatus includes a driver circuit characterized by an efficiency and a power output level. The driver circuit is electrically connected to a transmit circuit having an impedance. The impedance of the transmit circuit is within a complex impedance range including resistive and reactive variations. The transmitter apparatus further includes a filter circuit electrically connected to the driver circuit and configured to modify the impedance of the transmit circuit. The filter circuit has one or more reactive components with values selected derived from a first value and a second value. The first value,  $R_d$ , corresponds to a radius of a half circle. The half circle is defined by a set of complex impedance values along the perimeter of the half circle that correspond to values for which efficiency of the driver circuit is at least within 20% of the maximum efficiency of the driver circuit. The second value  $R_0$ , corresponds to a real impedance value at the load of the filter circuit that results in a desired transformed impedance being equal to  $R_d$  at an input of the filter circuit.

#### BRIEF DESCRIPTION OF THE DRAWINGS

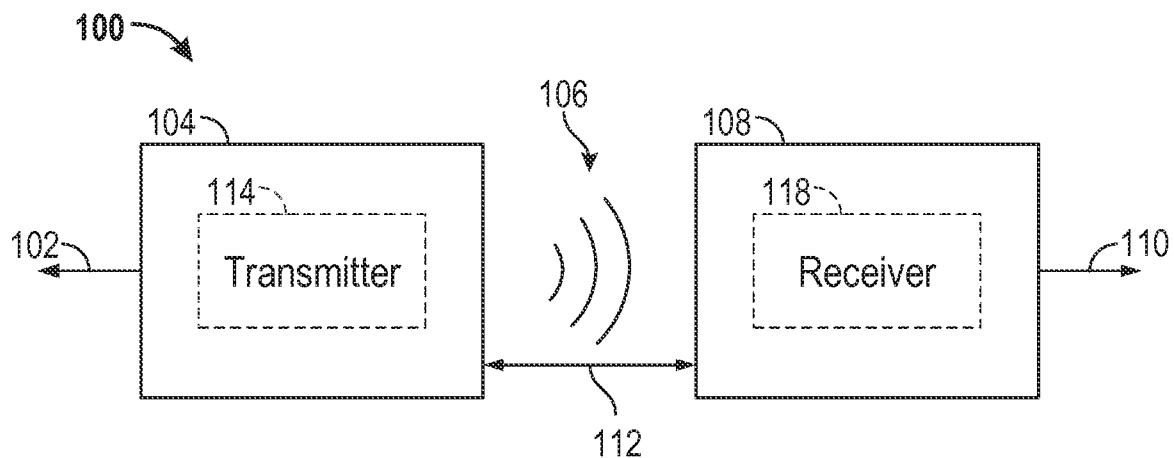

**[0009]** FIG. 1 is a functional block diagram of an exemplary wireless power transfer system, in accordance with exemplary embodiments of the invention.

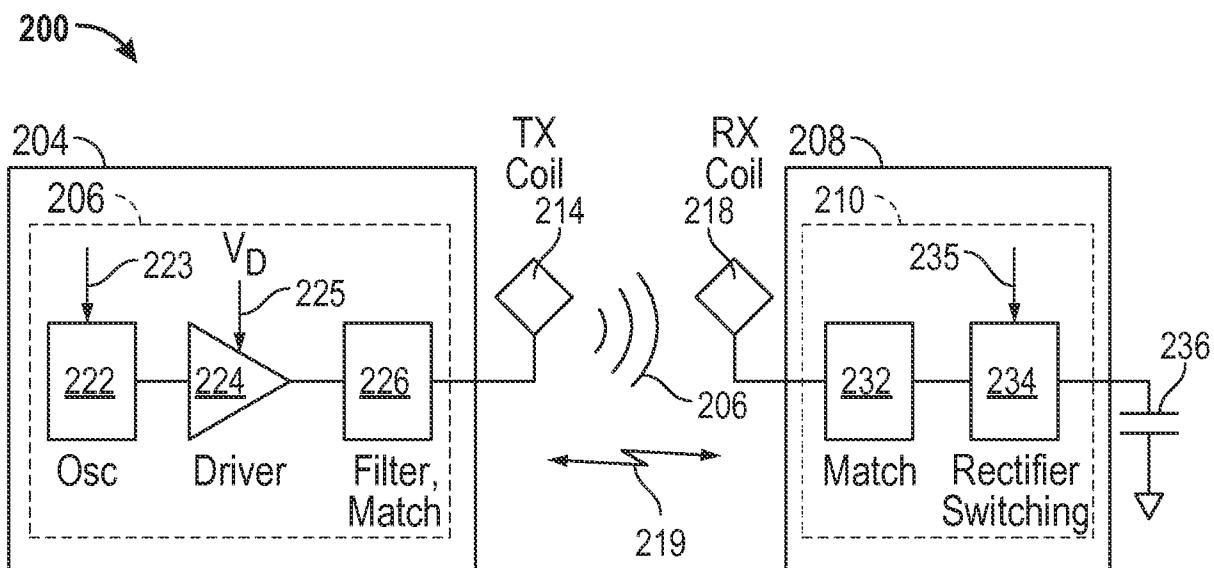

**[0010]** FIG. 2 is a functional block diagram of exemplary components that may be used in the wireless power transfer system of FIG. 1, in accordance with various exemplary embodiments of the invention.

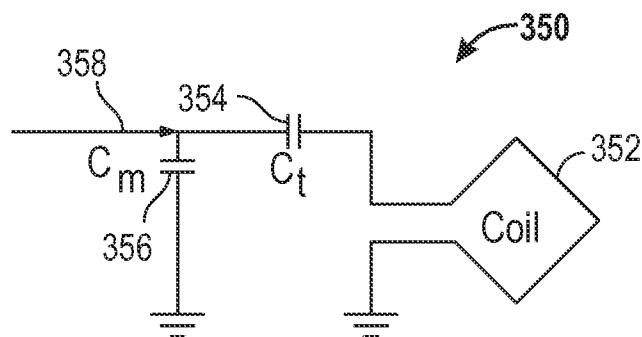

**[0011]** FIG. 3 is a schematic diagram of a portion of transmit circuitry or receive circuitry of FIG. 2 including a transmit or receive coil, in accordance with exemplary embodiments of the invention.

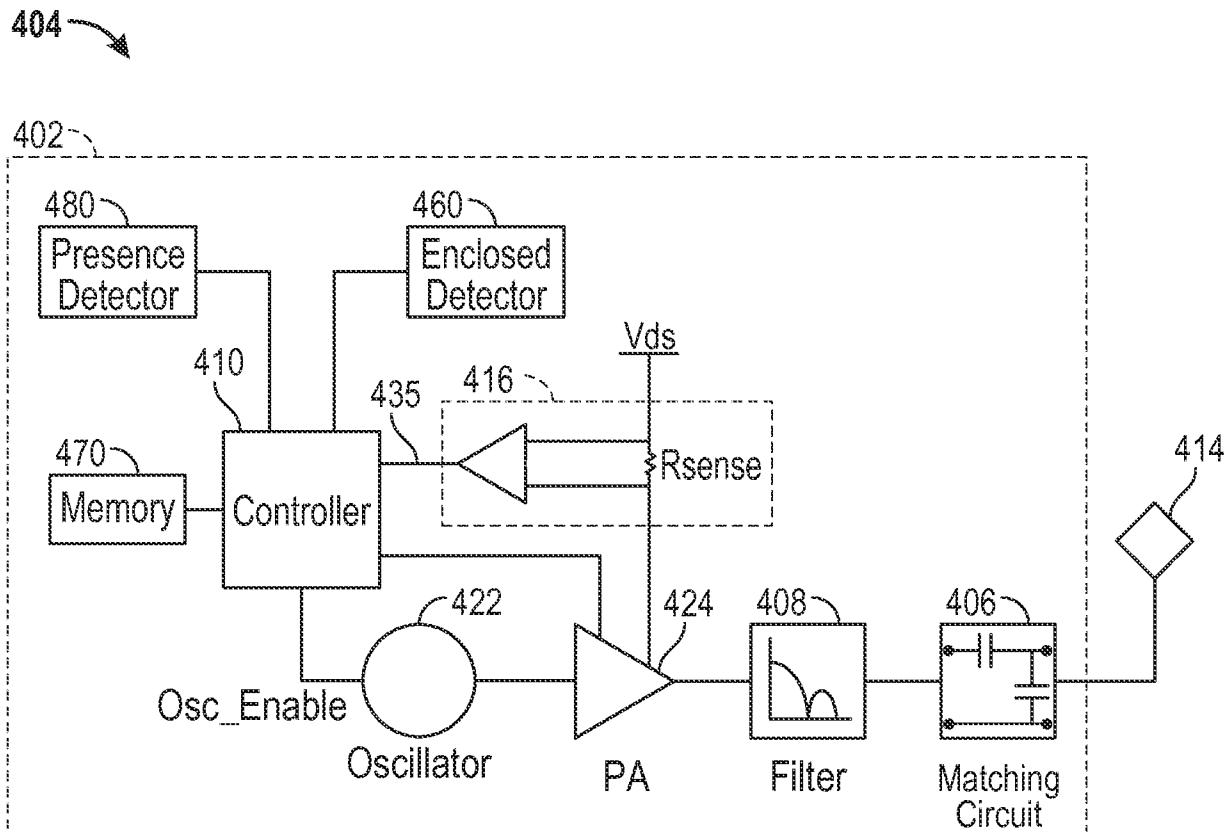

**[0012]** FIG. 4 is a functional block diagram of a transmitter that may be used in the wireless power transfer system of FIG. 1, in accordance with exemplary embodiments of the invention.

**[0013]** FIG. 5 is a functional block diagram of a receiver that may be used in the wireless power transfer system of FIG. 1, in accordance with exemplary embodiments of the invention.

**[0014]** FIG. 6 is a functional block diagram of an exemplary wireless power transfer system as in FIG. 2, where a transmitter may wirelessly provide power to multiple receivers, in accordance with various exemplary embodiments of the invention.

**[0015]** FIG. 7 is a schematic diagram of a driver circuit that may be used in the transmitter of FIG. 6, in accordance with exemplary embodiments of the invention.

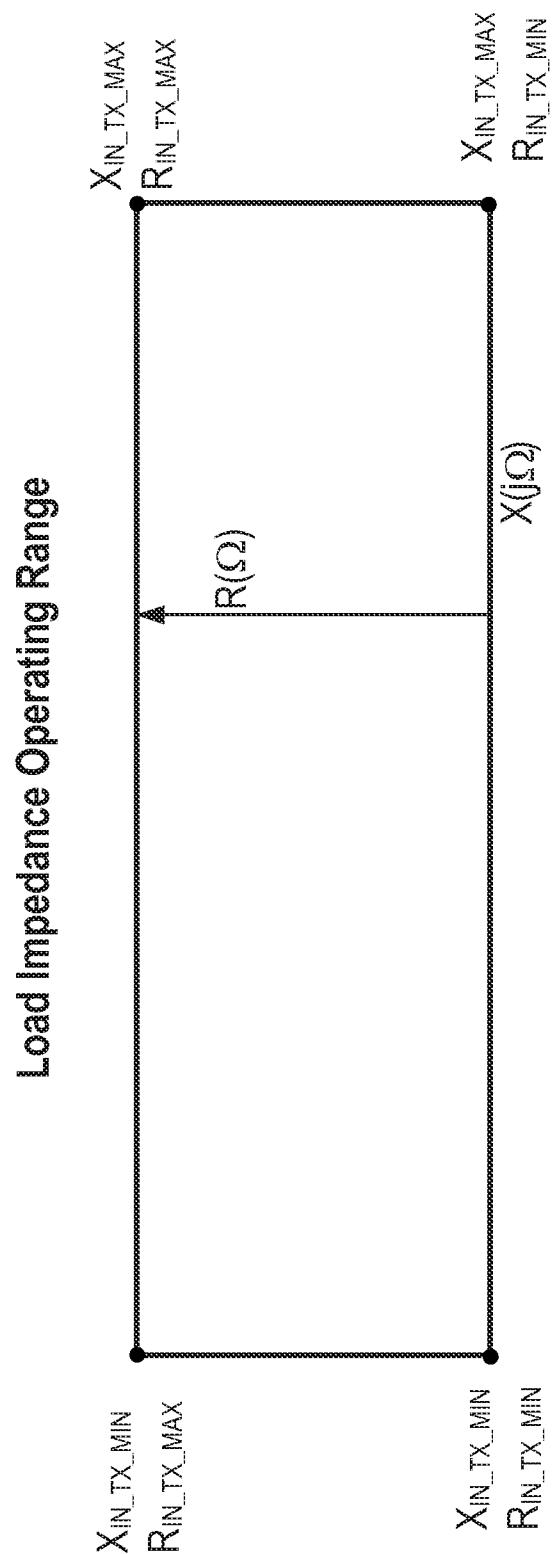

**[0016]** FIG. 8A is a diagram showing an exemplary range of complex impedances that may be presented to the driver circuit during operation of a wireless power transmitter.

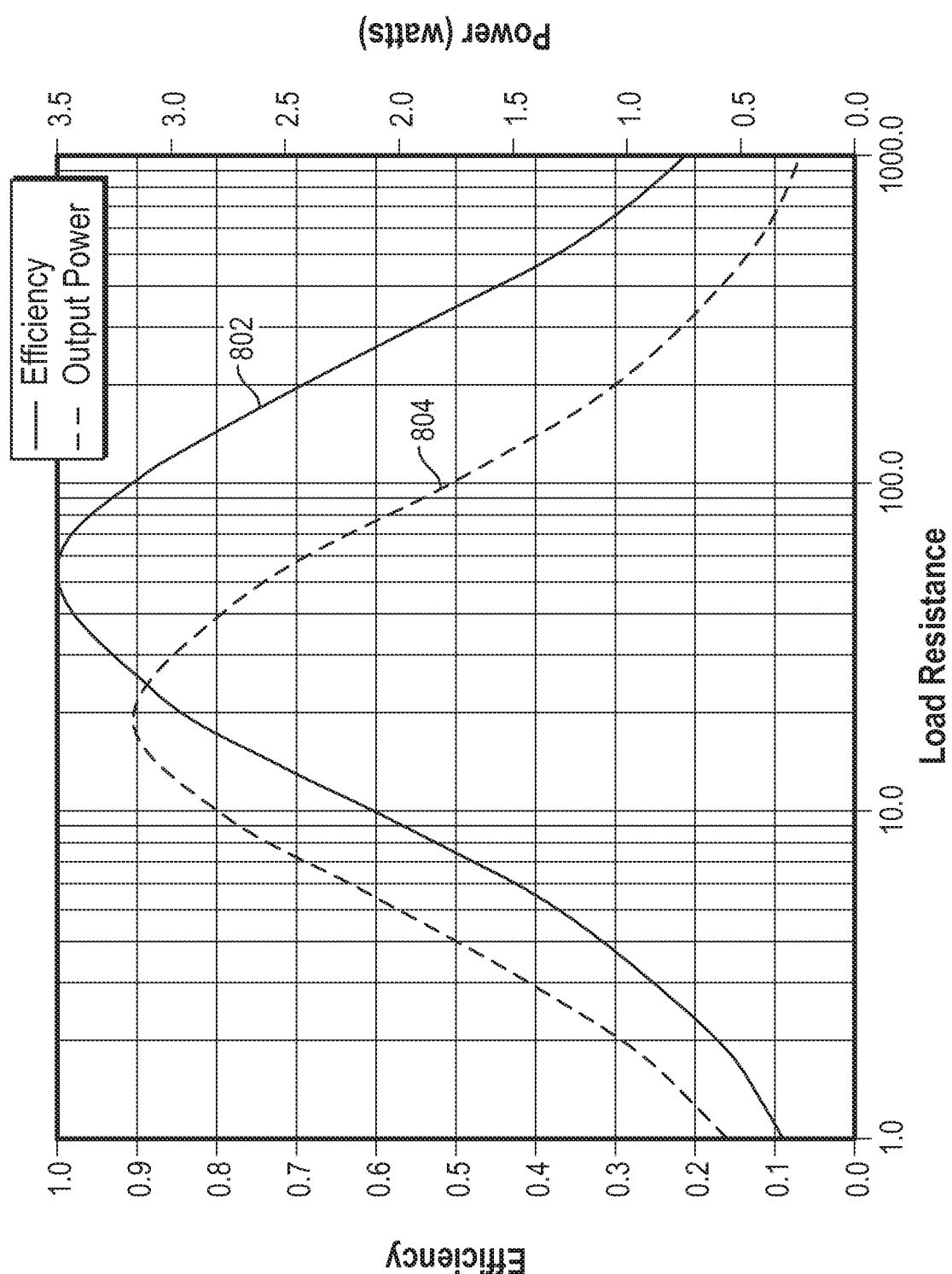

**[0017]** FIG. 8B is a plot showing efficiency and output power of the driver circuit of FIG. 7 as a function of the real impedance of a load of a driver circuit.

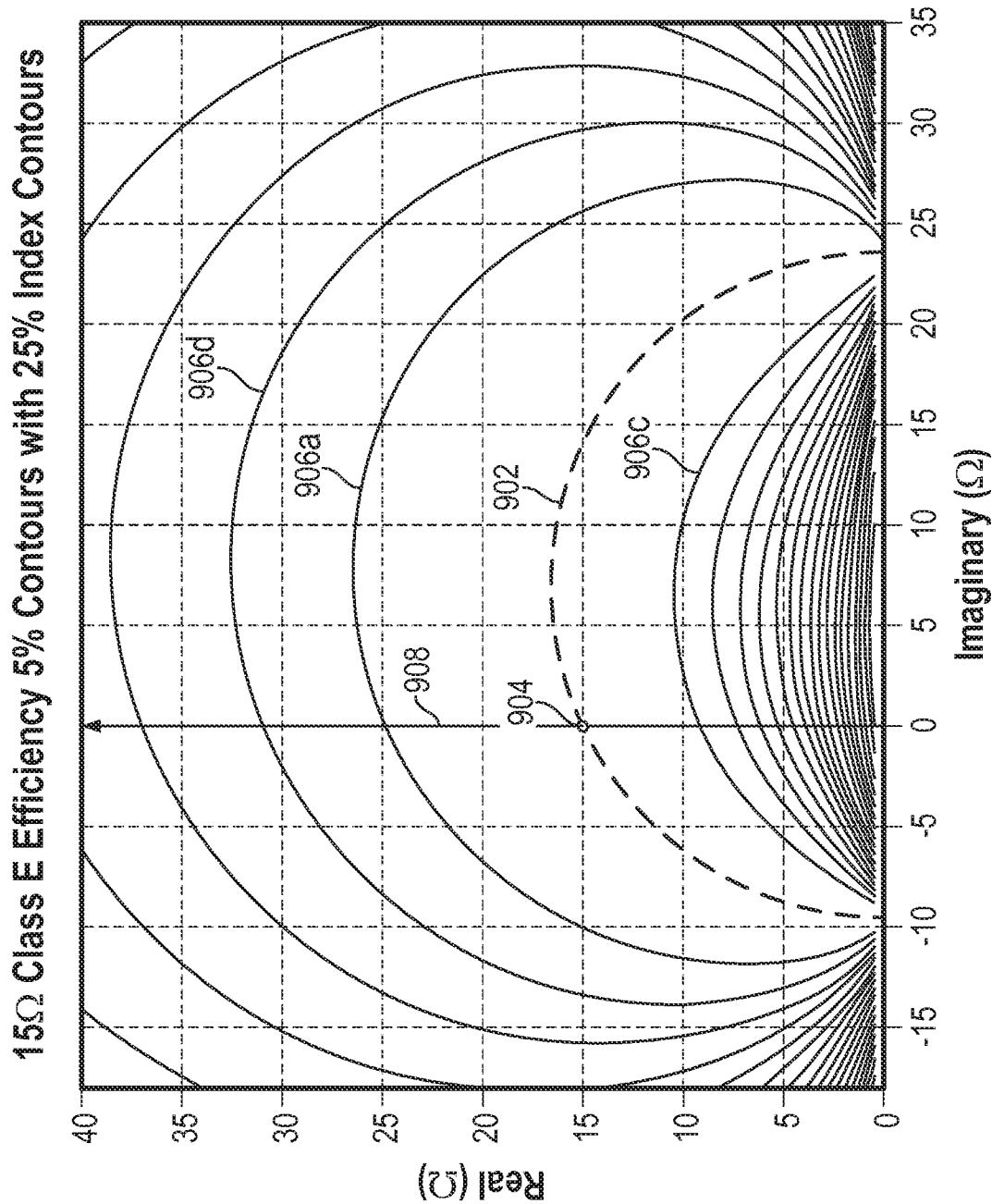

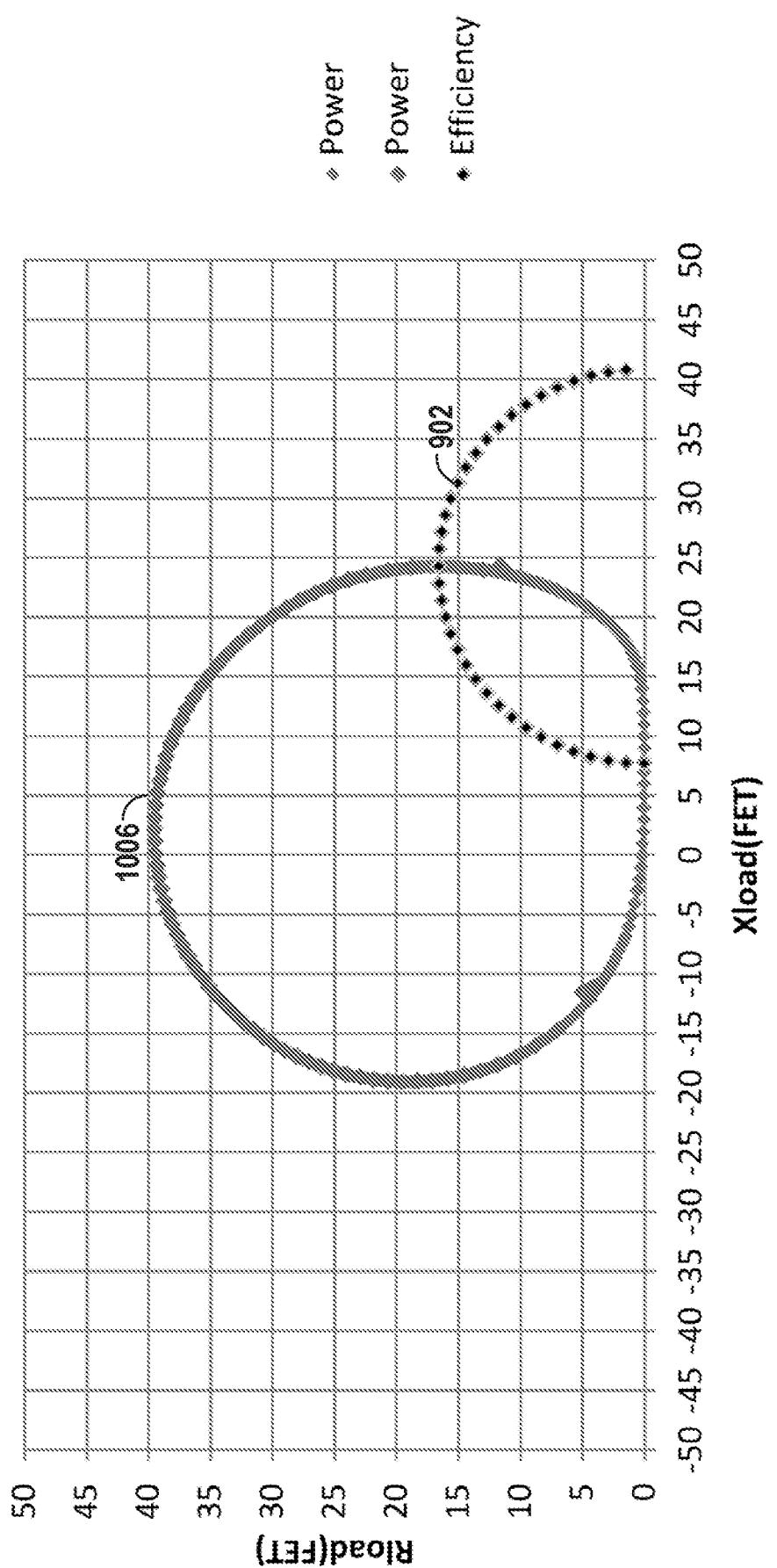

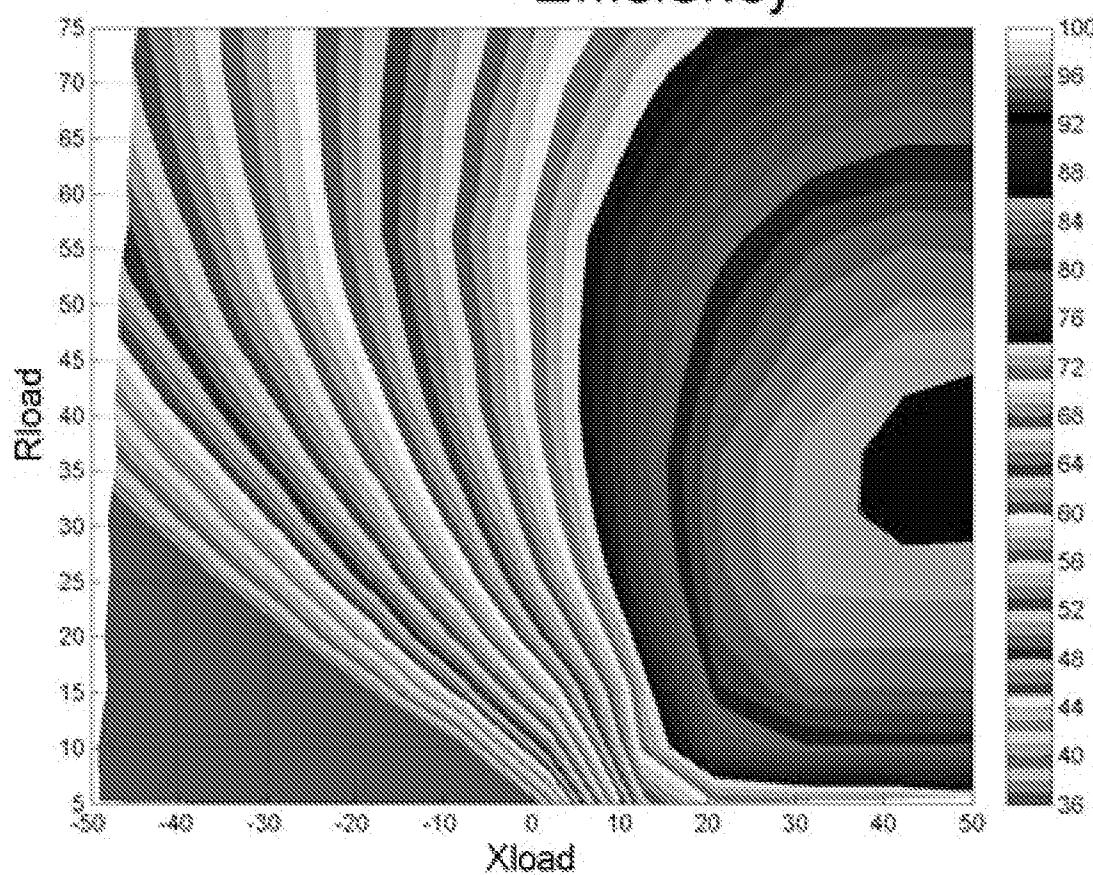

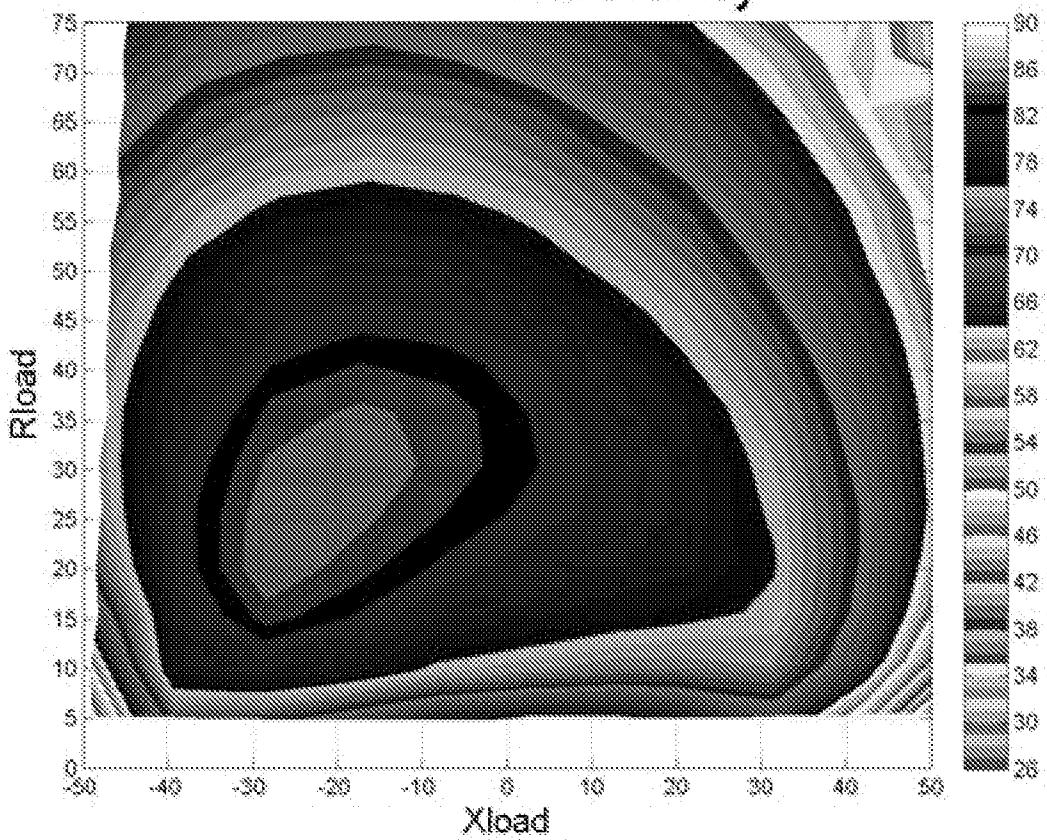

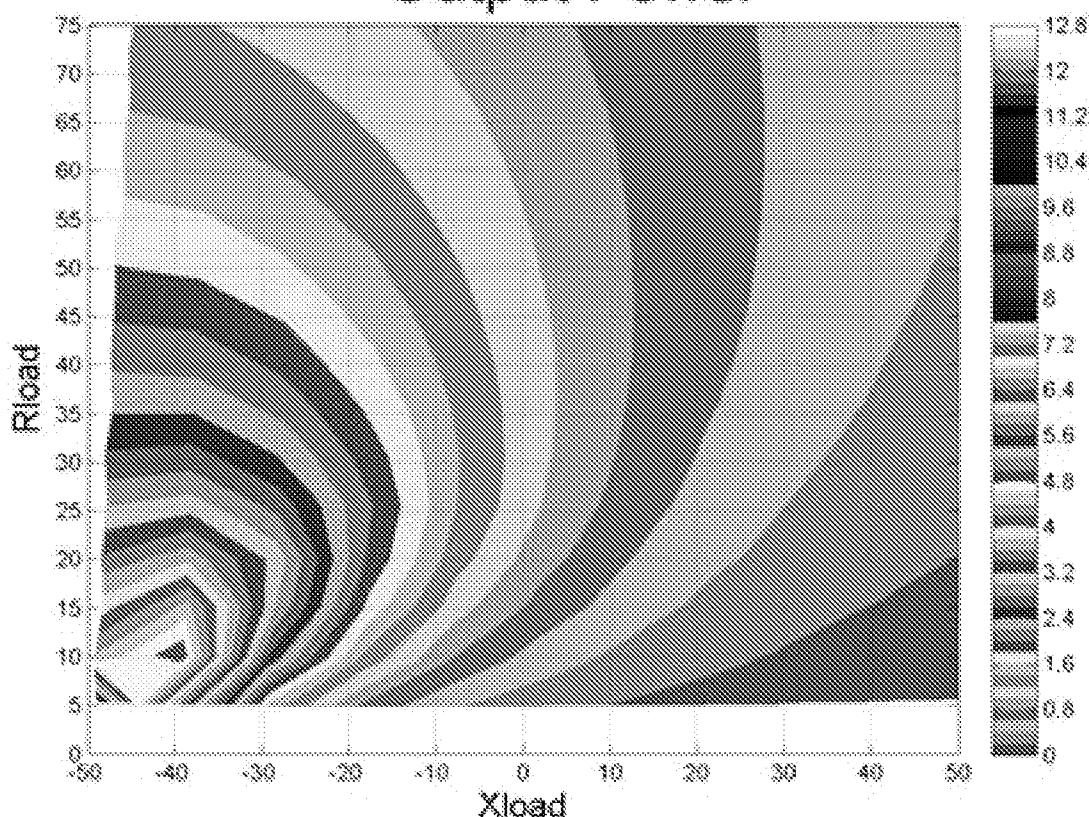

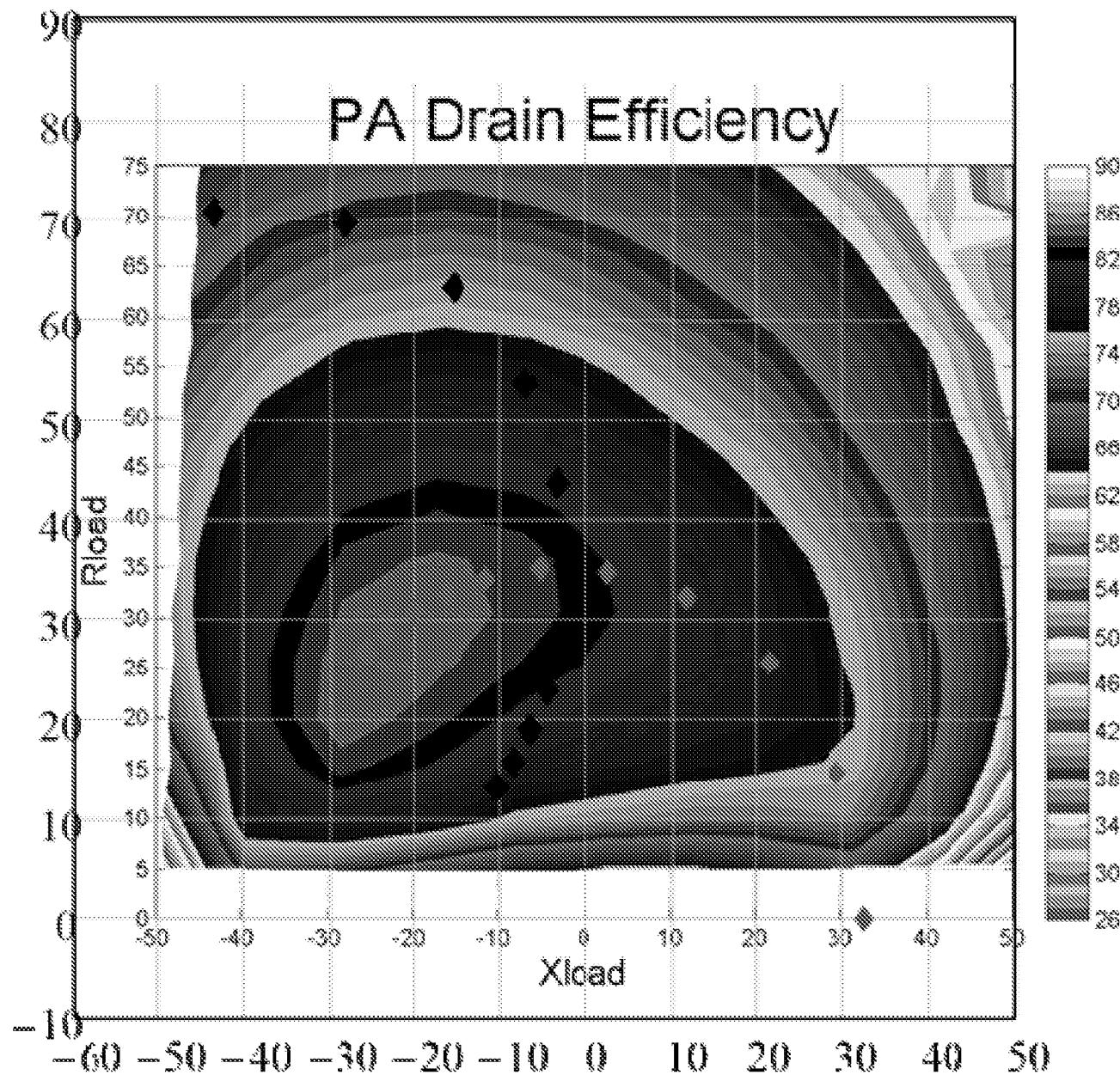

**[0018]** FIG. 9 is a contour plot showing the efficiency of a driver circuit as in FIG. 7 as a function of the real and imaginary components of the load impedance presented to the driver circuit.

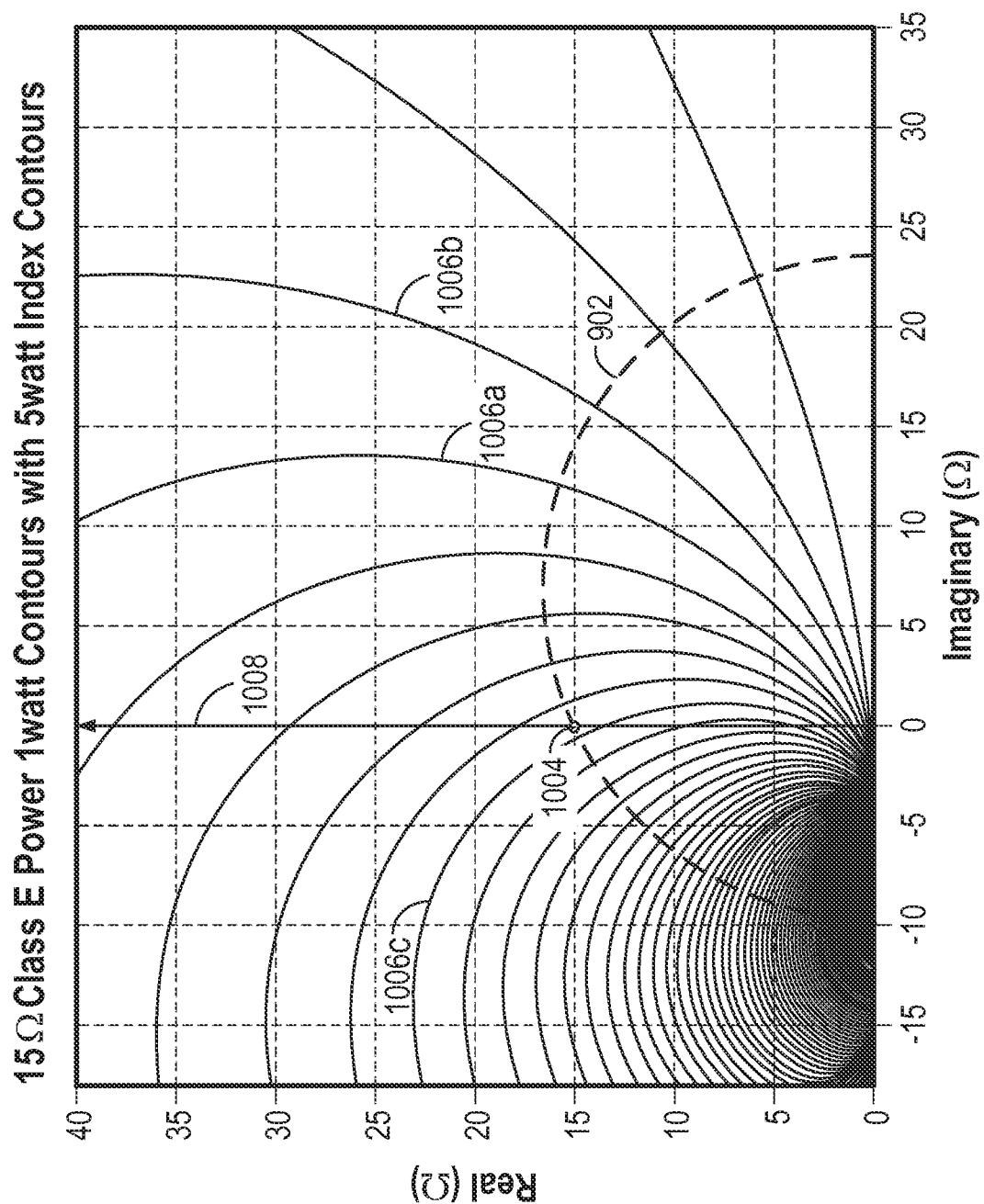

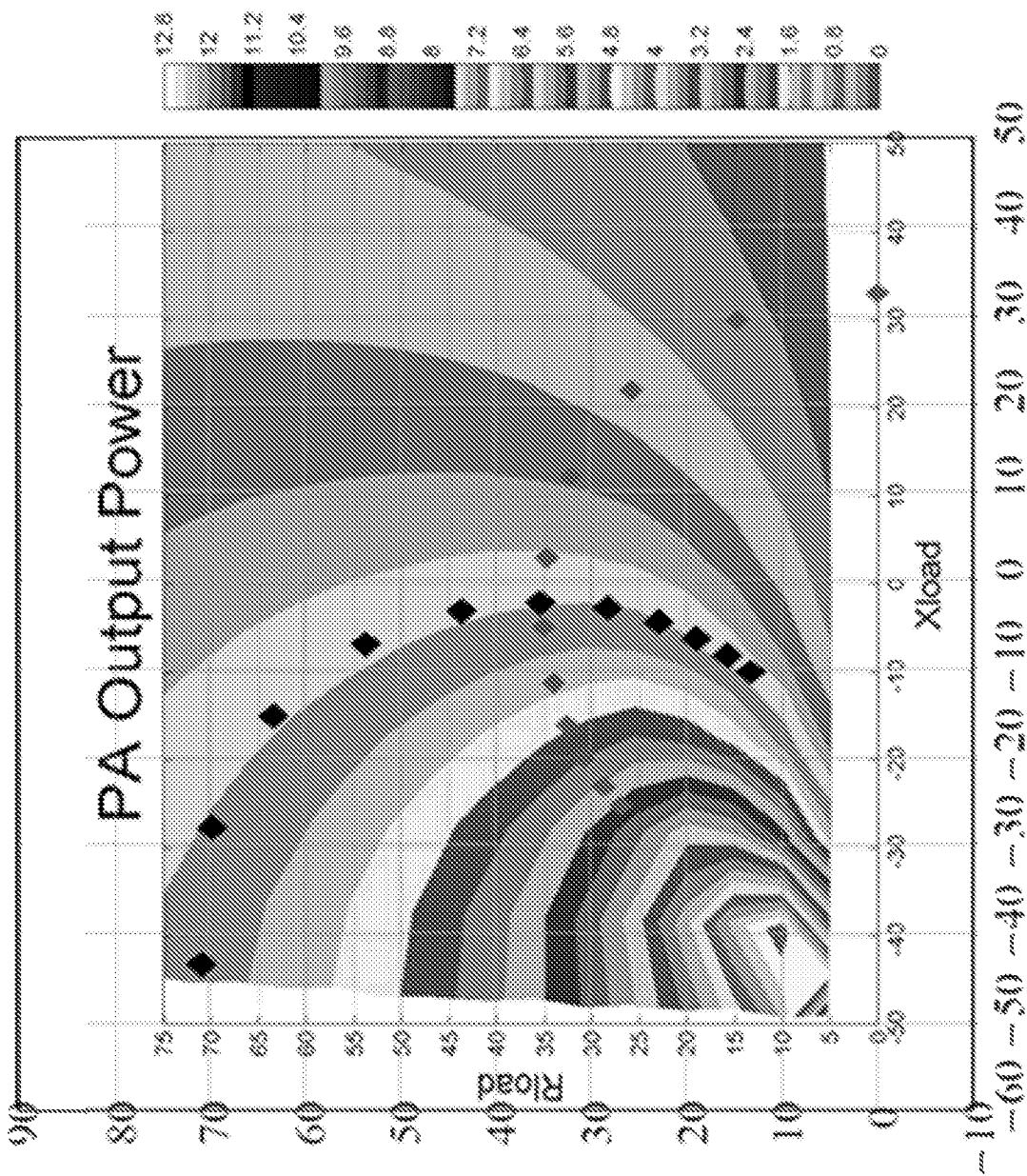

**[0019]** FIG. 10A is a contour plot showing the power output of a driver circuit as in FIG. 7 and a maximum efficiency contour as a function of real and imaginary components of the load impedance presented to the driver circuit.

**[0020]** FIG. 10B is another plot showing a selected power output contour and a maximum efficiency contour for a driver circuit as in FIG. 7 as a function of real and imaginary components of the load impedance presented to the driver circuit.

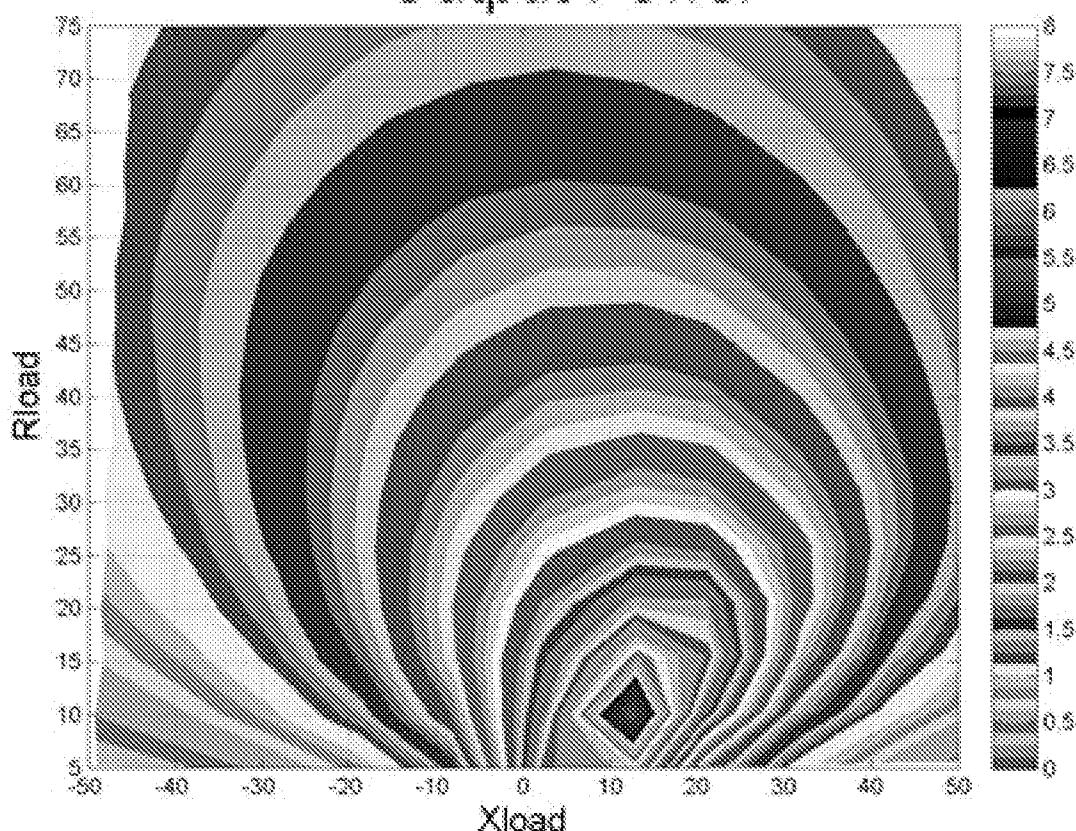

**[0021]** FIGS. 11A, 11B, 12A, and 12B show corresponding measured results as compared to FIG. 10B showing power output and efficiency of a driver circuit as in FIG. 7 as a function of real and imaginary components of the load impedance presented to the driver circuit.

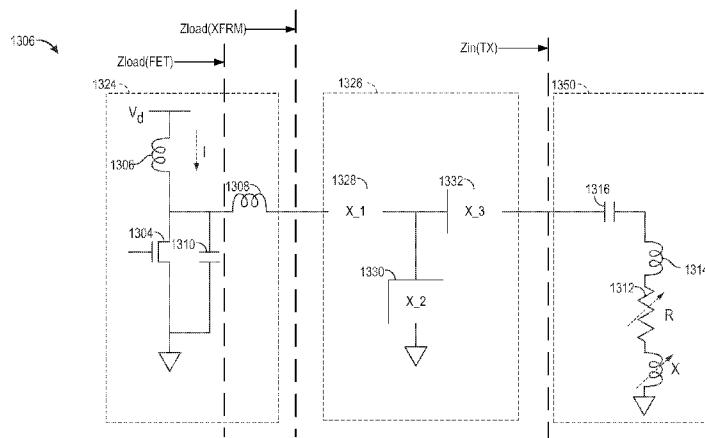

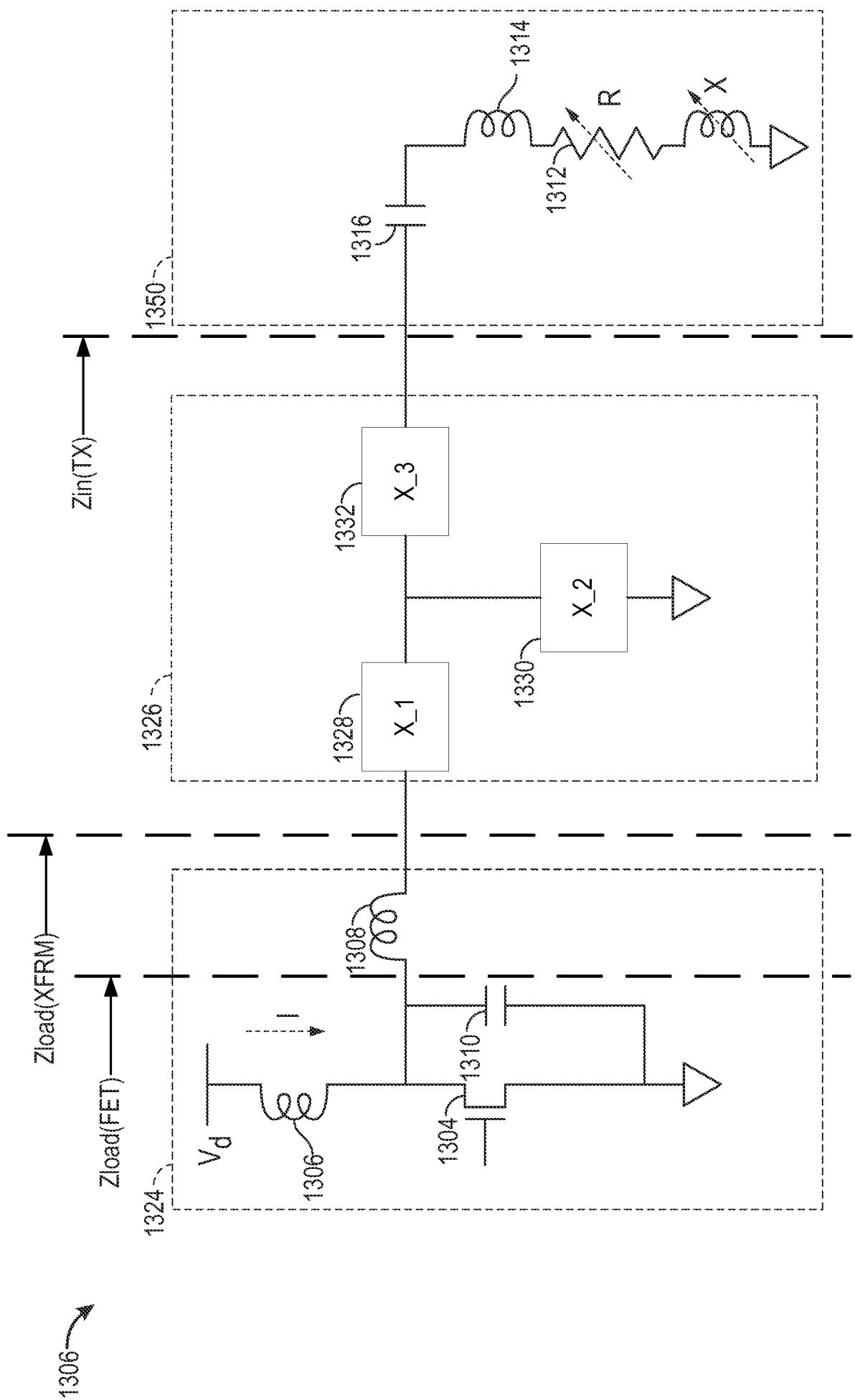

**[0022]** FIG. 13 is a schematic diagram of a driver circuit as in FIG. 7 including a filter circuit, in accordance with exemplary embodiments of the invention.

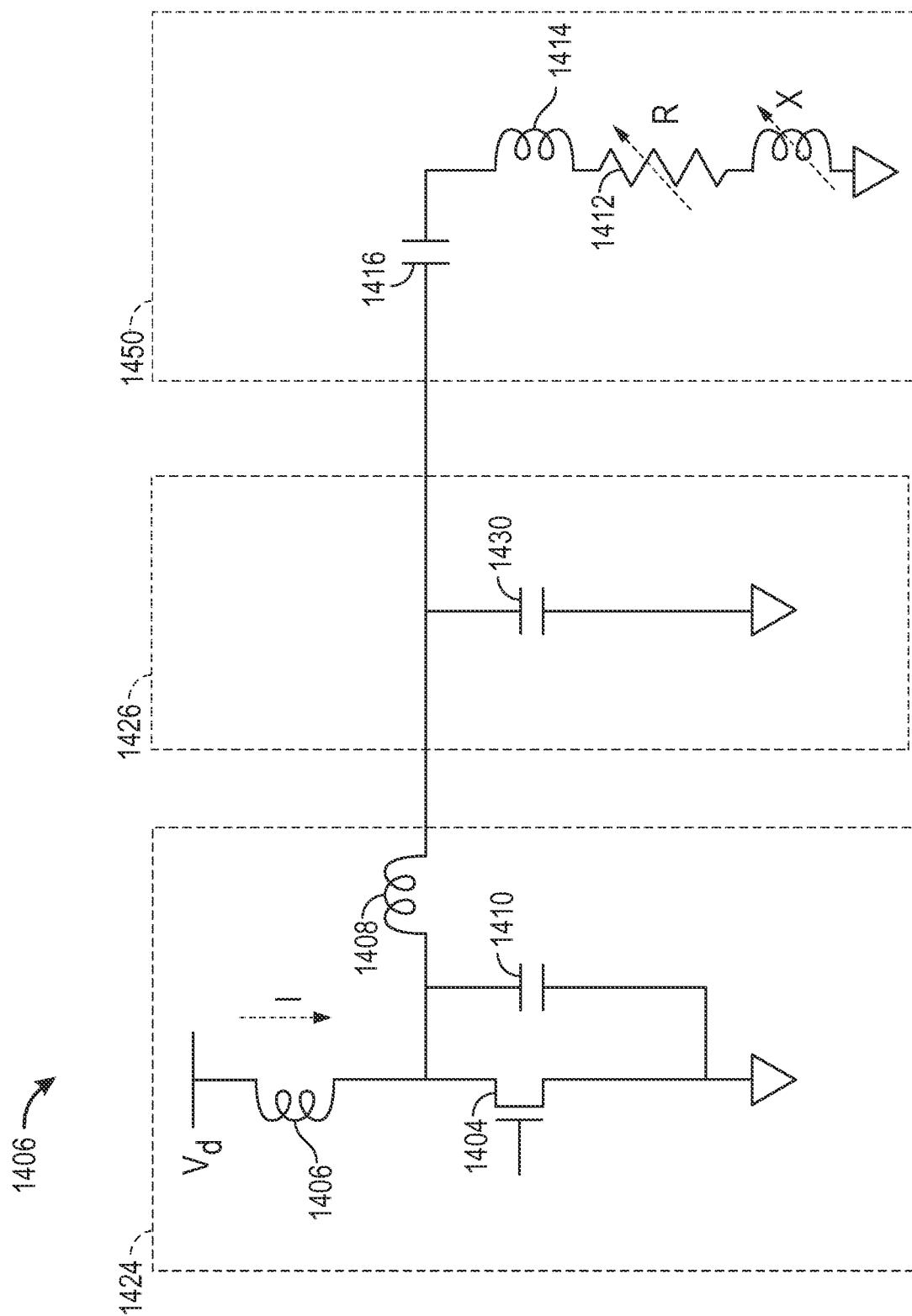

**[0023]** FIG. 14 is a schematic diagram of the circuit of FIG. 13 in accordance with an embodiment.

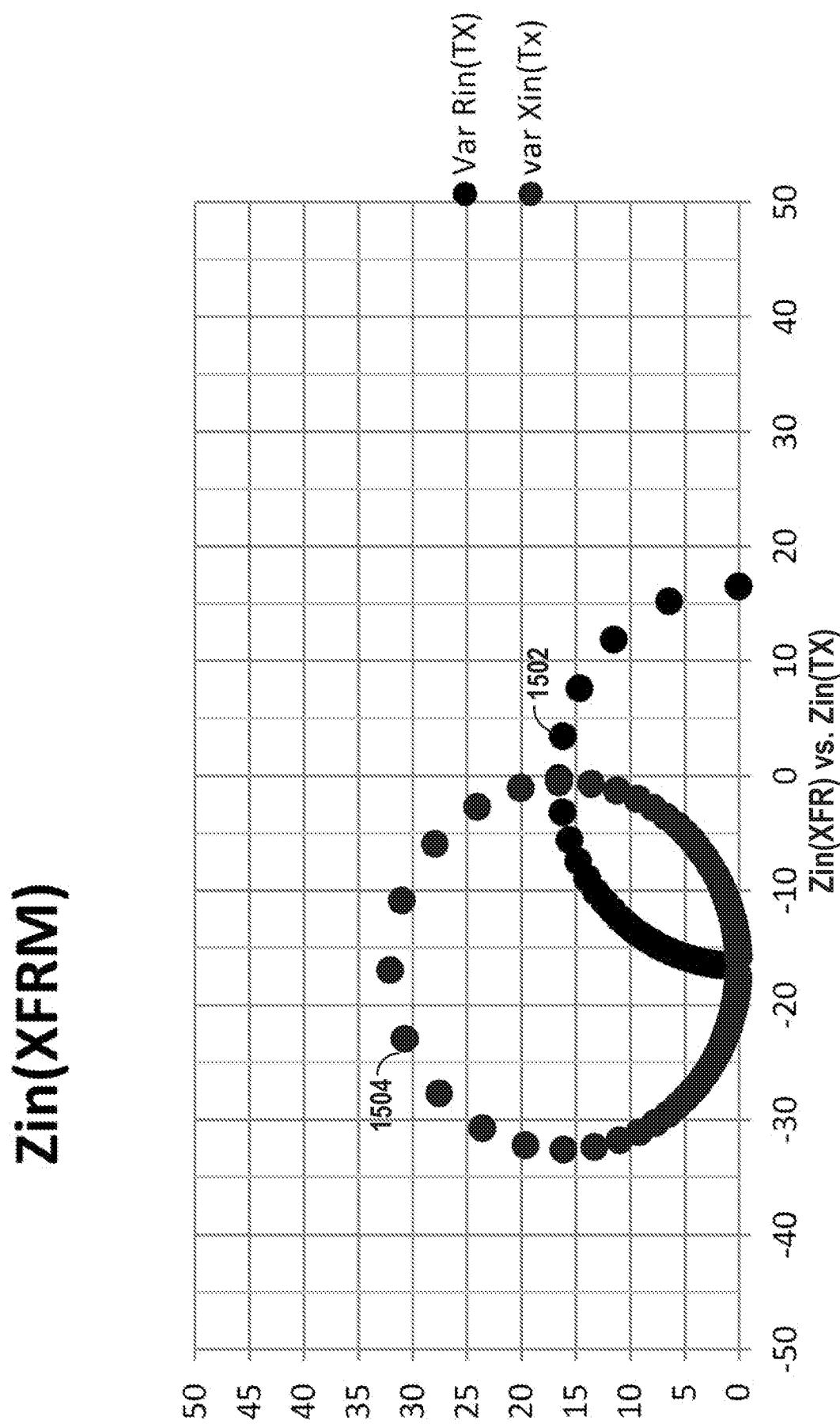

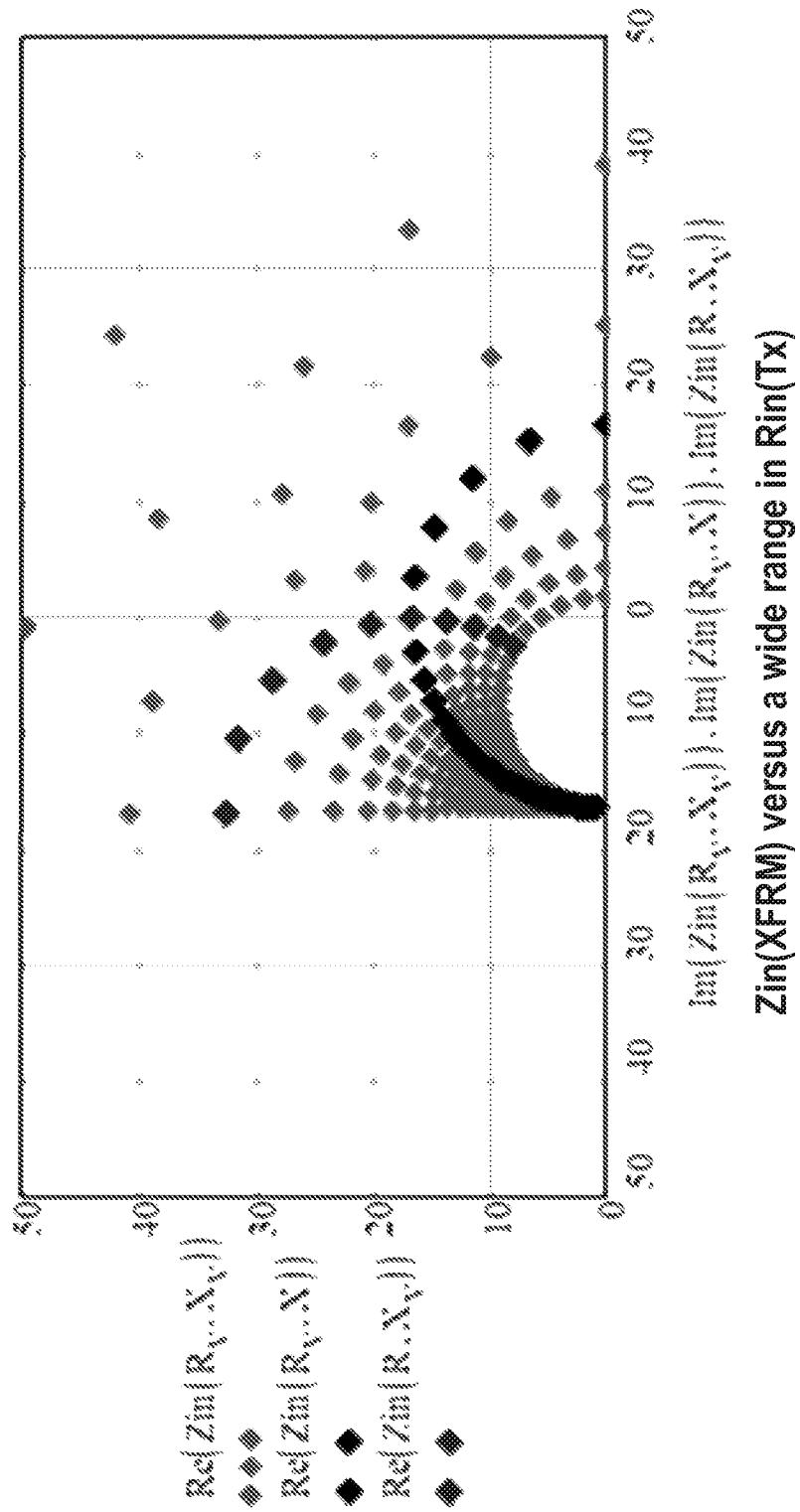

[0024] FIG. 15 is a plot showing the impedance transformed by the filter circuit versus the impedance presented to the transmit circuit as mapped to a high efficiency contour.

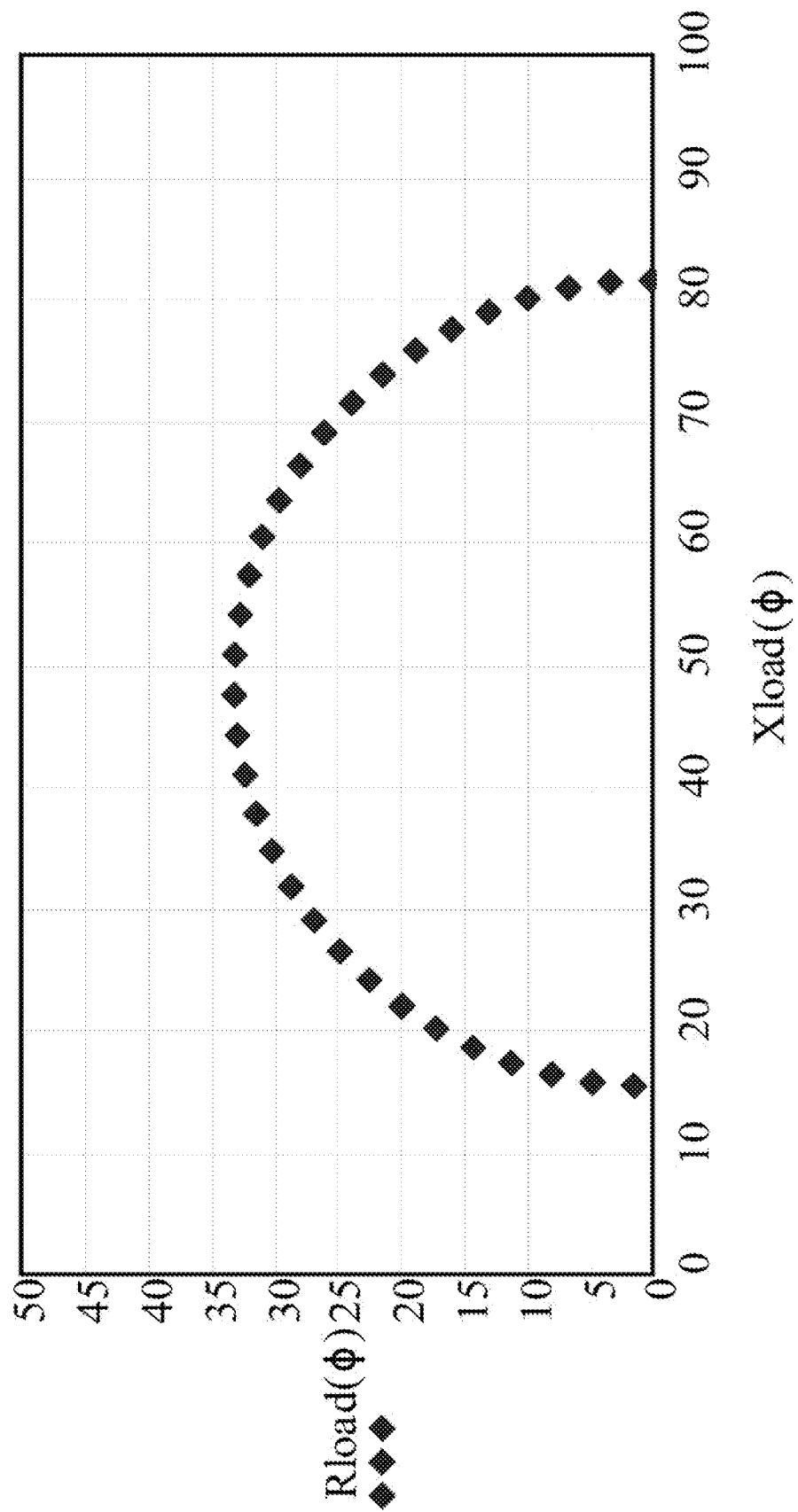

[0025] FIG. 16 is a plot showing the impedance transformed by the filter circuit over a large real range presented to the transmit circuit.

[0026] FIG. 17 is a contour plot showing the maximum efficiency of a driver circuit as a function of the real and imaginary components of the load impedance presented to the driver circuit.

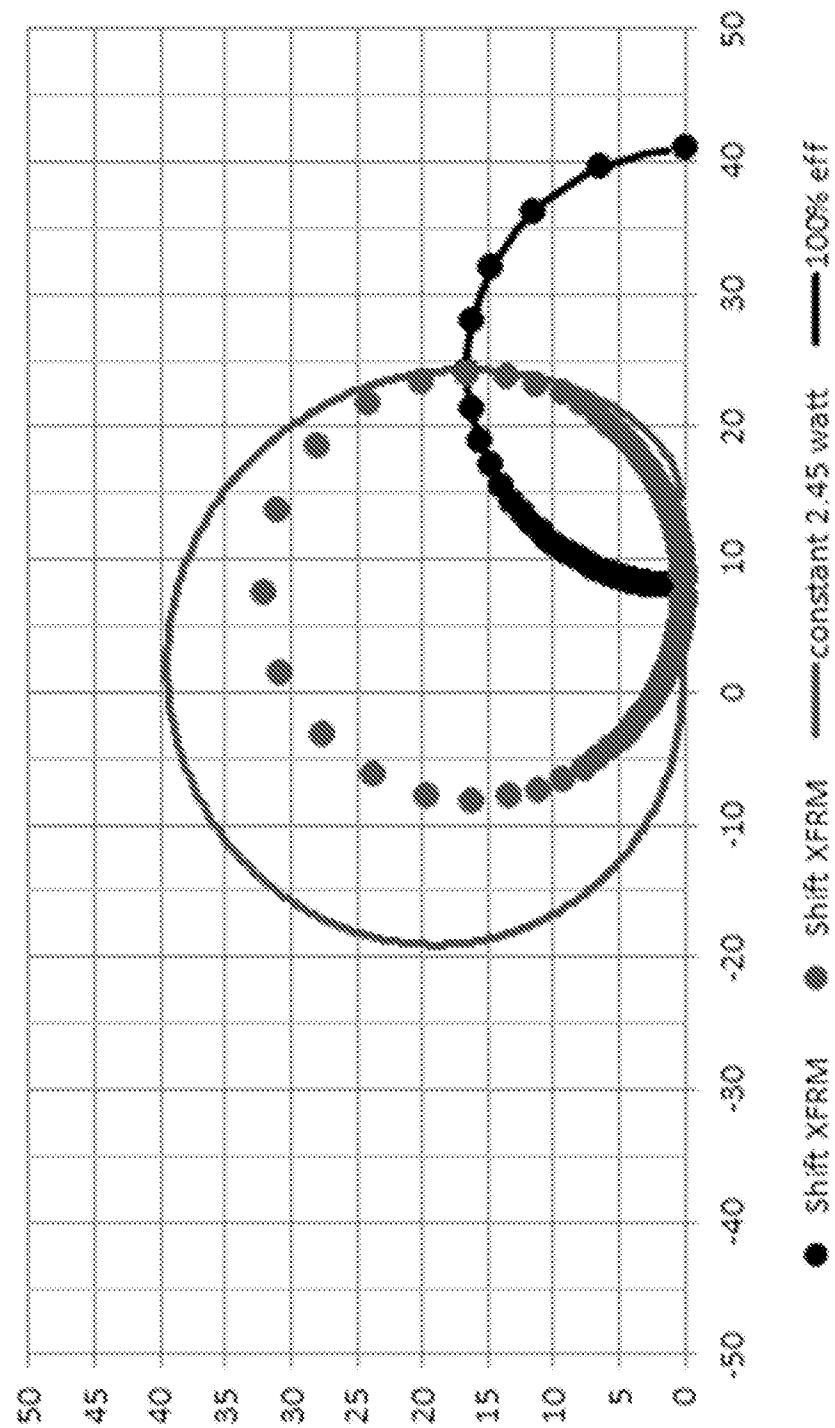

[0027] FIG. 18 is a plot showing measured impedance transformed by a filter circuit overlaid on calculated values for which power is substantially constant and efficiency is maximum.

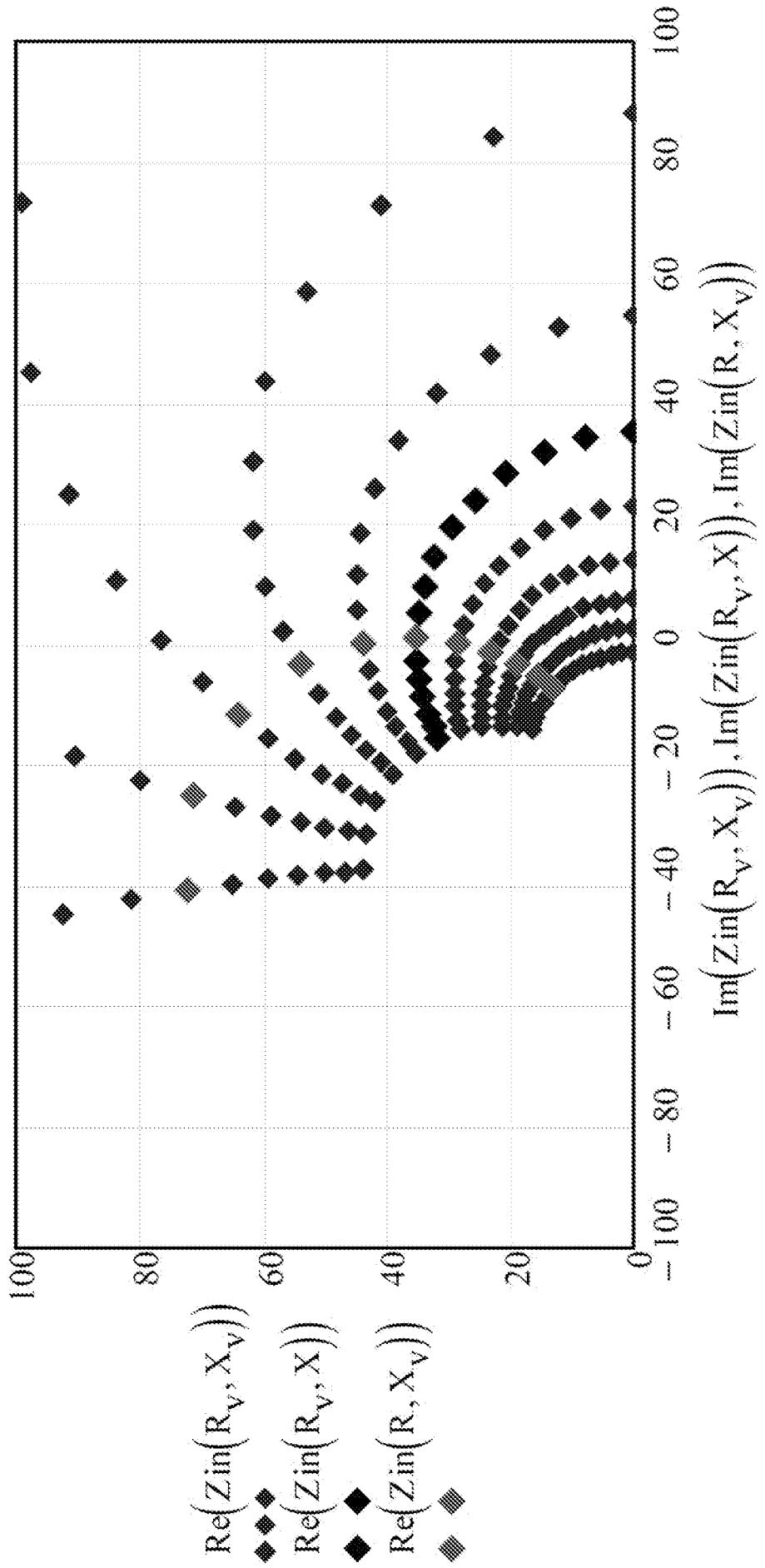

[0028] FIG. 19 is a plot showing the impedance transformed by a filter circuit when presented with a complex impedance range.

[0029] FIG. 20 shows the measured paths of a result of a filter circuit overlaid on the data of FIG. 12B.

[0030] FIG. 21 shows the measured paths of a result of a filter circuit overlaid on the data of FIG. 11B.

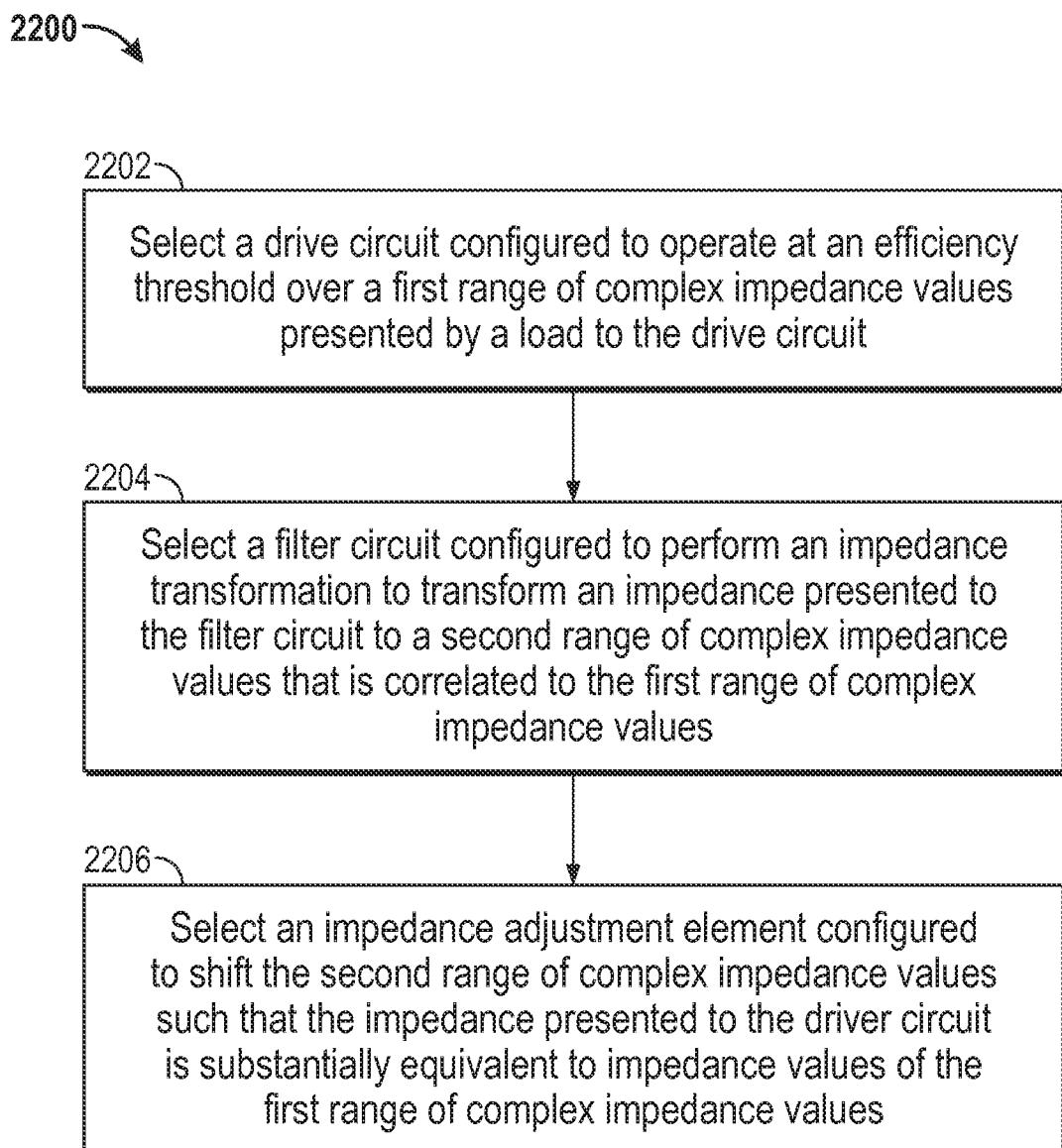

[0031] FIG. 22 is a flowchart of an exemplary method for designing a highly efficient transmit circuit.

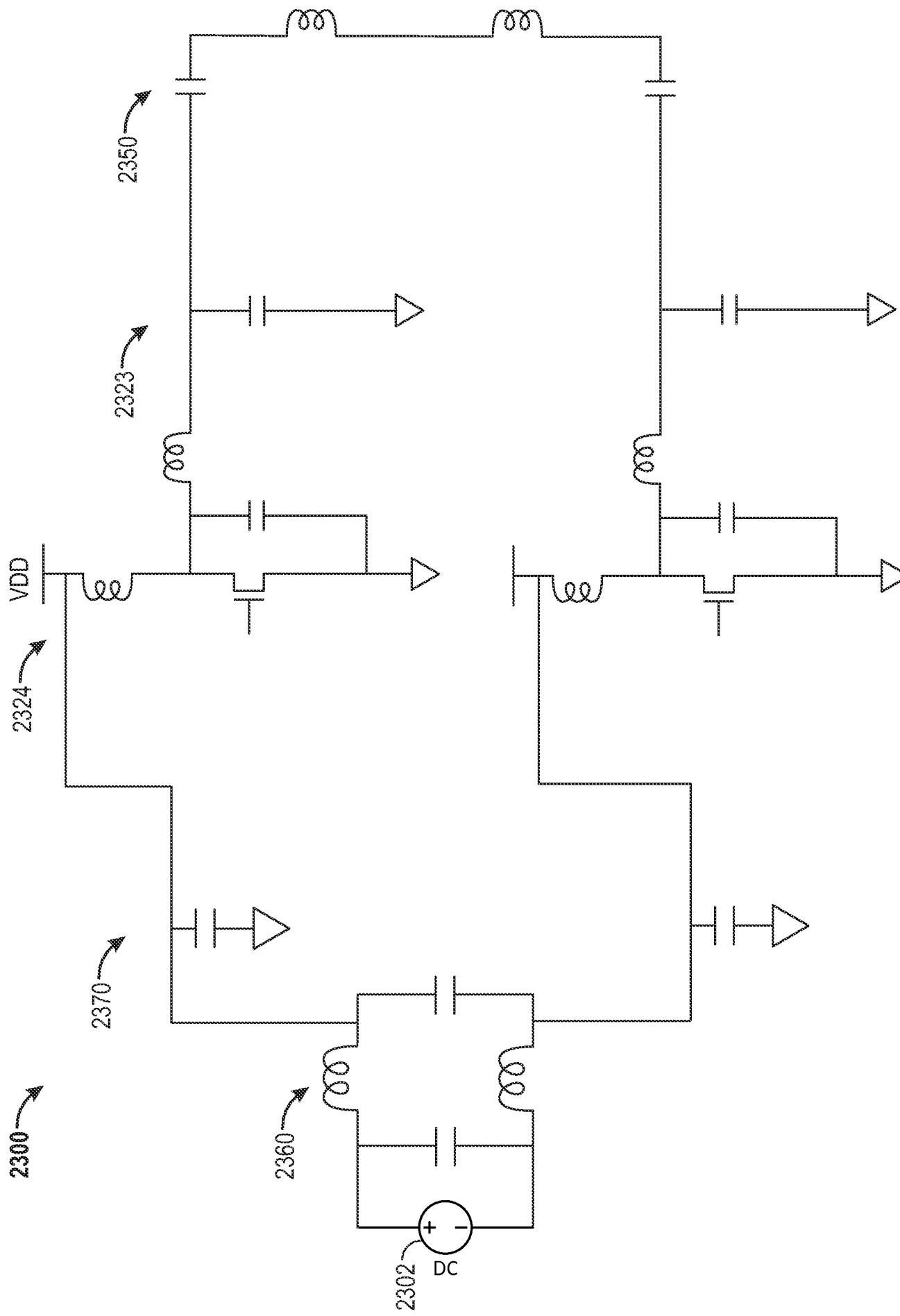

[0032] FIG. 23 is another schematic diagram of portion of transmit circuitry, in accordance with an exemplary embodiment of the invention.

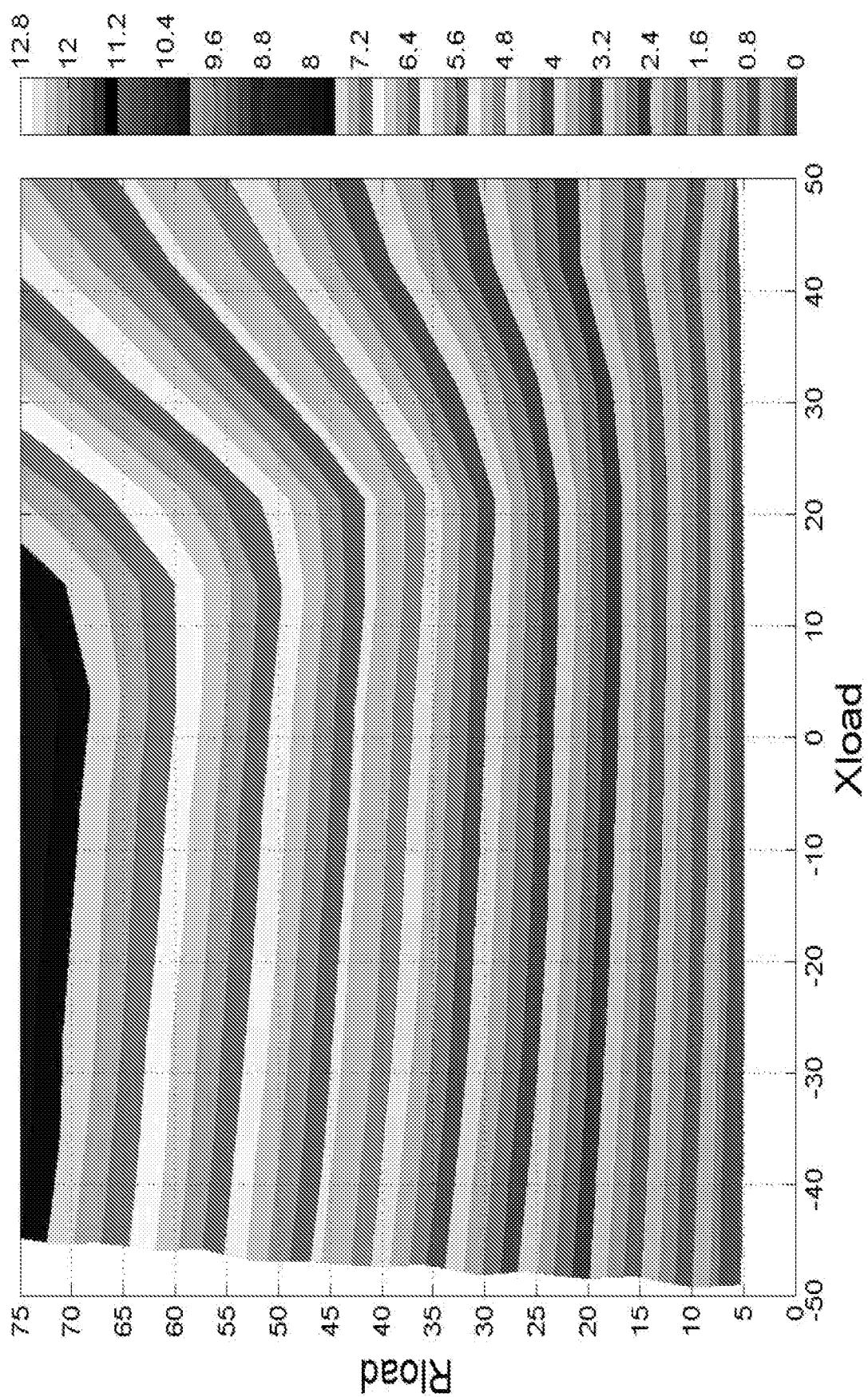

[0033] FIG. 24 shows measured results for power output from a driver circuit as in FIG. 13 as a function of real and imaginary components of the load impedance presented to the driver circuit.

[0034] The various features illustrated in the drawings may not be drawn to scale. Accordingly, the dimensions of the various features may be arbitrarily expanded or reduced for clarity. In addition, some of the drawings may not depict all of the components of a given system, method or device. Finally, like reference numerals may be used to denote like features throughout the specification and figures.

## DETAILED DESCRIPTION

[0035] The detailed description set forth below in connection with the appended drawings is intended as a description of exemplary embodiments of the invention and is

not intended to represent the only embodiments in which the invention may be practiced. The term “exemplary” used throughout this description means “serving as an example, instance, or illustration,” and should not necessarily be construed as preferred or advantageous over other exemplary embodiments. The detailed description includes specific details for the purpose of providing a thorough understanding of the exemplary embodiments of the invention. The exemplary embodiments of the invention may be practiced without these specific details. In some instances, well-known structures and devices are shown in block diagram form in order to avoid obscuring the novelty of the exemplary embodiments presented herein.

**[0036]** Wirelessly transferring power may refer to transferring any form of energy associated with electric fields, magnetic fields, electromagnetic fields, or otherwise from a transmitter to a receiver without the use of physical electrical conductors (e.g., power may be transferred through free space). The power output into a wireless field (e.g., a magnetic field) may be received, captured by, or coupled by a “receiving coil” to achieve power transfer.

**[0037]** FIG. 1 is a functional block diagram of an exemplary wireless power transfer system 100, in accordance with exemplary embodiments of the invention. Input power 102 may be provided to a transmitter 104 from a power source (not shown) for generating a field 106 for providing energy transfer. A receiver 108 may couple to the field 106 and generate output power 110 for storing or consumption by a device (not shown) coupled to the output power 110. Both the transmitter 104 and the receiver 108 are separated by a distance 112. In one exemplary embodiment, transmitter 104 and receiver 108 are configured according to a mutual resonant relationship. When the resonant frequency of receiver 108 and the resonant frequency of transmitter 104 are substantially the same or very close, transmission losses between the transmitter 104 and the receiver 108 are minimal. As such, wireless power transfer may be provided over larger distance in contrast to purely inductive solutions that may require large coils that require coils to be very close (e.g., mms). Resonant inductive coupling techniques may thus allow for improved efficiency and power transfer over various distances and with a variety of inductive coil configurations.

**[0038]** The receiver 108 may receive power when the receiver 108 is located in an energy field 106 produced by the transmitter 104. The field 106 corresponds to a region where energy output by the transmitter 104 may be captured by a receiver 106. In some

cases, the field 106 may correspond to the “near-field” of the transmitter 104 as will be further described below.

**[0039]** The transmitter 104 may include a transmit coil 114 for outputting an energy transmission. The receiver 108 further includes a receive coil 118 for receiving or capturing energy from the energy transmission. The near-field may correspond to a region in which there are strong reactive fields resulting from the currents and charges in the transmit coil 114 that minimally radiate power away from the transmit coil 114. In some cases the near-field may correspond to a region that is within about one wavelength (or a fraction thereof) of the transmit coil 114. The transmit and receive coils 114 and 118 are sized according to applications and devices to be associated therewith. As described above, efficient energy transfer may occur by coupling a large portion of the energy in a field 106 of the transmit coil 114 to a receive coil 118 rather than propagating most of the energy in an electromagnetic wave to the far field. When positioned within the field 106, a “coupling mode” may be developed between the transmit coil 114 and the receive coil 118. The area around the transmit and receive coils 114 and 118 where this coupling may occur is referred to herein as a coupling-mode region.

**[0040]** FIG. 2 is a functional block diagram of exemplary components that may be used in the wireless power transfer system 100 of FIG. 1, in accordance with various exemplary embodiments of the invention. The transmitter 204 may include transmit circuitry 206 that may include an oscillator 222, a driver circuit 224, and a filter and impedance transforming circuit 226. The oscillator 222 may be configured to generate a signal at a desired frequency, such as 468.75 KHz, 6.78 MHz or 13.56 MHz, that may be adjusted in response to a frequency control signal 223. The oscillator signal may be provided to a driver circuit 224 configured to drive the transmit coil 214 at, for example, a resonant frequency of the transmit coil 214. The driver circuit 224 may be a switching amplifier configured to receive a square wave from the oscillator 222 and output a sine wave. For example, the driver circuit 224 may be a class E amplifier. A filter and impedance transforming circuit 226 may be also included to filter out harmonics or other unwanted frequencies and match the impedance of the transmitter 204 to the transmit coil 214. The filter and impedance transforming circuit 226 may be configured to perform a variety of impedance adjustments other than just matching the impedance of the transmitter 204 to the transmit coil 214.

**[0041]** The receiver 208 may include receive circuitry 210 that may include a matching circuit 232 (or any other type of impedance adjustment circuit) and a rectifier and switching circuit 234 to generate a DC power output from an AC power input to charge a battery 236 as shown in FIG. 2 or to power a device (not shown) coupled to the receiver 108. The matching circuit 232 may be included to match the impedance of the receive circuitry 210 to the receive coil 218. The receiver 208 and transmitter 204 may additionally communicate on a separate communication channel 219 (e.g., Bluetooth, zigbee, cellular, etc.). The receiver 208 and transmitter 204 may alternatively communicate via in-band signaling using characteristics of the wireless field 206.

**[0042]** As described more fully below, receiver 208, that may initially have a selectively disableable associated load (e.g., battery 236), may be configured to determine whether an amount of power transmitted by transmitter 204 and received by receiver 208 is appropriate for charging a battery 236. Further, receiver 208 may be configured to enable a load (e.g., battery 236) upon determining that the amount of power is appropriate. In some embodiments, a receiver 208 may be configured to directly utilize power received from a wireless power transfer field without charging of a battery 236. For example, a communication device, such as a near-field communication (NFC) or radio-frequency identification device (RFID) may be configured to receive power from a wireless power transfer field and communicate by interacting with the wireless power transfer field and/or utilize the received power to communicate with a transmitter 204 or other devices.

**[0043]** FIG. 3 is a schematic diagram of a portion of transmit circuitry or receive circuitry of FIG. 2 including a transmit or receive coil 352, in accordance with exemplary embodiments of the invention. As illustrated in FIG. 3, transmit circuitry 350 used in exemplary embodiments may include a coil 352. The coil may also be referred to or be configured as a “loop” antenna 352. The coil 352 may also be referred to herein or configured as a “magnetic” antenna or an induction coil. The term “coil” is intended to refer to a component that may wirelessly output or receive energy for coupling to another “coil.” The coil may also be referred to as an “antenna” of a type that is configured to wirelessly output or receive power. The coil may also be referred to as a wireless power transfer component of a type that is configured to wirelessly transmit or receive power. The coil 352 may be configured to include an air core or a physical core such as a ferrite core (not shown).

**[0044]** As stated, efficient transfer of energy between the transmitter 104 and receiver 108 may occur during matched or nearly matched resonance between the transmitter 104 and the receiver 108. However, even when resonance between the transmitter 104 and receiver 108 are not matched, energy may be transferred, although the efficiency may be affected. Transfer of energy occurs by coupling energy from the field 106 of the transmitting coil to the receiving coil residing in the neighborhood where this field 106 is established rather than propagating the energy from the transmitting coil into free space.

**[0045]** The resonant frequency of the loop or magnetic coils is based on the inductance and capacitance. Inductance may be simply the inductance created by the coil 352, whereas, capacitance may be added to the coil's inductance to create a resonant structure at a desired resonant frequency. As a non-limiting example, capacitor 354 and capacitor 356 may be added to the transmit circuitry 350 to create a resonant circuit that selects a signal 358 at a resonant frequency. Accordingly, for larger diameter coils, the size of capacitance needed to sustain resonance may decrease as the diameter or inductance of the loop increases. Furthermore, as the diameter of the coil increases, the efficient energy transfer area of the near-field may increase. Other resonant circuits formed using other components are also possible. As another non-limiting example, a capacitor may be placed in parallel between the two terminals of the coil 350. For transmit coils, a signal 358 with a frequency that substantially corresponds to the resonant frequency of the coil 352 may be an input to the coil 352.

**[0046]** In one embodiment, the transmitter 104 (FIG. 1) may be configured to output a time varying magnetic field with a frequency corresponding to the resonant frequency of the transmit coil 114. When the receiver is within the field 106, the time varying magnetic field may induce a current in the receive coil 118. As described above, if the receive coil 118 is configured to be resonant at the frequency of the transmit coil 118, energy may be efficiently transferred. The AC signal induced in the receive coil 118 may be rectified as described above to produce a DC signal that may be provided to charge or to power a load.

**[0047]** FIG. 4 is a functional block diagram of a transmitter 404 that may be used in the wireless power transfer system of FIG. 1, in accordance with exemplary embodiments of the invention. The transmitter 404 may include transmit circuitry 406 and a transmit coil 414. The transmit coil 414 may be the coil 352 as shown in FIG. 3.

Transmit circuitry 406 may provide RF power to the transmit coil 414 by providing an oscillating signal resulting in generation of energy (e.g., magnetic flux) about the transmit coil 414. Transmitter 404 may operate at any suitable frequency. By way of example, transmitter 404 may operate at the 6.78 MHz ISM band.

**[0048]** Transmit circuitry 406 may include a fixed impedance matching circuit 406 for matching the impedance of the transmit circuitry 406 (e.g., 50 ohms) to the transmit coil 414 and a low pass filter (LPF) 408 configured to reduce harmonic emissions to levels to prevent self-jamming of devices coupled to receivers 108 (FIG. 1). Other exemplary embodiments may include different filter topologies, including but not limited to, notch filters that attenuate specific frequencies while passing others and may include an adaptive impedance match, that may be varied based on measurable transmit metrics, such as output power to the coil 414 or DC current drawn by the driver circuit 424. Transmit circuitry 406 further includes a driver circuit 424 configured to drive an RF signal as determined by an oscillator 422. The transmit circuitry 406 may be comprised of discrete devices or circuits, or alternately, may be comprised of an integrated assembly. An exemplary RF power output from transmit coil 414 may be on the order of 2.5 Watts.

**[0049]** Transmit circuitry 406 may further include a controller 410 for selectively enabling the oscillator 422 during transmit phases (or duty cycles), for adjusting the frequency or phase of the oscillator 422, and for adjusting the output power level for implementing a communication protocol for interacting with neighboring devices through their attached receivers. It is noted that the controller 410 may also be referred to herein as processor 410. Adjustment of oscillator phase and related circuitry in the transmission path may allow for reduction of out of band emissions.

**[0050]** The transmit circuitry 406 may further include a load sensing circuit 416 for detecting the presence or absence of active receivers in the vicinity of the near-field generated by transmit coil 414. By way of example, a load sensing circuit 416 monitors the current flowing to the driver circuit 424, that may be affected by the presence or absence of active receivers in the vicinity of the field generated by transmit coil 414 as will be further described below. Detection of changes to the loading on the driver circuit 424 are monitored by controller 410 for use in determining whether to enable the oscillator 422 for transmitting energy and to communicate with an active receiver. As described more fully below, a current measured at the driver circuit 424 may be used to

determine whether an invalid device is positioned within a wireless power transfer region of the transmitter 404.

**[0051]** The transmit coil 414 may be implemented with a Litz wire or as an antenna strip with the thickness, width and metal type selected to keep resistive losses low. In a one implementation, the transmit coil 414 may generally be configured for association with a larger structure such as a table, mat, lamp or other less portable configuration. Accordingly, the transmit coil 414 generally may not need “turns” in order to be of a practical dimension. An exemplary implementation of a transmit coil 414 may be “electrically small” (i.e., fraction of the wavelength) and tuned to resonate at lower usable frequencies by using capacitors to define the resonant frequency.

**[0052]** The transmitter 404 may gather and track information about the whereabouts and status of receiver devices that may be associated with the transmitter 404. Thus, the transmitter circuitry 404 may include a presence detector 480, an enclosed detector 460, or a combination thereof, connected to the controller 410 (also referred to as a processor herein). The controller 410 may adjust an amount of power delivered by the driver circuit 424 in response to presence signals from the presence detector 480 and the enclosed detector 460. The transmitter 404 may receive power through a number of power sources, such as, for example, an AC-DC converter (not shown) to convert conventional AC power present in a building, a DC-DC converter (not shown) to convert a conventional DC power source to a voltage suitable for the transmitter 404, or directly from a conventional DC power source (not shown).

**[0053]** As a non-limiting example, the presence detector 480 may be a motion detector utilized to sense the initial presence of a device to be charged that is inserted into the coverage area of the transmitter 404. After detection, the transmitter 404 may be turned on and the RF power received by the device may be used to toggle a switch on the Rx device in a pre-determined manner, which in turn results in changes to the driving point impedance of the transmitter 404.

**[0054]** As another non-limiting example, the presence detector 480 may be a detector capable of detecting a human, for example, by infrared detection, motion detection, or other suitable means. In some exemplary embodiments, there may be regulations limiting the amount of power that a transmit coil 414 may transmit at a specific frequency. In some cases, these regulations are meant to protect humans from electromagnetic radiation. However, there may be environments where a transmit coil

414 is placed in areas not occupied by humans, or occupied infrequently by humans, such as, for example, garages, factory floors, shops, and the like. If these environments are free from humans, it may be permissible to increase the power output of the transmit coil 414 above the normal power restrictions regulations. In other words, the controller 410 may adjust the power output of the transmit coil 414 to a regulatory level or lower in response to human presence and adjust the power output of the transmit coil 414 to a level above the regulatory level when a human is outside a regulatory distance from the electromagnetic field of the transmit coil 414.

**[0055]** As a non-limiting example, the enclosed detector 460 (may also be referred to herein as an enclosed compartment detector or an enclosed space detector) may be a device such as a sense switch for determining when an enclosure is in a closed or open state. When a transmitter is in an enclosure that is in an enclosed state, a power level of the transmitter may be increased.

**[0056]** In exemplary embodiments, a method by which the transmitter 404 does not remain on indefinitely may be used. In this case, the transmitter 404 may be programmed to shut off after a user-determined amount of time. This feature prevents the transmitter 404, notably the driver circuit 424, from running long after the wireless devices in its perimeter are fully charged. This event may be due to the failure of the circuit to detect the signal sent from either the repeater or the receive coil that a device is fully charged. To prevent the transmitter 404 from automatically shutting down if another device is placed in its perimeter, the transmitter 404 automatic shut off feature may be activated only after a set period of lack of motion detected in its perimeter. The user may be able to determine the inactivity time interval, and change it as desired. As a non-limiting example, the time interval may be longer than that needed to fully charge a specific type of wireless device under the assumption of the device being initially fully discharged.

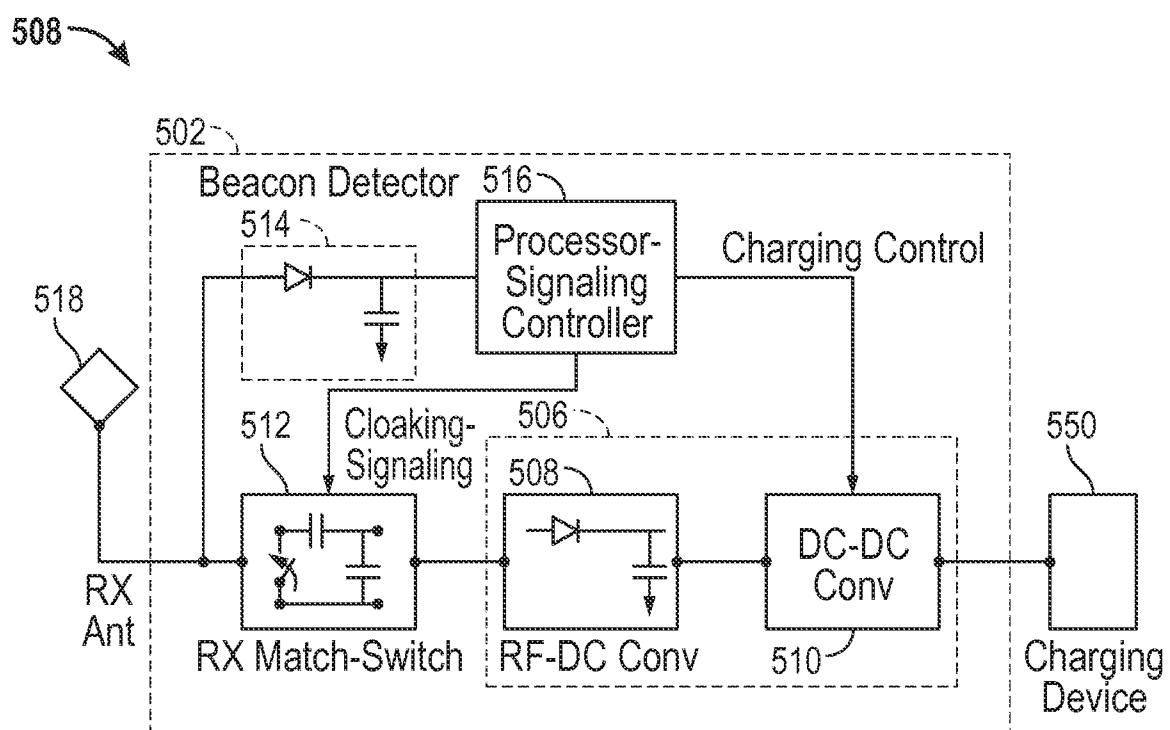

**[0057]** FIG. 5 is a functional block diagram of a receiver 508 that may be used in the wireless power transfer system of FIG. 1, in accordance with exemplary embodiments of the invention. The receiver 508 includes receive circuitry 510 that may include a receive coil 518. Receiver 508 further couples to device 550 for providing received power thereto. It should be noted that receiver 508 is illustrated as being external to device 550 but may be integrated into device 550. Energy may be propagated wirelessly to receive coil 518 and then coupled through the rest of the

receive circuitry 510 to device 550. By way of example, the charging device may include devices such as mobile phones, portable music players, laptop computers, tablet computers, computer peripheral devices, communication devices (e.g., Bluetooth devices), digital cameras, hearing aids (and other medical devices), and the like.

**[0058]** Receive coil 518 may be tuned to resonate at the same frequency, or within a specified range of frequencies, as transmit coil 414 (FIG. 4). Receive coil 518 may be similarly dimensioned with transmit coil 414 or may be differently sized based upon the dimensions of the associated device 550. By way of example, device 550 may be a portable electronic device having diametric or length dimension smaller than the diameter or length of transmit coil 414. In such an example, receive coil 518 may be implemented as a multi-turn coil in order to reduce the capacitance value of a tuning capacitor (not shown) and increase the receive coil's impedance. By way of example, receive coil 518 may be placed around the substantial circumference of device 550 in order to maximize the coil diameter and reduce the number of loop turns (i.e., windings) of the receive coil 518 and the inter-winding capacitance.

**[0059]** Receive circuitry 510 may provide an impedance match to the receive coil 518. Receive circuitry 510 includes power conversion circuitry 506 for converting a received RF energy source into charging power for use by the device 550. Power conversion circuitry 506 includes an RF-to-DC converter 508 and may also include a DC-to-DC converter 510. RF-to-DC converter 508 rectifies the RF energy signal received at receive coil 518 into a non-alternating power with an output voltage represented by  $V_{rect}$ . The DC-to-DC converter 510 (or other power regulator) converts the rectified RF energy signal into an energy potential (e.g., voltage) that is compatible with device 550 with an output voltage and output current represented by  $V_{out}$  and  $I_{out}$ . Various RF-to-DC converters are contemplated, including partial and full rectifiers, regulators, bridges, doublers, as well as linear and switching converters.

**[0060]** Receive circuitry 510 may further include switching circuitry 512 for connecting receive coil 518 to the power conversion circuitry 506 or alternatively for disconnecting the power conversion circuitry 506. Disconnecting receive coil 518 from power conversion circuitry 506 not only suspends charging of device 550, but also changes the "load" as "seen" by the transmitter 404 (FIG. 2).

**[0061]** As disclosed above, transmitter 404 includes load sensing circuit 416 that may detect fluctuations in the bias current provided to transmitter power driver circuit

410. Accordingly, transmitter 404 has a mechanism for determining when receivers are present in the transmitter's near-field.

**[0062]** When multiple receivers 508 are present in a transmitter's near-field, it may be desirable to time-multiplex the loading and unloading of one or more receivers to enable other receivers to more efficiently couple to the transmitter. A receiver 508 may also be cloaked in order to eliminate coupling to other nearby receivers or to reduce loading on nearby transmitters. This "unloading" of a receiver is also known herein as a "cloaking." Furthermore, this switching between unloading and loading controlled by receiver 508 and detected by transmitter 404 may provide a communication mechanism from receiver 508 to transmitter 404 as is explained more fully below. Additionally, a protocol may be associated with the switching that enables the sending of a message from receiver 508 to transmitter 404. By way of example, a switching speed may be on the order of 100  $\mu$ sec.

**[0063]** In an exemplary embodiment, communication between the transmitter 404 and the receiver 508 refers to a device sensing and charging control mechanism, rather than conventional two-way communication (i.e., in band signaling using the coupling field). In other words, the transmitter 404 may use on/off keying of the transmitted signal to adjust whether energy is available in the near-field. The receiver may interpret these changes in energy as a message from the transmitter 404. From the receiver side, the receiver 508 may use tuning and de-tuning of the receive coil 518 to adjust how much power is being accepted from the field. In some cases, the tuning and de-tuning may be accomplished via the switching circuitry 512. The transmitter 404 may detect this difference in power used from the field and interpret these changes as a message from the receiver 508. It is noted that other forms of modulation of the transmit power and the load behavior may be utilized.

**[0064]** Receive circuitry 510 may further include signaling detector and beacon circuitry 514 used to identify received energy fluctuations, that may correspond to informational signaling from the transmitter to the receiver. Furthermore, signaling and beacon circuitry 514 may also be used to detect the transmission of a reduced RF signal energy (i.e., a beacon signal) and to rectify the reduced RF signal energy into a nominal power for awakening either un-powered or power-depleted circuits within receive circuitry 510 in order to configure receive circuitry 510 for wireless charging.

**[0065]** Receive circuitry 510 further includes processor 516 for coordinating the processes of receiver 508 described herein including the control of switching circuitry 512 described herein. Cloaking of receiver 508 may also occur upon the occurrence of other events including detection of an external wired charging source (e.g., wall/USB power) providing charging power to device 550. Processor 516, in addition to controlling the cloaking of the receiver, may also monitor beacon circuitry 514 to determine a beacon state and extract messages sent from the transmitter 404. Processor 516 may also adjust the DC-to-DC converter 510 for improved performance.

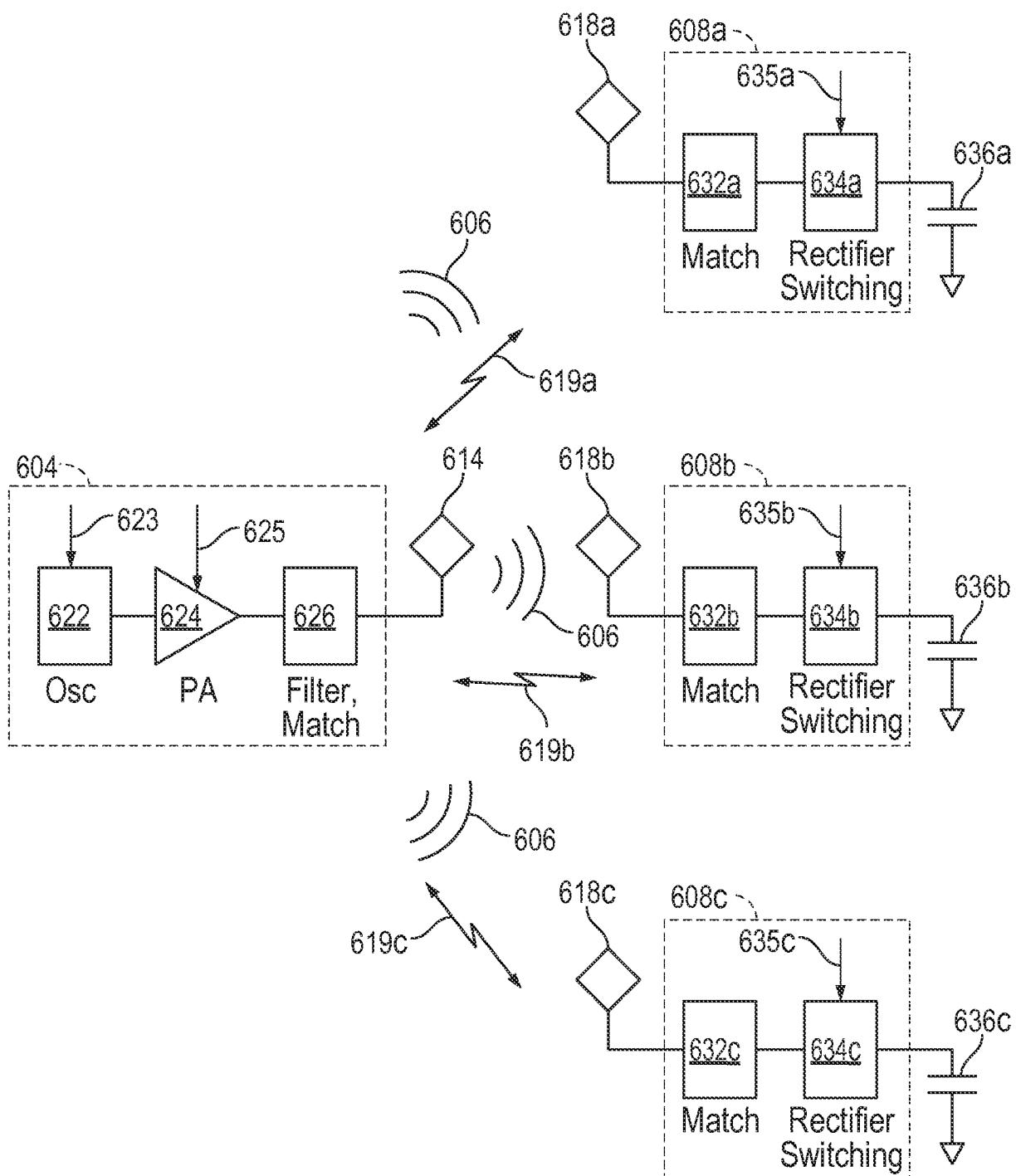

**[0066]** FIG. 6 is a functional block diagram of an exemplary wireless power transfer system 600 as in FIG. 2, where a transmitter 604 may wirelessly provide power to multiple receivers 608a, 608b, and 608c, in accordance with various exemplary embodiments of the invention. As shown in FIG. 6, a transmitter 604 may transmit power via a transmit coil 614 via a field 606. Receiver devices 608a, 608b, and 608c may receive wireless power by coupling a portion of energy from the field 606 using receive coils 618a, 618b, and 618c to charge or power respective loads 636a, 636b, and 636c. Furthermore, the transmitter 604 may establish communication links 619a, 619b, and 619c with receivers 618a, 618b, and 618c respectively. While three receivers 608a, 608b, and 608c are shown, additional receivers (not shown) may receive power from the transmitter 604.

**[0067]** In a wireless power transfer system 600 the receivers 608a, 608b, or 608c may correspond to the load the transmitter drives while transferring power. As such, the load driven by the transmitter 604 may be a function of each receiver 608a, 608b, or 608c that is wirelessly receiving power from the field 606. When receivers 608a, 608b, or 608c enter the field 606, leave the field, or disable or enable their capability to receive power from the field 606, the complex load presented to the transmitter 604 is altered accordingly. Both resistive and reactive variations of the load are altered. The behavior of the transmitter 604 may be a function of characteristics of the variable complex load. For example, the efficiency at which the transmitter 604 may provide power to a receiver 608a, 608b, or 608c may vary as the complex load of the transmitter 604 varies. Furthermore, the amount of power that the transmitter 604 outputs may also vary as the complex load varies. Each of the receivers 608a, 608b, and 608c may form a portion of the load of the transmitter 404 when each receiver 608a, 608b, and 608c is receiving power via the field 606. The total impedance of the load seen by the transmit

coil 614 may be a sum of impedances resulting from each receiver 608a, 608b, and 608c as the impedances they present to the transmit circuit 614 may combine in series.

**[0068]** In one aspect, exemplary embodiments are directed to a transmitter 604 that is suitable for efficiently charging a dynamic number of receivers 608a, 608b, and 608c. To efficiently allow for two receivers 608a and 608b to receive more power than when one receiver 608a is positioned to receive power, the transmitter 604 may be preferably designed such that the load (characterized by its complex impedance) at which the maximum power may be delivered is lower than the load at which the maximum transmitter efficiency may be provided. Furthermore, the transmitter 604 may be preferably designed to provide power at high efficiency over a resistive and reactive range of complex load values as a variable number of receivers 608a, 608b, and 608c will result in a range of different loads being presented to the transmitter 604. Otherwise, significant power losses may arise. Moreover, the transmitter 604 may be preferably designed such that the load at which maximum power is provided is greater than a total load presented by multiple receivers 608a, 608b, and 608c. In this case, the transmitter 604 may have sufficient power to supply multiple devices simultaneously.

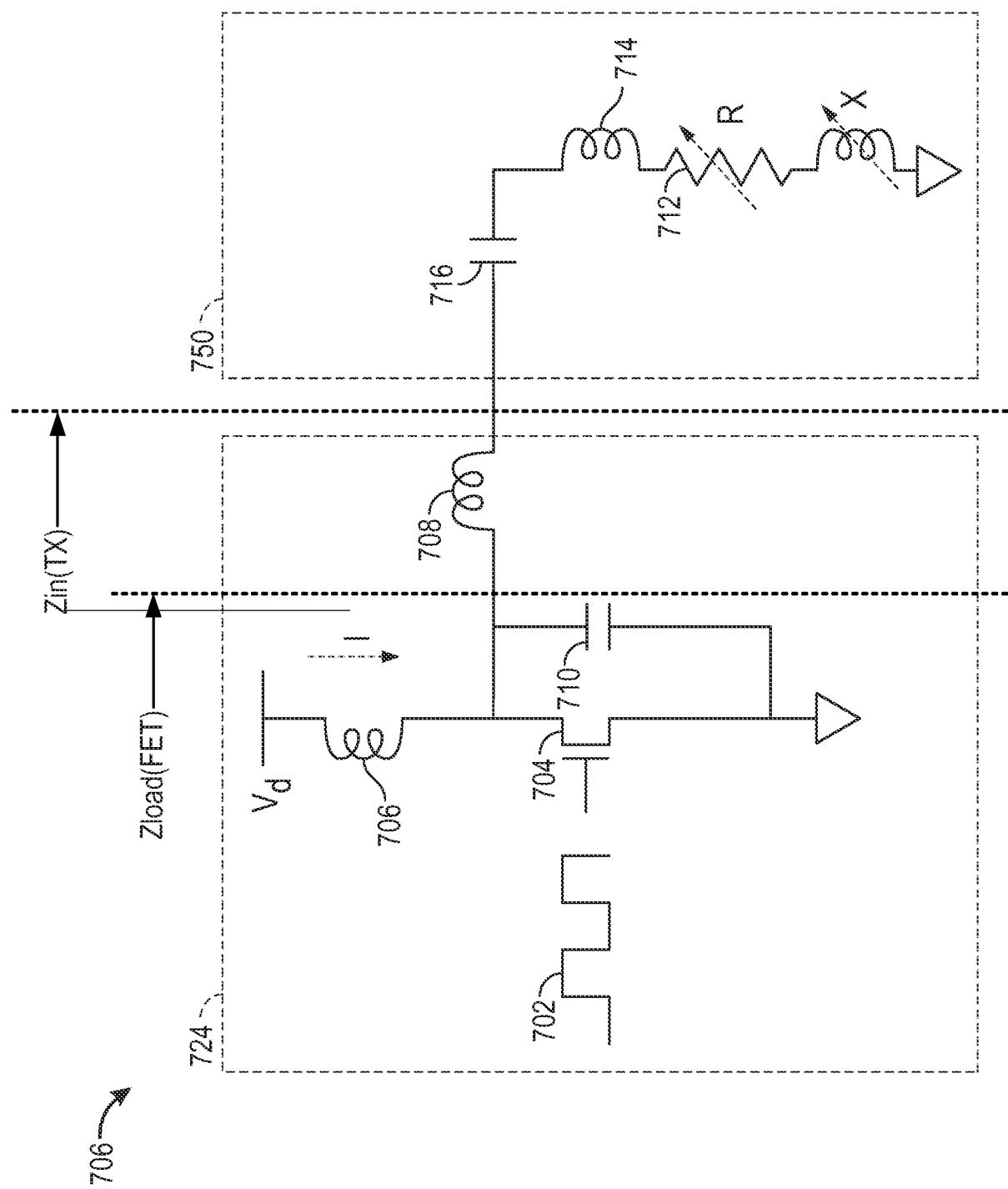

**[0069]** The transmit circuit may be driven by a driver circuit. FIG. 7 is a schematic diagram of a driver circuit 724 that may be used in the transmitter 604 of FIG. 6, in accordance with exemplary embodiments of the invention. As stated, the power output and efficiency of the driver circuit (e.g., a driver circuit 424) varies as a function of the load presented to the driver circuit 724. In some embodiments, the driver circuit 724 may be a switching amplifier. The driver circuit 724 may be configured to receive a square wave and output a sine wave to be provided to the transmit circuit 750. The driver circuit 724 is shown as an ideal (i.e., no internal resistive losses) class E amplifier. The driver circuit 724 includes a switched shunt capacitor 710 and a series inductance 708.  $V_D$  is a DC source voltage applied to the driver circuit 724 that controls the maximum power that may be delivered into a series tuned load. The driver circuit 724 is driven by an oscillating input signal 702 to a switch 704.

**[0070]** While the driver circuit 724 is shown as a class E amplifier, embodiments in accordance with the invention may use other types of driving circuits as may be known by those skilled in the art. A driver circuit 724 may be used to efficiently drive a load. The load may be a transmit circuit 750 configured to wirelessly transmit power. The transmit circuit 750 may include a series inductor 714 and capacitor 716 to form a

resonant circuit as described above with reference to FIG. 3. While the load is shown as a transmit circuit 750, embodiments in accordance with the invention may be applicable to other loads. As described above with reference to FIG. 6, the load presented to the transmit circuit 750 may be variable due to the number of wireless power receivers 608a, 608b, and 608c and may be represented by a variable resistor 712 indicative of resistive variation of the load and a variable inductor 712 indicative of reactive variation of the load. The driver circuit 724 may be driven by an input signal 702, such as from an oscillator 222 (FIG. 2). As the load presented to the transmit circuit 750 varies, for example, due to a dynamic number of wireless power receivers 638a, 638b, and 638c as described above, a load presented to the driver circuit 724 may also vary according to a wide resistance and reactance range. For example, when an additional receiver 638a is positioned to receive power from the transmit circuit 750, the receiver 638a picking up power increases the resistance presented to the transmit circuit 750 and therefore to the driver circuit 724. In addition, adding a receiver 638b that includes certain material (e.g., metal) may result in a large reactance swing presented to the transmit circuit 750 and therefore to the driver circuit 724. For example certain large receivers (e.g., a tablet) may present a negative reactance swing on the order of an excess of  $-j100$ . Power provided by the driver circuit 724 may not be flat across a load reactance range.

**[0071]** The load presented to the driver circuit 724 may be described by the impedance presented to the transmit circuit 750 including both resistive and reactive components and defined as  $Z_{in(TX)} = R_{in(TX)} + jX_{in(TX)}$ . The value of  $Z_{in(TX)}$  depends on various factors such as the transmit coil and receive coil structures, the type and number of devices to be charged, the power demanded by each receiver, and the like. The range of the load may be defined by four corner impedances:

$$R_{IN\_TX\_MIN} \leq Re\{Z_{IN\_TX}\} \leq R_{IN\_TX\_MAX}$$

$$X_{IN\_TX\_MIN} \leq Im\{Z_{IN\_TX}\} \leq X_{IN\_TX\_MAX}$$

**[0072]** FIG. 8A is a diagram showing an exemplary range of impedances that may be presented to the transmit circuit 750 during operation. FIG. 8A shows the corner impedances as described above. According to the type and number of devices to charge, the possible values for the corner impedances may vary widely. For example, for purposes of illustration,  $R_{IN\_TX\_MIN}$  may be defined as  $0 \Omega$  while  $R_{IN\_TX\_MAX}$  may be  $75 \Omega$ . In addition, for purposes of illustration,  $X_{IN\_TX\_MIN}$  may be defined as  $-50 j\Omega$  while  $X_{IN\_TX\_MAX}$  may be  $+50 j\Omega$ . In accordance with another embodiment,  $R_{IN\_TX\_MIN}$

0  $\Omega$ ,  $R_{IN\_TX\_MAX}$  is substantially 200  $\Omega$ ,  $X_{IN\_TX\_MIN}$  is substantially -200  $j\Omega$ , and  $X_{IN\_TX\_MAX}$  is substantially +200  $j\Omega$ . The principles described herein may apply to these and other complex impedance ranges. According to another exemplary embodiment, in an operating mode the real load impedance (i.e., resistance) presented to the driver circuit 724 may fall between 1  $\Omega$  and 40  $\Omega$ . Additionally, in an operating mode, the imaginary load impedance (i.e., reactance) may be between 5  $j\Omega$  and 48.7  $j\Omega$  (for example in the absence of multiple receivers). In another embodiment, impedances presented to the driver circuit 724 in an operating range may be from 4  $\Omega$  to 40  $\Omega$  and between -4  $j\Omega$  and 50  $j\Omega$ . Due to, for example, a varying number of wireless power receivers or other factors, the driver circuit 724 may be presented loads with resistances in the 0 to 80  $\Omega$  range and reactances from the -165  $j\Omega$  to 95  $j\Omega$ . It is desirable for the driver circuit 724 to operate efficiently and provide sufficient power to any load falling within this range. It is desirable to provide efficient and substantially constant power over all these ranges given various design considerations.

[0073] In one aspect, a range of impedance values presented to the driver circuit 724 may be defined by complex impedance values including real impedance values and imaginary impedance values. The real impedance values may be defined or characterized by a ratio between a first real impedance values to a second real impedance value. The ratio could be one of 2 to 1, 5 to 1, and 10 to 1. For example, the range of real impedance values presented to the driver circuit 724 could be between 8  $\Omega$  and 80  $\Omega$  (a ratio of 10:1). In another embodiment, the range could be between 4  $\Omega$  and 40  $\Omega$  (also a ratio of 10:1). In another embodiment, the range could be between substantially 1  $\Omega$  and substantially 200  $\Omega$ . In addition, the range of impedance values presented to the driver circuit 724 may be further defined by a range of imaginary impedance values. The range of the imaginary impedance values may be defined as a ratio of the magnitude of the imaginary impedance values (i.e., magnitude between minimum and maximum imaginary impedance values) to a magnitude of the real impedance values. For example, a magnitude of the real impedance values could be the magnitude of the difference between a first real impedance value and a second real impedance value. The ratio of the magnitude of the imaginary impedance values to the magnitude of the real impedance values may be at least one of 1:2, 2:1, 1:1, 2:3 etc. For example, if a real impedance range is between 8  $\Omega$  and 80  $\Omega$ , a magnitude may be 72  $\Omega$ . As such, if the ratio of the magnitude of the imaginary impedance values to the

magnitude of the real impedance values is 2 to 1, then the range of imaginary impedance values may be 144 (i.e., a range from  $-4j\Omega$  to  $+140j\Omega$ ). In any event, it is desirable to provide efficient and safe operation over a range of complex impedance values that may be defined according to various methods.

**[0074]** As described above, the power and efficiency of a driver circuit 724 are a function of the load the driver circuit 724 is driving. FIG. 8B is a plot showing efficiency 802 and output power 804 of the driver circuit 724 of FIG. 7 as a function of the real impedance of a load (i.e., load resistance) of the driver circuit 724. As shown in FIG. 8, 100% (or maximum) efficiency at a single real load impedance value may exist (e.g.,  $50\Omega$  as shown in FIG. 8) for an ideal class E amplifier. The efficiency 802 decreases as the load impedance varies in either direction. FIG. 8 also shows that the total output power 804 is similarly a function of the load impedance and which peaks at particular load impedance value (e.g.,  $20\Omega$ ). Similar results are described in Raab, "Effects of Circuit Variations on the class E Tuned Power Amplifier" (IEEE Journal of Solid State Circuits, Vol. SC-13, No. 2, 1978).

**[0075]** If the driver circuit 724 drives a load with a constant impedance, then the driver circuit 724 may be ideally designed (e.g., values of the capacitor 710 and inductor 708, etc. may be chosen) such that the driver circuit 724 operates at maximum efficiency. For example, by using the values in the plot in FIG. 8B, if the driver circuit 724 is configured to drive a load with an unvarying impedance that is substantially equal to  $50\Omega$ , the driver circuit 724 may drive the load at a maximum efficiency level. However, if the load of the driver circuit 724 varies, then the average efficiency and power delivered by the driver circuit 724 may be significantly lower than its maximum efficiency or maximum power as shown in FIG. 8. Furthermore, as the impedance of the load increases, the power delivered may not increase.

**[0076]** As shown in FIG. 7 and as described above, the load driven by the driver circuit 724 may be a wireless power transmit circuit 750. The load presented to the transmit circuit 750, given a varying number of wireless power receivers 608a, 608b, 608c (FIG. 6), may thus vary the load seen by the driver circuit 724. In this case, the total load impedance presented to the transmit circuit 750 may be the sum of each of the load impedances presented by each wireless power receiver 608a, 608b, 608c as they may combine in series. Ideally, the driver circuit 724 would provide maximum efficiency over all loads while having the power increase linearly as the resistance of the

load increases. Power would then be divided among the loads. However, as seen in FIG. 8B, maximum efficiency for the driver circuit 724 may occur for a single real load impedance value.

**[0077]** One aspect of exemplary embodiments are directed to achieving high efficiency of the driver circuit 724 as the real load impedance varies while also increasing power as the load resistance increases. In one aspect, this may allow for efficient wireless power transfer for a variable number of wireless power receivers 608a, 608b, and 608c. To provide improved efficiency of a variety of loads, the efficiency of a class E amplifier 724 is analyzed over variations in both a real component of the load impedance (i.e., resistance) and the imaginary component of the load (i.e., reactance). FIG. 9 is a contour plot showing the efficiency of a driver circuit 724 as in FIG. 7 as a function of the real and imaginary components of the load impedance presented to the driver circuit 724. The plot may correspond to a driver circuit 724 that is designed to have a maximum efficiency for a load with a resistance of  $15 \Omega$  and a reactance of  $0 \Omega$ . In the illustrated embodiment, the drive voltage is 15 V. The complex load plot of FIG. 9 shows efficiency contours 906a, 906b, and 906c at increments of 5%. For example, points along the contour 906a may represent the combinations of resistance and reactance values that correspond to a load for which the class E amplifier is 95%. The contour 902 corresponds to load impedance values that correspond to an efficiency 100%.

**[0078]** The results of the plot shown in FIG. 8B may be seen in FIG. 9 by holding the reactance at zero and varying the resistance from 0 to  $40 \Omega$  as shown by the arrow 908. The path 908 passes through the point 904 with a value of  $15 \Omega + j0 \Omega$  where efficiency is 100%. The contour 902 shows that there is a path (e.g., a range of impedances) at which efficiency is 100%. As such, rather than just analyzing efficiency over real impedance values only, analyzing efficiency for both real and imaginary impedance values (i.e., a range of resistance and reactance values) shows that there is a range of complex impedance values for which efficiency of the driver circuit 724 is 100%.

**[0079]** FIG. 10A is a contour plot showing the power output of a driver circuit 724 as in FIG. 7 as a function of real and imaginary components of the load impedance presented to the driver circuit 724. The complex load plot of FIG. 10A shows power contours 1006a, 1006b, and 1006c at 1 watt increments. For example, points along the

contour 1006b may represent combinations of resistance values and reactance values that represent an impedance value at which 5 watts of power may be delivered. Points along the contour 1006c may represent combinations of resistance values and reactance values that represent an impedance value at which 10 watts of power may be delivered. The results of the plot shown in FIG. 8B may be seen by holding the reactance at zero and varying the resistance from  $0 \Omega$  to  $40 \Omega$  as shown by the arrow 1008. The path 1008 passes through the point 1004 where efficiency (shown by the contour 902 from FIG. 9) is 100% and power delivered is a little over 6 Watts. The 100% efficiency contour 902 of FIG. 9 placed in the plot of FIG. 10 shows that there is path 902 where efficiency is 100% and where the power continually increases as shown as the contours represent increasing power. As shown in FIGS. 9 and 10, the 100% efficiency path 902 starts at an impedance of  $j24 \Omega$ , passes through  $15 + j0 \Omega$  and continues to  $-j10 \Omega$ .

[0080] FIG. 10B is another plot showing power output and efficiency of a driver circuit 724 as in FIG. 7 as a function of real and imaginary components of the load impedance presented to the driver circuit 724. The contour 902 represents the combinations of resistance and reactance values for which efficiency is maximum, where efficiency may be defined as the ratio of power delivered to the load divided by the DC power into the FET drain of the driver circuit 724. The contour 1006 represents the resistance and reactance values for which power delivered to the load is constant for a particular drive voltage  $V_d$ . While power may depend on both the drive voltage  $V_d$  and the complex load, efficiency may depend on the load alone. The drive voltage  $V_d$  and power output may be chosen such that the power contour 1006 passes through the efficiency contour 902 at the peak value of the load to the FET of the driver circuit 724. Accordingly, the contours 1006 and 902 are exemplary and indicate that there is a range of complex values for which the driver circuit 724 is efficient and for which power is constant. It is noted that the contours shown in FIG. 10B may reflect the load seen by the FET of the driver circuit 724,  $Z_{load}(FET)$  which may be offset from results that would be in terms of  $Z_{in}(TX)$ . The difference may be due to a series inductance. However,  $Z_{load}(FET)$  and  $Z_{load}$  may be used interchangeably. FIG. 10B shows one particular results for when a drive voltage is on the order of 10 volts and resulting power is on the order of 2.45 Watts. In this case values were selected to result in the power contour 1006 passing through the efficiency circle at the peak value of  $R_{load}(FET)$  as shown. As a result when the  $Z_{load}$  is  $16.55 + 24.3j$  ohms, at 10V dc, a single sided

driver circuit 724 delivers 2.45 watts with maximum efficiency into the real part of the load. These values are merely exemplary and for purposes of illustration of values that may be found to define the maximum efficiency and constant power contours.

**[0081]** As indicated above, however, a wide range of reactive and resistive impedances may be presented to the driver circuit 724 from a transmit circuit 750 due to, for example, a variable number of receivers being positioned to receive power from the transmit circuit 750. Impedance values presented to the driver circuit 724 as a result of the variation of impedance presented to the transmit circuit 750 may result in reduced efficiency and fluctuations in the amount of power delivered.

**[0082]** FIGS. 11A, 11B, 12A, and 12B show corresponding measured results as compared to FIG. 10 showing power output and efficiency of a driver circuit 724 as in FIG. 7 as a function of real and imaginary components of the load impedance presented to the driver circuit 724. The measured results show power and efficiency contours as described above and when taking into account various losses or other effects of the system. For example, the results may illustrate the effects of losses of the FET of the driver circuit (e.g., as compared to an ideal switch) and the effect of the resonant series LC circuit of the transmit circuit 750 between the switch and the load. As such FIGS. 11A, 11B, 12A and 12B show measured efficiency and power contours when all load values within the range defined by  $R_{IN\_TX\_MIN} = 0 \Omega$ ,  $R_{IN\_TX\_MAX} = 75 \Omega$ ,  $X_{IN\_TX\_MIN} = -50 j\Omega$ , and  $X_{IN\_TX\_MAX} = +50 j\Omega$  are presented to a driver circuit 724. The results may reflect the output from a double-sided driver circuit 724 (i.e., including two driver circuits 724 of FIG. 7) operating a particular driver voltage (e.g., both driven by a 5.5 V DC supply). In using the double-sided driver circuit 724, load to each FET of the driver circuit 724 is  $\frac{1}{2}$  that seen in FIGS. 11A, 11B, 12A, and 12B.

**[0083]** In accordance, FIG. 11A shows measured efficiency contours for a tuned double-sided driver circuit 724 without an added series inductance 708 for the load range as noted above. FIG. 11B shows measured efficiency contours for a tuned double-sided driver circuit 724 with an added series inductance 708. In accordance FIG. 12A shows measured power contours for a tuned double-sided driver circuit 724 without an added series inductance 708 for a wide load range as described above. FIG. 11B shows measured power contours for a tuned double-sided driver circuit 724 with an added series inductance 708. Thus, FIGS. 11A–B show different powers for the same load, illustrating the effect of  $V_D$  on power. FIGS. 12A–B show output power.

**[0084]** It is noted that the measured efficiency and power contours of FIGS. 11A, 11B, 12A, and 12B are merely exemplary for a particular configuration of driver circuit 724 and are used for purposes of illustration. More specifically, FIGS. 11A, 11B, 12A, and 12B provide values illustrating the range of complex impedance values for which the driver circuit 724 is efficient and for which power is constant. It is noted that the contour plots of FIGS. 11A, 11B, 12A, and 12B may correspond to results from a double-sided driver circuit 724 configuration. To compare with a single sided driver circuit 724, the values would be divided by two. As compared to FIG. 10B, it is noted that the constant power contours shown in FIGS. 12A and 12B are still circular in form, although distorted due to the effect of body diodes inherent in FET 704. Likewise, the efficiency contours shown in FIGS. 11A are similar to FIG. 10B, however efficiency values decrease as the load resistance to the FET decreases which may be due to losses in the FET 704.

**[0085]** Based on the results of FIGS. 9-12, certain aspects of exemplary embodiments are directed to an impedance transform circuit (also referred to herein as a filter circuit) located between the driver circuit 724 and the transmit circuit 750 that transforms a variable load impedance presented to the transmit circuit 750 into values for which the driver circuit 724 is highly efficient and where power is substantially constant. These values may be defined by the high efficiency and constant power contours as shown in FIGS. 9-12. The variable load presented to the transmit circuit 750 may vary widely over both reactance and resistance as further described above. As will be indicated below, the transform circuit is configured to transform the impedance to maintain the efficiency at a high level while keeping the power transfer as constant as possible over a wide range in reactive load. This may allow for a driver circuit 724 in a wireless power transmitter 604 to efficiently provide power as the load presented to the transmit circuit 750 varies reactively and resistively due to a dynamic number of wireless power receivers 608a, 608b, and 608c (FIG. 6).

**[0086]** In one embodiment, a filter circuit is used to transform a variable load impedance presented to a transmit circuit 750 into complex load values for which the driver circuit 724 may be highly efficient and for which power is constant. FIG. 13 is a schematic diagram of a driver circuit 1324 as in FIG. 7 including a filter circuit 1326, in accordance with exemplary embodiments of the invention. The filter circuit 1326 (i.e., a transform circuit) is positioned between the driver circuit 1324 and the transmit circuit

1350. As shown the transmit circuit 1350 shows a variable load 1312 including both variations in resistance and variations in reactance. The filter circuit 1326 includes three reactive components, X1 1328, X2 1330, and X3 1332. In some embodiments, X1 1328 and X3 1332 are series inductors, while X2 1330 is a shunt capacitor. The filter circuit 1326 is configured to transform the impedance  $Z_{in(TX)}$  presented by the transmit circuit 1350 into an impedance  $Z_{load(XFRM)}$  presented to the driver circuit 1324 including the series inductor 1308. This impedance,  $Z_{load(XFRM)}$  is then shifted by the series inductance 1308 so as to “best” fit the load lines for which the driver circuit 1324 is maximally efficient with a constant or steady power as the load varies. The full transformed impedance presented to the FET 1304 is defined by  $Z_{load(FET)}$ . The component values for the filter circuit 1326 and series inductance 1308 are configured to increase power linearly with the resistive portion of the load presented the transmit circuit 1350 and have as high efficiency as possible as the reactance varies. The values of the components are selected to provide a balance between maximizing efficiency versus variation in the resistive portion  $R_{in(TX)}$  and minimizing load power variation versus variation in the reactive portion  $X_{in(TX)}$ .

**[0087]** While also operating as a low pass filter configured to reduce harmonics in the signal, the filter circuit 1326 is configured to convert linear variations in  $Z_{in(TX)}$  to circular variations in  $Z_{in(XFRM)}$ . As noted above, the series reactance 1308 shifts the load into a particular range for the FET 1304. The filter circuit 1326 is configured as a T network. While other configurations are also contemplated according to the embodiments described herein, the T network may reduce the number of components.

**[0088]** It is noted that according to some embodiments, where series inductors are used for reactance components X1 1328 and X3 1332, high power requirements may increase the cost of the inductors. As such, it may be desirable to eliminate one or more of the reactance components. Using the T network may allow for eliminating the reactance components X1 1328 and X3 1332 which may be absorbed into the coil 1314 and/or the series inductor 1308. FIG. 14 is a schematic diagram of the circuit of FIG. 13 in accordance with an embodiment. As shown, reactance component X2 1330 of FIG. 13 is shown as a shunt capacitor 1430. Reactance components X1 and X3 of FIG. 14 are absorbed into the coil 1414 and series inductor 1408. As such, the filter circuit 1426 includes only of a shunt capacitor. It is noted that the values of X1 and X3 are still selected based on the principles described herein to achieve the desired impedance

transformation, and as such, the amount of the determined values of X1 and X3 is taken into account when being absorbed into the other series elements. It is noted that the shunt capacitor 1430 could be replaced by a single shunt capacitor network (e.g., some configuration of parallel or series connected capacitors). However, only a shunt network is needed. This may reduce the number of components and reduce other high cost inductors. The values of the reactive components 1410, 1408, 1430, 1416, and 1414 are selected such that the circuit 1406 is configured to transform the impedance into values that correspond to high efficiency for the driver circuit 1424 with constant power. For example, the shunt capacitor 1430 is selected based on an impedance transformation ratio which is proportional to output power or current at a fixed supply voltage. The series L value 1408 may then be selected from the shunt C value. As such the circuit 1406 may work efficiently across a wide reactance range while maintaining its output power, and reactance load switches to tune out the reactance swing may be unnecessary. As such, a single shunt capacitor network positioned between a class E amplifier and a resonant transmit circuit, when combined with tuning adjustments of the existing inductances, can provide a particular impedance transform as described herein. This includes delivering power linearly versus the real load over a wide reactance range, having reduced sensitivity to the reactive load changes and providing high efficiency for substantially maximum power. Furthermore, the value of the shunt capacitor 1430 may be selected to determine an impedance ratio of the filter transform that may allow trading the impedance ratio off against other factors such as mutual coupling between a source coil (i.e., transmitter) and the load coil (i.e., receiver).

**[0089]** With reference again to FIG. 13, values of the components of the filter circuit 1326 may be chosen such that the varying impedance of the transmit circuit 1350 (due to receivers 608a, 608b, and 608c) is transformed by the filter circuit 1326. The transformed impedance values may correspond to impedance values (such as those as shown in FIGS. 9 and 10) that provide highly efficient driver circuit 1324 operation while also increasing the flatness of power delivery given wide reactance swings. The component values of the filter circuit 1326 are chosen to perform an impedance transform that transforms the impedance of the load 1312 seen by the transmit coil 1350 into a complex impedance that fits as closely as possible to complex values that provide high efficiency and constant power as shown in FIGS. 9-12. In some embodiments as will be further described below, the selection of the series inductance 1308 of the driver

circuit 1324 is used in conjunction with the filter circuit 1326 to shift the impedance transformation performed by the filter circuit 1326 to match as closely as possible to complex values that provide high efficiency and constant power.

**[0090]** In one exemplary embodiment, the filter circuit 1326 may be configured to modify the impedance presented to the filter circuit 1326 (e.g., the impedance of the transmit circuit 1350 due to a variable number of receivers 608a, 608b, and 608c) to maintain the efficiency of a driver circuit 1324 at a level that is within 20% of a maximum efficiency of the driver circuit 1324 within some complex impedance range with real and reactive variations. In another embodiment, efficiency may be maintained at a level that is within 10% or lower of a maximum efficiency of the driver circuit 1324. The filter circuit 1326 is further configured to maintain a substantially constant power output level irrespective of the reactive variations within the complex impedance range presented from the transmit circuit 1350. Moreover, the filter circuit 1326 is configured to maintain a substantially linear relationship between the power output level and the resistive variations within the complex impedance range. The filter circuit 1326 may be referred to as or be configured as an impedance transformation network. The range of impedance values presented to the filter circuit 1326 that are transformed by the filter circuit 1326 may be characterized by a range of complex impedance values. The range of complex impedance values may be within a range defined by a first real impedance value and a second real impedance value, where a ratio between the first real impedance value to the second real impedance value is at least two to one. In addition, the range of reactive variation of the impedance may be related to the real impedance range. For example, the magnitude of the range of reactive variation for which the filter is configured to maintain efficiency at 20% of a maximum efficiency may be substantially twice the magnitude of the real impedance range. The center of the reactive impedance range may be substantially centered at the instantaneous real impedance value (i.e., resistive) presented to the transmit circuit. The filter circuit 1326 is further configured to maintain a substantially constant power level irrespective of the reactive variations within the impedance range. In addition, the filter circuit 1326 is configured to maintain a substantially linear relationship between the power level and the real variations within the impedance range. For example, the range of real (i.e., resistive) impedance values may be substantially between  $8 \Omega$  and  $80 \Omega$  or  $4 \Omega$  and  $40 \Omega$  having a ratio of 10 to 1. In this case, the range of imaginary (i.e., reactive) may have

a magnitude on the order of 144 and could span anywhere from  $-74 \text{ j}\Omega$  to  $+152 \text{ j}\Omega$  depending on an instantaneous value of the real impedance. In another embodiment, the range of real impedance values may be between substantially  $1 \Omega$  and substantially  $200 \Omega$ . Furthermore, in an embodiment, the range of imaginary impedances may be between substantially  $-200 \text{ j}\Omega$  and  $+200 \text{ j}\Omega$ . Within this range of real and imaginary impedances (i.e., resistive and reactive), the filter circuit 1326 and selection of series inductance 1308 is configured to maintain the efficiency of the driver circuit 1324 within 20% of a maximum efficiency of the driver circuit 1324, maintain a substantially constant power level irrespective of the reactive variations, and/or maintain a substantially linear relationship between the power level and the real variations within the impedance range.

**[0091]** The imaginary impedance range may also be defined by a first imaginary impedance value and a second imaginary impedance value. The first imaginary impedance value and the second imaginary impedance value may define approximate minimum and maximum imaginary impedance values. The range of imaginary impedance values (i.e., the magnitude of the difference between the first imaginary impedance value and the second imaginary impedance value) may be defined by a ratio of the magnitude of the imaginary impedance value to the magnitude of the real impedance value (e.g., equal to a magnitude of the difference between the first real impedance value and the second real impedance value). The ratio may be at least one of 1:2, 2:1, 1:1, 2:3, 3:2, etc. For example, if the magnitude of the real impedance values is  $72 \Omega$ , and the ratio is 2:1, the magnitude of the range of imaginary impedance values may be  $144 \text{ j}\Omega$  (e.g., a range of a minimum to a maximum). In another example, in one embodiment, the first real impedance value may be substantially  $4 \Omega$ , the second real impedance value may be substantially  $40 \Omega$ , the first imaginary impedance value may be substantially  $-4 \text{ j}\Omega$ , and the second imaginary impedance value may be substantially  $\text{j}50 \Omega$ . A wide range of complex impedance values may be presented to the filter circuit 1126 given the design parameters and the potential number of receivers. As such, ranges and ratios contemplated by various exemplary embodiments described herein may substantially vary from the specific examples provided herein.

**[0092]** According to certain embodiments, a passive or fixed filter circuit 1326 (i.e., substantially all of the components of the filter circuit 1326 may be passive circuit elements) as shown in FIG. 13 may be provided. The circuitry would have an absence

of dynamic switching in of reactive elements. As such, the filter circuit 1125 may not require control signals or other dynamic logic to control or configure the circuit as the load changes during operation. This may reduce cost and complexity and may provide other benefits as will be appreciated by one/those skilled in the art.

**[0093]** In some embodiments, a driver circuit 1324 may generate harmonics of 6.78 MHz, when the operating frequency of the driver circuits 1324 is substantially 6.78 MHz. For various reasons, including for meeting regulatory requirements, the filter circuit 1326 may be further configured to reduce unwanted harmonics produced by the driver circuit 1324. By using information derived from the plots such as FIGS. 9 and 10, the filter circuit 1326 may be designed (in various embodiments) to meet spectral emission mask requirements (via reducing harmonics), ensure that the load impedance at which maximum power may be delivered is above the load at which maximum efficiency is achieved, and/or expand the range of load impedance values for which the driver circuit 1324 is highly efficient.

#### Exemplary Filter Circuit Operation

**[0094]** FIG. 15 is a plot showing the impedance transformed by the filter circuit 1326 versus the impedance presented to the transmit circuit 1350 as mapped to a high efficiency contour. For example, to illustrate the operation of the filter circuit 1326, FIG. 15 shows an exemplary result of a filter circuit 1326 configured to match the theoretical single sided driver circuit 724 and having the load contours shown in FIG. 10B. While specific values are described, it is noted that these values are merely exemplary and for purposes of illustration of the operation of the filter circuit for one particular driver circuit configuration, and a wide variety of other values are contemplated according to the principles described herein. Two circles 1502 and 1504 are shown in FIG. 15. One circle 1502, centered at  $R_{in}(XFRM) = 0+0 j$ , defines  $Z_{in}(XFRM)$  for an  $R_{in}(TX)$  variation from 0 to 1000 ohms, in 5 ohm steps, with  $X_{in}(TX) = 0$ . The path proceeds in a counter clockwise direction as  $R_{in}(TX)$  increases. The radius of this circle (defined as  $R_d$ ) is 16.55 ohms, selected to match the 100% efficiency theoretical contour 902 of FIG. 10B. Since the markers are for  $R_{in}(TX)$  5 ohms apart, it is noted that  $Z_{in}(XFRM)$  peaks when  $Z_{in}(TX) = 25+j0$  Ohms. This defines the impedance transform ratio of the circuit, and can be set as desired. For

variations in  $R_{in(TX)}$  given other values of  $X_{in(TX)}$ , it is noted that the ratios result in circles that all pass through  $Z_{in(XFRM)} = 0, -16.55j$ .