(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第4286097号

(P4286097)

(45) 発行日 平成21年6月24日(2009.6.24)

(24) 登録日 平成21年4月3日(2009.4.3)

(51) Int.CI.

H01S 5/22 (2006.01)

F 1

H01S 5/22

請求項の数 17 (全 22 頁)

(21) 出願番号 特願2003-336765 (P2003-336765)

(22) 出願日 平成15年9月29日 (2003.9.29)

(65) 公開番号 特開2005-108917 (P2005-108917A)

(43) 公開日 平成17年4月21日 (2005.4.21)

審査請求日 平成17年9月1日 (2005.9.1)

(73) 特許権者 000001889

三洋電機株式会社

大阪府守口市京阪本通2丁目5番5号

(74) 代理人 100104433

弁理士 宮園 博一

(72) 発明者 井上 大二朗

大阪府守口市京阪本通2丁目5番5号 三

洋電機株式会社内

(72) 発明者 畑 雅幸

大阪府守口市京阪本通2丁目5番5号 三

洋電機株式会社内

(72) 発明者 野村 康彦

大阪府守口市京阪本通2丁目5番5号 三

洋電機株式会社内

最終頁に続く

(54) 【発明の名称】半導体レーザ素子および半導体レーザ装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1導電型の第1クラッド層と、

前記第1クラッド層上に形成された活性層と、

前記活性層上に形成され、平坦部と、前記平坦部から突出するように形成されたリッジ部を構成する凸部とを有する第2導電型の第2クラッド層と、

前記第2クラッド層の平坦部上における前記凸部近傍に形成された第1の絶縁物の層と

前記第2のクラッド層の平坦部上における前記凸部から離れた部分に形成された第2の絶縁物の層とを備え、

前記第1の絶縁物の層は、前記第2のクラッド層の平坦部上において前記凸部から離れた部分にまで延在して形成され、

前記第2の絶縁物の層は、前記第1の絶縁物の層上に形成されていることを特徴とする半導体レーザ素子。

## 【請求項 2】

前記第2の絶縁物の層は、前記第1の絶縁物の層よりも厚みが大きい、請求項1に記載の半導体レーザ素子。

## 【請求項 3】

前記第2の絶縁物の層の上面の高さは、前記凸部を含むリッジ部の上面の高さと実質的に等しい、請求項1または2に記載の半導体レーザ素子。

10

20

**【請求項 4】**

第 1 導電型の第 1 クラッド層と、

前記第 1 クラッド層上に形成された活性層と、

前記活性層上に形成され、平坦部と、前記平坦部から突出するように形成されたリッジ部を構成する凸部とを有する第 2 導電型の第 2 クラッド層と、

前記第 2 クラッド層の平坦部上における前記凸部近傍に形成されると共に、前記第 2 のクラッド層の平坦部上において前記凸部から離れた部分にまで延在して形成される第 1 の絶縁物の層と、

前記第 2 のクラッド層の平坦部上における前記凸部から離れた部分において、前記第 1 の絶縁物の層上に形成された第 2 の絶縁物の層と、

前記第 1 の絶縁物の層および前記第 2 の絶縁物の層の上に形成され、前記第 2 クラッド層の凸部に電気的に接続するように形成された金属層とを備え、

前記凸部は、前記第 2 クラッド層の平坦部の中央部付近に形成され、

前記第 2 の絶縁物の層の側面が順テーパ形状であることを特徴とする、半導体レーザ素子。

**【請求項 5】**

前記第 2 の絶縁物の層は、前記第 1 の絶縁物の層よりも厚みが大きい、請求項 4 に記載の半導体レーザ素子。

**【請求項 6】**

前記第 2 の絶縁物の層の上面の高さは、前記凸部を含むリッジ部の上面の高さと実質的に等しい、請求項 4 または 5 に記載の半導体レーザ素子。

**【請求項 7】**

前記第 2 クラッド層上に形成された第 2 導電型のコンタクト層とを備えた、請求項 4 ~ 6 のいずれか 1 項に記載の半導体レーザ素子。

**【請求項 8】**

前記金属層に接触するように形成された放熱部材とを備えた、請求項 4 ~ 7 のいずれか 1 項に記載の半導体レーザ装置。

**【請求項 9】**

第 1 導電型の第 1 クラッド層と、

前記第 1 クラッド層上に形成された活性層と、

前記活性層上に形成され、平坦部と、前記平坦部から突出するように形成されたリッジ部を構成する凸部とを有する第 2 導電型の第 2 クラッド層と、

前記第 2 クラッド層の平坦部上における前記凸部近傍に形成されると共に、前記第 2 のクラッド層の平坦部上において前記凸部から離れた部分にまで延在して形成される第 1 の絶縁物の層と、

前記第 2 のクラッド層の平坦部上における前記凸部から離れた部分において、前記第 1 の絶縁物の層上に形成された第 2 の絶縁物の層と、

前記第 1 の絶縁物の層および前記第 2 の絶縁物の層の上に形成され、前記第 2 クラッド層の凸部に電気的に接続するように形成された金属層とを備え、

前記凸部は、前記第 2 クラッド層の平坦部の中央部付近に形成され、

前記第 2 の絶縁物の層の側面上の前記金属層の表面が順テーパ形状であることを特徴とする、半導体レーザ素子。

**【請求項 10】**

前記第 2 の絶縁物の層は、前記第 1 の絶縁物の層よりも厚みが大きい、請求項 9 に記載の半導体レーザ素子。

**【請求項 11】**

前記第 2 の絶縁物の層の上面の高さは、前記凸部を含むリッジ部の上面の高さと実質的に等しい、請求項 9 または 10 に記載の半導体レーザ素子。

**【請求項 12】**

前記第 2 クラッド層上に形成された第 2 導電型のコンタクト層とを備えた、請求項 9 ~

10

20

40

50

1 1 のいずれか 1 項に記載の半導体レーザ素子。

**【請求項 1 3】**

前記金属層に接触するように形成された放熱部材とを備えた、請求項 9 ~ 1 2 のいずれか 1 項に記載の半導体レーザ装置。

**【請求項 1 4】**

第 1 導電型の第 1 クラッド層を形成する工程と、

前記第 1 クラッド層上に活性層を形成する工程と、

前記活性層上に第 2 導電型の第 2 クラッド層を形成する工程と、

前記第 2 クラッド層上に、平坦部と、前記平坦部から突出するように形成されたリッジ部を構成する凸部とを形成する工程と、

前記第 2 クラッド層の平坦部上における前記凸部近傍に第 1 の絶縁物の層を形成する工程と、

前記凸部上及び前記第 1 の絶縁物の層上に、第 2 の絶縁物の層を形成する工程と、

前記第 2 の絶縁物の層上にマスク層を形成する工程と、

前記マスク層が形成されていない前記凸部上及び前記凸部近傍上の前記第 2 の絶縁物の層をエッチングにより除去する工程と、を備える、半導体レーザ素子の製造方法。

**【請求項 1 5】**

前記第 2 の絶縁物の層を、前記第 1 の絶縁物の層よりも大きい厚みとなるように形成する、請求項 1 4 に記載の半導体レーザ素子の製造方法。

**【請求項 1 6】**

前記第 2 の絶縁物の層の側面が順テーパ形状となるように、前記第 2 の絶縁物の層を除去する、請求項 1 4 または 1 5 に記載の半導体レーザ素子の製造方法。

**【請求項 1 7】**

前記第 1 の絶縁物の層および前記第 2 の絶縁物の層の上に、前記第 2 クラッド層の凸部に電気的に接続するように金属層を形成する工程を、さらに備える、請求項 1 4 ~ 1 6 のいずれか 1 項に記載の半導体レーザ素子の製造方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0 0 0 1】**

本発明は、半導体レーザ素子および半導体レーザ装置に関し、特に、絶縁物からなる電流ブロック層を有するリッジ導波型の半導体レーザ素子および半導体レーザ装置に関する。

**【背景技術】**

**【0 0 0 2】**

従来、半導体レーザ素子は、光ディスクシステムにおける記録用光源として用いられている。近年では、記録速度の向上のために、半導体レーザ素子のレーザ出力の高出力化が図られている。また、従来の光ディスクシステム用の半導体レーザ素子としては、出射ビームの安定性などの観点から、リッジ導波型の半導体レーザ素子が一般的に用いられている。このリッジ導波型の半導体レーザ素子において、記録速度の向上を実現するためには、レーザ出力の高出力化に加えて、動作速度を向上させる必要がある。

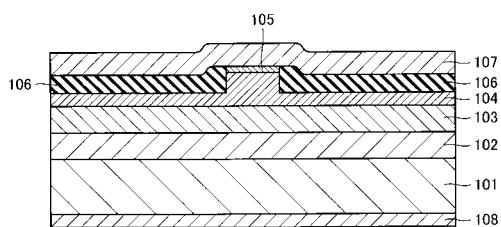

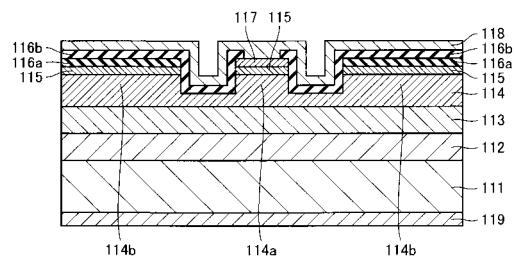

**【0 0 0 3】**

図 1 9 は、従来の一例によるリッジ導波型の半導体レーザ素子を示した断面図である。図 1 9 を参照して、従来の一例によるリッジ導波型の半導体レーザ素子では、第 1 導電型の基板 1 0 1 上に、第 1 導電型の第 1 クラッド層 1 0 2 が形成されている。第 1 クラッド層 1 0 2 上には、発光層として機能する活性層 1 0 3 が形成されている。活性層 1 0 3 上には、平坦部と、平坦部の中央部から突出するように形成された凸部（リッジ部）とを有する第 2 導電型の第 2 クラッド層 1 0 4 が形成されている。第 2 クラッド層 1 0 4 の凸部上には、コンタクト層 1 0 5 が形成されている。なお、第 2 クラッド層 1 0 4 の凸部と、コンタクト層 1 0 5 とによって、リッジ部が構成されている。このリッジ部の側面と、第

10

20

30

40

50

2 クラッド層 104 の平坦部とを覆うように、電流ブロック層 106 が形成されている。また、電流ブロック層 106 およびコンタクト層 105 上には、コンタクト層 105 の上面にオーミック接触するように、p 側電極 107 が形成されている。また、第 1 導電型の基板 101 の裏面にオーミック接触するように、n 側電極 108 が形成されている。

#### 【0004】

ここで、図 19 に示した従来の一例によるリッジ導波型の半導体レーザ素子において、電流ブロック層 106 は、リッジ部のみに電流を供給するための電流阻止層としての機能と、リッジ部に対して屈折率差を設けて光閉じ込めを行う機能との 2 つの機能を有している。また、電流ブロック層 106 は、第 1 導電型の半導体または絶縁物から構成されている。この場合、半導体レーザ素子の高速動作のためには、半導体に比べて容量値を低減しやすい絶縁物を用いるのが好ましい。10

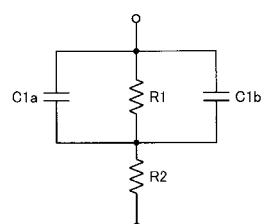

#### 【0005】

半導体レーザ素子の高周波動作特性は、通常、等価回路によって議論される。図 20 は、図 19 に示した従来の一例によるリッジ導波型の半導体レーザ素子の等価回路を簡易的に示した図である。図 20 を参照して、リッジ部の抵抗に相当する抵抗 R1 に対して、両側の電流ブロック層 106 による容量 C1a と C1b とが並列に発生する。そして、抵抗 R1、容量 C1a および C1b に対して、直列に、第 2 クラッド層 104 の平坦部以下の各層の抵抗に相当する抵抗 R2 が接続されている。動作速度を向上させるためには、図 20 に示した抵抗 R1 および R2 の抵抗値と、容量 C1a および C1b の容量値とを低減する必要がある。このうち、抵抗値に関しては、材料特性上の制約から大幅に低減することが困難な場合が多い。その一方、下記の式(1)に示すように、容量値 C は、構成材料の誘電率 ε と、電流ブロック層 106 の形成面積 S とに比例し、空乏化した部分の膜厚である絶縁物からなる電流ブロック層 106 の膜厚 d に反比例する。このため、誘電率 ε の小さい材料を用いたり、電流ブロック層 106 の形成面積 S を小さくしたり、または、電流ブロック層 106 の膜厚 d を大きくすることによって、容量 C1a および C1b の容量値を低減することが理論的には可能である。20

#### 【0006】

$$C = S / d \quad \dots \quad (1)$$

しかし、上記した容量値を低減する方法のうち、電流ブロック層 106 の誘電率 ε を小さくする方法については、電流ブロック層 106 が光閉じ込め層としての機能を有しているため、誘電率 ε を小さくしすぎると、半導体からなるリッジ部との屈折率差が大きくなつて光閉じ込めが強くなりすぎる。これにより、半導体レーザ素子の発振特性が劣化してしまうという不都合が生じる。また、電流ブロック層 106 の形成面積 S を小さくする方法では、放熱特性を向上させるために、電流ブロック層 106 の上部に熱伝導率の高い金属層やヒートシンク（放熱部材）を装着する場合に、電流ブロック層 106 の形成面積 S が小さいと、ヒートシンクなどとの接着面積が小さくなる。この場合には、放熱が十分に行えなくなるとともに、接着強度が弱くなるという不都合が生じる。また、電流ブロック層の形成面積 S を小さくすると、チップのハンドリングが困難になるという不都合も生じる。30

#### 【0007】

また、電流ブロック層 106 の膜厚 d を大きくする方法では、電流ブロック層を構成する絶縁物は熱伝導率が小さいため、その絶縁物の膜厚を大きくすると、レーザ素子動作中に最も発熱が大きいリッジ部近傍からの放熱を十分に行えなくなるという不都合が生じる。これにより、半導体レーザ素子の発光部となる p-n 接合部の温度が上昇するので、動作電流が増大するという不都合が生じる。40

#### 【0008】

そこで、従来、上記のような不都合を生じることなく、電流ブロック層の膜厚 d を大きくする方法により容量値を低減することが可能な構造が提案されている（たとえば、特許文献 1 参照）。

#### 【0009】

10

20

30

40

50

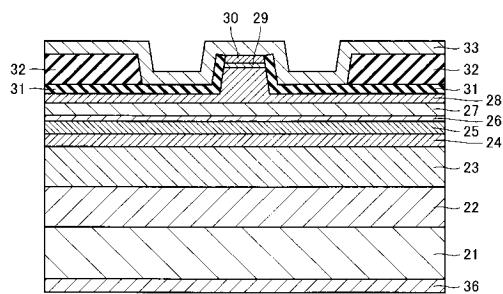

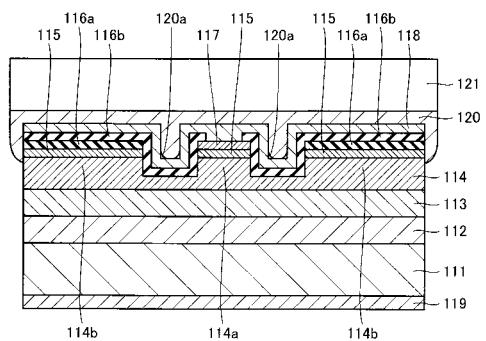

この特許文献 1 に提案された従来の他の例によるリッジ導波型構造の半導体レーザ素子では、図 2 1 に示すように、第 1 導電型の基板 111 上に、第 1 導電型の第 1 クラッド層 112、活性層 113 および第 2 導電型の第 2 クラッド層 114 が順次形成されている。第 2 導電型の第 2 クラッド層 114 には、リッジ部を構成する凸部 114a と、リッジ部を構成する凸部 114a の両側に所定の間隔を隔ててリッジ部を構成しない 2 つの凸部 114b とが設けられている。この凸部 114a および 114b は同じ高さで形成されている。また、第 2 クラッド層 114 の凸部 114a および 114b 上には、オーム接触層（コンタクト層）115 が形成されている。リッジ部を構成する凸部 114a 上のコンタクト層 115 上には、p 側電極 117 が形成されている。また、リッジ部を構成しない凸部 114b 上には、絶縁膜 116a が形成されている。また、リッジ部の上面の一部以外の全面を覆うように絶縁膜 116b が形成されている。また、全面を覆うとともに p 側電極 117 の上面に接触するように、p 側パッド電極 118 が形成されている。また、第 1 導電型の基板 111 の裏面上には、n 側電極 119 が形成されている。

#### 【0010】

ここで、図 2 1 に示した従来の提案された他の例によるリッジ導波型の半導体レーザ素子では、第 2 クラッド層 114 のリッジ部を構成する凸部 114a の近傍に、絶縁膜 116b のみが形成されるとともに、リッジ部を構成しない凸部 114b 上には、絶縁膜 116a および絶縁膜 116b の 2 層が形成されている。このため、リッジ部を構成する凸部 114a の近傍では、絶縁物は絶縁膜 116b のみの厚みになるとともに、リッジ部を構成しない凸部 114b 上では、絶縁物は、2 層の絶縁膜 116a および 116b によって絶縁膜 116b のみの場合よりも大きな厚みになる。これにより、リッジ部近傍の絶縁物の厚みを小さくしながら、リッジ部近傍以外の部分での絶縁物の厚み d をある程度増加させることができる。したがって、図 2 1 に示した従来の他の例によるリッジ導波型の半導体レーザ素子では、リッジ部近傍の絶縁膜の厚みを小さくすることにより上記したリッジ部近傍からの放熱を十分に行えなくなるという不都合が生じるのを抑制しながら、リッジ部近傍以外の絶縁膜の厚みをある程度大きくすることにより上記した式（1）の容量値 C をある程度低減することが可能になる。

#### 【0011】

また、図 2 2 には、図 2 1 に示した従来の他の例による半導体レーザ素子のリッジ部側に、半田からなる融着層 120 を介して、放熱部材としてのヒートシンク 121 を取り付けた構造が示されている。図 2 2 に示したようなヒートシンク 121 を取り付ける場合に、リッジ部を構成しない凸部 114b 上に形成された 2 層の絶縁膜 116a および 116b の上面の高さを、リッジ部を構成する凸部 114a 上に形成される 1 層の絶縁膜 116b の上面の高さよりも大きくすると、リッジ部を構成しない凸部 114b 上に形成された 2 層の絶縁膜 116a および 116b の上面によりヒートシンク 121 が支持された構造になる。このような構造の場合、リッジ部とヒートシンク 121 との間の距離が大きくなるので、半田からなる融着層 120 は、リッジ部とヒートシンク 121 との間に十分に充填されずに、空洞（図示せず）が形成される場合がある。このようにリッジ部とヒートシンク 121 との間に空洞が形成されると、放熱を十分に行なうことが困難になるという不都合がある。また、リッジ部を構成する凸部 114a 上の 1 層の絶縁膜 116b の上面の高さを、リッジ部を構成しない凸部 114b 上に形成された 2 層の絶縁膜 116a および 116b の上面の高さよりも大きくすると、リッジ部のみによりヒートシンク 121 が支持された構造になるため、ヒートシンク 121 の装着時にリッジ部への応力集中が発生するという不都合がある。

#### 【0012】

上記した不都合を防止するため、図 2 2 に示したようなヒートシンク 121 を装着する構造では、リッジ部を構成する凸部 114a 上の 1 層の絶縁膜 116b の上面の高さと、リッジ部を構成しない凸部 114b 上に形成された 2 層の絶縁膜 116a および 116b の上面の高さとを、ほぼ同じにする必要がある。

**【発明の開示】****【発明が解決しようとする課題】****【0013】**

図22に示した従来の他の例による半導体レーザ素子では、上記のように、リッジ部を構成する凸部114a上に形成される1層の絶縁膜116bの上面の高さと、リッジ部を構成しない凸部114b上に形成される2層の絶縁膜116aおよび116bの上面の高さとをほぼ同じにする必要があるため、リッジ部近傍の絶縁膜の厚みを小さくしながら、リッジ部近傍以外の部分の絶縁膜の厚みをこれ以上増加するには困難であった。すなわち、図22に示した従来の他の例による半導体レーザ素子において、リッジ部近傍の絶縁膜の厚みを小さくしながら、リッジ部近傍以外の部分の絶縁膜の厚みを増加させようとすると、リッジ部を構成しない凸部114b上に形成される2層の絶縁膜116aおよび116bのうちの下層の絶縁膜116aの厚みを増加する必要がある。

10

**【0014】**

しかしながら、下層の絶縁膜116aの厚みを増加すると、リッジ部を構成しない凸部114b上に形成される2層の絶縁膜116aおよび116bの上面の高さが、リッジ部を構成する凸部114a上に形成される1層の絶縁膜116bの上面の高さよりも高くなる。この場合には、上記したように、リッジ部を構成しない凸部114b上に形成された2層の絶縁膜116aおよび116bの上面によりヒートシンク121が支持された構造になるので、リッジ部とヒートシンク121との間に空洞が形成され、その結果、放熱を十分に行なうことが困難になるという不都合が発生する。このため、図22に示した従来の他の例による半導体レーザ素子では、2層の絶縁膜116aおよび116bからなる絶縁膜の厚みを十分に大きくするのが困難である。

20

**【0015】**

また、図22に示した従来の他の例による半導体レーザ素子では、2層の絶縁膜116aおよび116bは、リッジ部を構成する凸部114aと同じ高さを有するリッジ部を構成しない凸部114b上に形成されているので、リッジ部を構成しない凸部114b上に形成される2層の絶縁膜116aおよび116bの上面の高さと、リッジ部を構成する凸部114a上に形成される1層の絶縁膜116bの上面の高さとを同じにしようとすると、絶縁膜116aは、厚みのそれほど大きくなないp側電極117とほぼ同じ厚みで形成する必要がある。この点でも、絶縁膜116aの厚みを大きくすることは困難であるので、2層の絶縁膜116aおよび116bからなる絶縁膜の厚みを大きくするのは困難である。

30

**【0016】**

このように、図22に示した従来の他の例による半導体レーザ素子では、リッジ部近傍以外の部分に位置する2層の絶縁膜116aおよび116bからなる絶縁膜の厚みを十分に大きくするのが困難であるので、容量値Cの十分な低減効果を得ることが困難である。その結果、動作速度を十分に向上させるのが困難であるという問題点がある。

**【0017】**

また、図22に示した従来の他の例による半導体レーザ素子では、上記のように、リッジ部を構成する凸部114aと同じ高さを有するリッジ部を構成しない凸部114b上に形成される絶縁膜116aおよび116bの厚みを大きくすることが困難であるため、ヒートシンク121の装着時に、半田などからなる融着層120を融着する場合に、融着層120が、図22に示すように、チップの側面に露出した第2クラッド層114の側端面にまで達しやすいという不都合もある。このような場合には、リーク電流が流れるという問題点がある。

40

**【0018】**

この発明は、上記のような課題を解決するためになされたものであり、この発明の1つの目的は、放熱特性の低下を抑制しながら、動作速度を十分に向上させることができ、かつ、ヒートシンクを装着する場合にリーク電流が発生しにくい半導体レーザ素子および半導体レーザ装置を提供することである。

50

**【課題を解決するための手段および発明の効果】****【0019】**

この発明の第1の局面による半導体レーザ素子は、第1導電型の第1クラッド層と、第1クラッド層上に形成された活性層と、活性層上に形成され、平坦部と、平坦部から突出するように形成されたリッジ部を構成する凸部とを有する第2導電型の第2クラッド層と、第2クラッド層の凸部の側面上および平坦部上に形成され、凸部近傍に位置する第1部分の厚みが第1部分以外の第2部分の厚みよりも小さい絶縁物からなる電流ブロック層とを備えている。

**【0020】**

この第1の局面による半導体レーザ素子では、上記のように、凸部近傍に位置する第1部分の厚みが第1部分以外の第2部分の厚みよりも小さい絶縁物からなる電流ブロック層を設けることによって、凸部近傍の第1部分では、電流ブロック層を構成する熱伝導性の低い絶縁物の厚みが小さいので、放熱特性が低下するのを抑制することができる。また、絶縁物からなる電流ブロック層の凸部近傍以外の第2部分の厚みを、凸部近傍の第1部分の厚みよりも大きくすることによって、絶縁物からなる電流ブロック層の第2部分における寄生容量を低減することができる。この場合、電流ブロック層の第2部分は、第2クラッド層の平坦部上に形成されているので、リッジ部の上面と第2部分の上面と同じ高さになるようにした場合にも、平坦部からリッジ部の上面までの距離に対応する大きな厚みを有する第2部分を形成することができる。これにより、絶縁物からなる電流ブロック層の大きな厚みを有する第2部分により寄生容量を十分に低減することができるので、動作速度を十分に向上させることができる。また、上記のように、リッジ部の上面と第2部分の上面と同じ高さになるようにした場合にも、平坦部からリッジ部の上面までの距離に対応する大きな厚みを有する第2部分を形成することができるので、半田などの融着層などを介してリッジ部側にヒートシンク（放熱部材）を装着する場合に、半田などの融着層が素子端面に回り込んだ場合にも、その融着層の先端部が第2の部分の絶縁物で止まり、その下の半導体層の部分まで延びるのを抑制することができる。これにより、半田などの融着層がチップ側面に露出した半導体層に接触することに起因するリーク電流の発生を有效地に抑制することができる。

**【0021】**

上記第1の局面による半導体レーザ素子において、好ましくは、電流ブロック層の第2部分の厚みは、凸部を含むリッジ部の高さと実質的に等しい。このように構成すれば、絶縁物からなる電流ブロック層の第2部分の厚みをリッジ部の高さ分に相当する大きな厚みに形成することができるので、容易に、寄生容量を十分に低減することができる。これにより、容易に、動作速度を十分に向上させることができる。

**【0022】**

上記第1の局面による半導体レーザ素子において、好ましくは、電流ブロック層の凸部近傍に位置する第1部分のうち、凸部の両側の平坦部上に形成される部分の各々の幅は、凸部の底部の幅よりも大きい。このように構成すれば、凸部の両側の平坦部上に形成される熱伝導性の低い絶縁物からなる電流ブロック層のうち、厚みの小さい第1部分の幅を大きくすることができるので、熱伝導性の低い絶縁物に起因して放熱特性が低下するのを抑制することができる。

**【0023】**

上記第1の局面による半導体レーザ素子において、好ましくは、電流ブロック層の凸部近傍に位置する第1部分のうち、凸部の両側の平坦部上に形成される部分の各々の幅の合計幅は、第2の部分の合計幅よりも小さい。このように構成すれば、電流ブロック層の厚みが小さいために寄生容量の大きい第1部分よりも、電流ブロック層の厚みが大きいために寄生容量の小さい第2部分の方が大きくなるので、素子全体の寄生容量を有效地に低減することができる。これにより、動作速度をより向上させることができる。

**【0024】**

この発明の第2の局面による半導体レーザ装置は、第1導電型の第1クラッド層と、第

10

20

30

40

50

1 クラッド層上に形成された活性層と、活性層上に形成され、平坦部と、平坦部から突出するように形成されたリッジ部を構成する凸部とを有する第2導電型の第2クラッド層と、第2クラッド層の凸部の側面上および平坦部上に形成され、凸部近傍に位置する第1部分の厚みが第1部分以外の第2部分の厚みよりも小さい絶縁膜からなる電流ブロック層と、電流ブロック層を覆うとともに、第2クラッド層の凸部に電気的に接続するように形成された金属層と、金属層に接触するように形成された放熱部材とを備えている。

#### 【0025】

この第2の局面による半導体レーザ装置では、上記のように、凸部近傍に位置する第1部分の厚みが第1部分以外の第2部分の厚みよりも小さい絶縁物からなる電流ブロック層を設けるとともに、電流ブロック層を覆うように金属層を形成し、かつ、その金属層に接觸するように放熱部材を形成することによって、凸部近傍の第1部分では、電流ブロック層を構成する熱伝導性の低い絶縁物の厚みが小さいとともに熱伝導性に優れた金属層が形成されているので、金属層および放熱部材を介して、発光部で発生した熱を良好に放熱することができる。これにより、発光部の温度上昇を抑制することができるので、発光部の温度上昇に起因する動作電流の増大を抑制することができる。また、絶縁物からなる電流ブロック層の凸部近傍以外の第2部分の厚みを、凸部近傍の第1部分の厚みよりも大きくすることによって、絶縁物からなる電流ブロック層の第2部分における寄生容量が増加するのを抑制することができる。この場合、電流ブロック層の第2部分は、第2クラッド層の平坦部上に形成されているので、リッジ部の上面と第2部分の上面とと同じ高さになるようにした場合にも、平坦部からリッジ部の上面までの距離に対応する大きな厚みを有する第2部分を形成することができる。これにより、絶縁物からなる電流ブロック層の第2部分により寄生容量を十分に低減することができるので、動作速度を十分に向上させることができる。また、上記のように、リッジ部の上面と第2部分の上面とと同じ高さになるようにした場合にも、平坦部からリッジ部の上面までの距離に対応する大きな厚みを有する第2部分を形成することができるので、ヒートシンク（放熱部材）を装着する場合に、半田などの融着層が素子端面に回り込んだ場合にも、その融着層の先端部が第2の部分の絶縁物で止まり、その下の半導体層の部分まで延びるのを抑制することができる。これにより、半田などの融着層がチップ側面に露出した半導体層に接触することに起因するリーク電流の発生を有效地に抑制することができる。

#### 【発明を実施するための最良の形態】

#### 【0026】

以下、本発明を具体化した実施形態を図面に基づいて説明する。

#### 【0027】

##### （第1実施形態）

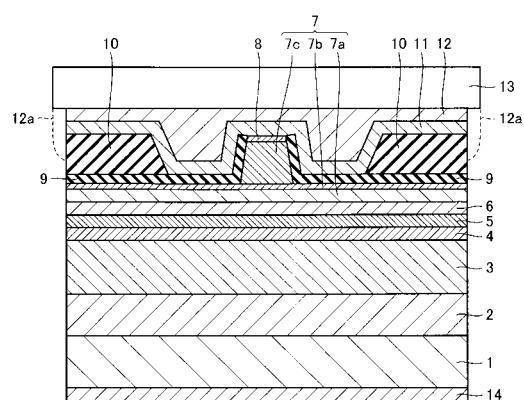

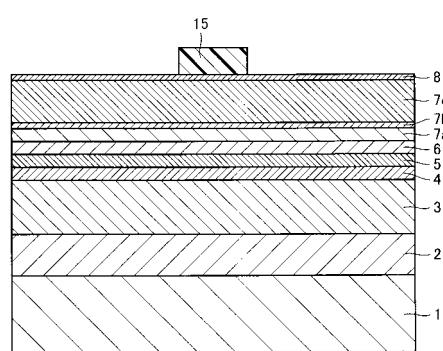

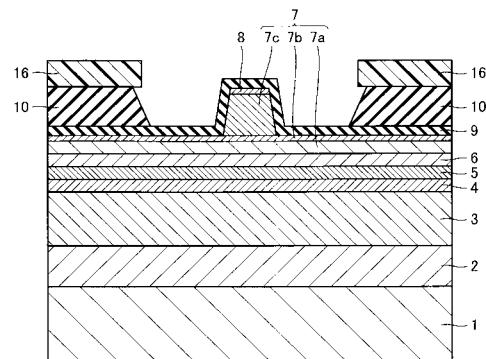

図1は、本発明の第1実施形態によるリッジ導波型の半導体レーザ装置（赤色LD）の構造を示した断面図であり、図2は、図1に示した第1実施形態による半導体レーザ装置の活性層部分の詳細構造を示した断面図である。この第1実施形態では、焼化物系半導体を用いた660nm帯の半導体レーザ素子および半導体レーザ装置（赤色LD）に本発明を適用した場合について説明する。まず、図1および図2を参照して、第1実施形態による半導体レーザ装置（赤色LD）の構造について説明する。

#### 【0028】

この第1実施形態による半導体レーザ装置では、図1に示すように、n型GaAs基板1の(100)面上に、約1μmの厚みを有するn型GaAsからなるバッファ層2が形成されている。バッファ層2上には、約2μmの厚みを有するn型(A<sub>1.0</sub>.<sub>7</sub>Ga<sub>0.3</sub>)<sub>0.5</sub>In<sub>0.5</sub>Pからなるn型クラッド層3が形成されている。なお、このn型クラッド層3は、本発明の「第1クラッド層」の一例である。

#### 【0029】

また、n型クラッド層3上には、約10nmの厚みを有するアンドープ(A<sub>1.0</sub>.<sub>5</sub>Ga<sub>0.5</sub>)<sub>0.5</sub>In<sub>0.5</sub>Pからなるn側光ガイド層4が形成されている。そして、このn側光ガイド層4上には、多重量子井戸構造を有するMQW(MultipeQua

10

20

30

40

50

antum Well) 活性層 5 が形成されている。この MQW 活性層 5 は、図 2 に示すように、約 4 nm の厚みを有するアンドープ ( $\text{Al}_{0.5}\text{Ga}_{0.5}$ )<sub>0.5</sub> $\text{In}_{0.5}$  P からなる 2 層の障壁層 5 a と、約 6 nm の厚みを有するアンドープ  $\text{In}_{0.5}\text{Ga}_{0.5}$  P からなる 3 層の井戸層 5 b とが交互に積層された構造を有する。なお、MQW 活性層 5 は、本発明の「活性層」の一例である。MQW 活性層 5 上には、約 10 nm の厚みを有するアンドープ ( $\text{Al}_{0.5}\text{Ga}_{0.5}$ )<sub>0.5</sub> $\text{In}_{0.5}$  P からなる p 側光ガイド層 6 が形成されている。

#### 【0030】

p 側光ガイド層 6 上には、図 1 に示すように、約 1.6 μm の厚みを有するとともに、中央部付近に凸部を有する p 型クラッド層 7 が形成されている。この p 型クラッド層 7 は、本発明の「第 2 クラッド層」の一例である。この p 型クラッド層 7 は、約 0.2 μm の厚みを有する p 型 ( $\text{Al}_{0.7}\text{Ga}_{0.3}$ )<sub>0.5</sub> $\text{In}_{0.5}$  P からなる第 1 p 型クラッド層 7 a と、約 10 nm の厚みを有するとともに、エッティングストップ層として機能する p 型  $\text{In}_{0.5}\text{Ga}_{0.5}$  P からなる第 2 p 型クラッド層 7 b と、約 1.4 μm の高さの台形形状を有するとともに、ストライプ状の ( $\text{Al}_x\text{Ga}_{1-x}$ )<sub>0.5</sub> $\text{In}_{0.5}$  P からなる第 3 p 型クラッド層 7 c とによって構成されている。そして、第 1 p 型クラッド層 7 a と第 2 p 型クラッド層 7 b とによって平坦部が構成され、第 3 p 型クラッド層 7 c により凸部が構成されている。台形形状の断面形状を有する第 3 p 型クラッド層 7 c は、約 2 μm の上部幅と、約 2.4 μm の下部幅（底部幅）とを有する。また、第 3 p 型クラッド層 7 c は、層内で Al 組成が変化するように設計されており、下部（底部）で  $x = 0.7$ 、上部で  $x = 0.6$  になっている。

#### 【0031】

凸部を構成する第 3 p 型クラッド層 7 c 上には、約 0.1 μm の厚みを有する p 型  $\text{In}_{0.5}\text{Ga}_{0.5}$  P 層と、約 0.2 μm の厚みを有する p 型 GaAs 層とを積層した p 型コンタクト層 8 が形成されている。第 3 p 型クラッド層 7 c と p 型コンタクト層 8 とによって、約 1.7 μm の高さを有する電流注入領域となるリッジ部が構成されている。このリッジ部の側面は、順テーパ形状を有するように形成されている。

#### 【0032】

第 3 p 型クラッド層 7 c と p 型コンタクト層 8 とにより構成されるリッジ部の側面上と、平坦部を構成する第 2 p 型クラッド層 7 b の上とに、約 0.2 μm の厚みを有する Si N からなる第 1 電流プロック層 9 が形成されている。この Si N 膜は、リッジ部との間に適度な屈折率差を設け、電流 - 光出力特性（I - L 特性）におけるキンクの発生を抑制することができる。そして、第 1 電流プロック層 9 上のリッジ部側面より約 10 μm 離れた部分から外側に、約 1.5 μm の厚みを有するポリイミド膜からなる第 2 電流プロック層 10 が形成されている。この第 2 電流プロック層 10 のリッジ部側の側面は、順テーパ形状を有するように形成されている。なお、第 1 電流プロック層 9 および第 2 電流プロック層 10 は、本発明の「電流プロック層」の一例である。

#### 【0033】

ここで、第 1 実施形態では、リッジ部近傍（第 1 部分）に、Si N からなる第 1 電流プロック層 9 が形成され、リッジ部側面から所定の距離離れたリッジ部近傍以外の部分（第 2 部分）の平坦部（第 2 p 型クラッド層 7 b）上には、Si N からなる第 1 電流プロック層 9 およびポリイミドからなる第 2 電流プロック層 10 の 2 層が形成されている。このため、リッジ部近傍以外の部分（第 2 部分）で、電流プロック層を構成する絶縁物の厚みが厚くなっている。また、リッジ部の両側に位置する第 1 電流プロック層 9 のみが形成されている第 1 部分の各々の幅は、リッジ部（第 3 p 型クラッド層 7 c）の底部の幅よりも大きくなるように形成されている。また、リッジ部の両側に位置する第 1 電流プロック層 9 のみが形成されている第 1 部分の各々の幅の合計幅は、第 1 電流プロック層 9 および第 2 電流プロック層 10 が積層された第 2 部分の合計幅よりも小さくなるように形成されている。また、第 1 電流プロック層 9 よりも厚みの大きい第 2 電流プロック層 10 を構成するポリイミド膜の比誘電率は、約 3.5 であり、第 1 電流プロック層 9 を構成する Si N の

比誘電率（約7）よりも小さい。

【0034】

また、第1実施形態では、第3p型クラッド層7cおよびp型コンタクト層8により構成されるリッジ部の高さ（約1.7μm）と、リッジ部の近傍以外の部分に形成された第1電流ブロック層9および第2電流ブロック層10からなる絶縁物の厚み（約1.7μm）とは等しくなるように形成されている。したがって、リッジ部（p型コンタクト層8）の上面の高さと、第2電流ブロック層10の上面の高さとは、ほぼ等しい。

【0035】

また、p型コンタクト層8上と、第1電流ブロック層9上と、第2電流ブロック層10上とには、下層から上層に向かって50nmの厚みを有するCr層と1μmの厚みを有するAu層とからなるp側電極11が形成されている。そして、p側電極11上には、AuSn（Sn30%）半田からなる融着層12を介して、ダイヤモンドからなるヒートシンク13が装着されている。なお、ヒートシンク13は、本発明の「放熱部材」の一例である。また、n型GaAs基板1の裏面上には、基板側から約0.2μmの厚みを有するAuGe層と約10nmの厚みを有するNi層と約0.6μmの厚みを有するAu層とからなるn側電極14が形成されている。なお、第1実施形態における半導体レーザ素子の幅は、約200μmであり、奥行きは、約1mmである。

【0036】

第1実施形態では、上記のように、リッジ部近傍では、厚みの小さい絶縁物（SiN）からなる第1電流ブロック層9のみを形成するとともに、リッジ部近傍以外の部分では、厚みの小さい絶縁物（SiN）からなる第1電流ブロック層9と厚みの大きい絶縁物（ポリイミド）からなる第2電流ブロック層10との積層膜を形成することによって、リッジ部近傍では、熱伝導性の低い絶縁物の厚みが小さいので、熱伝導性が良好な半田からなる融着層12を介して半導体レーザ素子の発光部の熱をヒートシンク13側に良好に放熱することができる。これにより、発光部の温度上昇を抑制することができるので、発光部の温度上昇に起因する動作電流の増大を抑制することができる。また、リッジ部近傍以外の部分では、第1電流ブロック層9および第2電流ブロック層10の積層構造により絶縁物の厚みを大きくすることができる。この場合、第1電流ブロック層9および第2電流ブロック層10は、p型クラッド層7の平坦部を構成する第2p型クラッド層7b上に形成されているので、リッジ部の上面と、第2電流ブロック層10の上面とを同じ高さになるようにした場合にも、平坦部からリッジ部の上面までの距離に対応する大きな厚みを有する第1電流ブロック層9および第2電流ブロック層10からなる絶縁物層を形成することができる。これにより、電流ブロック層部分の寄生容量を大幅に低減することができるので、半導体レーザ素子の動作速度を十分に向上させることができる。

【0037】

また、第1実施形態では、リッジ部の両側に位置する第1電流ブロック層9のみが形成されている第1部分の各々の幅を、リッジ部（第3p型クラッド層7c）の底部の幅よりも大きくなるように形成することによって、リッジ部の両側に位置する熱伝導性の低い絶縁膜の厚みの小さい第1部分の幅をある程度大きくすることができるので、熱伝導性の低い絶縁物に起因して放熱特性が低下するのを抑制することができる。

【0038】

また、リッジ部の両側に位置する第1電流ブロック層9のみが形成されている第1部分の各々の幅の合計幅を、第1電流ブロック層9および第2電流ブロック層10が積層された厚みの大きい第2部分の合計幅よりも小さくなるように形成することによって、絶縁膜（第1電流ブロック層9）の厚みが小さいために寄生容量の大きい第1部分よりも、絶縁膜（第1電流ブロック層9および第2ブロック層10）の厚みが大きいために寄生容量の小さい第2部分の方が大きくなるので、素子全体の寄生容量を有効に低減することができる。これにより、動作速度をより向上させることができる。

【0039】

また、第1実施形態では、素子端部においても、第1電流ブロック層9および第2電流

10

20

30

40

50

ブロック層10の積層構造により厚みの大きい絶縁膜層が形成されているので、図1に示すヒートシンク13をAuSn半田からなる融着層12を介して装着する際に、融着層12が図1の点線部分（融着層12a）のように素子の端部に回り込んだ場合にも、融着層12aの先端部分が第2電流ブロック層10の絶縁膜部分で止まり、素子端部の半導体層（第2p型クラッド層7b）まで達するのを防止することができる。これにより、融着層12aが素子端部の半導体層（第2p型クラッド層7b）に接触することによりリーク電流が流れるのを防止することができる。

#### 【0040】

また、第1実施形態では、リッジ部（p型コンタクト層8）の上面の高さと、リッジ部近傍以外の領域の第2電流ブロック層10の上面の高さとをほぼ同じにすることによって、半導体レーザ素子にヒートシンク13を装着する場合に、第2電流ブロック層10の高さがリッジ部の高さよりも大きくなりすぎた場合に発生するリッジ部とヒートシンク13との間に空洞が形成される現象を抑制することができるので、放熱特性が低下するのを抑制することができる。また、リッジ部（p型コンタクト層8）の上面の高さと、リッジ部近傍以外の領域の第2電流ブロック層10の上面の高さとをほぼ同じ高さにすることによって、ヒートシンク13の装着時にリッジ部に応力が集中するのを緩和することができる。

10

#### 【0041】

また、第1実施形態では、リッジ部の側面および第2電流ブロック層10の側面を順テーパ形状に形成することによって、図22に示した従来の他の例のように、融着層120によりヒートシンク121を取り付ける際に、融着層120とp側パッド電極118との界面に、空洞部120a（図22参照）が発生するのを抑制することができる。これにより、空洞部120aが発生することに起因する放熱特性の低下を抑制することができるので、効率よく放熱を行うことができる。これによっても、半導体レーザ装置の発光部の温度上昇を抑制することができるので、発光部の温度上昇に起因する動作電流の増加をより抑制することができる。

20

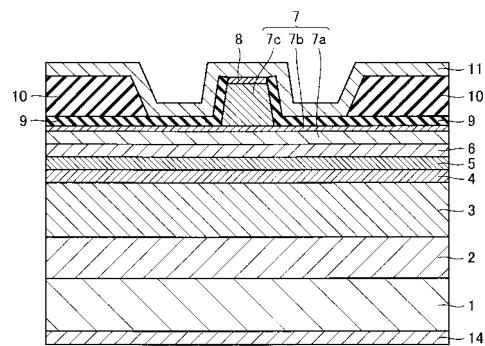

#### 【0042】

図3～図7は、図1に示した第1実施形態による半導体レーザ装置の製造プロセスを説明するための断面図である。次に、図1～図7を参照して、第1実施形態による半導体レーザ素子の製造プロセスについて説明する。

30

#### 【0043】

まず、図3に示すように、n型GaAs基板1上に、MOVPE（Metal Organic Vapor Phase Epitaxy：有機金属気相成長）法を用いて、基板温度を約800℃に保持した状態で、約1μmの厚みを有するn型GaAs層からなるバッファ層2、約2μmの厚みを有するn型（Al<sub>0.7</sub>Ga<sub>0.3</sub>）<sub>0.5</sub>In<sub>0.5</sub>Pからなるn型クラッド層3、約10nmの厚みを有するアンドープ（Al<sub>0.5</sub>Ga<sub>0.5</sub>）<sub>0.5</sub>In<sub>0.5</sub>Pからなるn側光ガイド層4、MQW活性層5、約10nmの厚みを有するアンドープ（Al<sub>0.5</sub>Ga<sub>0.5</sub>）<sub>0.5</sub>In<sub>0.5</sub>Pからなるp側光ガイド層6、約0.2μmの厚みを有するp型（Al<sub>0.7</sub>Ga<sub>0.3</sub>）<sub>0.5</sub>In<sub>0.5</sub>Pからなる第1p型クラッド層7a、約10nmの厚みを有するp型（Al<sub>0.5</sub>Ga<sub>0.5</sub>）<sub>0.5</sub>In<sub>0.5</sub>Pからなる第2p型クラッド層7b、約1.4μmの厚みを有するp型（Al<sub>x</sub>Ga<sub>1-x</sub>）<sub>0.5</sub>In<sub>0.5</sub>Pからなる第3p型クラッド層7c、および、約0.1μmの厚みを有するp型In<sub>0.5</sub>Ga<sub>0.5</sub>P層と約0.2μmの厚みを有するp型GaAs層とを積層したp型コンタクト層8を順次形成する。

40

#### 【0044】

なお、MQW活性層5は、図2に示したように、約6nmの厚みを有するアンドープIn<sub>0.5</sub>Ga<sub>0.5</sub>Pからなる3層の井戸層5bと、約4nmの厚みを有するアンドープ（Al<sub>0.5</sub>Ga<sub>0.5</sub>）<sub>0.5</sub>In<sub>0.5</sub>Pからなる2層の障壁層5aとを交互に成長させることによって形成する。

#### 【0045】

50

また、図3に示したp型コンタクト層8上の所定領域に、フォトレジスト15を形成する。そして、フォトレジスト15をマスクとして、たとえば、シュウ酸系エッティング液を用いて、p型コンタクト層8および第3p型クラッド層7cを、図4に示すように、第2p型クラッド層7bが露出するまでウェットエッティングする。これにより、素子中央部付近に電流注入領域となるリッジ部が形成される。この場合、第3p型クラッド層7cのA1組成を層内で変化させているため、サイドエッティング速度が上部にいくほど小さくなる。つまり、上部に行くほどサイドエッティングされにくくなる。このため、ウェットエッティングを行った場合にも、上部が下部に対して小さくなりすぎて電気抵抗が増大するという不都合が発生するのを防止することができるとともに、リッジ部の上部と下部との幅の差を適度に制御して順テーパ形状にすることができる。この後、フォトレジスト15を除去する。

#### 【0046】

次に、図5に示すように、プラズマCVD(Chemical Vapor Deposition: 化学気相堆積)法を用いて、SiN膜からなる第1電流プロック層9を約0.2μmの厚みで形成する。そして、ポリイミド膜(図示せず)を全面に塗布してベーキングにより固化させた後、そのポリイミド膜上に、リッジ部を中心に約25μmの開口部を有するフォトレジスト16を形成する。そして、そのフォトレジスト16をマスクとして、たとえば、ヒドラジンヒドロードを用いて、ポリイミド膜をエッティングすることにより、図5に示したように、リッジ部から約10μmの間隔をあけた部分に、ポリイミド膜からなる第2電流プロック層10が形成される。このポリイミド膜からなる第2電流プロック層10は、約1.5μmの厚みを有するように形成する。この場合、第2電流プロック層10の側面はウェットエッティングにより順テーパ形状になる。この後、フォトレジスト16を除去する。

#### 【0047】

次に、図6に示すように、リッジ部に開口部を有するフォトレジスト17を形成する。そして、このフォトレジスト17をマスクとして、p型コンタクト層8上の第1電流プロック層9をエッティングすることにより、p型コンタクト層8の上面を露出させる。この後、フォトレジスト17を除去する。

#### 【0048】

次に、図7に示すように、真空蒸着法を用いて、約50nmの厚みを有するCr層(下層)と約1μmの厚みを有するAu層(上層)とからなるp側電極11を形成する。この場合、リッジ部の側面および第2電流プロック層10の側面が順テーパ形状になっているので、p側電極11は、全域に亘って空洞なく形成されるとともに、p側電極11の表面も順テーパ形状になる。

#### 【0049】

この後、n型GaAs基板1の裏面を酒石酸などを用いてエッティングすることにより、たとえば、n型GaAs基板1を100μm程度の厚みまで薄くする。そして、そのn型GaAs基板1の裏面上に、真空蒸着法を用いて、基板側から、0.2μmの厚みを有するAuGe層、約10nmの厚みを有するNi層および約0.6μmの厚みを有するAu層からなるn側電極14を形成する。この後、へき開およびブレーキングを行うことによって、図7に示したような第1実施形態による半導体レーザ素子が製造される。

#### 【0050】

その後、図1に示したように、AuSn(Sn30%)半田からなる融着層12を用いて、ダイヤモンドからなるヒートシンク13を装着することによって、図1に示したような半導体レーザ装置(赤色LD)が形成される。この場合、p側電極11の表面も順テーパ形状であるため、融着層12を融着した場合に空洞部が形成されることがない。このため、空洞部が発生することに起因する放熱特性の低下を防止することができる。

#### 【0051】

この後、ヒートシンク13をステム(図示せず)に取り付けた後、ワイヤボンドを行うとともに、キャップ封入を行うようにしてもよい。

10

20

30

40

50

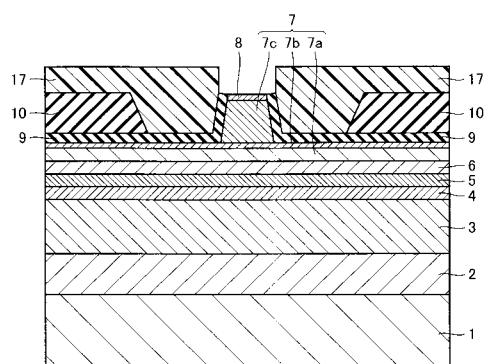

(第2実施形態)

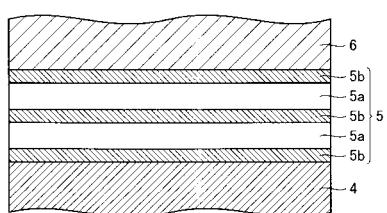

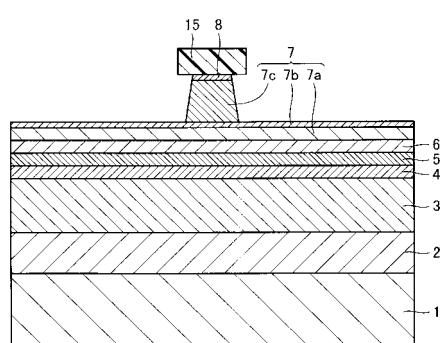

図8は、本発明の第2実施形態による半導体レーザ装置(青紫色LD)を示した断面図であり、図9は、図8に示した第2実施形態による半導体レーザ装置の活性層部分の詳細を示した断面図である。図8および図9を参照して、この第2実施形態では、窒化物系半導体を用いた400nm帯の半導体レーザ素子および半導体レーザ装置(青紫色LD)に本発明を適用した場合について説明する。

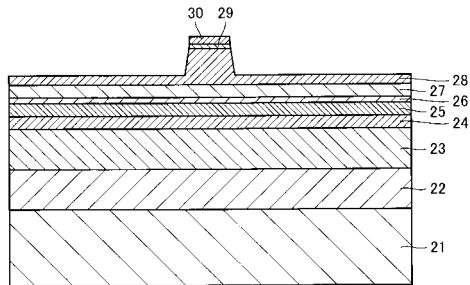

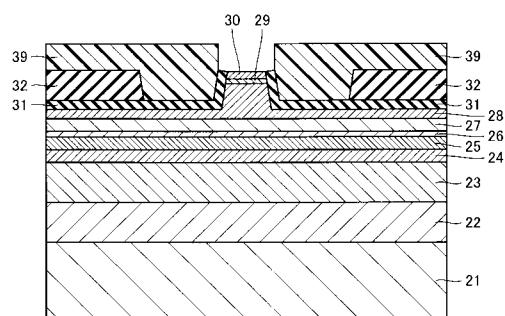

**【0052】**

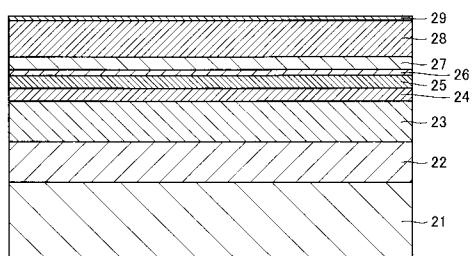

この第2実施形態による半導体レーザ装置では、図8に示すように、(0001)Ga面を表面とするn型GaN基板21上に、約1μmの厚みを有するn型GaN層からなるバッファ層22が形成されている。このバッファ層22上には、約1μmの厚みを有するn型Al<sub>0.15</sub>Ga<sub>0.85</sub>Nからなるn型クラッド層23が形成されている。なお、n型クラッド層23は、本発明の「第1クラッド層」の一例である。10

**【0053】**

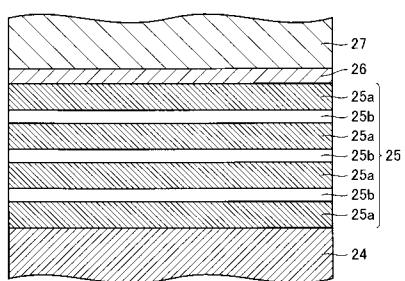

n型クラッド層23上には、約0.1μmの厚みを有するn型GaNからなるn型光ガイド層24が形成されている。n型光ガイド層24上には、多重量子井戸構造を有するMQW活性層25が形成されている。このMQW活性層25は、図9に示すように、約15nmの厚みを有するアンドープGa<sub>0.95</sub>In<sub>0.05</sub>Nからなる4層の障壁層25aと、約4nmの厚みを有するアンドープGa<sub>0.9</sub>In<sub>0.1</sub>Nからなる3層の井戸層25bとが交互に積層された構造を有する。なお、MQW活性層25は、本発明の「活性層」の一例である。20

**【0054】**

MQW活性層25上には、図8に示すように、約20nmの厚みを有するアンドープAl<sub>0.3</sub>Ga<sub>0.7</sub>Nからなる保護層26が形成されている。保護層26上には、約0.1μmの厚みを有するアンドープGaNからなるp側光ガイド層27が形成されている。p側光ガイド層27上には、約0.1μmの厚みを有する平坦部と、平坦部の中央部付近に、約1.5μmの幅と約0.4μmの高さとを有するストライプ状の凸部とを有するp型Al<sub>0.15</sub>Ga<sub>0.85</sub>Nからなるp型クラッド層28が形成されている。なお、p型クラッド層28は、本発明の「第2クラッド層」の一例である。p型クラッド層28の凸部上には、約10nmの厚みを有するアンドープIn<sub>0.05</sub>Ga<sub>0.95</sub>Nからなるp側コンタクト層29が形成されている。p型クラッド層28の凸部と、p側コンタクト層29とによって、電流注入領域となるリッジ部が形成されている。このリッジ部の側面は、順テーパ形状に形成されている。30

**【0055】**

p側コンタクト層29上には、p側コンタクト層29側から、約1nmの厚みを有するPd層、約10nmの厚みを有するPt層および約0.2μmの厚みを有するAu層からなるp側電極30が形成されている。また、p型クラッド層28の平坦部上と、リッジ部およびp側電極30の側面上とに、約0.1μmの厚みを有するSiO<sub>2</sub>膜からなる第1電流プロック層31が形成されている。また、リッジ部側面より約10μm離れた部分から外側の部分には、第1電流プロック層31上に、約0.5μmの厚みを有するSiO<sub>2</sub>膜からなる第2電流プロック層32が形成されている。この第2電流プロック層32の側面は、順テーパ形状に形成されている。なお、第1電流プロック層31および第2電流プロック層32は、本発明の「電流プロック層」の一例である。40

**【0056】**

このように、第2実施形態では、リッジ部近傍(第1部分)に、厚みの小さいSiO<sub>2</sub>膜からなる第1電流プロック層31のみが形成されているとともに、リッジ部近傍以外の部分(第2部分)のp型クラッド層28の平坦部上には、厚みの小さいSiO<sub>2</sub>膜からなる第1電流プロック層31と厚みの大きいSiO<sub>2</sub>膜からなる第2電流プロック層32との積層膜が形成されている。また、リッジ部の両側に位置する第1電流プロック層31のみが形成されている第1部分の各々の幅は、リッジ部(p型クラッド層28の凸部)の底部の幅よりも大きくなるように形成されている。また、リッジ部の両側に位置する第1電50

流ブロック層31のみが形成されている第1部分の各々の幅の合計幅は、第1電流ブロック層31および第2電流ブロック層32が積層された第2部分の合計幅よりも小さくなるように形成されている。

#### 【0057】

ここで、第2実施形態では、第1電流ブロック層31および第2電流ブロック層32が積層された部分の厚み(約0.6μm)が、リッジ部の高さ(約0.4μm)とp側電極30の厚み(約0.2μm)とを合計した高さ(約0.6μm)とほぼ同じ厚みになるように形成されている。したがって、第2電流ブロック層32の上面の高さと、リッジ部上のp側電極30の上面の高さとは、ほぼ等しい。

#### 【0058】

また、p側電極30、第1電流ブロック層31および第2電流ブロック層32上には、下層から上層に向かって、約0.1μmの厚みを有するTi層と約0.5μmのAu層とからなるp側パッド電極33が形成されている。p側パッド電極33上には、AuSn(Sn30%)半田からなる融着層34を介して、ダイヤモンドからなるヒートシンク35が装着されている。なお、ヒートシンク35は、本発明の「放熱部材」の一例である。また、n型GaN基板21の裏面上には、基板側から、約5nmの厚みを有するAl層、約10nmの厚みを有するPt層および約0.3μmの厚みを有するAu層からなるn側電極36が形成されている。なお、第2実施形態における素子の幅は、約200μmであり、奥行きは、約600μmである。

#### 【0059】

第2実施形態では、上記のように、リッジ部近傍では、厚みの小さいSiO<sub>2</sub>膜からなる第1電流ブロック層31のみを形成するとともに、リッジ部近傍以外の部分では、厚みの小さいSiO<sub>2</sub>膜からなる第1電流ブロック層31と厚みの大きいSiO<sub>2</sub>膜からなる第2電流ブロック層32との積層膜を形成することによって、リッジ部近傍では、熱伝導性の低い絶縁物(SiO<sub>2</sub>)の厚みが小さいので、熱伝導性が良好な半田からなる融着層34を介して半導体レーザ素子の発光部の熱をヒートシンク35側に良好に放熱することができる。ここで、窒化物系の半導体レーザにおいては、発振波長が長い他の半導体レーザに比べて、動作電圧が高いため、発熱が顕著である。このため、第2実施形態の構造を用いることにより、リッジ部で発生した熱を良好に放熱することができるので、窒化物系の半導体レーザ素子の発光部の温度上昇を有效地に抑制することができる。その結果、窒化物系半導体レーザ装置において、動作電流を低減することができる。

#### 【0060】

また、第2実施形態では、リッジ部近傍以外の部分で、第1電流ブロック層31および第2電流ブロック層32の積層構造により絶縁物の厚みを大きくすることができます。この場合、第1電流ブロック層31および第2電流ブロック層32は、p型クラッド層28の平坦部上に形成されているので、リッジ部(p側電極30)の上面と、第2電流ブロック層32の上面と同じ高さになるようにした場合にも、平坦部からリッジ部(p側電極30)の上面までの距離に対応する大きな厚みを有する第1電流ブロック層31および第2電流ブロック層32からなる絶縁物層を形成することができる。これにより、電流ブロック層部分の寄生容量値を大幅に低減することができる。特に、第2実施形態による窒化物系の短波長の半導体レーザにおいては、発振波長が長い半導体レーザに比べて、高密度記録・再生が可能な光ディスクシステムに用いられるため、高速動作が必須である。第2実施形態では、上記のように、寄生容量を大幅に低減することにより動作速度を十分向上させることができるので、窒化物系半導体レーザに求められる高い記録速度を得ることができる。

#### 【0061】

また、第2実施形態では、素子端部においても、第1電流ブロック層31および第2電流ブロック層32の積層構造により厚みの大きい絶縁膜層が形成されているので、図8に示すヒートシンク35をAuSn半田からなる融着層34を介して装着する際に、融着層34が図8の点線部分(融着層34a)のように素子の端部に回り込んだ場合にも、融着

10

20

30

40

50

層34aの先端部分が第2電流ブロック層32の絶縁膜部分で止まり、素子端部の半導体層（p型クラッド層28）まで達するのを防止することができる。これにより、融着層34aが素子端部の半導体層（p型クラッド層28）に接触することによりリーク電流が流れのを防止することができる。

#### 【0062】

また、第2実施形態では、リッジ部（p側電極30の上面）の高さと、リッジ部近傍以外の領域の第2電流ブロック層32の上面の高さとをほぼ同じにすることによって、半導体レーザ素子にヒートシンク35を装着する場合に、第2電流ブロック層32の高さがリッジ部（p側電極30の上面）の高さよりも大きくなりすぎた場合に発生するリッジ部とヒートシンク35との間に空洞が形成される現象を抑制することができる。これにより、放熱特性が低下するのを抑制することができる。また、リッジ部（p側電極30の上面）の高さと、リッジ部近傍以外の領域の第2電流ブロック層32の上面の高さとをほぼ同じにすることによって、ヒートシンク35の装着時にリッジ部に応力が集中するのを緩和することができる。10

#### 【0063】

なお、第2実施形態のその他の効果は、上記第1実施形態と同様である。

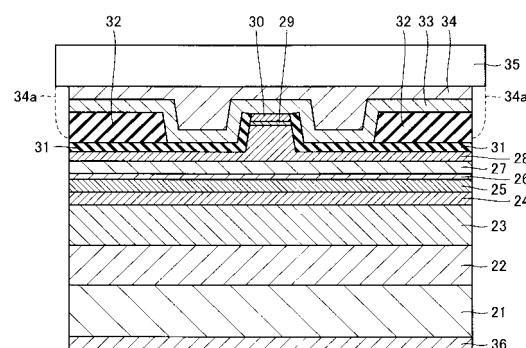

#### 【0064】

図10～図18は、図8に示した第2実施形態による半導体レーザ装置の製造プロセスを説明するための断面図である。次に、図8～図18を参照して、第2実施形態による半導体レーザ装置の製造プロセスについて説明する。20

#### 【0065】

まず、図10に示すように、MOVPE法を用いて、n型GaN基板21上に、基板温度を約1150℃に保持した状態で、約1μmの厚みを有するn型GaN層からなるバッファ層22、約1μmの厚みを有するn型Al<sub>0.15</sub>Ga<sub>0.85</sub>Nからなるn型クラッド層23、および、約0.1μmの厚みを有するn型GaNからなるn型光ガイド層24を順次成長させる。

#### 【0066】

次に、基板温度を約850℃に保持した状態で、n型光ガイド層24上に、約15nmの厚みを有するアンドープIn<sub>0.05</sub>Ga<sub>0.95</sub>Nからなる4層の障壁層25aと、約4nmの厚みを有するアンドープIn<sub>0.1</sub>Ga<sub>0.9</sub>Nからなる3層の井戸層25bとを交互に成長させることにより、MQW活性層25を形成する。30

#### 【0067】

続いて、MQW活性層25上に、約10nmの厚みを有するアンドープAl<sub>0.3</sub>Ga<sub>0.7</sub>Nからなる保護層26を成長させる。この保護層26は、MQW活性層25のIn原子が脱離するのを防止することにより、MQW活性層25の結晶品質が劣化するのを防止する機能を有する。

#### 【0068】

この後、基板温度を約1150℃に設定した状態で、保護層26上に、約0.1μmの厚みを有するアンドープGaNからなるp側光ガイド層27と、約0.5μmの厚みを有するp型Al<sub>0.15</sub>Ga<sub>0.85</sub>Nからなるp型クラッド層28とを順次成長させる。40

#### 【0069】

次に、基板温度を約850℃に保持した状態で、p型クラッド層28上に、約10nmの厚みを有するアンドープIn<sub>0.05</sub>Ga<sub>0.95</sub>Nからなるp側コンタクト層29を形成する。

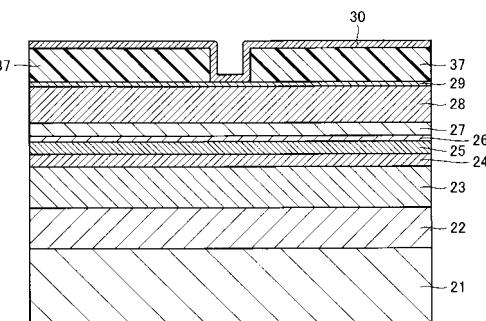

#### 【0070】

この後、図11に示すように、p側コンタクト層29上に、約1.5μm幅のストライプ状の開口部を有するフォトレジスト37を形成する。そして、全面を覆うように、真空蒸着法を用いて、下層から上層に向かって、約1nmの厚みを有するPd層、約10nmの厚みを有するPt層、および、約0.2μmの厚みを有するAu層を形成した後、フォトレジスト37をリフトオフすることにより、図12に示すような、約1.5μmの幅を50

有するストライプ形状の p 側電極 3 0 が形成される。この p 側電極 3 0 をマスクとして、たとえば、反応性イオンビームエッチャリング法を用いて、p 側コンタクト層 2 9 と、p 型クラッド層 2 8 の一部とをエッチャリングにより除去することによって、図 1 3 に示されるような、電流注入領域となるリッジ部が形成される。この場合、エッチャリング条件を適度に設定することによって、リッジ部の側面を順テーパ形状にする。

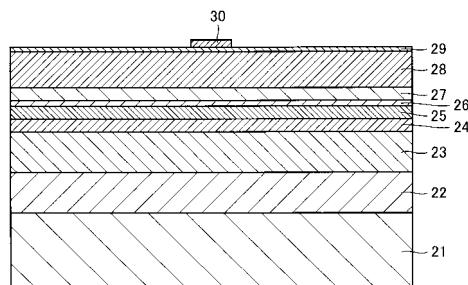

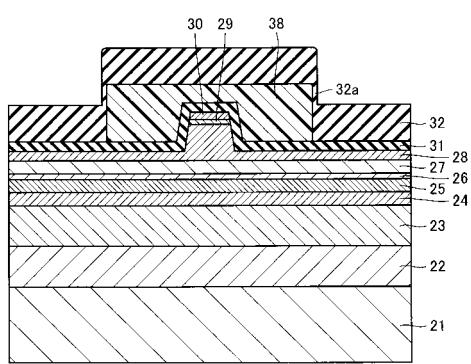

#### 【0071】

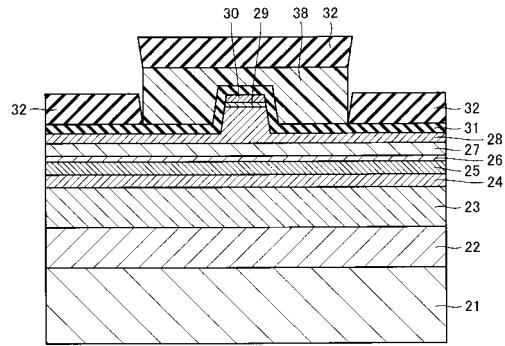

そして、図 1 4 に示すように、全面を覆うように、プラズマ CVD 法を用いて、SiO<sub>2</sub> 膜からなる第 1 電流ブロック層 3 1 を約 0.1 μm の厚みで形成する。そして、リッジ部を中心とした幅 25 μm のフォトレジスト 3 8 を形成した後、全面を覆うように、ECR (Electron Cyclotron Resonance : 電子サイクロトロン共鳴) プラズマ CVD 法を用いて、室温で SiO<sub>2</sub> 膜からなる第 2 電流ブロック層 3 2 を形成する。10 この状態で、緩衝フッ酸を用いて、短時間処理を行うことによって、フォトレジスト 3 8 の側壁部分に形成された脆弱な SiO<sub>2</sub> 膜 3 2 a (図 1 4 参照) を選択的に除去する。これにより、図 1 5 に示されるような形状が得られる。その後、リフトオフ法により、フォトレジスト 3 8 を除去することにより、図 1 6 に示されるような、順テーパ形状の側面を有する SiO<sub>2</sub> 膜からなる第 2 電流ブロック層 3 2 が、リッジ部から約 10 μm の間隔を隔てて形成される。

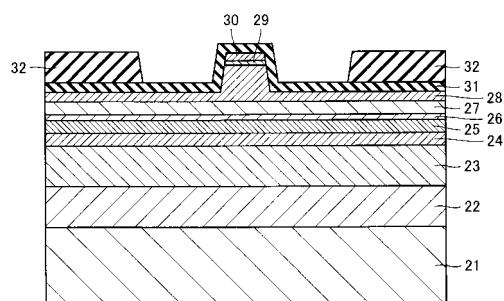

#### 【0072】

次に、図 1 7 に示すように、リッジ部に開口部を有するフォトレジスト 3 9 を形成した後、そのフォトレジスト 3 9 をマスクとして、p 側電極 3 0 上の第 1 電流ブロック層 3 1 をエッチャリングすることによって、p 側電極 3 0 の上面を露出させる。この後、フォトレジスト 3 9 を除去する。20

#### 【0073】

次に、図 1 8 に示すように、真空蒸着法を用いて、p 側電極 3 0 、第 1 電流ブロック層 3 1 および第 2 電流ブロック層 3 2 上に、下層から上層に向かって、約 0.1 μm の厚みを有する Ti 層および約 0.5 μm の厚みを有する Au 層からなる p 側パッド電極 3 3 を形成する。その場合、リッジ部および電流ブロック層段差部が順テーパ形状になっているので、p 側パッド電極 3 3 が全域に亘って空洞なく形成されるとともに、p 側パッド電極 3 3 の表面も順テーパ形状になる。この後、n 型 GaN 基板 2 1 の裏面を研磨することにより、たとえば、n 型 GaN 基板 2 1 を 100 μm 程度の厚みにする。そして、n 型 GaN 基板 2 1 の裏面上に、真空蒸着法を用いて、基板側から約 5 nm の厚みを有する Al 層、約 10 nm の厚みを有する Pt 層、および、約 0.3 μm の厚みを有する Au 層からなる n 側電極 3 6 を形成する。そして、へき開およびブレーキングを行うことによって、図 1 8 に示したような半導体レーザ素子が形成される。30

#### 【0074】

その後、図 8 に示したように、AuSn (Sn 30%) 半田からなる融着層 3 4 を介して、ヒートシンク 3 5 を装着することによって、第 2 実施形態による窒化物系の半導体レーザ装置 (青紫色 LD) が製造される。この場合、p 側パッド電極 3 3 の表面も順テーパ形状であるため、融着層 3 4 に空洞部が発生することなく、ヒートシンク 3 5 を装着することができる。40

#### 【0075】

また、ヒートシンク 3 5 をシステム (図示せず) に取り付けた後、ワイヤボンディングを行うとともに、キャップ封入を行ってもよい。

#### 【0076】

なお、今回開示された実施形態は、すべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は、上記した実施形態の説明ではなく特許請求の範囲によって示され、さらに特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれる。

#### 【0077】

たとえば、上記実施形態では、本発明を赤色半導体レーザ素子または青紫色半導体レー50

ザ素子に適用した例を示したが、本発明はこれに限らず、リッジ導波型の他の半導体レーザ素子に適用してもよい。

【0078】

また、上記実施形態では、リッジ部近傍以外の部分において、第1電流ブロック層と第2電流ブロック層との2層により電流ブロック層の厚みを大きくする例を示したが、本発明はこれに限らず、電流ブロック層を1層にして、リッジ部近傍ではその電流ブロック層の厚みを小さくするとともにリッジ部近傍以外の部分ではその単一層からなる電流ブロック層の厚みを大きくするようにしてもよい。

【図面の簡単な説明】

【0079】

10

【図1】本発明の第1実施形態による半導体レーザ装置（赤色LD）の構造を示した断面図である。

【図2】図1に示した第1実施形態による半導体レーザ装置の活性層の詳細構造を示した断面図である。

【図3】図1に示した第1実施形態による半導体レーザ装置の製造プロセスを説明するための断面図である。

【図4】図1に示した第1実施形態による半導体レーザ装置の製造プロセスを説明するための断面図である。

【図5】図1に示した第1実施形態による半導体レーザ装置の製造プロセスを説明するための断面図である。

20

【図6】図1に示した第1実施形態による半導体レーザ装置の製造プロセスを説明するための断面図である。

【図7】図1に示した第1実施形態による半導体レーザ装置の製造プロセスを説明するための断面図である。

【図8】本発明の第2実施形態による半導体レーザ装置（青紫色LD）の構造を示した断面図である。

【図9】図8に示した第2実施形態による半導体レーザ装置の活性層の詳細構造を示した断面図である。

【図10】図8に示した第2実施形態による半導体レーザ装置の製造プロセスを説明するための断面図である。

30

【図11】図8に示した第2実施形態による半導体レーザ装置の製造プロセスを説明するための断面図である。

【図12】図8に示した第2実施形態による半導体レーザ装置の製造プロセスを説明するための断面図である。

【図13】図8に示した第2実施形態による半導体レーザ装置の製造プロセスを説明するための断面図である。

【図14】図8に示した第2実施形態による半導体レーザ装置の製造プロセスを説明するための断面図である。

【図15】図8に示した第2実施形態による半導体レーザ装置の製造プロセスを説明するための断面図である。

40

【図16】図8に示した第2実施形態による半導体レーザ装置の製造プロセスを説明するための断面図である。

【図17】図8に示した第2実施形態による半導体レーザ装置の製造プロセスを説明するための断面図である。

【図18】図8に示した第2実施形態による半導体レーザ装置の製造プロセスを説明するための断面図である。

【図19】従来の一例によるリッジ導波型の半導体レーザ素子を示した断面図である。

【図20】図19に示した従来の一例による半導体レーザ素子の等価回路図である。

【図21】従来の他の例による半導体レーザ素子を示した断面図である。

【図22】図21に示した従来の他の例による半導体レーザ素子にヒートシンクを取り付

50

けた状態を示した断面図である。

【符号の説明】

【0080】

- 3、23 n型クラッド層(第1クラッド層)

- 5、25 MQW活性層(活性層)

- 7、28 p型クラッド層(第2クラッド層)

- 9、31 第1電流ブロック層(電流ブロック層)

- 10、32 第2電流ブロック層(電流ブロック層)

- 11 p側電極

- 12、34 融着層

- 13、35 ヒートシンク(放熱部材)

- 30 p側電極

- 33 p側パッド電極

10

【図1】

【図3】

【図2】

【図4】

【 図 5 】

【図6】

【 四 7 】

【 四 8 】

【 図 9 】

【図10】

【 四 1 1 】

( 図 12 )

【図13】

【図14】

【図15】

【図16】

【図17】

【図19】

【図18】

【図21】

【図22】

---

フロントページの続き

(72)発明者 山口 勤

大阪府守口市京阪本通2丁目5番5号 三洋電機株式会社内

審査官 松崎 義邦

(56)参考文献 特開平02-156588 (JP, A)

特開平11-145558 (JP, A)

特開2000-164986 (JP, A)

特開2003-069153 (JP, A)

特開平08-220358 (JP, A)

特開平06-237046 (JP, A)

特開平04-291781 (JP, A)

特開平08-111565 (JP, A)

特開平04-276682 (JP, A)

特表2003-518758 (JP, A)

国際公開第01/039342 (WO, A1)

(58)調査した分野(Int.Cl., DB名)

H01S5/00 - 5/50